(19)日本国特許庁(JP)

(12)特許公報(B2)

(11)特許番号

特許第7373346号

(P7373346)

(45)発行日 令和5年11月2日(2023.11.2)

(24)登録日 令和5年10月25日(2023.10.25)

|                        |               |

|------------------------|---------------|

| (51)国際特許分類             | F I           |

| H 04 N 25/10 (2023.01) | H 04 N 25/10  |

| H 04 N 25/17 (2023.01) | H 04 N 25/17  |

| H 04 N 25/779(2023.01) | H 04 N 25/779 |

請求項の数 12 外国語出願 (全33頁)

|                   |                             |          |                                                 |

|-------------------|-----------------------------|----------|-------------------------------------------------|

| (21)出願番号          | 特願2019-180013(P2019-180013) | (73)特許権者 | 501302980<br>フォペオン・インコーポレーテッド                   |

| (22)出願日           | 令和1年9月30日(2019.9.30)        |          | アメリカ合衆国 9 4 6 1 0 カリフォル                         |

| (65)公開番号          | 特開2020-78056(P2020-78056A)  |          | ニア州、オークランド、ウォーカーアベ                              |

| (43)公開日           | 令和2年5月21日(2020.5.21)        |          | ニュー 8 0 9 、スイート 1                               |

| 審査請求日             | 令和4年9月28日(2022.9.28)        | (74)代理人  | 110000626<br>弁理士法人英知国際特許商標事務所                   |

| (31)優先権主張番号       | 16/148,951                  | (72)発明者  | ラマスワミ、シュリ<br>アメリカ合衆国 9 5 1 3 4 カリフォル            |

| (32)優先日           | 平成30年10月1日(2018.10.1)       |          | ニア州、サンノゼ、ユニット 1 6 、カ<br>ミレ サークル 4 1 9           |

| (33)優先権主張国・地域又は機関 | 米国(US)                      | (72)発明者  | 乾 達也<br>神奈川県川崎市麻生区栗木 2 丁目 4 番 1<br>6 号 株式会社シグマ内 |

|                   |                             | (72)発明者  | 山崎 滋巳                                           |

(54)【発明の名称】 垂直検知器画素センサのためのサブサンプルされた色チャンネル読み出し配線

## (57) 【特許請求の範囲】

【請求項1】

垂直検知器色画素センサの行列を含むアレイであって、各垂直検知器色画素センサは、前記アレイの行列に配置され幾つかの色の個々の色検知器を有する、前記アレイにおける、読み出し配線構造は、

前記アレイの各行の複数の行選択ラインであって、行選択ラインの数は、前記アレイ内の前記垂直検知器色画素センサの色の数に等しい、複数の行選択ラインと、

前記アレイの各列の個々の列ラインと、

前記アレイ内の各垂直検知器色画素センサ内の個々の各色検知器の転送トランジスタであって、各転送トランジスタは、前記アレイの列に配置された色検知器と、前記色検知器が配置される前記アレイの前記列に関連付けられた列ラインとの間に結合され、各転送トランジスタは、前記垂直検知器色画素センサが配置される前記アレイの行内の前記複数の行選択ラインの1つに結合されたゲートを有する、転送トランジスタと、

を備え、

前記アレイの隣接する列内の各色検知器の前記アレイの各行内の少なくとも幾つかの前記転送トランジスタの前記ゲートは、前記アレイの前記行の前記行選択ラインの異なるものに結合される、読み出し配線構造。

## 【請求項2】

前記アレイ内の各行について、行選択ラインへの転送トランジスタのゲートの前記結合は、各色の前記アレイの第1の連続する列内の転送トランジスタのゲートが第1の命令で

前記行選択ラインに結合され、各色の前記アレイの第2の連続する列内の転送トランジスタのゲートが前記第1の命令と異なる第2の命令で前記行選択ラインに結合され、各色の前記アレイの第3の連続する列内の転送トランジスタのゲートが前記第1の命令及び前記第2の命令と異なる第3の命令で前記行選択ラインに結合される、3つの連続する列の群で繰り返される、請求項1に記載の読み出し配線構造。

#### 【請求項3】

前記第1の連続する列において、第1の色検知器の前記転送トランジスタの前記ゲートは第1の行選択ラインに結合され、第2の色検知器の前記転送トランジスタの前記ゲートは第2の行選択ラインに結合され、第3の色検知器の前記転送トランジスタの前記ゲートは第3の行選択ラインに結合され、

前記第2の連続する列において、前記第1の色検知器の前記転送トランジスタの前記ゲートは前記第3の行選択ラインに結合され、前記第2の色検知器の前記転送トランジスタの前記ゲートは前記第1の行選択ラインに結合され、前記第3の色検知器の前記転送トランジスタの前記ゲートは前記第2の行選択ラインに結合され、

前記第3の連続する列において、前記第1の色検知器の前記転送トランジスタの前記ゲートは前記第2の行選択ラインに結合され、前記第2の色検知器の前記転送トランジスタの前記ゲートは前記第3の行選択ラインに結合され、前記第3の色検知器の前記転送トランジスタの前記ゲートは前記第1の行選択ラインに結合される、請求項2に記載の読み出し配線構造。

#### 【請求項4】

前記アレイ内の各行について、行選択ラインへの転送トランジスタのゲートの前記結合は、各色の前記アレイの第1の連続する列内の転送トランジスタのゲートが第1の命令で前記行選択ラインに結合され、各色の前記アレイの第2の連続する列内の転送トランジスタのゲートが前記第1の命令と異なる第2の命令で前記行選択ラインに結合され、各色の前記アレイの第3の連続する列内の転送トランジスタのゲートが前記第1の命令及び前記第2の命令と異なる第3の命令で前記行選択ラインに結合され、各色の前記アレイの第4の連続する列内の転送トランジスタのゲートが前記第1の命令で前記行選択ラインに結合される、4つの連続する列の群で繰り返される、請求項1に記載の読み出し配線構造。

#### 【請求項5】

前記第1の連続する列において、第1の色検知器の前記転送トランジスタの前記ゲートは第1の行選択ラインに結合され、第2の色検知器の前記転送トランジスタの前記ゲートは第2の行選択ラインに結合され、第3の色検知器の前記転送トランジスタの前記ゲートは第3の行選択ラインに結合され、

前記第2の連続する列において、前記第1の色検知器の前記転送トランジスタの前記ゲートは前記第2の行選択ラインに結合され、前記第2の色検知器の前記転送トランジスタの前記ゲートは前記第3の行選択ラインに結合され、前記第3の色検知器の前記転送トランジスタの前記ゲートは前記第1の行選択ラインに結合され、

前記第3の連続する列において、前記第1の色検知器の前記転送トランジスタの前記ゲートは前記第3の行選択ラインに結合され、前記第2の色検知器の前記転送トランジスタの前記ゲートは前記第1の行選択ラインに結合され、前記第3の色検知器の前記転送トランジスタの前記ゲートは前記第2の行選択ラインに結合され、

前記第4の連続する列において、前記第1の色検知器の前記転送トランジスタの前記ゲートは前記第1の行選択ラインに結合され、前記第2の色検知器の前記転送トランジスタの前記ゲートは前記第2の行選択ラインに結合され、前記第3の色検知器の前記転送トランジスタの前記ゲートは前記第3の行選択ラインに結合される、請求項4に記載の読み出し配線構造。

#### 【請求項6】

前記アレイ内の各*i*番目の行について、各色の前記アレイの各*j*番目の列内の前記転送トランジスタは第1の命令で前記行選択ラインに結合され、各色の前記アレイの各(*j*+1)番目の列内の前記転送トランジスタは前記第1の命令と異なる第2の命令で前記行選

10

20

30

40

50

択ラインに結合され、

前記アレイ内の各( $i + 1$ )番目の行について、各色の前記アレイの各 $j$ 番目の列内の前記転送トランジスタは前記第1の命令で前記行選択ラインに結合され、各色の前記アレイの各( $j + 1$ )番目の列内の前記転送トランジスタは前記第1の命令及び前記第2の命令と異なる第3の命令で前記行選択ラインに結合される、請求項1に記載の読み出し配線構造。

#### 【請求項7】

第1の色及び第2の色の前記アレイの*i*番目の行内の前記転送トランジスタの前記ゲートは、前記アレイの隣接する列内の第1の行選択ラインと第2の行選択ラインとの間で交互になり、第3の色の前記アレイの前記*i*番目の行内の前記転送トランジスタの前記ゲートは、前記アレイ内の全ての列について第3の行選択ラインに結合され、

10

前記第1の色の前記アレイの( $i + 1$ )番目の行内の前記転送トランジスタの前記ゲートは、前記アレイ内の全ての列について第1の行選択ラインに結合され、前記第2の色及び前記第3の色の前記アレイの前記( $i + 1$ )番目の行内の前記転送トランジスタの前記ゲートは前記アレイの隣接する列内の第2の行選択ラインと第3の行選択ラインとの間で交互になる、請求項1に記載の読み出し配線構造。

#### 【請求項8】

垂直検知器色画素センサの行列を含むアレイであって、各垂直検知器色画素センサは前記アレイの行列に配置され幾つかの色の個々の色検知器を有する、前記アレイにおける、読み出し配線構造は、

20

前記アレイの各行の複数の行選択ラインであって、行選択ラインの数は、前記アレイ内の前記垂直検知器色画素センサの色の数に等しい、複数の行選択ラインと、

前記アレイの各列の個々の列ラインと、

前記アレイ内の各垂直検知器色画素センサ内の個々の各色検知器の転送トランジスタであって、各転送トランジスタは、前記アレイの列内の色検知器と、前記アレイの列ラインとの間に結合され、各転送トランジスタは、前記垂直検知器色画素センサが配置される前記アレイの行内の前記複数の行選択ラインの1つに結合されたゲートを有する、転送トランジスタと

を備え、

前記アレイの列内の垂直検知器色画素センサ内の各色検知器の前記転送トランジスタは、前記垂直検知器色画素センサが配置される前記列ラインの直前の前記列ライン、前記垂直検知器色画素センサが配置される前記列ライン、及び前記垂直検知器色画素センサが配置される前記列ラインの直後の前記列ラインの異なる1つに結合される、読み出し配線構造。

30

#### 【請求項9】

前記アレイの列内の垂直検知器色画素センサにおける第1の色検知器の前記転送トランジスタは、前記垂直検知器色画素センサが配置される前記列ラインの直前の前記列ラインに結合され、

前記アレイの列内の垂直検知器色画素センサにおける第2の色検知器の前記転送トランジスタは、前記垂直検知器色画素センサが配置される前記列ラインに結合され、

40

前記アレイの列内の垂直検知器色画素センサにおける第3の色検知器の前記転送トランジスタは、前記垂直検知器色画素センサが配置される前記列ラインの直後の前記列ラインに結合される、請求項8に記載の読み出し配線構造。

#### 【請求項10】

前記垂直検知器色画素センサのアレイは、半導体本体に配置され、

各垂直検知器色画素センサは、少なくとも、第1の個々の色センサ及び第2の個々の色センサを備え、前記第1及び第2の個々の色センサは、前記半導体本体の表面の下の異なる深さに配置され、

前記第1の個々の色センサは、捕捉された光電荷を前記第1の個々の色センサから前記半導体本体の前記表面上の第1の場所に伝導する第1のプラグに電気的に接続され、

50

前記第2の個々の色センサは、捕捉された光電荷を前記第2の個々の色センサから、前記第1の場所から離間されている、前記半導体本体の前記表面上の第2の場所に伝導する第2のプラグに電気的に接続され、

前記第1の場所及び前記第2の場所は、前記アレイの各行内の垂直検知器色画素センサの少なくとも幾つかについて異なる、請求項1に記載の読み出し配線構造。

#### 【請求項11】

前記第1の場所及び前記第2の場所は、前記アレイの各行内の隣接する垂直検知器色画素センサにおいて互いに対向する、請求項10に記載の読み出し配線構造。

#### 【請求項12】

垂直検知器色画素センサの行列を含むアレイをビデオモードで動作させる方法であって、各垂直検知器色画素センサは、個々の赤色検知器、緑色検知器及び青色検知器を有し、前記アレイの各列は1つの共通列出力ラインを有し、前記アレイの列内の垂直検知器色画素センサにおける各赤色検知器は、赤転送トランジスタを通して前記共通列出力ラインに結合され、前記アレイの列内の垂直検知器色画素センサにおける各緑色検知器は、緑転送トランジスタを通して前記共通列出力ラインに結合され、前記アレイの列内の垂直検知器色画素センサにおける各青色検知器は、青転送トランジスタを通して前記共通列出力ラインに結合され、前記アレイの行内の各赤転送トランジスタのゲートは、赤転送行ラインに結合され、前記アレイの行内の各緑転送トランジスタのゲートは、緑転送行ラインに結合され、前記アレイの行内の各青転送トランジスタのゲートは、青転送行ラインに結合され、前記方法は、

10

前記アレイの*i*番目の行毎に前記赤転送トランジスタ及び前記緑転送トランジスタを順次作動させるステップと、

20

前記アレイの(*i*+8)番目の行毎に前記緑転送トランジスタ及び前記青転送トランジスタを順次作動させるステップと

を含む、方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、画素センサに関する。より詳細には、本発明は、色画素センサ、特にカリフオルニア州サンノゼに所在のFoveon, Inc.により設計及び製造される撮像アレイ内の画素センサ等の垂直3色画素センサと、そのような撮像アレイの行/列読み出し配線に関する。

30

##### 【背景技術】

##### 【0002】

Foveon X3(登録商標)センサ等の垂直色画素センサは、非常に高い情報コンテンツを有する画像を生成する。この特性は、高品質静止画像の生成には良いが、画像毎に大量のデータを生成する。大量のデータを撮像アレイから転送する必要性は、フレームレートに制約を課し、これは、特にビデオの記録に制限を課す。

30

##### 【0003】

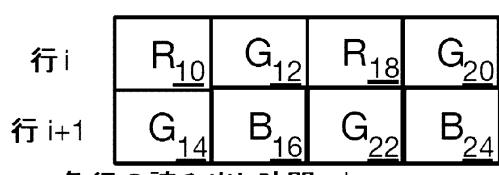

多くの従来技術による撮像システムは、ベイヤーパターンイメージャー等のモザイクイメージャーを利用する。ベイヤーパターンイメージャーにおける1つの「画素」は、実際には4個の画素センサであり、2つは、緑センサであり、1つは、赤センサであり、1つは、青センサである。ベイヤーパターンイメージャーの2つの色画素を、典型的なベイヤーパターン色画素センサレイアウトの上面図である図1に示す。第1の色画素は、赤センサ10、緑センサ12及び14並びに青センサ16を備える。第2の色画素は、赤センサ18、緑センサ20及び22並びに青センサ24を備える。各色画素は、行*i*及び行(*i*+1)として図1に示される2つの隣接する行を占有する。行毎の読み出し時間が*t*である場合、1画素内の3色の読み出し時間は、2行の読み出しを必要とし、2*t*に等しい。

40

##### 【0004】

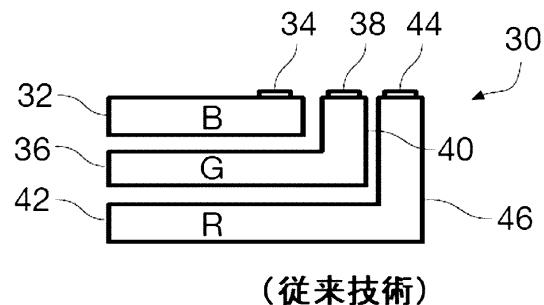

半導体基板内の異なる深さに配置された3つの水平に位置合わせされた垂直色画素セン

50

サを備える、F o v e o n X 3 (登録商標) 色画素センサ等の色CMOS画像センサ30の簡易化した断面を図2Aに示す。青センサ32は、半導体基板又はウェルの表面又は表面付近に配置される。青センサ32へのコンタクトは、コンタクト領域34を介して行われる。緑センサ36は、青センサ32の下に、青センサ32と水平に位置合わせされて半導体基板又はウェル内に配置される。緑センサ36へのコンタクトは、コンタクトプラグ40の上に形成されるコンタクト領域38を介して行われる。赤センサ42は、青センサ32及び緑センサ36の下に、青センサ32及び緑センサ36と水平に位置合わせされて半導体基板又はウェル内に配置される。赤センサ42へのコンタクトは、コンタクトプラグ46の上に形成されるコンタクト領域44を介して行われる。青、緑及び赤画素センサは、当技術分野で既知のようにフォトダイオードとして形成される。

10

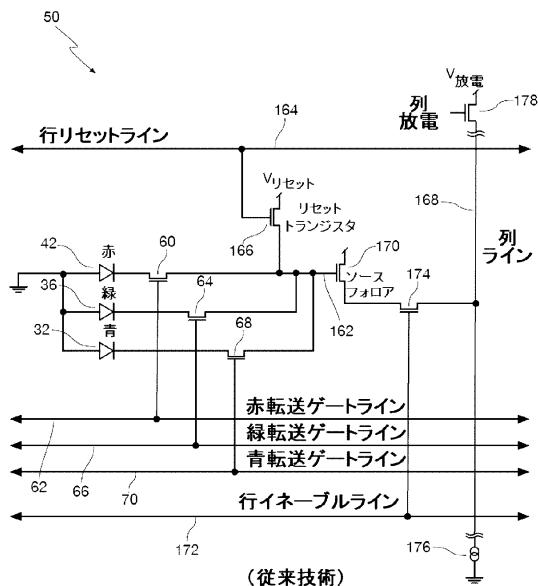

#### 【0005】

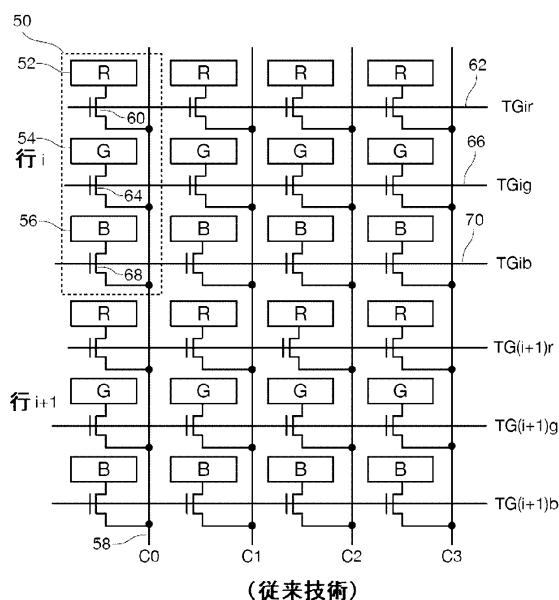

ここで、図2Bを参照すると、図2Aに示されるもの等の画素センサのアレイの一部の簡易化された概略図は、アレイを動作させるための従来技術による例示的な行列配線方式を示す。アレイは、2行、すなわち行*i*及び行(*i*+1)並びに4列の画素センサC0、C1、C2及びC3を備える。行*i*、列C0における画素センサは、破線50で識別される。

#### 【0006】

個々の色画素センサは、図2Bでは矩形として示される。画素(破線50内に示される)は、赤センサ52、緑センサ54及び青センサ56を備える。赤センサ52は、転送トランジスタ60を介して列ラインC0(参照番号58)に結合され、転送トランジスタ60のゲートは、参照番号62において転送ゲートラインT Gi rにより駆動される。緑センサ54は、転送トランジスタ64を介して列ラインC0\_58に結合され、転送トランジスタ64のゲートは、参照番号66において転送ゲートラインT Gi gにより駆動される。青センサ56は、転送トランジスタ68を介して列ラインC0\_58に結合され、転送トランジスタ68のゲートは、参照番号70において転送ゲートラインT Gi bにより駆動される。他の画素(図2Bにおいて参照番号が示されていない)は、通常、画素50と同一であることを当業者は理解するであろう。

20

#### 【0007】

図2Bに示されるアレイの読み出しプロセスは、転送ゲートライン62(赤)、66(緑)及び70(青)の1つをアクティビ化することにより、赤センサ52、緑センサ54及び青センサ56の出力を一度に1つずつ列ラインC0\_58に配置する。行*i*の他の列(C1、C2及びC3)内の個々の色画素センサから蓄積された電荷も、詳細に上述したようにセンサ52、54及び56と同時に読み出され、次に、ここでは行*i*について詳述したのと同じ動作を使用して、アレイの他の行内の画素センサを読み出し得ることを当業者は容易に理解するであろう。画素リセット及び暗レベル読み出し動作等の他のステップもアレイの動作に関わるが、本開示を過度に複雑にし、したがって本発明を曖昧にするのを避けるため、これらのステップについて本明細書で詳述しないことも当業者は容易に理解するであろう。

30

#### 【0008】

図2Bに示される構造は、行毎に3つの転送ゲートライン(62、66及び70)及び列毎に1つの列ライン(例えば、C0\_58)を利用する。図1のベイヤーパターンセンサ例の行読み出し時間tを使用すると、図2Bのアレイの1行を読み出す時間は、3tである。これらの3つのバスは、各行の3色の全てを捕捉するのに必要である。図2Bの構造の一利点は、色エイリアシングを有さないことである。

40

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0009】

本発明の様々な態様によれば、本発明により画素読み出しを配線することにより、2つの読み出しモードを利用することができる。疎なサンプリングパターンは、高品質静止画像のデータ密度に影響せずにビデオに使用することができる。疎なサンプリングは、各パ

50

スで読み出される色チャンネル数を2倍にするため、フレームレートは、2倍になる。Foveon X3(登録商標)等の垂直色画像センサにより提供される最高データ密度を利用するため、完全サンプリングパターンを利用することもできる。

#### 【0010】

本発明の一態様によれば、垂直検知器色画素センサの行列を含むアレイであって、各垂直検知器色画素センサはアレイの行列に配置され幾つかの色の個々の色検知器を有する、アレイにおける、読み出し配線構造は、アレイの各行の複数の行選択ラインであって、行選択ラインの数は、アレイ内の垂直検知器色画素センサの色の数に等しい、複数の行選択ラインを備える。個々の列ラインは、アレイの各列に提供される。転送トランジスタは、アレイ内の各垂直検知器色画素センサ内の個々の各色検知器に提供される。各転送トランジスタは、アレイの列に配置された色検知器と、色検知器が配置されるアレイの列に関連付けられた列ラインとの間に結合される。各転送トランジスタは、垂直検知器色画素センサが配置されるアレイの行内の複数の行選択ラインの1つに結合されたゲートを有する。アレイの隣接する列内の各色検知器のアレイの各行内の少なくとも幾つかの転送トランジスタのゲートは、アレイのその行の行選択ラインの異なるものに結合される。

#### 【0011】

本発明の別の態様によれば、アレイ内の各行について、行選択ラインへの転送トランジスタのゲートの結合は、各色のアレイの第1の連続する列内の転送トランジスタのゲートが第1の命令で行選択ラインに結合され、各色のアレイの第2の連続する列内の転送トランジスタのゲートが、第1の命令と異なる第2の命令で行選択ラインに結合され、各色のアレイの第3の連続する列内の転送トランジスタのゲートが、第1の命令及び第2の命令と異なる第3の命令で行選択ラインに結合される3つの連続する列の群で繰り返される。

#### 【0012】

本発明の別の態様によれば、第1の連続する列において、第1の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第2の行選択ラインに結合され、第3の色検知器の転送トランジスタのゲートは、第3の行選択ラインに結合され、第2の連続する列において、第1の色検知器の転送トランジスタのゲートは、第3の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合され、第3の連続する列において、第1の色検知器の転送トランジスタのゲートは、第2の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第3の行選択ラインに結合され、第3の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合される。

#### 【0013】

本発明の別の態様によれば、アレイ内の各行について、行選択ラインへの転送トランジスタのゲートの結合は、各色のアレイの第1の連続する列内の転送トランジスタのゲートが第1の命令で行選択ラインに結合され、各色のアレイの第2の連続する列内の転送トランジスタのゲートが第1の命令と異なる第2の命令で行選択ラインに結合され、各色のアレイの第3の連続する列内の転送トランジスタのゲートが第1の命令及び第2の命令と異なる第3の命令で行選択ラインに結合され、各色のアレイの第4の連続する列内の転送トランジスタのゲートが第1の命令で行選択ラインに結合される4つの連続する列の群で繰り返される。

#### 【0014】

本発明の別の態様によれば、第1の連続する列において、第1の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第2の行選択ラインに結合され、第3の色検知器の転送トランジスタのゲートは、第3の行選択ラインに結合され、第2の連続する列において、第1の色検知器の転送トランジスタのゲートは、第2の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第3の行選択ラインに結合され、第3の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合され、第3の連続する列において、第1の色検

10

20

30

40

50

知器の転送トランジスタのゲートは、第3の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合され、第3の色検知器の転送トランジスタのゲートは、第2の行選択ラインに結合され、第4の連続する列において、第1の色検知器の転送トランジスタのゲートは、第1の行選択ラインに結合され、第2の色検知器の転送トランジスタのゲートは、第2の行選択ラインに結合され、第3の色検知器の転送トランジスタのゲートは、第3の行選択ラインに結合される。

#### 【 0 0 1 5 】

本発明の別の態様によれば、アレイ内の各 $i$ 番目の列について、各色のアレイの各 $i$ 番目の列内の転送トランジスタは、第1の命令で行選択ラインに結合され、各色のアレイの各( $i+1$ )番目の列内の転送トランジスタは第1の命令と異なる第2の命令で行選択ラインに結合され、アレイ内の各( $i+1$ )番目の行について、各色のアレイの各 $i$ 番目の列内の転送トランジスタは第1の命令で行選択ラインに結合され、各色のアレイの各( $i+1$ )番目の列内の転送トランジスタは第1の命令及び第2の命令と異なる第3の命令で行選択ラインに結合される。

10

#### 【 0 0 1 6 】

本発明の別の態様によれば、第1の色及び第2の色のアレイの $i$ 番目の行内の転送トランジスタのゲートは、アレイの隣接する列内の第1の行選択ラインと第2の行選択ラインとの間で交互になり、第3の色のアレイの $i$ 番目の行内の転送トランジスタのゲートは、アレイ内の全ての列について第3の行選択ラインに結合され、第1の色のアレイの( $i+1$ )番目の行内の転送トランジスタのゲートはアレイ内の全ての列について第1の行選択ラインに結合され、第2の色及び第3の色のアレイの( $i+1$ )番目の行内の転送トランジスタのゲートはアレイの隣接する列内の第2の行選択ラインと第3の行選択ラインとの間で交互になる。

20

#### 【 0 0 1 7 】

本発明の別の態様によれば、アレイは、垂直検知器色画素センサの行列を備え、各垂直検知器色画素センサは、アレイの行列に配置され、幾つかの色の個々の色検知器を有する。読み出し配線構造は、アレイの各行の複数の行選択ラインであって、行選択ラインの数は、アレイ内の垂直検知器色画素センサの色の数に等しい、複数の行選択ラインを備える。個々の列ラインは、アレイの各列に提供される。転送トランジスタは、アレイ内の各垂直検知器色画素センサ内の個々の各色検知器に提供され、各転送トランジスタは、アレイの列内の色検知器と、アレイの列ラインとの間に結合され、垂直検知器色画素センサが配置されるアレイの行内の複数の行選択ラインの1つに結合されたゲートを有する。アレイの列内の垂直検知器色画素センサ内の各色検知器の転送トランジスタは、垂直検知器色画素センサが配置される列ラインの直前の列ライン、垂直検知器色画素センサが配置される列ライン、及び液垂直検知器色画素センサが配置される列ラインの直後の列ラインの異なる1つに結合される。

30

#### 【 0 0 1 8 】

本発明の別の態様によれば、アレイの列内の垂直検知器色画素センサにおける第1の色検知器の転送トランジスタは、垂直検知器色画素センサが配置される列ラインの直前の列ラインに結合され、アレイの列内の垂直検知器色画素センサにおける第2の色検知器の転送トランジスタは、垂直検知器色画素センサが配置される列ラインに結合され、アレイの列内の垂直検知器色画素センサにおける第3の色検知器の転送トランジスタは、垂直検知器色画素センサが配置される列ラインの直後の列ラインに結合される。

40

#### 【 0 0 1 9 】

本発明の別の態様によれば、垂直検知器色画素センサの行列を備えるアレイをビデオモードで動作させる方法であって、各垂直検知器色画素センサは、個々の赤色検知器、緑色検知器及び青色検知器を有し、アレイの列内の垂直検知器色画素センサにおける各赤色検知器は、赤転送トランジスタを通して列出力ラインに結合され、アレイの列内の垂直検知器色画素センサにおける各緑色検知器は、緑転送トランジスタを通して列出力ラインに結合され、アレイの列内の垂直検知器色画素センサにおける各青色検知器は、青転送トラン

50

ジスタを通して列出力ラインに結合され、アレイの行内の各赤転送トランジスタのゲートは、赤転送行ラインに結合され、アレイの行内の各緑転送トランジスタのゲートは、緑転送行ラインに結合され、アレイの行内の各青転送トランジスタのゲートは、青転送行ラインに結合される、方法が開示される。本方法は、アレイの  $i$  番目の行毎に赤転送トランジスタ及び緑転送トランジスタを順次作動させるステップと、アレイの  $(i + 8)$  番目の行毎に緑転送トランジスタ及び青転送トランジスタを順次作動させるステップとを含む。

【0020】

本発明について、実施形態及び図面を参照して以下により詳細に説明する。

【0021】

10

【0022】

【0023】

【0024】

【0025】

【0026】

【0027】

【0028】

【0029】

【0030】

【0031】

【0032】

20

【0033】

【0034】

【0035】

【0036】

【0037】

【0038】

【図面の簡単な説明】

【0039】

【図1】ベイヤーパターンセンサ等の典型的なモザイク色画素センサを示す上面図である。

【図2A】半導体基板内の異なる深さに配置された、3つの水平に位置合わせされた色画

素センサを備える色CMOS画像センサの簡易化された断面図である。

30

【図2B】アレイを動作させる例示的な従来技術による行列配線構造を有する、図2Aに

示されるもの等の画素センサのアレイの部分の簡易化された概略図である。

【図3】本発明の態様による、アレイを動作させる例示的な行列配線構造を有する、図2

Aに示されるもの等の画素センサのアレイの部分を示す簡易化された概略図である。

【図4】図3に示されるアレイの列ライン上の出力を示す表である。

【図5】本発明の態様による、アレイを動作させる例示的な行列配線構造を有する、図2

Aに示されるもの等の画素センサのアレイの部分を示す簡易化された概略図である。

【図6】図5に示されるアレイの列ライン上の出力を示す表である。

【図7】本発明の別の態様による、アレイを動作させる例示的な行列配線構造を有する、

図2Aに示されるもの等の画素センサのアレイの部分を示す簡易化された概略図である。

40

【図8】図7に示されるアレイの列ライン上の出力を示す表である。

【図9】本発明の別の態様による、アレイを動作させる例示的な行列配線構造を有する、

図2Aに示されるもの等の画素センサのアレイの部分を示す簡易化された概略図である。

【図10】図9に示されるアレイの列ライン上の出力を示す表である。

【図11】本発明の別の態様による、アレイを動作させる例示的な行列配線構造を有する

、図2Aに示されるもの等の画素センサのアレイの部分を示す簡易化された概略図である。

【図12】図11に示されるアレイの列ライン上の出力を示す表である。

【図13】多色垂直画素センサを展開することができる典型的な環境を示す概略図である。

【図14】埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置を

50

示すような画素センサのアレイの行における図 2 A の画素センサのような垂直画素センサの対の従来技術によるレイアウトの簡易化された部分の上面図である。

【図 15】本発明の態様による、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置を示すような画素センサのアレイの行における図 2 A の画素センサのような垂直画素センサの対のレイアウトの簡易化された部分の上面図である。

【図 16】本発明の態様による、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置を示すような画素センサのアレイの行における図 2 A の画素センサのような垂直画素センサの対のレイアウトの簡易化された部分の上面図である。

【図 17】本発明の態様による、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置及び青センサのコンタクトの位置を示すような画素センサのアレイの行における図 2 A の画素センサのような垂直画素センサの対のレイアウトの簡易化された部分の上面図である。10

【図 18】本発明の態様による、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置及び青センサのコンタクトの位置を示すような画素センサのアレイの行における図 2 A の画素センサのような垂直画素センサの対のレイアウトの簡易化された部分の上面図である。

#### 【発明を実施するための形態】

##### 【0040】

本発明の以下の説明が単なる例示であり、決して限定するものではないことを当業者は認識するであろう。そのような当業者は、本発明の他の実施形態に容易に想到するであろう。20

##### 【0041】

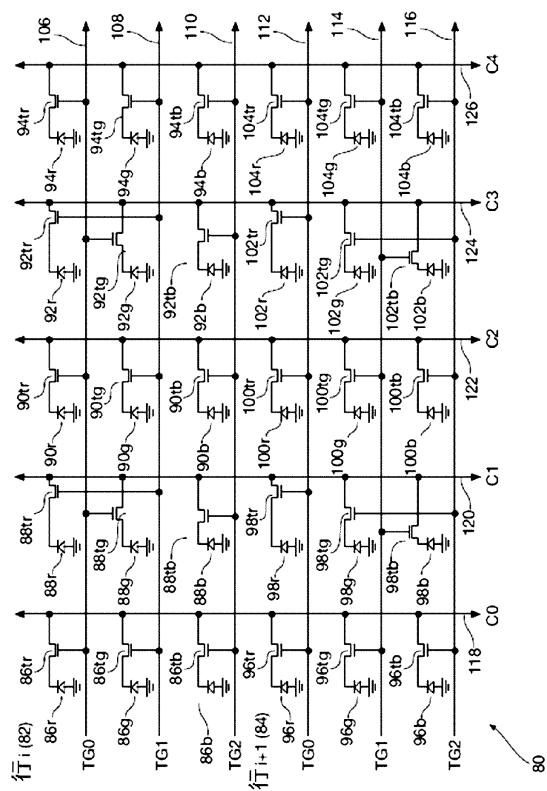

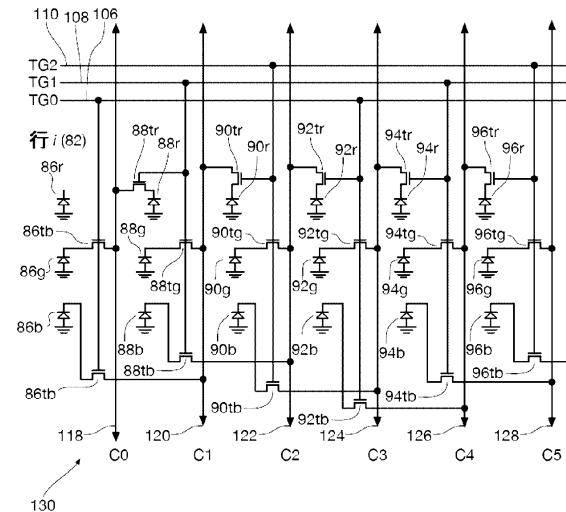

ここで、図 3 を参照して、本発明の一態様による、画素センサアレイ 80 内の 3 色垂直画素センサの隣接する行 82 及び 84 の対の配線構造を示す。各 3 色画素センサは、赤色、緑色、青色を検知するための赤画素センサ、緑画素センサ及び青画素センサを備える。各画素センサは、その画素及び色を示す参照番号で識別される。したがって、例えば、3 色画素センサ 86 内の赤画素センサは、参照番号 86r で識別され、3 色画素センサ 86 内の緑画素センサは、参照番号 86g で識別され、3 色画素センサ 86 内の青画素センサは、参照番号 86b で識別される。他の画素センサの付番もこの規則に従う。

##### 【0042】

第 1 の行 i (82) は、5 列の 3 色画素センサを備え、3 色画素センサ 86r、86g 及び 86b は、第 1 の 3 色画素センサを形成し、3 色画素センサ 88r、88g 及び 88b は、第 2 の 3 色画素センサを形成し、3 色画素センサ 90r、90g 及び 90b は、第 3 の 3 色画素センサを形成し、3 色画素センサ 92r、92g 及び 92b は、第 4 の 3 色画素センサを形成し、3 色画素センサ 94r、94g 及び 94b は、第 5 の 3 色画素センサを形成する。同様に、第 2 の行 i + 1 (84) も 5 つの 3 色画素センサを備え、3 色画素センサ 96r、96g 及び 96b は、第 1 の 3 色画素センサを形成し、3 色画素センサ 98r、98g 及び 98b は、第 2 の 3 色画素センサを形成し、3 色画素センサ 100r、100g 及び 100b は、第 3 の 3 色画素センサを形成し、3 色画素センサ 102r、102g 及び 102b は、第 4 の 3 色画素センサを形成し、3 色画素センサ 104r、104g 及び 104b は、第 5 の 3 色画素センサを形成する。30

##### 【0043】

アレイの各行は、3 つの転送ゲートラインを有する。行 82 の 3 つの転送ゲートラインは、それぞれ参照番号 106 (TG0)、108 (TG1) 及び 110 (TG2) で識別される。行 84 の 3 つの転送ゲートラインは、それぞれ参照番号 112 (TG0)、114 (TG1) 及び 116 (TG2) で識別される。40

##### 【0044】

アレイの各列は、列出力ラインを有する。列 C0 の列出力ラインは、参照番号 118 で識別される。列 C1 の列出力ラインは、参照番号 120 で識別される。列 C2 の列出力ラインは、参照番号 122 で識別される。列 C3 の列出力ラインは、参照番号 124 で識別50

される。列 C 4 の列出力ラインは、参照番号 126 で識別される。

**【 0 0 4 5 】**

個々の各色画素センサは、転送トランジスタを通して関連付けられた列の列出力ラインに接続される。各転送トランジスタは、添え字「 t 」、及び赤は、「 r 」、緑は、「 g 」又は青は、「 b 」の色識別子が続く、その画素を識別する参照番号で識別される。一例として、画素センサ 86 内の赤画素センサの転送トランジスタは、 86 tr として識別される。転送トランジスタは、本明細書に開示される構造により、アクティブ化のために転送ゲートライン 106 、 108 、 110 、 112 、 114 及び 116 の 1 つに接続されたゲートを有する。

**【 0 0 4 6 】**

図 3 に示される本発明の態様によれば、第 1 の行 82 内の第 1 の色及び第 2 の色の画素センサは、それぞれの転送トランジスタを通してその行の第 1 及び第 2 の転送ゲートライン 106 及び 108 に交互に接続される。例えば、奇数列 (C0 、 C2 及び C4 、それら参照番号 118 、 122 及び 126) 内の赤画素センサ 86 r 、 90 r 及び 94 r は、それぞれの転送トランジスタ 86 tr 、 90 tr 及び 94 tr を通して転送ゲート TG0 106 に接続され、偶数列 (C1 及び C3 、それら参照番号 120 及び 124) 内の第 1 の行 82 における緑画素センサ 88 g 及び 92 g は、それぞれの転送トランジスタ 88 tg 及び 92 tg (画素センサ 88 g 及び 92 g の転送トランジスタ 88 tg 及び 92 tg として示される) を通して転送ゲート TG0 106 に接続される。偶数列 (C1 及び C3) 内の赤画素センサ 88 r 及び 92 r は、それぞれの転送トランジスタ 88 tr 及び 92 tr を通して転送ゲート TG1 108 に接続され、第 1 の行 82 内の奇数列 (C0 、 C2 及び C4) 内の緑画素センサ 86 g 、 90 g 及び 94 g は、それぞれの転送トランジスタ 86 tg 、 90 tg 及び 94 tg を通して転送ゲート TG0 106 に接続される。

**【 0 0 4 7 】**

隣接する行の対の第 2 の行 84 では、第 1 の色の全ての画素センサ 96 r 、 98 r 、 100 r 及び 102 r (赤) は、その行の第 1 の転送ゲートライン TG0 112 に接続される。第 2 の色 (緑) 及び第 3 の色 (青) の画素センサは、その行の転送ゲートライン 114 及び 116 の第 2 及び第 3 の転送ゲートラインに交互に接続される。例えば、奇数列 (C0 、 C2 及び C4 、それら参照番号 118 、 122 及び 124) 内の第 2 の色の全ての画素センサ 96 g 、 100 g 及び 104 g (緑) 並びに偶数列 (C1 及び C3 、それら参照番号 120 及び 124) 内の第 3 の色の全ての画素センサ 98 b 及び 102 b (青) は、その行の転送ゲートラインの第 2 の転送ゲートライン TG1 114 に接続され、奇数列 (C0 、 C2 及び C4 、それら参照番号 118 、 122 及び 126) 内の第 3 の色の全ての画素センサ 96 b 、 100 b 及び 104 b (青) 並びに偶数列 (C1 及び C3 、それら参照番号 120 及び 124) 内の第 2 の色の全ての画素センサ 98 g 及び 102 g (緑) は、その行の転送ゲートラインの第 3 の転送ゲートライン TG2 116 に接続される。

**【 0 0 4 8 】**

行 82 及び 84 は、それぞれ例示を目的として 5 つの垂直 3 色画素センサを有するものとして示されるが、本発明により製造される実際の画像センサが任意の数の行列の画素センサを有し得ることを当業者は理解するであろう。色画素センサから転送ゲートラインへの接続のパターンが 2 列群で繰り返されることを当業者は理解するであろう。したがって、図 3 では、第 3 の列 C2 、参照番号 122 における色画素センサ 90 r 、 90 g 、 90 b から転送ゲートライン 106 、 108 及び 110 への第 1 の行 i (82) 上の接続並びに最後の列 C4 、参照番号 126 における色画素センサ 94 r 、 94 g 、 94 b から転送ゲートライン 106 、 108 及び 110 への接続は、第 1 の列 C0 、参照番号 118 における色画素センサ 86 r 、 86 g 及び 86 b から転送ゲートライン 106 、 108 及び 110 への接続と同じであることを見て取ることができる。同じことは、第 1 の行 i (82) の第 2 及び第 4 の列のそれらにおける色画素センサ 88 r 、 88 g 及び 88 b 及び色画素センサ 92 r 、 92 g 及び 92 b と転送ゲートライン 106 、 108 及び 110 との

10

20

30

40

50

間の接続にも当てはまる。

#### 【0049】

同様に、図3では、第3の列C2、参照番号122における色画素センサ100r、100g、100bから転送ゲートライン112、114及び116への第2の行 $i+1$ (84)上の接続並びに第5の列C4、参照番号126における色画素センサ104r、104g、104bから転送ゲートライン106、108及び110への接続は、第1の列C0、参照番号118における色画素センサ96r、96g及び96bから転送ゲートライン106、108及び110への接続と同じであることを見て取ることができる。

#### 【0050】

図3及び上記説明から分かるように、第1の行 $i+82$ 及び第2の行 $i+1+84$ の両方における行/列接続のパターンは、隣接する2列群で繰り返される。 10

#### 【0051】

図4の表に示されるように、第1の色が赤であり、第2の色が緑であり、第3の色が青である図3に示される特定の実施形態の場合、色は、以下の順に列にわたり(8列に拡張される)読み出される。

#### 【表1】

| 列位置           | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---------------|---|---|---|---|---|---|---|---|

| 行 $i$ TG0     | R | G | R | G | R | G | R | G |

| 行 $i$ TG1     | G | R | G | R | G | R | G | R |

| 行 $i$ TG2     | B | B | B | B | B | B | B | B |

| 行 $(i+1)$ TG0 | R | R | R | R | R | R | R | R |

| 行 $(i+1)$ TG1 | G | B | G | B | G | B | G | B |

| 行 $(i+1)$ TG2 | B | G | B | G | B | G | B | G |

20

30

#### 【0052】

行毎の読み出し時間が $t$ である場合、静止ショットの場合での2行82及び84内の各画素の3色全ての合計読み出し時間は、 $6t$ である。これは、従来技術による実施により行転送ゲートラインを配線することにより得られるのと全く同じ性能である。

#### 【0053】

モザイクフォーマットでビデオ読み出しを実行するため、行 $i+82$ の第1の転送ゲート106及び行 $(i+1)$ の第2の転送ゲート114は、アクティブ化され、列にわたる色の読み出しは、以下の通りであり、全行にわたり続けられる。

#### 【表2】

| 列位置           | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---------------|---|---|---|---|---|---|---|---|

| 行 $i$ TG0     | R | G | R | G | R | G | R | G |

| 行 $(i+1)$ TG1 | G | B | G | B | G | B | G | B |

| 行 $(i+8)$ TG0 | R | G | R | G | R | G | R | G |

| 行 $(i+9)$ TG1 | G | B | G | B | G | B | G | B |

40

#### 【0054】

50

上記表から見て取ることができるように、このパターンは、8行毎に繰り返され、この例では、転送ゲートTG0について行( $i + 1$ )~( $i + 7$ )をスキップし、転送ゲートTG1について行( $i + 2$ )~( $i + 8$ )をスキップする。読み出す次の行は、( $i + 8$ )及び( $i + 9$ )である。同じように読み出す次の行は、行( $i + 10$ )~( $i + 15$ )をスキップして行( $i + 16$ )及び( $i + 17$ )である。

#### 【0055】

この色の読み出しが図1のベイヤーパターンモザイクセンサの色の読み出しと同じであることを当業者は認識するであろう。行毎の読み出し時間が $t$ である場合、4行の全体読み出し時間は、 $4t$ であり、通常の配線を用いたモザイクビデオ読み出しそれよりも2倍高速である。

10

#### 【0056】

画素内の3色全てに共通する1つの列読み出し線を有するFoveon X3(登録商標)等の垂直色センサは、色情報は各画素場所でサンプリングされ、バス毎に1つのみの色チャンネルを読み出す能力を有する。モザイクフィルタセンサ(ベイヤーパターンセンサ等)は、バス毎に2色を読み出すが、各場所で同じ色をサンプリングすることができない。図3に示される読み出し配線及び動作モードを参照して説明される本発明の態様は、これらの2つの動作モードを組み合わせ、ビデオ等の用途で速度が求められる場合、モザイクフィルタとして動作する能力を有し、画質がより重要な場合、画素場所毎に全色を読み出すことにより最高解像度を提供する能力を保持する。動作のこの多様性は、消費電力にペナルティを課すことなく達成される。

20

#### 【0057】

標準X3でもなければモザイクでもない、図3に示されるアレイの交互ビデオ読み出しは、以下の表に示されるように実行し得る。

#### 【表3】

| 列位置                    | 0 | 1 | 2 | 3 |

|------------------------|---|---|---|---|

| 行 $i \text{ TG0}$      | R | G | R | G |

| 行 $(i+5) \text{ TG2}$  | B | G | B | G |

| 行 $(i+10) \text{ TG0}$ | R | G | R | G |

| 行 $(i+15) \text{ TG2}$ | B | G | B | G |

30

#### 【0058】

この読み出しへは、 $2t^*8/5$ ( $3 \cdot 2t$ )かかり、したがってエイリアシングが多いという犠牲の下で $4t$ でのモザイク読み出しそれよりも高速である。

40

#### 【0059】

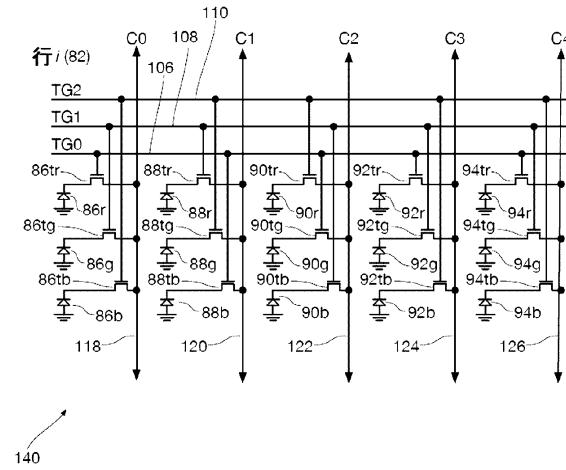

ここで、図5を参照して、本発明の別の態様による、画素センサアレイ130における3色垂直画素センサの行*i*~82の配線構造を示す。図3に示される実施形態と同様に、図5に示される実施形態における各3色画素センサは、撮像アレイにおける同じ場所での個々の赤色、緑色及び青色の検知のための赤画素センサ、緑画素センサ及び青画素センサを備える。図5に示される撮像アレイの要素は、図3の撮像アレイに示される要素に対応する場合、図3で使用されるのと同じ参照番号を使用して識別される。

#### 【0060】

50

図5の調査から分かり得るように、行i(82)は、6列の3色画素センサを備え、3色画素センサ86r、86g及び86bは、第1の3色画素センサを形成し、3色画素センサ88r、88g及び88bは、第2の3色画素センサを形成し、3色画素センサ90r、90g及び90bは、第3の3色画素センサを形成し、3色画素センサ92r、92g及び92bは、第4の3色画素センサを形成し、3色画素センサ94r、94g及び94bは、第5の3色画素センサを形成し、3色画素センサ96r、96g及び96bは、第6の3色画素センサを形成する。

#### 【0061】

行82は、3つの転送ゲートラインTG0、TG1及びTG2を有する。行82の3つの転送ゲートラインは、それぞれ参照番号106、108及び110で識別される。

10

#### 【0062】

アレイの各列は、列出力ラインを有する。列C0の列出力ラインは、参照番号118で識別される。列C1の列出力ラインは、参照番号120で識別される。列C2の列出力ラインは、参照番号122で識別される。列C3の列出力ラインは、参照番号124で識別される。列C4の列出力ラインは、参照番号126で識別される。列C5の列出力ラインは、参照番号128で識別される。

#### 【0063】

個々の各色画素センサは、転送トランジスタを通して関連付けられた列の列出力ラインに接続される。図3に示される実施形態と同様に、図5に示される実施形態における各転送トランジスタは、添え字「t」、及び赤は、「r」、緑は、「g」又は青は、「b」の色識別子が続く、その画素を識別する参照番号で識別される。一例として、画素センサ86内の赤画素センサの転送トランジスタは、86trとして識別される。各転送トランジスタは、本明細書に開示される構造により、画素読み出しのために転送ゲートライン106、108及び110の1つに接続されたゲートを有する。

20

#### 【0064】

赤画素86rは、図6の表において名称×××で示されるように、いずれの列ラインにも結合されない。C0がアレイ内の最初の列ではない場合、赤画素86rは、その転送トランジスタ(図示せず)により、先行する列ラインC(-1)に結合される。

#### 【0065】

緑画素86gは、行ラインTG0 106に接続されたゲートを有する転送トランジスタ86tgにより列出力ラインC0 118に結合される。青画素86bは、行ラインTG0 106に接続されたゲートを有する転送トランジスタ86tbにより列出力ラインC1 120に結合される。

30

#### 【0066】

赤画素88r(R1)は、行ラインTG1 108に接続されたゲートを有する転送トランジスタ88trにより列出力ラインC0 118に結合される。緑画素88g(G1)は、行ラインTG1 108に接続されたゲートを有する転送トランジスタ88tgにより列出力ラインC1 120に結合される。青画素88b(B1)は、行ラインTG1 108に接続されたゲートを有する転送トランジスタ88tbにより列出力ラインC2 122に結合される。

40

#### 【0067】

赤画素90r(R2)は、行ラインTG2 110に接続されたゲートを有する転送トランジスタ90trにより列出力ラインC1 120に結合される。緑画素90g(G2)は、行ラインTG2 110に接続されたゲートを有する転送トランジスタ90tgにより列出力ラインC2 122に結合される。青画素90b(B2)は、行ラインTG2 110に接続されたゲートを有する転送トランジスタ90tbにより列出力ラインC3 124に結合される。

#### 【0068】

赤画素92r(R3)は、行ラインTG0 106に接続されたゲートを有する転送トランジスタ92trにより列出力ラインC2 122に結合される。緑画素92g(G3)

50

)は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 2 t g により列出力ライン C 3 1 2 4 に結合される。青画素 9 2 b ( B 3 )は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 2 t b により列出力ライン C 4 1 2 6 に結合される。

#### 【 0 0 6 9 】

赤画素 9 4 r ( R 4 )は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 4 t r により列出力ライン C 3 1 2 4 に結合される。緑画素 9 4 g ( G 4 )は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 4 t g により列出力ライン C 4 1 2 6 に結合される。青画素 9 4 b ( B 4 )は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 4 t b により列出力ライン C 5 1 2 8 に結合される。10

#### 【 0 0 7 0 】

赤画素 9 6 r ( R 5 )は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 6 t r により列出力ライン C 4 1 2 6 に結合される。緑画素 9 6 g ( G 5 )は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 6 t g により列出力ライン C 5 1 2 8 に結合される。青画素 9 6 b ( B 5 )は、図 6 の表において名称 x x x で示されるように、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 6 t b により、C 6 ( 図示せず ) である次の列出力ラインに結合される。

#### 【 0 0 7 1 】

本発明のこの態様を示すために、1行及び6列(3の2つの繰り返しパターン)が図5に示されているが、本発明のこの態様により構成される撮像アレイが任意の数の行列を有し得ることを当業者は理解するであろう。20

#### 【 0 0 7 2 】

上記説明及び図5の調査並びに図6の表の調査から分かるように、静止ショットを捕捉するために、行ライン T G 1 ( 1 0 8 )は、アクティブ化され、R 1 ( 赤画素 8 8 r )、G 1 ( 緑画素 8 8 g )及びB 1 ( 青画素 8 8 b )を列ライン C 0 、 C 1 及び C 2 上にそれぞれ駆動する。行ライン T G 2 ( 1 1 0 )は、アクティブ化され、R 2 ( 赤画素 9 0 r )、G 2 ( 緑画素 9 0 g )及びB 2 ( 青画素 9 0 b )を列ライン C 1 、 C 2 及び C 3 上にそれぞれ駆動する。行ライン T G 0 ( 1 0 6 )は、アクティブ化され、R 3 ( 赤画素 9 2 r )、G 3 ( 緑画素 9 2 g )及びB 3 ( 青画素 9 2 b )を列ライン C 2 、 C 3 及び C 4 上にそれぞれ駆動する。各画素の3色全ての読み出し時間は、1行で 3 t である。これは、図2Bに示される従来の配線での従来技術による実施による行転送ゲートラインの配線により得られるのと全く同じ性能である。なお、不完全な画素は、アレイのエッジにおける列にのみ配置される。30

#### 【 0 0 7 3 】

F o v e o n X 3 フォーマットでビデオ読み出しを実行するために、行 i の行ライン T G 1 ( 1 0 8 )は、アクティブ化されて、列 1 、 4 、 7 、 . . . から緑色画素 G 1 、 G 4 及び G 7 を駆動し、また列 0 、 3 、 6 から赤色画素 R 1 、 R 4 及び R 7 を駆動し、列 2 、 5 、 8 から青色画素 B 1 、 B 4 及び B 7 を駆動する。これは、行 ( i + 8 )に対して繰り返され、続く 8 行毎に繰り返される。各行からの読み出しには時間 1 t かかる。これは、色エイリアシングなしで X 3 読み出しを与えるながら、図2Bに示される従来技術よりも 3 倍高速である。40

#### 【 0 0 7 4 】

緑画素が、常に、列に関連付けられた列ラインから読み出され、赤画素が、常に、前の列に関連付けられた列ラインから読み出され、青画素が、常に、次の列に関連付けられた列ラインから読み出されることに当業者は留意するであろう。そのような当業者は、この例示的な実施形態では、赤画素が左にシフトされ、青画素が右にシフトされ、色の任意の 2 つがそれぞれ左右にシフトされ得、第 3 の色がシフトされないままであることも理解するであろう。

#### 【 0 0 7 5 】

10

20

30

40

50

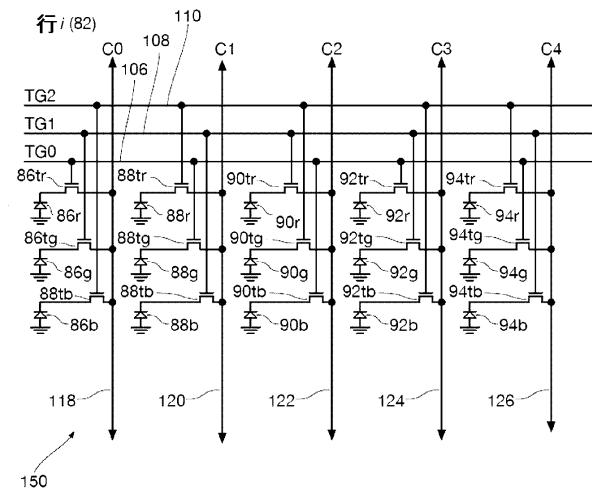

ここで、図7を参照して、本発明の別の態様による、画素センサアレイ140における3色垂直画素センサの行i 82の配線構造を示す。図3に示される実施形態と同様に、図7に示される実施形態における各3色画素センサは、撮像アレイにおける同じ場所での個々の赤色、緑色及び青色の検知のための赤画素センサ、緑画素センサ及び青画素センサを備える。図7に示される撮像アレイの要素は、図3の撮像アレイに示される要素に対応する場合、図3で使用されるのと同じ参照番号を使用して識別される。

#### 【0076】

図7の調査から分かり得るように、行i (82)は、5列の3色画素センサを備え、3色画素センサ86r (R0)、86g (G0)及び86b (B0)は、第1の3色画素センサを形成し、3色画素センサ88r (R1)、88g (G1)及び88b (B1)は、第2の3色画素センサを形成し、3色画素センサ90r (R2)、90g (G2)及び90b (B2)は、第3の3色画素センサを形成し、3色画素センサ92r (R3)、92g (G3)及び92b (B3)は、第4の3色画素センサを形成し、3色画素センサ94r (R2)、94g (G2)及び94b (B2)は、第5の3色画素センサを形成する。

10

#### 【0077】

行82は、3つの転送ゲートラインTG0、TG1及びTG2を有する。行82の3つの転送ゲートラインは、それぞれ参照番号106、108及び110で識別される。

#### 【0078】

アレイの各列は、列出力ラインを有する。列C0の列出力ラインは、参照番号118で識別される。列C1の列出力ラインは、参照番号120で識別される。列C2の列出力ラインは、参照番号122で識別される。列C3の列出力ラインは、参照番号124で識別される。

20

#### 【0079】

個々の各色画素センサは、転送トランジスタを通して関連付けられた列の列出力ラインに接続される。図3に示される実施形態と同様に、図7に示される実施形態における各転送トランジスタは、添え字「t」、及び赤は、「r」、緑は、「g」又は青は、「b」の色識別子が続く、その画素を識別する参照番号で識別される。一例として、画素センサ86内の赤画素センサの転送トランジスタは、86trとして識別される。各転送トランジスタは、本明細書に開示される構造により、画素読み出しのために転送ゲートライン106、108及び110の1つに接続されたゲートを有する。

30

#### 【0080】

赤画素86rは、行ラインTG0 106に接続されたゲートを有する転送トランジスタ86trにより列出力ラインC0 118に結合される。緑画素86gは、行ラインTG1 108に接続されたゲートを有する転送トランジスタ86tgにより列出力ラインC0 118に結合される。青画素86bは、行ラインTG2 110に接続されたゲートを有する転送トランジスタ86tbにより列出力ラインC0 118に結合される。

#### 【0081】

赤画素88rは、行ラインTG1 108に接続されたゲートを有する転送トランジスタ88trにより列出力ラインC1 120に結合される。緑画素88gは、行ラインTG2 110に接続されたゲートを有する転送トランジスタ88tgにより列出力ラインC1 120に結合される。青画素88bは、行ラインTG0 106に接続されたゲートを有する転送トランジスタ88tbにより列出力ラインC1 120に結合される。

40

#### 【0082】

赤画素90rは、行ラインTG2 110に接続されたゲートを有する転送トランジスタ90trにより列出力ラインC2 122に結合される。緑画素90gは、行ラインTG0 106に接続されたゲートを有する転送トランジスタ90tgにより列出力ラインC2 122に結合される。青画素90bは、行ラインTG1 108に接続されたゲートを有する転送トランジスタ90tbにより列出力ラインC2 122に結合される。

#### 【0083】

赤画素92rは、行ラインTG0 106に接続されたゲートを有する転送トランジス

50

タ 9 2 t r により列出力ライン C 3 1 2 4 に結合される。緑画素 9 2 g は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 2 t g により列出力ライン C 3 1 2 4 に結合される。青画素 9 2 b は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 2 t b により列出力ライン C 3 1 2 4 に結合される。

#### 【 0 0 8 4 】

赤画素 9 4 r は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 4 t r により列出力ライン C 4 1 2 6 に結合される。緑画素 9 4 g は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 4 t g により列出力ライン C 4 1 2 6 に結合される。青画素 9 4 b は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 4 t b により列出力ライン C 4 1 2 6 に結合される。

#### 【 0 0 8 5 】

図 7 及び図 8 に示される色画素センサから転送ゲートラインへの接続のパターンは、アレイの行にわたり 4 つの隣接する列において 4 画素群で繰り返される。赤、緑及び青画素センサ 9 4 r、9 4 g 及び 9 4 b が次の繰り返される 4 画素群の最初の列を形成することを当業者は理解するであろう。本発明のこの態様を示すために、1 行及び 5 列が図 7 に示されるが、本発明のこの態様により構成される撮像アレイが任意の数の行列を有し得ることも当業者は理解するであろう。

#### 【 0 0 8 6 】

図 8 の表に示されるように、第 1 の色が赤であり、第 2 の色が緑であり、第 3 の色が青である図 7 に示される特定の実施形態の場合、色は、以下の順に列にわたり（8 列に拡張される）読み出される。

#### 【表 4】

| 列位置         | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-------------|---|---|---|---|---|---|---|---|

| 行 i TG0     | R | B | G | R | R | B | G | R |

| 行 i TG1     | G | R | B | G | G | R | B | G |

| 行 i TG2     | B | G | R | B | B | G | R | B |

| 行 (i+1) TG0 | R | B | G | R | R | B | G | R |

| 行 (i+1) TG1 | G | R | B | G | G | R | B | G |

| 行 (i+1) TG2 | B | G | R | B | B | G | R | B |

#### 【 0 0 8 7 】

行毎の読み出し時間が  $t$  である場合、静止ショットの場合での行  $i$  (8 2) 内の各画素の 3 色全ての合計読み出し時間は、 $6t$  である。これは、従来技術による実施により行転送ゲートラインを配線することにより得られるのと全く同じ性能である。

#### 【 0 0 8 8 】

この構成 (X 3 式読み出しでもなければ、モザイク読み出しでもない) のビデオ読み出しを実行するために、色は、以下のように列において読み出される (8 列を示すために拡張される)。

10

20

30

40

50

【表 5】

| 列位置         | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-------------|---|---|---|---|---|---|---|---|

| 行 i TG0     | - | B | G | - | - | B | G | - |

| 行 i TG1     | G | R | - | - | G | R | - | - |

| 行 (i+8) TG0 | - | B | G | - | - | B | G | - |

| 行 (i+8) TG1 | G | R | - | - | G | R | - | - |

10

## 【0089】

この読み出しプロセスは、4tかかり、モザイク配線を有するアレイからのビデオモザイク読み出しと同じである。このアレイからのビデオ画像は、異なる色の画素がモザイクアレイよりも一緒に近いため、良好な色エイリアシングを有するが、通常のX3式読み出しほど良好ではない。

## 【0090】

色の置換（すなわち各位置に1色を提供するが、赤、緑及び青の順を変える）が本発明の範囲内であると見なされることを当業者は容易に理解するであろう。

20

## 【0091】

ここで、図9を参照して、本発明の別の態様による、画素センサアレイ150における3色垂直画素センサの行i-82の配線構造を示す。図3に示される実施形態と同様に、図9に示される実施形態における各3色画素センサは、撮像アレイにおける同じ場所での個々の赤色、緑色及び青色の検知のための赤画素センサ、緑画素センサ及び青画素センサを備える。図9に示される撮像アレイの要素は、図3の撮像アレイに示される要素に対応する場合、図3で使用されるのと同じ参照番号を使用して識別される。

## 【0092】

図9の調査から分かり得るように、行i(82)は、3列の3色画素センサを備え、3色画素センサ86r(R0)、86g(G0)及び86b(B0)は、第1の3色画素センサを形成し、3色画素センサ88r(R1)、88g(G1)及び88b(B1)は、第2の3色画素センサを形成し、3色画素センサ90r(R2)、90g(G2)及び90b(B2)は、第3の3色画素センサを形成する。

30

## 【0093】

行82は、3つの転送ゲートラインTG0、TG1及びTG2を有する。行82の3つの転送ゲートラインは、それぞれ参照番号106、108及び110で識別される。

## 【0094】

アレイの各列は、列出力ラインを有する。列C0の列出力ラインは、参照番号118で識別される。列C1の列出力ラインは、参照番号120で識別される。列C2の列出力ラインは、参照番号122で識別される。

40

## 【0095】

個々の各色画素センサは、転送トランジスタを通して関連付けられた列の列出力ラインに接続される。図3に示される実施形態と同様に、図9に示される実施形態における各転送トランジスタは、添え字「t」、及び赤は、「r」、緑は、「g」又は青は、「b」の色識別子が続く、その画素を識別する参照番号で識別される。一例として、画素センサ86内の画素センサの転送トランジスタは、86trとして識別される。各転送トランジスタは、本明細書に開示される構造により、画素読み出しのために転送ゲートライン106、108及び110の1つに接続されたゲートを有する。

## 【0096】

赤画素86rは、行ラインTG0-106に接続されたゲートを有する転送トランジス

50

タ 8 6 t r により列出力ライン C 0 1 1 8 に結合される。緑画素 8 6 g は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 8 6 t g により列出力ライン C 0 1 1 8 に結合される。青画素 8 6 b は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 8 6 t b により列出力ライン C 0 1 1 8 に結合される。

#### 【 0 0 9 7 】

赤画素 8 8 r は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 8 8 t r により列出力ライン C 1 1 2 0 に結合される。緑画素 8 8 g は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 8 8 t g により列出力ライン C 1 1 2 0 に結合される。青画素 8 8 b は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 8 8 t b により列出力ライン C 1 1 2 0 に結合される。

10

#### 【 0 0 9 8 】

赤画素 9 0 r は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 0 t r により列出力ライン C 2 1 2 2 に結合される。緑画素 9 0 g は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 0 t g により列出力ライン C 2 1 2 2 に結合される。青画素 9 0 b は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 0 t b により列出力ライン C 2 1 2 2 に結合される。

#### 【 0 0 9 9 】

当業者により理解されるように、図 9 及び図 10 に示される色画素センサから転送ゲートラインへの接続のパターンは、3 列群で繰り返される。本発明のこの態様を示すために、1 行及び 3 列が図 9 に示されるが、本発明のこの態様により構成される撮像アレイが任意の数の行列を有し得ることを当業者は理解するであろう。

20

#### 【 0 1 0 0 】

図 10 の表に示されるように、第 1 の色が赤であり、第 2 の色が緑であり、第 3 の色が青である図 9 に示される特定の実施形態の場合、色は、以下の順に列にわたり（6 列に拡張される）読み出される。

#### 【 表 6 】

| C           | 0 | 1 | 2 | 3 | 4 | 5 |

|-------------|---|---|---|---|---|---|

| 行 i TG0     | R | G | B | R | G | B |

| 行 i TG1     | G | B | R | G | B | R |

| 行 i TG2     | B | R | G | B | R | G |

| 行 (i+1) TG0 | R | G | B | R | G | B |

| 行 (i+1) TG1 | G | B | R | G | B | R |

| 行 (i+1) TG2 | B | R | G | B | R | G |

30

40

#### 【 0 1 0 1 】

行毎の読み出し時間が t である場合、行 i (8 2) 内の各画素の 3 色全ての合計読み出し時間は、6 t である。これは、従来技術による実施により行転送ゲートラインを配線することにより得られるのと全く同じ性能である。

#### 【 0 1 0 2 】

50

この構成（X3式読み出しでもなければ、モザイク読み出しでもない）のビデオ読み出しを実行するために、色は、以下のように列において読み出される（6列を示すために拡張される）。

【表7】

| 列位置         | 0 | 1 | 2 | 3 | 4 | 5 |

|-------------|---|---|---|---|---|---|

| 行 i TG0     | R | G | B | R | G | B |

| 行 (i+8) TG0 | R | G | B | R | G | B |

10

## 【0103】

2行での読み出し速度は、2tであり、モザイク配線を使用したモザイク読み出しの速度の2倍である。

## 【0104】

色の置換（すなわち各位置に1色を提供するが、赤、緑及び青の順を変える）が本発明の範囲内であると見なされることを当業者は容易に理解するであろう。

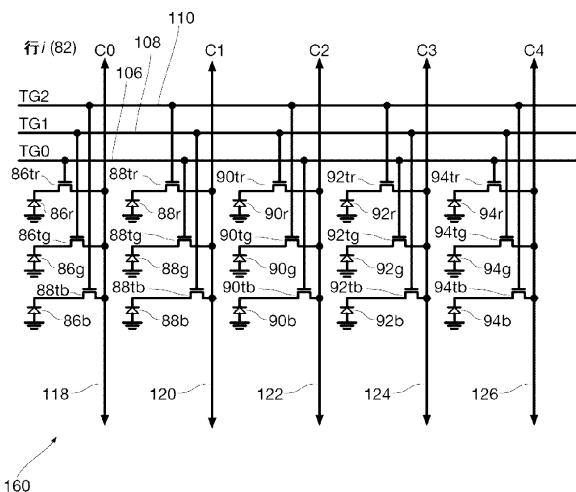

## 【0105】

ここで、図11を参照して、本発明の別の態様による、画素センサアレイ160における3色垂直画素センサの行i-82の配線構造を示す。図3に示される実施形態と同様に、図11に示される実施形態における各3色画素センサは、撮像アレイにおける同じ場所での個々の赤色、緑色及び青色の検知のための赤画素センサ、緑画素センサ及び青画素センサを備える。図11に示される撮像アレイの要素は、図3の撮像アレイに示される要素に対応する場合、図3で使用されるのと同じ参照番号を使用して識別される。

20

## 【0106】

図11の調査から分かり得るように、行i(82)は、4列の3色画素センサを備え、3色画素センサ86r(R0)、86g(G0)及び86b(B0)は、第1の3色画素センサを形成し、3色画素センサ88r(R1)、88g(G1)及び88b(B1)は、第2の3色画素センサを形成し、3色画素センサ90r(R2)、90g(G2)及び90b(B2)は、第3の3色画素センサを形成し、3色画素センサ92r(R3)、92g(G3)及び92b(B3)は、第4の3色画素センサを形成する。

30

## 【0107】

行82は、3つの転送ゲートラインTG0、TG1及びTG2を有する。行82の3つの転送ゲートラインは、それぞれ参照番号106、108及び110で識別される。

## 【0108】

アレイの各列は、列出力ラインを有する。列C0の列出力ラインは、参照番号118で識別される。列C1の列出力ラインは、参照番号120で識別される。列C2の列出力ラインは、参照番号122で識別される。列C3の列出力ラインは、参照番号124で識別される。

40

## 【0109】

個々の各色画素センサは、転送トランジスタを通して関連付けられた列の列出力ラインに接続される。図3に示される実施形態と同様に、図11に示される実施形態における各転送トランジスタは、添え字「t」、及び赤は、「r」、緑は、「g」又は青は、「b」の色識別子が続く、その画素を識別する参照番号で識別される。一例として、画素センサ86内の赤画素センサの転送トランジスタは、86trとして識別される。各転送トランジスタは、本明細書に開示される構造により、画素読み出しのために転送ゲートライン106、108及び110の1つに接続されたゲートを有する。

## 【0110】

50

赤画素 8 6 r は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 8 6 t r により列出力ライン C 0 1 1 8 に結合される。緑画素 8 6 g は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 8 6 t g により列出力ライン C 0 1 1 8 に結合される。青画素 8 6 b は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 8 6 t b により列出力ライン C 0 1 1 8 に結合される。

#### 【 0 1 1 1 】

赤画素 8 8 r は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 8 8 t r により列出力ライン C 1 1 2 0 に結合される。緑画素 8 8 g は、行ライン T G 0 1 0 8 に接続されたゲートを有する転送トランジスタ 8 8 t g により列出力ライン C 1 1 2 0 に結合される。青画素 8 8 b は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 8 8 t b により列出力ライン C 1 1 2 0 に結合される。10

#### 【 0 1 1 2 】

赤画素 9 0 r は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 0 t r により列出力ライン C 2 1 2 2 に結合される。緑画素 9 0 g は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 0 t g により列出力ライン C 2 1 2 2 に結合される。青画素 9 0 b は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 0 t b により列出力ライン C 2 1 2 2 に結合される。

#### 【 0 1 1 3 】

赤画素 9 2 r は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 2 t r により列出力ライン C 3 1 2 4 に結合される。緑画素 9 2 g は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 2 t g により列出力ライン C 3 1 2 4 に結合される。青画素 9 2 b は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 2 t b により列出力ライン C 3 1 2 4 に結合される。20

#### 【 0 1 1 4 】

赤画素 9 4 r は、行ライン T G 0 1 0 6 に接続されたゲートを有する転送トランジスタ 9 4 t r により列出力ライン C 4 1 2 6 に結合される。緑画素 9 4 g は、行ライン T G 1 1 0 8 に接続されたゲートを有する転送トランジスタ 9 4 t g により列出力ライン C 4 1 2 6 に結合される。青画素 9 4 b は、行ライン T G 2 1 1 0 に接続されたゲートを有する転送トランジスタ 9 4 t b により列出力ライン C 4 1 2 6 に結合される。

#### 【 0 1 1 5 】

当業者により理解されるように、図 1 1 及び図 1 2 に示される色画素センサから転送ゲートラインへの接続のパターンは、4 列群で繰り返される。本発明のこの態様を示すために、1 行及び 4 列が図 1 1 に示されるが、本発明のこの態様により構成される撮像アレイが任意の数の行列を有し得ることを当業者は理解するであろう。

#### 【 0 1 1 6 】

図 1 2 の表に示されるように、第 1 の色が赤であり、第 2 の色が緑であり、第 3 の色が青である図 1 1 に示される特定の実施形態の場合、色は、以下のように列にわたり（8 列を示すために拡張される）読み出される。

#### 【 0 1 1 7 】

10

20

30

40

50

【表 8】

| 列位置           | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---------------|---|---|---|---|---|---|---|---|

| 行 $i$ TG0     | R | G | B | G | R | G | B | G |

| 行 $i$ TG1     | G | B | R | B | G | B | R | B |

| 行 $i$ TG2     | B | R | G | R | B | R | G | R |

| 行 $(i+1)$ TG0 | R | G | B | G | R | G | B | G |

| 行 $(i+1)$ TG1 | G | B | R | B | G | B | R | B |

| 行 $(i+1)$ TG2 | B | R | G | R | B | R | G | R |

## 【0 1 1 8】

行毎の読み出し時間が  $t$  である場合、行  $i$  ( 8 2 ) 内の各画素の 3 色全ての合計読み出し時間は、 $6t$  である。これは、従来技術による実施により行転送ゲートラインを配線することにより得られるのと全く同じ性能である。

## 【0 1 1 9】

この構成 ( X 3 式読み出しでもなければ、モザイク読み出しでもない ) のビデオ読み出しを実行するために、色は、以下のように列において読み出される ( 8 列を示すために拡張される )。

## 【表 9】

| 列位置           | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---------------|---|---|---|---|---|---|---|---|

| 行 $i$ TG0     | R | G | B | G | R | G | B | G |

| 行 $(i+8)$ TG0 | R | G | B | G | R | G | B | G |

## 【0 1 2 0】

これは、2 行で  $2t$  かかり、モザイク配線を使用したモザイク読み出しの速度の 2 倍である。

## 【0 1 2 1】

「RGB」及び「BGR」群が「G」位置において 1 つの画素に結合されることに当業者は留意するであろう。これは、図 9 の実施形態よりも多くの計算された画素 ( 2 つの水平画素毎に 1 つ ) を与える。

## 【0 1 2 2】

図 1 1 及び図 1 2 に示される実施形態は、モザイク配線と同様に、幾らかの色エイリアシングを有する。この実施形態は、繰り返しパターン 2 を有するモザイク配線とは対照的に、繰り返しパターン 4 を有する。

## 【0 1 2 3】

本発明の別の実施形態によれば、図 2 B に示される従来通りに配線されたアレイは、ビデオモードで読み出し得る。以下の表に図 2 B での全色及び全画素の読み出しを示す。

10

20

30

40

50

【表 1 0】

| 列位置         | 0 | 1 | 2 | 3 |

|-------------|---|---|---|---|

| 行 i TG0     | R | R | R | R |

| 行 i TG1     | G | G | G | G |

| 行 i TG2     | B | B | B | B |

| 行 (i+1) TG0 | R | R | R | R |

| 行 (i+1) TG1 | G | G | G | G |

| 行 (i+1) TG2 | B | B | B | B |

10

【0 1 2 4】

20

この読み出し構造は、図 2 B の配線を使用するが、追加のエイリアシングを犠牲にして図 4 の実施形態を使用するモザイク読み出しと同じ速度を与える。

【0 1 2 5】

この構成 (X 3 式読み出しでもなければ、モザイク読み出しでもない) のビデオ読み出しを実行するために、色は、以下のように列において読み出される。

【表 1 1】

| 行位置         | 0 | 1 | 2 | 3 |

|-------------|---|---|---|---|

| 行 i TG0     | R | R | R | R |

| 行 i TG1     | G | G | G | G |

| 行 (i+8) TG1 | G | G | G | G |

| 行 (i+8) TG2 | B | B | B | B |

30

【0 1 2 6】

40

図 3、図 5、図 7、図 9 及び図 1 1 に示される全ての実施形態において、画面を過度に複雑にし、本発明を曖昧にする可能性を避けるために、概略図が簡易化されていることを当業者は即座に認識するであろう。図 2 A の個々の多色垂直画素センサ 3 0 は、画素センサのアレイ内の行ライン及び列ラインに接続される。図 1 3 は、図 2 A の個々の多色垂直画素センサ 3 0 が利用される環境の非限定的な例を示すために提供される。

【0 1 2 7】

図 1 3 の要素は、画素 3 0 及びアレイへの接続の一例をより詳細に提供するために、行

50

列配線に関して図 2 B の従来技術によるアレイの状況で示される。適切な場合、図 2 B に利用される参照番号は、それらの従来の図面に存在する図 1 3 の要素を示すのに使用される。

#### 【 0 1 2 8 】

図 2 B に示される従来技術による構成では、アレイの行  $i$  内の赤センサは、参照番号 5 2 におけるダイオードとして示され、緑センサは、参照番号 5 4 におけるダイオードとして示され、青センサは、参照番号 5 6 におけるダイオードとして示される。赤転送トランジスタは、参照番号 6 0 において示され、ゲートは、転送ゲートライン T G i r 6 2 に結合される。緑転送トランジスタは、参照番号 6 4 において示され、ゲートは、転送ゲートライン T G i g 6 6 に結合される。青転送トランジスタは、参照番号 6 8 において示され、ゲートは、転送ゲートライン T G i b 7 0 に結合される。転送ゲートラインは、行  $i$  内の全ての赤センサが赤転送ゲートライン 6 2 に結合され、行  $i$  内の全ての緑センサが緑転送ゲートライン 6 6 に結合され、行  $i$  内の全ての青センサが青転送ゲートライン 7 0 に結合されるという点で従来通り配線される。

#### 【 0 1 2 9 】

図 1 3 に示される実際のセンサの非限定的な例では、赤、緑及び青転送トランジスタ 6 0、6 4 及び 6 8 は、共通ノード 1 6 2 と一緒に接続される。共通ノード 1 6 2 は、行リセットライン 1 6 4 に結合されたゲートを有する画素リセットトランジスタ 1 6 6 を通してリセット電位  $V_{reset}$  に結合し得る。共通ノード 1 6 2 は、共通ノードに結合されたゲートを有するソースフォロア増幅器トランジスタ 1 7 0 等のデバイスを通してアレイの列出力ライン 1 6 8 にも結合可能である。フォトダイオード 3 2、3 6 及び 4 2 により蓄積された電荷を読み出すことが望ましい場合、行イネーブルライン 1 7 2 は、トランジスタ 1 7 4 を作動させて、ソースフォロアトランジスタ 1 7 0 の出力を結合する。当業者に理解されるように、列ライン 1 6 8 は、当技術分野で既知のように、電流源 1 7 6 により駆動し得る。列ライン 1 6 8 は、列放電信号を列放電ソースフォロアトランジスタ 1 7 8 のゲートに印加することにより、選択されたときに列放電電位  $V_{discharge}$  に放電し得る。

#### 【 0 1 3 0 】

本発明の原理が、本明細書に提示される本発明の幾つかの実施形態を用いて開示されるように、赤、緑及び青選択ライン 6 2、6 6 及び 7 0 を再配置し、転送ゲートライン T G 0 1 0 6、T G 1 1 0 8 及び T G 2 1 1 0 を置き換えることにより、限定ではなく、図 1 3 の例に示されるもの等の多色垂直画素センサのアレイに容易に適用されることを当業者は理解するであろう。

#### 【 0 1 3 1 】

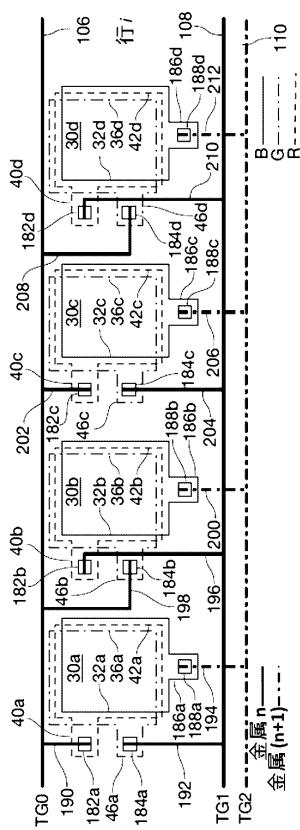

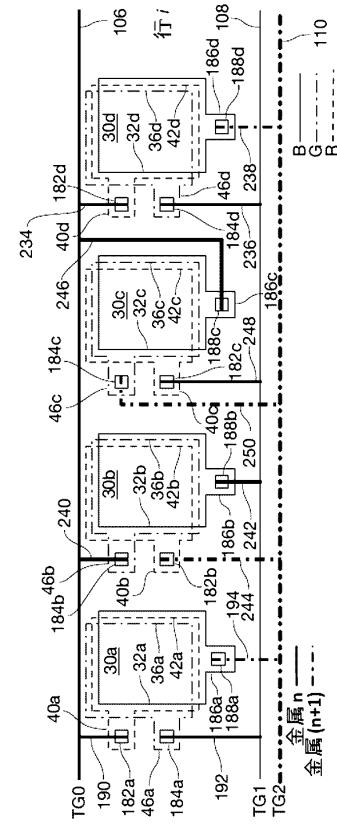

ここで、図 1 4 を参照すると、図 3 に示されるそのような画素センサのアレイの行内の図 2 A の画素センサ 3 0 のような 4 つの垂直画素センサのレイアウトの簡易化された部分の上面図は、埋められた赤及び緑センサからの電荷の転送に使用されるプラグ並びに青センサのコンタクトの位置を示す。図 2 A の画素センサの要素が図 1 4 に示されている場合、それらは、図 2 A におけるこれらの要素の指定に使用されるのと同じ参照番号を使用して参照される。図 1 4 には 4 つの画素が示されるため、添え字「a」～「d」を含む参照番号でそれぞれ識別される。画素センサ 3 0 a、3 0 b、3 0 c 及び 3 0 d 内に埋められた赤及び緑センサが互いにわずかにオフセットされることを示す図 1 4 の上面図が描かれるが、これは、本発明を例示するために行われ、垂直画素センサの実際の実施形態では、青、緑及び赤色センサが互いに位置合わせされることを当業者は理解するであろう。

#### 【 0 1 3 2 】

図 1 4 の画素センサ 3 0 a において、参照番号 4 0 a は、電荷を赤センサ（参照番号 4 2 a により破線で示される）から運ぶプラグがコンタクトする赤センサ 4 2 a から外向きに延びるタブを示す。参照番号 4 6 a は、電荷を緑センサ（参照番号 3 6 a により破線で示される）から運ぶプラグがコンタクトする緑センサ 3 6 a から外向きに延びるタブを示す。同様に、画素センサ 3 0 b ～ 3 0 d において、参照番号 4 0 b ～ 4 0 d は、それぞれ電荷を赤センサ（参照番号 4 2 b ～ 4 2 d により破線で示される）から運ぶプラグの場所

10

20

30

40

50

を示す赤センサから伸びるタブを示し、参照番号 4 6 b ~ 4 6 d は、それぞれ電荷を緑センサ（参照番号 3 6 b ~ 3 6 d により破線で示される）から運ぶプラグの場所に対応するタブを示す。当業者により理解されるように、タブ 4 0 a ~ 4 0 d 及び 4 6 a ~ 4 6 d は、各センサの集光エリアを十分に利用するために、各センサの集光エリアのエッジ外部に配置される。

#### 【 0 1 3 3 】

青センサ 3 2 a ~ 3 2 d は、画素センサの表面にあり、プラグを必要とせず、代わりに青センサ 3 2 a ~ 3 6 d にコンタクトするための 1 8 6 a ~ 1 8 6 d という名称のタブを有するため、実線で示されている。

#### 【 0 1 3 4 】

画素センサ 3 0 a において、参照番号 1 8 2 a、1 8 4 a 及び 1 8 8 a は、それぞれ赤、緑及び青センサからのそれぞれの接続構造を示す。当業者に理解されるように、プラグ（4 0 及び 4 6、それぞれ緑及び赤センサについて図 2 A に示される）は、埋められた緑及び赤センサの出力を半導体表面に運ぶのに必要である。各接続構造は、これらの構造が転送トランジスタ、リセットトランジスタ並びに青、緑及び赤センサ 3 2 a、3 6 a 及び 4 2 a の転送トランジスタに結合される増幅器トランジスタのゲートに接続するという点で、図 2 A において青、緑及び赤センサ 3 2、3 6 及び 4 2 への接続をそれぞれ示す単純なコンタクト 3 4、3 8 及び 4 4 よりもはるかに複雑な接続構造である。図面を過度に複雑にするのを避けるために、これらの要素のいずれも図 1 4 に明示的に示されておらず、図 1 3 に示されるように、そのようなアレイ内のこれらの構成要素の存在及び配置は、当業者に周知である。同様にして、画素センサ 3 0 b ~ 3 0 d において、参照番号 1 8 2 b ~ d、1 8 4 b ~ d 及び 1 8 8 b ~ d は、それぞれ画素センサ 3 0 a について説明したような接続構造を示す。

#### 【 0 1 3 5 】

図 1 4 に示される等の多色垂直画素センサアレイの一レイアウトにおいて、表面赤及び緑接続構造にコンタクトするのに使用されるコンタクトプラグにコンタクトする赤及び緑センサから伸びるタブ並びに全ての画素センサ 3 0 a ~ 3 0 d における青接続構造にコンタクトするのに使用される表面青センサから伸びるタブの場所は、あらゆる画素で同じである。したがって、図 3 に示される本発明の実施形態を実施するために、転送ゲートライン T G 0（図 3、図 5、図 7、図 9 及び図 1 1 の全てにおいて参照番号 1 0 6）は、画素センサ 3 0 a 及び 3 0 c における赤センサ 4 2 a、4 2 c の接続構造 1 8 2 a 及び 1 8 2 c からの第 1 のルーティング（配線区分 1 9 0 及び 2 0 2）並びに画素センサ 3 0 b 及び 3 0 d における緑センサ 3 6 b、3 6 d の接続構造 1 8 4 b 及び 1 8 4 d からの第 2 の異なるルーティング（配線区分 1 9 8 及び 2 0 8）を使用して接続され、したがって、集積回路のメタライゼーション構造を複雑にする。同じことは、画素センサ 3 0 a 及び 3 0 c における緑センサ 3 6 a、3 6 c の接続構造 1 8 4 a 及び 1 8 4 c からの第 1 のルーティング（配線区分 1 9 2 及び 2 0 4）並びに画素センサ 3 0 b 及び 3 0 d における赤センサ 4 2 b、4 2 d の接続構造 1 8 2 b 及び 1 8 2 d からの第 2 の異なるルーティング（配線区分 1 9 6 及び 2 1 0）を使用して接続されるという点でゲートライン T G 1（図 3、図 5、図 7、図 9 及び図 1 1 の全てにおいて参照番号 1 0 8）にも当てはまる。なお、単純な配線区分 1 9 0 及び 1 9 2 を使用して、転送ゲートライン T G 0 及び T G 1 をそれぞれ画素センサ 3 0 a 内の赤及び緑接続構造 1 8 2 a 及び 1 8 4 a に接続し、単純な配線区分 2 0 2 及び 2 0 4 を使用して、転送ゲートライン T G 0 及び T G 1 をそれぞれ画素センサ 3 0 c 内の赤及び緑接続構造 1 8 2 c 及び 1 8 4 c に接続する。単純な配線区分 1 9 4、2 0 0、2 0 6 及び 2 1 2 を使用して、転送ゲートライン T G 2 を青接続構造 1 8 8 a、1 8 8 b、1 8 8 c 及び 1 8 8 d に接続する。転送ゲートライン T G 0 及び T G 1 がある金属相互接続層に配置され、転送ゲートライン T G 2 が、第 2 の異なる金属相互接続層に配置されることに当業者は留意するであろう。

#### 【 0 1 3 6 】

転送ゲートライン T G 1（参照番号 1 0 8）から接続構造 1 8 2 b に伸びるより長い金

10

20

30

40

50

属線区分 196 及び転送ゲートライン TG0 ( 参照番号 106 ) から接続構造 184b に延びる、同様により長い金属線区分 198 を必要とすることにより、プラグを通して転送ゲートライン TG0\_106 及び TG1\_108 をそれぞれ画素センサ 30b 内の赤及び緑接続構造 182b 及び 184d に接続するために、より複雑で長いルーティングが必要とされる。同じことは、転送ゲートライン TG1 ( 参照番号 108 ) から接続構造 182d に延びるより長い金属線区分 210 及び転送ゲートライン TG0 ( 参照番号 106 ) から接続構造 184d に延びる、同様により長い金属線区分 208 を必要とすることにより、画素センサ 30d 内の赤及び緑接続構造 182d 及び 184d の接続にも当てはまる。

### 【 0137 】

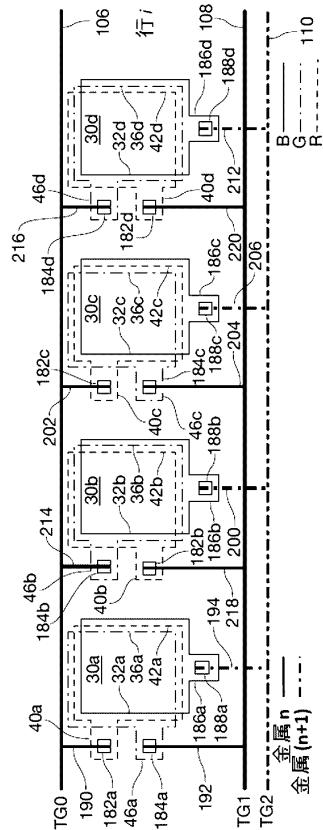

本発明の実施形態によれば、変更された画素レイアウトは、画素センサへの配線を簡易化する。ここで、図 15 を参照すると、上面図は、アレイの行内の 4 つの垂直画素センサ 30a ~ 30d のレイアウトの簡易化された部分を示して、本発明の別の態様を示し、それにより、埋められた赤及び緑センサからの電荷の転送に使用されるプラグに接続するタブの位置は、本発明の態様により、交互の隣接する画素センサにおいて異なる。本発明のこの態様による図 15 に示されるレイアウトは、図 3 に示される本発明の実施形態に対応する。図 14 の場合と同様に、転送ゲートライン TG0\_106 及び TG1\_108 がある金属相互接続層に配置され、転送ゲートライン TG2\_110 が第 2 の異なる金属相互接続層に配置されることに当業者は留意するであろう。

### 【 0138 】

図 15 における画素センサ 30a ~ 30d の配置が図 14 の画素センサ 30a ~ 30d のものと同様であるが、画素センサ 30b 及び 30d におけるタブ 40d、46d、40d 及び 46d の物理的な位置は、画素センサ 30a 及び 30c における対応するタブ 40a、46a、40c 及び 46c の位置から逆になることを当業者は観測するであろう。図 15 から見て取ることができるように、このレイアウト変更は、集積回路のメタライゼーション構造を簡易化し、より単純で短い金属線区分 214 及び 216 が転送ゲート TG0 ( 参照番号 106 ) から緑金属相互接続構造 184b 及び 184 に延び、より短い金属線区分 218 及び 220 が転送ゲートライン TG1 ( 参照番号 108 ) からそれぞれ延びて、画素センサ 30b 及び 30d における赤金属相互接続構造 182b 及び 182d に接続することができる。したがって、画素センサ 30b における金属線区分 214 及び 218 並びに画素センサ 30d における金属線区分 216 及び 220 は、画素センサ 30a における金属線区分 190 及び 192 並びに画素センサ 30c における金属線区分 202 及び 204 と幾何学的に同じであり得る。画素センサ 30a ~ 30d における青コンタクトへの接続は、図 14 に示されるものと同じである。

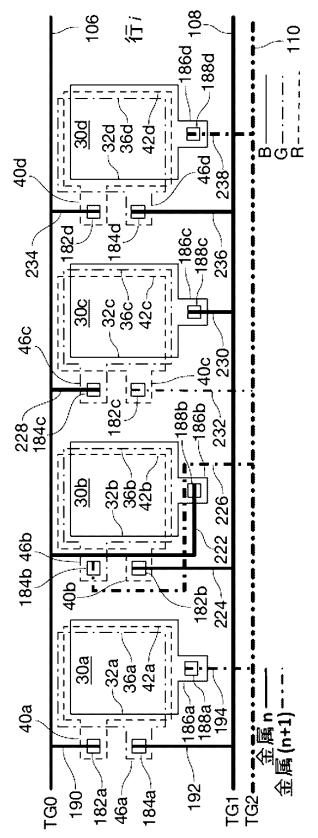

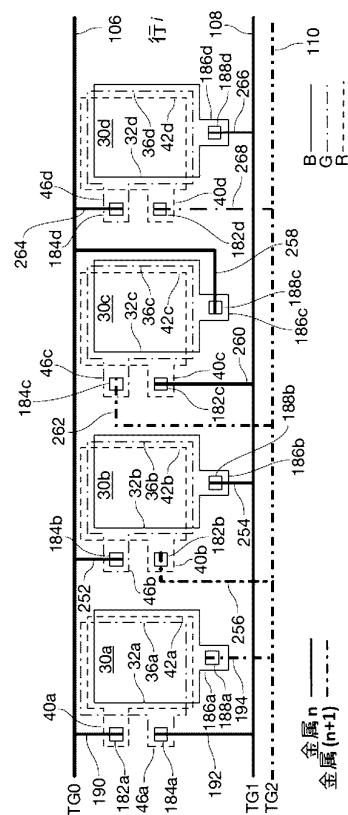

### 【 0139 】

ここで、図 16 を参照すると、上面図は、アレイの行内の 4 つの隣接する垂直画素センサ 30a、30b、30c 及び 30d のレイアウトの簡易化された部分を示して、本発明の別の態様を示し、それにより、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置は、本発明の態様により、4 つの隣接する画素センサの群において異なる。図 16 における画素センサ 30a ~ 30d の配置はまた、図 14 の画素センサ 30a ~ 30d のものと同様であるが、画素センサ 30b 及び 30c における赤及び緑タブ 40b 及び 46d 並びに赤及び緑タブ 40c 及び 46c は、画素センサ 30a 及び 30d における対応する赤及び緑タブ 40a 及び 46a 並びに赤及び緑タブ 40d 及び 46d の位置から逆になることを当業者は観測するであろう。本発明のこの態様による図 16 に示されるレイアウトは、図 7 に示される本発明の実施形態に対応する。転送ゲートライン TG0、TG1 及び TG2 への接続のパターンは、隣接する画素 30a、30b 及び 30c で異なる。画素 30a の転送ゲート接続は、図 14 及び図 15 と同じである。画素 30b において、転送ゲート TG0\_106 は、金属区分 222 により青金属相互接続構造 188b に接続され、転送ゲート TG1\_108 は、金属区分 224 により赤相互接続構造 182b に接続され、転送ゲート TG2\_110 は、金属区分 226 により緑相互接続構造 184b に接続される。画素 30c において、転送ゲート TG106 は、金属区分 228

10

20

30

40

50

により緑金属相互接続構造 184c に接続され、転送ゲート TG1 108 は、金属区分 230 により青金属相互接続構造 188c に接続され、転送ゲート TG2 110 は、金属区分 232 により赤金属相互接続構造 182c に接続される。第 4 の画素センサ 30d のレイアウトは、第 1 の画素センサ 30a のものと同じである。画素 30d において、転送ゲート TG0 106 は、金属区分 234 により赤金属相互接続構造 182d に接続され、転送ゲート TG1 108 は、金属区分 236 により緑金属相互接続構造 184d に接続され、転送ゲート TG2 110 は、金属区分 238 により青金属相互接続構造 188d に接続される。パターンは、画素の 4 列毎に繰り返され、赤画素 94r、緑画素 94g 及び青画素 94b を含む図 7 に示される第 5 の列 (C4) 内の 5 番目の画素センサは、4 つの垂直画素センサの繰り返される次の群における最初の画素センサである。転送ゲートライン TG0 106 及び TG1 108 は、ある金属相互接続層に配置され、転送ゲートライン TG2 110 は、第 2 の異なる金属相互接続層に配置される。

#### 【0140】

ここで、図 17 を参照すると、上面図は、アレイの行内の 4 つの隣接する垂直画素センサ 30a、30b、30c 及び 30d のレイアウトの簡易化された部分を示して、本発明の別の態様を示し、それにより、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置は、本発明の態様により、4 つの隣接する画素センサの群において異なる。本発明のこの態様による図 17 に示されるレイアウトは、図 9 に示される本発明の実施形態に対応する。転送ゲートライン TG0、TG1 及び TG2 への接続のパターンは、隣接する画素 30a、30b 及び 30c で異なる。画素 30a の転送ゲート接続は、図 14、図 15 及び図 16 と同じである。

#### 【0141】

転送ゲートライン TG0 106 は、配線区分 190 により画素センサ 30a の赤センサ 42a の金属相互接続構造 182a に接続される。転送ゲートライン TG1 108 は、配線区分 192 により画素センサ 30a の緑センサ 36a の金属相互接続構造 184a に接続される。転送ゲートライン TG2 110 は、配線区分 194 により画素センサ 30a の青センサ 32a の金属相互接続構造 188a に接続される。転送ゲートライン TG2 及び配線区分 194 の両方は、他の転送ゲート及び配線区分と異なるメタライゼーション層に配置される。

#### 【0142】

画素センサ 30b において、赤及び緑タブ 40b 及び 46b の位置は、画素センサ 30a における対応するタブの位置から逆になる。転送ゲートライン TG0 106 は、配線区分 240 により画素センサ 30b の緑センサ 36b の接続構造 184b に接続される。転送ゲートライン TG1 108 は、配線区分 242 により画素センサ 30b の青センサ 32b の接続構造 188b に接続される。転送ゲートライン TG2 110 は、配線区分 244 により画素センサ 30b の赤センサ 42b の接続構造 182b に接続される。配線区分 244 は、転送ゲートライン TG2 110 と同じメタライゼーション層に配置される。

#### 【0143】

画素センサ 30c において、赤及び緑タブ 40c 及び 46c の位置は、画素センサ 30b における対応するタブの位置と同じである。転送ゲートライン TG0 106 は、配線区分 246 により画素センサ 30c の青センサ 32c の接続構造 188c に接続される。転送ゲートライン TG1 108 は、配線区分 248 により画素センサ 30c の赤センサ 42c の接続構造 182c に接続される。転送ゲートライン TG2 110 は、配線区分 250 により画素センサ 30c の緑センサ 36c の接続構造 184c に接続される。配線区分 250 は、転送ゲートライン TG2 110 と同じメタライゼーション層に配置される。

#### 【0144】

図 17 における画素センサ 30d は、図 16 の画素センサ 30d と同じように転送ゲートラインに接続される。転送ゲートライン TG0 106 は、配線区分 234 により画素

10

20

30

40

50

センサ30dの赤センサ42dの金属相互接続構造182dに接続される。転送ゲートラインTG1 108は、配線区分236により画素センサ30dの緑センサ36dの金属相互接続構造184dに接続される。転送ゲートラインTG2 110は、配線区分238により画素センサ30dの青センサ32dの青接続構造188dに接続される。

#### 【0145】

ここで、図18を参照すると、上面図は、アレイの行内の図2Aのような4つの隣接する垂直画素センサ30a、30b、30c及び30dのレイアウトの簡易化された部分を示して、本発明の別の態様を示し、それにより、埋められた赤及び緑センサから電荷を転送するのに使用されるプラグの位置は、本発明の態様により、4つの隣接する画素センサの群において異なる。本発明のこの態様による図18に示されるレイアウトは、図11に示される本発明の実施形態に対応する。10

#### 【0146】

転送ゲートラインTG0、TG1及びTG2への接続のパターンは、全ての画素センサ30a～30dで異なる。パターンは、画素の4列毎に繰り返され、赤画素94r、緑画素94g及び青画素94bを備える図11に示される第5の列(C4)内の5番目の画素センサは、4つの垂直画素センサの繰り返される次の群における最初の画素センサである。図18において、転送ゲートラインTG0 106及びTG1 108は、ある金属相互接続層に配置され、転送ゲートラインTG2 110は、第2の異なる金属相互接続層に配置される。

#### 【0147】

転送ゲートラインTG0 106は、配線区分190により画素センサ30aの赤センサ42aの金属相互接続構造182aに接続される。転送ゲートラインTG1 108は、配線区分192により画素センサ30aの緑センサ36aの金属相互接続構造184aに接続される。転送ゲートラインTG2 110は、配線区分194により画素センサ30aの青センサ32aの青接続構造188aに接続される。配線194は、転送ゲートラインTG2と同じ配線区分に配置される。20

#### 【0148】

転送ゲートラインTG0 106は、配線区分252により画素センサ30bの緑センサ36bの接続構造184bに接続される。転送ゲートラインTG1 108は、配線区分254により画素センサ30bの青センサ32bの青接続構造188bに接続される。転送ゲートラインTG2 110は、配線区分256により画素センサ30bの赤センサ42bの赤接続構造182bに接続される。配線区分256は、転送ゲートラインTG2と同じ配線区分に配置される。30

#### 【0149】

転送ゲートラインTG0 106は、配線区分258により画素センサ30cの青センサ32cの青接続構造188cに接続される。転送ゲートラインTG1 108は、配線区分260により画素センサ30cの赤センサ42cの接続構造182cに接続される。転送ゲートラインTG2 110は、配線区分262により画素センサ30cの緑センサ36cの接続構造184cに接続される。配線区分262は、転送ゲートラインTG2と同じ配線区分に配置される。40

#### 【0150】

転送ゲートラインTG0 106は、配線区分264により画素センサ30dの緑センサ36dの接続構造184dに接続される。転送ゲートラインTG1 108は、配線区分266により画素センサ30dの青センサ32dの青接続構造188dに接続される。転送ゲートラインTG2 110は、配線区分268により画素センサ30dの赤センサ42dの接続構造182dに接続される。配線区分268は、転送ゲートラインTG2と同じ配線区分に配置される。

#### 【0151】

本発明の実施形態及び適用について示し説明したが、本明細書における本発明の概念から逸脱せずに、上記よりもはるかに多くの変更形態が可能であることが当業者に理解され50

る。したがって、本発明は、添付の特許請求の範囲の趣旨以外に限定されるべきではない。

【図面】

【図 1】

各行の読み出し時間 =  $t$

2行3色の読み出し時間 =  $2t$

(従来技術)

【図 2 A】

(従来技術)

10

【図 2 B】

【図 3】

20

30

40

50

【図 4】

|            | C0  | C1 | C2 | C3 | C4 |

|------------|-----|----|----|----|----|

| 行 <i>i</i> | TG0 | R  | G  | R  | G  |

|            | TG1 | G  | R  | G  | R  |

|            | TG2 | B  | B  | B  | B  |

|              | C0  | C1 | C2 | C3 | C4 |

|--------------|-----|----|----|----|----|

| 行 <i>i+1</i> | TG0 | R  | R  | R  | R  |

|              | TG1 | G  | B  | G  | B  |

|              | TG2 | B  | G  | B  | G  |

【図 5】

10

【図 6】

|     | C0  | C1 | C2 | C3 | C4 | C5  |

|-----|-----|----|----|----|----|-----|

| TG0 | G0  | B0 | R3 | G3 | B3 | xxx |

| TG1 | R1  | G1 | B1 | R4 | G4 | B4  |

| TG2 | xxx | R2 | G2 | B2 | R5 | G5  |

【図 7】

20

30

40

50

【図 8】

|     | C0 | C1 | C2 | C3 | C4 |

|-----|----|----|----|----|----|

| TG0 | R0 | B1 | G2 | R3 | R4 |

| TG1 | G0 | R1 | B2 | G3 | G4 |

| TG2 | B0 | G1 | R2 | B3 | B4 |

【図 9】

10

【図 10】

|     | C0 | C1 | C2 | C3 | C4 |

|-----|----|----|----|----|----|

| TG0 | R0 | G1 | B2 | R3 | G4 |

| TG1 | G0 | B1 | R2 | G3 | B4 |

| TG2 | B0 | R1 | G2 | B3 | R4 |

【図 11】

20

30

40

50

【図 1 2】

|     | C0 | C1 | C2 | C3 | C4 |

|-----|----|----|----|----|----|

| TG0 | R0 | G1 | B2 | G3 | R4 |

| TG1 | G0 | B1 | R2 | B3 | G4 |

| TG2 | B0 | R1 | G2 | R3 | B4 |

【図 1 3】

10

20

【図 1 4】

【図 1 5】

30

40

50

【図16】

【図17】

【図18】

---

フロントページの続き

神奈川県川崎市麻生区栗木2丁目4番16号 株式会社シグマ内

(72)発明者 ユウ、ジョナサン

アメリカ合衆国 94587 カリフォルニア州、ユニオン シティ、マリナ コート 32453

(72)発明者 ケラー、グレン

アメリカ合衆国 19382 ペンシルバニア州、ウェスト チェスター、チッカディー レーン 904

審査官 鈴木 明

(56)参考文献 特表2002-513145 (JP, A)

特開2008-004753 (JP, A)

特開2006-228801 (JP, A)

特開2013-021660 (JP, A)

特開2014-072541 (JP, A)

特開2001-086520 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79