(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5366127号

(P5366127)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月20日(2013.9.20)

(51) Int.Cl.

F 1

|               |           |              |   |

|---------------|-----------|--------------|---|

| HO 1 L 21/82  | (2006.01) | HO 1 L 21/82 | M |

| HO 1 L 27/118 | (2006.01) | HO 1 L 27/04 | A |

| HO 1 L 21/822 | (2006.01) |              |   |

| HO 1 L 27/04  | (2006.01) |              |   |

請求項の数 6 (全 34 頁)

(21) 出願番号

特願2008-305100 (P2008-305100)

(22) 出願日

平成20年11月28日 (2008.11.28)

(65) 公開番号

特開2010-129895 (P2010-129895A)

(43) 公開日

平成22年6月10日 (2010.6.10)

審査請求日

平成23年8月25日 (2011.8.25)

(73) 特許権者 504378124

スパンション エルエルシー

アメリカ合衆国 カリフォルニア州 94

088-3453 サニーベイル テグウ

イン ドライブ 915

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(72) 発明者 有賀 健太

東京都新宿区西新宿二丁目7番1号 富士

通マイクロエレクトロニクス株式会社内

(72) 発明者 橋 大

東京都新宿区西新宿二丁目7番1号 富士

通マイクロエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】アナログ集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のトランジスタセルが、アレイ状に配置されたアナログ回路用セルアレイを有する

アナログ集積回路であって、

前記複数のトランジスタセルは、PMOSトランジスタセルと、NMOSトランジスタ

セルと、を備え、

同種のトランジスタセルが、4行ずつ、4列以上連続して配置されており、4行ずつ、

4列以上連続して配置された同種のトランジスタセルの中心部分の2×2個のトランジス

タセルを使用したコモンセントロイド配置の、共通の重心を有する2つのトランジスタ対

を備え、

前記複数のトランジスタセルの各トランジスタセルは、

隣接して順に配置された第1ソース領域、第1チャネル領域、共通のドレイン領域、第

2チャネル領域および第2ソース領域と、

前記第1チャネル領域および前記第2チャネル領域上にそれぞれ配置された第1ゲート

電極および第2ゲート電極と、を備え、

前記第1ゲート電極と前記第2ゲート電極は接続して使用され、

前記第1ソース領域と前記第2ソース領域は接続して使用されることを特徴とする

アナログ集積回路。

## 【請求項 2】

各トランジスタセルは、前記第1ゲート電極と前記第2ゲート電極を接続する接続電極

を備える請求項 1 に記載のアナログ集積回路。

**【請求項 3】**

各トランジスタセルの前記第 1 ゲート電極および前記第 2 ゲート電極は、それぞれ前記第 1 チャネル領域および前記第 2 チャネル領域の外側に伸び、外側の部分に配線コンタクトを備える請求項 1 または 2 に記載のアナログ集積回路。

**【請求項 4】**

各トランジスタセルの境界部分に設けられ、各トランジスタセルのウェルに給電するための拡散領域を備える請求項 1 から 3 のいずれか 1 項に記載のアナログ集積回路。

**【請求項 5】**

使用されるトランジスタセルの前記第 1 チャネル領域および前記第 2 チャネル領域上には、金属配線が配置されない請求項 1 から 4 のいずれか 1 項に記載のアナログ集積回路。 10

**【請求項 6】**

前記中心部分以外のトランジスタセルをダイオード接続した 2 つのトランジスタセルであって、前記コモンセントロイド配置の各トランジスタ対の 2 個のトランジスタセルの前記第 1 ゲート電極と前記第 2 ゲート電極に接続されるトランジスタセルを備え、前記ダイオード接続した 2 つのトランジスタセルは、前記共通の重心に対して点対称の位置に配置されている請求項 1 に記載のアナログ集積回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、アナログ回路用セルアレイおよびそのようなアナログ回路用セルアレイを使用して形成したアナログ集積回路に関する。 20

**【背景技術】**

**【0002】**

所望のデジタル回路を有するデジタル集積回路を短いリードタイムで製造するために、ゲートアレイを利用することが知られている。ゲートアレイは、トランジスタや論理回路要素などの基本セルを多数アレイ状に配列したものである。これにユーザの所望のデジタル回路に応じた配線パターンを形成することにより、簡単にデジタル集積回路が製造できる。

**【0003】**

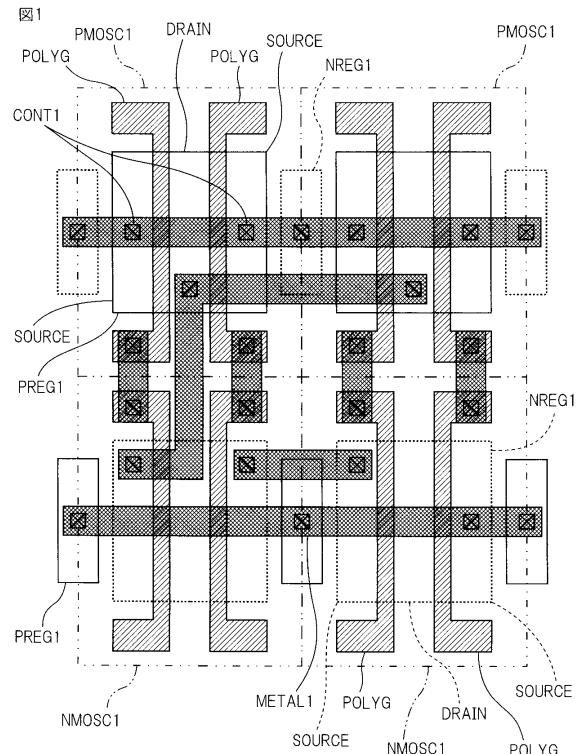

図 1 は、ゲートアレイの 4 個の基本セルに配線パターンを形成した例を示す図である。図 1 の例では、2 個の PMOS 基本セル PMOSC1 および 2 個の NMOS 基本セル NMOSC1 が隣接して配置されている。PMOS 基本セル PMOSC1 は、P 型拡散領域 PREG1 と、PREG1 の上に形成された 2 本のポリシリコンゲート電極 POLYG と、を有する。2 本の POLYG の間が P 型トランジスタのドレイン領域 DRAIN で、2 本の POLYG の両側が P 型トランジスタのソース領域 SOURCE である。すなわち、この基本セルには、2 個の PMOS トランジスタを形成できる。同様に、NMOS 基本セル NMOSC1 は、N 型拡散領域 NREG1 と、NREG1 の上に形成された 2 本のポリシリコンゲート電極 POLYG と、を有する。2 本の POLYG の間が N 型トランジスタのドレイン領域 DRAIN で、2 本の POLYG の両側が N 型トランジスタのソース領域 SOURCE である。すなわち、この基本セルには、2 個のトランジスタを形成できる。隣接する PMOSC1 の間には N 型拡散領域 NREG1 が、隣接する NMOSC1 の間には P 型拡散領域 PREG1 が、それぞれ形成される。基本セル PMOSC1 および NMOSC1 のゲート電極 POLYG、ドレイン領域 DRAIN、ソース領域 SOURCE および素子間の拡散領域 PREG1、NREG1 は、金属配線 METAL1 とコンタクト CONTACT1 により接続される。 40

**【0004】**

PMOSC1 および NMOSC1 を基本単位として、多数の基本単位がアレイ状に配置される。

**【0005】**

10

20

30

40

50

なお、図1の例では、各基本単位PMOS C1およびNMOS C1には、2個のトランジスタを形成できるが、1個のトランジスタのみを形成できる場合もある。また、各基本単位の2個のトランジスタは、駆動能力を2倍にするために、同じ動作をするトランジスタとして使用する場合もあるが、2個の個別のトランジスタとして動作するように使用することが可能である。同じ動作をするトランジスタとして使用する場合には、ドレイン領域は共通であり、2本のゲート電極および2個のソース領域はそれぞれ電気的に接続される。また、2個の個別のトランジスタとして動作する場合には、2本のゲート電極および2個のソース領域の少なくとも一方は電気的に接続されない。このように、各基本単位PMOS C1およびNMOS C1の2個のトランジスタは、基本的には1個ずつ使用されることを前提として形成されている。

10

## 【0006】

デジタル回路用のゲートアレイは広く知られているので、詳しい説明は省略する。

## 【0007】

近年、アナログ回路は、高い集積度を有するとともに、短いリードタイムで製造することが要望されている。

## 【0008】

デジタル回路は、0または1の所定のレベル範囲の2値信号を出力するかまたはそのような2値信号で動作すればよく、所定の製造誤差範囲であれば正常に動作する回路を容易に製造することが可能である。これに対して、アナログ回路は、電圧値や電流値などの信号のアナログ値が動作や出力に直接関係する。そのため、製造誤差による素子の特性差の影響を受け易いという問題があった。そこで、アナログ回路は、仕様に応じて個別に設計され、製造段階でも調整などを行い、所望の製造を実現していた。

20

## 【0009】

アナログ回路では、製造時のイオン注入の分布や、酸化膜厚さの分布などのために、配置位置によりトランジスタの特性に差を生じる。このような特性の差を相殺するために、コモンセントロイド配置と呼ばれる配置方法が知られている。例えば、差動アンプの差動対をなす2個のトランジスタの特性に差があるとアナログ回路の誤差が大きくなるので、差動対をなす2個のトランジスタがコモンセントロイド配置される。

## 【0010】

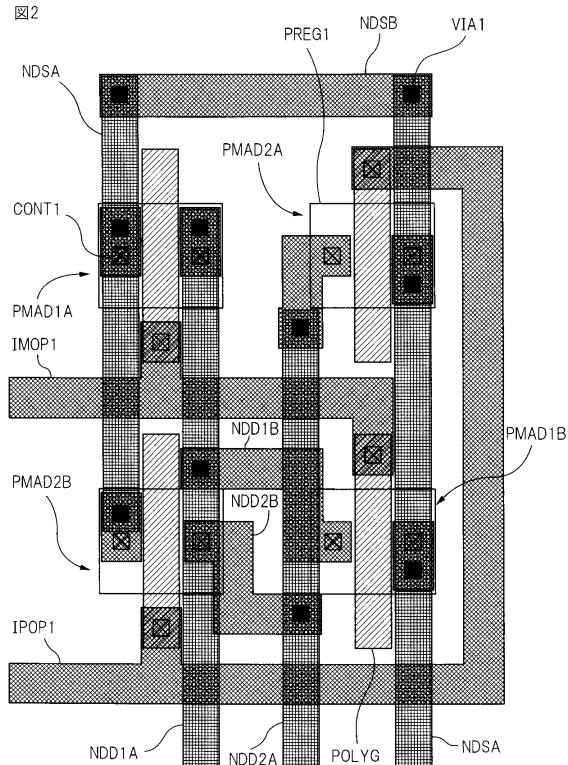

図2は、P型トランジスタの差動対のコモンセントロイド配置のレイアウト例を示す図である。差動対をなす一方の第1P型トランジスタPMAD1は、PMAD1AとPMAD1Bで形成され、差動対をなす他方の第2P型トランジスタPMAD2は、PMAD2AとPMAD2Bで形成される。PMAD1AとPMAD1Bは対角に配置され、PMAD2AとPMAD2Bも対角に配置され、4個のトランジスタが長方形の頂点をなす。4個のP型トランジスタPMAD1A, PMAD1B, PMAD2A, PMAD2Bのソース領域は、一層目の金属配線NDSAおよび二層目の金属配線NDSB、コンタクトCONT1およびスルーホールVIA1を介して接続される。2個のP型トランジスタPMAD1A, PMAD1Bのドレイン領域は、金属配線NDD1A, NDD1B、コンタクトCONT1およびスルーホールVIA1を介して第1の出力に接続される。2個のP型トランジスタPMAD2A, PMAD2Bのドレイン領域は、金属配線NDD2A, NDD2B、コンタクトCONT1およびスルーホールVIA1を介して第2の出力に接続される。2個のP型トランジスタPMAD1A, PMAD1Bのゲート電極は、金属配線IMOP1およびコンタクトCONT1を介して第1の入力に接続される。2個のP型トランジスタPMAD2A, PMAD2Bのゲート電極は、金属配線IPOP1およびコンタクトCONT1を介して第2の入力に接続される。

30

## 【0011】

図2に示すように、差動対をなす2個のトランジスタをそれぞれ2個のトランジスタで形成し、それらをコモンセントロイド配置することで、イオン注入の分布や、酸化膜厚さの分布などの影響を相殺して、差動対をなす2個のトランジスタの特性差を低減できる。

トランジスタのマッチングを悪化させる他の要因として、アンテナ効果が知られている

40

50

。

アンテナ効果とは、MOSトランジスタの製造時に、プラズマを使用したプロセス（製造工程）において、プラズマの電荷に起因して、MOSトランジスタのゲート酸化膜に、電気的ストレスが加わり、信頼性の問題や、MOSトランジスタの特性変動が引き起こされることを指している。ゲート酸化膜に接続された金属配線の加工時に、加工途中の金属配線が、電荷を集めて、ゲート酸化膜に損傷を与える可能性があることから、アンテナ効果と一般に呼ばれることが多い。

プラズマプロセスでの配線加工時に、アンテナ（ゲートに接続された金属配線）が集めた電荷により、MOSトランジスタのしきい値電圧V<sub>th</sub>が変動し、不均一なアンテナ効果により、差動対を構成するMOSトランジスタのマッチングが劣化することが指摘されている。10

アンテナ効果によって、MOSトランジスタが受けるストレスを軽減するために、従来より、アンテナダイオードと呼ばれるダイオード素子を保護すべきMOSトランジスタのゲートノードへ挿入する方法が知られていた。

アンテナダイオードは、プラズマプロセスでの配線加工時に電流放電経路として働き、ゲート酸化膜の受ける損傷を防ぐ効果がある。製造後の通常の動作時には、逆バイアスされているので、多少のリーク電流と、容量、面積の増加は招くが、動作にはほとんど影響しないようになっている。

#### 【0012】

MOSトランジスタのチャネル上に配線がある場合と、無い場合で、トランジスタのしきい値電圧V<sub>th</sub>が変化する事が知られている。20

MOSトランジスタのチャネルとゲート酸化膜の界面では、結晶構造が急激に変化するために、ダングリングボンドと呼ばれる未結合手が存在する。このダングリングボンドはキャリアのトラップとして働くために、水素でダングリングボンドを終端することが望ましいといわれている。チャネル直上に金属配線がある場合、製造工程の終盤で、水素でダングリングボンドを終端するよう働くアニール工程で、水素がチャネル界面に到達することを妨げる場合がある。従って、マッチングが必要なMOSトランジスタ上の配線は、ないほうが望ましいといわれている。あるいは、マッチングが必要なトランジスタ部分においては、MOSトランジスタのチャネル部分の上空の配線も含めて、同じ形状でなければならないといわれている。30

#### 【0013】

【特許文献1】特開平8-97387号公報

【特許文献2】特開平11-8319号公報

【特許文献3】特公平7-28013号公報

【特許文献4】特開2001-177357号公報

【非特許文献1】Hyungcheol Shin, Zhi-Jian Ma and Chenming Hu, "Impact of Plasma Charging Damage and Diode Protection on Scaled Thin Oxide," in Proc. IEEE International Electron Device Meeting, pp.18.3.1-18.3.4, 1993.

【非特許文献2】Donggun Park, Chenming Hu, Scott Zheng, and Nguyen Bui, "A Full-Process Damage Detection Method Using Small MOSFET and Protection Diode," IEEE ELECTRON DEVICE LETTERS, VOL. 17, NO. 12, pp.563-565, DECEMBER 1996.40

【非特許文献3】Li-Da Huang, Xiaoping Tang, Hua Xiang, D. F. Wong, and I-Min Liu, "A Polynomial Time-Optimal Diode Insertion/Routing Algorithm for Fixing Antenna Problem," IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, VOL. 23, NO. 1, pp.141-147, JANUARY 2004.

【非特許文献4】Hans Tuinhout, Marcel Pelgrom, Red Penning de Vries, Maarten Vertregt, "Effects of Metal Coverage on MOSFET Matching," in Proc. IEEE International Electron Device Meeting, pp.29.3.1-29.3.4, 1996.

#### 【発明の開示】

【発明が解決しようとする課題】

50

**【0014】**

このため、アナログ回路の集積度を高めるのは難しく、製造までのリードタイムも長いという問題があった。

**【0015】**

開示の実施形態は、短いリードタイムで製造でき、高い集積度を有するアナログ回路を実現する。

**【課題を解決するための手段】****【0016】**

実施形態に開示されたアナログ回路用セルアレイは、複数のトランジスタセルが、アレイ状に配置されたアナログ回路用セルアレイであり、回路仕様に応じて配線パターンを形成することにより、高い集積度を有する所望のアナログ回路が短いリードタイムで製造できる。各トランジスタセルは、隣接して順に配置された第1ソース領域、第1チャネル領域、共通のドレイン領域、第2チャネル領域および第2ソース領域と、第1チャネル領域および第2チャネル領域上にそれぞれ配置された第1ゲート電極および第2ゲート電極と、を備え、第1ゲート電極と第2ゲート電極は接続して使用され、第1ソース領域と第2ソース領域は接続して使用される。10

**【発明の効果】****【0017】**

実施形態のアナログ回路用セルアレイは、回路仕様に応じて配線パターンを形成するだけで高精度のアナログ回路を容易に製造できるので、製造のリードタイムを大幅に短縮できる。20

**【発明を実施するための最良の形態】****【0018】**

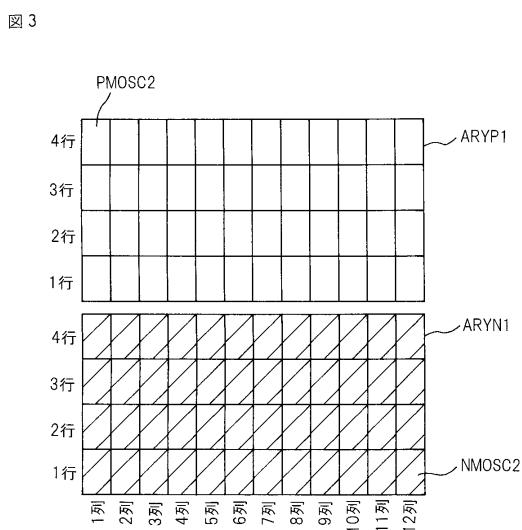

図3は、実施形態のアナログ回路用セルアレイの基本構成を示す図である。図3に示すように、実施形態のアナログ回路用セルアレイは、PMOS基本セルPMOS C2を4行12列で配列したPMOSアレイARYP1と、NMOS基本セルNMOS C2を4行12列で配列したNMOSアレイARYN1と、を有する。このアナログ回路用セルアレイを有する半導体装置は、このほかに、入力信号端子、出力信号端子、電源端子などを有し、さらにアナログ回路用セルアレイを動作させるために必要な回路部分なども有するが、ここでは図示を省略している。また、ゲートアレイなどのデジタル回路部分に、図3のアナログ回路用セルアレイを搭載して、アナログ/デジタル回路混載半導体装置を実現することも可能である。これら48個のPMOS基本セルPMOS C2および48個のNMOS基本セルNMOS C2に配線パターンを形成して所望のアナログ回路を実現する。30

**【0019】**

図3に示すように、PMOSアレイARYP1およびNMOSアレイARYN1は、4行の基本セル列を有する。差動対などをなすトランジスタ対など特性差が小さいことを要求されるトランジスタは、2行目および3行目の基本セルで実現することが望ましい。すなわち、高精度を要求されるトランジスタなどは、PMOSアレイARYP1およびNMOSアレイARYN1のエッジに隣接しない基本セルを使用して形成する。また、後述するアンテナダイオードなど、特性誤差の許容範囲の大きな素子は、1行目および4行目の基本セルで実現しても、精度低下の問題は生じない。40

**【0020】**

高精度のトランジスタなどを、PMOSアレイARYP1およびNMOSアレイARYN1のエッジに隣接しない基本セルで形成し、コモンセントロイド配置するには、PMOSアレイARYP1およびNMOSアレイARYN1は4行、4列の構成が最小となる。しかし、行数および列数はこれらより大きくてよく、例えば、6行6列のNMOSアレイと6行6列のPMOSアレイを用いることも可能である。また、単純なアナログ回路は少ない基本セルで実現可能であるが、複雑なアナログ回路を実現するには多数の基本セルが必要である。従って、アレイ構成の異なる複数種類のアナログ回路用セルアレイを用意しておき、実現するアナログ回路に応じて適宜選択可能にすることが望ましい。50

## 【0021】

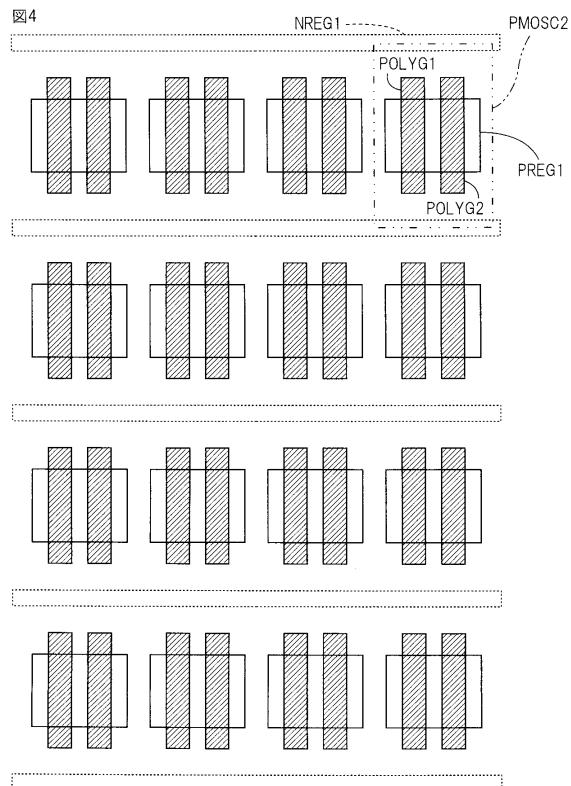

図4は、図3のPMOSアレイARYP1における $4 \times 4$ のPMOS基本セルPMOS C2の部分を示す図である。図4に示すように、1個のPMOS C2は、P型拡散領域PREG1と、2個のポリシリコンゲート電極POLYG1、POLYG2と、を有する。以下、PREG1は実線の矩形パターンとして示し、POLYGはクロス斜線のハッティング图形として示した。また、特に断らない限り、同じ層のパターンは同じ方法で図示するものとし、説明の重複を避けるものとする。2個のポリシリコンゲート電極POLYG1、POLYG2の下の部分のP型拡散領域PREG1が、第1および第2チャネル領域である。2個のポリシリコンゲート電極POLYG1、POLYG2の間のP型拡散領域PREG1の部分が、共通ドレイン領域である。2個のポリシリコンゲート電極POLYG1、POLYG2の外側のP型拡散領域PREG1の部分が、第1および第2ソース領域である。ここでは、1個のPMOS C2は二点鎖線で示す範囲を有し、このようなPMOS C2が4行×12列で配列され、各行の間にはN型拡散領域NREG1が連続して設けられる。第1および第2チャネル領域の幅は、適切なチャネル長、すなわちゲート長に設定され、ゲート長は例えば $2 \mu m$ である。P型拡散領域PREG1の幅は、チャネル幅、すなわちゲート幅であり、ゲート幅は例えば $10 \mu m$ に設定される。ゲート長およびゲート幅は、アナログ回路の仕様およびレイアウトの容易さなどから決定される。なお、以下の説明では、POLYG1およびPOLYG2をまとめてPOLYGと称する場合がある。

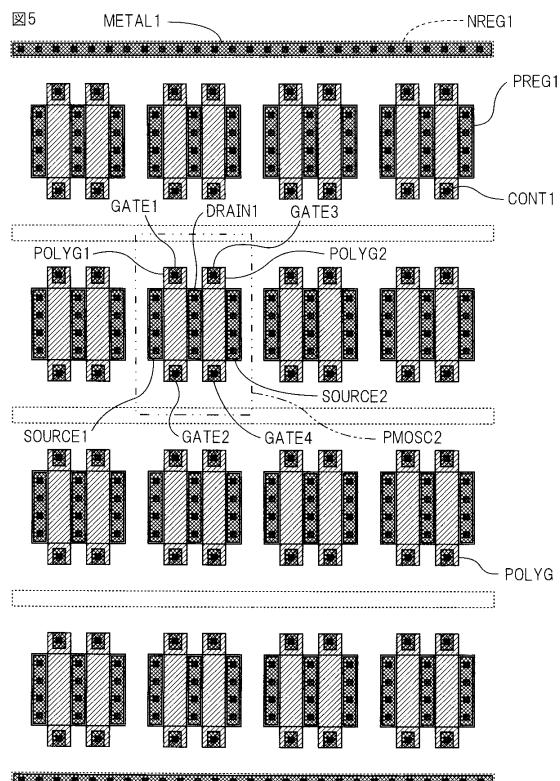

## 【0022】

図5は、図4に示したPMOS基本セルPMOS C2の部分に、一層目の金属配線METAL1を形成した状態を示す。後述するように、実際にアナログ回路を形成する場合には、各基本セルのポリシリコンゲート電極POLYG、ドレイン領域およびソース領域は、ほかの基本セルの電極、電源電極、入力端子および出力端子などに、一層目の金属配線METAL1を介して接続される。しかし、ここでは説明を簡単にするために、電極間の接続が行われない状態を示している。

## 【0023】

図5では、METAL1はクロス斜線のハッティング图形として示、CONT1は正方形とその頂点を対角線で結んだ图形として示している。

## 【0024】

図5に示すように、PMOS基本セルPMOS C2は、2個のポリシリコンゲート電極POLYG1、POLYG2のP型拡散領域PREG1外に伸びた上下部分に設けられた4個のコンタクトGATE1, GATE2, GATE3, GATE4と、中央の共通ドレイン領域の上に設けられたドレイン電極DRAIN1と、両側のソース領域の上に設けられたソース電極SOURCE1, SOURCE2と、を有する。さらに、1行目の基本セルの上側および4行目の基本セルの下側のN型拡散領域NREG1の上には一層目の金属配線METAL1が設けられ、NREG1に接続される。2個のポリシリコンゲート電極POLYG1とPOLYG2および2個のソース電極SOURCE1とSOURCE2は、ドレイン電極DRAIN1に対して対称に配置される。これにより、基本セルPMOS C2には、2個の同じサイズのPMOSトランジスタが形成される。4個のコンタクトGATE1, GATE2, GATE3, GATE4は、2個のPMOSトランジスタのゲートとMETAL1との接続のためのコンタクト部分である。DRAIN1は、2個のPMOSトランジスタの共通ドレイン電極であり、SOURCE1, SOURCE2は2個のPMOSトランジスタのソース電極である。

## 【0025】

図4および図5では、PMOS基本セルPMOS C2がレイアウトの基本単位であり、基本セルはP型トランジスタのバックゲート電極となるN型拡散領域NREG1を、上下の境界部分に有する。

## 【0026】

後述するように、使用される基本セルの2個のゲート電極は共通に接続され、2個のソ

ース電極は共通に接続される。これにより、基本セル単位で、電流の向きが反対となる2つのトランジスタの並列接続が実現される。

#### 【0027】

微細化のすすんだMOSトランジスタの製造工程では、斜め方向からイオンを注入するような工程が採用されることがある。このような場合、例えば、ポリシリコンゲート電極POLYGの右側と左側で、ソース、ドレインの拡散層の高濃度領域とゲート電極のオーバーラップ幅が異なることが起こりえる。これは、POLYGの右側と左側で、実効の寄生抵抗が異なる状況を生じさせる。そのため、POLYGの右側拡散層をソース、左側拡散層をドレインとする場合と、POLYGの左側拡散層をソース、右側拡散層をドレインとする場合で、MOSトランジスタの特性が異なる状況を生じる。このような製造工程の性質から、マッチングの必要なトランジスタ同士では、電流の流れる向きまで含めて、素子の形状、素子の使用法をそろえる必要がある。以下、しきい値電圧 $V_{th}$ やドレイン電流などの素子特性を一致させることをマッチングと称する。10

#### 【0028】

ところが、レイアウト時の電流の向きは、回路結線を確認するLVSと呼ばれるソフトウェアやDRCと呼ばれるソフトウェアでは、確認することができない。なぜなら、MOSトランジスタの電流の流れる向きを知るためにには、回路の動作を理解し、マッチングが必要な素子を認識するという複雑な回路の全体の理解が必要となるためである。このため、従来は、電流の向きまで含めた素子の配置の同一性の確認は人手に頼るのが一般的であった。20

#### 【0029】

そのため、単一のMOSトランジスタのソース、ドレインを入れ替えることで、特性が変動し、例えば、ソース、ドレインの実効寄生抵抗が異なるような場合には、電流の流れる方向まで考慮して、対称性を確保することが望ましい。

#### 【0030】

図5のレイアウトでは、PMOS基本セルPMOS C2を、ドレインを共通とする2つのPMOSトランジスタとして、ソースからドレインに流れる電流の向きが異なる2つのトランジスタが基本セル内に含まれるようにできる。これにより、基本セルを単位として、基本セルと基本セルを、例えば、コモンセントロイド配置とすると、基本セル内部での電流の向きを考慮しなくても必然的に、電流の向きが異なるトランジスタの電流の合計電流を加算して、電流の向きが異なるMOSトランジスタの不一致を相殺できるようになる効果が得られる。30

#### 【0031】

また、PMOS基本セルPMOS C2は、PMOSのバックゲート電極となるN型拡散領域NREG1を含み、基本セル構造に基板あるいはWELL給電のための拡散領域を含むよう構成することで、N型WELLの給電部分を別途用意する必要がなくなる。

#### 【0032】

基本単位を電流の向きが反対となる2つのトランジスタの並列接続としておくことで、図5の基本セルの構造を守っている限り、電流の向きを詳細に考慮したり、検証する必要がなくなる利点が得られる。つまり、電流の向きが異なることによる特性のずれを見落とす可能性をゼロとできる。40

#### 【0033】

アナログ回路で、オフセット電圧をできるだけ小さくするためには、使用するトランジスタの特性をできるだけ一致させておかなければならない。レジストの露光の不均一性やエッティング時の不均一性の影響を避けるために、同じ形状のMOSトランジスタを使用し、精度を必要とする素子の周辺にダミー素子を配置することが、従来より一般的だった。ところが、最近の微細化のすすんだMOSトランジスタにおいては、意図的にチャネルに応力を加えることにより電流駆動能力の向上を図る場合があることからも分かるように、素子分離領域の応力の違いによる移動度の変化が無視できない。トレンチ型の分離構造が採用されることが多いので、この分離領域の形状、ソース、ドレインの電極部分の形状、50

分離領域との比率など、MOSトランジスタのチャネル部分の応力に影響する要素も、すべて同じ構造となるように配慮、配置する必要がある。

#### 【0034】

同一形状のPMOSトランジスタを繰り返しながらべた構造においても、N型のWELL給電部分は、必ずどこかに必要となる。さらに、N型のWELL給電部分を、例えば、PMOSトランジスタを繰り返し並べた構造の一番外側に配置するような方法を採用すると、WELL給電部分自体が分離領域の形状の同一性を損なうことに、発明者らは、気づいた。つまり、WELL給電部分も含めて、同一の形状を繰り返すほうが、分離領域まで含めたトランジスタ構造の対称性、同一性が確保できるので望ましい。そのため、このような対称性を実現するための、基本トランジスタセル構造、配線構造を、工夫する必要がある。10

#### 【0035】

図5のレイアウトは、このWELL給電部分も含めて、同一の形状を繰り返し、かつ素子への配線が可能な構造となっている。図5はN型のWELLへの給電部分NREG1も含めて、PMOS基本セルPMOSC2が繰り返し構造となっていることを示している。2点鎖線で示した基本セルPMOSC2が縦、横に繰り返され、上下のセルで、NREG1が共有される構造となっている。PMOS基本セルPMOSC2の境界を表す2点鎖線がN型WELLの給電領域NREG1の中央部分にあるのは、このことを表わしている。このようなセル構造(基本構造)とすることで、分離領域まで含めたトランジスタ構造の対称性、同一性が保たれ、チャネル部分の応力の違いを極力小さくする効果が得られる。20

これにより移動度の一致の程度が向上する。

#### 【0036】

さらに、4個のコンタクトGATE1, GATE2, GATE3, GATE4をあらかじめ用意しておき、各コンタクトを独立してMETAL1に接続できるようにすることでの方向からでもゲートに給電することが可能となり、またゲート配線部分の規則性も向上する効果が得られる。

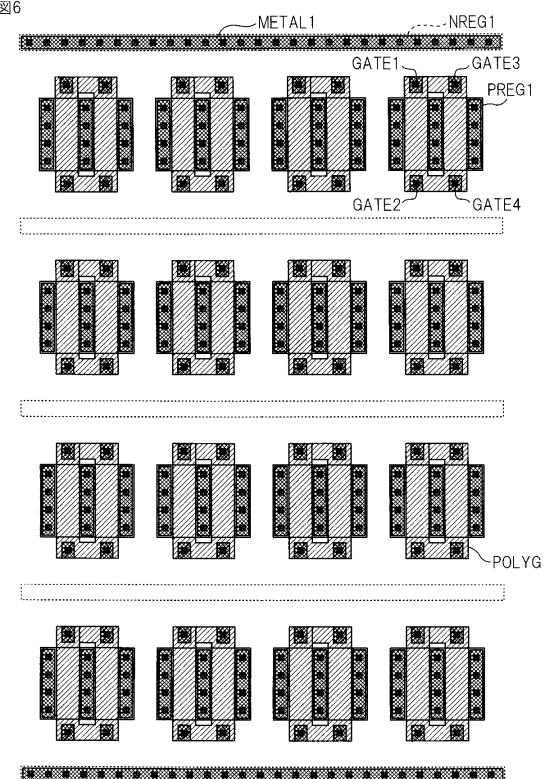

#### 【0037】

上記のように、使用される基本セルの2個のゲート電極は共通に接続して使用される。そこで、図4に示した2個の各基本セルのポリシリコンゲート電極POLYGを、接続された形で形成してもよい。図6は、接続された形で形成した基本セルのポリシリコンゲート電極POLYGに対して一層目の金属配線METAL1を形成した状態を示す。30

#### 【0038】

図5に示した2つのトランジスタのゲートが独立した構造では、例えば、パワーダウン用の素子などで、電流の流れる方向を気にしなくてよい場合には、ソース電極とドレイン電極を入れ替えて、2つの独立なトランジスタとして使用できる可能性を残している。しかし、電流の異なる2つのトランジスタを基本セル内で並列接続するという基本的な考え方からは、図6のように、基本セル内部で、2個のゲートを直接POLYG配線で接続してしまってもかまわない。配線もできるだけ対称に配置しておくことが望ましいこと、配線だけでの回路変更の可能性を考慮すると、POLYGとMETAL1とのコンタクト部分は4箇所となるが、この4つのゲートとMETAL1接続部分に配線するだけで、基本セル内部のゲートに電位を供給、接続できるので、信号配線の引き出しの自由度が大きくなる効果が得られる。40

#### 【0039】

次に、実施形態のアナログ回路用セルアレイにおける配線について説明する。

#### 【0040】

MOSトランジスタのチャネル上に配線がある場合と、ない場合で、トランジスタのしきい値電圧V<sub>th</sub>が変化することが知られている。MOSトランジスタのチャネルとゲート酸化膜の界面では、結晶構造が急激に変化するために、ダングリングボンドと呼ばれる未結合手が存在する。このダングリングボンドはキャリアのトラップとして働くために、水素でダングリングボンドを終端することが望ましいといわれている。チャネル直上に金50

属配線がある場合、製造工程の終盤で、水素でダングリングボンドを終端するよう働くアニール工程で、水素がチャネル界面に到達することを妨げる場合がある。従って、マッチングが必要なMOSトランジスタ上の配線は、ないほうが望ましいといわれている。あるいは、マッチングが必要なトランジスタ部分においては、MOSトランジスタのチャネル部分の上部の配線も含めて、同じ形状でなければならないといわれている。

#### 【0041】

トランジスタのしきい値電圧  $V_{th}$  の変化を避けるために、図5のレイアウトにおいて、P型拡散領域 PREG1と2個のポリシリコンゲート POLYGが重なった領域、すなわちトランジスタの反転層が形成されるチャネル上部には配線を置かないことが必要である。

10

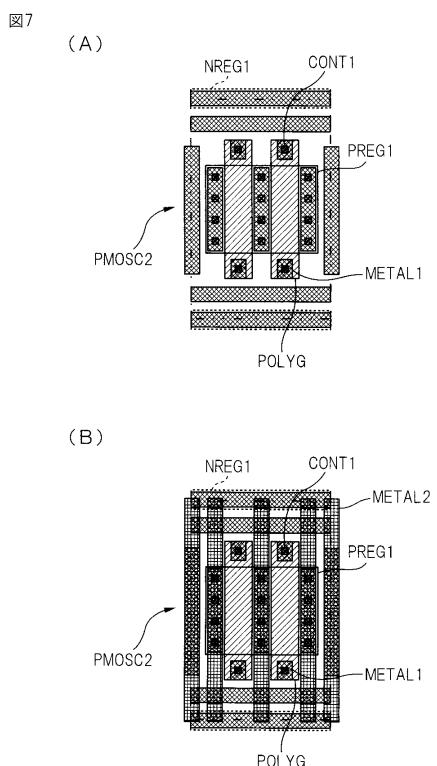

#### 【0042】

図7は、1個のPMOS基本セルPMOSCELL2における配線例を示す図であり、(A)は一層目の金属配線METAL1を配線した状態を、(B)は二層目の金属配線METAL2を配線した状態を示す。図7の(A)および(B)に示すように、PMOS基本セルPMOSCELL2は、横方向(電流経路方向)の一層目金属配線METAL1の配線チャネルを少なくとも3つ備える。基本セル構造内の2つの横方向METAL1配線チャネルと、隣接基本セルと共有する横方向METAL1配線チャネルを1つ備える(共有なので $0.5 + 0.5 = 1$ )。場合によっては、基本セル構造内の横方向METAL1配線チャネルは5つであってもかまわない。いずれにしろ、PMOSトランジスタの電流チャネル上には配線を配置しない。

20

#### 【0043】

また、PMOS基本セルPMOSCELL2は、縦方向(ゲート幅方向)の二層目金属配線METAL2の配線チャネルを少なくとも4つ備える。基本セル構造内に3つの縦方向METAL2配線チャネルと、隣接基本セルと共有する縦方向METAL2配線チャネルを1つ備える。基本セル構造内の3つの縦方向METAL2配線チャネルは、基本セルPMOSCELL2のドレイン電極およびソース電極(METAL1)の上部とする。場合によっては、基本セル構造内のMETAL2配線チャネルは6つであってもかまわない。また、隣接基本セルと共有する縦方向METAL2配線チャネルの下部は、METAL1配線の縦方向配線にも使用できる。

30

#### 【0044】

上記のように、横方向(電流経路方向)の一層目金属配線METAL1の基本セル構造内の2つの横方向METAL1配線チャネルと、隣接基本セルと共有する横方向METAL1配線チャネルを1つ備えることで、WELL給電のための配線のほかに、2つの横方向信号配線を用意できる。

#### 【0045】

また、基本セルの構造を、ドレインを共通、ソースを独立な2つの電極としたので、2つのソース、ドレイン、ゲート、WELLの5つのノードをMETAL1で配線しなければならない。これを可能とするために、ゲートとPOLYGのコンタクト部分のMETAL1とは別に配線チャネルが必要となる。セル構造の対称性を保つためには、隣接セルと共有するMETAL1配線チャネルのほかに偶数本のMETAL1配線チャネルを用意することが必要である。

40

#### 【0046】

さらに、METAL1配線チャネルをMOSトランジスタの電流が流れる電流チャネル(POLYGとPREG1が重なる部分)を避けて、用意することで、ゲートチャネルの上部部分に金属配線を配置しない構造が可能となり、金属配線による $V_{th}$ の変動を避けることが可能となり、相対精度が向上する。

#### 【0047】

同様に、基本セルPMOSCELL2のMETAL1で構成されるドレイン電極、ソース電極の上部とし、縦方向(ゲート幅方向)の二層目金属配線METAL2の配線チャネルを、基本セル構造内に3つの縦方向METAL2配線チャネルと、隣接基本セルと共有する縦

50

方向METAL2配線チャネルを1つとすることで、4つの縦方向信号配線可能な領域を確保できる。

#### 【0048】

METAL2配線チャネルをMOSトランジスタの電流が流れる電流チャネル（POLY GとPREG1が重なる部分）を避けて、用意することで、電流チャネルの上部部分に金属配線を配置しない構造が可能となり、金属配線によるVthの変動を避けることが可能となり、相対精度が向上する。そして、METAL2配線チャネルをMOSトランジスタの電流が流れる電流チャネルを避けるために、METAL1で構成されるドレイン電極、ソース電極の上部を、METAL2の配線チャネルとし、隣接セルと共有するチャネルを設けることで、セル構造の対称性を保つことができる。

10

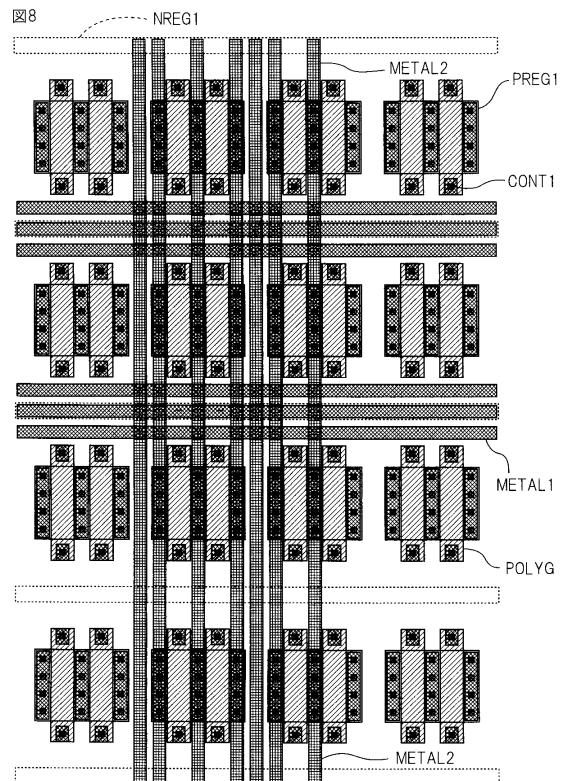

#### 【0049】

図8は、実施形態のレイアウトにおける配線チャネルの考え方を説明するための図であり、縦方向配線および横方向配線を回路接続とは関係なく可能な配線として示している。

#### 【0050】

PMOSトランジスタの電流チャネル部分の上部を配線禁止とするので、METAL2配線は、縦方向に伸びる。PMOS基本セルPMOSC2同士で共有するセル間の縦方向配線、ソース上、ドレイン上の配線の4本の配線が、1列あたりに可能な縦方向METAL2配線となる。横方向METAL1配線は、NREG1上の配線に加えて、NREG1とゲートコントラクト部分との隙間の横方向配線が可能なMETAL1の横方向配線となる。つまり、基本セル1行あたり、3本の横方向METAL1配線が可能な構造となっている。NREG1上の配線チャネルは、上下の隣接セルと共有されている。

20

#### 【0051】

NREG1配線は原則としてVDD配線とすることがNREG1へのVDD給電の観点から望ましいが、必要であれば、特定の部分で、VDDではなく信号配線として使用する。NREG1のすべての領域でVDDを必ずMETAL1から給電しなければならないわけではないことを利用すれば、NREG1上有る部分のMETAL1配線を信号配線として使用できる。さらに、P型基本セルの場合、NREG1上の配線は、原則としてVDD配線となるが、必要なときには、局所的に信号配線として使用可能である。基本セルの左右の端に、縦方向のMETAL1配線が図示されているのは、縦方向METAL2配線の直下をMETAL1配線領域としても使用できることを示している。あるいは、このセルとセルの左右の境界をMETAL1の縦方向配線として使用できるように、セル構造を設計している。このように、セル境界部分をMETAL1配線が通過可能として縦方向に信号を接続可能なセル構造を採用しておくことで、後述するようなアンテナダイオードの接続が可能となる効果が得られる。

30

#### 【0052】

以上、PMOSアレイARYP1における $4 \times 4$ のPMOS基本セルPMOSC2の部分の構成を説明したが、NMOSアレイARYN1における $4 \times 4$ のNMOS基本セルNMOSC2の部分の構成は、拡散層の極性が逆であることを除けば同様であり、図示および説明は省略する。

40

#### 【0053】

次に、上記のような実施形態のアナログ回路用セルアレイを利用してシリーズレギュレータのバンドギャップ回路を形成する実施形態を説明する。

#### 【0054】

マイクロコントローラ（MCU）は、電子機器のプログラマブルな部品として使用される。半導体加工技術の進歩、つまり微細化の進展とともに、MCUの適用される領域はますます拡大している。微細化の進展とともに、MCUの処理能力の向上が続いていることと、機能あたりのコストの低下が継続していることが背景として挙げられる。微細化の進展とともに、デジタル回路を構成する微細MOSトランジスタの素子耐圧は下がっている。例えば、ゲート長0.18μmのCMOS回路では、電源電圧は1.8V程度が一般的である。一方、自動車用途などでは、MCUのインターフェース電圧として伝統的な5Vが

50

求められることも多い。MCU外部から供給する電源電圧、インターフェース電圧は例えば、5Vとすることが求められ、一方、内部回路の素子耐圧から決まるデジタル回路部分の電源電圧は、例えば、1.8Vとすべき場合がある、このような場合には、外部部品を削減するために、MCUにシリーズレギュレータを搭載し、外部から供給した5V電源から1.8V電源を発生し、内部のデジタル回路に供給するような構成が一般的となっている。

#### 【0055】

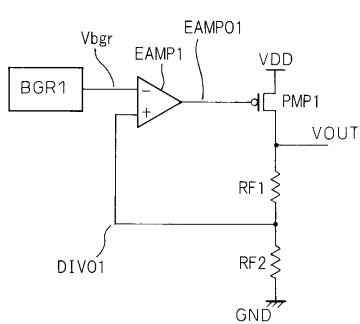

図9は、シリーズレギュレータ回路の一例を示す図であり、外部から供給した5V電源から1.8V電源を発生するシリーズレギュレータの一般的な構成を示す。シリーズレギュレータは、基準電圧を発生するバンドギャップ回路BGR1と、誤差アンプEAMP1と、出力トランジスタPMP1と、レギュレータ出力電位を分圧する抵抗分圧回路を有する。抵抗分圧回路は、レギュレータ出力電位を分圧する抵抗RF1と抵抗RF2を有する。図9において、V<sub>bgr</sub>はバンドギャップ回路BGR1が出力する基準電圧を、EAMP1は誤差アンプEAMP1の出力を、V<sub>OUT</sub>はレギュレータ出力を、DIVO1は抵抗分圧回路の出力を、VDDは例えば外部から供給する5V電源を、GNDはGND電位(0V)を、示している。以下の説明では、Rで始まる素子名は抵抗を、PMで始まる素子名はPMOSトランジスタを、表わしているものとする。

#### 【0056】

図9のレギュレータ回路では、バンドギャップ回路BGR1が、温度、電源電圧に依存しない基準電圧であるバンドギャップ電圧V<sub>bgr</sub>(1.2V)を発生する。RF1とRF2の抵抗分圧回路は、レギュレータ出力電位V<sub>OUT</sub>を、例えば、2/3に分圧した分圧出力を発生する。誤差アンプEAMP1により、出力トランジスタPMP1のゲートを制御し、抵抗分圧回路出力DIVO1と、基準電圧(バンドギャップ電圧)V<sub>bgr</sub>(1.2V)が一致するように負帰還制御する。

#### 【0057】

レギュレータ出力×2/3の電位DIVO1と、バンドギャップ電圧の電位V<sub>bgr</sub>(1.2V)が一致するので、例えば、レギュレータ出力電位V<sub>OUT</sub>は、温度、電源電圧、負荷電流に(理想的には)依存せず、1.8Vの一定電位に制御される。

#### 【0058】

バンドギャップ電圧は、理想的には、1.2V程度の電位となり、温度、電源電圧に依存しないが、実際には、CMOSバンドギャップ回路を構成するMOSトランジスタの誤差などに起因して、回路毎にその出力電圧は変化する。典型的なCMOSバンドギャップ回路では、例えば、1.2V±8%程度の出力電位の絶対値の幅がある。

#### 【0059】

基準電圧V<sub>bgr</sub>が、例えば、1.2V±8%とすると、レギュレータ出力電位V<sub>OUT</sub>も、上の例では(誤差アンプのオフセット電圧を無視すると)、1.2V±8%となり、変動幅を絶対値で表現すると、1.2V±140mVとなる。つまり、レギュレータ出力電位V<sub>OUT</sub>は1.8Vを中心として、1.66Vから1.94Vに分布する。

#### 【0060】

レギュレータの出力電圧V<sub>OUT</sub>は、ゲート長0.18μmのCMOS回路で構成されたロジック回路の電源電圧となるので、サンプルによっては、MCUのロジック回路の電源電圧が1.66Vとなり、別のサンプルでは、MCUのロジック回路の電源電圧が1.94Vとなることを意味している。

#### 【0061】

MCUのロジック回路の電源電圧が低い場合には、ロジック回路を構成する基本回路の遅延時間が大きくなるので、動作周波数の面から不利になる。一方、MCUのロジック回路の電源電圧の上限は、素子の信頼性の観点(例えばTDDDB(Time-Dependent Dielectric Breakdown、酸化膜経時破壊)、ホットキャリア劣化などの観点)から、例えば2.0V以下としたいなどの制限がある。

#### 【0062】

10

20

30

40

50

レギュレータの出力電位の誤差が大きいと、信頼性から決まる電源電圧の上限を満足しながら、動作速度の要請から決まるレギュレータの出力する電源電圧の下限を同時に満足することが難しくなる。

#### 【0063】

例えば、レギュレータ回路においては、このような背景から、バンドギャップ回路の出力電圧精度をできるだけ改善することが要求されている。

#### 【0064】

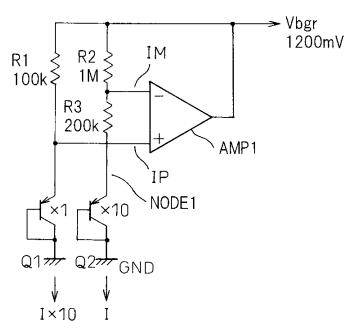

図10は、バンドギャップ回路の一例を示している。アナログ集積回路では、温度、電源電圧に依存しない基準電圧が必要な場合、バンドギャップ回路と呼ばれる基準電圧回路が広く用いられている。デジタル回路との混載が容易なことから重要なCMOSアナログ集積回路においても、バンドギャップ回路は、安定な基準電圧回路として広く用いられてきた。10

#### 【0065】

バンドギャップ回路では、順バイアスされたpn接合の電位と、絶対温度(T)に比例(Proportional To Absolute Temperatureと一般に称されている)する電圧を加算することで、温度に依存しない基準電圧を得る各種の回路が考案され実用に供されてきた。順バイアスされたpn接合の電位は(pn接合の電位を1次式で近似すれば、あるいは、1次式で近似できる範囲内では)、CTAT(Complementary To Absolute Temperature: 絶対温度に対して負の線形依存性)であることが知られている。この順バイアスされたpn接合の電位に(適切な)PTAT電圧を加算することで、ほぼ温度に依存しない基準電圧が得られることが知られている。20

#### 【0066】

このようなバンドギャップ回路の典型的な回路例を図10に示している。図10において、Q1、Q2はpnpnバイポーラトランジスタ(以下pnpnBJTと略す)を、R1、R2、R3は抵抗(その抵抗値もR1、R2、R3で示すものとする。)を、AMP1はオペアンプ回路を、GNDはGND端子を、V<sub>bgr</sub>は出力基準電位を、NODE1、IM、IPは内部のノードを、示している。抵抗に添えられた値は、抵抗値の例を、BJTに添えられた数字は、BJTの相対的な面積の比を示す。

#### 【0067】

図10のバンドギャップ回路の動作を簡単に説明する。BJTのベース、エミッタ間電圧あるいは、pn接合の順方向電圧をV<sub>be</sub>で表わすと、その、pn接合の順方向電圧と絶対温度Tの関係は、概略、式(1)となることが知られている。30

#### 【0068】

$$V_{be} = V_{eg} - aT \quad (1)$$

(V<sub>be</sub>: pn接合の順方向電圧、V<sub>eg</sub>: シリコンのバンドギャップ電圧、約1.2V、a: V<sub>be</sub>の温度依存性、約2mV/、T: 絶対温度)(aの値はバイアス電流により異なるが、実用領域で、概略2mV/程度となることが、知られている。)

また、BJTのエミッタ電流I<sub>E</sub>と電圧V<sub>be</sub>の関係は、概略、式(2)となることが知られている。

#### 【0069】

$$I_E = I_0 e \times p (q V_{be} / kT) \quad (2)$$

(I<sub>E</sub>: BJTのエミッタ電流あるいはダイオードの電流、I<sub>0</sub>: 定数(面積に比例)、q: 電子の電荷、k: ボルツマン定数)

オペアンプAMP1による負帰還により、AMP1の電圧利得が十分大きい場合には、AMP1の入力IMとIPの電位がほぼ等しくなって回路が安定する。このとき、図10に示すように、R1とR2の抵抗の値を、例えば1:10(100k:1M)に設計しておくと、Q1とQ2に流れる電流の大きさは、10:1となり、Q1に流れる電流を10Iで、Q2に流れる電流をIで表わす。(Q1、Q2の下に添えられたI×10とIは、この電流の相対関係を示す。)

仮に、Q2のエミッタ面積は、Q1のエミッタ面積の10倍とし(図10のQ1、Q250

に添えられた  $\times 1$ 、 $\times 10$  は、このエミッタ面積の相対関係を示す。）、Q1のベース、エミッタ間電圧を  $V_{be1}$  で、Q2のベース、エミッタ間電圧を  $V_{be2}$  で表わすと、式(2)より、式(3)と式(4)の関係があることがわかる。

#### 【0070】

$$10 \times I = I_0 \exp(qV_{be1}/kT) \quad (3)$$

$$I = 10 \times I_0 \exp(qV_{be2}/kT) \quad (4)$$

両辺それぞれを割り算し、 $V_{be1} - V_{be2} = V_{be}$  と表わすと、式(5)、式(6)が得られる。

#### 【0071】

$$100 = \exp(qV_{be1}/kT - qV_{be2}/kT) \quad (5)$$

$$V_{be} = (kT/q) \ln(100) \quad (6)$$

つまり、Q1とQ2のベース、エミッタ間電圧の差、 $V_{be}$  は、Q1とQ2の電流密度比100の対数( $\ln(100)$ )と熱電圧( $kT/q$ )で表わされる。この  $V_{be}$  が抵抗R3の両端の電位差に等しいので、抵抗R2、R3には、 $V_{be}/R3$  の電流が流れる。

#### 【0072】

従って、抵抗R2の両端の電位差  $V_{R2}$  は、式(7)で表わされる。

#### 【0073】

$$V_{R2} = V_{be} R2 / R3 \quad (7)$$

IPの電位と、IMの電位は、 $V_{be1}$  で等しいので、基準電圧  $V_{bgr}$  の電位は式(8)で表わされる。

#### 【0074】

$$V_{bgr} = V_{be1} + V_{be} R2 / R3 \quad (8)$$

p-n接合の順方向電圧  $V_{be1}$  は温度の上昇とともに減少する負の温度依存性を持つ(式(1)： $V_{be} = V_{eg} - aT$ )、一方  $V_{be}$  は式(6)に示されるように温度に比例して大きくなる。適切に定数を選ぶことで、基準電圧  $V_{bgr}$  の値が温度に依存しないように設計できる。そのときの  $V_{bgr}$  の値は、シリコンのバンドギャップ電圧に相当する約1.2V(1200mV)となる。

#### 【0075】

このように、図10の回路では、回路定数を適切に選ぶことで、温度に依存しないバンドギャップ電圧を比較的簡単な回路で発生することが可能となっていた。

#### 【0076】

図10のバンドギャップ回路では、上で説明したように、比較的単純な回路で、基準電圧を発生できる利点があったが、一方、次に説明するような欠点もあった。

#### 【0077】

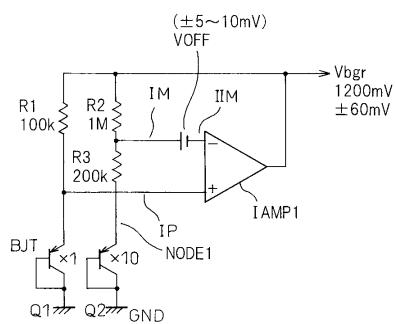

図11に、図10のバンドギャップ回路の問題点を示す。

#### 【0078】

図11において、Q1、Q2はp-n-pバイポーラトランジスタ(以下p-n-pBJTと略す)を、R1、R2、R3は抵抗(その抵抗値もR1、R2、R3で示すものとする。)を、IAMP1は理想オペアンプ回路を、GNDはGND端子を、 $V_{bgr}$  は出力基準電位を、NODE1、IM、IPは内部のノードを、VOFFはオペアンプのオフセット電圧を表わす等価電圧源を、IIMは理想オペアンプIAMP1の-側の入力端子を、示している。抵抗に添えられた値は、抵抗値の例を、BJTに添えられた数字は、BJTの相対的な面積の比を示す。

#### 【0079】

図10のバンドギャップ回路の問題点を説明するために、図10のAMP1を、図11では、理想オペアンプIAMP1と、等価オフセット電圧VOFFで示した。基本的な動作は図10の説明で述べたので、図11では、オフセット電圧VOFFが出力  $V_{bgr}$  の電圧にどう影響するかを説明する。

#### 【0080】

10

20

30

40

50

C M O S回路で、バンドギャップ回路、とくに図10のような回路を構成する場合、オペアンプのオフセット電圧の影響は避けることができない。理想的には、図10のAMP1の入力電位 $I_M$ と $I_P$ が等しい場合、AMP1の出力電位は、(例えば)電源電圧の1/2程度の電位となる。しかし実際の集積回路では、アンプを構成する素子の特性が完全に一致することはないので、AMP1の出力電位が、(例えば)電源電圧の1/2程度の電位となる電位は、それぞれのアンプによって異なり、そのときの入力電位の差電位はオフセット電圧と呼ばれる。典型的なオフセット電圧は±10mV程度であることが知られている。

#### 【0081】

このような、現実のアンプの特性がバンドギャップ回路の出力電位に、どう影響するかを説明するために、図11では、図10のAMP1を、理想オペアンプIA M P1と、等価オフセット電圧 $V_{O F F}$ で示している。理想オペアンプIA M P1のオフセット電圧は0mVとする。

#### 【0082】

図10の理想的な回路では、 $I_M$ と $I_P$ の電位が一致した。一方、現実の回路では、仮想的な理想オペアンプ入力 $I_I M$ と $I_P$ の電位が一致するので、 $I_M$ と、 $I_P$ の電位は、オフセット電圧 $V_{O F F}$ に相当する電位に相当する値分ずれる。簡単のために、理想状態で抵抗 $R_3$ の両端に加わる電位差を式(9)で表わす。

#### 【0083】

$$V_{R3} = V_{be} \quad (9)$$

20

図11の抵抗 $R_3$ に加わる電位差 $V_{R3}'$ は概略式(9')で表わされる。( $V_{O F F}$ はオフセット電圧 $V_{O F F}$ の値を示すものとする。)

$$V_{R3}' = V_{be} + V_{O F F} \quad (9')$$

抵抗 $R_2$ の両端の電位差 $V_{R2}'$ は、式(10)で表される。

#### 【0084】

$$V_{R2}' = (V_{be} + V_{O F F}) R_2 / R_3 \quad (10)$$

したがって、 $V_{bg r}$ は式(11)で表わされる。

#### 【0085】

$$V_{bg r} = V_{be1} + V_{O F F} + (V_{be} + V_{O F F}) R_2 / R_3 \quad (11)$$

30

図3のように $R_2 / R_3 = 5$ とすると、 $V_{bg r}$ の値は、理想値にオフセット電圧を(約)6倍した値を加えた値となる。

#### 【0086】

図10、図11の回路では、できるだけオペアンプのオフセット電圧の影響を小さくするために、Q1に対してQ2の面積を10倍に、さらに、Q1に流れる電流をQ2に流れる電流の10倍とした例を示している。これにより例えばR3の両端の電位差は、式(12)で表される。

#### 【0087】

$$V_{be} = (kT/q) \ln(100) = 26mV \times 4.6 = 120mV \quad (12)$$

式(12)に示されるように、電位差は120mVと比較的大きな値とできる。これにより $V_{O F F}$ の影響を比較的小さく抑えることが可能だが、この場合でも、約600mVの $V_{be}$ にPTAT電圧を加算して1200mVのバンドギャップ電圧を得るために、式(12)の値を5倍して、 $V_{be1}$ に加算しなければならない。このため、オフセット電圧 $V_{O F F}$ がある場合には(1+5)=6倍程度、 $V_{O F F}$ の影響が増幅されて、 $V_{bg r}$ に影響する。(図11中に示したBGR出力の式は、このオフセット電圧の影響を示している。)

40

つまり、図10の回路は、比較的単純な回路構成で、バンドギャップ回路を構成できる利点をもってはいるが、オペアンプ回路のオフセット電圧により、達成される基準電圧 $V_{bg r}$ の精度が制限されるという限界を持っている。

#### 【0088】

以上、図10の回路を例に、バンドギャップ回路の出力電圧の精度を改善するためには

50

、 B G R 回路に使用するオペアンプのオフセット電圧を極力小さくすることが必要なことを説明した。前述のように、従来より、オフセット電圧ができるだけ小さくするためのレイアウトの工夫としてコモンセントロイドが知られている。

#### 【 0 0 8 9 】

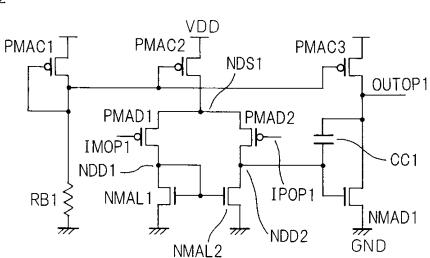

図 1 2 はオペアンプ回路をトランジスタレベルで示している。

#### 【 0 0 9 0 】

図 1 2 において、 P M A C 1 、 P M A C 2 、 P M A C 3 はカレントミラーを構成する P M O S トランジスタを、 P M A D 1 、 P M A D 2 は差動対を構成する P M O S トランジスタを、 R B 1 はバイアス用の抵抗を、 N M A L 1 、 N M A L 2 は差動対の負荷を構成する N M O S トランジスタを、 N M A D 1 はソース接地の増幅段を構成する N M O S トランジスタを、 C C 1 は位相補償容量を、 I M O P 1 は - 側のオペアンプ入力を、 I P O P 1 は + 側のオペアンプ入力を、 N D D 1 、 N D D 2 は差動対のドレンインノードを、 N D S 1 は差動対の共通ソースノードを、 V D D は例えば 5 V 電源を、 G N D は G N D 電位 ( 0 V ) を、 O U T O P 1 はオペアンプの出力を、それぞれ示している。

10

#### 【 0 0 9 1 】

図 1 2 の回路は一般的なオペアンプ回路なので、詳細な動作の説明は省略する。

#### 【 0 0 9 2 】

図 1 2 のオペアンプ回路の入力換算オフセットをできるだけ小さくするために、マッチングが必要な素子は、まず、 P M O S トランジスタ P M A D 1 と P M A D 2 であることが知られている。 N M O S トランジスタ N M A L 1 と N M A L 2 の素子特性も一致している必要がある。このようなマッチングが必要なトランジスタや素子のレイアウト手法として、前述のコモンセントロイド配置が知られている。

20

#### 【 0 0 9 3 】

前述の図 2 は、図 1 2 の P M O S トランジスタ P M A D 1 と P M A D 2 をコモンセントロイド配置とする場合のレイアウト例を示している。コモンセントロイド配置については、図 2 で説明したので説明を省略する。

#### 【 0 0 9 4 】

以上、レギュレータ回路の出力電圧精度にバンドギャップ回路の出力電圧が関係していること、このバンドギャップ回路の出力電圧精度が重要なこと、バンドギャップ電圧の精度をできるだけ高く保つためには、オペアンプのオフセット電圧を小さくする必要があること、そのための手法としてコモンセントロイド配置が知られていることを説明した。

30

#### 【 0 0 9 5 】

オペアンプのオフセット電圧や、デジタル回路に影響する要因としてアンテナ効果が知られている。アンテナ効果とは、 M O S トランジスタの製造時に、プラズマを使用したプロセス（製造工程）において、プラズマの電荷に起因して、 M O S トランジスタのゲート酸化膜に、電気的ストレスが加わり、信頼性の問題や、 M O S トランジスタの特性変動が引き起こされることを指している。ゲート酸化膜に接続された金属配線の加工時に、加工途中の金属配線が、電荷を集めて、ゲート酸化膜に損傷を与える可能性があることから、アンテナ効果と一般に呼ばれることが多い。

40

#### 【 0 0 9 6 】

従来より、プラズマプロセスでの配線加工時に、アンテナ（ゲートに接続された金属配線）が集めた電荷により、 M O S トランジスタのしきい値電圧 V t h が変動し、不均一なアンテナ効果により、差動回路のオフセット電圧が増加することが指摘されている。

#### 【 0 0 9 7 】

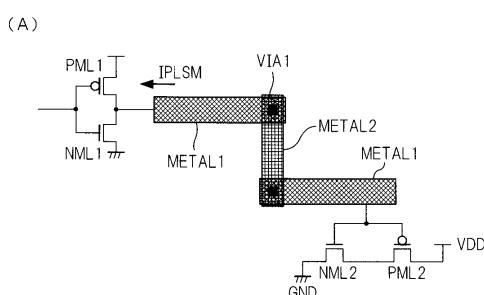

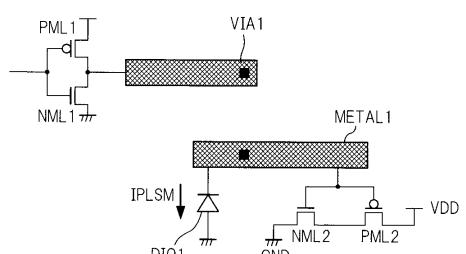

図 1 3 は、アンテナ効果を説明する図である。図 1 3 において、 P M L 1 、 P M L 2 は P M O S トランジスタを、 N M L 1 、 N M L 2 は N M O S トランジスタを、 V D D は回路形成後に + の電源となる端子を、 G N D は回路形成後に G N D となる端子を、 M E T A L 1 は一層目金属配線を、 M E T A L 2 は二層目金属配線を、 V I A 1 はスルーホールを、 I P L S M はプラズマ工程で流れる電流を、示している。

#### 【 0 0 9 8 】

10

20

30

40

50

図13のMETAL1、METAL2、VIA1の表示方法は図2、図12と同じであるので説明は省略する。

#### 【0099】

図13の(A)は、METAL2のエッティング時(パターニング時)に流れる電流IP LSMを示している。METAL2のエッティング時には、図13の(A)のような配線形状では、METAL2がVIA1、METAL1に接続されているので、PML1、NML1のドレイン接合に接続されている。従って、エッティング時に配線により集められた電荷は、例えば、PML1、NML1のドレインの接合のリーク電流により放電される経路が存在する。

#### 【0100】

一方、図13の(B)は、METAL2をエッティングする前の段階、METAL1のエッティング時に流れる電流を示している。図13の(B)のような配線構造では、METAL1のエッティング時には、PML1、NML1のドレインに接続されるMETAL1と、PML2、NML2のゲートに接続されるMETAL1が異なる配線となる。このため、PML1、NML1のドレインに接続されるMETAL1が集めた電荷は、図7の(A)に示したのと同様の経路(PML1、NML1のドレイン)で放電される。しかし、PML2、NML2のゲートだけに接続されたMETAL1が、METAL1のエッティング時に集めた電荷は、放電経路がない。このため、プラズマ工程で集められた電荷は、ゲート酸化膜を通じて流れるしかなく、トンネル電流となってIPLSMが、ゲート酸化膜を流れる。この電流により、例えば、MOSトランジスタのVthの変化が引き起こされる。あるいは、ゲート酸化膜が損傷を受ける。

10

#### 【0101】

このような、配線加工時のゲート酸化膜の損傷を避けるために、従来より、アンテナダイオードと呼ばれる保護ダイオードが使用されている。

#### 【0102】

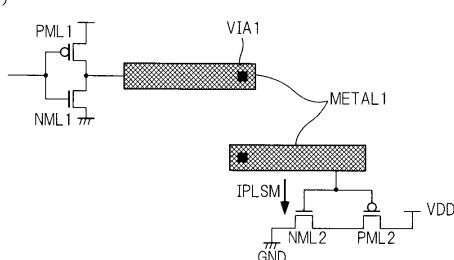

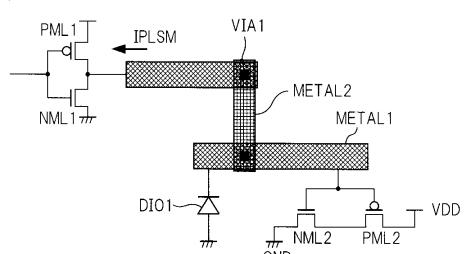

図14は、この保護のためのダイオードの例を示している。図14と図13の違いはダイオードDIO1と、DIO1の接続のためのMETAL1の形状の違いだけなので、この部分を説明する。

#### 【0103】

図14の(A)は、図13の(A)と同じく、METAL2の加工時に流れる電流を示している。図13の(A)でもMETAL2の加工時には、加工しているメタルにドレイン接合が接続されているので、ゲート酸化膜に電流が流れることはなかった。図14においても配線構造が図13と同じなので、METAL2の加工時にプラズマ工程で配線が集める電荷がゲート酸化膜の損傷の原因となることはない。図13の(B)では、METAL1の加工時にMETAL1がゲート酸化膜だけに接続されているパターンが存在することにより、METAL1加工時の電荷がゲート酸化膜に流れ、酸化膜の損傷の原因となることがあった。このような状況を回避するために、図14の構造では、アンテナダイオードと呼ばれるダイオードDIO1がゲートに接続されるMETAL1配線に接続されている。このような電流経路DIO1を用意しておくことで、ゲートに接続されるMETAL1の加工時に、ゲート酸化膜に電流が流れることを防ぐことができる。METAL1が集めた電荷は、例えば、DIO1のリーク電流となって、図14の(B)のIPLSMの経路で放電される。DIO1は、配線の加工時には、電流放電経路として働くが、製造後の通常の動作時には、逆バイアスされているので、多少のリーク電流と、容量、面積の増加は招くが、動作には、ほとんど影響しないようになっている。

30

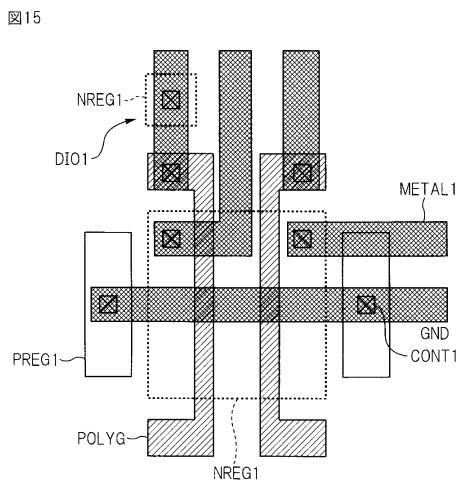

#### 【0104】

図15は、このアンテナダイオードの平面構造の一例を、図16は断面構造の一例を示している。図15のPOLYG、NREG1、PREG1、CONT1、METAL1などの表示の方法は、図1の表示方法と同じなので重複する説明は省略する。図15のDIO1はアンテナダイオードとなる部分を示している。図15に示すように、ごく小さい面積のダイオードをゲート電極に接続されるMETAL1に接続することでゲート酸化膜を

40

50

保護できることが知られている。例えば、P型基板中に、N型の拡散領域NREG1をおいて、メタル(METAL1)に接続することで、逆バイアスされたダイオードを、ゲート電極に接続される配線に接続することができる。

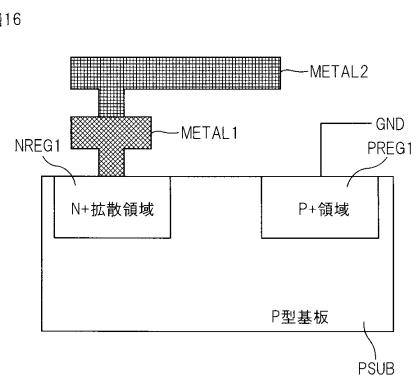

#### 【0105】

図16において、PSUBはP型基板を、PREG1はP型の拡散領域(P+領域として示した)を、NREG1はN型の拡散領域(N+領域として示した)を、GNDはGND端子となる部分を、METAL1は一層目の金属配線を、METAL2は2層目の金属配線を、示している。図16に示すように、P型の基板PSUBは、製造後の動作時には、GND電位となるので、PSUBがDIO1のアノードとなり、NREG1がカソードとなる。つまり、既に説明したように、逆バイアスされるので、回路の動作には影響しない。10

#### 【0106】

図14から図16で説明したように、ゲート酸化膜の保護のために、アンテナダイオードを使用することで、デジタル回路用の微細MOSトランジスタの劣化や破壊を防いだり、アナログ回路部分のオフセット電圧の増加を防げることが知られていた。

#### 【0107】

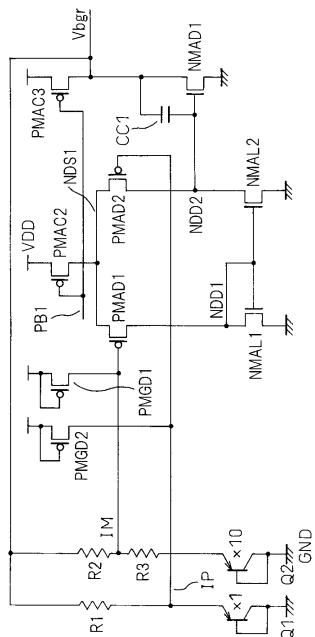

以上説明した技術に基づいて、ここでは図17に示すようなバンドギャップ回路を製造する。

#### 【0108】

図17において、PMAC2、PMAC3は電流源を構成するPMOSトランジスタを、PMAD1、PMAD2は差動対を構成するPMOSトランジスタを、R1、R2、R3は抵抗を、NMAL1、NMAL2は差動対の負荷を構成するNMOSトランジスタを、NMAD1はソース接地の増幅段を構成するNMOSトランジスタを、CC1は位相補償容量を、IMは-側のオペアンプ入力を、IPは+側のオペアンプ入力を、NDD1、NDD2は差動対のドレインノードを、NDS1は差動対の共通ソースノードを、VDDは例えれば5V電源を、GNDはGND電位(0V)を、Vbgrはバンドギャップ回路出力を、Q1、Q2はpnpバイポーラトランジスタ(以下pnpBJTと略す)を、BJTに添えられた数字は、BJTの相対的な面積の比を、PMGD1とPMGD2はアンテナダイオードとして働くトランジスタを、PB1はバイアス電位を、示している。(Rで始まる素子名は抵抗を、PMで始まる素子名はPMOSトランジスタを、NMで始まる素子名はNMOSトランジスタを、Cで始まる素子名は容量を、表わしているものとする。)2030

図17で、図10および図12の回路に相当する素子、ノード部分には、同じ名称を与えて、対応関係がわかるように示している。

#### 【0109】

図12で説明したように、オペアンプ回路の入力換算オフセットができるだけ小さくするため、マッチングが必要な素子は、まず、PMOSトランジスタPMAD1とPMAD2となる。NMOSトランジスタNMAL1とNMAL2の素子特性も一致している必要がある。

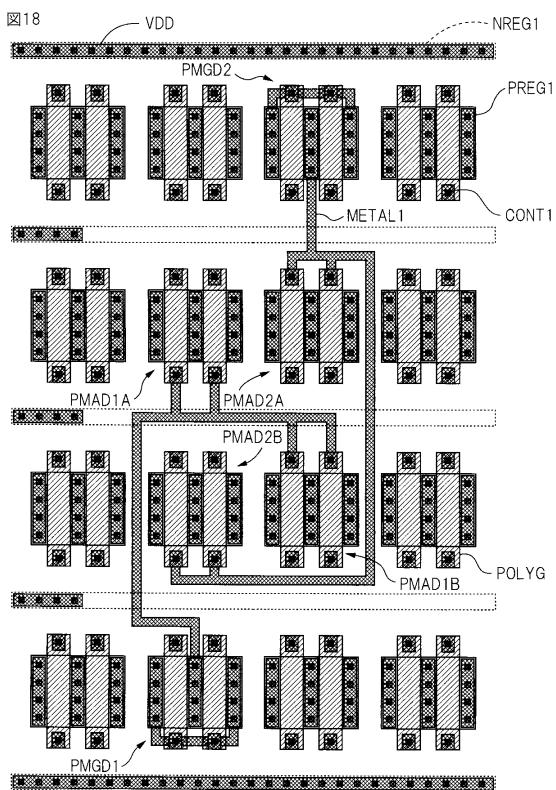

#### 【0110】

図18は、図17のバンドギャップ回路のP型MOSトランジスタ対をなす2個のPMOSトランジスタPMAD1とPMAD2、およびアンテナダイオードをなす2個のPMOSトランジスタPMGD1とPMGD2の部分を、アナログ回路用セルアレイを用いて形成したレイアウト例を示す図である。図18は、このレイアウト例を、METAL1までの配線の例として示している。40

#### 【0111】

図18において、CONT1はコンタクトを、PREG1はP型の拡散領域を、METAL1は1層目の金属配線を、POLYGはPoly-Siゲート電極(ポリシリコンゲート電極)を、NREG1はN型の拡散領域を、VDDは+の電源となる領域を、PMA1A、PMAD1Bは、図17のPMAD1を分割配置したトランジスタを、PMAD2A、PMAD2Bは図17のPMAD2を分割配置したトランジスタを、PMGD1、50

P M G D 2 はアンテナダイオードとして働く P M O S トランジスタを、示す。

【 0 1 1 2 】

図 1 8 の P M A D 1 A および P M A D 1 B は、図 1 7 の P M A D 1 を分割配置したトランジスタであり、P M A D 2 A および P M A D 2 B は図 1 7 の P M A D 2 を分割配置したトランジスタである。P M A D 1 A と P M A D 1 B 、 P M A D 2 A と P M A D 2 B を対角に配置し、コモンセントロイド配置を実現している。

【 0 1 1 3 】

例えば、酸化膜厚さなどが製造時に場所によって、不均一となつたとする。P M A D 1 は、左に配置された P M A D 1 A と、右に配置された P M A D 1 B を並列接続している。一方、P M A D 2 も左に配置された P M A D 2 B と、右に配置された P M A D 2 A を並列接続しているので、P M A D 1 と P M A D 2 の関係では、左右の特性の違いが相殺される。同様に上下方向の特性のずれも相殺されることが明らかであろう。

10

【 0 1 1 4 】

また、前述のように、微細化のすすんだ M O S トランジスタの製造工程では、斜め方向からイオンを注入するような工程が採用されることがある。このような場合、例えば、P o l y - S i ゲート電極 P O L Y G の右側と左側で、ソース、ドレインの拡散層の高濃度領域とゲート電極のオーバーラップ幅が異なることが起こりえる。これは、P O L Y G の右側と左側で、実効の寄生抵抗が異なる状況を生じさせ、P O L G の右側拡散層をソース、左側拡散層をドレインとする場合と、P O L G の左側拡散層をソース、右側拡散層をドレインとする場合で、M O S トランジスタの特性が異なる状況を生じる。このような製造工程の性質から、マッチングの必要なトランジスタ同士では、電流の流れる向きまで含めて、素子の形状、素子の使用法をそろえる必要がある。

20

【 0 1 1 5 】

ところが、レイアウト時の電流の向きは、回路結線を確認する L V S と呼ばれるソフトウェアや D R C と呼ばれるソフトウェアでは、確認することができない。なぜなら、M O S トランジスタの電流の流れる向きを知るためにには、回路の動作を理解し、マッチングが必要な素子を認識するという複雑な回路の全体の理解が必要となるためである。このため、従来は、電流の向きまで含めた素子の配置の同一性の確認は人手に頼るのが一般的であった。図 1 8 のレイアウトでは、図 1 8 に示すようにドレインを共通とする 2 つの M O S トランジスタを基本レイアウト単位として採用しているので、この問題が解決される。

30

【 0 1 1 6 】

図 1 8 では、レイアウトの基本単位をドレインを共通とするゲート幅、ゲート長の等しい 2 つの P M O S トランジスタとしている。中央部分 D R A I N 1 をドレイン、左と右の電極をソースとしているので、基本セル単位内で、電流の向きが反対となる 2 つのトランジスタの並列接続が実現されている。これにより、図 1 8 のように、P M A D 1 と P M A D 2 のコモンセントロイド配置する場合に、それぞれのトランジスタの個々の電流の向きは考慮しなくてよい効果が得られる。なぜなら、P M A D 1 A 、 P M A D 1 B 、 P M A D 2 A 、 P M A D 2 B それぞれが、右向きの電流を流すとトランジスタと、左向きの電流を流すトランジスタの並列接続となっているので、電流の向きの違いによる特性のずれは相殺されるからである。

40

【 0 1 1 7 】

基本単位を電流の向きが反対となる 2 つのトランジスタの並列接続としておくことで、図 1 8 の基本セルの構造を守っている限り、電流の向きを詳細に考慮したり、検証する必要がなくなる利点が得られる。つまり、電流の向きが異なることによる特性のずれを見落とす可能性をゼロとできる。

【 0 1 1 8 】

図 1 8 で、4 行、4 列に配置された基本 P M O S トランジスタセル P M O S C 2 のアレイの周辺部分は従来のダミー素子と同様に機能する。つまり、規則的に繰り返されたトランジスタ配列の中央部分は、より、周辺部分の影響を受けず、加工の均一性が向上することが期待され、この部分に、マッチングの必要な素子を配置する。

50

**【0119】**

図18でも、PMAD1A、PMAD2A、PMAD1B、PMAD2Bを配列（アレイ）の中央部分に配置しているのは、このためである。

**【0120】**

ゲート酸化膜を保護するアンテナダイオードを、仮にトランジスタアレイ部分の外に専用のアンテナダイオードを用意した場合、METAL1配線での接続が困難になる問題がある。また、規則的に配置したトランジスタ配列に、形状の異なるダイオードを配置しようとすると、トランジスタ形状、分離領域の形状の均一性、同一性が保てなくなる。さらに、例えば、PMOS基本セル内部にダイオードを配置すると、レイアウト単位の同一性の問題は解決できるが、実際には使用しないダイオードを多数用意しておくことになり、占有面積の観点から不利となる。10

**【0121】**

そこで、本実施形態のレイアウトでは、アンテナダイオードとして、基本セルのトランジスタの、例えばドレイン電極を利用する。（ソース電極であってもよい。）

図17の回路図に示すように、例えば、マッチングの必要なPMOSトランジスタのゲートを保護するために、ゲートをVDD電位としたPMOSトランジスタのドレイン電極をMETAL1配線により、PMAD1、PMAD2のゲートに接続しておく。PMGD1、PMGD2のゲートとソースをVDDとしておくことで、PMGD1、PMGD2はOFF状態となり、トランジスタとしては機能しない。このPMGD1、PMGD2のドレイン接合をダイオードとして利用することで、トランジスタアレイの規則性、同一性を損なうことなくアンテナダイオードによるゲート酸化膜の保護が可能となる。図18に示すように、PMOS基本セルとPMOS基本セルの左右の辺は、METAL1が配線できるように、配線チャネルを確保しておく。このような基本セル構造を採用しておくことと、コモンセントロイド配置したPMOS基本セルのゲートをMETAL1配線で接続し、さらに、アンテナダイオードとなるトランジスタのドレインとの接続が可能となる。20

**【0122】**

PMOSアレイの中央部分にマッチングの必要なトランジスタを配置し、アンテナダイオードはアレイの端の部分を利用する。アンテナダイオードに特性の一貫性が必要ないためである。図18の例ではアレイの一番上の行にPMGD2を配置し、アレイの一番下の行にアンテナダイオードPMGD1を配置する例を示した。2行目と3行目にPMAD1とPMAD2を配置しているので、縦方向にMETAL1でアンテナダイオードと保護すべきゲートを接続する配線が必要となる。つまり、必然的に、縦方向のMETAL1配線が利用可能な配置としてトランジスタアレイを構成する必要がある。図18は、これを満たす構造の一例となっている。30

**【0123】**

素子分離領域の均一性、周期性を保つために、基本セル構造にPMOSのN型WELLに給電するN領域NREG1を含めているので、基本セルの行と行の間にWELL給電領域が存在する。すべてのNREG1領域にMETAL1でVDD電位を給電する必要はないが、原則として、NREG1の部分はMETAL1でVDD電位を給電（コンタクトCONT1で接続）することが望ましい。また、ゲートPOLY部分には、POLYの接続のためのMETAL1との接続部分が必要なので（図5のGATE1、GATE2、GATE3、GATE4）、回路を構成するためには横方向の配線可能領域がNREG1上の空間とは別に必要となる。40

**【0124】**

そこで、図18のNREG1とゲートのコンタクト部分との隙間に、横方向にMETAL1配線が可能な領域を確保している。この部分の配線領域をMETAL1配線としているのは、縦方向配線をMETAL2配線とするほうが、都合がいいためである。

**【0125】**

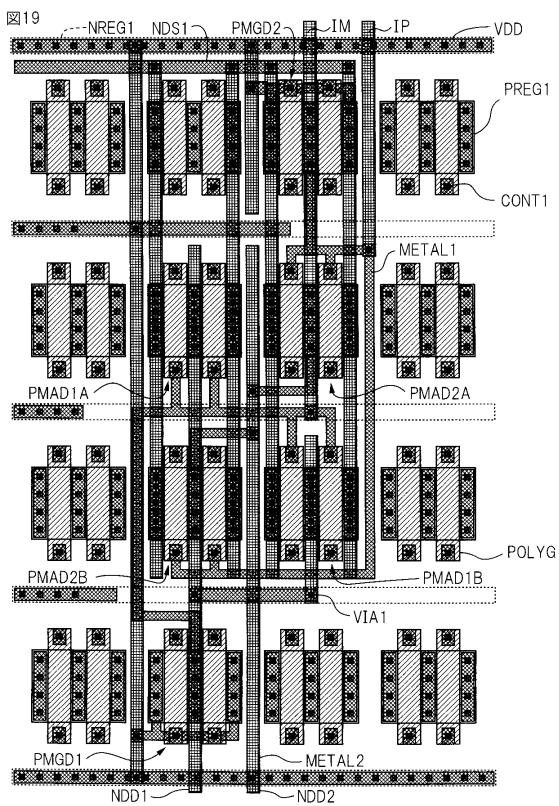

図19は、図18に、METAL2とVIA1を追加して表示した図となっている（一部METAL1も追加されている）。図18の構造で、各部のノードを接続したり、外部50

に引き出したりすることが可能なことを説明する図となっている。層が重なって分かりにくい部分は、図18を参照しながら各部の接続の例を説明する。

#### 【0126】

図19を用いて、METAL2配線も含めてレイアウトの説明をすすめる。図19において、METAL2は2層目の金属配線を、VIA1はスルーホールを、IM、IP、VDD、NDS1、NDD1、NDD2は、図18の同じ名前の回路ノードに対応する部分を、示している。図19において、PVIA1は黒く塗りつぶした正方形として示した。METAL1は斜め(-)45度の縞模様のハッチング图形として示した。METAL2は水平垂直方向の縞模様のハッチング图形として示した。その他の層の表示方法は他の図と同じとなっている。

10

#### 【0127】

図18で、PMGD2のドレインとPMAD2A、PMAD2BのゲートをMETAL1で接続できることが分かる。同様にPMAD1A、PMAD1BのゲートとPMGD1のドレインをMETAL1で接続可能なことが分かる。図19は、PMAD1、PMAD2のソース、ドレイン、PMGD1、PMGD2のゲート、ソースを配線する例を示している。

#### 【0128】

PMAD1A、PMAD2A、PMAD2B、PMAD1Bのソース電極は、共通のソースノードNDS1に接続されなければならない。これを実現するために、ソース電極上の縦方向METAL2配線で、VIA1を経由して、これら差動対のPMOSトランジスタのソースを共通ノードに接続する。トランジスタのソース、ドレインには、拡散層と配線を接続するためのコンタクトCONTACT1とMETAL1が(図18に示すように)必ず存在するので、これらの上部を縦方向に配線する配線層は必然的にMETAL2となる。従って、PMAD1AとPMAD2Bのソースを接続する2本のMETAL2配線、PMAD2A、PMAD1Bのソースを接続する2本のMETAL2配線どうしを接続する配線は、METAL1あるいは3層目の配線METAL3となる。

20

#### 【0129】

図19では、NDS1として示した横方向METAL1配線に、これらソース電極を引き出したMETAL2をVIA1で接続する例が示されている。

#### 【0130】

30

図18の説明で、横方向配線をMETAL1とし、縦方向配線をMETAL2配線とするほうが都合のいいことを述べたが、図19のように縦方向にMETAL2配線を使用するほうがMETAL1を縦方向配線とするより縦方向配線の総数を確保できるからである。ソース、ドレイン部分にMETAL1配線がすでに存在するので、縦方向配線にMETAL1を使用しようとすると、トランジスタと隣接するトランジスタの間の領域しか使用できなくなる。これに対して、METAL2配線を縦方向配線に使用すると、ドレイン、ソースの上部部分を縦方向配線チャネルとして利用できる利点が生まれる。

#### 【0131】

すでに説明したように、MOSトランジスタの電流チャネル上に配線がある場合と、ない場合で、トランジスタのしきい値電圧V<sub>th</sub>が変化する場合がある。これを避けるためには、図19で、PREG1とPOLYGが重なった領域、トランジスタの反転層が形成されるチャネル上部には配線を置けない。図19でも、トランジスタの電流チャネル部分にはいっさいの配線を配置していない。このことからも、縦方向にMETAL2配線を使用して、ドレイン、ソースの上部を配線チャネルとして使用する利点が理解できる。

40

#### 【0132】

アレイの最上部のMETAL1配線はVDDとして図示している。N型WELL領域の給電部分なので、この部分のMETAL1はVDDに接続される。また、アレイの行と行の間のWELL給電部分でMETAL1配線が可能な部分もVDDとなる。これらMETAL1配線同士をMETAL2で縦方向に接続することで、VDDを各部に給電できる。また電源構造もメッシュ状となり都合がいい。

50

**【 0 1 3 3 】**

図18ではPMGD2のゲート、ソースがVDDに接続されていなかったが、アレイ周辺のVDD配線と、縦方向METAL2配線、横方向METAL1配線を利用して、図19のPMGD2のように配線可能となる。PMGD1もPMGD2と同様の考え方で、ゲートとソースにVDDを供給することが可能なことは図19のPMGD1部分を見れば明らかであろう。

**【 0 1 3 4 】**

NDD1はPMAD1A、PMAD1Bのドレインに接続されなければならない。図19ではNDD1は、METAL2配線として示した。VIA1と横方向METAL1配線、縦方向METAL2配線を使用して接続できる。図18では、図を簡単にするために図示していないが、PMAD2Bのドレイン電極は、図19では、METAL1配線を使用してMETAL2のNDD2に接続している。基本セルのゲートとMETAL1の接続部分の間をMETAL1配線が通過可能なサイズとしておくことで、図19のような接続が可能となる。

10

**【 0 1 3 5 】**

トランジスタのゲート長Lはアナログ回路の場合 $1\text{ }\mu\text{m}$ から $2\text{ }\mu\text{m}$ 程度と大きいので、図5のPMOS基本セルPMOSC2のGATE1とGATE3、GATE2とGATE4のMETAL1の隙間にMETAL1配線を通すことは十分可能である。

**【 0 1 3 6 】**

PMAD2Bのドレイン上にはPMAD1Aのドレイン配線のためのMETAL2配線が通過しているので、PMAD2BはMETAL1でドレインを引き出している。同様に、PMAD2Aのドレイン電極の接続もゲートコントラクト部分のメタルの間を通過するMETAL1配線で引き出している。PMAD2Aのドレイン上にはPMAD1Aのゲート電極とPMAD1Bのゲート電極を引き出すためのMETAL2配線IMが通過しているためである。

20

**【 0 1 3 7 】**

METAL2配線IM、IPは、縦方向に、PMAD1、PMAD2のゲートに接続される。PMAD1、PMAD2のゲートは、PMGD1、PMGD2のドレインをアンテナダイオードとして保護しているので、これらのMETAL1配線をMETAL2配線に接続して外部にとりだすことができる。

30

**【 0 1 3 8 】**

図19では、差動対PMAD1、PMAD2、これらのアンテナダイオードの接続だけを図示したが、図19の考え方で、同様に任意の回路を構成できることはいうまでもない。図18、図19に示したような基本セルの構造と配線チャネルの考え方で、コモンセンタロイド配置を実現できる。図で使用していないトランジスタは未配線のまま図示しているが、これらの素子を回路素子として使用してよいこと、アレイの列数も図示の都合で4列としたが、任意の列数でかまわないこと、行数も4行としたが、アレイの中心部分を使用するための最低限の行数で、より大きい行数でもかまわないこと、周辺部分のトランジスタを未使用のトランジスタとする場合には、ゲート、ドレイン、ソースなどを簡単に電源電位に固定できることはいうまでもない。WELL給電部分のコントラクト、METAL1配線も完全には図示していないが、必要に応じて、配線が可能な範囲でVDD電位を給電すればよい。

40

**【 0 1 3 9 】**

以上、図17のバンドギャップ回路のオペアンプのPMOSトランジスタPMAD1とPMAD2を、PMOSアレイARYP1を利用して実現する例を説明した。オペアンプ回路のNMOSトランジスタNMAL1とNMAL2も、同様にNMOSアレイARYN1を利用して実現することが可能である。

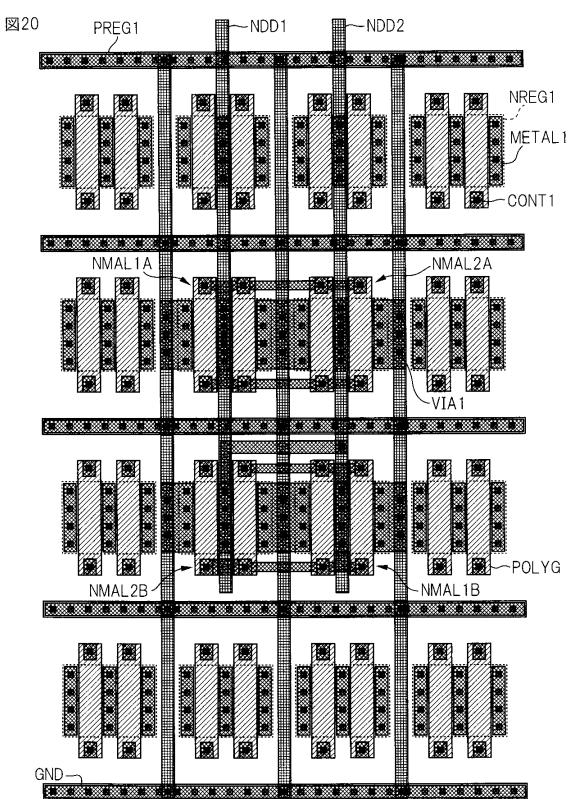

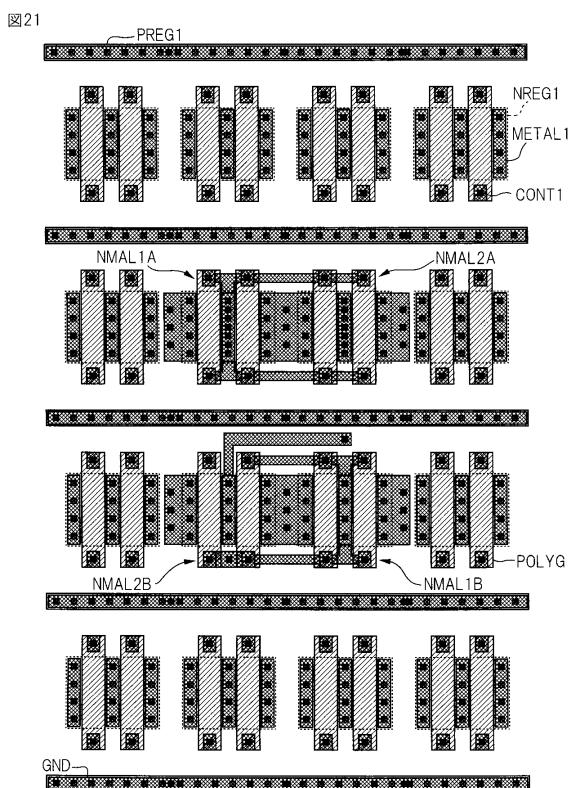

**【 0 1 4 0 】**

図20は、NMOSアレイARYN1におけるNMOSアレイの配置、接続例をMETAL2配線までを図示して示している。図21は、図20のMETAL2部分を取り除い

50

てMETAL 1までを示している。これらの図を用いて、PMOSを例に説明した発明の考え方でNMOS回路部分も構成できることを説明する。

#### 【0141】

図17のバンドギャップ回路のオペアンプのオフセット電圧をできる限り小さくするために、NMAL1とNMAL2の特性がそろっている必要がある。NMAD1とNMAL1、NMAL2の特性も一致していることが望ましいが、図が複雑になるので、ここでは、NMAL1とNMAL2をコモンセントロイド配置とする例を図20、図21を用いて説明する。

#### 【0142】

図20、図21のレイアウト層の表現方法はこれまで説明した図と同じとなっている。

NMOSトランジスタ部分なので、ソース、ドレイン部分を形成するのがNREG1であること、PMOSアレイではNREG1で形成されていたWELL給電部分がP基板の給電部分PREG1となっていること以外、PMOSアレイと同様に作られている。

#### 【0143】

図20において、NDD1、NDD2は、図17の回路ノードNDD1、NDD2に対応する配線を示している。NMAL1とNMAL2を分割し、NMAL1A、NMAL1BとNMAL2A、NMAL2Bとし、コモンセントロイド配置としている。NMAL1はゲートとドレインが同じノードとなるので、図21に示すように、ゲート部分のコンタクト部分のMETAL1とドレイン部分のMETAL1が接続されている。

#### 【0144】

図20に示すように、METAL2配線NDD1をVIA1によりNMAL1Aのドレインに接続し、NMAL2Bのゲート部分のMETAL1とNDD1をVIA1で接続することで、例えば、NDD1を接続、配線することが可能である。NDD2についても同様に、縦方向のMETAL2配線をVIA1でドレインに接続することで、NMAL2Aと接続可能となる。NMAL2Bのドレイン上には、図20の場合、例えば、NDD1のMETAL2配線があるので、METAL1配線でドレインを引き出しNDD2に接続すればよい。GND配線は、PREG1に給電するMETAL1配線、縦方向のMETAL2配線を使用して、ソース電極に接続すればよい。

#### 【0145】

図20、図21に示すように、この場合、NMOSのソース電位はGNDなので、PMOSの差動回路部分より、配線がより単純になる。PMOS差動回路部分では、ソース電位がVDDではないので、NDS1配線のための配線が必要となるが、NMAL1、NMAL2ではNMOSトランジスタのソースはP型基板給電部分と同電位でよく、必要な信号配線総数が少なくてすむ。つまり、図18のようなソース電位が電源電位ではない回路部分がレイアウト可能であれば、実用上十分な回路が、発明の考え方で配線可能、実現可能となる。

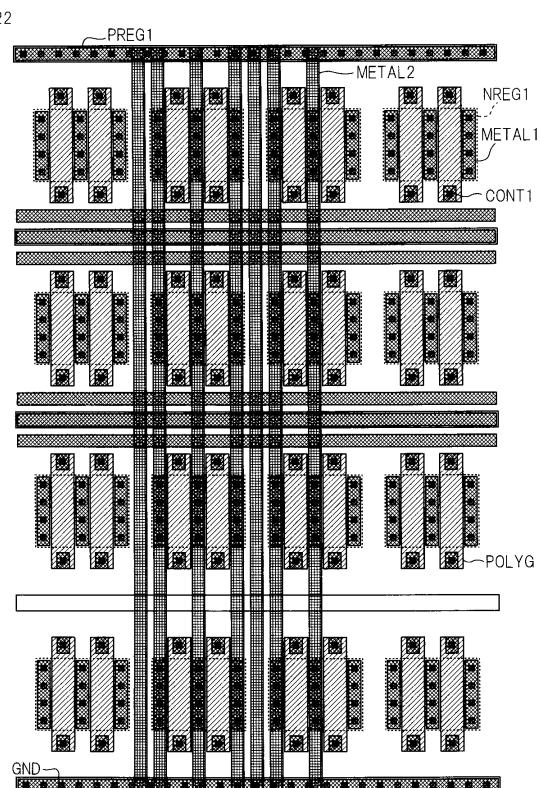

#### 【0146】

図22は、図8と同様にNMOSトランジスタ部分の配線可能領域に、仮想的に配線を配置して示した図となっている。PMOSの場合と拡散層の極性が逆になっていることを除いて、同様に配線可能のこと、NMOSトランジスタにおいても、電流チャネル上部を避けて配線チャネルを配置できることがわかる。

#### 【0147】

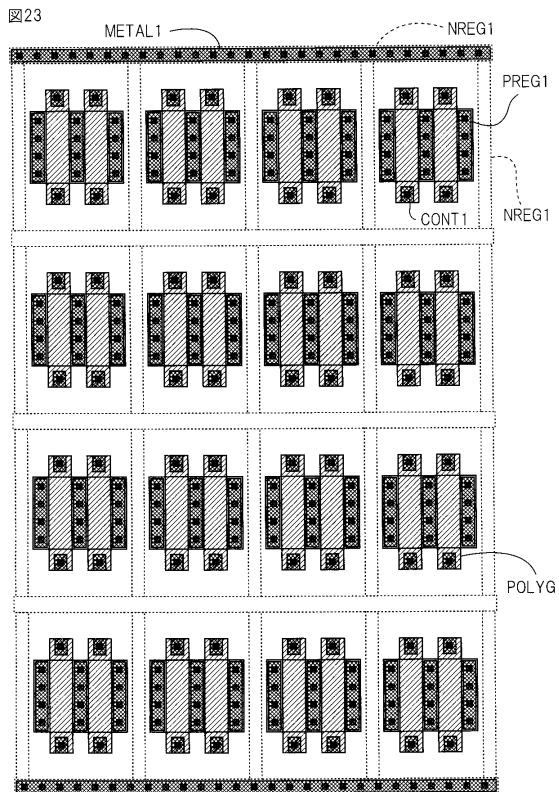

次に、基本セルの繰り返し構造の他の例を図23から図28を用いて説明する。

#### 【0148】

図23はPMOSアレイの基本構造の他の例を示している。層の表示の方法は図5と同じとなっている。図5では、基本セルとしてセルの上下でN型WELLに給電するためのNREG1を配置した構造を示した。図23では、セルの上下に加えて、セルの左右にもWELL給電部分を追加した構造となっている。WELL給電部分も含めて繰り返し構造を実現する必要があることを、図5では説明した。アレイの左右の端でWELLに電位を供給するためのNREG1を基本セル構造に取り込むことで、列数が少ない場合でもアレ

10

20

30

40

50

イ端部の影響を軽減できる。

**【0149】**

セルの左右にもWELL給電部分を設ける構造は、NMOS基本セルの繰り返し構造にも適用可能である。

**【0150】**

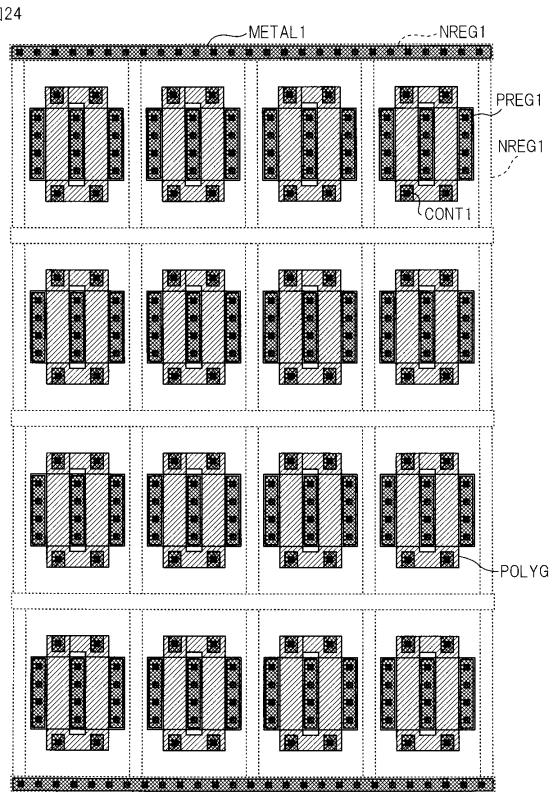

図24は、図6の基本セル内部で、2つのPMOSトランジスタのゲート同士をPOLY Gで直接接続した構造に、セルの左右にもWELL給電部分を設ける構造を適用した場合の基本構造を示す。図18のPMG D1にみられるように、ゲートとMETAL 1のコンタクト部分の間を、METAL 1の配線を通過させて信号を引き出すような場合には、図24のセル構造のほうが、配線しやすくなる。図24の構造は、当然NMOS基本セルにも適用可能である。

10

**【0151】**

PMOSアレイの基本構造とNMOSアレイの基本構造は同じ例を説明してきたが、これら可能な構造を組み合わせて使用し得ることはいうまでもないであろう。

**【0152】**

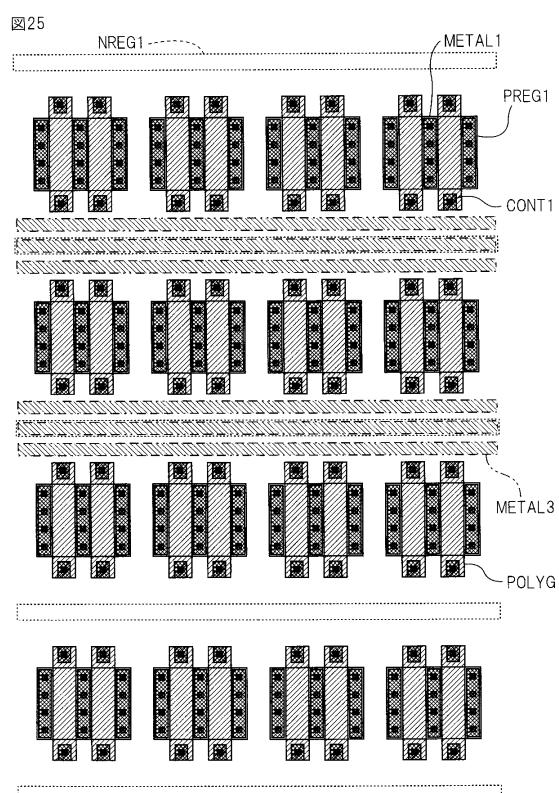

図25は、図8で示したPMOSアレイのMETAL 2までの配線チャネルの考え方を、3層目の配線METAL 3に適用した一例となっている。図25で、METAL 3は3層目金属配線の層を示している。図25では、METAL 3はPOLY Gとは逆の傾きの斜めハッチングかつ、矩形の外側が2点鎖線の図形として表示した。

**【0153】**

原則として、横方向配線にMETAL 1を割り当て、縦方向配線をMETAL 2とすることが配線の容易さの観点から望ましいことを説明してきた。このため、METAL 3はMETAL 2と直交する横方向配線とすることが自然となる。図25は、METAL 1配線の上部をMETAL 3配線とする場合となっている。実際の回路の配線ではなく、可能な配線として図示している。

20

**【0154】**

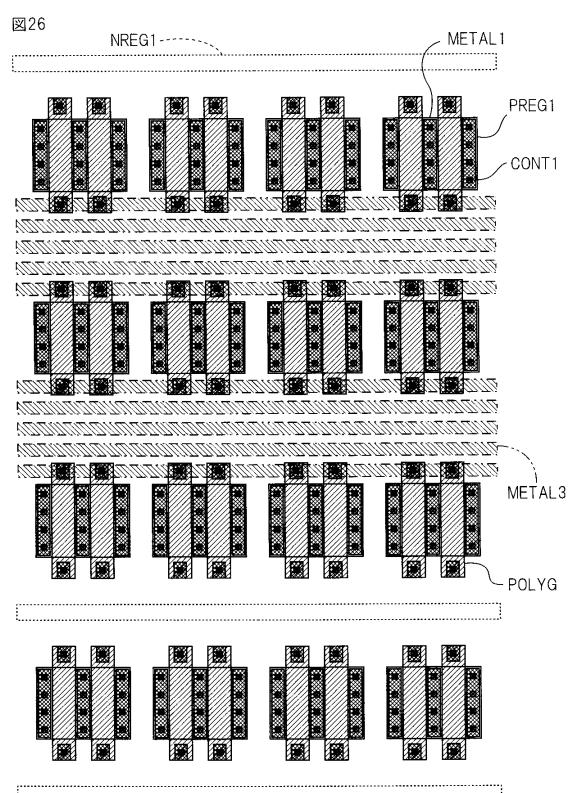

図26は、METAL 3配線の他の例となっている。METAL 1はゲートとMETAL 1のコンタクトのために、POLY Gの端部にすでに存在する。このため、POLY Gの端部はMETAL 1の信号配線チャネルとしては使用できないが、METAL 3配線では、このPOLY Gの端の部分も含めて、配線チャネルとすることも可能である。トランジスタの反転層が形成される部分の上部を配線領域としないことは、同様である。

30

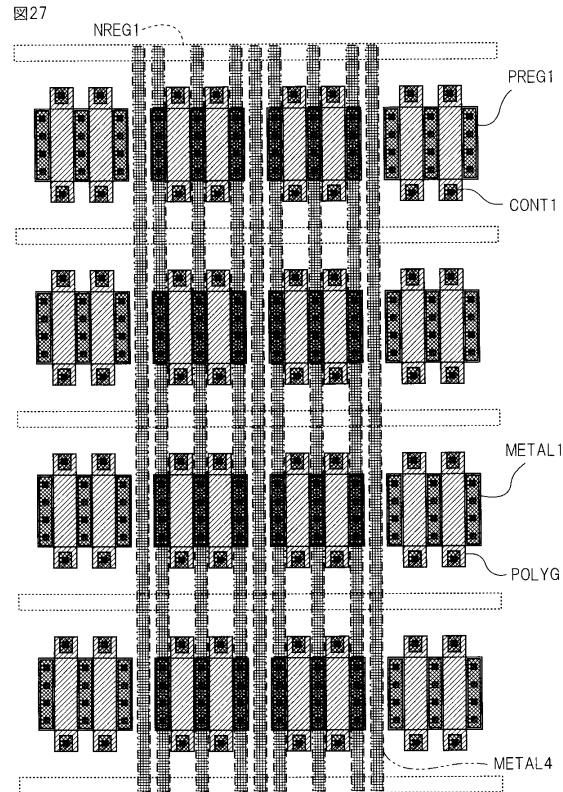

**【0155】**

図27は、図8で示したPMOSアレイの4層目金属配線METAL 4の配線チャネルの考え方を示している。図27で、METAL 4はMETAL 2と同様の水平垂直方向の縞模様ハッチングに加えて、外周を2点鎖線として図示した。

**【0156】**

METAL 2と同様の考え方で、図27のMETAL 4の配線チャネルを配置してよい。電流チャネル上部には、配線領域を置かない。

**【0157】**

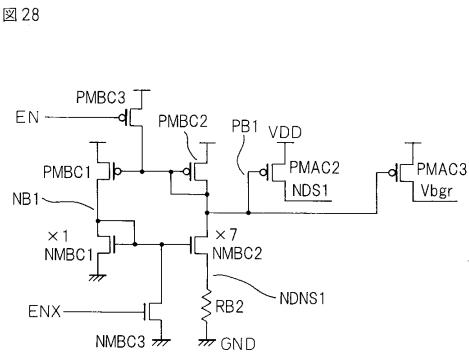

図28はバイアス回路の例を示している。このようなバイアス回路も本発明のレイアウト方法で配置できる例を、以下示す。

40

**【0158】**

図28において、PMBC 1、PMBC 2、PMBC 3はバイアス回路を構成するPMOSトランジスタを、NMBC 1、NMBC 2、NMBC 3はバイアス回路を構成するNMOSトランジスタを、RB 2は抵抗を、PMAC 2、PMAC 3は例えば、図12のPMOSトランジスタを、PB 1はPMOSトランジスタのバイアス電位を、ENはイネーブル信号をEN XはLで回路が動作状態となるENと逆相のイネーブル信号を、NB 1はNMOSトランジスタのバイアス電位を、NDS 1、Vbgrは図12の同名のノードを、NDNS 1はNMBC 2のソースのノードを、示す。

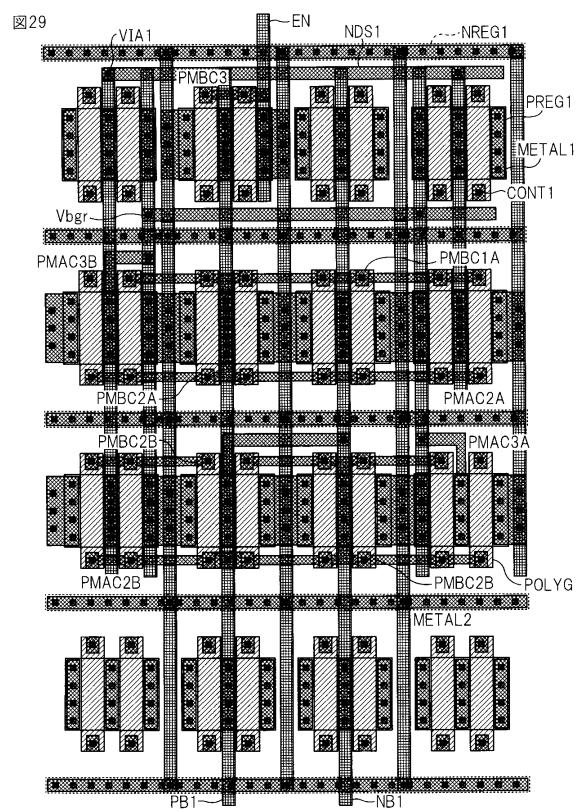

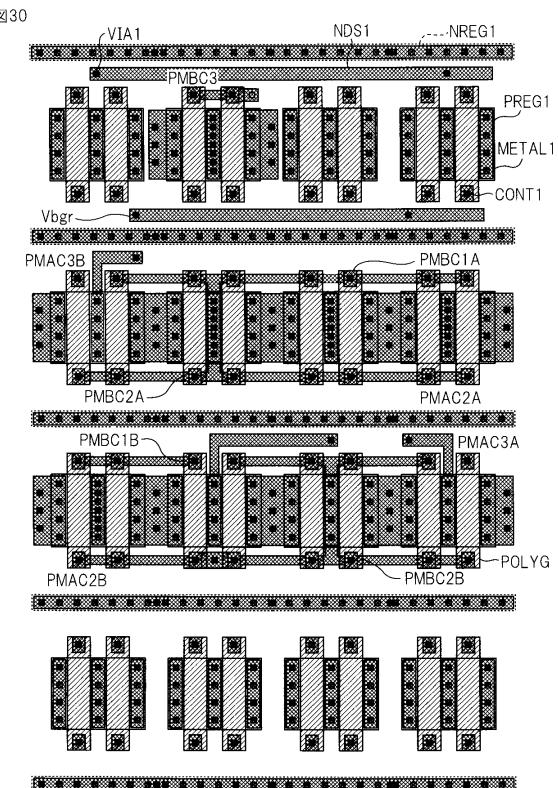

**【0159】**

図29は、図28のバイアス回路のPMOS部分のレイアウトの一例を示している。レイアウトの層の表現方法は他の図にそろえた。また対応する回路ノード名も一部示している。図29ではMETAL2配線までを図示し、図30ではMETAL1だけを示した。

#### 【0160】

これら図29、図30を用いて、図33のバイアス回路のレイアウト例の説明をすすめる。

#### 【0161】

図28でマッチングが必要となるトランジスタ対はPMBC1とPMBC2となるPMAC2、PMAC3もこれらと同じ特性であることが望ましい。

#### 【0162】

図29では、PMBC1をPMBC1AとPMBC1Bに分割し、PMBC2をPMBC2AとPMBC2Bに分割し、コモンセントロイド配置としている。同様にPMAC2とPMAC3も分割し、コモンセントロイド配置とするレイアウト例となっている。図30に見られるように、これら8つのトランジスタはゲート電位が共通なので、それぞれの行でMETAL1配線でゲートを横方向に接続できる。また、これらのゲート電極はPMBC2のドレインにも接続されるので、図30に示すように、PMBC2Aのドレインとゲート電極がMETAL1で接続され、PMBC2BのドレインとゲートがMETAL1で接続されている。

#### 【0163】

図30から分かるように、これら8つのトランジスタのゲートはMETAL1でドレインに接続されているので、PMBC2のドレインがアンテナダイオードとして働く。コモンセントロイド配置された分割されたPMBC2、PMBC1、PMAC2、PMAC3のドレイン電極どうしを、縦方向METAL2配線と、横方向METAL1配線を利用して相互に接続していけば、回路接続が完成する。また、これらトランジスタのソース電位はVDDなので縦方向のMETAL2配線を利用してソースにVDDを供給していけばよい。

#### 【0164】

このような基本的な考え方にもとづいて、配線したのが図29となっている。異なる信号線が上部にある場合のドレイン電極の引き出しはゲートコンタクト部分の間からMETAL1で信号を引き出している。PMBC1Bのドレイン電極の引き出し、PMAC3Bのドレイン電極の引き出しが、このような方法によっている。NDS1やVbgを横方向配線に接続することで、例えば、図19のNDS1に接続可能となりPMOS差動回路が完成する。Vbg配線に関連する回路部分は説明していないが、縦方向配線、横方向配線を使用して所望の位置まで、配線を引きだすことが可能である。ドレインの配線、NDS1、Vbgはアンテナ効果を心配する必要がないので、図29、図19のような構成が効果的である。

#### 【0165】

PMCB3はPB1をVDD電位とするためのパワーダウン制御のための素子となっている。PB1配線をドレインに接続し、ソースをVDDとし、ゲートをENとすることで、図28の回路接続を実現することができる。パワーダウンに関する制御用の素子は特性の一一致の必要がないので、図29、図30に示すように、アレイの最上段に配置している。このように、マッチングの必要ない素子、マッチングの優先度の低い素子を周辺に配置し、中心部分に最もマッチングが必要な素子を配置していくことで、アレイの周辺部分を無駄にすることなく、アレイの中心部分に対してはダミーとしての効果を発揮することが可能となる。

#### 【0166】

図29、図30では、図28のバイアス回路のPMOS部分を例に、レイアウトの実現例を示したが、図19、図29と同様の考え方で、バイアス回路のNMOS部分も容易にレイアウト可能なことはいうまでもない。

#### 【0167】

10

20

30

40

50

以上説明してきた、回路構成、レイアウトによりオペアンプのオフセット電圧をより小さくすることが可能となる。これによりバンドギャップ回路の出力電圧精度の改善が期待できる。さらには、バンドギャップ回路を使用したレギュレータ回路の出力電圧精度も向上する。

#### 【0168】

以上、実施形態を説明したが、開示の技術は、記載した実施形態に限定されるものでなく、各種の変形例が可能であることは、当業者には容易に理解されることである。

#### 【図面の簡単な説明】

#### 【0169】

【図1】図1は、従来のデジタル回路用ゲートアレイの構成と配線例を示す図である。

10

【図2】図2は、オペアンプ回路のトランジスタ対をコモンセントロイド配置したレイアウト例を示す図である。

【図3】図3は、実施形態のアナログ回路用セルアレイにおけるPMOS基本セルおよびNMOS基本セルの配列例を示す図である。

【図4】図4は、実施形態のアナログ回路用セルアレイにおけるPMOS基本セルのゲートポリシリコンと拡散層の配置例を示す図である。

【図5】図5は、実施形態のアナログ回路用セルアレイにおけるPMOS基本セルの構造例を示す図である。

【図6】図6は、実施形態のアナログ回路用セルアレイにおけるPMOS基本セルの構造の変形例を示す図である。

20

【図7】図7は、実施形態のアナログ回路用セルアレイにおける各PMOS基本セルの配線領域を説明する図である。

【図8】図8は、実施形態のアナログ回路用セルアレイにおける配線領域を説明する図である。

【図9】図9は、実施形態に関係するレギュレータ回路の回路例を示す図である。

【図10】図10は、レギュレータ回路内のバンドギャップ回路(BGR回路)の回路例を示す図である。

【図11】図11は、バンドギャップ回路(BGR回路)のオフセット電圧と出力電圧の関係を説明する図である。

【図12】図12は、バンドギャップ回路(BGR回路)内のオペアンプ回路の回路例を示す図である。

30

【図13】図13は、アンテナ効果を説明する図である。

【図14】図14は、アンテナ効果を防ぐためのアンテナダイオードの例を示す図である。

【図15】図15は、アンテナダイオードのレイアウトの従来例を示す図である。

【図16】図16は、アンテナダイオードの断面構造の一例を示す図である。

【図17】図17は、実施形態のアナログ回路用セルアレイを使用して実現するオペアンプ回路とアンテナダイオードの回路を示す図である。

【図18】図18は、コモンセントロイド配置した図17のオペアンプ回路のP型トランジスタ対とアンテナダイオードを、実施形態のアナログ回路用セルアレイを使用して実現するレイアウト例を、一層目金属配線まで示した図である。

40

【図19】図19は、コモンセントロイド配置した図17のオペアンプ回路のP型トランジスタ対とアンテナダイオードを、実施形態のアナログ回路用セルアレイを使用して実現するレイアウト例を、二層目金属配線まで示した図である。

【図20】図20は、コモンセントロイド配置した図17のオペアンプ回路のN型トランジスタ対を、実施形態のアナログ回路用セルアレイを使用して実現するレイアウト例を、二層目金属配線まで示した図である。

【図21】図21は、コモンセントロイド配置した図17のオペアンプ回路のN型トランジスタ対を、実施形態のアナログ回路用セルアレイを使用して実現するレイアウト例を、一層目金属配線まで示した図である。

50

【図22】図22は、実施形態のアナログ回路用N MOSセルアレイの配線チャネルを説明する図である。

【図23】図23は、実施形態のアナログ回路用セルアレイのPMOS基本セル構造の変形例を示したである。

【図24】図24は、実施形態のアナログ回路用セルアレイのPMOS基本セル構造の変形例を示したである。

【図25】図25は、実施形態のアナログ回路用PMOSセルアレイの3層目の配線チャネルを説明する図である。

【図26】図26は、実施形態のアナログ回路用PMOSセルアレイの3層目の配線チャネルを説明する図である。

10

【図27】図27は、実施形態のアナログ回路用PMOSセルアレイの4層目の配線チャネルを説明する図である。

【図28】図28は、実施形態のアナログ回路用セルアレイで実現するバイアス回路の例を示した図である。

【図29】図29は、バイアス回路のPMOS部分のレイアウト例を、二層目配線まで示した図である。

【図30】図30は、バイアス回路のPMOS部分のレイアウト例を、一層目配線まで示した図である。

#### 【符号の説明】

##### 【0170】

PMOSC2 PMOS基本セル

20

NMOSC2 NMOS基本セル

ARYP1 PMOSアレイ

ARYN1 NMOSアレイ

PREG1 P型拡散領域

NREG1 N型拡散領域

POLYG ゲート電極

DRAIN1 (共通)ドレイン

SOURCE1 第1ソース

SOURCE2 第2ソース

30

GATE1 - GATE4 ゲートコンタクト

CONT1 コンタクト

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

(B)

【図14】

図14

(A)

(B)

【図15】

【図16】

【図17】

図17

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

---

フロントページの続き

(72)発明者 岡田 浩司

東京都新宿区西新宿二丁目7番1号 富士通マイクロエレクトロニクス株式会社内

審査官 須原 宏光

(56)参考文献 特開2002-368117(JP,A)

特開2004-281467(JP,A)

特開2007-036194(JP,A)

特開2001-358221(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82

H01L 27/04