(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5180186号

(P5180186)

(45) 発行日 平成25年4月10日(2013.4.10)

(24) 登録日 平成25年1月18日(2013.1.18)

(51) Int.Cl.

H03M 13/41 (2006.01)

F 1

H03M 13/41

請求項の数 24 (全 11 頁)

(21) 出願番号 特願2009-503182 (P2009-503182)

(86) (22) 出願日 平成19年3月23日 (2007.3.23)

(65) 公表番号 特表2009-531987 (P2009-531987A)

(43) 公表日 平成21年9月3日 (2009.9.3)

(86) 國際出願番号 PCT/US2007/064816

(87) 國際公開番号 WO2007/109793

(87) 國際公開日 平成19年9月27日 (2007.9.27)

審査請求日 平成20年9月24日 (2008.9.24)

(31) 優先権主張番号 11/389,443

(32) 優先日 平成18年3月23日 (2006.3.23)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔡田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】 Viterbi パック命令

## (57) 【特許請求の範囲】

## 【請求項 1】

Viterbi パック方法であつて、

第1のマスクされたデータを生成するために、第1のマスキング値を用いて第1のプレディケートレジスタのコンテンツをマスクし、第2のマスクされたデータを生成するために、第2のマスキング値を用いて第2のプレディケートレジスタのコンテンツをマスクすることと、

前記第1のマスクされたデータの選択されたビットと前記第2のマスクされたデータの選択されたビットとを目的レジスタ内へパックすることとを備える方法。

## 【請求項 2】

前記目的レジスタ内のビットは、前記第1のプレディケートレジスタのコンテンツの偶数ビットと、前記第2のプレディケートレジスタのコンテンツの奇数ビットとを備える請求項1に記載のViterbi パック方法。

## 【請求項 3】

前記パックすることの前に、前記第1のマスクされたデータと前記第2のマスクされたデータとの論理和をとることを更に備える請求項1に記載のViterbi パック方法。

## 【請求項 4】

前記第1のプレディケートレジスタのコンテンツをマスクすることは、前記第1のプレディケートレジスタのコンテンツと前記第1のマスキング値との論理積をとることを備え

、前記第2のプレディケートレジスタのコンテンツをマスクすることは、前記第2のプレディケートレジスタのコンテンツと前記第2のマスキング値との論理積をとることを備える請求項1に記載のViterbiパック方法。

【請求項5】

前記第1のマスキング値は16進法の55を備え、前記第2のマスキング値は16進法のAAを備える請求項4に記載のViterbiパック方法。

【請求項6】

ビットワイズ方式で動作する請求項1に記載のViterbiパック方法。

【請求項7】

Viterbiパック回路を有するデバイスであって、前記Viterbiパック回路が、

第1のプレディケートレジスタと、

第2のプレディケートレジスタと、

目的レジスタと、

少なくとも1つのメモリと、

前記第1のプレディケートレジスタに接続された第1の入力と、前記少なくとも1つのメモリに接続された第2の入力と、出力とを有する第1のANDゲートと、

前記第2のプレディケートレジスタに接続された第1の入力と、前記少なくとも1つのメモリに接続された第2の入力と、出力とを有する第2のANDゲートと、

前記第1のANDゲートの出力に接続された第1の入力と、前記第2のANDゲートの出力に接続された第2の入力と、前記目的レジスタに接続された出力とを有するORゲートと

を備えるデバイス。

【請求項8】

前記少なくとも1つのメモリが、第1のマスキング値と第2のマスキング値とを格納する請求項7に記載のデバイス。

【請求項9】

前記第1のマスキング値は16進法の55を備え、前記第2のマスキング値は16進法のAAを備える請求項8に記載のデバイス。

【請求項10】

デジタル信号プロセッサを更に備える請求項7に記載のデバイス。

【請求項11】

無線通信デバイスを更に備える請求項7に記載のデバイス。

【請求項12】

Viterbiパックを実行するように構成されたデバイスであって、

第1のマスクされたデータを生成するために、第1のマスキング値を用いて第1のプレディケートレジスタのコンテンツをマスクし、第2のマスクされたデータを生成するために、第2のマスキング値を用いて第2のプレディケートレジスタのコンテンツをマスクする手段と、

前記第1のマスクされたデータの選択されたビットと前記第2のマスクされたデータの選択されたビットとを目的レジスタ内へパックする手段と

を備えるデバイス。

【請求項13】

前記目的レジスタ内のビットは、前記第1のプレディケートレジスタのコンテンツの偶数ビットと、前記第2のプレディケートレジスタのコンテンツの奇数ビットとを備える請求項12に記載のデバイス。

【請求項14】

前記第1のマスクされたデータと前記第2のマスクされたデータとの論理和をとる手段を更に備える請求項12に記載のデバイス。

【請求項15】

10

20

30

40

50

前記第1のプレディケートレジスタのコンテンツと前記第1のマスキング値との論理積をとる手段と、

前記第2のプレディケートレジスタのコンテンツと前記第2のマスキング値との論理積をとる手段と

を更に備える請求項12に記載のデバイス。

【請求項16】

前記第1のマスキング値は16進法の55を備え、前記第2のマスキング値は16進法のAAを備える請求項15に記載のデバイス。

【請求項17】

デジタル信号プロセッサを更に備える請求項12に記載のデバイス。 10

【請求項18】

無線通信デバイスを更に備える請求項12に記載のデバイス。

【請求項19】

Vi te r b i パック方法の各ステップを実行するために機械によって実行可能な命令のプログラムを組み込んだ、前記機械によって読み取可能なプログラム記憶媒体であって、前記方法は、

第1のマスクされたデータを生成するために、第1のマスキング値を用いて第1のプレディケートレジスタのコンテンツをマスクし、第2のマスクされたデータを生成するために、第2のマスキング値を用いて第2のプレディケートレジスタのコンテンツをマスクすることと、 20

前記第1のマスクされたデータの選択されたビットと前記第2のマスクされたデータの選択されたビットとを目的レジスタ内へパックすることと

を備えるプログラム記憶媒体。

【請求項20】

前記目的レジスタ内のビットは、前記第1のプレディケートレジスタのコンテンツの偶数ビットと、前記第2のプレディケートレジスタのコンテンツの奇数ビットとを備える請求項19に記載のプログラム記憶媒体。

【請求項21】

前記方法は、前記パックすることの前に、前記第1のマスクされたデータと前記第2のマスクされたデータとの論理和をとることを更に備える請求項19に記載のプログラム記憶媒体。 30

【請求項22】

前記第1のプレディケートレジスタのコンテンツをマスクすることは、前記第1のプレディケートレジスタのコンテンツと前記第1のマスキング値との論理積をとることを備え、前記第2のプレディケートレジスタのコンテンツをマスクすることは、前記第2のプレディケートレジスタのコンテンツと前記第2のマスキング値との論理積をとることを備える請求項19に記載のプログラム記憶媒体。

【請求項23】

前記第1のマスキング値は16進法の55を備え、前記第2のマスキング値は16進法のAAを備える請求項22に記載のプログラム記憶媒体。 40

【請求項24】

前記方法がビットワイズ方式で動作する請求項19に記載のプログラム記憶媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、一般にVi te r b i パック命令に関する。特に、複数のプレディケートレジスタから単一の目的レジスタへビットをパックするVi te r b i パック命令に関する。

【背景技術】

【0002】 50

Viterbiアルゴリズムは、通信において便利なアルゴリズムである。Viterbiアルゴリズムは、無線通信システムにおいて、重畠コードを復号するために用いられることができる。このようなコードは、単なる一例として、符号分割多元接続（CDMA）、CDMA2000、広帯域符号分割多元接続（WCDMA）、時分割同期符号分割多元接続（TD-SCDMA）、及びグローバル・システム・フォー・モバイル・コミュニケーション（GSM）のような多数の形式の無線通信において用いられる。Viterbiアルゴリズムはまた、802.11無線ローカルアクセスネットワーク（WLAN）において、音声認識における誤り補正スキームとしても用いられ、その他多数の目的のために用いられることができる。

## 【0003】

10

Viterbiアルゴリズムを用いると、各状態へ導く複数のパスを伴う複数の状態が存在する状態のトレリスの中に、（しばしばViterbiパスと称される）最もありそうな隠蔽状態のシーケンスが見られる。状態間のどの遷移が（しばしば残存パスと称される）最もありそうな遷移かを決定するために、異なる遷移の可能性を比較することができる。残存パスは、トレリスにわたって、関連する状態遷移期間の各々に関して決定することができる。Viterbiデコーダでは、例えばトレースバックが、出力ビットを生成するために残存パスとともに後に実行される。

## 【0004】

Viterbiアルゴリズムを実行する場合、一般的に、異なる遷移の可能性を表すパスメトリックを生成し比較する。フラグビットは、このような比較の出力を表すことができる。この出力は、例えば後でトレースバックを実行する時に用いられるために、メモリ内に格納されうる。別々のレジスタからメモリ内へ書き込まれたいくつかの比較の結果を有することは、より多くのメモリを占有する。

20

## 【0005】

例えばWCDMA及びCDMA2000のような3G無線通信システムにおいて、もし2つのパスメトリックの比較の出力を表すフラグの各々が、メモリの別々のバイトに格納されれば、 $268 \times 256$ バイト = 68キロバイトのメモリが必要である。しかし、もしこれらのビットがバイトではなくビットとして格納されることができれば、 $268 \times 256 / 8 = 8$ キロバイトのメモリで済む。

## 【0006】

30

より多くのセーブ動作が必要とされることによって、速度に悪影響がもたらされる。これは、キャッシュミスの可能性を高くする。加えて、もしフラグが自然な順番で格納されなければ、トレースバックを実行するためにより多くのサイクルが必要である。

## 【0007】

Viterbiアルゴリズムは、例えば多数の無線通信システムで用いられる重畠コードを復号するために不可欠であるので、アルゴリズムの実行の速度は、例えば無線通信システムの実行に直接的に影響する。

## 【0008】

従って、処理時間を短縮しメモリスペースをセーブするために、複数のプレディケートレジスタ内のビットを单一の目的レジスタ内へパックするViterbiパック命令を提供することが有利であろう。

40

## 【発明の開示】

## 【発明の概要】

## 【0009】

Viterbiパック命令が開示される。Viterbiパック命令は、1つのプレディケートレジスタの選択されたビットと別のプレディケートレジスタの選択されたビットとを、单一の目的レジスタ内へパックすることを含む。

## 【0010】

特定の実施形態において、Viterbiパック命令は、第1のマスキング値を用いて第1のプレディケートレジスタのコンテンツをマスクし、第2のマスキング値を用いて第

50

2 のプレディケートレジスタのコンテンツをマスクする。その結果生じるマスクされたデータは、目的レジスタへ書き込まれる。別の特定の実施形態において、第 1 のマスキング値は 16 進法の 55 であり、第 2 のマスキング値は 16 進法の AA である。更なる特定の実施形態において、結果として生じるマスクされたデータは、目的レジスタへ書き込まれる前に、論理和をとられる。

【0011】

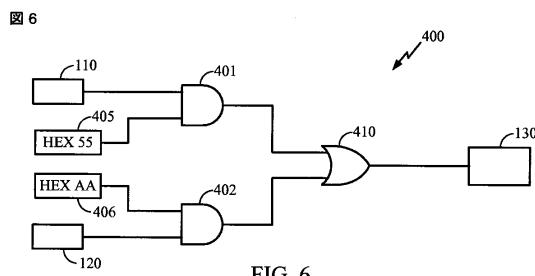

別の特定の実施形態において、Viterbi パック命令は、Viterbi パック回路を備える。Viterbi パック回路は、第 1 及び第 2 のプレディケートレジスタと、目的レジスタと、メモリと、第 1 及び第 2 の AND ゲートと、OR ゲートとを備える。

【0012】

また別の特定の実施形態において、Viterbi パック命令を動作させるデジタル信号プロセッサが開示される。別の特定の実施形態において、Viterbi パック命令を備える無線通信デバイスが開示される。

【0013】

本明細書に開示される 1 つ又は複数の実施形態の利点は、Viterbi アルゴリズムを実行する時間を低減することを含むことができる。

【0014】

本明細書に開示される 1 つ又は複数の実施形態の利点は、メモリスペースをセーブすることを含むことができる。

【0015】

別の利点は、無線通信システムにおける例えばセルラー電話のような無線通信デバイスに関するより短い取得時間を含むことができる。

【0016】

本開示のその他の局面、利点、及び特徴が、特許請求の範囲、詳細な説明、及び図面の簡単な説明を含む本出願全体を精査した後で明らかになるであろう。

【詳細な説明】

【0017】

本明細書に記載される実施形態の局面及びそれに伴う利点が、添付の図面と関連して考慮される場合、以下の詳細な説明の参照によってより容易に明らかになるであろう。

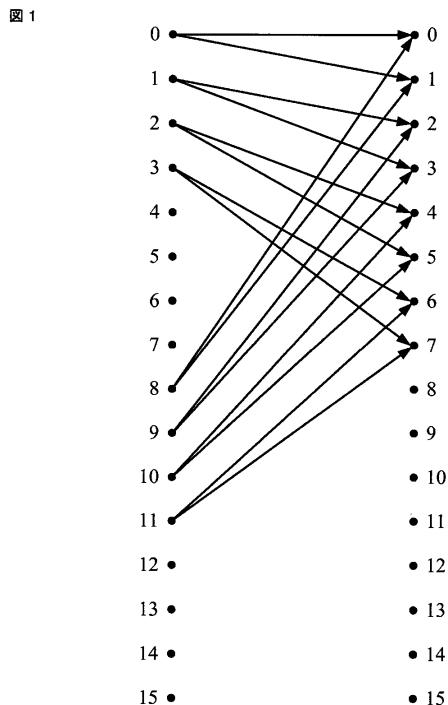

【0018】

図 1 は、例えば Viterbi アルゴリズムに関連するような状態のトレリスの例を示す。この例において、16 の起こりうる状態 (0 乃至 15) が示される。図示されるように、右側の状態 0 乃至 7 の各々は、左側の異なる 2 つの状態から到達することができる。例えば状態 0 は、状態 0 又は状態 8 の何れかから到達することができる。

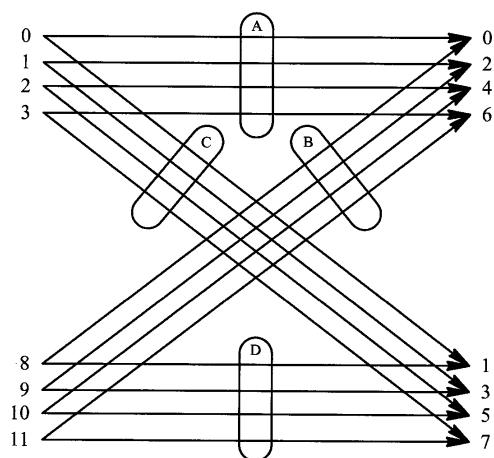

【0019】

図 2 は、図 1 に示す状態間の起こりうる遷移を示すベクトル図である。この例において、4 つのベクトル A 乃至 D が示される。ベクトル A は、状態 0、1、2 及び 3 から状態 0、2、4 及び 6 への遷移を表す。ベクトル B は、状態 8、9、10 及び 11 から状態 0、2、4 及び 6 への遷移を表す。ベクトル C は、状態 0、1、2 及び 3 から状態 1、3、5 及び 7 への遷移を表す。ベクトル D は、状態 8、9、10 及び 11 から状態 1、3、5 及び 7 への遷移を表す。

【0020】

上述したように、Viterbi アルゴリズムでは、最もありそうなパスが決定される。どのパスが最もありそうかを決定するために、異なる遷移ベクトルの可能性を比較するベクトル比較が用いられる。

【0021】

レジスタのコンテンツを比較することができる比較命令を有することが望ましい。汎用的な比較命令は、バイト比較、16 ビットハーフワード比較、ワード比較、及び長ワード比較を実行することができるので、様々な状況でアルゴリズムを用いることができる。このような比較命令を用いて、長ワードと他との比較によって、例えば、どの長ワードがよ

10

20

30

40

50

り大きいかを示す単一ビットの出力を生成することができる。2つのワードと他の2つのワードとの比較によって、各々がワード比較のうちの1つの結果を表す2ビットの出力を生成することができる。同様に、4つのハーフワード比較によって4ビットを生成し、8バイト比較によって8ビットを生成することができる。結果の格納を簡略化するために、各比較結果は、目的レジスタ内のデータのバイトへ書き込まれることができ、長ワード比較によって、結果ビットは、ただ1つのビットではなく目的レジスタ内のバイトの全てのビット内へ書き込まれることができる。ワード比較に関して、第1の結果ビットはバイトの最初の4ビットへ書き込まれ、第2の結果ビットは残りの4ビットへ書き込まれることができる。ハーフワード比較に関して、第1の結果ビットは最初の2ビットへ書き込まれ、第2の結果ビットは次の2ビットへ書き込まれ、と続くことができる。

10

#### 【0022】

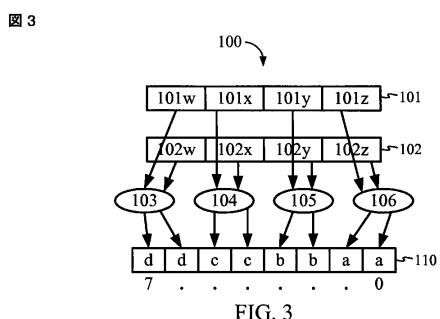

図3は、例えばViterbi復号中のように、Viterbiアルゴリズムとともに用いるのに便利な汎用ベクトル比較命令100の機能を示す。

#### 【0023】

Viterbi復号で用いられるベクトル比較命令100において、例えば、レジスタ101に格納されたAベクトルとレジスタ102に格納されたBベクトルとが比較され、その結果がプレディケートレジスタ110に格納される。ベクトル及びレジスタは、任意の適切なサイズであることができる。例えば、Aベクトル及びBベクトルの両者は、各ハーフワードが、図1及び図2に示す例えれば状態0から状態0のような状態遷移うちの1つのパスマトリックを表す4つの16ビットハーフワード101w乃至101z及び102w乃至102zからなることができる。Aベクトルは64ビットのレジスタ101に格納され、Bベクトルは64ビットのレジスタ102に格納されることができる。レジスタ101及びレジスタ102は、代わりに複数のレジスタとして実現されうる。例えば、一方又は両方のレジスタが、それぞれ2つの分離したレジスタから成ることができる。

20

#### 【0024】

図示されるように、各々がハーフワード101w乃至101zとハーフワード102w乃至102zとをそれぞれ比較する103乃至106を比較されたい。上述したように、汎用ベクトル比較命令は、プレディケートレジスタ110内の隣接する2つのビットに、比較103乃至106の各々に関する結果ビットを簡単に格納することができる。従って、比較103の結果であるビットdは、プレディケートレジスタ110のビット7及び6の両方へ書き込まれうる。同様に、ビットc、b及びaはそれぞれ、プレディケートレジスタ110の2つのビットへ書き込まれることができる。

30

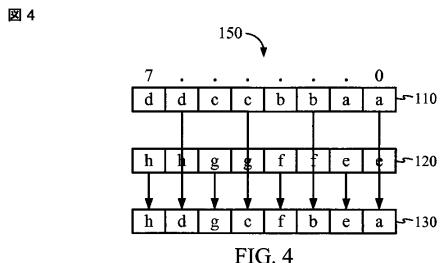

#### 【0025】

図4は、典型的なViterbiパック命令150の機能を示す。この限定的でない例において、プレディケートレジスタ110はベクトル比較命令100の結果を含み、プレディケートレジスタ120は、例えば他のベクトルC及びDを比較させるベクトル比較命令の結果を含む。Viterbiパック命令150では、2つのベクトル比較命令の結果を2つのレジスタ内に残さず、これらの結果は目的レジスタ130内へパックされる。目的レジスタ130は、例えば長さ8ビット又はそれより大きいサイズのような任意の適切なサイズであることができる。Viterbiパック命令150は、ソフトウェア、ファームウェア、ハードウェア、又はこれらの任意の組み合わせによって実現されることがある。

40

#### 【0026】

限定的でない実施形態において、Viterbiパック命令150は、以下のように表されることができる。

#### 【0027】

$$R_D = (P_0 \& 0 \times 55) | (P_1 \& 0 \times AA)$$

ここで $R_D$ は目的レジスタ130であり、 $P_0$ は第1のプレディケートレジスタ110であり、 $P_1$ は第2のプレディケートレジスタ120である。

#### 【0028】

50

このV i t e r b i パック命令150の限定的でない実施形態の実行中、プレディケートレジスタ110の偶数ビット(d、c、b及びa)は、目的レジスタ130の偶数ビット(ビット6、4、2及び0)内へ書き込まれる。加えて、プレディケートレジスタ120の奇数ビット(h、g、f及びe)は、目的レジスタ130の奇数ビット(ビット7、5、3及び1)内へ書き込まれる。従って、目的レジスタ130内のビットは、2つのプレディケートレジスタ110及び120内に格納されたビットを交互にする。このようにして、目的レジスタ130内のビットは、処理速度を上げるために、より自然な順番に配置される。

#### 【0029】

長ワード又はワードを比較するベクトル比較に関して、8つ又は4つのプレディケートレジスタが、各レジスタからのビットを交互にすることによって、目的レジスタ内の単一のバイトへパックされうることが留意されるべきである。 10

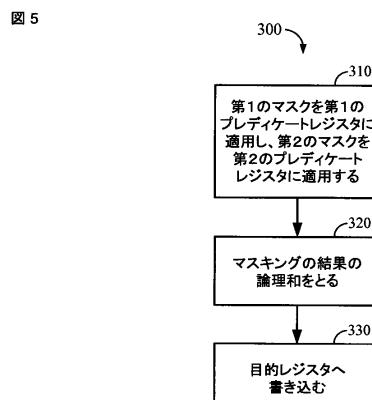

#### 【0030】

図5は、V i t e r b i パック方法を示す。方法300の限定的でない実施形態に従うと、ステップ310において、第1のマスキング値が第1のプレディケートレジスタ110のコンテンツに適用され、第2のマスキング値が第2のプレディケートレジスタ120のコンテンツに適用されることができる。例えば、第1のマスキング値は16進法の55であり、第2のマスキング値は16進法のAAでありうる。例えば長ワード比較又はワード比較が実行される場合のように、2つより多くのレジスタをパックするために、他の異なる16進法のマスキング値が用いられるであろう。 20

#### 【0031】

ステップ320において、2つのマスキングの結果生じるマスクされたデータは、両者の論理和をとられる。その後ステップ330において、論理和をとられたデータは、目的レジスタ130へ書き込まれる。これらのステップは、もし望まれれば、異なるビットに関して同時に起こるステップを伴ってビットワイズベースで起こることができる。

#### 【0032】

図6は、V i t e r b i パック回路400の限定的でない実施形態を示す。第1のプレディケートレジスタ110のコンテンツはANDゲート401へ送られ、例えばメモリ405に格納されうる16進法の55との論理積をとられる。第2のプレディケートレジスタ120のコンテンツはANDゲート402へ送られ、例えばメモリ406に格納されうる16進法のAAとの論理積をとられる。2つより多くのレジスタをパックするために、他の適切な16進法の値が用いられるであろう。メモリ405及びメモリ406は、単一のメモリ要素であるか、任意の適切なタイプの別々のメモリ要素であることができる。ANDゲート401及び402は、ORゲート410の入力に接続されている。ORゲート410の出力は、目的レジスタ130へ送られる。 30

#### 【0033】

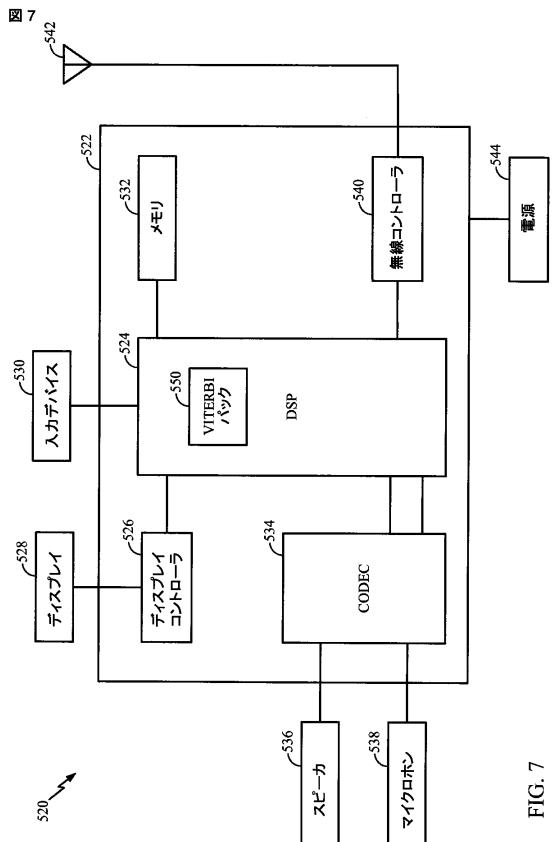

図7は、一般的に設計された無線通信デバイス520の限定的でなく典型的な実施形態を示す。無線通信デバイスは、デジタル信号プロセッサ524を含むシステム522を含む。ディスプレイコントローラ526は、デジタル信号プロセッサ524及びディスプレイ528に接続されている。更に、入力デバイス530は、デジタル信号プロセッサ524に接続されている。図示するように、メモリ532は、デジタル信号プロセッサ524に接続されている。加えて、符号器/復号器(CODEC)534が、デジタル信号プロセッサ524に接続されることができる。スピーカ536及びマイクロホン538は、CODEC530に接続されている。デジタル信号プロセッサ524は、図4乃至6で提供された任意のタイプの例であるV i t e r b i パック命令550を実行できるハードウェア又はファームウェアを含むか、又はソフトウェアを実行することができる。もしV i t e r b i パック命令550がソフトウェア形式であれば、ソフトウェアは代わりにメモリ532内に格納され、単にデジタル信号プロセッサ524で実行されることができる。 40

#### 【0034】

図7はまた、無線コントローラ540が、デジタル信号プロセッサ524及び無線アン

10

20

30

40

50

テナ 542 に接続されうることも示す。特定の実施形態において、システム 522 に、電源 544 が接続されている。ディスプレイ 528、入力デバイス 530、スピーカ 536、マイクロホン 538、無線アンテナ 542、及び電源 544 は、システム 522 に外付けでありうる。しかし、各々はシステム 522 の構成要素に接続されている。

#### 【0035】

当業者は更に、本明細書に開示された実施形態に関連して記載された、実例となる様々な論理ブロック、構成、モジュール、回路、及びアルゴリズムステップが、ハードウェア、ファームウェア、ソフトウェア、又はこれらの組み合わせとして実現されうることをよく理解するであろう。当業者は、各特定のアプリケーションのために上述した機能を様々な方法で実装することができるが、このような実現の決定は、本開示の範囲から逸脱させるものとして解釈されてはならない。 10

#### 【0036】

本明細書で開示された実施形態に関連して記述された方法やアルゴリズムのステップは、ハードウェアによって直接的に、ファームウェアによって、プロセッサによって実行されるソフトウェアモジュールによって、又は、これらの組み合わせによって具現化される。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、PRO ROMメモリ、EEPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、あるいは当該技術で知られているその他の形式の記憶媒体に収納されうる。典型的な記憶媒体は、プロセッサがそこから情報を読み取り、またそこに情報を書き込むことができるようプロセッサに結合されうる。プロセッサ及び記憶媒体は、ASIC 内に存在することができる。ASIC は、計算デバイス又はユーザ端末内に存在することができる。あるいはプロセッサ及び記憶媒体は、計算デバイス又はユーザ端末内のディスクリート部品として存在することができる。 20

#### 【0037】

開示された実施形態における上記記載は、当業者をして、本開示の製造又は利用を可能とするために提供される。これらの実施形態への様々な変形例もまた、当業者に対しては明らかであって、本明細書で定義された一般原理は、本開示の主旨又は範囲から逸脱することなくその他の実施形態にも適用されうる。従って、本開示は、本明細書に開示された実施形態に限定することは意図されておらず、請求項によって定義されたような原理及び新規特徴と整合が取れた最も広い範囲と一致するように意図されている。 30

#### 【図面の簡単な説明】

#### 【0038】

【図1】図1は、Viterbiアルゴリズムに関する典型的な状態図である。

【図2】図2は、図1の状態図に基づくベクトル図である。

【図3】図3は、ベクトル比較命令を示す機能図である。

【図4】図4は、Viterbiパック命令を示す機能図である。

【図5】図5は、Viterbiパック命令の方法を示すフローチャートである。

【図6】図6は、Viterbiパック命令回路を示す論理図である。

【図7】図7は、図4乃至6の任意のViterbiパック命令を組み込む無線通信デバイスの図である。 40

【 図 1 】

FIG. 1

【 図 2 】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【 図 5 】

FIG. 5

【 6 】

FIG. 6

【図7】

FIG. 7

---

フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100100952

弁理士 風間 鉄也

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100070437

弁理士 河井 将次

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 ジェング、マオ

アメリカ合衆国、テキサス州 78759、オースティン、テイラー・ドレイパー・レーン 11

250、ナンバー 1022

(72)発明者 コドレスキュ、ルシアン

アメリカ合衆国、テキサス州 78726、オースティン、グラシアーパーク・コーブ 125

05

審査官 上田 翔太

(56)参考文献 特表2002-521907(JP, A)

米国特許第04012722(US, A)

(58)調査した分野(Int.Cl., DB名)

H03M 13/41