(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

11) N° de publication :

*2 634 604*

là n'utiliser que pour les commandes de reproduction

(21) N° d'enregistrement national :

89 09994

(51) Int CI5: H 03 F 1/34, 31/14.

RATION. -- US.

## (2) DEMANDE DE BREVET D'INVENTION

**A1**

- (22) Date de dépôt : 25 juillet 1989.

- (30) Priorité: US, 25 juillet 1988, nº 07/223 796.

- (72) Inventeur(s): Anthony D. Wang; Robert Mark Stitt II.

(71) Demandeur(s): Société dite: BURR-BROWN CORPO-

- (43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 4 du 26 janvier 1990.

- Références à d'autres documents nationaux apparentés :

- (73) Titulaire(s):

- (74) Mandataire(s): Rinuy et Santarelli.

- Procédé de commande des corrections effectuées par un circuit de polarisation sur un étage d'entrée d'un amplificateur à bande large et cet amplificateur.

- (57) L'invention concerne un amplificateur à bande large à circuit intégré.

Il comprend deux circuits miroirs de courant détectant les courants d'émetteurs de transistors NPN et PNP 1, 2 de l'étage de sortie 21 de l'amplificateur. Les courants d'émetteurs sont divisés d'un facteur de 20, additionnés et environ 1/20 du courant total passe à travers un transistor 45 dont le collecteur est connecté à la grille d'un transistor 64 à effet de champ d'un circuit de commande de polarisation pour produire un courant de réaction réduit.

Domaine d'application : amplificateurs à bande large à circuits intégrés, etc.

L'invention concerne des amplificateurs à bande large, et plus particulièrement un circuit de commande de polarisation pouvant être mis en oeuvre avec un condensateur de compensation assez petit pour être intégré dans un circuit intégré monolithique.

On connaît un grand nombre de circuits amplificateurs à bande large, tels que ceux décrits dans les brevets des Etats-Unis d'Amérique N° 4 358 739 et N° 4 502 020. Tous les circuits amplificateurs à bande 10 large de l'art antérieur (ainsi que le circuit de la présente invention) exigent des circuits de polarisation d'entrée qui détectent le courant circulant dans l'étage à gain symétrique pour générer une réaction pour le circuit de polarisation d'entrée. En réponse à la réaction, le 15 circuit de polarisation génère des tensions de polarisation pour l'étage d'entrée afin d'empêcher une dérive résultant de variations affectant la dissipation de puissance dans l'étage de sortie. La correction par réaction empêche des accroissements des courants dans les transistors de sortie 20 par suite de baisses, dues à la température, de la tension base-emetteur  $\mathbf{V}_{\mathrm{RE}}$  des transistors de sortie. Ces tensions V<sub>BE</sub> diminuées, en l'absence d'une compensation, pourraient provoquer un "emballement thermique" des courants des transistors de sortie, aboutissant à une destruction de ces 25 transistors de sortie.

Les circuits de réaction de polarisation des amplificateurs à bande large de l'art antérieur ont toujours une réponse l'ente à des variations détectées du courant dans les transistors de sortie de l'étage symétri30 'que de sortie. La lenteur de la réponse empêche le circuit de polarisation d'interagir avec le comportement à haute fréquence de l'étage d'entrée de l'amplificateur à bande large. Dans tous les amplificateurs à bande large de l'art antérieur, de très gros condensateurs de compensation, ayant des capacités d'au moins environ 0,01 microfarad,

sont nécessaires pour produire la lenteur demandée de la réponse de la réaction. Malheureusement, il est tout à fait impossible de placer sur un circuit intégré monolithique ou hybride un tel condensateur de forte dimension. Par conséquent, des broches supplémentaires de boîtiers et de gros condensateurs extérieurs sont nécessaires dans les amplificateurs à bande large à circuit intégré de l'art antérieur.

Un objet de l'invention est donc de proposer un circuit intégré amplificateur à bande large comportant un condensateur interne de compensation du circuit de polarisation.

Un autre objet de l'invention est de proposer un circuit intégré amplificateur à bande large qui 15 fonctionne de façon fiable avec un condensateur interne de compensation du circuit de polarisation dans son circuit de réaction de polarisation d'entrée.

Brièvement décrite et selon une forme de réalisation, l'invention propose un circuit de réaction de 20 polarisation d'entrée dans un amplificateur pouvant fonctionner avec une capacité de compensation assez basse pour qu'un condensateur de compensation puisse être incorporé sur une microplaquette à circuit intégré, avec l'amplificateur. Dans une forme de réalisation de l'inven-25 tion, un premier circuit miroir de courant est utilisé pour détecter un courant d'émetteur d'un premier transistor dans un étage de sortie de l'amplificateur. Un courant de réaction, qui est égal à un certain pourcentage du courant miroir, est amené à circuler à travers un second transistor 30 ayant une impédance de sortie très élevée. Un courant de référence est appliqué par une source de courant à haute impédance et le courant de réaction est comparé au courant de référence pour produire un signal d'erreur. Le signal d'erreur est appliqué à une borne d'entrée à haute impédance d'un circuit de polarisation à courant continu

qui règle une tension continue de polarisation appliquée à un étage de sortie de l'amplificateur afin de rendre le courant de réaction égal au courant de référence. Le signal d'erreur est compensé par le condensateur de compensation. 5 Dans la forme de réalisation décrite de l'invention, un courant d'émetteur d'un second transistor de l'étage de sortie est détecté au moyen d'un second circuit miroir de courant pour produire un second courant miroir. Une réplique inversée du premier courant miroir fait l'objet 10 d'une sommation avec le second courant miroir pour produire un courant de réaction est une certaine fraction des courants miroirs additionnés. Le courant de réaction circule à travers un transistor ayant une haute impédance de sortie et fait l'objet d'une sommation avec un courant 15 de référence provenant de la source de courant à haute impédance.

L'invention sera décrite plus en détail en regard des dessins annexés à titre d'exemple nullement limitatif et sur lesquels :

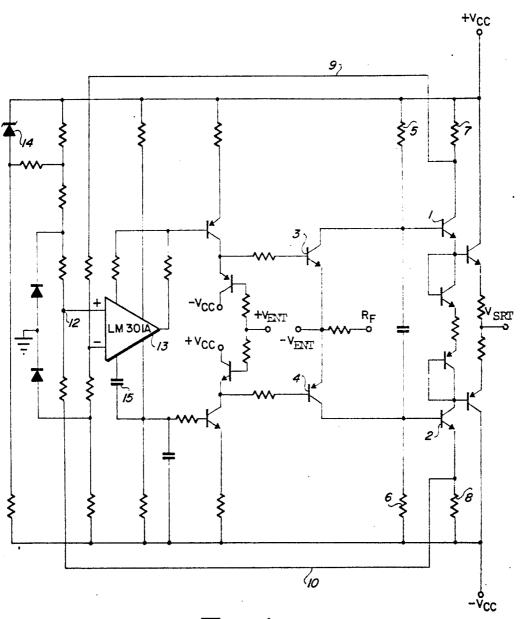

la figure 1 est un schéma d'un circuit de l'art 20 antérieur utile pour une comparaison avec la présente invention ; et

25

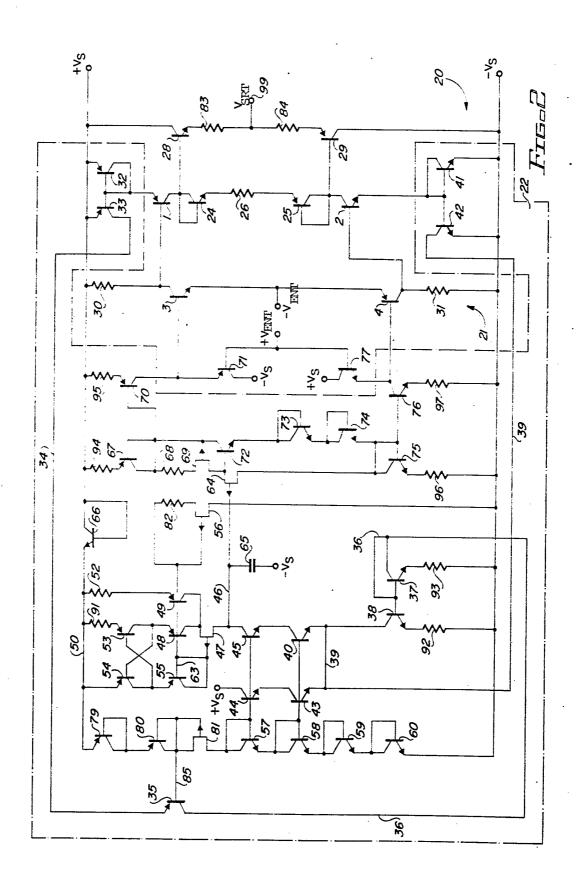

la figure 2 est un schéma de l'amplificateur à bande large de la présente invention.

Avant de décrire la forme de réalisation actuellement préférée de l'invention en regard de la figure 2, il est utile de décrire brièvement le circuit de l'art antérieur, montré sur la figure 1, pour mieux comprendre les particularités inédites de la présente invention. La 30 figure 1 montre un circuit de l'amplificateur à bande large "COMLINEAR CLC300A". Son étage de sortie symétrique comprend un transistor PNP 1 et un transistor NPN 2, dont les collecteurs sont couplés par deux diodes et une résistance. Des transistors 3 et 4 et des résistances 5 et 35 6 maintiennent des tensions de polarisation sur les bases des transistors 1 et 2. Pour ajuster les tensions de polarisation appliquées aux entrées du circuit d'attaque de sortie symétrique NPN/PNP produisant la tension de sortie  $V_{\rm SRT}$ , des résistances 7 et 8 connectent les émetteurs des transistors 1 et 2, respectivement, à +V $_{\rm CC}$  et -V $_{\rm CC}$  et détectent les courants d'émetteurs circulant à travers les transistors 1 et 2, respectivement.

On peut aisément voir que si le courant circulant à travers la résistance 5, le transistor 3, le 10 transistor 4 et la résistance 6 est relativement constant, un brusque accroissement de la dissipation de puissance dans la zone des transistors 1 et 2 amène les tensions  $V_{\mathrm{RF}}$ des transistors 1 et 2 à décroître, provoquant une élévation du courant traversant les transistors 1 et 2. 15 Ceci élève encore leur température et tend à provoquer un emballement thermique à moins que des corrections correspondantes soient apportées à une tension de polarisation appliquée entre les bases des transistors 1 et 2. Les conducteurs 9 et 10 transmettent les élévations de tension à travers les résistances 7 et 8 du fait de ces diminutions des tensions  $V_{\rm EE}$  des transistors 1 et 2, produisant un signal de réaction entre les entrées d'un amplificateur opérationnel 13. La sortie de l'amplificateur opérationnel 13 génère une tension de correction qui est appliquée entre les bases des transistors 3 et 4 afin de compenser la diminution des tensions  $\mathbf{V}_{\mathrm{BE}}$  des transistors 1 et 2. Dans ce circuit, un condensateur 15 de compensation de polarisation doit avoir une valeur d'au moins environ 0,01 microfarad pour éviter divers problèmes tels qu'une modulation du 30 courant d'alimentation au repos, une dérive de la tension de décalage d'entrée, des variations des tensions et des courants internes de polarisation qui peuvent affecter des paramètres en régime alternatif tels que la largeur de bande et le temps de stabilisation, et ce condensateur ne 35 peut donc pas être inclus dans une microplaquette unique à circuit intégré, avec le reste de l'amplificateur à bande large.

En référence à présent à la figure 2, un amplificateur 20 à bande large à circuit intégré mono

5 lithique comprend un étage amplificateur 21 qui comporte un circuit classique très semblable à l'étage amplificateur du circuit de l'art antérieur montré sur la figure 1.

L'amplificateur 20 à bande large comprend aussi le circuit 22 de polarisation de réaction de la présente invention.

10 L'étage amplificateur 21 comprend un transistor PNP 70 dont l'émetteur est couplé par une résistance de 1,2 kilohm à +V<sub>S</sub> et dont le collecteur est connecté à l'émetteur d'un transistor PNP 71. Le collecteur du transistor 70 est également connecté a la base du transistor NPN 3. Le transistor 71 est connecté par son collecteur à -V<sub>S</sub> et sa base est couplée à +V<sub>ENT</sub>.

Un transistor NPN 76 est connecté par son émetteur à  $-V_S$  par l'intermédiaire d'une résistance de 1,2 kilohm et son collecteur est connecté à l'émetteur d'un 20 transistor NPN 77. Le collecteur du transistor 76 est également connecté à la base du transistor PNP 4. Le collecteur du transistor 77 est connecté à  $+V_S$  et sa base est couplée à  $+V_{ENT}$ . Les émetteurs des transistors 3 et 4 sont connectés à  $-V_{ENT}$ .

Le collecteur du transistor 3 est connecté par une résistance 30 de 1,2 kilohm à  $+V_S$  et à la base du transistor PNP 1. De façon similaire, le collecteur du transistor 4 est connecté par une résistance 31 de 1,2 kilohm à  $-V_S$  et à la base du transistor NPN 2.

25

Le collecteur du transistor 1 est connecté à la base d'un transistor NPN 28 et au collecteur et à la base d'un transistor NPN 24 connecté en diode, dont l'émetteur est connecté à une borne d'une résistance 26 de 16,25 ohms, l'autre borne de cette résistance étant l'émetteur d'un transistor PNP 25 connecté en diode. La base et le

collecteur du transistor 25 sont connectés à la base d'un transistor PNP 29 d'attaque de sortie et au collecteur du transistor 2. Le collecteur du transistor NPN 28 d'attaque de sortie est connecté à  $+V_S$  et son émetteur est connecté par une résistance 83 de 3,25 ohms à  $V_{\rm SRT}$ . Le collecteur du transistor 29 est connecté à  $-V_S$  et son émetteur est connecté par une résistance 84 de 3,25 ohms à  $V_{\rm SRT}$ .

Conformément à la présente invention, courants d'émetteurs des transistors 1 et 2 ne sont pas 10 détectés par des résistances telles que 7 et 8 sur la figure 1. Par contre, le courant d'émetteur du transistor 11 circule dans un circuit PNP mircir de courant comprenant des transistors 32 et 33. La surface d'émetteur du transistor 32 peut être 20 fois celle du transistor 33, 15 bien que le rapport exact ne soit pas essentiel. Le collecteur et la base du transistor 32 sont connectés à l'émetteur du transistor 1. Les émetteurs des transistors 32 et 33 sont connectés à +Vs. Le collecteur du transistor 33 est connecté par un conducteur 34 à l'émetteur d'un 20 transistor PNP 35 qui fait partie du circuit de réaction de polarisation. Par conséquent, le courant passant dans le conducteur 34 est égal à 1/20 du courant d'émetteur du transistor 1.

Similairement, un circuit NPN miroir de courant comprenant des transistors NPN 41 et 42 reflète une valeur réduite (c'est-à-dire d'un facteur de 20) du courant d'émetteur du transistor 2 vers le circuit de réaction de polarisation. Le collecteur et la base d'un transistor NPN 41 sont connectés à l'émetteur du transistor 2 et à la base d'un transistor NPN 42. Les émetteurs des transistors 41 et 42 sont connectés à -V<sub>S</sub>. Le collecteur du transistor 42 est connecté par un conducteur 39 au circuit de polarisation par réaction qui comprend les transistors 35, 37, 38, 40, 43, 45 et 47 et le condensateur de compensation 65.

La base du transistor 35 est connectée par un conducteur 85 au collecteur et à la base d'un transistor PNP 80 et à la grille et à la source d'un transistor JFET 81. (Il convient de noter que tous les transistors à effet de champ à jonctions JFET décrits ici sont des transistors JFET à canal P). L'émetteur du transistor 80 est connecté au collecteur et à la base d'un transistor PNP 79 dont l'émetteur est connecté à un conducteur 50. Le drain du transistor JFET 81 est connecté au collecteur et à la base d'un transistor JFET 81 est connecté au collecteur et à la base 10 d'un transistor NPN 57 dont l'émetteur est connecté en série avec des transistors 58, 59 et 60 montés en diodes.

L'émetteur d'un transistor 48 est connecté au collecteur d'un transistor PNP 53 et à la base d'un transistor PNP 54. Le collecteur du transistor 48 est 15 connecté à la source d'un transister JFET 47 et au collecteur d'un transistor NPN 49. L'émetteur d'un transistor 55 est connecté à la base du transistor 53 et au collecteur du transistor 54. L'émetteur du transistor 54 est connecté au conducteur 50. L'émetteur du transistor 53 20 est connecté par une résistance 91 de 8,87 kilohms au conducteur 50. L'émetteur du transistor 49 est connecté par une résistance 52 de 84,95 kilohms au conducteur 50 qui est connecté à l'émetteur d'un transistor NPN 66 monté en diode. Le collecteur et la base du transistor 66 sont 25 connectés à  $+V_S$ . Les bases des transistors 48, 49 et 55 sont connectées par un conducteur 63 à la grille d'un transistor JFET 56. La source du JFET 56 est connectée par une résistance 82 de 1,5 kilohm à un conducteur 63. Le drain du JFET 56 est connecté à  $-V_S$ .

30 'Le drain du JFET 47 est connecté par un conducteur 46 à une borne d'un condensateur 65 de compensation de 350 picofarads dont l'autre borne est connectée à -Vs. Le conducteur 46 est également connecté à la grille d'un JFET 64 dont la source est connectée au drain d'un 35 JFET 69 et à la base d'un transistor NPN 72.

Le collecteur du transistor 35 est connecté par un conducteur 36 au collecteur et à la base d'un transistor NPN 37 et à la base d'un transistor NPN 38 dont les émetteurs sont connectés par des résistances de 0,3 kilohm 5 à -Vs. Les surfaces des transistors 37 et 38 et les valeurs des résistances 92 et 93 peuvent être égales, auquel cas le courant circulant dans le conducteur 36 et à travers le transistor 37 est reflété de façon inchangée à travers le collecteur du transistor 38 et fait l'objet d'une sommation 10 à la connexion du conducteur 39 sur le collecteur du transistor 38 avec le courant circulant sur le conducteur 39 et dans le collecteur du transistor NPN 42. Le conducteur 39 est connecté aux émetteurs des transistors NPN 40 et 43, dont les bases sont connectées à la base et au 15 collecteur d'un transister NPN 58 monté en diode. Les transistors 58, 59 et 60 montés en diodes maintiennent la base du transistor 58 à trois tensions  $V_{\mathrm{BE}}$  au-dessus de -Vs.

Le collecteur du transistor 40 est connecté à 1'émetteur d'un transistor NFN 45 dont le collecteur est connecté au drain du JFET 47. La base du transistor 45 est connectée à la base d'un transistor NPN 44, dont le collecteur est connecté à +V<sub>S</sub> et dont l'émetteur est connecté au collecteur du transistor NPN 43. La base du 25 transistor 45 est également connectée à la base et au collecteur d'un transistor NPN 57 monté en diode.

Le collecteur d'un transistor NPN 72 est connecté à la grille d'un transistor JFET 69 et à la base d'un transistor PNP 70, et au collecteur et à la base du 30 transistor 67. La source du JFET 69 est connectée par une résistance de 2 kilohms au collecteur et à la base d'un transistor PNP 67 monté en diode, dont l'émetteur est connecté par une résistance 94 de 0,6 kilohm à +Vs. L'émetteur du transistor 70 est connecté par une résistance 95 de 0,6 kilohm à +Vs.

Un transistor NPN 73 monté en diode est connecté en série entre l'émetteur d'un transistor 72 et le collecteur et la base d'un transistor NPN 74 monté en diode dont l'émetteur est connecté à la base d'un transistor NPN 5 76 et au collecteur et à la base d'un transistor NPN 75 monté en diode, ainsi qu'au drain d'un transistor JFET 64. L'émetteur du transistor 75 est connecté par une résistance 96 de 0,6 kilohm à -Vs. L'émetteur du transistor 76 est connecté par une résistance 97 de 0,6 kilohm à -Vs.

Le circuit 22 de polarisation de réaction peut être analysé à la manière d'un jeu de blocs. Les premiers blocs comprennent les transistors 32 et 33 miroirs de courant et les transistors 41 et 42. Le miroir de courant PNP, comprenant les transistors 32 et 33, prélève le 15 courant d'émetteur du transistor 1 et en reproduit une partie à échelle réduite sur le conducteur 34. Similairement, le miroir de courant NPN, constitué des transistors 41 et 42, prélève le courant d'émetteur du transistor 2 et le reproduit à échelle réduite sur le conducteur 39. Le 20 facteur d'échelle de ce circuit est de 1/20 et est le même pour les deux miroirs.

10

Le transistor 66 établit simplement une chute de diode entre +Vs et la source de courant de bande interdite (transistors 54, 53, 55, 48, 49, JFET 47, JFET 56 25 et résistances 82, 52 et 91) et la suite de polarisations par diode (transistors 79, 80, JFET 81, transistors 57, 58, 59 et 60). Ceci est effectué pour laisser une "garde" suffisante entre l'émetteur du transistor 35 et le collecteur du transistor 33 afin que le dernier dispositif ne 30 sature pas lors de la mise en marche initiale.

Les transistors 79, 80, le JFET 81, transistors 57, 58, 59 et 60 produisent une polarisation pour d'autres éléments du circuit 22 de polarisation. Le JFET 81 est connecté de façon que sa grille soit liée à sa 35 source, ce qui en fait une source de courant autopolarisée pour les autres transistors montés en diodes dans cette suite.

La source de courant de bande interdite est composée de transistors 54, 53, 55, 48, 49, JFET 47, JFET 56 et de résistances 82, 52 et 91. Les transistors 54, 53, 55, 48 et la résistance 91 produisent un courant qui croît avec la température, tandis que le transistor 49 et la résistance 52 produisent un courant qui décroît avec la température. Ces deux courants font l'objet d'une sommation dans la source du transistor JFET 47. Le drain du JFET 47 fournit un courant ayant un coefficient de température égal à zéro ou presque, tout en présentant en même temps une impédance de sortie très élevée. Le JFET 56 est connecté par sa source à une résistance 82 dont l'autre extrémité est connectée à la grille de ce JFET afin de constituer une source de courant autopolarisée de faible valeur pour la mise en marche de la source de courant de bande interdite.

Le transistor 35 est en série avec le transistor 33 pour produire à travers le transistor 33 une

20 polarisation base-collecteur comparable à celle qui

apparaît à travers le transistor 42. Celui-ci agit aussi à

la manière d'un cascode pour empêcher une variation du

courant fourni au transistor 37 lorsque les tensions

d'alimentation varient ; ceci est dû à l'effet Early connu

25 de l'homme de l'art. Les transistors 37 et 38 et les

résistances 92 et 93 forment un autre miroir de courant qui

convertit le courant provenant du transistor 35 et donc du

transistor 33 à la même polarité que celle du courant

provenant du transistor 42. Ces courants font l'objet d'une

30 sommation aux connexions d'émetteurs des transistors 40 et

Les transistors 40 et 43 se partagent une tension V<sub>BE</sub> commune et sont donc proportionnés. Dans ce cas, la surface d'émetteur du transistor 43 est 19 fois plus grande que l'émetteur du transistor 40 et transmet

donc 19 fois le courant de l'émetteur du transistor 40. Essentiellement, la somme des courants à la connexion 39 est divisée par 20 à sa sortie du collecteur du transistor 40. Le transistor 45 agit à la manière d'un cascode pour 5 élever l'impédance de sortie sur le conducteur 46 auquel la source de courant de bande interdite est également reliée. Un transistor 44 oblige la tension collecteur-base du transistor 43 à être égale à celle du transistor 40, ce qui minimise les erreurs induites par l'effet Early.

10

Un JFET 64, un JFET 69, des transistors 72, 73 et 74 et une résistance 68 forment une source de courant commandée en tension. Le JFET 69, à la source duquel est connectée une résistance 68 dont l'autre extrémité est connectée à sa grille, forme une source de courant 15 autopolarisée de valeur modérée. Il sert à fournir un courant de polarisation pour le JFET 64 et un courant de base pour le transistor 72. Le JFET 64 agit à la manière d'une source asservie pour attaquer la base du transistor 72. Lorsque la tension de grille du JFET 64 s'élève, elle 20 oblige le transistor 72 à transmettre davantage de courant. Les transistors 73 et 74 agissent à la manière de dispositifs de rétablissement de niveau pour maintenir la tension de grille du JFET 64 assez élevée pour empêcher le transistor 45 d'arriver à saturation.

Le courant provenant de la source de courant 25 commandée en tension (JFET 64, JFET 69, transistors 72, 73 et 74 et résistance 68) pénètre dans les miroirs de courant 67, 70 et dans des résistances 94 et 95 à la barre d'alimentation positive, et dans des transistors 75 et 76 30 et des résistances 96 et 97 à la barre d'alimentation négative. Ces miroirs de courant alimentent l'amplificateur 21 à bande large. Bien que cela ne soit pas réalisé dans ce circuit, les miroirs peuvent être proportionnés. Par exemple, l'un pourrait tendre à réduire le courant appelé 35 par la source de courant commandée en tension.

En fonctionnement, le circuit de réaction de polarisation fonctionne de la façon suivante. Le courant d'émetteur du transistor de gain 1 passe à travers le transistor 32 et est reflété à travers le transistor 33 5 pour produire un courant reflété ou courant miroir dans le conducteur 34, lequel courant est réduit d'un facteur de 20 par rapport au courant d'émetteur du transistor 1. Ce courant réduit circule à travers le transistor 35 et le conducteur 36 pour arriver au transistor miroir de courant 10 NPN 37. Ce courant est reflété d'un facteur de 1 pour produire un courant de même amplitude circulant dans le collecteur et l'émetteur du transistor 38 pour arriver à -Vs. En fait, le "sens" du courant circulant dans le collecteur du transistor 33 a été "inversé" de manière 15 qu'il "se dissipe" à présent en -VS au lieu d'être "débité" par +Vg. Il fait ensuite l'objet d'une "sommation" conducteur 39, avec le courant reflété, réduit, circulant sur le conducteur 39 à travers le collecteur du transistor miroir de courant 42, qui, également, se "dissipe" dans 20 -Vg. Le courant de collecteur du transistor 42 est obtenu à partir du courant d'émetteur du transistor 2 d'une manière similaire.

La somme des deux courants reflétés, réduits, des transistors 1 et 2 est donc divisée de façon que 19/20 25 de ce courant circule à travers le transistor 43 et 1/20 circule à travers le transistor 40. Par conséquent, 1/400ème de la somme des courants circulant dans les émetteurs des transistors 1 et 2 s'écoule à travers le transistor 45 (le rapport de 1/400ème n'est pas critique, pourvu que l'impédance du conducteur 45 impose une charge très élevée au drain du JFET 47 et au collecteur du transistor 45). Avec ce courant très faible circulant à travers son collecteur, le transistor 45 présente une impédance de collecteur très élevée.

En fonctionnement, le miroir de courant comprenant les transistors 32 et 33 détecte tout accroissement de courant à travers le transistor 1 dû à une élévation locale de température et à la réduction résul-5 tante du "seuil"  $V_{\mathrm{BE}}$ , et réduit d'un facteur de 20 cette augmentation de courant. Similairement, le miroir de courant comprenant les transistors 41 et 42 détecte et réduit d'un facteur de 20 les augmentations de courant dans le transistor 2. L'accroissement total du courant circulant 10 à travers les transistors 1 et 2, déjà réduit d'un facteur de 20, est encore divisé par 20, car 1/20 de ce courant circule à travers les transistors 40 et 45. Le courant passant dans le collecteur du transistor 45 est ensuite comparé à un courant de référence produit par la source de 15 courant de référence de bande interdite et un ajustement correspondant est réalisé sur la tension de polarisaton appliquée entre les bases des transistors 3 et 4 afin d'amener le courant circulant dans le collecteur du transistor 45 à correspondre à l'amplitude de référence 20 traversant le JFET 47.

Comme mentionné précédemment, les impédances de sortie du collecteur du transistor 45 et du drain du JFET 47 sont très élevées. L'impédance, en regardant dans la grille du JFET 64, est également très élevée. Etant donné que les trois éléments sont tous connectés à un noeud 46, l'impédance relevée à ce noeud est très élevée. Ceci constituerait alors le point idéal pour connecter un condensateur afin de limiter la réponse en fréquence du circuit de réaction. Le condensateur Cc de 350 picofarads est connecté entre ce noeud et la tension d'alimentation négative -V<sub>S</sub>. Cette connexion, en plus de limiter la réponse du circuit à environ 9,7 hertz, permet une réjection accrue de l'alimentation de puissance car toute fluctuation de l'alimentation négative est transmise au noeud 46. Cette capacité peut être aisément intégrée dans

la microplaquette à circuit intégré que celle portant la partie restante de l'amplificateur à bande large.

Par conséquent, le pôle de très basse fréquence d'environ 10 hertz est établi pour le circuit de réaction 5 afin que le fonctionnement du circuit de réaction de polarisation ne produise aucune interférence notable avec le comportement à haute fréquence de la section 21 constituée par l'amplificateur à bande large.

L'ajustement, provoqué par la réaction, de la 10 tension de polarisation appliquée entre les bases des transistors 3 et 4 pourrait peut-être être mieux compris en supposant que le courant traversant le JFET supérieur à celui traversant la résistance 45. Le courant excédentaire arrivant dans le conducteur 46 élève alors la 15 tension du conducteur 46. Le JFET 64 à source asservie élève la tension sur la base du transistor 72, augmentant le courant traversant ce transistor 72 et, par conséquent, augmentant aussi le courant traversant les transistors 70 et 76. Ceci élève la tension de polarisation appliquée 20 entre les bases des transistors 3 et 4, ce qui accroît les courants traversant les transistors 1 et 2. Les courants accrus traversant les transistors 1 et 2 sont renvoyés par effet de miroir par des conducteurs 34 et 39 et font l'objet d'une sommation, comme expliqué précédemment. Par 25 conséquent, le courant passant dans le collecteur transistor 45 augmente jusqu'à ce qu'il corresponde au courant de drain du JFET 47. Il convient de noter que des circuits de polarisation autres que ceux représentés peuvent être utilisés. Par exemple, la Demanderesse 30 développe un circuit de polarisation à tension de décalage d'entrée égale à zéro.

Dans la forme de réalisation de circuit intégré monolithique du circuit de la figure 2, la capacité Cc de 350 picofarads occupe une surface qui n'est que d'environ 35 0,724 mm par 0,724 mm. Par contre, un condensateur de

0,01 microfarad, exigé par l'art antérieur, demanderait une surface de 3,87 par 3,87 mm s'il était réalisé sur la même microplaquette monolithique.

L'invention décrite ci-dessus propose un circuit de commande de réaction de polarisation relativement simple pour le circuit amplificateur à bande large sans la nécessité d'un condensateur extérieur de compensation, tout en évitant l'effet précité d'interaction entre le fonctionnement du circuit de réaction par polarisation et les caractéristiques de l'amplificateur à bande large.

Il convient de noter que l'expression "étage de sortie" telle qu'utilisée ici entend englober à la fois un circuit à gain (tel que celui comprenant les transistors 1 et 2) et/ou un circuit tampon de sortie (tel que celui comprenant les transistors 28 et 29), de manière que l'étage de sortie soit disposé entre les sorties d'un étage de circuit antérieur (tel que celui comprenant les transistors 3 et 4) et une borne de sortie, telle que la borne 99 V<sub>CDD</sub>.

20 Il va de soi que de nombreuses modifications peuvent être apportées au procédé et à l'amplificateur décrits et représentés sans sortir du cadre de l'invention.

## REVENDICATIONS

- 1. Procédé de commande des corrections effectuées par un circuit de polarisation (22) sur un étage d'entrée d'un amplificateur (20) à bande large, caractérisé en ce qu'il consiste :

- (a) à détecter un courant d'émetteur d'un premier transistor (1, 2) d'un étage de sortie (21) de l'amplificateur à bande large et à produire un premier courant inférieur d'un premier facteur au courant d'émet-10 teur;

- (b) à diviser le premier courant en un deuxième courant et un troisième courant qui est inférieur d'un second facteur au premier courant, et à faire sortir le troisième courant d'un deuxième transistor (45) dont le 15 collecteur est connecté par un premier conducteur (46) à une grille d'un premier transistor (64) à effet de champ qui est un transistor de commande du circuit de polarisation;

- (c) à appliquer un quatrième courant au premier conducteur au moyen d'un circuit source de courant constant, le circuit de polarisation ajustant une tension sur la base du premier transistor afin d'amener le troisième courant à être égal au quatrième courant.

- Procédé selon la revendication 1, dans

lequel l'étape (a) consiste à détecter le courant d'émetteur et à produire un premier courant au moyen d'un premier circuit miroir de courant.

- 3. Procédé selon la revendication 2, caractérisé en ce qu'il consiste à compenser la réponse du 30 circuit de polarisation au troisième courant en couplant un condensateur (65) sur le premier conducteur, l'amplificateur à bande large, le circuit de polarisation, le premier transistor à effet de champ, le premier circuit miroir de courant et le condensateur étant tous incorporés sur une 35 microplaquette de circuit intégré monolithique.

- 4. Procédé selon la revendication 3, caractérisé en ce que l'étape (a) consiste à détecter un courant d'émetteur d'un troisième transistor (1) dans l'étage de sortie et à produire un cinquieme courant qui est inférieur du premier facteur au courant d'émetteur du troisième transistor, à additionner le cinquième courant et un courant ayant l'amplitude du premier courant pour produire un sixième courant, et en ce que l'étape (b) consiste à diviser le sixième courant pour produire le troisième courant.

- 5. Amplificateur à bande large comprenant un étage d'entrée, un étage de sortie (21) et un circuit de polarisation (22), caractérisé en ce qu'il comporte des moyens destinés à détecter un courant d'émetteur d'un 15 premier transistor (1, 2) de l'étage de sortie et à produire, en réponse à cette détection, un premier courant qui est inférieur d'un premier facteur au courant d'émetteur du premier transistor, des moyens destinés à diviser un courant ayant l'amplitude du premier courant en un 20 deuxième courant et un troisième courant qui est inférieur d'un deuxième facteur au premier courant, des moyens destinés à faire sortir le troisième courant d'un deuxième transistor (45) dont le collecteur est connecté par un premier conducteur (46) à la grille d'un premier transistor 25 (64) à effet de champ qui est un transistor de commande du circuit de polarisation, et des moyens (64, 69, 72, 73, 74, 68) destinés à fournir un quatrième courant au premier conducteur au moyen d'un circuit de source de courant constant, le circuit de polarisation ajustant une tension 30 sur la base du premier transistor afin d'amener le 'troisième courant à être égal au quatrième courant.

- 6. Amplificateur selon la revendication 5, caractérisé en ce que les moyens de détection et de production du premier courant comprennent un premier 35 circuit miroir de courant (32, 33) monté en série avec

- l'émetteur du premier transistor et produisant le premier courant.

- 7. Amplificateur selon la revendication 6, caractérisé en ce qu'il comporte un condensateur (65) de 5 compensation connecté au premier conducteur (46).

- 8. Amplificateur selon la revendication 7, caractérisé en ce qu'il comporte des moyens destinés à détecter un courant d'émetteur d'un troisième transistor de l'étage de sortie et à produire un cinquième courant qui 10 est inférieur du premier facteur au courant d'émetteur du troisième transistor, et des moyens destinés à additionner le cinquième courant et un courant ayant la même amplitude que le premier courant avec le cinquième courant pour produire un sixième courant, les premiers moyens de 15 division de courant divisant le sixième courant pour produire le troisième courant.

- 9. Procédé de commande d'un courant continu de polarisation dans un étage de sortie (21) d'un amplificateur (20) par réaction de l'étage de sortie vers un étage d'entrée, caractérisé en ce qu'il consiste à détecter un courant d'émetteur d'un premier transistor (1) dans l'étage de sortie au moyen d'un premier miroir de courant pour produire un premier courant miroir, à conduire un courant de réaction qui correspond à un certain pour-centage du premier courant miroir à travers un deuxième transistor (45), à comparer le premier courant de réaction à un courant de référence pour produire un signal d'erreur, et à ajuster la tension continue de polarisation de l'étage de sortie en réponse au signal d'erreur afin d'amener le premier courant de réaction à être égal au courant de référence.

- 10. Procédé selon la revendication 9, caractérisé en ce qu'il consiste en outre à compenser le signal d'erreur au moyen d'un condensateur (65) de compensation, 35 l'amplificateur et le condensateur de compensation étant situés sur une seule microplaquette de circuit intégré.

$F_{IG}$ .1