(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4739510号

(P4739510)

(45) 発行日 平成23年8月3日(2011.8.3)

(24) 登録日 平成23年5月13日(2011.5.13)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G09F 9/30 (2006.01)

G09F 9/30 338

H01L 29/786 (2006.01)

H01L 29/78 613Z

H01L 29/78 619B

請求項の数 12 (全 21 頁)

(21) 出願番号

特願2000-382760 (P2000-382760)

(22) 出願日

平成12年12月15日 (2000.12.15)

(65) 公開番号

特開2002-182244 (P2002-182244A)

(43) 公開日

平成14年6月26日 (2002.6.26)

審査請求日

平成19年11月1日 (2007.11.1)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100110858

弁理士 柳瀬 瞳肇

(72) 発明者 荒尾 達也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 浅見 宗広

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小久保 千穂

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置およびその作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

ソース線と、前記ソース線に電気的に接続されたTFTと、保持容量を有する半導体装置であって、

前記保持容量は、前記ソース線と前記TFTを接続する配線と同一の層で形成された遮光膜と、前記遮光膜上の絶縁膜と、画素電極からなることを特徴とする半導体装置。

## 【請求項2】

ソース線と、前記ソース線に電気的に接続されたTFTと、保持容量を有する半導体装置であって、

前記保持容量は、前記ソース線と前記TFTを接続する配線と同一の層で形成された遮光膜と、前記遮光膜上の絶縁膜と、画素電極からなり、

前記画素電極は、前記配線上に形成された層間絶縁膜と前記遮光膜上の絶縁膜を覆って形成されていることを特徴とする半導体装置。

## 【請求項3】

ソース線と、ゲート線と、前記ソース線と前記ゲート線に電気的に接続されたTFTと、保持容量を含む半導体装置であって、

前記TFTは、チャネル形成領域とソース領域とドレイン領域を有する半導体層と、ゲート絶縁膜と、ゲート電極を含み、

前記ゲート電極は、前記半導体層の下に形成された前記ゲート線と接続されており、

前記保持容量は、前記ソース線と前記TFTを接続する配線と同一の層で形成された遮

10

20

光膜と、前記遮光膜上の絶縁膜と、画素電極からなることを特徴とする半導体装置。

**【請求項 4】**

ソース線と、ゲート線と、前記ソース線と前記ゲート線に電気的に接続された TFT と、第 1 保持容量と、第 2 保持容量を含む半導体装置であって、

前記 TFT は、チャネル形成領域とソース領域とドレイン領域を有する半導体層と、ゲート絶縁膜と、ゲート電極を含み、

前記ゲート電極は、前記半導体層の下に形成された前記ゲート線と接続されており、

前記第 1 保持容量は、前記ソース線と前記 TFT を接続する配線と同一の層で形成された遮光膜と、前記遮光膜上の絶縁膜と、画素電極からなり、

前記第 2 保持容量は、前記ドレイン領域から連続する前記半導体層と、前記ゲート絶縁膜と、前記ゲート電極と同一の工程で形成された容量電極からなることを特徴とする半導体装置。 10

**【請求項 5】**

請求項 3 または請求項 4 において、前記ゲート線は、前記 TFT のチャネル形成領域にあたる光を遮ることを特徴とする半導体装置。

**【請求項 6】**

請求項 1 乃至請求項 5 のいずれか一項において、前記ソース線と前記 TFT を接続する配線と、前記遮光膜は、複数の導電膜が積層されていることを特徴とする半導体装置。

**【請求項 7】**

請求項 1 乃至請求項 6 のいずれか一項において、前記遮光膜上の絶縁膜は、前記遮光膜の陽極酸化膜であることを特徴とする半導体装置。 20

**【請求項 8】**

基板にゲート線を形成する第 1 の工程と、

基板上に下地絶縁膜を形成する第 2 の工程と、

前記下地絶縁膜上に半導体層を形成する第 3 の工程と、

前記半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記下地絶縁膜および前記ゲート絶縁膜に前記ゲート線に達するコンタクトホールを形成する第 5 の工程と、

前記ゲート絶縁膜上に前記ゲート線と接続されたゲート電極を形成する第 6 の工程と、

前記半導体層に不純物元素を添加する第 7 の工程と、 30

前記ゲート電極上に第 1 層間絶縁膜および第 2 層間絶縁膜を形成する第 8 の工程と、

前記第 1 層間絶縁膜および前記第 2 層間絶縁膜に前記半導体層に達するコンタクトホールを形成する第 9 の工程と、

前記半導体層に達する配線および遮光膜を同時に形成する第 10 の工程と、

前記遮光膜上に第 3 層間絶縁膜を形成する第 11 の工程と、

前記第 3 層間絶縁膜に前記遮光膜および前記配線に達するコンタクトホールを形成する第 12 の工程と、

前記遮光膜上に絶縁膜を形成する第 13 の工程と、

前記遮光膜上の絶縁膜および前記第 3 層間絶縁膜上に画素電極を形成する第 14 の工程を有し、 40

前記配線は前記画素電極と前記半導体層との間に位置することを特徴とする半導体装置の作製方法。

**【請求項 9】**

基板にゲート線を形成する第 1 の工程と、

前記ゲート線上に下地絶縁膜を形成する第 2 の工程と、

前記下地絶縁膜上に半導体層を形成する第 3 の工程と、

前記半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記下地絶縁膜および前記ゲート絶縁膜に前記ゲート線に達するコンタクトホールを形成する第 5 の工程と、

前記ゲート絶縁膜上に前記ゲート線と接続されたゲート電極を形成する第 6 の工程と、 50

前記半導体層に不純物元素を添加する第7の工程と、

前記ゲート電極上に第1層間絶縁膜および第2層間絶縁膜を形成する第8の工程と、

前記第1層間絶縁膜および前記第2層間絶縁膜に前記半導体層に達するコンタクトホールを形成する第9の工程と、

前記半導体層に達する配線および遮光膜を同時に形成する第10の工程と、

前記遮光膜上に絶縁膜を形成する第11の工程と、

第3層間絶縁膜を形成する第12の工程と、

前記第3層間絶縁膜に前記遮光膜上の絶縁膜および前記配線に達するコンタクトホールを形成する第13の工程と、

前記遮光膜上の絶縁膜および前記第3層間絶縁膜上に画素電極を形成する第14の工程 10

を有し、

前記配線は前記画素電極と前記半導体層との間に位置することを特徴とする半導体装置の作製方法。

【請求項10】

基板にゲート線を形成する第1の工程と、

前記ゲート線上に下地絶縁膜を形成する第2の工程と、

前記下地絶縁膜上に非晶質半導体膜を形成する第3の工程と、

前記非晶質半導体膜に触媒元素を添加して第1の加熱処理を行って結晶質半導体膜を形成する第4の工程と、

第2の加熱処理を行って前記結晶質半導体膜から触媒元素を除去する第5の工程と、 20

前記結晶質半導体膜をパターニングして半導体層を形成する第6の工程と、

前記半導体層上にゲート絶縁膜を形成する第7の工程と、

前記下地絶縁膜および前記ゲート絶縁膜に前記ゲート線に達するコンタクトホールを形成する第8の工程と、

前記ゲート絶縁膜上に前記ゲート線と接続されたゲート電極を形成する第9の工程と、

前記半導体層に不純物元素を添加する第10の工程と、

前記ゲート電極上に第1層間絶縁膜および第2層間絶縁膜を形成する第11の工程と、

前記第1層間絶縁膜および前記第2層間絶縁膜に前記半導体層に達するコンタクトホールを形成する第12の工程と、

前記半導体層に達する配線および遮光膜を同時に形成する第13の工程と、 30

第3層間絶縁膜を形成する第14の工程と、

前記第3層間絶縁膜に、前記遮光膜および前記配線に達するコンタクトホールを形成する第15の工程と、

前記遮光膜上に絶縁膜を形成する第16の工程と、

前記遮光膜上の絶縁膜および前記第3層間絶縁膜上に画素電極を形成する第17の工程を有し、

前記配線は前記画素電極と前記半導体層との間に位置することを特徴とする半導体装置の作製方法。

【請求項11】

基板にゲート線を形成する第1の工程と、 40

前記ゲート線上に下地絶縁膜を形成する第2の工程と、

前記下地絶縁膜上に非晶質半導体膜を形成する第3の工程と、

前記非晶質半導体膜に触媒元素を添加して第1の加熱処理を行って結晶質半導体膜を形成する第4の工程と、

第2の加熱処理を行って前記結晶質半導体膜から触媒元素を除去する第5の工程と、

前記結晶質半導体膜をパターニングして半導体層を形成する第6の工程と、

前記半導体層上にゲート絶縁膜を形成する第7の工程と、

前記下地絶縁膜および前記ゲート絶縁膜に前記ゲート線に達するコンタクトホールを形成する第8の工程と、

前記ゲート絶縁膜上に前記ゲート線と接続されたゲート電極を形成する第9の工程と、 50

前記半導体層に不純物元素を添加する第10の工程と、

前記ゲート電極上に第1層間絶縁膜および第2層間絶縁膜を形成する第11の工程と、

前記第1層間絶縁膜および前記第2層間絶縁膜に前記半導体層に達するコンタクトホールを形成する第12の工程と、

前記半導体層に達する配線および遮光膜を同時に形成する第13の工程と、

前記遮光膜上に絶縁膜を形成する第14の工程と、

第3層間絶縁膜を形成する第15の工程と、

前記第3層間絶縁膜に、前記遮光膜上の絶縁膜および前記配線に達するコンタクトホールを形成する第16の工程と、

前記遮光膜上の絶縁膜および前記第3層間絶縁膜上に画素電極を形成する第17の工程

を有し、

前記配線は前記画素電極と前記半導体層との間に位置することを特徴とする半導体装置の作製方法。

#### 【請求項12】

請求項8乃至請求項11のいずれか一項において、前記遮光膜上の絶縁膜は、陽極酸化法を用いて形成されることを特徴とする半導体装置の作製方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、絶縁体表面に形成された半導体膜を活性層として作製した半導体装置およびその作製方法に関する。なお、本明細書において、半導体装置とは、トランジスタ、特に電界効果型トランジスタ、代表的にはMOS(Metal Oxide Semiconductor)トランジスタや薄膜トランジスタ(Thin Film Transistor:以下、TFTとする)といった装置を指し、該半導体装置を用いて作製された回路を駆動回路や画素部に有する液晶表示装置、該液晶表示装置を表示部に用いた電気器具もその範疇に含まれるものとする。

##### 【0002】

##### 【従来技術】

近年、同一基板上に駆動回路と画素部とが形成されたアクティブマトリクス型の液晶表示装置の開発が活発に進められてきている。なかでも、小型の液晶パネル(以下、液晶表示装置という)を用いる液晶プロジェクタの普及が急速に進んでいる。パソコンコンピュータ(PC)の画面をスクリーン上に投影することのできるプロジェクターが発表されて以来、企業のプレゼンテーションでの使用など需要が増大し続けている。また、近年では、家庭でも大画面で映像を楽しもうとする(ホームシアター)動きが盛んになり、学校の授業に使用するという計画も進行中である。使用される場が広がってくるにつれ便利性が求められるため、小型化、高輝度化、高精細化ならびに低価格化などを進めるための開発が続けられている。

##### 【0003】

液晶プロジェクタや電気器具の表示部に用いられるアクティブマトリクス型液晶表示装置の画素部には数百万個の各画素があり、各画素にはTFTが形成されており、各画素のTFTには画素電極が設けられている。液晶を挟んだ対向基板側には対向電極が設けられており、液晶を誘電体とした一種のコンデンサを形成している。そして、各画素に印加する電位をTFTのスイッチング機能により制御して、このコンデンサへの電荷を制御することで液晶を駆動して透過光量を制御して画像を表示する仕組みになっている。

##### 【0004】

このコンデンサはリーク電流により次第にその容量が減少するため、透過光量が変化して画像表示のコントラストを低下させる原因となっていた。そこで、従来では容量配線を設けて、液晶を誘電体とするコンデンサとは別のコンデンサ(保持容量)を並列に設けてあった。この保持容量は、液晶を誘電体とするコンデンサが損失する容量を補う働きをしている。

##### 【0005】

10

20

30

40

50

しかし、画素部に容量配線を用いた保持容量を形成して十分な容量を確保しようとする

と、開口率を犠牲にしなければならなかつた。特に、液晶プロジェクタに用いられる

ような小型の高精細な液晶表示装置では、一個当たりの画素面積も小さいため、容量配線による

開口率の低下は問題となつてゐる。

#### 【0006】

そこで、特許第2924506号では、開口率を犠牲にすることなく保持容量を形成し、

光もれを遮断することができる構造として、ソース電極およびドレイン電極の形成後、層

間膜を形成し、該層間膜上にアルミニウムからなる遮光膜を形成し、遮光膜を陽極酸化して

遮光膜の上面および側面にAl<sub>2</sub>O<sub>3</sub>からなる陽極酸化膜を形成し、その上に透明画素電

極を形成して、遮光膜 / Al<sub>2</sub>O<sub>3</sub>膜 / 透明画素電極からなる保持容量を有する画素構造を

開示している。

10

#### 【0007】

しかし、透過型液晶表示装置の基板のTFTが形成されていない面（以下、基板裏面とい

う）側からの光や、上面から入射した光が基板中を乱反射した光によって、光リーク電流

が増えてしまいオフ電流が高くなつてしまふ。リーク電流が高くなれば、補償するための

保持容量を大きくしなければならず、開口率の問題を考えると、活性層の下側にも遮光膜

を形成する必要があつた。

#### 【0008】

##### 【発明が解決しようとする課題】

今後、画素サイズの縮小化は、液晶表示装置の小型化と同時に高精細化が求められる限り

続くことが十分予想される。例えば対角0.9インチ小型の液晶表示装置で、XGA（1024

×768画素）という高精細な表示を実現するためには、画素のひとつひとつのサイズが、1

8 μm × 18 μmという極めて小さな面積となつてゐる。

20

#### 【0009】

現在、高輝度化のためには開口率をあげ、また高精細化のためには画素数を増やして対応

してきているが、画素サイズが小型化し続けるなかで、開口率の向上および画素数の向上

を同時に満たすような画素構造の設計をすることは、極めて難しい問題である。遮光膜を

形成し、さらに開口率の向上および画素数の向上を同時に満たすような画素構造を実現し

ようとすれば、当然工程数が増え、工程も複雑になるため、歩留まりが悪くなり液晶表示

装置の製造コストがあがつてしまふという問題があつた。

30

#### 【0010】

本発明はこのような画素構造に関する課題を解決するための技術であり、TFTと保持容

量の構成に関し、従来技術より工程数を増加することなく、開口率が高く高精細な表示を行

うことができ、さらに、信頼性の高いアクティブマトリクス型液晶表示装置を実現する

ことを課題としている。また、十数μm角という非常に小さな画素サイズで設計された液晶

表示装置および該液晶表示装置を表示部に用いた電気器具においても明るい高精細な画

像表示を実現することを課題とする。

#### 【0011】

##### 【課題を解決するための手段】

本発明では、上記の課題を解決するために、ソース線とTFTを電気的に接続する配線お

よびTFTと画素電極とを電気的に接続する配線と同一の面上に遮光膜を形成し、該遮光

膜上に絶縁膜を形成した後、有機絶縁膜を用いて層間絶縁膜を形成する。この層間絶縁膜

に絶縁膜および配線に達するコンタクトホールを形成して、画素電極を形成している。また

遮光膜 / 絶縁膜 / 画素電極で保持容量を形成している。

40

#### 【0012】

また、TFTは、チャネル形成領域、ソース領域およびドレイン領域を含む活性層、ゲー

ト絶縁膜およびゲート電極を含み、ゲート電極は活性層より下層（基板側）に形成された

下部遮光膜をかねるゲート線に接続されている。

#### 【0013】

また、ソース線とTFTを電気的に接続する配線およびTFTと画素電極とを電気的に接

50

続する配線と同一の工程で遮光膜を形成しているため、工程数を増やさなくてもよい。さらに、下部遮光膜および遮光膜を有しているため、光もれによるリーク電流の発生を防ぐことができる。

**【0014】**

**【発明の実施の形態】**

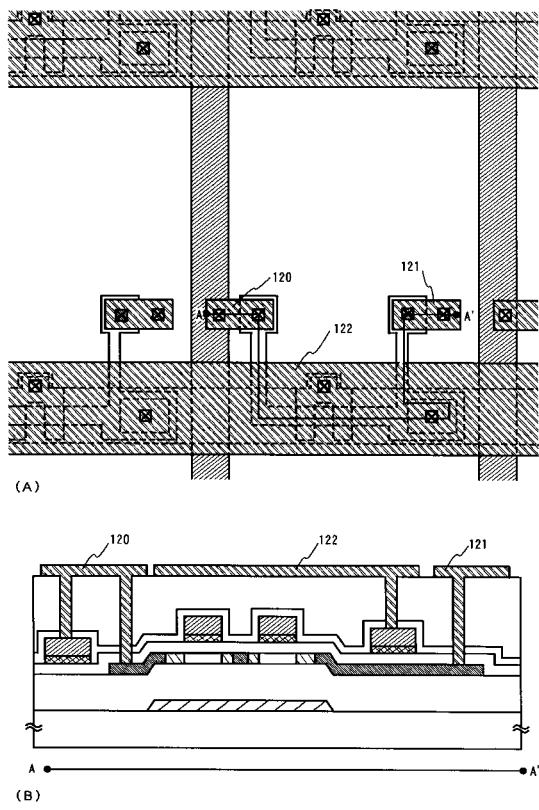

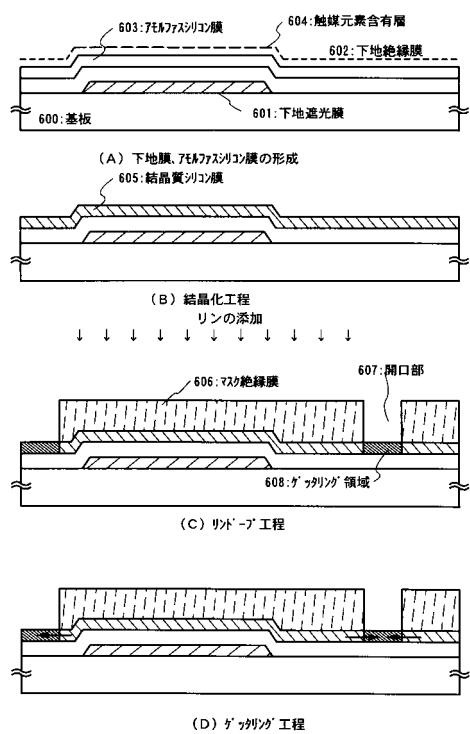

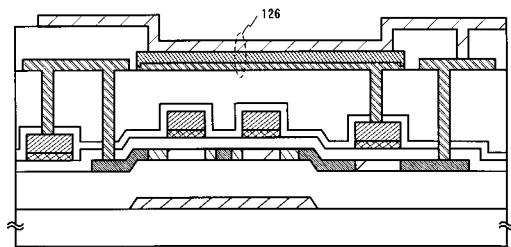

図6(C)の断面図を用いて、本発明の画素構造について説明する。

**【0015】**

基板100上に下部遮光膜としても機能するゲート線101が形成されている。ゲート線101上には下地絶縁膜102、半導体層109、ゲート絶縁膜110の順に形成されている。ゲート絶縁膜110上のゲート電極114はゲート線101と接続されている。ゲート電極114上には第1層間絶縁膜、第2層間絶縁膜が積層されており、第2層間絶縁膜上にTFT(特にチャネル形成領域)の遮光膜122および配線120、121が形成されている。遮光膜122上には酸化絶縁膜123が形成されている。酸化絶縁膜123の形成方法としては、陽極酸化法を用いればよい。次いで、第3層間絶縁膜124を形成した後、画素電極125が形成される。

10

**【0016】**

遮光膜122がTFTとソース線115とを電気的に接続する配線120およびTFTと画素電極125とを電気的に接続する配線121と同一の工程において形成されている。この遮光膜122、該遮光膜122上に形成された絶縁膜123、該絶縁膜123上に形成された画素電極125から保持容量126を形成している点に特徴がある。また、画素電極125で遮光膜122および絶縁膜123を覆うのではなく、第3層間絶縁膜124を形成した後、この第3層間絶縁膜に絶縁膜123および配線121に達するコントクトホールを形成し、画素電極125を形成している。従来、画素電極で遮光膜を覆う画素構造が一般的であったが、この方法では、画素電極を形成してできる段差が遮光膜の外側になるため、ラビング処理後に配向不良を起こし、光もれを起こす原因となっていた。

20

**【0017】**

本発明で開示する画素構造は、画素電極125を形成した後形成される段差が、遮光膜122の真上に形成されるため(図6(C))、光もれを防ぐことができる。また、保持容量は前記段差の内側の絶縁膜123の膜厚が均一であって、容量が均一に得られる領域で形成されている。

30

**【0018】**

また、本発明で開示する画素構造は、下部遮光膜(ゲート線)101を有しているため、半導体層にあたる可能性があった基板裏面側の光や、上面から入射した光が基板中を乱反射した光を遮ることができる。

**【0019】**

また、本発明で開示する画素構造は、保持容量の一方の電極として用いる遮光膜122がTFTとソース線115とを電気的に接続する配線120およびTFTと画素電極125とを電気的に接続する配線121と同一の工程において形成されているため、工程数を増やすずに保持容量を形成することができる。

40

**【0020】**

また、本発明で開示する画素構造は、絶縁膜123を陽極酸化法により形成する場合、遮光膜122は配線120、121とは接続されていないため、配線120、121に陽極酸化膜が形成されることなく、さらに、TFTに陽極酸化時に電流が流れてしまうこともない。

**【0021】**

**【実施例】**

**(実施例1)**

本実施例においては、本発明を用いてアクティブマトリクス基板を作製する工程について説明する。なお、本明細書において、アクティブマトリクス基板とは駆動回路および画素部(TFTおよび保持容量を有する)が同一基板上に作製された基板のことをいう。

50

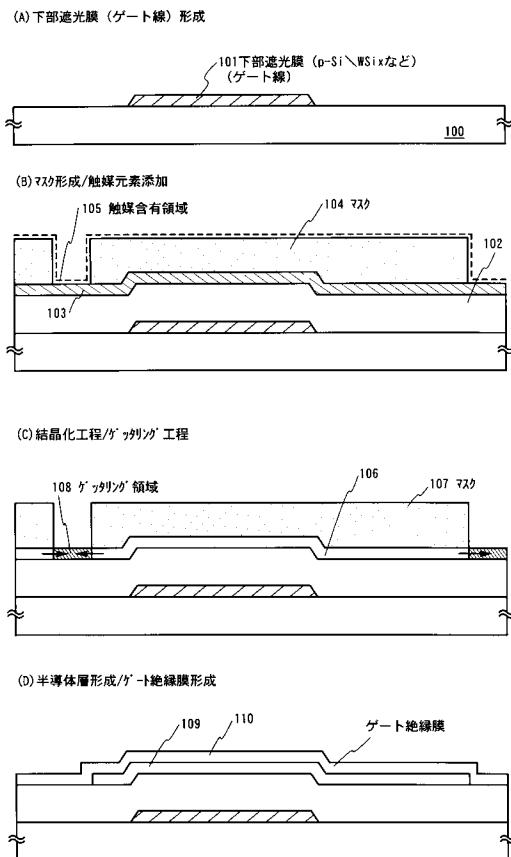

## 【0022】

まず、基板（石英基板）100の絶縁表面にポリシリコン膜およびWSi<sub>x</sub>膜を積層し、これらの膜を所望の形状にパターニングして基板裏側からの光を遮光するための下部遮光膜101を形成する。下部遮光膜を形成する膜としては、ポリシリコン膜、WSi<sub>x</sub>（x=2.0~2.8）膜、Al、Ta、W、Cr、Mo等の導電性材料からなる膜のいずれか一種または複数種を成膜すればよい。なお、下部遮光膜101は、ゲート線としての機能も果たす。本実施例では、ポリシリコン膜を下部遮光膜101aとして膜厚50nm、WSi<sub>x</sub>膜を第2下部遮光膜101bとして膜厚100nmで積層して形成した。以下では、下部遮光膜101をゲート線101と称する（図1（A））。

## 【0023】

10

次いで、ゲート線101を覆う下地絶縁膜102を形成する。下地絶縁膜102は、シリコンを含む絶縁膜（例えば、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜等）をプラズマCVD法またはスパッタ法等で形成する。

## 【0024】

次いで、下地絶縁膜102上に、減圧CVD法により非晶質半導体膜を形成する。非晶質半導体膜としては、特に限定はないが、好ましくはシリコンもしくはシリコングルマニウム（Si<sub>x</sub>Ge<sub>1-x</sub> : 0 < x < 1、代表的には、x = 0.001 ~ 0.05）合金などで形成するとよい。なお、本実施例では、非晶質半導体膜としてアモルファスシリコン膜103を膜厚65nmに形成した（図2（A））。

## 【0025】

20

次いで、アモルファスシリコン膜103を結晶化する。まず、アモルファスシリコン膜103上にマスク104を形成して、アモルファスシリコン膜103に選択的に結晶化を促進する作用を有する触媒元素（例えばNi）を含有する触媒元素含有層105を形成する。続いて、窒素雰囲気において600（500~700）、12時間（4~12時間）の加熱処理を行って、結晶質シリコン膜106を形成する。なお、触媒元素含有層105を形成した後、アモルファスシリコン膜103中に含まれる水素を低減するために、450で1時間、水素出しのための加熱処理を行ってよい。また、結晶化のための加熱処理後、結晶質シリコン膜の結晶性をさらに向上させるために、レーザー照射を行ってよい（図1（B））。

## 【0026】

30

続いて、結晶質シリコン膜106から触媒元素をゲッタリングするための加熱処理工程を行う。触媒元素は、シリコン膜中に深いエネルギー準位を形成してキャリアを捕獲し再結合してしまい、電気特性や悪影響を及ぼす。また、結晶質半導体膜中に残留した触媒元素は結晶粒界に偏析してしまい、この偏析が微弱な電流の逃げ道となりオフ電流の突発的な増加の原因になるとも考えられている。そこで、TFTの特性に悪影響を及ぼさない程度にまで、残留触媒元素の濃度を低減する必要がある。そこで、触媒元素ゲッタリング作用を有する不純物元素を選択的に結晶質シリコン膜に添加する。マスク107は、触媒元素含有層105を形成する工程で用いたマスク104を除去せずに用いている。続いて、不純物元素を添加してゲッタリング領域108を形成する。なお、本実施例ではゲッタリング作用を有する不純物元素として周期表の15族に属する元素、代表的にはリン（P）を添加した。この後、700（600~800）で12時間の加熱処理を行って結晶質シリコン膜105中の触媒元素（Ni）をゲッタリング領域108に捕獲させる。ゲッタリングのための加熱処理工程が終了したら、ゲッタリング領域108は除去する。

なお、上記した半導体膜の結晶化のためおよび触媒元素のゲッタリングのための加熱処理はロータリーポンプやメカニカルブースターポンプにより排気を行った減圧雰囲気（圧力1.33~133Pa）において行うことが好ましい（図1（C））。

## 【0027】

40

次いで、結晶質シリコン膜106の結晶性を向上させるための加熱処理を行う。減圧CVD装置により20nm厚の酸化シリコン膜（図示せず）を成膜し、950で加熱酸化処理を行う。この処理により、結晶質シリコン膜上に結晶質シリコン膜が酸化されて形成され

50

た膜（熱酸化膜）が形成される。以上の加熱処理により結晶質シリコン膜は、膜厚35nm程度になる。この結晶質シリコン膜を所望の形状にパターニングして、後のTFTの活性層となる半導体層109を形成する。

#### 【0028】

次いで、半導体層109を覆うゲート絶縁膜110を形成する（図1（D））。続いて、ゲート絶縁膜110を介してp型を付与する不純物元素（以下、p型不純物元素とする）を添加する。p型不純物元素としては、代表的に周期表の13族に属する元素、典型的にはボロンまたはガリウムを用いることができる。この工程（チャネルドープ工程という）はTFTのしきい値電圧を制御するための工程である。この工程により、後のTFTの活性層となる半導体層109に $1 \times 10^{15} \sim 1 \times 10^{18}$ atoms/cm<sup>3</sup>（代表的には、 $5 \times 10^{16} \sim 5 \times 10^{17}$ atoms/cm<sup>3</sup>）の濃度でp型不純物元素が添加される。10

#### 【0029】

次いで、レジストからなるマスクを形成し、n型不純物元素（本実施例では、リン）を添加して、高濃度にリンを含む不純物領域111を形成する。この領域には、リンが $1 \times 10^{20} \sim 5 \times 10^{21}$ atoms/cm<sup>3</sup>、代表的には $2 \times 10^{20} \sim 1 \times 10^{22}$ atoms/cm<sup>3</sup>の濃度が含まれるようにする。

#### 【0030】

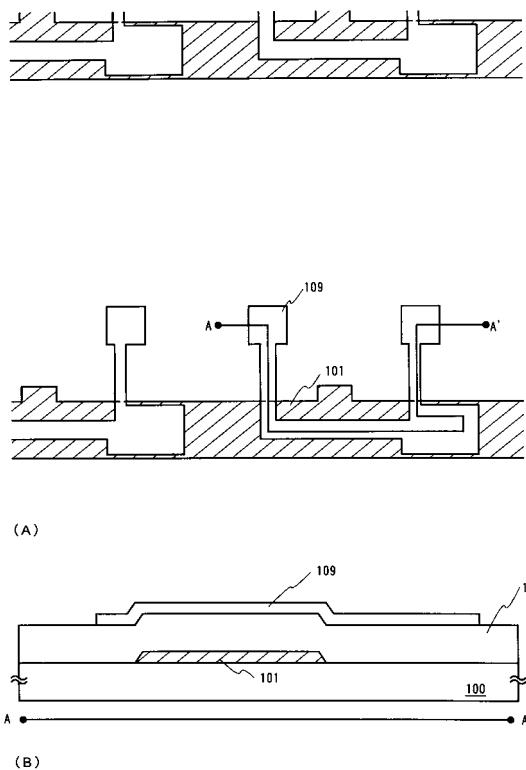

続いて、下地絶縁膜にゲート線101に達するコンタクトホールを形成する。その後、ゲート電極となる導電膜を形成する。なお、ゲート電極は、単層の導電膜で形成してもよいが、必要に応じて2層、3層といった積層膜とすることが好ましい。本実施例では、導電膜（A）112および導電膜（B）113でなる積層膜を形成する（図3（A））。20

#### 【0031】

本実施例では、導電膜（A）112としてTaN膜、導電膜（B）113としてW膜を用いるが、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タンゲステン（W）、クロム（Cr）、シリコン（Si）から選ばれた元素、または前記元素を主成分とする導電膜（代表的には、窒化タンタル膜、窒化タンゲステン膜、窒化チタン膜等）、または前記元素を組み合わせた合金膜（代表的にはMo-W合金膜、Mo-Ta合金膜、タンゲステンシリサイド膜等）を用いることができる。なお、導電膜（A）112は、10~50nm（好ましくは、20~30nm）とし、導電膜（B）113は200~400nm（好ましくは、250~350nm）の厚さで成膜すればよい。その後、導電膜（A）112および導電膜（B）113を所望の形状にパターニングして、ゲート電極114、ソース線115および容量電極116を形成する（図3（B）および図4）。

#### 【0032】

次いで、ゲート電極114をマスクとして用いて、n型を付与する不純物元素（以下、n型不純物元素とする）を後のTFTの活性層となる半導体層に添加する。n型不純物元素としては、周期表の15族に属する元素、典型的にはリンまたはヒ素を用いることができる。このn型不純物元素が添加された領域は、LDD領域117として機能させるための低濃度不純物領域であり、n型不純物元素が $1 \times 10^{16} \sim 5 \times 10^{18}$ atoms/cm<sup>3</sup>（代表的には、 $1 \times 10^{17} \sim 5 \times 10^{18}$ atoms/cm<sup>3</sup>）の濃度で含まれている。30

#### 【0033】

次いで、後のnチャネル型TFTとなる領域をマスクで覆い、後のpチャネル型TFTの活性層となる半導体層にp型不純物元素としてボロンを $3 \times 10^{20} \sim 3 \times 10^{21}$ atoms/cm<sup>3</sup>、代表的には $5 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>の濃度が含まれるように添加する（図示せず）。

#### 【0034】

次に、第1層間絶縁膜118として窒化シリコン膜、酸化シリコン膜または窒化酸化シリコン膜を50~500nm、代表的には200~300nmの厚さで形成する。本実施例では、プラズマCVD法で、200nm厚の窒化酸化シリコン膜を形成した（図3（B））。

#### 【0035】

その後、それぞれの半導体層にそれぞれの濃度で添加されたn型およびp型の不純物元素40

50

を活性化するための加熱処理を行った。この工程は、電気炉を用いたアニール法、レーザー・アニール法、ランプ・アニール法またはそれらを併用して行うことができる。電気炉を用いたアニール法を行う場合は、不活性ガス雰囲気中において、550～1000で行えばよい。本実施例では、950、30分の加熱処理を行い、不純物元素の活性化を行う。

#### 【0036】

なお、本実施例でゲート電極として用いている導電膜は、非常に酸化されやすく、酸化すると抵抗率が上がってしまうという問題があった。そこで、本実施形態における活性化のための加熱処理は、ロータリーポンプおよびメカニカルブースターポンプにより排気を行って雰囲気中の酸素濃度を低減し、減圧の雰囲気下で加熱処理を行うことが好ましい。

10

#### 【0037】

次いで、熱的に励起された水素により活性層中のダンギングボンドを終端する水素化のため、水素雰囲気中で、410で1時間の加熱処理を行う。水素化の他の手段として、プラズマにより励起された水素を用いるプラズマ水素化を行ってもよい。

#### 【0038】

なお、第2層間絶縁膜119を無機絶縁膜を用いて形成する場合には、水素化のための加熱処理は、保持容量の誘電体となる絶縁膜を形成した後に行ってもよい。

#### 【0039】

次いで、第2層間絶縁膜119を膜厚500～1000nm(本実施例では800nm)に形成する。第2層間絶縁膜としては、アクリル、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)といった有機絶縁膜、もしくは、酸化窒化シリコン膜もしくは窒化酸化シリコン膜といった無機絶縁膜を用いればよい。

20

#### 【0040】

続いて、半導体層109に達するコンタクトホールをゲート絶縁膜110、第1層間絶縁膜118および第2層間絶縁膜119に、ソース線115および容量電極116に達するコンタクトホールを第1層間絶縁膜118および第2層間絶縁膜119に形成する。次いで、それぞれのTFTを電気的に接続する配線およびTFT(チャネル形成領域)を遮光するための遮光膜を形成するために導電膜を形成し、所望の形状にパターニングして配線120、121および上部遮光膜122を形成する。配線材料としては、チタン(Ti)を主成分とする導電膜を膜厚50～100nmに成膜した後、アルミニウム(A1)を主成分とする導電膜を膜厚300～500nmに成膜する積層構造とすればよい。なお、配線および遮光膜を形成するための導電膜としては、タンタル(Ta)を主成分とする膜、アルミニウム(A1)を主成分とする導電膜またはチタン(Ti)を主成分とする膜のいずれかを積層させて形成すればよい(図5(A)、(B))。

30

#### 【0041】

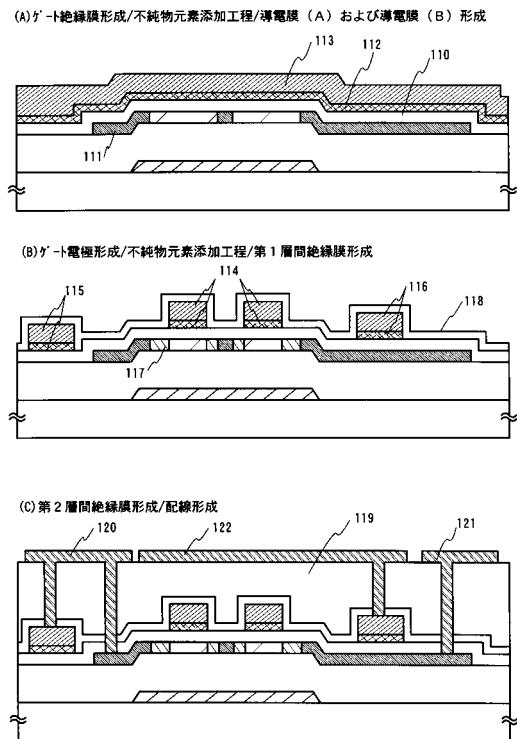

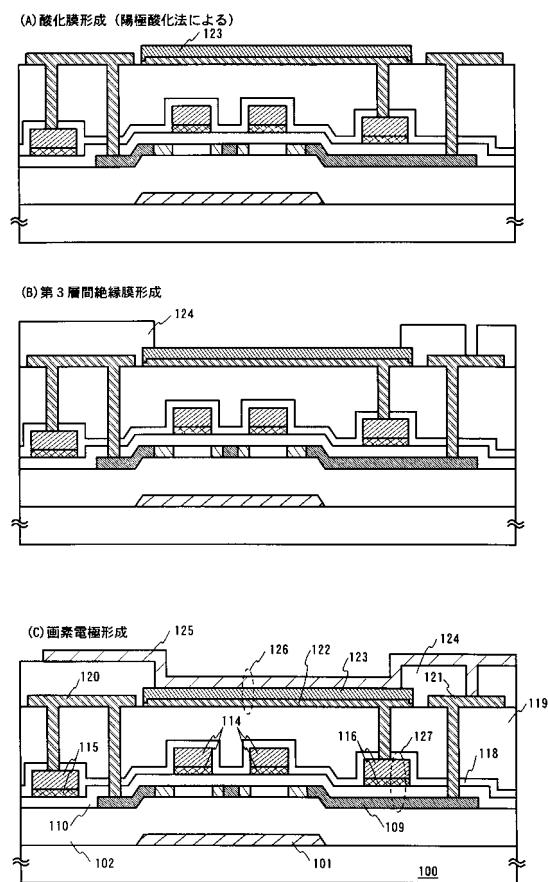

次に、遮光膜122の表面に陽極酸化法またはプラズマ酸化法(本実施例では陽極酸化法)により20～100nm(好ましくは30～50nm)の厚さの酸化膜123を形成する。本実施例では遮光膜122としてチタンを主成分とする膜とアルミニウムを主成分とする膜とを積層して用いており、アルミニウムを主成分とする膜が陽極酸化され、陽極酸化絶縁膜123として酸化アルミニウム膜(アルミナ膜)が形成される。この酸化絶縁膜123を保持容量の誘電体として用いる。なお、タンタル(Ta)またはチタン(Ti)を陽極酸化して得られる酸化絶縁膜も誘電率が高いため、保持容量の誘電体として好適に用いることができる(図6(A))。

40

#### 【0042】

この陽極酸化処理に際して、まず十分にアルカリイオン濃度の小さい酒石酸エチレングリコール溶液を作製する。これは15%の酒石酸アンモニウム水溶液とエチレングリコールとを2:8で混合した溶液であり、これにアンモニア水を加え、pHが7±0.5となるように調節する。そして、この溶液中に陰極となる白金電極を設け、遮光膜122が形成されている基板を溶液に浸し、遮光膜122を陽極として、一定(数mA～数十mA)の直流電流を流す。本実施例では1枚の基板に200mAの電流を流した。

50

## 【0043】

溶液中の陰極と陽極との間の電圧は陽極酸化物の成長に従い時間と共に変化するが、定電流のまま一定の昇圧レートで電圧を上昇させて、到達電圧45Vに達したところで陽極酸化処理を終了させる。このようにして遮光膜122の表面には厚さ約50nmの陽極酸化絶縁膜123を形成することができる。なお、ここで示した陽極酸化法に係わる数値は一例にすぎず、作製する素子の大きさ等によって当然最適値は変化しうるものである。

## 【0044】

本実施例における陽極酸化法の条件で、アルミニウム膜に陽極酸化膜を形成すると膜厚51.4nmのAlO<sub>x</sub>膜が形成された。このAlO<sub>x</sub>膜上に1mmのITO膜を形成し、Al膜-AlO<sub>x</sub>膜-ITO膜間に5Vの電圧をかけたところ、 $1 \times 10^{-11}$ (A)の微少なリーケ電流が測定された。これにより、AlO<sub>x</sub>膜は液晶表示装置の保持容量の誘電体として用いることができることがわかった。10

## 【0045】

なお、この陽極酸化工程で陽極酸化されるのは、遮光膜122だけである。配線120、121は遮光膜122と接続していないため、陽極酸化膜が形成されることはない。また、陽極酸化の際にTFTに電流が流れることもないためTFTの劣化を防ぐことができる。。

## 【0046】

また、ここでは陽極酸化法を用いて遮光膜表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCVD法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。また、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、DLC(Diamond Like Carbon)膜、酸化タンタル膜または有機絶縁膜を用いても良い。さらに、これらを組み合わせた積層膜を用いても良い。20

## 【0047】

酸化絶縁膜123を形成した後、積層構造となっている配線120、121の2層目のアルミニウムを含む導電膜を除去する。

## 【0048】

次いで、第3層間絶縁膜124を形成する。第3層間絶縁膜124は、平坦化する必要があるため、ポリイミド、アクリルといった有機絶縁膜を用いて膜厚1.5μmに形成する。続いて、保持容量となる領域の層間絶縁膜はエッチングして除去し、酸化絶縁膜123を露出させる。また、同一の工程において第3層間絶縁膜124にドレイン配線121に達するコンタクトホールを形成し(図6(B))、画素電極125を形成する(図6(C))。画素電極125は、一部の領域で酸化絶縁膜123に接し、遮光膜122を下部電極、陽極酸化膜123を誘電体、画素電極125を上部電極とした第1保持容量126が形成される。本実施例では、透過型の液晶表示装置とするために、ITO膜(酸化インジウムと酸化スズとの化合物)を用いて、膜厚100nmでスパッタ法により成膜する。なお、第2保持容量127は、半導体層109、ゲート絶縁膜110および容量電極116からなる。30

## 【0049】

図16には、容量電極を形成せずに第1保持容量のみを有する場合の画素構造を示した。40

## 【0050】

このように、本実施例を用いると、開口率が55%のアクティブマトリクス基板を作製することができる。また、こうして形成されたアクティブマトリクス基板に液晶層を配向させる配向膜を形成し、公知のセル組み技術を用いて対向電極および配向膜が形成された対向基板およびアクティブマトリクス基板を貼り合わせた後、液晶を注入し封止することでアクティブマトリクス型液晶表示装置を完成することができる。

## 【0051】

## (実施例2)

実施例1で作製されたアクティブマトリクス基板を用いて作製されたアクティブマトリクス型液晶表示装置の一例について説明する。50

**【0052】**

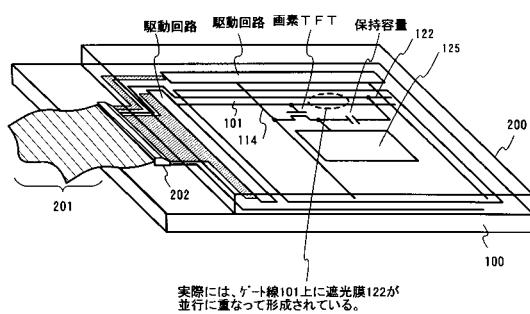

図7において、アクティブマトリクス基板は基板100上に形成された画素部と駆動回路とその他の信号処理回路とで構成される。画素部にはTFT(画素TFTともいう)と保持容量とが設けられ、画素部の周辺に設けられる駆動回路はCMOS回路を基本として構成されている。

**【0053】**

遮光膜122は、ゲート線101の上方にゲート線101と平行な方向に設けられ、保持容量の下部電極として機能している。ソース線115は、ゲート線101と垂直な方向に設けられている。

**【0054】**

駆動回路からは、それぞれゲート線101、ソース線115が画素部に延在し、画素TFTに接続している。また、フレキシブルプリント配線板(Flexible Printed Circuit: FPC)201が外部入力端子202に接続していて画像信号などを入力するのに用いる。FPC201は補強樹脂によって強固に接着されており、接続配線で、それぞれの駆動回路に接続している。また、対向基板200には図示していないが、透明対向電極が設けられている。

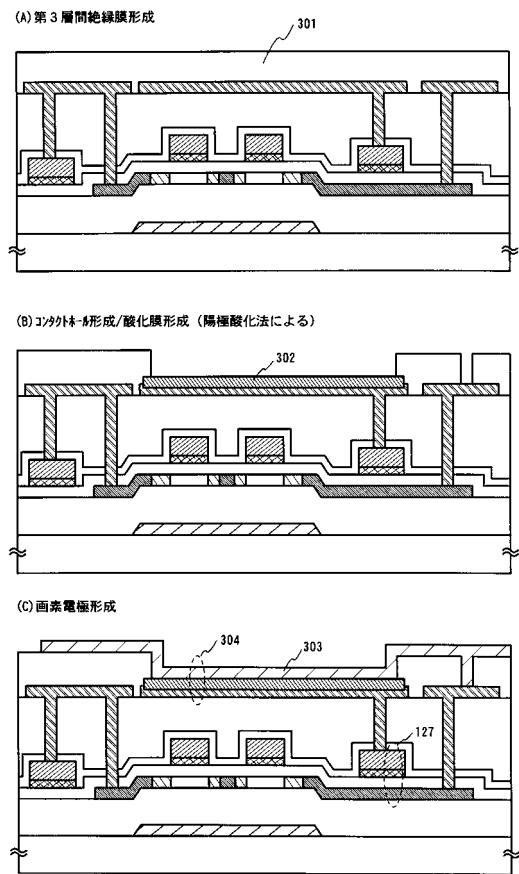

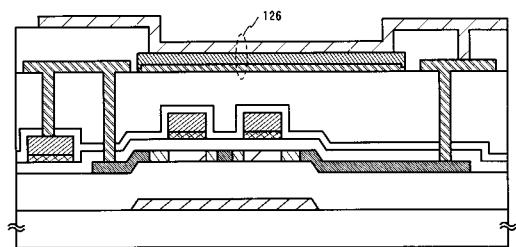

**【0055】****(実施例3)**

本実施例では、実施例1とは異なるアクティブマトリクス基板の作製方法について図8を用いて説明する。なお、実施例1の図5(B)で示す配線および遮光膜の形成までは同一であるので、説明は省略する。

10

20

**【0056】**

実施例1に従って、TFTとソース線とを電気的に接続するための配線および遮光膜を形成し、図5(B)の状態まで形成する。

**【0057】**

次いで、第3層間絶縁膜301を形成する。第3層間絶縁膜301は、平坦化する必要があるため、ポリイミド、アクリルといった有機絶縁膜を用いて形成する(図8(A))。続いて、第3層間絶縁膜301をエッティングし、遮光膜122および配線121の一部を露出させる(図8(B))。

**【0058】**

30

次に、遮光膜122の表面に陽極酸化法により陽極酸化膜302を形成する。陽極酸化膜302として酸化アルミニウム膜( $Al_2O_3$ 膜)が形成される。

**【0059】**

酸化絶縁膜302を形成した後、次の工程で形成する画素電極として用いるITO膜と接する配線121の2層目のアルミニウムを主成分とする導電膜を除去する。

**【0060】**

次いで、画素電極303を形成する(図8(C))。画素電極303は、一部酸化絶縁膜302に接するように形成される。本実施例では、透過型の液晶表示装置するために、ITO膜(酸化インジウムと酸化スズとの化合物)を用いて、膜厚100nmでスパッタ法により成膜する。ここまででの工程により、遮光膜122を下部電極、陽極酸化膜302を誘電体、画素電極303を上部電極とした保持容量304が形成される。

40

**【0061】**

以上のような工程順序にすると、第2層間絶縁膜および配線の間に陽極酸化膜が形成される可能性がなくなるため、遮光膜が第2層間絶縁膜から剥がれる可能性がなく、信頼性の高いアクティブマトリクス基板を作製することができる。

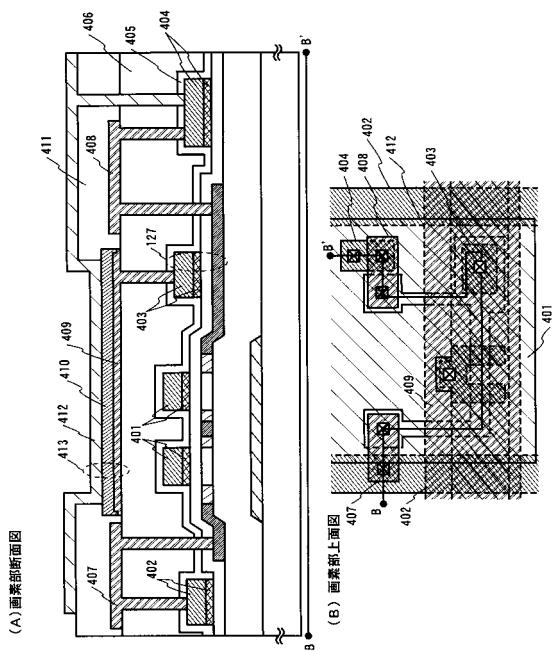

**【0062】****(実施例4)**

本実施例では、実施例1と異なる構造の画素部について、図9を用いて説明する。なお、基本的な構造は、図6(C)に示した画素部と同一構造であるので、相違点のみを説明する。

50

**【 0 0 6 3 】**

実施例 1 に従って、図 4 ( B ) に示すゲート電極を形成するための導電膜を形成する工程まで行う。次いで、導電膜を所望の形状にパターニングして、ゲート電極 401、ソース線 402、容量電極 403 および接続電極 404 を形成する。接続電極 404 は、ドレイン配線および画素電極を電気的に接続するために形成するための電極である。

**【 0 0 6 4 】**

次いで、後の TFT の活性層となる半導体層に不純物元素を添加して n 型不純物領域および p 型不純物領域を形成する。なお、n チャネル型 TFT のソース領域またはドレイン領域となる n 型不純物領域には、n 型不純物元素が  $1 \times 10^{20} \sim 1 \times 10^{22}$  atoms/cm<sup>3</sup> の濃度、LDD 領域となる n 型不純物領域には、 $1 \times 10^{16} \sim 5 \times 10^{18}$  atoms/cm<sup>3</sup> の濃度で添加されている。<sup>10</sup> p 型不純物元素を添加する工程においては、後の n チャネル型 TFT の活性層となる半導体層を p 型不純物元素が添加されないようにマスクで覆う。p チャネル型 TFT のソース領域またはドレイン領域となる p 型不純物領域には、 $2 \times 10^{20} \sim 2 \times 10^{22}$  atoms/cm<sup>3</sup> の濃度の p 型不純物元素が添加されている。

**【 0 0 6 5 】**

次いで、第 1 層間絶縁膜 405 を 200nm の膜厚の窒化シリコン膜で形成する。

その後、それぞれの半導体層にそれぞれの濃度で添加された n 型および p 型の不純物元素を活性化するための加熱処理を行った。この工程は、電気炉を用いたアニール法、レーザーアニール法、ランプアニール法またはそれらを併用して行うことができる。電気炉を用いたアニール法を行う場合は、不活性ガス雰囲気中において、550 ~ 1000 で行えればよい。本実施例では、950、30 分の加熱処理を行い、不純物元素の活性化を行う。<sup>20</sup> 本実施例における活性化のための加熱処理は、ロータリーポンプおよびメカニカルブースターポンプにより排気を行って雰囲気中の酸素濃度を低減し、減圧の雰囲気下で加熱処理を行うことが好ましい。続いて、熱的に励起された水素により活性層中のダングリングボンドを終端する水素化のため、水素雰囲気中で、410 で 1 時間の加熱処理を行う。水素化の他の手段として、プラズマにより励起された水素を用いるプラズマ水素化を行ってもよい。

**【 0 0 6 6 】**

次いで、第 2 層間絶縁膜 406 を形成する。第 2 層間絶縁膜としては、酸化窒化シリコン膜もしくは窒化酸化シリコン膜といった無機絶縁膜を 800nm の膜厚で形成した。続いて、ゲート絶縁膜 110、第 1 層間絶縁膜 405 および第 2 層間絶縁膜 406 に、半導体層 109、容量電極 403、ソース線 402 および接続電極 404 に達するコントクトホールを形成する。<sup>30</sup>

**【 0 0 6 7 】**

次いで、TFT およびソース線ならびに TFT のドレイン配線および接続電極 404 を電気的に接続する配線 407、408、TFT (チャネル形成領域) を遮光する遮光膜 409 を形成する。

**【 0 0 6 8 】**

次いで、上部遮光膜 409 に実施例 1 に記載されたような陽極酸化法を施して、陽極酸化絶縁膜 410 を形成する。この酸化絶縁膜 410 は、保持容量の誘電体として用いる。<sup>40</sup> 続いて、実施例 1 に従って有機絶縁膜により第 3 層間絶縁膜 411、ITO 膜を用いて画素電極 412 を形成し、アクティブラトリクス基板が完成する。

**【 0 0 6 9 】**

なお、本実施例では陽極酸化膜を形成した後に、第 3 層間絶縁膜 411 を形成しているが、実施例 3 のように第 3 層間絶縁膜 411 を先に形成してもよく、工程順序は適宜実施者が決定すればよい。

**【 0 0 7 0 】****( 実施例 5 )**

本実施例では、実施例 1 と異なる構造の画素部について、図 10 を用いて説明する。

**【 0 0 7 1 】**

複数種の異なる素材の電極を電解液に浸したとき、イオン化傾向の違いで、浸した電極が電解液に溶け出してしまう電蝕という現象がある。アルミニウム（A1）膜とITO膜を積層し、パターニング、エッチングする工程中に現像液に浸すと、この現象が起こる可能性がある。この電蝕は、微細加工した際、形状の変化による導通不良の原因となってしまう。そこで、図10に示すように、ドレイン配線121および画素電極501を接続させるために、第3層間絶縁膜119にドレイン配線121の線幅より大きいコンタクトホールを形成し、配線のアルミニウムを主成分とする膜を除去する。配線は、線幅いっぱいに露出しているため、アルミニウム膜を残らず除去することができる。したがって、画素電極として用いるITO膜とアルミニウム膜との接触による電蝕を防ぐことができる。

## 【0072】

10

本実施例を用いて作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製することができる。

## 【0073】

## (実施例6)

本実施例では、実施例1と異なる構造の画素部について、図15を用いて説明する。

## 【0074】

図15は、実施例1に従って図1(D)に示すゲート絶縁膜110の形成まで行う。その後、ゲート電極を形成するための導電膜を積層して、所望の形状にパターニングしてゲート電極を形成する。

## 【0075】

20

次いで、ゲート電極をマスクとして半導体層にn型不純物元素を添加する。n型不純物元素として本実施例では、リン(P)を用いる。ここでは、LDD領域として機能させるための低濃度不純物領域(不純物濃度 $1 \times 10^{16} \sim 5 \times 10^{18}$ atoms/cm<sup>3</sup>)が形成される。

続いて、レジストからなるマスクを形成して、高濃度( $1 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>)にn型不純物元素を含む領域を形成する。

## 【0076】

次いで、後のnチャネル型TFTとなる領域をマスクで覆い、pチャネル型TFTとなる領域にp型不純物元素としてボロンを $2 \times 10^{20} \sim 2 \times 10^{21}$ atoms/cm<sup>3</sup>の濃度添加する。

## 【0077】

30

後の工程を実施例1に従って形成する。このように、不純物元素の添加工程の順序を変えて、図15に示すようなアクティブマトリクス基板を形成することができる。

## 【0078】

## (実施例7)

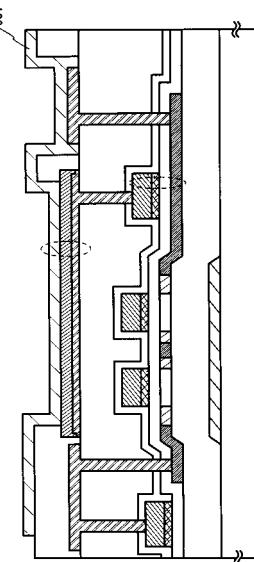

本実施例では、活性層として用いる半導体膜の結晶化の方法の他の一例について図11を用いて説明する。

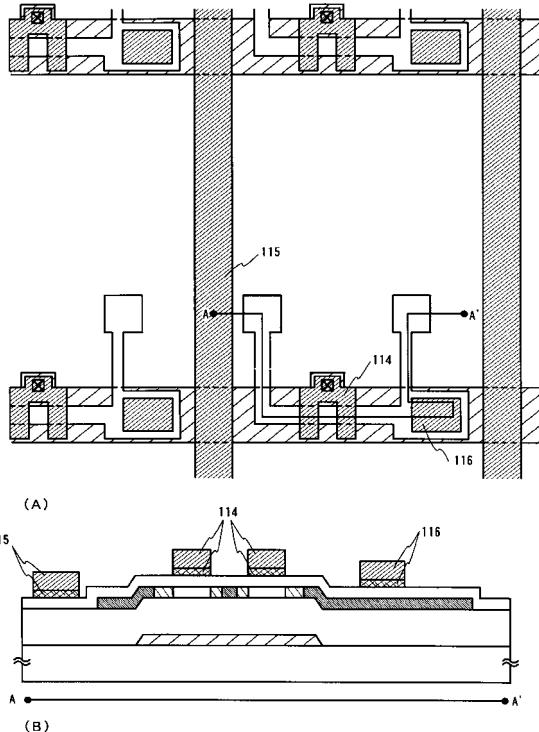

## 【0079】

基板600上に下部遮光膜(ゲート線)601を形成する。次いで、下地絶縁膜602として窒化シリコン膜、酸化シリコン膜または窒化酸化シリコン膜からなるまたはこれらの膜の積層からなる膜を形成する。次いで、下地絶縁膜602上に非晶質半導体膜としてアモルファスシリコン膜603を形成する。なお、下地絶縁膜602およびアモルファスシリコン膜603は、大気開放せずに連続的に形成することができる。

40

## 【0080】

次いで、アモルファスシリコン膜603の全面に重量換算で0.1~50ppm、本実施例では10ppmの触媒元素(代表的にはニッケル)を含む触媒元素をスピンドルコート法で塗布して、触媒元素含有層604を形成する。なお、ここで触媒元素としてはニッケルの他に、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)といった金属元素を使用することができる。また、本実施例では、触媒元素をスピンドルコート法で塗布しているが、蒸気法やスパッタ法などにより触媒元素を含むごく薄い膜を形成してもよい(図11(A))。

50

**【 0 0 8 1 】**

続いて、結晶化の工程に先立ち、アモルファスシリコン膜中に含まれる水素を離脱させるための加熱処理を行う。400～500<sup>10</sup>で1時間程度の加熱処理を行う。次いで、ロータリーポンプおよびメカニカルプースターポンプにより排気を行い、減圧(1.33～26.7Pa)にした窒素雰囲気において加熱処理を行い、結晶質シリコン膜605が形成される(図11(B))。

**【 0 0 8 2 】**

次いで、結晶質半導体膜605上にマスク絶縁膜606を形成し、触媒元素をゲッタリング(捕獲)する作用を有する元素、代表的には、周期表の15族に属する不純物元素(本実施例では、リン)を半導体層に添加してゲッタリング領域608を形成する。不純物元素は、 $1 \times 10^{19} \sim 1 \times 10^{22}$ atoms/cm<sup>3</sup>の濃度で半導体層に添加される。<sup>10</sup>

**【 0 0 8 3 】**

続いて、結晶化の際に用いた触媒元素を活性層となる半導体層からゲッタリング(捕獲)するための加熱処理を行う。処理を行う炉の雰囲気を真空ポンプ(例えばロータリーポンプまたはメカニカルプースターポンプ、もしくは、両方のポンプ)を用いて排気を行い、雰囲気を減圧の状態にする。雰囲気は、窒素を5l/minで注入し、圧力を13.3～26.7Paに保つ。450～950<sup>20</sup>で4～12時間の加熱処理により触媒元素をチャネル形成領域となる領域から触媒元素をゲッタリングする。なお、ゲッタリング領域に周期表の15族に属する不純物元素に加えて、周期表の13族に属する不純物元素も添加されていることが好ましい(図11(C))。

**【 0 0 8 4 】**

なお、このゲッタリング工程は、半導体層に添加されたn型およびp型不純物元素の活性化のための加熱処理と同一の工程において行ってもよい。また、ゲッタリング領域は、後にTFTの活性層のソース領域またはドレイン領域となる領域がゲッタリングに必要な濃度の不純物元素を含んでいることから、これらの領域を用いてもよい。

**【 0 0 8 5 】**

本実施例は、実施例1～6のいずれかと組み合わせて用いることができる。

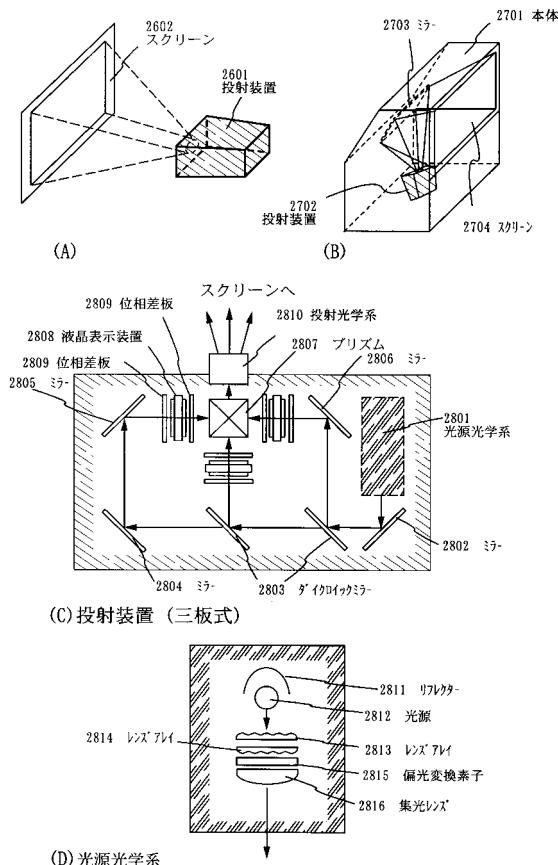

**【 0 0 8 6 】****(実施例8)**

本発明を実施して形成されたアクティブマトリクス型液晶表示装置をプロジェクタに用いた例を図12に示す。<sup>30</sup>

**【 0 0 8 7 】**

図12(A)はフロント型プロジェクタであり、投射装置2601、スクリーン2602等を含む。

**【 0 0 8 8 】**

図12(B)はプロジェクタであり、本体2701、投射装置2702、ミラー2703、スクリーン2704等を含む。

**【 0 0 8 9 】**

なお、図12(C)は、図12(A)及び図12(B)中における投射装置2601、2702の構造の一例を示した図である。投射装置2601、2702は、光源光学系2801、ミラー2802、2804～2806、ダイクロイックミラー2803、プリズム2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図12(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。<sup>40</sup>

**【 0 0 9 0 】**

また、図12(D)は、図12(C)中における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801は、リフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構

成される。なお、図12(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0091】

ただし、図12に示したプロジェクタにおいては、透過型の電気光学装置を用いた場合を示しており、反射型の液晶表示装置の適用例は図示していない。

【0092】

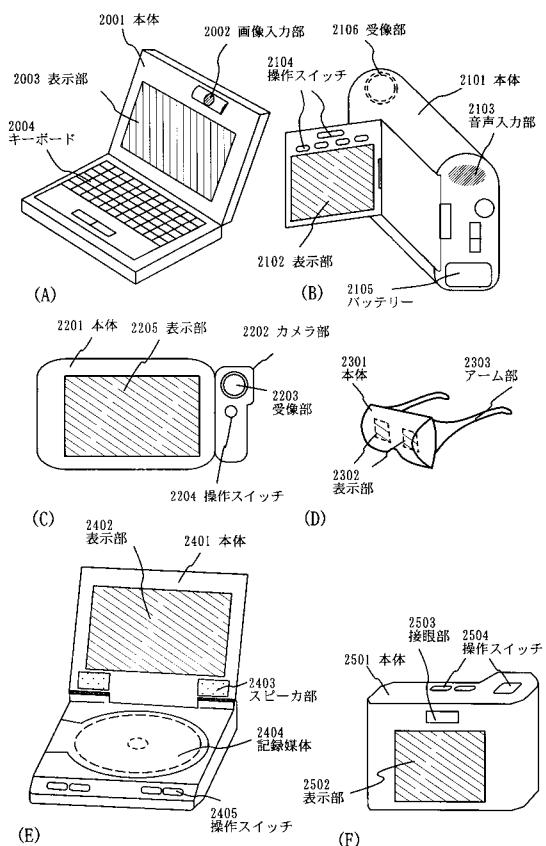

本発明を用いて作製された液晶表示装置は、他の電気器具の表示部に組み込んで用いることもできる。電気器具の例として、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、パソコン、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図13及び図14に示す。

10

【0093】

図13(A)はパソコンであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。

【0094】

図13(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。

【0095】

図13(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205等を含む。

20

【0096】

図13(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303等を含む。

【0097】

図13(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405等を含む。なお、このプレーヤーは記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。

30

【0098】

図13(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。

【0099】

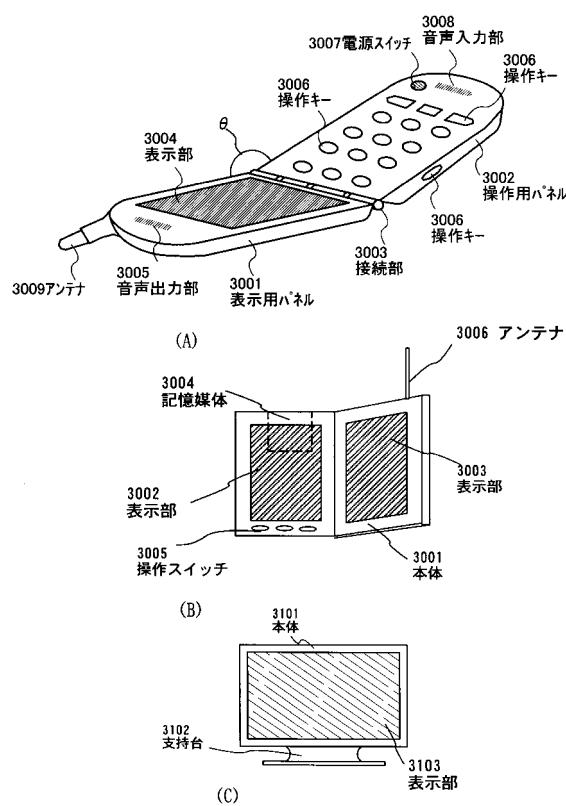

図14(A)は携帯電話であり、3001は表示用パネル、3002は操作用パネルである。表示用パネル3001と操作用パネル3002とは接続部3003において接続されている。接続部3003における、表示用パネル3001の表示部3004が設けられている面と操作用パネル3002の操作キー3006が設けられている面との角度は、任意に変えることができる。さらに、音声出力部3005、操作キー3006、電源スイッチ3007、音声入力部3008を有している。

40

【0100】

図14(B)は携帯書籍(電子書籍)であり、本体3001、表示部3002、3003、記憶媒体3004、操作スイッチ3005、アンテナ3006等を含む。

【0101】

図14(C)はディスプレイであり、本体3101、支持台3102、表示部3103等を含む。

【0102】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用することが可能である。また、本実施例の電気器具は実施例1~7を組み合わせて実現することができる。

50

## 【0103】

## 【発明の効果】

本発明を用いることにより、工程数を増加することなく、十分な保持容量を有し、開口率の高い半導体装置を作製することができる。また、非常に小さな画素サイズで設計された液晶表示装置および該液晶表示装置を表示部に用いた電気器具においても明るい高精細な画像表示を実現することができる。

## 【図面の簡単な説明】

- 【図1】 本発明の実施の一例を示す図。

- 【図2】 本発明の実施の一例を示す図。

- 【図3】 本発明の実施の一例を示す図。

- 【図4】 本発明の実施の一例を示す図。

- 【図5】 本発明の実施の一例を示す図。

- 【図6】 本発明の実施の一例を示す図。

- 【図7】 本発明の実施の一例を示す図。

- 【図8】 本発明の実施の一例を示す図。

- 【図9】 本発明の実施の一例を示す図。

- 【図10】 本発明の実施の一例を示す図。

- 【図11】 本発明の実施の一例を示す図。

- 【図12】 電気器具の一例を示す図。

- 【図13】 電気器具の一例を示す図。

- 【図14】 電気器具の一例を示す図。

- 【図15】 本発明の実施の一例を示す図。

- 【図16】 本発明の実施の一例を示す図。

10

20

## 【図1】

## 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

審査官 小濱 健太

(56)参考文献 特開昭64-028622(JP,A)

特開平10-010581(JP,A)

特開平08-234239(JP,A)

特開平01-274117(JP,A)

特開平02-044317(JP,A)

特開平06-138484(JP,A)

特開2000-315798(JP,A)

特開平10-170961(JP,A)

特許第2924506(JP,B2)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368