(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6436616号

(P6436616)

(45) 発行日 平成30年12月12日(2018.12.12)

(24) 登録日 平成30年11月22日(2018.11.22)

(51) Int.Cl.

G O 1 D 5/244 (2006.01)

F 1

G O 1 D 5/244

J

請求項の数 10 (全 20 頁)

(21) 出願番号 特願2013-123379 (P2013-123379)

(22) 出願日 平成25年6月12日 (2013.6.12)

(65) 公開番号 特開2014-240790 (P2014-240790A)

(43) 公開日 平成26年12月25日 (2014.12.25)

審査請求日 平成28年6月13日 (2016.6.13)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100114775

弁理士 高岡 亮一

(72) 発明者 伊藤 貴文

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 岡田 芳幸

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 吉田 久

最終頁に続く

(54) 【発明の名称】計測装置、計測方法、および処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

対象物の変位に伴って変化する信号の検出を行って前記対象物の位置を計測する計測装置であつて、

1 周期の中に所定周期の信号を出力する第1期間と一定値の信号を出力する第2期間を含んでおり、前記対象物の位置の出力用位置データを要求する要求信号に基づいて、該要求信号の周期より短い周期を有する第1クロック信号を生成するクロック生成部と、

前記第1クロック信号の周期ごとに前記検出を行う検出部と、

前記検出部の出力に基づいて、前記対象物の処理用位置データを得る演算部と、

前記演算部からの複数の前記処理用位置データに基づいて単位時間当たりの前記対象物の変位量を得、前記出力用位置データの要求信号が受信される前に前記出力用位置データのための計測が開始された時点と前記出力用位置データの前記要求信号が受信された時点との間の時間差と、前記変位量とに基づいて、前記演算部が得た処理用位置データのうち補正対象の処理用位置データを補正する補正部と、

10

を有しております、

前記クロック生成部は、前記第1期間では、前記要求信号に含まれる前記所定周期の信号に同期した前記第1クロック信号を出力し、前記第2期間では、前記第1期間に出力した前記要求信号の周期より短い周期を有する第1クロック信号を継続して出力するよう動作が維持される位相同期部を含む、

ことを特徴とする計測装置。

10

20

**【請求項 2】**

前記クロック生成部は、前記要求信号に同期し且つ該要求信号の周期より短い周期を有する第2クロック信号に同期して前記第1クロック信号を生成する、ことを特徴とする請求項1に記載の計測装置。

**【請求項 3】**

前記時間差を計測する時間差計測部を有する、ことを特徴とする請求項1または2に記載の計測装置。

**【請求項 4】**

前記補正部は、前記補正対象の処理用位置データを補正して、前記要求信号を受信した時点における出力用位置データを得る、

10

ことを特徴とする請求項1ないし3のいずれか1項に記載の計測装置。

**【請求項 5】**

前記補正部は、前記補正対象の処理用位置データを補正して、前記要求信号を受信した時点より後の時点における出力用位置データを得る、

ことを特徴とする請求項1ないし4のいずれか1項に記載の計測装置。

**【請求項 6】**

前記検出部は、光電変換素子を含み、

前記出力用位置データのための前記計測が開始される前記時点は、前記光電変換素子の受光時間の中間に設定されている、ことを特徴とする請求項1ないし5のいずれか1項に記載の計測装置。

20

**【請求項 7】**

対象物を処理する処理装置であって、

前記対象物の変位を計測する請求項1ないし6のいずれか1項に記載の計測装置を有することを特徴とする処理装置。

**【請求項 8】**

対象物の変位に伴って変化する信号の検出を行って前記対象物の位置を計測する計測方法であって、

1周期の中に所定周期の信号を出力する第1期間と一定値の信号を出力する第2期間を含んでおり、前記対象物の位置の出力用位置データを要求する要求信号に基づいて、該要求信号の周期より短い周期を有する第1クロック信号を生成し、

30

前記第1クロック信号の周期ごとに前記検出を行い、

前記検出に基づいて、前記対象物の処理用位置データを得、

複数の前記処理用位置データに基づいて単位時間当たりの前記対象物の変位量を得、前記出力用位置データの要求信号が受信される前に前記出力用位置データのための計測が開始された時点と前記出力用位置データの前記要求信号が受信された時点との間の時間差と、前記変位量とに基づいて、演算部が得た処理用位置データのうち補正対象の処理用位置データを補正し、

前記第1期間では、前記要求信号に含まれる前記所定周期の信号に同期した前記第1クロック信号を出力し、前記第2期間では、前記第1期間に出力した前記要求信号の周期より短い周期を有する第1クロック信号を継続して出力することが維持される、ことを特徴とする計測方法。

40

**【請求項 9】**

対象物を移動させる機構と、該対象物の変位に伴って変化する信号の検出を行って前記対象物の位置を計測する計測装置とを有する装置であって、

1周期の中に所定周期の信号を出力する第1期間と一定値の信号を出力する第2期間を含んでおり、前記対象物の位置の出力用位置データを要求する要求信号に基づいて、該要求信号の周期より短い周期を有する第1クロック信号を生成するクロック生成部と、

前記第1クロック信号の周期ごとに前記検出を行う検出部と、

前記検出部の出力に基づいて、前記対象物の処理用位置データを得る演算部と、

前記演算部からの複数の前記処理用位置データに基づいて単位時間当たりの前記対象物

50

の変位量を得、前記出力用位置データの要求信号が受信される前に前記出力用位置データのための計測が開始された時点と前記出力用位置データの前記要求信号が受信された時点との間の時間差と、前記変位量に基づいて、前記演算部が得た処理用位置データのうち補正対象の処理用位置データを補正する補正部と、

を有しており、

前記クロック生成部は、前記第1期間では、前記要求信号に含まれる前記所定周期の信号に同期した前記第1クロック信号を出力し、前記第2期間では、前記第1期間に出力した前記要求信号の周期より短い周期を有する第1クロック信号を継続して出力するように動作が維持される位相同期部を含む、

ことを特徴とする装置。

10

#### 【請求項10】

対象物の位置を計測する、請求項1乃至6いずれか1項に記載の計測装置と、

該計測装置に出力用位置データの要求信号を送信するシステムと、

を備えることを特徴とする産業用装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、計測装置、計測方法、および処理装置に関する。

##### 【背景技術】

##### 【0002】

従来、位置や角度を計測する計測装置として、出力形式の異なるインクリメンタルエンコーダやアブソリュートエンコーダが存在する。例えば、位置計測を行うリニアエンコーダとして、相対的な位置（位置の変化、または変位）を計測するインクリメンタルリニアエンコーダや絶対位置を計測するアブソリュートリニアエンコーダがある。さらに、角度計測を行うロータリーエンコーダとして、相対的な角度（角度の変化、または変位）を計測するインクリメンタルロータリーエンコーダや絶対角度を計測するアブソリュートロータリーエンコーダがある。また、動作原理がそれぞれ異なる光学式エンコーダや磁気式エンコーダが存在する。このうち、光学式エンコーダは、光源からの光をスケールに照射して、スケールからの透過光または反射光を光電変換素子で受光する。光源および光電変換素子は、移動または回転する対象物に取り付けられ、スケールは、基準となる固定側に取り付けられるが、またその逆もある。インクリメンタルエンコーダでは、スケールに等間隔の透過膜または反射膜が加工されており、受光強度が一定周期の正弦波となる。信号処理部は、検出された正弦波信号の波数をカウントする。そして、周期内の位相を細かく分割することで、計測分解能と精度とを向上させている。一方、アブソリュートエンコーダでは、スケールに擬似乱数コードを有する透過膜または反射膜が加工され、擬似乱数コードを伴った受光強度を検出する。信号処理部は、参照テーブルを用いて擬似乱数コードに対する絶対位置または絶対角度を算出する。そして、擬似乱数コードの位相を細かく分割することで、計測分解能と精度とを向上させている。

20

##### 【0003】

一般に、これらのエンコーダによる位置または角度の計測データは、外部の上位システムからのデータ要求信号に応じて上位システムに送信される。例えば、上位システムは、エンコーダを用いる産業用装置であって、エンコーダから得られた計測データに基づいて対象物の位置決め制御を実行する。ここで、このようなエンコーダでは、対象物が移動している場合、計測の遅延時間に起因した、すなわち移動速度と遅延時間との積による計測誤差が発生し得る。この計測誤差を補正する技術として、特許文献1は、前にサンプリングされた位置データを用いて位置データを出力するのに要する遅延時間における対象物の移動量を見積もり、今回サンプリングされた位置データを補正するエンコーダを開示している。また、特許文献2は、外部からのデータ要求に対し、A/D変換のサンプリングからデータ要求までの時間を測定し、データ要求の前後の位置データを補間して位置データを出力するエンコーダ出力の内挿方法を開示している。

40

50

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開平8-261794号公報

【特許文献2】特開2007-71865号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

近年、産業用装置などでは、より高精度な位置または角度の計測が要求される一方、対象物の移動速度または回転速度が高速化している。これに伴い、エンコーダにおける計測の遅延時間による計測誤差が増加しつつあり、高精度な計測を困難としている。ここで、特許文献1に示すエンコーダは、上位システムからのデータ要求信号により計測を開始して信号処理を行い、遅延時間による誤差を補正して出力する。しかしながら、対象物が加速度運動を行っている場合、位置誤差を補正するために用いる速度情報と、対象物の実際の速度との誤差が大きくなり、正確な位置または角度を出力することが難しい。一方、特許文献2に示すエンコーダは、データ要求の前後の位置データが必要となるところ、位置データを出力する時間間隔が粗いと、位置データの補間精度が悪化し、正確な位置または角度を出力することが難しい。これに対して、上位システムからのデータ要求信号の周期を短くすると、エンコーダからの出力データ量が増加するため、上位システムでの演算負荷が増加する。その結果、上位システムが複雑かつ高価なものとなる。

10

**【0006】**

本発明は、このような状況に鑑みてなされたものであり、例えば、高速で変位する対象物に対する変位計測精度の点で有利な計測装置を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

上記課題を解決するために、本発明は、対象物の変位に伴って変化する信号の検出を行って対象物の位置を計測する計測装置であって、1周期の中に所定周期の信号を出力する第1期間と一定値の信号を出力する第2期間を含んでおり、対象物の位置の出力用位置データを要求する要求信号に基づいて、該要求信号の周期より短い周期を有する第1クロック信号を生成するクロック生成部と、第1クロック信号の周期ごとに検出を行う検出部と、検出部の出力に基づいて、対象物の処理用位置データを得る演算部と、演算部からの複数の処理用位置データに基づいて単位時間当たりの対象物の変位量を得、出力用位置データの要求信号が受信される前に出力用位置データのための計測が開始された時点と出力用位置データの要求信号が受信された時点との間の時間差と、変位量とに基づいて、演算部が得た処理用位置データのうち補正対象の処理用位置データを補正する補正部と、を有しており、クロック生成部は、第1期間は、要求信号に含まれる所定周期の信号に同期した第1クロック信号を出力し、第2期間は、第1期間に出力した要求信号の周期より短い周期を有する第1クロック信号を継続して出力するように動作が維持される位相同期部を含む、ことを特徴とする。

20

**【発明の効果】****【0008】**

本発明によれば、例えば、高速で変位する対象物に対する変位計測精度の点で有利な計測装置を提供することができる。

30

**【図面の簡単な説明】****【0009】**

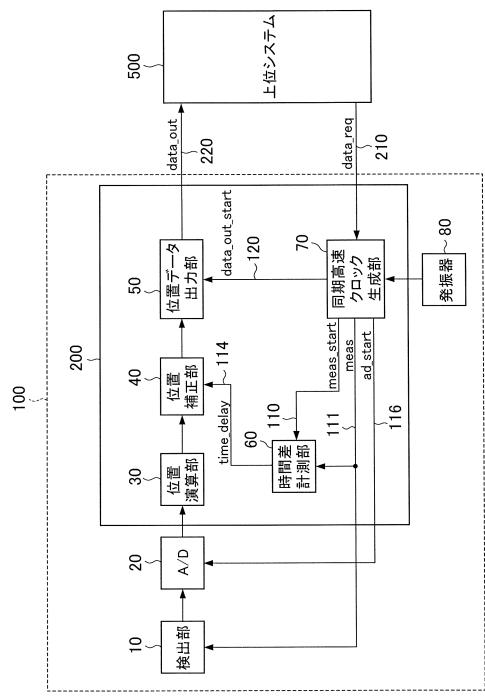

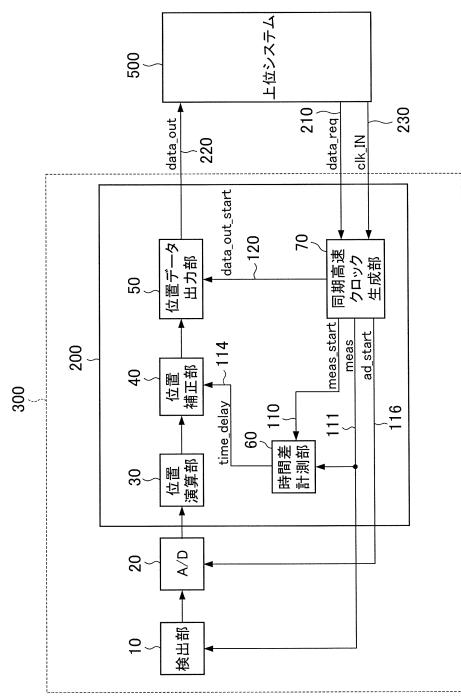

【図1】本発明の第1実施形態に係るエンコーダの信号処理系を示す図である。

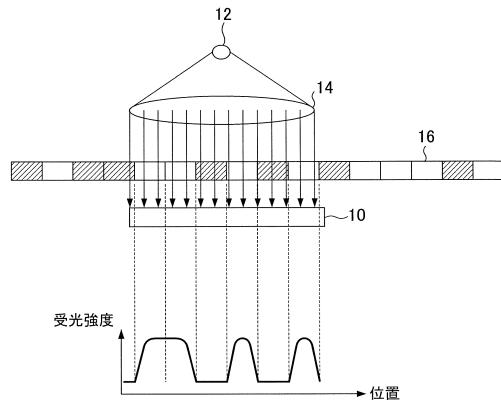

【図2】第1実施形態に係るエンコーダの光学系の構成などを示す図である。

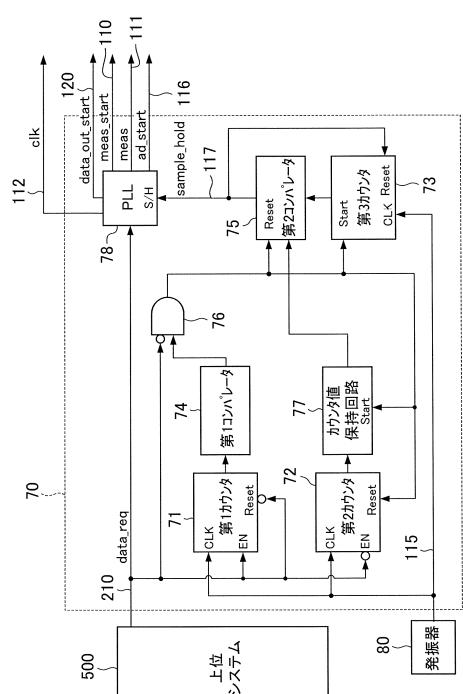

【図3】同期高速クロック生成部の構成を示す図である。

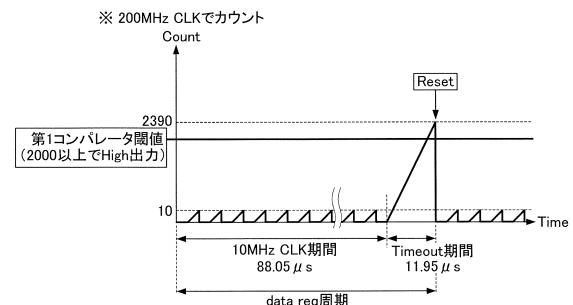

【図4】同期高速クロック生成部内の第1カウンタの動作を示す図である。

【図5】同期高速クロック生成部内の第2カウンタの動作を示す図である。

40

50

【図6】同期高速クロック生成部内のPLLの構成を示す図である。

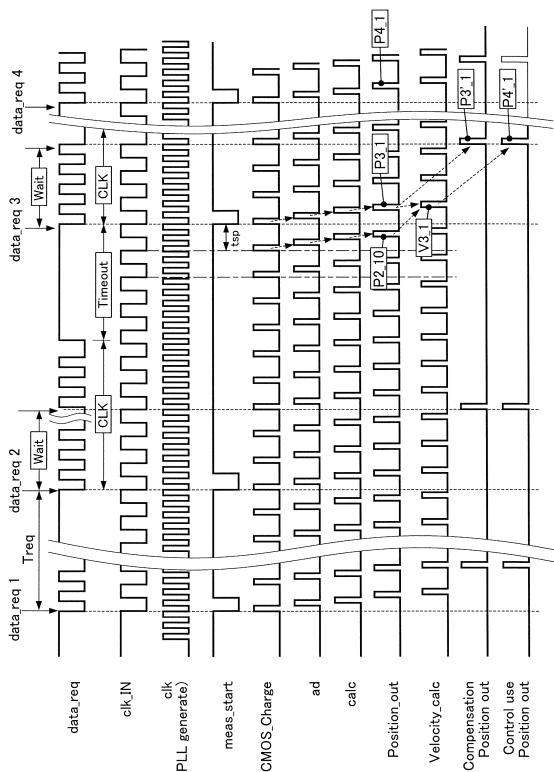

【図7】第1実施形態における各部の動作タイミングを表すタイミング図である。

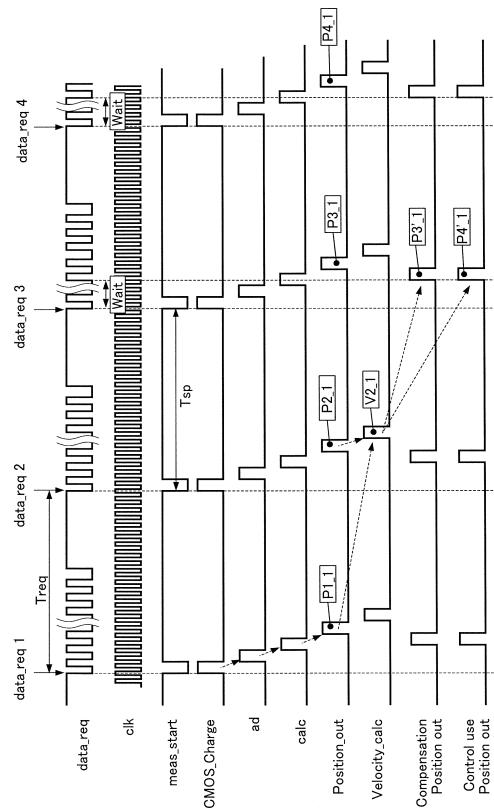

【図8】第1実施形態における各部の動作タイミングを表すタイミング図である。

【図9】第1実施形態における対象物の加速度変動を示すグラフである。

【図10】第1実施形態と従来との場合を比較した位置誤差を示すグラフである。

【図11】第1実施形態におけるTspに対する位置誤差を示すグラフである。

【図12】本発明の第2実施形態に係るエンコーダの信号処理系を示す図である。

【図13】第2実施形態における各部の動作タイミングを表すタイミング図である。

【図14】従来の各部の動作タイミングを表すタイミング図である。

【発明を実施するための形態】

10

【0010】

以下、本発明を実施するための形態について図面などを参照して説明する。

【0011】

(第1実施形態)

まず、本発明の第1実施形態に係る計測装置について説明する。本実施形態に係る計測装置は、対象物（計測対象物）の変位に伴って変化する信号を検出して変位を計測する、いわゆるエンコーダであり、以下、対象物の位置の変化、または変位を計測する光学式のアブソリュートエンコーダを例に説明する。なお、本発明の計測装置は、このような位置の変化、もしくは変位を計測するエンコーダに限らず、角度の変化、もしくは変位を計測するエンコーダ、またはインクリメンタルエンコーダにも適用可能である。

20

【0012】

図1は、本実施形態に係るエンコーダ100の信号処理系の構成を示すブロック図である。まず、エンコーダ100に対して位置データ（計測データ）を要求する信号（以下、「データ要求信号」という。）を送信するとともに、データ要求のタイミングで計測された位置データを受信する上位システム500について説明する。上位システム500は、エンコーダ100から得られた位置データを利用する処理装置（以下、その制御部という意味でも用いる）に相当する。ここで、「処理装置」とは、具体的には、対象物の特性の計測を行う計測装置、対象物を（非破壊）検査する検査装置、または対象物を加工する加工装置などである。すなわち、上位システム500は、例えば、単に位置データを収集したり解析したりする計測装置または検査装置のデータ収集解析部ともなるし、得られた位置データに基づいて、さらに位置決め制御を実行する加工装置の制御部ともなる。上位システム500が位置決め制御部であるとすると、位置決め制御の制御帯域は、数十～数百Hz程度である。また、データ要求の周期は、1ms～100μs、すなわち周波数は、1kHz～10kHz程度である。例えば、10kHzのデータ要求で位置決め制御をする場合には、上位システム500は、100μs間に位置データを取得し、それに基づいて、例えばPID制御のような制御演算を実行する。一般的に、上位システムは、よりデータ要求周期を短くしようとすると、100μsよりも短い時間間隔で制御演算を行なわなければならず、演算負荷が増加する。これは、上位システムにはそれに伴う高性能化が要求され、上位システム自体が高価かつ複雑なものとなることを意味する。したがって、一般的な上位システムでも、上記のとおり、データ要求の周期を1ms～100μsとするのが妥当である。そして、上位システム500は、その制御演算により算出された結果に基づいてアクチュエータを動作させ、位置決めを実施させる。

30

【0013】

なお、上位システム500がデータ収集解析部である場合には、エンコーダ100がデータ要求信号を出力した時点での正確な位置データが必要な（取得すべき）情報である。これに対して、上位システム500が位置決め制御を実行する制御部である場合には、エンコーダ100がデータ要求信号を出力した次のクロック以降で位置決め制御が実行されるので、この位置決め制御が行なわれる時点での正確な位置データが必要な情報である。そこで、以下、まず上位システム500が位置データを収集する（取得する）ものであるとして説明し、引き続き、その取得した位置データに基づいて位置決め制御を実行する場

40

50

合について説明する。

**【0014】**

図2は、エンコーダ100の光学系の構成と、検出される光の強度（受光強度）とを関係付けて示す図である。エンコーダ100は、例えば、検出部10と、光源12と、コリメータレンズ14と、スケール16とを備える。検出部10は、例えばCMOSイメージセンサやCCDセンサなどの光電変換素子とし得るが、それには限定されず、計測方式に応じて種々の変更が可能である。光源12は、例えばLEDであり、光をコリメータレンズ14を介して平行光とした上でスケール16に照射する。エンコーダ100は、ここではアブソリュートエンコーダとしているので、スケール16には、擬似乱数コード、例えばM系列巡回符号が加工されている。なお、スケール16は、エンコーダ100のように位置を計測するリニアエンコーダの場合には一方向に延びた板状部材であるが、角度を計測するロータリーエンコーダの場合には円板状部材とし得る。透過または反射によりスケール16を出射した光は、擬似乱数コードによる受光強度を有し、検出部10は、この光を受光する。受光強度は、図2中のグラフに示すように、スケール16に形成されている擬似乱数コードを反映した強弱信号となる。また、光源12および検出部10は、移動（または回転する）対象物に取り付けられ、スケール16は、基準となる固定側に取り付けられているが、その逆でもよい。10

**【0015】**

図1に戻り、検出部10の後段には、不図示の電流／電圧変換器が構成され、受光強度を電圧信号に変換する。また、検出部10は、さらに必要に応じて後段に電圧増幅器を置き、信号を所定の電圧レベルまで増幅する。A/D変換器20は、検出部10からの信号をA/D変換し、アナログ信号をデジタル信号に変換する。20

**【0016】**

信号処理部200は、A/D変換器20から受信したデジタル信号を処理するものであり、FPGA、ASICまたはDSPなどの高速なデジタル信号処理器である。なお、FPGAは、Field-Programmable Gate Arrayの略記である。ASICは、Application Specific Integrated Circuitの略記である。そして、DSPは、Digital Signal Processorの略記である。信号処理部200は、位置演算部30と、位置補正部40と、位置データ出力部50と、時間差計測部60と、同期高速クロック生成部70とを含む。30

**【0017】**

位置演算部（演算部）30は、A/D変換器20からの信号を受けて、位置データを算出する。例えばアブソリュートエンコーダでは、位置演算部30は、図2に示すような擬似乱数コードを反映した強弱信号より、0と1とで表される擬似乱数コードを再生する。そして、位置演算部30は、その内部に保有する不図示の擬似乱数コードに対する絶対位置の参照テーブルと照合し、検出された擬似乱数コードに対する絶対位置を求める。さらに、位置演算部30は、擬似乱数コードの位相を細かく分割することにより、計測分解能を向上させている。

**【0018】**

同期高速クロック生成部（クロック生成部）70は、meas信号111、meas\_start信号110、ad\_start信号116およびdata\_out\_start信号120を生成する。また、同期高速クロック生成部70は、位置演算部30や位置補正部40における演算用のクロック信号（clock信号112：図3参照）も生成する。40

**【0019】**

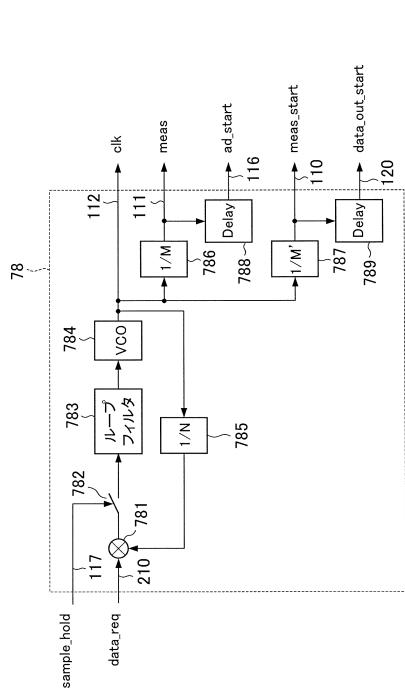

図3は、同期高速クロック生成部70の構成を示すブロック図である。同期高速クロック生成部70は、3つのカウンタ（第1カウンタ71～第3カウンタ73）と、2つのコンパレータ（第1コンパレータ74、第2コンパレータ75）と、論理積回路76と、カウンタ値保持回路77と、位相同期部（PLL78）とを含む。同期高速クロック生成部70には、上位システム500からデータ要求信号としてdata\_req信号210が入力される。data\_req信号210は、所定の周波数のクロック信号の期間（第150

期間)と、所定時間一定の電圧(一定値)となる期間(第2期間)とを合わせて1周期となる間欠的な信号である。例えば、data\_req信号210として、BiSS-Cオープンプロトコルに基づく信号とし得る。以下、上記の第1の期間を「クロック(CLK)期間」といい、第2の期間を「タイムアウト(Timeout)期間」という。さらに、data\_req信号210は、PLL78、論理積回路76、第1カウンタ71および第2カウンタ72に入力される信号へと分けられる。まず、同期高速クロック生成部70は、data\_req信号210に基づいて、位相同期部を用いてmeas信号111を生成する。meas信号111は、data\_req信号210に同期した、位置計測用の高速クロック信号(第1のクロック信号)である。また、位相同期部は、例えばPLL(Phase Locked Loop:以下「PLL78」と表記する。)である。

なお、data\_req信号210は、タイムアウト期間を含んだ間欠的な信号であるから、そのままPLL78に入力して分周器により高遅倍のクロック信号を生成しようとすると、タイムアウト期間にて同期が外れ、クロック精度が低下する。そこで、タイムアウト期間では、PLL78の動作をホールドするような処理を実行することで、タイムアウト期間の影響を受けないようにする必要がある。

#### 【0020】

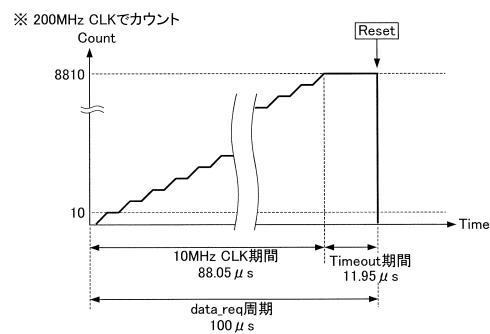

第1カウンタ71は、data\_req信号210のハイ期間を発振器80からのクロック信号115によりカウントし、data\_req信号210がローとなったときにリセットする。図4は、第1カウンタ71の動作を示す図であり、横軸が時間、縦軸がカウント数である。ここで、data\_req信号210の周期は、100μsである。data\_req信号210のクロック期間は、88.05μsであり、このクロック期間におけるクロック信号の周波数は、10MHzである。一方、data\_req信号210のタイムアウト期間は、11.95μsである。そして、発振器80より出力されるクロック信号115の周波数は、200MHzである。この例では、第1カウンタ71は、data\_req信号210のクロック期間におけるロー期間(50ns)ではカウントしない。そして、第1カウンタ71は、ハイ期間(50ns)で10カウントまでカウントした時点でdata\_req信号210がローとなり、リセットされる。これを繰り返すことで、第1カウンタ71のカウント動作は、図4に示すような鋸歯状となる。なお、例えば、data\_req信号210のクロック期間におけるクロック周波数が0.1MHzの場合には、第1カウンタ71のカウント動作は、同様に1000カウントごとの鋸歯状となる。また、タイムアウト期間では、data\_req信号210がハイであるため、第1カウンタ71は、カウントし続ける。そして、第1カウンタ71が2390カウントまでカウントした時点でdata\_req信号210の1周期分の時間が経過して、data\_req信号210がローとなり、第1カウンタ71はリセットされる。

#### 【0021】

第1コンパレータ74は、第1カウンタ71のカウント値と、第1コンパレータ74が持つ閾値とを比較し、閾値よりもカウント値が大きい場合にハイを出力する。第1コンパレータ74の閾値は、クロック期間でのカウント値では超えることがなく、かつタイムアウト期間でのカウント値でのみ超えるような値に設定される。図4に示す例では、第1コンパレータ74の閾値を2000カウントとしている。

#### 【0022】

論理積回路76は、第1コンパレータ74の出力と、data\_req信号210のローとの論理積演算を実行する。上記のとおり、第1コンパレータ74は、data\_req信号210のタイムアウト期間中にハイを出力する。そして、第1コンパレータ74がハイを出力した後にdata\_req信号210がローとなるのは、タイムアウト期間が終了する時点、すなわちdata\_req信号210の1周期分の時間が経過した時点となる。論理積回路76は、このdata\_req信号210の1周期分の時間が経過した時点と同期してハイを出力する。論理積回路76の出力は、後述する第2カウンタ72のリセット信号、カウンタ値保持回路77のスタート信号、および第3カウンタ73のスタート信号として用いられる。

## 【0023】

第2カウンタ72は、第1カウンタ71とは反対に、data\_req信号210のロー期間を、発振器80からのクロック信号115によりカウントする。また、第2カウンタ72は、論理積回路76の出力によりリセットされる。図5は、第2カウンタ72の動作を示す図であり、横軸が時間、縦軸がカウント数である。なお、data\_req信号210、および発振器80からのクロック信号115の条件は、上記の第1カウンタ71の動作を説明した際のものと同一とする。この例では、第2カウンタ72は、data\_req信号210のクロック期間におけるロー期間(50ns)で10カウントまでカウントし、その後のハイ期間(50ns)ではカウントせずに値を保持する。そして、第2カウンタ72は、さらに次のロー期間(50ns)でさらに10カウント加えた20カウントまでカウントする。これを繰り返すことで、第2カウンタ72のカウント動作は、図5に示すような階段状となる。なお、例えば、data\_req信号210のクロック期間におけるクロック周波数が0.1MHzの場合には、第2カウンタ72のカウント動作は、同様に1000カウントごとの階段状となる。また、タイムアウト期間では、data\_req信号210がハイであるため、第2カウンタ72は、カウントせずに値を保持し続ける。そして、このカウント値を最終カウント値とする。上記の条件では、最終カウント値は、8810カウントとなる。そして、論理積回路76のハイ出力時点、すなわちdata\_req信号210の1周期分の時間が経過した時点で、第2カウンタ72はリセットされる。

## 【0024】

カウンタ値保持回路77は、最終カウント値、例えば、論理積回路76の出力をスタート信号としたその時点でのカウント値を保持する。なお、カウンタ値保持回路77は、第2カウンタ72がリセットした後のカウント値を保持してしまわないよう、第2カウンタ72の出力を遅延させて入力されるように構成してもよい。また、カウンタ値保持回路77は、図3に示す構成とは異なるが、第1コンパレータ74の出力をスタート信号としてカウント値を保持するような構成としてもよい。このように得られた最終カウント値は、data\_req信号210のクロック期間の長さを示す値となる。また、最終カウント値は、後述する第2コンパレータ75の閾値として用いられる。

## 【0025】

第3カウンタ73は、カウントのスタート信号として論理積回路76の出力が入力されて、data\_req信号210の1周期分の時間が経過した時点で、すなわちデータ要求時点からカウントを開始する。また、第3カウンタ73には、カウントの基準となるクロックとして、第1カウンタ71および第2カウンタ72と同様に、発振器80からのクロック信号115が入力される。

## 【0026】

第2コンパレータ75は、第3カウンタ73のカウント値と、第2コンパレータ75が持つ閾値とを比較する。第2コンパレータ75の閾値は、カウンタ値保持回路77から出力される最終カウント値となるように設定される。第2コンパレータ75は、第3カウンタ73のカウント値が第2コンパレータ75の閾値を超えない間、すなわちdata\_req信号210のクロック期間にはローを出力する。その後、第2コンパレータ75は、第3カウンタ73のカウント値が第2コンパレータ75の閾値を超える時間、すなわちdata\_req信号210のタイムアウト期間となるとハイを出力する。この第2コンパレータ75からハイが出力された時点で、第3カウンタ73はリセットされる。そして、第3カウンタ73は、再びスタート信号が入力されるまで、すなわちdata\_req信号210の1周期分の時間が経過するまではカウントを停止する。ただし、第2コンパレータ75は、論理積回路76の出力を受けてリセットされるまで、すなわちdata\_req信号210の1周期分の時間が経過するまではハイを出力し続ける。第2コンパレータ75の出力は、PLL78にてサンプル動作とホールド動作とを切り替える制御信号として用いられる。以下、この第2コンパレータ75の出力を、sample\_hold信号117と表記する。

10

20

30

40

50

**【0027】**

P L L 7 8 は、 s a m p l e \_ h o l d 信号 1 1 7 がローの間、すなわち d a t a \_ r e q 信号 2 1 0 のクロック期間には、サンプル動作する。一方、 P L L 7 8 は、 s a m p l e \_ h o l d 信号 1 1 7 がハイの間、すなわち d a t a \_ r e q 信号 2 1 0 のタイムアウト期間には、ホールド動作する。図 6 は、 P L L 7 8 の構成を示すブロック図である。P L L 7 8 は、位相比較器 7 8 1 と、サンプル／ホールド切替器 7 8 2 と、ループフィルタ 7 8 3 と、電圧制御発振器 7 8 4 と、第 1 分周器 7 8 5 と、第 2 分周器 7 8 6 と、第 3 分周器 7 8 7 と、第 1 遅延回路 7 8 8 と、第 2 遅延回路 7 8 9 とを含む。

**【0028】**

位相比較器 7 8 1 は、入力信号 ( d a t a \_ r e q 信号 2 1 0 ) と出力信号 ( c l k 信号 1 1 2 ) とを比較するように、フィードバックループを構成する。そして、位相比較器 7 8 1 は、入力信号と出力信号との位相比較を行い、その位相差を位相差信号として出力する。ループフィルタ 7 8 3 は、積分回路であり、短周期変動の除去を行う。電圧制御発振器 ( V C O ) 7 8 4 は、ループフィルタ 7 8 3 から入力された位相差信号に基づいて、発振周波数を調整し、 c l k 信号 1 1 2 を出力する。なお、 c l k 信号 1 1 2 は、上記のとおり位置演算部 3 0 や位置補正部 4 0 における演算用のクロック信号となる。

**【0029】**

まず、 d a t a \_ r e q 信号 2 1 0 のクロック期間、すなわち s a m p l e \_ h o l d 信号 1 1 7 がローの間は、サンプル／ホールド切替器 7 8 2 がオンとなり、位相比較器 7 8 1 のフィードバックループが構成される。このとき、 P L L 7 8 は、サンプル動作となる。フィードバックされる出力信号は、第 1 分周器 7 8 5 により分周された後、位相比較器 7 8 1 に入力されて、 d a t a \_ r e q 信号 2 1 0 のクロック信号と比較される。そして、電圧制御発振器 7 8 4 は、 d a t a \_ r e q 信号 2 1 0 のクロック周波数を遙倍した信号を出力する。例えば、クロック周波数が 1 0 M H z で、第 1 分周器 7 8 5 の分周比 ( 1 / N ) が 1 / 2 0 であるとすると、電圧制御発振器 7 8 4 は、クロック信号に同期した周波数 2 0 0 M H z の信号を出力する。このように、 P L L 7 8 は、 d a t a \_ r e q 信号 2 1 0 のクロック信号に同期した高周波の第 2 のクロック信号 ( c l k 信号 1 1 2 ) を出力することができる。

**【0030】**

一方、 d a t a \_ r e q 信号 2 1 0 のタイムアウト期間、すなわち s a m p l e \_ h o l d 信号 1 1 7 がハイの間は、サンプル／ホールド切替器 7 8 2 がオフとなり、位相比較器 7 8 1 のフィードバックループは構成されない。このとき、 P L L 7 8 は、ホールド動作となる。この場合、電圧制御発振器 7 8 4 は、新たな位相差信号が入力されないため、 d a t a \_ r e q 信号 2 1 0 のクロック期間に調整された発振周波数の信号を継続して出力する。したがって、 P L L 7 8 は、タイムアウト期間における一定時間固定の電圧による影響を受けることなく、 d a t a \_ r e q 信号 2 1 0 のクロック信号に同期した第 2 のクロック信号 ( c l k 信号 1 1 2 ) を出力することができる。

**【0031】**

なお、 c l k 信号 1 1 2 は、 P L L 7 8 にて生成するものに限らず、例えば、発振器 8 0 などの外部のクロックを用いてもよい。この場合、 c l k 信号 1 1 2 は、 d a t a \_ r e q 信号 2 1 0 と非同期となるが、 c l k 信号 1 1 2 の周波数が 2 0 0 M H z の場合には最大で 1 周期 5 n s の同期ずれがあるものの、この同期ずれによる計測誤差は極めて小さいため、影響は無視できる。

**【0032】**

また、 P L L 7 8 は、 c l k 信号 1 1 2 を第 2 分周器 7 8 6 で分周することで、 d a t a \_ r e q 信号 2 1 0 と同期した位置計測用の高速クロック信号である m e a s 信号 1 1 1 を生成する。例えば、第 2 分周器 7 8 6 の分周比 ( 1 / M ) を 1 / 2 0 0 0 とすると、 m e a s 信号 1 1 1 は、 d a t a \_ r e q 信号 2 1 0 と同期した周波数 1 0 0 k H z の信号となる。また、 P L L 7 8 は、第 1 遅延回路 7 8 8 を用いて m e a s 信号 1 1 1 を検出部 1 0 にて位置計測開始から位置計測終了までの時間分遅延させることで、 A / D 変換器

10

20

30

40

50

【 0 0 3 3 】

なお、PLLは、一般的に入力に対して位相をロックするまでに所定の時間が必要となる。そのため、PLL78は、位相をロックして安定的に動作するまでの間は、データ要求に対してエラー信号を返すように構成する。そして、位相比較器781の出力をモニタすることで、PLL78が位相をロックして安定的に動作しているかどうかを確認することができる。例えば、位相比較器781の出力がほぼゼロとなれば、PLL78が位相をロックして安定的に動作していることがわかる。

[ 0 0 3 4 ]

図 1 の説明に戻り、検出部 10 は、同期高速クロック生成部 70 から受信した `meas` 信号 111 の周期ごとに位置計測を行う。また、A/D 変換器 20 は、同期高速クロック生成部 70 から受信した `ad_start` 信号 116 により A/D 変換を開始する。

[ 0 0 3 5 ]

時間差計測部 60 は、同期高速クロック生成部 70 から受信した `meas_start` 信号 110 と `meas` 信号 111 とに基づいて、位置データを補正するための補正遅延時間 (`Tsp`) を計測し、`time_delay` 信号 114 として出力する。なお、補正遅延時間がエンコーダ 100 の設計値から求め求まる場合には、その値を用いることとし、時間差計測部 60 を構成する必要はない。

[ 0 0 3 6 ]

位置補正部（補正部）40は、time\_delay信号114を用いて、少なくとも2つの位置データの単位時間当たり（meas信号111の1周期当たり）の変化量（変位量）より速度に関係した信号を算出する。そして、位置補正部40は、算出した信号と補正遅延時間との積により位置演算部30で算出された、補正対象の位置データを補正する。ここで補正された補正位置データは、位置データ出力部50に一旦格納されて、同期高速クロック生成部70から受信したdata\_out\_start信号120に同期し、data\_out信号220として上位システム500へ出力される。

( 0 0 3 7 )

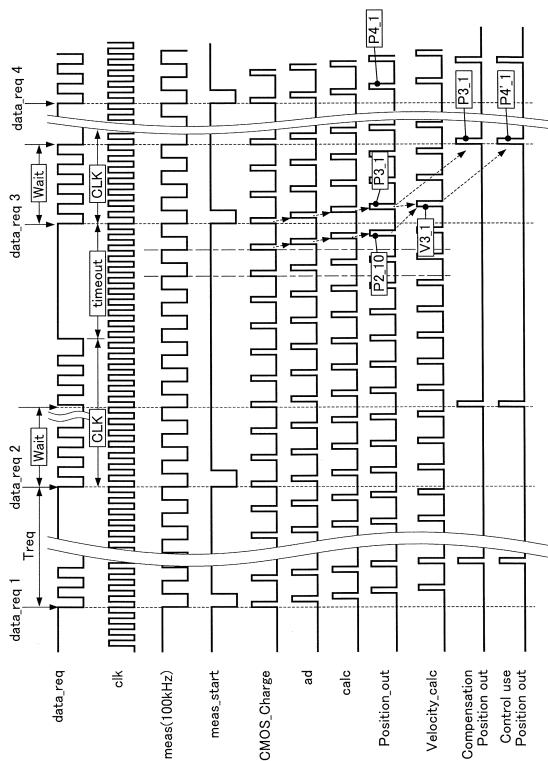

次に、エンコーダ100における各部の動作タイミングおよび信号処理について説明する。図7は、各部の動作タイミングを表すタイミング図である。まず、「data\_req」は、data\_req信号210である。ここで、data\_reqの表記に関し、データ要求周期Treq(data\_req1, 2, 3点の時間間隔)は、100μsを想定している。両矢印で表す範囲「CLK」は、data\_req信号210のクロック期間を示す。両矢印で表す範囲「Timeout」は、data\_req信号210のタイムアウト期間を示す。両矢印で表す範囲「Wait」は、データ要求時点から実際に計測データが出力されるまでの待ち時間(以下、「Wait時間」という。)である。なお、これらの値は、上位システム500とエンコーダ100との通信プロトコルにより決定される。「clk」は、clk信号112であり、ここでは周波数200MHzとする。「meas(100kHz)」は、meas信号111であり、ここでは周波数100MHzとする。「meas\_start」は、meas\_start信号110であり、ここではデータ要求周期Treqと同じ100μs周期とする。「CMOS\_Charge」は、検出部10にて実際に位置データを取得している時間であり、例えば、CMOSイメージセンサの受光時間である。このCMOS\_Chargeは、meas信号111により開始され、検出部10は、そのmeas信号111の周期ごとに位置データを取得す

る。「ad」は、検出部10から出力されたアナログデータを、`ad_start`信号116を受信してA/D変換器20にてA/D変換を開始してからA/D変換が終了するまでの時間である。「calc」は、A/D変換器20から出力されたデジタルデータに基づいて、位置演算部30にて位置データを演算する時間である。そして、「Position\_out」は、位置演算部30から位置データが出力される時間である。

#### 【0038】

次に、図7を用いて、特に位置補正の演算に関わる動作タイミングおよび信号処理について説明する。まず、位置計測開始から補正位置データ演算までの処理時間が`Wait`時間よりも短い場合について説明する。例えば、位置計測開始から位置データ演算までの処理時間を10μs、`Wait`時間を30μsと想定し、上位システム500が図7における`data_req3`の時点での位置を得たい場合について考える。この場合、`Wait`時間中に位置データ演算までの処理が終了するため、`data_req3`の時点で取得した位置データ`P3_1`をそのまま出力する。すなわち、エンコーダ100は、補正処理をすることなく、`data_req3`の時点で計測した位置データを出力する。10

#### 【0039】

一方、上位システム500が、取得した位置データを用いて位置決め制御を実行する制御部である場合について説明する。例えば、`data_req3`の時点での計測要求に対し、実際に制御に使われるものが、次のクロックタイミングである`data_req4`の時点となる場合を考える。この場合、`data_req3`の時点での計測要求に対して、`data_req4`の時点での位置データ`P4_1`を予測した制御時補正位置データ`P4'_1`を出力する必要がある。20

#### 【0040】

ここで、制御時補正位置データの算出方法について説明する。まず、図7において、「Velocity\_calc」は、今回取得した位置データと前回取得した位置データに基づいて、今回の位置データを取得した時点での対象物の移動速度を演算する時間である。ここで、移動速度は、以下の式(1)により求められる。

$$\text{移動速度 [m/s]} = (\text{今回の位置データ [m]} - \text{前回の位置データ [m]}) / \text{位置計測周期 [s]} \quad (1)$$

例えば、位置データ`P3_1`の時点での速度`V3_1`を求める場合には、式(1)は、以下の式(2)のようになる。ただし、位置計測周期は、10μs(`meas`信号111の周波数100kHzより)である。30

$$V3_1 [\text{m/s}] = (P3_1 [\text{m}] - P2_10 [\text{m}]) / 10 [\mu\text{s}] \quad (2)$$

#### 【0041】

また、図7において、「control\_use Position\_out」は、この移動速度に基づいて制御時補正位置データを演算し、出力する時間である。そして、制御時補正位置データは、以下の式(3)により求められる。

$$\text{制御時補正位置データ [m]} = \text{今回の位置データ [m]} + \text{移動速度 [m/s]} \times \text{制御時点との時間差 [s]} \quad (3)$$

例えば、制御時補正位置データ`P4'_1`は、以下の式(4)により求められる。ただし、ここでは制御時点との時間差を100μsとしている。40

$$P4'_1 [\text{m}] = P3_1 [\text{m}] + V3_1 [\text{m/s}] \times 100 [\mu\text{s}] \quad (4)$$

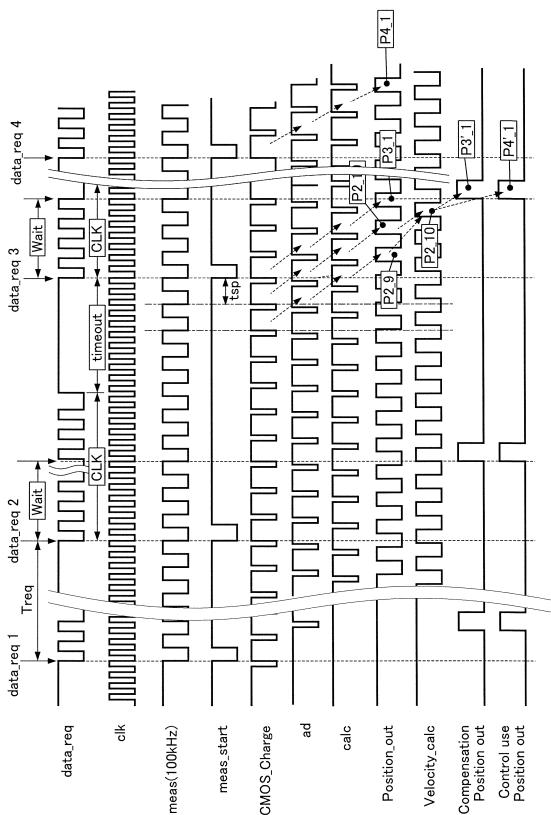

#### 【0042】

次に、図8を用いて、位置計測開始から補正位置データ演算までの処理時間が`Wait`時間よりも長い場合について説明する。以下、一例として、位置計測開始から位置データ演算までの処理時間を30μsとし、`Wait`時間を上記と同様に30μsと想定する。図8は、図7に対応した、この場合のタイミング図である。ここでも、上位システム500が図8の`data_req3`の時点での位置を知りたい場合を考える。図8に示すように、`data_req3`の時点での位置データ`P3_1`を出力するまでの処理は、図7に示す場合と異なり、`Wait`時間中に終わらない。すなわち、エンコーダ100は、位置データ`P3_1`をそのまま出力することができない。そこで、この場合には、`data_`50

`r eq 3` の時点での位置データ  $P_{3\_1}$  を予測した、計測時補正位置データ  $P_{3'\_1}$  を出力する必要がある。

#### 【0043】

この場合の計測時補正位置データを求める式は、上記式(3)と類似し、以下の式(5)となる。

$$\text{計測時補正位置データ [m]} = \text{今回の位置データ [m]} + \text{移動速度 [m/s]} \times T_{sp} [s] \quad (5)$$

ただし、移動速度を求める式は、上記式(1)と同一である。また、 $T_{sp}$  は、図8にも示すとおり、今回の位置データの計測開始時点とデータ要求時点との時間差であり、図1では、`time_delay` 信号 114 として、時間差計測部 60 から位置補正部 40 へと入力される。

10

#### 【0044】

ここで、 $T_{sp}$  を求める方法について説明する。まず、エンコーダ 100 の初期動作として、時間差計測部 60 は、データ要求周期  $T_{req}$  間における `meas` 信号 111 のクロック数をカウントする。これにより、時間差計測部 60 は、データ要求周期  $T_{req}$  の間に `meas` 信号 111 が何クロック含まれるかを認識できる。このクロック数を「全クロック数」とすると、図8の例における全クロック数は、10クロックとなる。なお、`meas` 信号 111 は、同期高速クロック生成部 70 で、`data_req` 信号 210 に基づいて生成される信号であるから、全クロック数は、同期高速クロック生成部 70 の設計値からもわかる。したがって、全クロック数を設計値から得る場合には、上記のとおり、時間差計測部 60 を構成する必要はない。そして、位置補正部 40 は、位置データ情報にデータ要求時点から何クロック目に計測されたデータかを示す情報を付加し、これを今クロック番号とする。例えば、図8の位置データ  $P_{2\_10}$  では、今クロック番号は、10となる。これにより、位置補正部 40 は、以下の式(6)より、その位置データ情報がデータ要求時点に対していくつ前のクロックかを認識できる。このクロックを「補正值演算基準クロック数」とする。

20

$$\text{補正值演算基準クロック番号} = (\text{全クロック数} + 1) - \text{今クロック番号} \quad (6)$$

例えば、位置データ  $P_{2\_10}$  については、 $10 + 1 - 10 = 1$  より、補正值演算基準クロック番号は 1 となる。すなわち、位置データ  $P_{2\_10}$  は、データ要求時点に対して 1 つ前のクロックで計測した位置データということになる。最終的に、 $T_{sp}$  は、以下の式(7)により求められる。

30

$$T_{sp} [s] = \text{meas} \text{ 信号の周期 [s]} \times \text{補正值演算基準クロック番号} \quad (7)$$

例えば、図8の  $T_{sp}$  は、以下の式(8)のように求められる。

$$T_{sp} [s] = 10 [\mu s] \times 1 = 10 [\mu s] \quad (8)$$

#### 【0045】

このように求められた  $T_{sp}$  を式(5)に代入すれば、計測時補正位置データを求めることができる。例えば、`data_req 3` の時点での計測時補正位置データ  $P_{3'\_1}$  は、以下の式(9)から求められる。

$$P_{3'\_1} [m] = P_{2\_10} [m] + V_{2\_10} [m/s] \times 10 [\mu s] \quad (9)$$

そして、位置データ出力部 50 は、この式(9)にて求められる計測時補正位置データのうち、`data_req 3` のデータ要求時点に最も時間的に近い計測時補正位置データを、上位システム 500 へと出力する。

40

#### 【0046】

なお、 $T_{sp}$  は、検出部 10 での計測開始時点とデータ要求時点との時間差であるが、より詳細な補正をするために検出部 10 の受光時間を考慮してもよい。例えば、以下の式(10)より求まる  $T_{sp}'$  を式(5)の  $T_{sp}$  に代入すればよい。

$$T_{sp}' [s] = T_{sp} [s] + \text{検出部 10 の受光時間 [s]} / 2 \quad (10)$$

なお、検出部 10 の受光時間は、設計値から求めてよいし、実際に計測して求めてよい。

#### 【0047】

次に、上位システム 500 が、取得した位置データを用いて位置決め制御を実行する制御部であるとして、制御時補正位置データを求める方法について説明する。ここでも、data\_req3 の要求に対して実際に制御に用いられるのは、次のクロックタイミングである data\_req4 の時点のものとする。そして、エンコーダ 100 は、data\_req4 の時点での位置データ P4\_1 を予測した制御時補正位置データ P4'\_1 を出力する必要がある。この制御時補正位置データは、以下の式(11)より求められる。

$$\text{制御時補正位置データ [m]} = \text{計測時補正位置データ [m]} + \text{移動速度 [m/s]} \times \text{制御時点との時間差 [s]} \quad (11)$$

例えば、図 8 の制御時補正位置データ P4'\_1 を求める場合には、以下の式(12)のようになる。ただし、ここでは制御時点との時間差を 100 μs としている。 10

$$P4'_1 [m] = P3'_1 [m] + V2_10 [m/s] \times 100 [\mu s] \quad (12)$$

#### 【0048】

なお、ここまで位置計測開始から位置データ演算までの処理時間が 30 μs 以上と長くなる場合について説明した。これに対して、処理時間が 30 μs 以下と短く、Wait 時間がそれよりもさらに短いことで、Wait 時間に処理が終了しない場合でも、同様の方法で位置データを補正することができる。

#### 【0049】

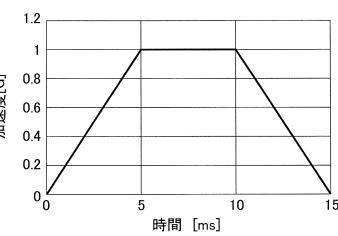

次に、上記のような構成および処理による具体的な効果について説明する。ここでは、一例として対象物が図 9 に示すような加速度を持つ場合について考える。なお、図 9 では、横軸の時間に対して、縦軸を重力加速度としている。この場合、対象物は、0 ~ 5 ms の間では、加速度が 0 G から 1 G まで線形に上昇(加速)し、5 ~ 10 ms の間では、一定加速度 1 G で推移し、10 ~ 15 ms の間では、加速度が 1 G から 0 G まで線形に下降(減速)する台形の加速度変化動作をする。 20

#### 【0050】

まず、比較のために、従来のエンコーダによる補正結果とそのときに生じ得る位置誤差について説明する。図 14 は、上記の図 7 および図 8 に対応した、従来のエンコーダによる各部の動作タイミングを表すタイミング図である。従来のエンコーダでは、図 7 および図 8 と比較してわかるとおり、位置計測用のクロック信号である meas 信号がなく、位置計測は、データ要求周期ごとに行なわれる。また、図 14 では、位置計測開始から補正位置データ演算までの処理時間が Wait 時間よりも長い場合を示している。 30

#### 【0051】

まず、上位システムがデータ収集解析部であり、図 14 における data\_req3 の時点での位置を得たい場合について考える。この場合、data\_req3 の時点での位置データ P3\_1 を出力するまでの処理が、Wait 時間に終わらないため、エンコーダは、data\_req3 の時点で取得した位置データ P3\_1 をそのまま出力することができない。したがって、エンコーダは、data\_req3 の時点での位置データ P3\_1 を予測した、計測時補正位置データ P3'\_1 を出力する必要がある。この計測時補正位置データ P3'\_1 は、上記の式(5)を参照すると、以下の式(13)により求められる。ただし、Tsp は、データ要求周期 Treq と同じ 100 μs である。 40

$$P3'_1 [m] = P2_1 [m] + V2_1 [m/s] \times 100 [\mu s] \quad (13)$$

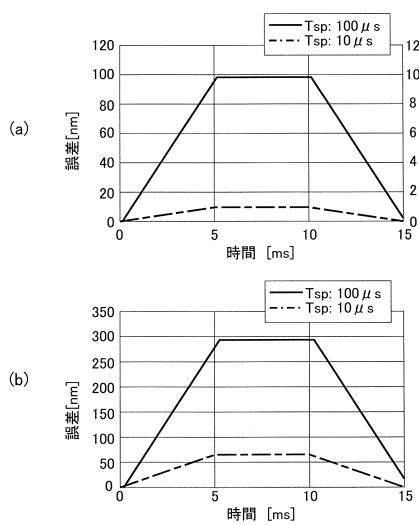

そして、実際の data\_req3 の時点での位置データ P3\_1 と、ここで得られた計測時補正位置データ P3'\_1 との差が、従来生じ得る位置誤差となる。図 10 は、図 9 の加速度動作をする対象物について求めた位置誤差を示すグラフである。特に、図 10 (a) は、計測時補正に係る位置誤差に関するものである。図 10 (a) 中の実線で示す従来の誤差量については、横軸の時間に対して、左側縦軸で示している。誤差量は、対象物の加速度の大きさに比例しており、最大で 98 nm となる。

#### 【0052】

これに対して、本実施形態に係るエンコーダ 100 では、Tsp を 10 μs とし、図 9 の動作をする対象物についての、式(5)より求められる計測時補正位置データと実際の 50

位置との差である位置誤差は、図10(a)中の一点鎖線で表される。なお、一点鎖線で示す誤差量については、横軸の時間に対して、右側縦軸で示している。この右側縦軸は、従来の場合の誤差量を示している左側縦軸に対して、スケールが1/10倍となっている。この場合の誤差量は、最大で0.98nmであり、従来の場合に比べて約1/100倍と大幅に低減している。このように、本実施形態によれば、位置誤差1nm以下の高精度な計測時補正位置データが得られることがわかる。

#### 【0053】

次に、上位システム500が、取得した位置データを用いて位置決め制御を実行する制御部である場合を考える。まず、従来のエンコーダによる補正結果とそのときに生じ得る位置誤差について見ると、ここでも、例えば、data\_req3の要求に対して実際に制御に用いられるのは、次のクロックタイミングのdata\_req4の時点である。この場合、エンコーダは、data\_req4の時点での位置データP4\_1を予測した制御時補正位置データP4'\_1を出力する必要がある。この制御時補正位置データP4'\_1は、上記の式(11)を参照すると、以下の式(14)により求められる。ただし、ここでは制御時点との時間差を100μsとしている。

$$P4'_1[m] = P3'_1[m] + V2_1[m/s] \times 100[\mu s] \quad (14)$$

そして、実際のdata\_req4の時点での位置データP4\_1と、ここで得られた計測時補正位置データP4'\_1との差が、従来生じ得る位置誤差となる。図10(b)は、制御時補正に係る位置誤差に関するものである。図10(b)中の実線で示す従来の誤差量は、対象物の加速度の大きさに比例しており、最大で294nmとなる。

#### 【0054】

これに対して、本実施形態に係るエンコーダ100では、Tspを10μsとし、図9の動作をする対象物についての式(11)より求められる計測時補正位置データと実際の位置との差である位置誤差は、図10(b)中の一点鎖線で表される。この場合の誤差量は、最大で64.6nmであり、従来の場合に比べて約1/4.5に低減している。このように、本実施形態によれば、位置誤差0.1μm以下の高精度な計測時補正位置データが得られることがわかる。

#### 【0055】

ここまで、Tspが10μsであるとして説明したが、Tspは、位置演算部30の処理速度などにより異なる。そこで、以下、Tspの大きさにより位置誤差量がどのように変化するかについて説明する。

#### 【0056】

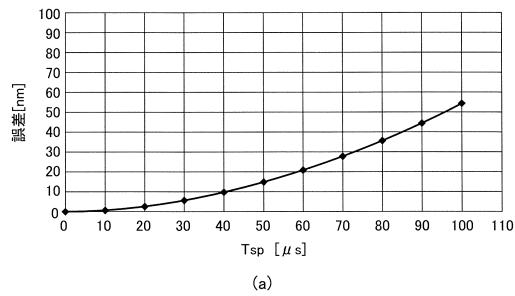

図11(a)は、計測時補正位置データについてTsp[μs]に対する位置誤差量[nm]を示すグラフである。例えば、Tsp=10μsでは、上記のとおり誤差量が0.98nmで、従来の場合に比べて約1/100倍となる。なお、Tsp=0μsでは、エンコーダ100は、取得した位置データをそのまま出力できるので、誤差量は0nmとなる。

#### 【0057】

図11(b)は、制御時補正位置データについてTsp[μs]に対する位置誤差量[nm]を示すグラフである。例えば、Tsp=10μsでは、上記のとおり誤差量が64.6nmで、従来の場合に比べて約1/4.5倍となる。また、Tsp=0μmでは、上位システム500での制御時点までの間に対象物が移動することで、誤差量が53.9nmで、従来の場合に比べて約1/5.5倍となる。

#### 【0058】

このように、エンコーダ100は、特に対象物が加速度運動を行う場合でも、データ要求信号の周期に同期した位置計測用の高速クロックを生成し用いることで、データ要求信号の周期よりも短い周期で位置または角度の計測を行う。すなわち、従来、データ要求信号の周期が短くなければ、正確な位置または角度を出力することが難しかったが、エンコーダ100では、データ要求信号の周期を短くする必要がない。したがって、データ要求信号の周期が短くなるように高速化する場合の上位システム500での演算負荷を増加さ

10

20

30

40

50

せる必要もないため、結果的に、上位システム 500 を複雑かつ高価なものとしなくてもよい。

### 【0059】

以上のように、本実施形態によれば、高速で変位する対象物に対する変位計測精度の点で有利な計測装置および計測方法を提供することができる。また、このような計測装置を用いることで、対象物の計測、検査、または加工などの処理の精度の点で有利な処理装置を提供することができる。

### 【0060】

#### (第2実施形態)

次に、本発明の第2実施形態に係る計測装置について説明する。図12は、本実施形態に係るエンコーダ300の信号処理系の構成を示すブロック図である。本実施形態に係るエンコーダ300の特徴は、第1実施形態に係るエンコーダ100が発振器80を有しているのに対してその発振器を含まず、上位システム500からclk\_IN信号230の入力を受ける点にある。なお、エンコーダ300のその他の構成は、第1実施形態に係るエンコーダ100と基本的に同一であるので、図12において同一の符号を付し、説明を省略する。

### 【0061】

clk\_IN信号230は、同様に上位システム500から送信されるdata\_re信号210に同期しているクロック信号である。エンコーダ300は、clk\_IN信号230を上位システム500から受信し、同期高速クロック生成部70は、clk\_IN信号230に基づいてmeas信号111を生成する。さらに、同期高速クロック生成部70は、位置演算部30や位置補正部40における演算用のクロックも生成する。具体的には、まず、同期高速クロック生成部70内のPLL78にclk\_IN信号230が入力される。clk\_IN信号230は、連続したクロック信号であるため、PLL78は、常にサンプル動作であればclk\_IN信号230に同期した新たなクロック信号を生成することができる。そのため、本実施形態では、PLL78中のサンプル／ホールド切替器782を必要としない。例えば、clk\_IN信号230の周波数を100kHz、第1分周器785の分周比(1/N)を1/2000とするとき、電圧制御発振器784は、clk\_IN信号230に同期した周波数200MHzのclk信号112を出力する。そして、同期高速クロック生成部70は、clk信号112に基づいて分周し、遅延を与えることで、meas信号111、ad\_start信号116、meas\_start信号110、およびdata\_out\_start信号120を生成する。

### 【0062】

図13は、第1実施形態における図7に対応した、本実施形態における各部の動作タイミングを表すタイミング図である。図13にて、図7と異なる点は、「clk」と「meas(100kHz)」との各信号に換わり、「clk\_IN」と「clk(PLL\_generate)」との各信号が存在することである。clk\_INは、clk\_IN信号230であり、同期高速クロック生成部70は、このclk\_INに基づいて、clk(PLL\_generate)を生成する。例えば、clk\_INの周波数を100kHz、clk(PLL\_generate)の周波数を200MHzとし得る。そして、同期高速クロック生成部70は、このclk(PLL\_generate)を分周することで、meas信号111を生成することができる。なお、meas信号111は、clk\_INと同じ周波数100kHzであり、図13では不図示(クロックタイミングは、clk\_INと同一)としている。そして、エンコーダ300内の検出部10は、このmeas信号111の周期ごとに位置計測を行うことになる。

### 【0063】

なお、図13は、位置計測開始から補正位置データ演算までの処理時間がWait時間よりも短い場合について示している。これに対して、Wait時間よりも長い場合については、clk\_INを第1実施形態における図8のmeas(100kHz)と、clk(PLL\_generate)を図8のclkとそれぞれ置き換えればよい。

10

20

30

40

50

**【 0 0 6 4 】**

このように、エンコーダ 300 は、データ要求信号の周期に同期したクロック信号を上位システム 500 から受信して用いるので、第 1 実施形態と比較すると、発振器 80 を要しない。したがって、本実施形態によれば、第 1 実施形態と同様の効果を奏しつつ、構成および信号処理を簡略化できるという利点がある。

**【 0 0 6 5 】**

以上、本発明の好ましい実施形態について説明したが、本発明は、これらの実施形態に限定されず、その要旨の範囲内で種々の変形および変更が可能である。

**【 0 0 6 6 】**

例えば、上記実施形態で例示した各クロック信号の周波数は、その値に限定するものではなく、その要旨の範囲内で変更可能である。また、各実施形態では、m e a s 信号 111 を、連続したクロック信号として説明したが、データ要求周期の間に複数の位置計測タイミングを検出部 10 に与えるものであれば、間欠的な信号であってもよい。さらに、データ要求信号である d a t a \_ r e q 信号 210 は、上記のように周期性を有するものであるが、精度的に許容される計測データが取得できるのであれば、周期性を有しなくともよい場合もある。10

**【 符号の説明 】****【 0 0 6 7 】**

|       |                    |    |

|-------|--------------------|----|

| 1 0   | 検出部                |    |

| 3 0   | 位置演算部              | 20 |

| 4 0   | 位置補正部              |    |

| 7 0   | 同期高速クロック生成部        |    |

| 1 0 0 | エンコーダ              |    |

| 1 1 1 | m e a s 信号         |    |

| 2 1 0 | d a t a _ r e q 信号 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

(a)

(b)

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(56)参考文献 特開2013-29511(JP,A)

特開平5-240631(JP,A)

特開2011-95121(JP,A)

特開2006-48380(JP,A)

特開2008-32562(JP,A)

特開2003-329485(JP,A)

特開2011-209375(JP,A)

特開2005-156282(JP,A)

特開平5-322598(JP,A)

米国特許出願公開第2004/0189496(US,A1)

米国特許出願公開第2004/0094338(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 01 D 5 / 00 - 5 / 38

G 01 B 7 / 00 - 7 / 34

G 08 C 13 / 00 - 25 / 04

H 02 K 11 / 00 - 11 / 40、24 / 00

G 03 F 7 / 20 - 7 / 24