(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년10월11일

(11) 등록번호 10-1665220

(24) 등록일자 2016년10월05일

- (51) 국제특허분류(Int. Cl.)

*H02M 7/48* (2007.01) *C25B 1/13* (2006.01)

(21) 출원번호 10-2014-7029941

(22) 출원일자(국제) 2013년03월18일

심사청구일자 2015년06월12일

(85) 번역문제출일자 2014년10월24일

(65) 공개번호 10-2014-0148443

(43) 공개일자 2014년12월31일

(86) 국제출원번호 PCT/US2013/032772

(87) 국제공개번호 WO 2013/148390

국제공개일자 2013년10월03일

(30) 우선권주장

13/431,521 2012년03월27일 미국(US)

(56) 선행기술조사문헌

JP2005333726 A

JP2009505626 A

KR1020070045143 A

US20070205727 A1

- (73) 특허권자

엠케이에스 인스트루먼츠, 인코포레이티드

미합중국 매사추세츠주 01810, 앤도버, 스위트

201, 테크 드라이브 2

(72) 발명자

트랜 켄

미국 매사추세츠주 01810 앤도버 스위트 201 테크

드라이브 2

켄 싱

미국 매사추세츠주 01810 앤도버 스위트 201 테크

드라이브 2

(뒷면에 계속)

(74) 대리인

제일특허법인

전체 청구항 수 : 총 20 항

심사관 : 꽈인구

(54) 발명의 명칭 산업용 유전체 장벽 방전 발생기 적용을 위한 다기능 영 전압 스위치 공진 인버터

**(57) 요약**

오존 발생에 이용되는 것과 같은 유전체 장벽 방전 시스템(dielectric barrier discharge system)을 위한 전력 시스템은 유전체 장벽 방전 셀 스택에 전력을 공급하는 신호를 출력하는 풀 브릿지 인버터 스테이지(full bridge inverter stage) 및 병렬 공진 탱크(parallel resonant tank)를 포함할 수 있다. 인버터 스테이지는 전부하

(뒷면에 계속)

**대 표 도** - 도3

(full load)로부터 경부하(light load)에 이르기까지 모든 부하 상태에서 소프트 스위칭(soft switching)을 가능하게 하기 위해 펄스폭 변조(PWM)와 주파수 변조(FM)의 조합을 이용하여 제어된다. 전류 제어 루프 오차 증폭기 보상기는 인버터 스테이지를 위한 스위칭 신호를 발생하는 위상 변이 PWM 제어기 칩에 듀티 사이클 조정 신호를 제공할 수 있다. 피드백 신호는 FM을 제공하기 위해 PWM 제어기 칩의 클록 주파수 시상수(clock frequency time constant)를 조정하는 데에도 이용된다. 일 실시예로, 피드백 신호는 전류 제어 루프 오차 증폭기 보상기의 출력에 연결된 인버팅 증폭기의 출력이다.

(72) 발명자

뉴랜 투셀 엘

미국 메사츄세츠주 01810 앤도버 스위트 201 테크

드라이브 2

리 프랭클린

미국 메사츄세츠주 01810 앤도버 스위트 201 테크

드라이브 2

---

## 명세서

### 청구범위

#### 청구항 1

유전체 장벽 방전 전력 시스템(dielectric barrier discharge power system)으로서, 인버터 스테이지(inverter stage)와, 상기 인버터 스테이지의 출력을 수신하고, 적어도 하나의 유전체 장벽 방전 셀에 전력을 공급하기 위한 신호를 출력하는 공진 탱크(resonant tank)와, 제어 회로를 포함하되, 상기 제어 회로는

소프트 스위칭(soft switching)을 위한 위상 변이를 포함하는 스위칭 신호를 상기 인버터 스테이지로 제공하는 게이트 드라이버와,

상기 게이트 드라이버를 위한 스위칭 주파수를 발생시키는 펄스폭 변조(PWM) 제어기—상기 PWM 제어기는, PWM을 수행하기 위해 상기 스위칭 주파수의 뉴티 사이클을 조정하는 제 1 신호를 수신하도록 구성된 제 1 입력부와, 주파수 변조(FM)를 수행하기 위해 상기 PWM 제어기의 클록 주파수 시상수(clock frequency time constant)를 조정하는 제 2 신호를 수신하도록 구성된 제 2 입력부를 가짐—를 포함하고,

상기 제어 회로는 상기 인버터 스테이지로부터의 출력 전류를 포함하는 피드백 신호를 수신하고, 상기 피드백 신호를 이용하여 상기 제 1 신호와 상기 제 2 신호를 발생시키는

유전체 장벽 방전 전력 시스템.

#### 청구항 2

제1항에 있어서,

상기 인버터 스테이지는 풀 브릿지(full bridge)로서 배열된 4개의 트랜지스터를 포함하는 유전체 장벽 방전 전력 시스템.

#### 청구항 3

제2항에 있어서,

상기 4개의 트랜지스터는 절연 게이트 바이폴라 트랜지스터(IGBT)인 유전체 장벽 방전 전력 시스템.

#### 청구항 4

제1항에 있어서,

상기 적어도 하나의 유전체 장벽 방전 셀에 전력을 공급하기 위한 상기 공진 탱크로부터의 신호를 점증(stepping up)시키는 변압기를 더 포함하는

유전체 장벽 방전 전력 시스템.

## 청구항 5

제1항에 있어서,

상기 스위칭 주파수는 20kHz 내지 40kHz의 범위내인

유전체 장벽 방전 전력 시스템.

## 청구항 6

제1항에 있어서,

상기 스위칭 주파수는 상기 공진 탱크의 공진 주파수보다 더 높게 구성되는

유전체 장벽 방전 전력 시스템.

## 청구항 7

제1항에 있어서,

상기 피드백 신호는 상기 인버터 스테이지의 출력에서 전류 센서로부터 수신된 측정된 전류 신호(a measured current signal)를 포함하는

유전체 장벽 방전 전력 시스템.

## 청구항 8

제7항에 있어서,

전체 부하 상태(all load conditions) 동안, 상기 측정된 전류 신호는 전류 설정 포인트 값(current set point value)과 비교되고, 상기 비교의 오차값은 상기 제 1 신호로 하여금 상기 측정된 전류 신호가 상기 전류 설정 포인트 값에 도달할 때까지 상기 스위칭 주파수의 뉴티 사이클을 조정하여 상기 PWM을 수행하게 하고, 상기 비교의 오차값은 또한 상기 제 2 신호로 하여금 상기 클록 주파수 시상수를 변경되도록 조정하여 상기 FM을 수행하게 하며,

상기 유전체 장벽 방전 전력 시스템이 전부하 상태(full load condition)로부터 경부하 상태(light load condition)로 동작할 때 상기 제어 회로는 전력을 제어하기 위한 상기 PWM과 상기 FM에 제공되는 가중치의 양이 변하도록 구성되는

유전체 장벽 방전 전력 시스템.

## 청구항 9

제7항에 있어서,

상기 제어 회로는 상기 제 1 신호와 상기 제 2 신호를 발생하는 전류 제어 루프를 포함하되, 상기 전류 제어 루프는 상기 인버터 스테이지의 출력에서 감지되는 상기 측정된 전류 신호와 전류 설정 포인트를 이용하는

유전체 장벽 방전 전력 시스템.

## 청구항 10

제9항에 있어서,

상기 전류 제어 루프는

상기 측정된 전류 신호와 상기 전류 설정 포인트를 수신하고, 상기 제 1 신호를 출력하는 오차 증폭기 보상기(error amplifier compensator)와,

상기 제 1 신호를 수신하고, 상기 제 2 신호를 출력하는 인버팅 증폭기(inverting amplifier)를 포함하는

유전체 장벽 방전 전력 시스템.

## 청구항 11

제9항에 있어서,

상기 전류 제어 루프는

상기 측정된 전류 신호와 상기 전류 설정 포인트를 수신하고, 상기 제 1 신호를 출력하는 오차 증폭기 보상기와,

상기 오차 증폭기 보상기의 출력을 수신하고, 상기 제 2 신호를 출력하는 인버팅 증폭기를 포함하는 유전체 장벽 방전 전력 시스템.

## 청구항 12

제9항에 있어서,

상기 피드백 신호는 입력 전력 신호를 더 포함하되, 상기 입력 전력 신호는 상기 인버터 스테이지에 공급되는 측정된 DC 버스 전압과 상기 인버터 스테이지에 공급되는 측정된 DC 버스 전류의 곱(product)이고,

상기 전류 제어 루프는

상기 측정된 전류 신호와 상기 전류 설정 포인트를 수신하고, 상기 제 1 신호를 출력하는 오차 증폭기 보상기와,

상기 입력 전력 신호를 수신하고, 상기 제 2 신호를 출력하는 인버팅 증폭기를 포함하는 유전체 장벽 방전 전력 시스템.

## 청구항 13

제9항에 있어서,

상기 피드백 신호는 출력 전력 신호를 더 포함하되, 상기 출력 전력 신호는 측정된 DC 출력 전압과 상기 측정된 전류의 곱이고,

상기 전류 제어 루프는

상기 측정된 전류 신호와 상기 전류 설정 포인트를 수신하고, 상기 제 1 신호를 출력하는 오차 증폭기 보상기와,

상기 출력 전력 신호를 수신하고, 상기 제 2 신호를 출력하는 인버팅 증폭기를 포함하는 유전체 장벽 방전 전력 시스템.

## 청구항 14

제9항에 있어서,

프로세서를 더 포함하되,

### 상기 프로세서는

상기 인버터 스테이지에 공급되는 DC 버스 전압 및 전류의 측정치를 수신하고—상기 DC 버스 전압 및 전류의 측정치는 전력 피드백 신호를 제공하기 위해 스케일링되어(scaled) 함께 곱해짐—,

상기 전력 피드백 신호를 전력 설정 포인트에 더하고,

상기 전류 제어 루프를 위한 상기 전류 설정 포인트를 출력하기 위해 상기 전력 피드백 신호와 상기 전력 설정 포인트를 이용하여 디지털 오차 보상을 수행하도록 구성되는

유전체 장벽 방전 전력 시스템.

### 청구항 15

유전체 장벽 방전을 발생시키는 방법으로서,

적어도 하나의 유전체 장벽 방전 셀에 전력을 공급하기 위해 인버터 스테이지 및 공진 탱크를 제공하는 단계와, 제어 회로를 이용하여 상기 인버터 스테이지를 위한 스위칭 신호를 발생시키는 단계—상기 스위칭 신호는 소프트 스위칭을 위한 위상 변이를 포함함—를 포함하되,

상기 스위칭 신호를 발생시키는 단계는

상기 인버터 스테이지의 출력 전류를 전류 설정 포인트 값에서 유지하기 위해 상기 스위칭 신호의 스위칭 주파수의 펄스폭 변조(이하, PWM)를 수행하는 단계와,

상기 PWM을 수행하는 단계와 동시에 주파수 변조(이하, FM)를 수행하는 단계—상기 FM은 경부하 상태 동안 출력 전력을 감소시키기 위해 상기 스위칭 신호의 스위칭 주파수를 증가시킴—를 포함하는

유전체 장벽 방전을 발생시키는 방법.

### 청구항 16

제15항에 있어서,

상기 스위칭 신호는 20kHz 내지 40kHz의 범위의 주파수를 갖는

유전체 장벽 방전을 발생시키는 방법.

### 청구항 17

제15항에 있어서,

상기 PWM를 수행하는 단계는

게이트 드라이버를 위해 상기 스위칭 주파수를 발생시키는 PWM 제어기를 제공하는 단계—상기 PWM 제어기는 PWM을 수행하기 위해 상기 스위칭 주파수의 뉴터 사이클을 조정하는 제 1 신호를 수신하도록 구성된 제 1 입력부와, FM을 수행하기 위해 상기 PWM 제어기의 클록 주파수 시상수를 조정하는 제 2 신호를 수신하도록 구성된 제 2 입력부를 가짐—와,

상기 인버터 스테이지의 상기 출력 전류를 감지하는 단계와,

오차 증폭기 보상을 수행함으로써 상기 출력 전류를 전류 설정 포인트와 비교하는 단계와,

상기 오차 증폭기 보상을 상기 제 1 신호로서 이용하는 단계를 포함하는

유전체 장벽 방전을 발생시키는 방법.

**청구항 18**

제17항에 있어서,

상기 FM을 수행하는 단계는 상기 제 2 신호를 출력하는 인버팅 증폭기를 이용하여 상기 오차 증폭기 보상을 반전시키는 단계를 포함하는

유전체 장벽 방전을 발생시키는 방법.

**청구항 19**

제18항에 있어서,

상기 FM을 수행하는 단계는 상기 인버팅 증폭기의 이득을 조정하는 단계를 더 포함하는

유전체 장벽 방전을 발생시키는 방법.

**청구항 20**

제17항에 있어서,

상기 인버터 스테이지에 공급되는 DC 버스 전압의 측정치와, 상기 인버터 스테이지에 공급되는 DC 버스 전류의 측정치를 수신하는 단계—상기 DC 버스 전압의 측정치 및 상기 DC 버스 전류의 측정치는 전력 피드백 신호를 제공하기 위해 스케일링되어 함께 곱해짐—와,

상기 전력 피드백 신호를 전력 설정 포인트에 더하는 단계와,

상기 전류 설정 포인트를 출력하기 위해 상기 전력 피드백 신호와 상기 전력 설정 포인트를 이용하여 디지털 오차 보상을 수행하는 단계를 더 포함하는

유전체 장벽 방전을 발생시키는 방법.

**발명의 설명****배경 기술**

[0001]

오존은 예를 들면 반도체 와이퍼 및 반도체 공정 장비의 공정 챔버를 세정하기, 반도체 웨이퍼상에 절연막을 입히기, 그리고 물, 음식 및 다른 소모품 또는 산업용 제품을 소독하기 등을 포함하여 많은 산업용과 반도체 공정 응용에 이용된다.

[0002]

오존 발생을 위한 한 가지 기술은 유전체 장벽 방전을 수반하는데, 여기서 고순도 산소(high purity oxygen)가 고전압 AC 전원의 인가에 의해 생성되는 전기 방전에 노출된다. 전기 방전은 산소 분자를 원자 상태로 분해하여, 산소가 오존( $O_3$ )과 산소( $O_2$ )의 혼합물로 재결합하게 한다. 이런 기술의 경우, 오존 농도는 오존 발생 시스템의 출력 전력에 비례한다. 비록 출력 전력을 증가시키는 것이 오존 농도를 증가시킨다하더라도, 성능 및 신뢰성에 대한 기대치 및 공간적 제약은 종종 대조적인 제약조건을 제공한다.

**발명의 내용**

[0003]

오존 발생기 및 다른 유전체 장벽 방전 시스템을 위한 전력 시스템 및 전력 제어 기술이 본원에 설명된다.

[0004]

특정 실시예에 따르면, 전통적인 하드 스위칭 토플로지(hard switching topology)를 대신해서 병렬 공진 토플로지(parallel resonant topology)를 이용하는 듀얼 공진 인버터 전력 스테이지(dual resonant inverter power stage)와; 경부하(light load)이더라도 임의의 동작하에서 우수한 동적 범위와 안정성을 달성하는 조합형 펄스 폭 변조 및 주파수 변조 제어 방식(a combined pulse width modulation(PWM) and frequency modulation(FM) control scheme)을 갖는 전력 시스템이 제공된다.

- [0005] 이 실시예에 따른 전력 시스템은 궁극적으로 고전압 AC 신호를 하나 이상의 유전체 장벽 방전 셀로 공급하는 공진 탱크(resonant tank) 및 변압기(transformer) 신호를 제공하는 인버터 스테이지와; 스위칭 신호를 상기 인버터 스테이지로 제공하는 피드백 제어 회로를 포함한다. 인버터 스테이지는 피드백 제어 회로를 통해 FM 제어와 조합된 PWM 및 위상 변이 ZVS(Zero Voltage Switch)와 함께 동작되는 풀 브릿지(full bridge)일 수 있다.

- [0006] 본 발명의 한 양상에 따르면, 본 발명의 전력 시스템 및 전력 제어 기술은 전체 전력으로 오존을 발생하는데 요구되는 출력 전력 미만에서 동작하는 능력을 제공하면서 증가된 출력 전력을 가능하게 한다. 일 실시예로, 20kHz 내지 40kHz의 범위에서 동작하는 시스템의 출력 전력은 5kW에서 10kW까지 증가될 수 있지만, 전력 시스템의 최대 출력의 약 1%에서 전체 전력에 이르기까지 동작하는 능력을 제공한다(주의:5% 오존 농도의 5kW 시스템의 최대 출력은 ~250W 출력 전력이다). 구체적인 실시예로, 5kW 출력 전력이 각기 가능한 두 개의 전력 트레인(power train)이 10kW 출력 전력을 달성하는데 이용된다.

- [0007] 본 발명의 다른 양상에서, 본 발명의 전력 시스템 및 전력 제어 기술이 이전의 시스템의 사이즈를 증가시키지 않으면서 달성된다. 일 실시예로, 전력 시스템은 종래의 비공진 전력 변환기와 비교하여 더 작은 공간에 설치된다.

- [0008] 본 개요는 이후의 상세한 설명에서 추가로 설명되는 개념 중에서 선정된 개념을 간략한 형태로 소개하기 위해 제공된다. 이 개요는 청구된 주제의 핵심 특징이나 필수 특징을 식별하려는 것이 아니며, 청구된 주제의 범주를 제한하는데 이용되는 것도 아니다.

### 도면의 간단한 설명

- [0009] 도 1a는 본 발명의 일 실시예에 따른 유전체 장벽 방전기를 위한 전력 스테이지의 기본도이다.

- 도 1b는 본 발명의 일 실시예에 따른 전력 스테이지의 소프트 스위칭 방식 및 최종 출력의 일련의 구성도를 도시한다.

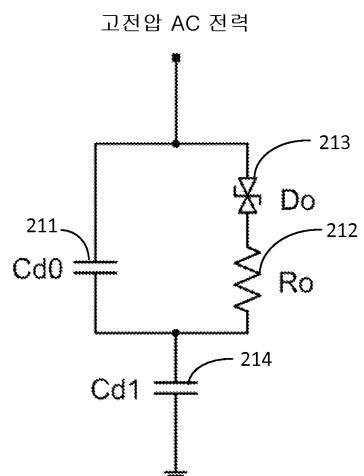

- 도 2a는 오존 셀 스택의 등가의 전기적 모델이다.

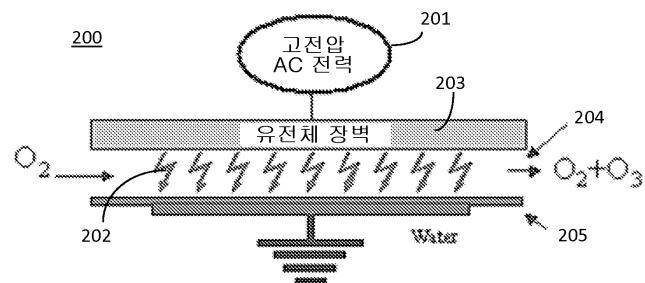

- 도 2b는 오존을 발생하는 유전체 장벽 방전 셀을 나타낸 것으로, 고 전압 AC 전력 신호가 본 발명의 일 실시예의 전력 시스템에 의해 제공될 수 있다.

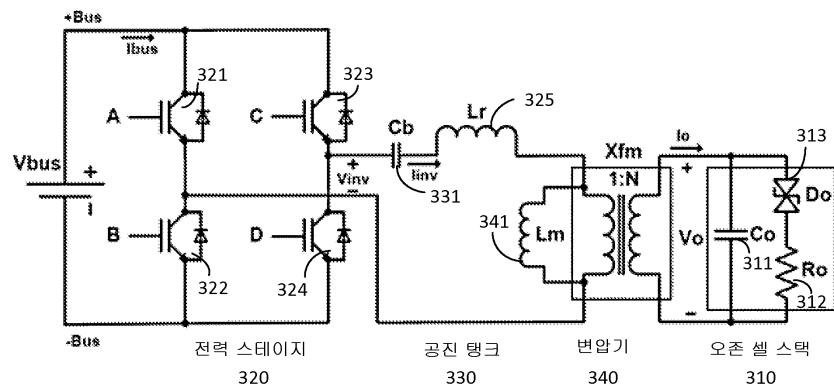

- 도 3은 본 발명의 일 실시예에 따른 공진 인버터 전력 스테이지를 갖는 단일 전력 트레인의 개략도이다.

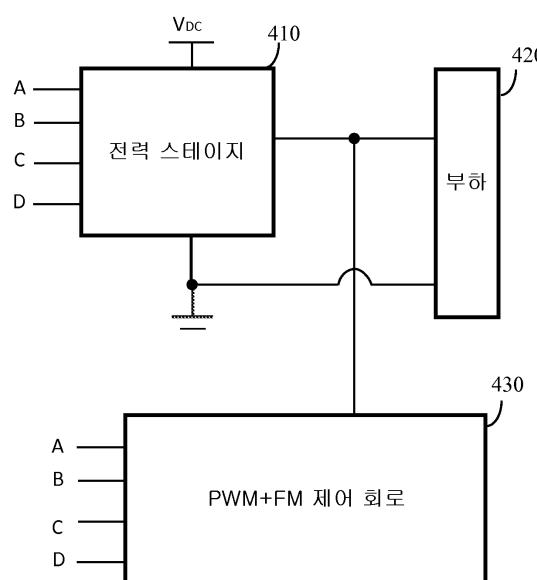

- 도 4는 본 발명의 일 실시예에 따른 유전체 장벽 방전 전력 시스템의 블록도이다.

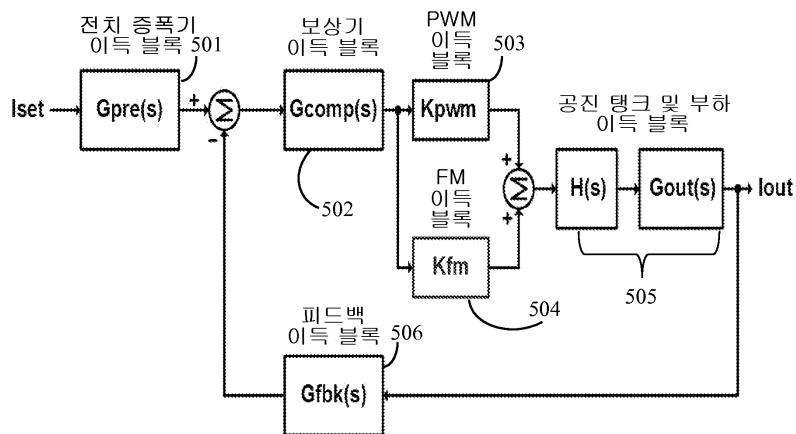

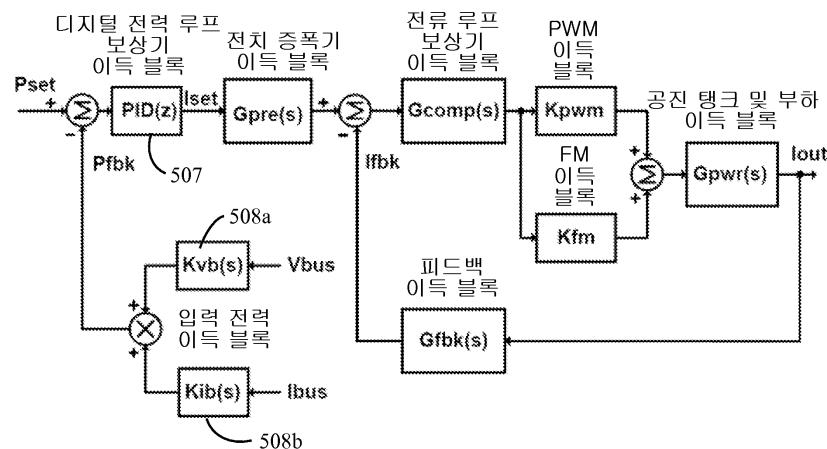

- 도 5a 및 도 5b는 본 발명의 제 1 실시예에 따른 PWM 및 TM 전류 루프 제어 방식의 기본 블록도(도 5a)와, 전력 루프를 갖는 시스템 레벨 제어 방식의 기본 블록도(도 5b)를 도시한다.

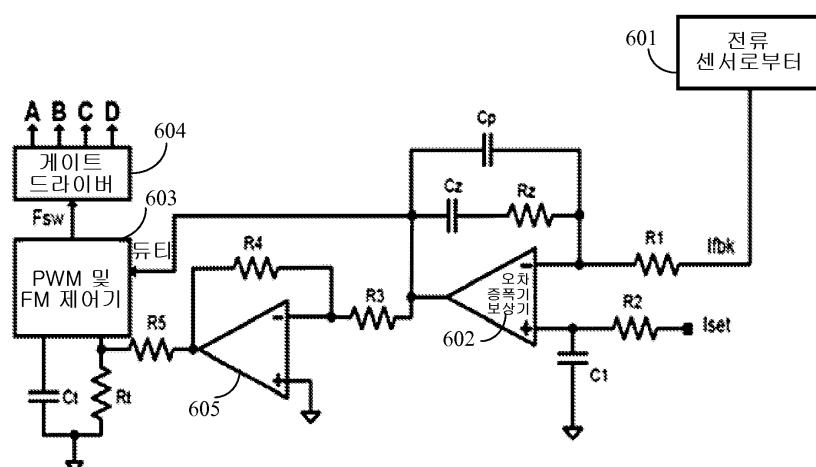

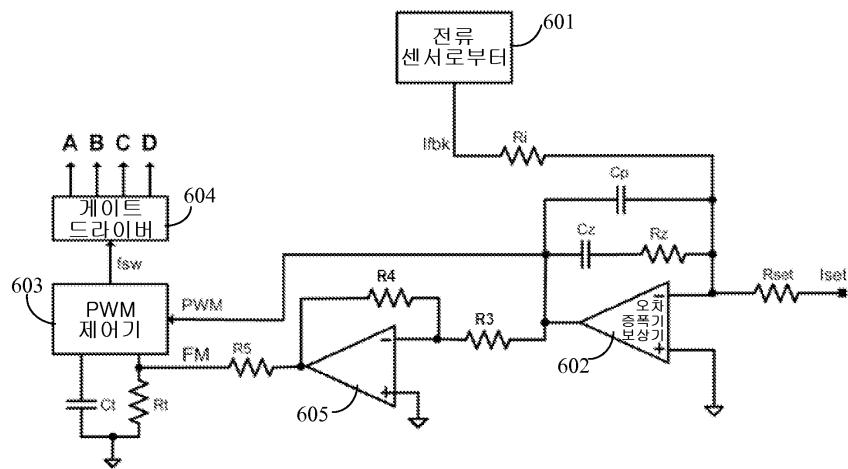

- 도 6a 및 도 6b는 본 발명의 특정 실시예에 따른 도 5a에 도시된 PWM 및 FM 전류 루프 제어 방식의 개략도를 도시한다.

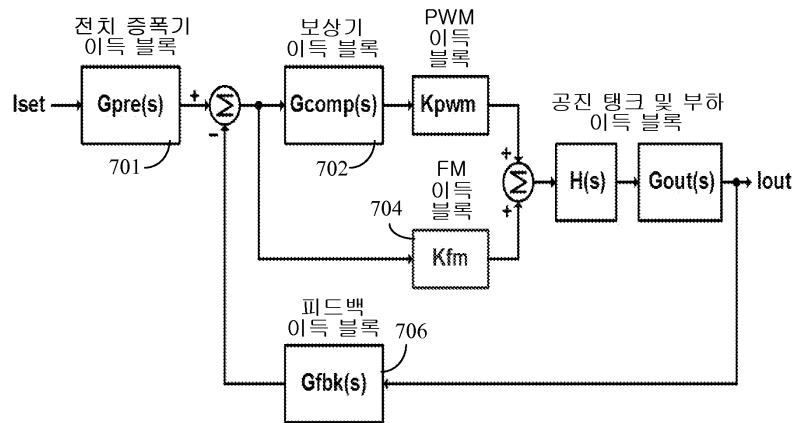

- 도 7은 본 발명의 제 2 실시예에 따른 PWM 및 FM 전류 루프 제어 방식의 기본 블록도를 도시한다.

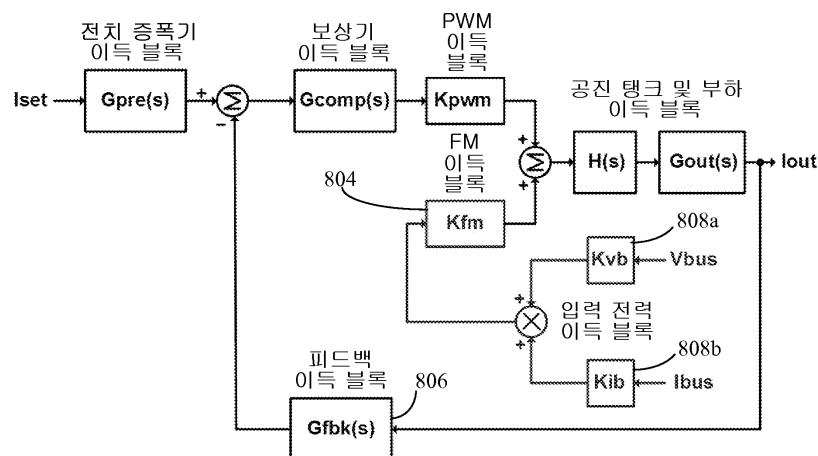

- 도 8은 본 발명의 제 3 실시예에 따른 PWM 및 FM 전류 루프 제어 방식의 기본 블록도를 도시한다.

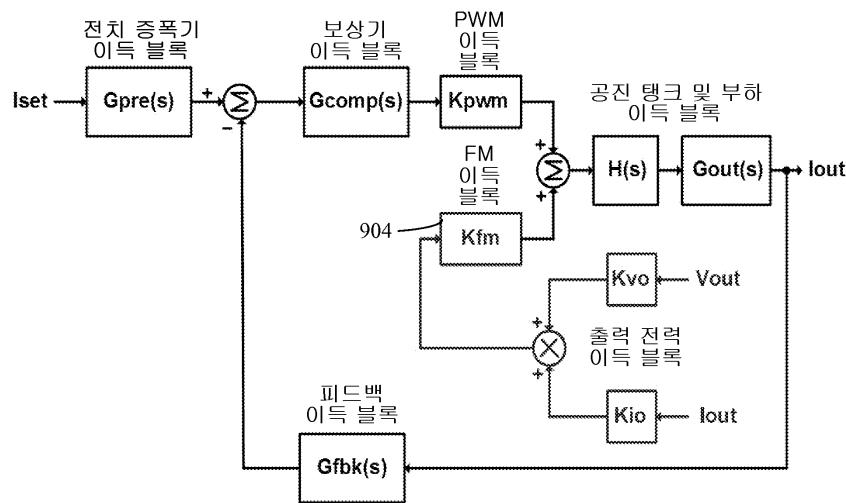

- 도 9는 본 발명의 제 4 실시예에 따른 PWM 및 FM 전류 루프 제어 방식의 기본 블록도를 도시한다.

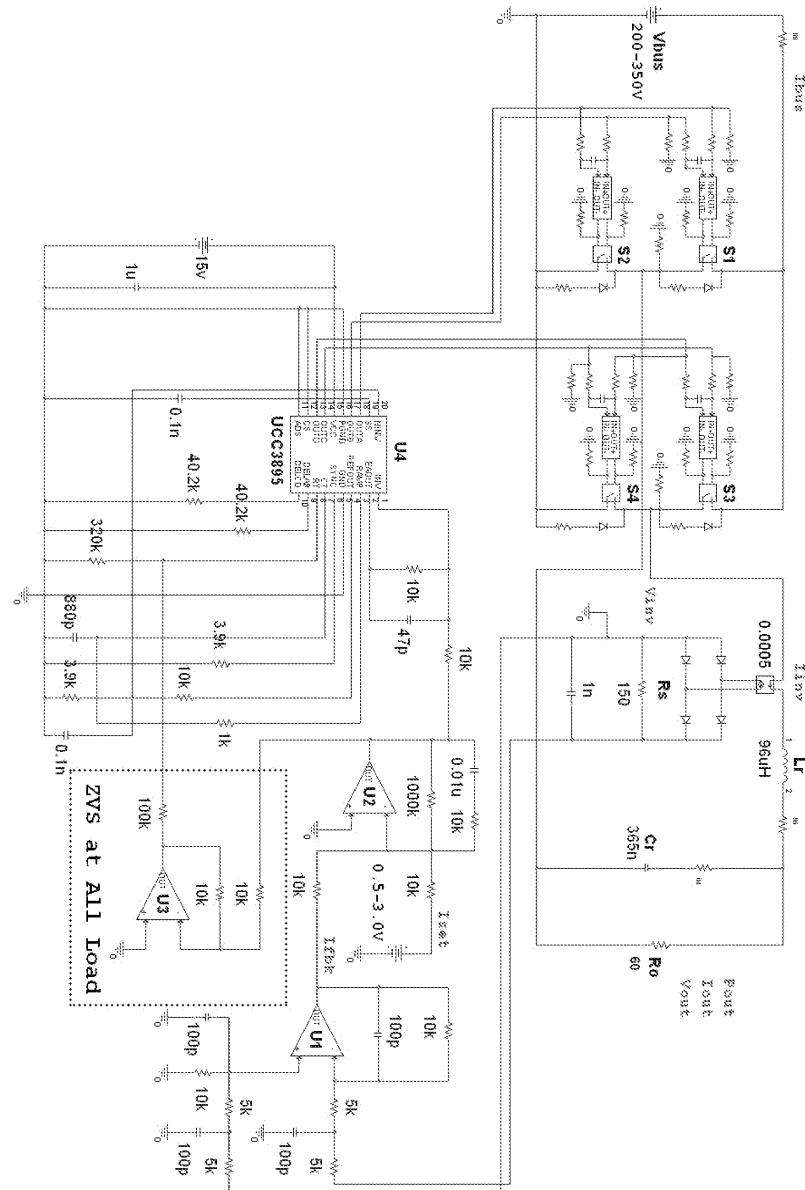

- 도 10은 본 발명의 일 실시예에 따른 PWM 및 FM 제어를 갖는 ZVS 공진 인버터 전류 루프의 시뮬레이션 개략도이다.

- 도 11a 내지 도 11d는 경부하 상태에서 본 주제의(subject) ZVS 공진 인버터의 일 실시예의 시뮬레이션 그림 및 스코프 파형(scope waveform)을 도시한다.

- 도 12a 내지 도 12d는 전부하 상태(full load conditions)에서 본 주제의 ZVS 공진 인버터의 일 실시예의 시뮬레이션 그림 및 스코프 파형을 도시한다.

### 발명을 실시하기 위한 구체적인 내용

- [0010] 본원에는 오존 발생기를 포함하여 유전체 장벽 방전기를 위한 개선된 제어 및 전력 출력을 가능하게 하는 기술

과 회로가 개시된다.

[0011] 본 발명의 일 실시예에 따르면, 완전 전력을 통해 오존을 발생하는데 요구되는 출력 전력 미만에서 동작하는 능력을 제공하면서 증가된 출력 전력을 가능하게하는 전력 시스템 및 전력 제어 기술이 제공된다. 본 발명의 구체적인 구현예에 따르면, 약 20-40kHz의 주파수 범위와 10kW의 출력 전력의 전력 시스템이 10kW의 ~1% 이하에 대한 제어로 제공된다. 구체적인 실시예에서, 5kW 출력 전력이 각기 가능한 두 개의 전력 트레인이 10kW 출력 전력을 달성하는데 이용된다.

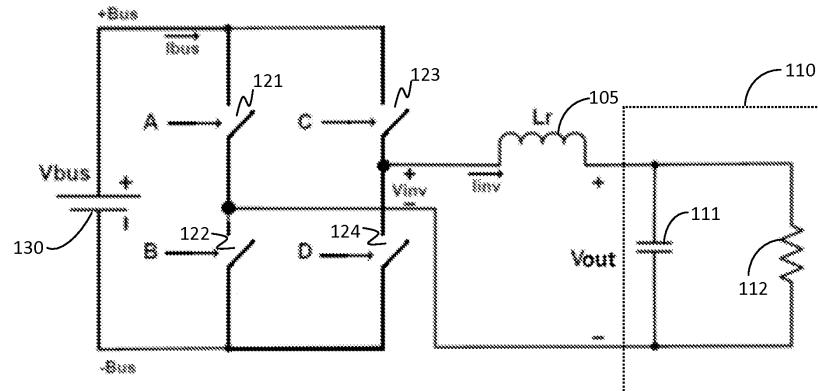

[0012] 도 1a는 본 발명의 일 실시예에 따라 유전체 정벽 방전기를 위한 전력 스테이지의 기본도를 예시한다. 도 1a에 도시된 전력 스테이지에서, 4개의 스위치(121, 122, 123, 124)는 인입 DC 버스 전압 입력(Vbus)을 공진 인덕터 Lr(105)와 오존 셀 스택(110)으로 표시된 병렬 공진 탱크 네트워크를 통해 정현파로 변환하는 풀 브릿지로서 배열된다. 스위치(121, 122, 123, 124)는, 제한적인 것은 아니지만, 바이폴라 접합 트랜지스터(BJT)와; 절연 게이트 바이폴라 접합 트랜지스터(IGBT)와; 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET) 및 고전자 이동도 트랜지스터(HEMTs)를 포함하는 전계 효과 트랜지스터(FET)를 포함한 임의의 적절한 스위치일 수 있다.

[0013] 공진 탱크(인덕터(105) 단독으로 제공되거나 또는 부하(110)의 캐패시터(111)와 조합하여 제공됨)는 풀 브릿지 전력원으로부터 AC 전압을 수신하고, 제어된 진폭의 고전압 정형파의 형태로 공진(또는 사실상 공진인) AC 전압을 유전체 장벽 방전 셀(110)에게 제공한다. 변압기(도면에는 도시되지 않음)는 신호를 원하는 레벨까지 점증(step up)시키기 위해 포함될 수 있다. 변압기의 효과는 Vout/N으로서 Vout을 나타냄으로써 단순화된 모델로 포함될 수 있으며, 여기서 N은 변압기 권선량이다.

[0014] 유전체 장벽 방전기의 셀(혹은 부하)(110)는 병렬 캐패시터(111)와 저항기(112)에 의해 모델링될 수 있다. 비록 캐패시터(111)가 셀(110)의 일부로서 도시되었지만, 모델링된 캐패시터의 캐패시턴스는 셀의 자연 캐패시턴스에 덧붙여서 독립적인 개별 캐패시터를 포함할 수도 있다.

[0015] 도 2a는 오존이 발생될 수 있기 전에 출력에서 요구되는 전압을 고려한 오존 셀 스택의 전기 회로 모델을 도시한다. 특히, 전압 클램프 Do(213)(도 1a의 기본도에는 도시되지 않음)는 오존을 발생하는 유전체 장벽 방전기 셀을 모델링할 때 저항기(212)와 직렬로 포함될 수 있다. 오존 농도는 출력 전력에 비례하므로, 오존 셀은 전압 클램프(213)와 직렬인 저항기(212)에 의해 모델링될 수 있다(예를 들면, 도 3에 도시된 저항기(312)와 전압 클램프(313)를 참조하라). 동작시, 오존은 출력 전압이 클램프의 전압보다 큰 특정 전압에 도달한 이후에 발생될 수 있는데, 이것은 저항기 Ro(212)에서 전력의 소비로서 모델링된다. 만약 출력 전압이 클램프의 전압(Do) 미만이면, Ro(212)는 전류를 도전할 수 없어서 전력 소비를 허용하고, 어떠한 오존 농도도 발생되지 않는다.

[0016] 출력 캐패시턴스 Co(도 1a의 캐패시터(111)로서 모델링됨)는  $Co = Cd0 * Cd1 / (Cd0 + Cd1)$ 로서 주어질 수 있으며, 여기서 Cd0는 직렬의 전압 클램프(213) 및 저항기(212)와 병렬인 캐패시터(211)이고, Cd1은 접지된 캐패시터(214)이다.

[0017] 도 2b는 자신의 고전압 AC 전력을 제공하기 위해 본원에 설명된 전력 스테이지 구성을 이용할 수 있는 유전체 장벽 방전 셀의 한 유형을 나타낸다. 도 2b에 도시된 것처럼, 셀(200)은 AC 전력(201)의 인가시 제 1 유전체 장벽막(203)으로부터 캡(204)을 거쳐 제 2 전극(205)으로 전기 방전(202)을 발생하는 제 1 전극(도시 안 됨)을 포함할 수 있다. 선택적인 제 2 유전체 장벽막(도시 안 됨)이 제 2 전극(205)상에 배치될 수 있다. 제 2 전극(205)으로부터 접지로 전하를 운반하는데 물이 이용될 수 있다. 구체적인 실시예에서, 제 1 유전체 장벽막(203)은 산화 알루미늄( $Al_2O_3$ )으로 형성되고, 제 2 전극(205)은 텅스텐으로 형성된다.

[0018] 오존 발생 응용인 경우, 캡을 통과하는 산소( $O_2$ )는 캡 양단의 전기 방전에 의해 산소 원자로 쪼개져서, 산소 원자가 오존( $O_3$ )과 산소( $O_2$ )의 혼합물로 재결합될 수 있게 한다.

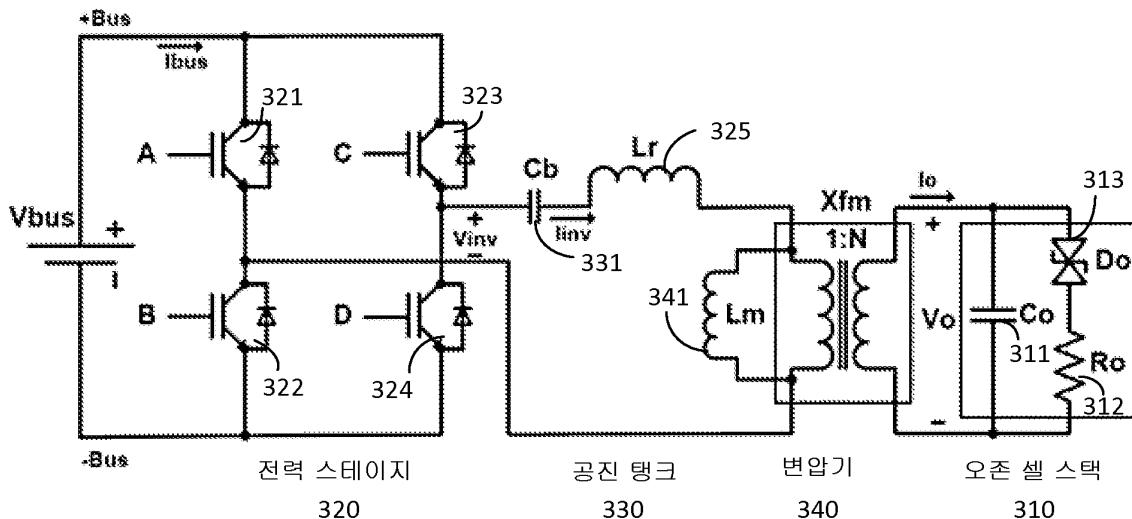

[0019] 도 3은 본 발명의 일 실시예에 따른 공진 인버터 전력 스테이지를 갖는 단일 전력 트레인의 개략도이다. 전력 트레인은 본 발명의 일 실시예에 따라 오존 발생기를 모델링하는데 이용될 수 있는 유전체 정벽 방전 셀의 전기 모델을 포함한다. 도 3에 도시된 것처럼, 전력 스테이지 인버터(320)의 스위치는 IGBT(321, 322, 323, 324)를 이용하여 구현되는데, 이것은 풀 브릿지내에 배열되며 인입 DC 버스 전압 입력(Vbus)을 병렬 공진 탱크 네트워크를 통해(공진 탱크(330), 변압기(340) 및 오존 셀 스택(310)을 통해) 정현파형으로 변환한다. 비록 IGBT가 도 3에 도시된 실시예와 관련하여 예시 및 설명되었지만, 실시예가 이것에만 제한되는 것은 아니며, 다른 적절한 트랜지스터 유형이 이용될 수도 있음을 유의해야 한다.

[0020] 공진 탱크(330)는 전력 스테이지(320)의 풀 브릿지 IGBT와 고전압 변압기(340)를 드라이브 회로내의 비대칭성으

로 인한 장해로부터 보호하는 블로킹 캐패시터(blocking capacitor)  $C_b(331)$ 과; 공진 인덕터  $L_r(325)$ (이것은 변압기 누설 인덕턴스를 포함할 수 있다)와; 고전압 점증 변압기  $X_{fm}(340)$ (자화된 인덕턴스  $L_m(341)$ 을 가짐)과; 오존 부하 셀 스택(310)(캐패시턴스  $C_o(311)$ , 임피던스  $R_o(312)$  및 클램프 전압  $D_o(313)$ 을 가짐)을 포함할 수 있다. 5kW 단일 전력 트레인으로, 변압기 출력 전압은 전 출력 부하 동작(full output load operation)에서 30kHz의 스위칭 주파수( $f_{sw}$ ) 부근에서 약 8kV 피크-피크까지 점증할 수 있다. 공진 탱크의 주파수  $f_{res}$ 는

$$f_{res} = \frac{1}{2 * \pi * \sqrt{L_r * C_o * N^2}}$$

로 주어지며, 여기서  $N$ 은 변압기 권선비이다.  $C_b >> C_o * N^2$ 이고,  $L_m >> L_r$ 이며, 품질 계

$$Q = \frac{R_o}{N^2 \sqrt{[L_r / (C_o * N^2)]}}$$

수  $Q$ 가 1을 초과하면서 정의되는 경우, 도 1a에 도시된 간략화가 유효하다. 특정 실시예에서, 공진 탱크의 전류의 재순환을 막기 위해서,  $Q$ 는 3 미만이 되도록 선택된다. 이 모델의 성분들은 분석의 단순화를 위해 고차 고조파(high order harmonic)를 무시하면서 (1차(first order)에 대해) 이상화되었다 (기본파에 대해).

[0021] 비록 도면에는 도시되지 않았더라도, 제한하는 것은 아니지만, 성분들의 성능을 개선하거나 최적화하기 위한 목적으로 유전체 장벽 방전 전력 시스템내에 추가 회로가 포함될 수도 있다. 예를 들어, 전력 스테이지 공진 탱크의 회로내에는 성분들의 허용한계(tolerance)에 다양한 변화가 있을 수 있고, 이러한 변화는 전력 스테이지의 성능을 열화하는 방식으로  $F_{res}$ 에 영향을 미칠 수 있다. 따라서, 일부 실시예에서, 공진 주파수  $f_{res}$ 보다 살짝 높은 주파수(~40kHz)로부터 시작해서 인버터 출력 공진 탱크의 곡선을 따라가면서 추적함으로써 동작하는 튜닝 회로(tuning circuit)가 포함될 수 있다. 이러한 추적은 원하는 입력 전력이 달성될 때 중지된다. 이런 유형의 회로를 피크 전력 포인트 검색 회로(peak power point search circuit)라고 할 수 있다. 이 회로는 전력 스테이지의 개별 인버터가 최대 출력 전력을 발생하는 것을 보장하는데 이용된다. 이런 회로의 예시적인 실시예는 미국 특히 출원 공개 번호 제2007/0108040호에 설명되며, 이 미국 출원은 본원에서 전체적으로 참조하고 있다. 이러한 자동 셀프-튜닝(auto self-tuning) 설계는 인버터 전력 스테이지의 성분 허용한계, 스위칭 주파수 변화, 온도 변화 및 오존 셀 스택 노화를 복사한다는 점에서 일부 유리한 점을 제공한다.

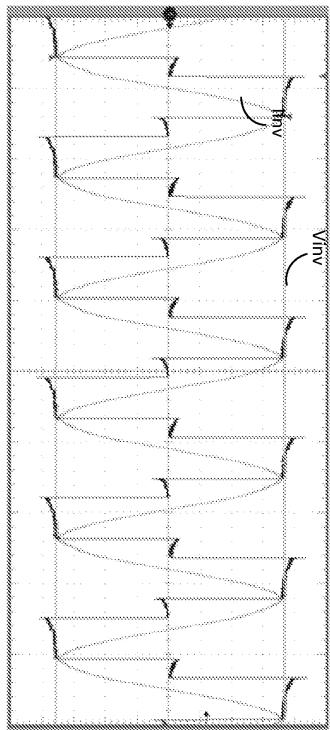

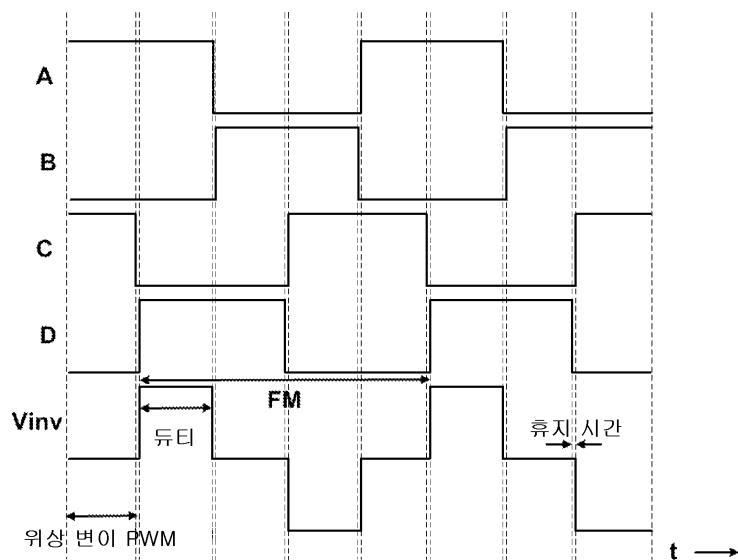

[0022] 도 1a로 다시 돌아가서, 제어 신호 A는 제 1 스위치(121)를 구동하고, 제어 신호 B는 제 2 스위치(122)를 구동하며, 제어 신호 C는 제 3 스위치(123)를 구동하고, 제어 신호 D는 제 4 스위치(124)를 구동한다. 동작시, 제어 신호 A 및 D는 정현 파형의 하부 레일(lower rail)에 대해 제 1 스위치(121)와 제 4 스위치(124)를 각각 턴-온하는데 이용되고, 제어 신호 B 및 C는 정현 파형의 상부 레일(higher rail)에 대해 제 2 스위치(122)와 제 3 스위치(123)를 각각 턴-온하는데 이용된다. 단순화된 타이밍도가 도 1b에 도시되는데, 이 도면은 본 발명의 일 실시예에 따른 영 전압 스위치(ZVS) 스위칭 방식 및 그 결과 출력 응답을 예시한다. ZVS 스위칭 방식은 소프트 스위칭 기술이다. 소프트 스위칭 기술은 영 전압에서 스위칭-온하고 영 전류에서 스위칭-오프하는데 공진 기술을 이용한다. 무시 가능한 스위칭 손실이 이 장치에서 발생할 수 있다.

[0023] 도 1b에 도시된 것처럼, 제어 신호에 위상 변이를 병합함으로써, 모든 스위치를 오프함으로써 초래되는 출력 전압에서의 링잉(ringing)을 최소화하는 것이 가능하다. A 및 D 제어 신호와, B 및 C 제어 신호에 대해 이용되는 위상 변이량은 시스템의 함수이며, 본 주제의 전력 스테이지가 이용되는 특정 시스템에서의 링잉을 막기 위한 임의의 적절한 위상 변이일 수 있다.

[0024] 본 발명의 다양한 실시예에 따르면, 전력 스테이지 제어 신호 A, B, C 및 D는 위상 변이 ZVS를 위해 조합형 펄스 폭 변조(PWM) 및 주파수 변조(FM) 제어 방식을 통해 발생된다.

[0025] 도 4는 본 발명의 일 실시예에 따른 유전체 장벽 방전기 시스템의 블록도를 도시한다. 도 4를 참조하면, 전력 스테이지(410)는 고전압 AC 전력을 부하(420)에 제공하기 위해서 DC 버스 전압  $V_{DC}$ 를 AC 신호로 변환한다. 특정 실시예에서, 전력 스테이지(410)의 구성과 부하(420)는 도 1a 및/또는 도 3에 도시된 것처럼 배열된다. 전력 스테이지 제어 신호 A, B, C 및 D는 피드백 루프의 일부를 형성하는 제어 회로(430)에 의해 발생 및 제어된다. 제어 회로(430)는 FM 제어와 조합된 위상 변이 ZVS PWM을 포함할 수 있다. 특정 실시예로, 전력 스테이지 제어 신호를 위한 신호 발생기는 위상 변조 및 가변 주파수 가능 PWM 칩이다. 물론, 일부 실시예로, 위상, 뉘티 사이클 및 주파수의 제어를 가능하게 하는 임의의 회로 또는 칩이 이용될 수 있는데, 여기서 출력 신호의 적어도 뉘티 사이클과 주파수는 이 회로나 칩에 대한 하나 이상의 입력에 의해 조정될 수 있다. 제어 신호 A, B, C 및 D의 펄스폭은 제어 회로(430)의 PWM 피드백 제어 방식에 의해 제어되고, 제어 신호 A, B, C 및 D의 주파수는 제어 회로(430)의 FM 피드백 제어 방식에 의해 제어된다. 특정 실시예에 따르면, PWM 및 FM 피드백 제어 방식은 전류 루프 제어 방식으로 구현되며, 여기서 출력 전류는 전력 스테이지의 출력에서 감지되어, 전력 스테이지

에 되공급되는 신호의 펄스폭 및 주파수를 제어하는데 이용된다.

[0026] 일 실시예에 따르면, PWM 제어와 PM의 통합은 단독의 PWM 기반 제어 방식의 경부하 하드 스위칭에 대항한다. 경부하에서는 인버터 출력 전압의 펄스폭이 크게 감소하므로 하드 스위칭이 일어난다. 이후에 이것은 공진 인덕터의 전류가 그에 따라 크게 감소하게 만든다. 그러므로, 공진 인덕터에 충분히 저장된 에너지가 없다면, 반도체 전력 장치는 소프트 스위칭을 더 이상 지속시키지 못한다.

[0027] 하드 스위칭에서, 접합 캐패시턴스에 저장된 에너지는 각각의 턠-온에서 트랜지스터로 방전된다. 그러므로, 하드 스위칭은 전력 손실, 전압/전류 스파이크(spike) 및 전자기 간섭(EMI) 문제들을 초래할 수 있다. 본원에 설명된 소프트 스위칭 토플로지와 함께 조합형 PWM 및 FM 제어 방식은 추가의 냉각 시스템에 대한 필요성을 없앤다. 예를 들어, 전술한 것처럼, 스위칭 신호를 제어하는데 오로지 PWM만 이용될 때, 하드 스위칭이 경부하에서 발생할 수도 있다. 이와 대조적으로, 본 발명의 일 실시예의 조합형 PWM 및 FM 제어 방식은 모든 부하(전부하 및 경부하)에 대해 소프트 스위칭을 가능하게 한다.

[0028] "경부하" 조건은 특정 시스템에 따르며, 일반적으로 전부하의 약 5%인 것으로 이해된다. 실제로, 경부하와 관련한 특정 비율은 오존이 계속 발생될 수 있는 비율이다. 본 개시물에서 예로서 예시된 것처럼, 본 발명의 실시예는 전부하의 5% 미만에서 동작할 수 있고, 오존이 발생되지 않을 때에도 기능할 수 있다.

[0029] 동작시, 본 주제의 조합형 PWM 및 FM 제어 방식은 경부하에서 주파수를 증가시켜서, 이전에 감소된 펄스폭이 무시될 수 있게 한다. 동작동안, PWM 및 FM 제어 방식은 병렬로 실행되지만, PWM과 FM에 제공되는 가중치는 부하상태의 변화에 따라 가변한다. 이것은 개선된 동적 범위 성능을 가져온다. 예를 들어, 정규 동작(전부하를 포함한)에서, 듀티 사이클은 오존 출력 전력을 제어하는데 이용되고, 반면에 경부하와 관련해서는 스위칭 주파수를 증가시킴으로써 이 전력이 더 감소된다. 또한, 특정 실시예에서 전력 시스템의 전력 스테이지가 최대 출력 전력의 0%까지 떨어지게 소프트 스위칭(예컨대, 영전압 스위칭)하도록 구성되므로, 전력 시스템의 신뢰성이 개선될 수 있다.

[0030] 도 5a는 일 실시예에 따른 전류 루프 제어 방식의 블록도를 도시한다. 이 도면은 완벽한 전류 루프 제어 방식을 위한 각각의 개별 이득의 전달 함수 블록을 제공한다. 함수 블록은 전치 증폭기 이득 블록(Pre-amp Gain Block)(501), 전류 루프 보상 이득 블록(current loop Compensation Gain Block)(502), PWM 이득 블록(503), FM 이득 블록(504), 공진 탱크 및 부하 이득 블록(505) 및 피드백 이득 블록(506)을 포함한다.

[0031] 일 실시예에 따르면, 전류 루프내의 각각의 개별 이득 블록의 수식은 다음과 같다.

[0032] "전치 증폭기 이득 블록"

$$G_{pre}(s) = G_{pre_{DC}} * 1/(s / 2 * \pi * fp\alpha + 1)$$

[0034] 전류 루프 "보상기 이득 블록"

$$G_{comp}(s) = G_{comp_{DC}} * (s + 2 * \pi * fz) / [s * (s / 2 * \pi * fp\beta + 1)]$$

[0036] "공진 탱크 및 부하 이득 블록"

$$H(s) * G_{out}(s) = G_{pwr}(s)$$

[0038] 예를 들어,

$$G_{pwr}(s) = \omega_o^2 / [s^2 + (1/Q) * \omega_o * s + \omega_o^2] \text{ 이고, 여기서 } \omega_o = 1/\sqrt{(Lr * Co * N^2)} \text{ 이다.}$$

[0040] 전류 "피드백 이득 블록"

$$G_{fbk}(s) = G_{fbk_{DC}} * 1/(s / 2 * \pi * fp\chi + 1)$$

[0042] PWM 이득 블록 및 FM 이득 블록과 관련해서는,  $K_{pwm} \neq K_{fm}$ =상수이다.

[0043] 도 5a를 참조하면, 전류 설정 포인트(Iset)가 특정 값으로 제공된다. 특정 실시예에서, 이것은 프로세서를 이용하여 수행될 수 있다(도 5b와 관련한 이하의 설명을 참조하라). 또한, 인버터 전력 스테이지(도 4의 도면부호(410) 참조하며, 도 5a에 도시된 것처럼 공진 탱크 및 부하 이득 블록(505)을 포함함)로부터 출력된 실제 전류(Iout)는 전류 센서에 의해 측정될 수 있으며, 피드백 이득 블록(506)을 통해 피드백 루프로 입력될 수 있다.

Iset(이것은 전치 증폭기 이득 블록(501)에 대응하는 전치 증폭기 스테이지를 통해 증폭될 수도 있다)와 피드백 이득 블록(506)으로부터 출력된 전류(Ifbk)는 대표적인 이득 블록(502)을 갖는 전류 루프 보상기에서 더해진다. 다음, 이 이득 스테이지의 출력은 위상 변이 PWM 및 FM 제어기 회로 또는 칩(대응하는 PWM 이득 블록(503)과 FM 이득 블록(504)을 가짐)에 의해 이용되어, 전력 스테이지의 게이트 드라이브(도 6a 및 도 6b 참조)에 대해 스위칭 주파수(Fsw)를 발생시킨다. 피드백 루프는 Iset 값과 동일한 레벨로 출력 전류를 유지하는 방식으로 수행한다.

[0044] 경부하의 경우, 전류 루프 보상기 이득 블록(503)은 PWM 칩의 클록의 주파수 시상수(frequency time constant)를 변경하는데 이용되는데, 이것은 주파수 변조로 하여금 Fsw가 시상수에 역비례하므로 발생하게 한다. 그러므로, 전력이 순간적으로 떨어질 때 주파수 변조 제어는 주파수를 낮추어 전력이 적절한 레벨로 유지될 수 있도록 한다.

[0045] 도 5a에 도시된 전류 루프 도면은 아날로그 제어 방식을 예시한다. 다른 실시예로, 도 5a에 도시된 아날로그 제어 방식을 대신하거나 또는 추가적으로 도 5b에 도시된 것같은 디지털 제어 방식이 활용될 수 있다. 도 5b는 ZVS 공진 인버터를 위한 제어 방식의 전력 루프와 내부 전류 루프를 갖는 시스템 수준 도면을 제공한다. 전류 루프 부분은 도 5a와 관련하여 설명된 것과 유사하게 기능을 수행한다. 일 실시예에 따르면, 전력 루프는 디지털 제어 방식을 이용하고, 전력 루프는 프로세서를 이용하여 구현된다. 제한하려는 것은 아니지만, 프로세서는 저가의 마이크로프로세서( $\mu$ P) 또는 디지털 신호 처리기(DSP)일 수 있다. 메모리는 프로세서의 일부로 포함될 수도 있고, 또는 별도의 성분으로 포함될 수도 있다. 동작시, 마이크로프로세서는 전력 설정 포인트(Pset)를 발행한다. 또한, 실제 입력 전력은 두 개의 DC 입력 공급원(Kvb(s)(508a) 및 Kib(s)(508b)같은)으로부터의 이득과 스케일링되어 입력 전력 이득 블록과 함께 곱셈된 DC 버스 전압(도 4의  $V_{DC}$  또는 도 1 및 도 3에 도시된 Vbus) 및 DC 버스 전류(도 1 및 도 3의 Ibus 참조)를 이용하여 측정된다. 스케일링 및 곱셈된 DC 입력 공급원의 곱은 전력 피드백 신호(Pfbk)를 만든다. 전력 설정 포인트 Pset과 전력 피드백 Pfbk는 함께 더해져서 디지털 전력 루프 보상기(PID)로 공급된다. PID의 출력은 도 5a와 관련해 설명된 것처럼 전류 설정 포인트 Iset이다.

[0046] 도 5a에서처럼, 도 5b에 도시된 도면은 전력 루프(내부 전류 루프와 함께 제어 방식에 대해 각각의 개별 이득의 전달 함수 블록을 제공한다. 일 실시예에 따르면, 전류 루프내의 각각의 개별 이득 블록의 수식은 도 5a와 관련해 제공된 것처럼 표현될 수 있으며, 전력 루프에 대한 각각의 개별 이득 블록은 다음과 같이 표현될 수 있다.

[0047] "디지털 전력 루프 보상기 이득 블록"

$$PID(z) = Kp + Ki / (1 - z^{-1}) + Kd * (1 - z^{-1})$$

[0049] 여기서,  $z = e^{s/Fclk}$ 이고, Fclk =  $\mu$ P\_Clock(프로세서로부터의 클록의 주파수)이다.

[0050] 입력 전력 이득 블록에 대해, 전력 피드백 버스 전압 "Vbus" 이득 블록은 다음과 같이 표현될 수 있다.

$$Kvb(s) = Kvb_{DC} * 1 / (s / 2 * \pi * fp\phi + 1)$$

[0052] 그리고 전력 피드백 버스 전류 "Ibus" 이득 블록은 다음과 같이 표현될 수 있다.

$$Kib(s) = Kib_{DC} * 1 / (s / 2 * \pi * fp\phi + 1)$$

[0054] 분석을 단순화하기 위해 고차 고조파(기본 고조파에 대한)는 무시하면서 모델의 성분들은 이상화되었음을 이해해야 한다.

[0055] 다른 실시예에서, 입력 전력을 제어(그리고 도 5b에 예시된 전력 루프를 이용)하는 대신에 출력 부하 전력 제어가 이용될 수 있다. 예를 들어, 인버터 스테이지의 출력에서 감지되는 출력 오존 전압 및 인버터 전류는 제어 루프의 일부로서 이용될 수 있다. 오존 셀이 복소 임피던스처럼 동작하고 전류와 전압은 둘 다 적절히 고주파수이므로, 대역폭, 슬루율(slew rate), 샘플링 시간 및 다른 요인들은 전류와 전압의 곱을 실시간으로 찾기 위해 요구된다.

[0056] 또다른 실시예에서, 도 5b에 도시된 전력 루프는 오존 농도에 기반하여 폐쇄(closed)될 수 있다. 예를 들어, 오존 셀로부터의 오존 농도가 농도 트랜스듀서(concentration transducer)로 측정될 수 있고, 이 트랜스듀서의

출력은 전력 루프를 닫는데 이용될 수 있다.

[0057] 도 6a 및 도 6b는 도 5a와 관련하여 설명된 제어 방식을 따르는 두 개의 예시적인 전류 루프 회로 구현을 예시 한다. 도 6a 및 도 6b에 도시된 것처럼, 인버터 스테이지의 출력에서의 전류는 전류 센서(601)에 의해 측정되고, Iset과 함께 전류 루프 오차 증폭기 보상기(602)에 공급된다. 일 실시예로, 도 6a에 도시된 것처럼, Iset은 전류 루프 오차 증폭기 보상기(602)의 정극성 입력 단자에 대한 입력으로서 제공되고, Ifbk는 전류 루프 오차 증폭기 보상기(602)의 부극성 입력 단자에 대한 입력으로서 제공된다. 다른 실시예에서, 도 6b에 도시된 것처럼, Iset 및 Ifbk는 합산되어, 둘 다 전류 루프 오차 증폭기 보상기(602)의 부극성 입력 단자에 제공된다. 오차 증폭기 보상기(602)의 출력은 위상 변이 PWM 제어기(603)에 대한 듀티 사이클 커맨드를 제공하고, PWM 제어기(603)가 게이트 드라이버(604)에 대해 스위칭 주파수 Fsw를 발생할 수 있게 한다. 스위칭 주파수는 오차 증폭기 보상기(602)의 출력을 수신하여 PWM 제어기(603)로 신호를 출력하는 인버팅 증폭기(605)를 통해 주파수 변조될 수 있다. 인버팅 증폭기(605)의 출력은 PWM 클록의 주파수 시상수를 변경하여, 주파수 변조가 일어나게 한다.

[0058] 게이트 드라이버(604)는 예컨대 도 1a 및 도 1b와 관련하여 설명된 것(스위치(121, 122, 123, 124)) 및 도 3과 관련하여 설명된 것(전력 스테이지(320)이 스위치(321, 322, 323, 324))같은 풀 브릿지 인버터 스테이지에 대해 제어 신호 A, B, C 및 D를 발생한다.

[0059] PWM 제어기(603)와 연결된 캐패시터 Ct와 저항기 Rt는 인버팅 증폭기(605)로부터의 전류 보상 신호에 의해 조정되는 초기 고정 주파수(initial fixed frequency)를 제공한다. 도 6a 및 도 6b에 도시된 인버팅 증폭기 구성에서, op-증폭기는 듀티 사이클(펄스폭)을 제어하는데 이용되는 신호의 배수(또는 분수)로 주파수 변조를 제어하는데 이용되는 신호를 조정하는데 이용될 수 있다. 다른 실시예로, FM 제어를 위한 증폭기의 이득은 가변 이득 증폭기를 이용함으로써 가변될 수 있다. 프로세서가 전송한 이득 제어 신호를 이용하여 이득이 제어될 수도 있다. 일 실시예로, 특정 조건이 충족될 때, 프로세서와 연관된 메모리내에 저장된 사전설정 변경(preset modification)이 이용될 수도 있다. 다른 실시예에서, 이를 조정의 사용자 제어를 가능하게 하기 위해 사용자 인터페이스가 포함될 수도 있다. 사용자 인터페이스는 프로세서에 연결되어 프로세서와 통신할 수도 있다. 선택적으로, 또는 추가적으로, 사용자 인터페이스는 전위차계(potentiometer)를 통한 저항의 수동 조정을 포함할 수도 있다(이것은 예컨대 도 6a의 R4 또는 도 6b의 R4를 조정할 수 있다).

[0060] 도 7 내지 도 9는 본 발명의 일부 실시예에 따른 전류 루프 구성을 예시한다. 예를 들어, 도 7을 참조하면, 제 2 실시예에 따른 전류 루프 제어 방식은 도 5a에 도시된 방식과 유사하다. 그러나, 전력 스테이지의 게이트 드라이브(도 6a 및 도 6b의 도면부호(604) 참조)를 위한 스위칭 주파수(Fsw)를 발행하기 위해 위상 변이 PWM 및 FM 제어기에 의해 이용되는 보상기 이득 블록(702) 스테이지의 출력을 대신하여, 전류 루프 보상기와 별별로 FM 이득 블록(704) 스테이지가 Iset(전치 증폭기 이득 블록(701)에 대응하는 전치 증폭기 스테이지를 통해 증폭될 수 있음)와, 피드백 이득 블록(706)으로부터 출력된 전류(Ifbk)를 수용한다.

[0061] 도 8에 도시된 실시예의 경우, FM 이득 블록(804) 스테이지는 Iset 전류와 도 5a 또는 도 7과 관련해 설명된 것 같은 피드백 이득 블록(806)으로부터 피드백 전류를 대신해 주파수를 제어하기 위해 입력 전력을 이용한다. 예를 들어, DC 버스 전압(도 4의 V<sub>DC</sub> 또는 도 1 및 도 3에 도시된 Vbus)과 DC 버스 전류(도 1 및 도 3의 Ibus 참조)는 두 개의 DC 입력 공급원(Kvb(s)(808a) 및 Kib(s)(808b)같은)으로부터의 이득과 스케일링되고, FM 이득 블록(804)을 통해 입력되기 전에 함께 곱셈된다.

[0062] 도 9에 도시된 실시예의 경우, FM 이득 블록(904) 스테이지는 도 8과 관련해 설명된 것처럼 입력 전력을 대신하여 주파수를 제어하기 위해 출력 전력을 이용한다.

[0063] 특정 실시예로, 도 5b와 관련해 설명된 전력 루프 부분은 도 7 내지 도 9에 도시된 전류 루프 중 하나로 구성될 수 있다.

[0064] 바람직하게는, 특정 실시예로, 전력을 유지하면서 전력선 변화를 수용하는 표준이 공간을 차지하면서 추가적인 냉각 기술도 요구할 수 있는 별도의 회로나 보호 캐패시터를 요구하지 않으면서 충족될 수 있다. 특히, 주파수 변조 제어를 이용함으로써, 전력선상의 부하로 인한 변화가 스위치를 구동하는 주파수의 변화와 전력선상의 전력을 유지하는 능력을 초래한다. 본 주제의 조합형 PWM 및 FM 제어 방식에 의해 충족될 수 있는 표준의 일 예가 SEMI F47 표준 "Specification for Semiconductor Processing Equipment Voltage Sag Immunity"로, 이것은 반도체 공정, 계측학 및 자동화 테스트 장비에서 이용되는 툴(tool)이 방해없이 끝까지 동작해야 하는 순간 전압 강하 보상 능력(또는 임계)을 정의한다.

- [0065] 본 주제의 전력 시스템과 전력 제어 기술의 실시예는 이전의 시스템의 사이즈를 증가시키지 않으면서 구현될 수 있다. 다양한 실시예에서, 전력 시스템은 동일하거나 더 큰 출력 전력 및 제어를 제공하면서 종래의 비상주(non-resident) 전력 인버터보다 더 밀집한 공간에 설치될 수 있다.

- [0066] 본 발명의 보다 나은 이해와 많은 이점들은 예시로서 제공된 다음의 예들로부터 제공될 수 있다. 다음의 예는 본 발명의 방법, 응용, 실시예 및 변형 중 일부를 예시하는 것이다. 물론 이들은 어떤 방식으로든 본 발명을 제한하지 않는 것으로 간주되어야 한다. 다양한 변화와 수정이 본 발명과 관련하여 수행될 수 있다.

- [0067] Cadence Design Systems, Inc.의 등록된 상표인 PSpice® 회로 시뮬레이터 툴이 본 발명의 일 실시예에 따라 설계된 유전체 장벽 방전기를 시뮬레이트하는데 이용되었다.

- [0068] 이 예에서, 듀얼 10kW 오존 전력 트레인(전력 트레인당 5kW)을 위한 PSpice® 시뮬레이션은 본 시스템 및 방법의 기능을 예시하는 실험 결과와 비교된다. 도 10은 본 발명의 일 실시예에 따른 범용 ZVS 공진 인버터 전류 루프 설계의 PSpice® 시뮬레이션에 이용되는 PSpice® 회로도를 도시한다. 이 회로도는 도 6b에 도시된 것과 유사한 구현을 따르는데, 여기서 피드백 전류 및 전류 설정 포인트 Iset은 보상기에 입력되기 전에 합산된다. 또한, 전류는 공통 모드 잡음을 막기 위해 차동 증폭기를 이용하여 측정된다. 공진 탱크 및 오존 셀은 도 1a와 관련하여 설명된 인덕터(105), 캐패시터(111) 및 저항기(112) 구성을 이용하여 시뮬레이트된다.

- [0069] 시뮬레이션을 위해, 입력 Vbus 전압은 저 라인 값에서부터 고 라인 값(200~350 VDC)까지 변화되었고, Iset은 0.5~3.0 VDC(0.5% 내지 110% 부하)에서 전압원을 이용하여 변화되었다. 이러한 두 조건은 예측된 동작 범위를 포함한다.

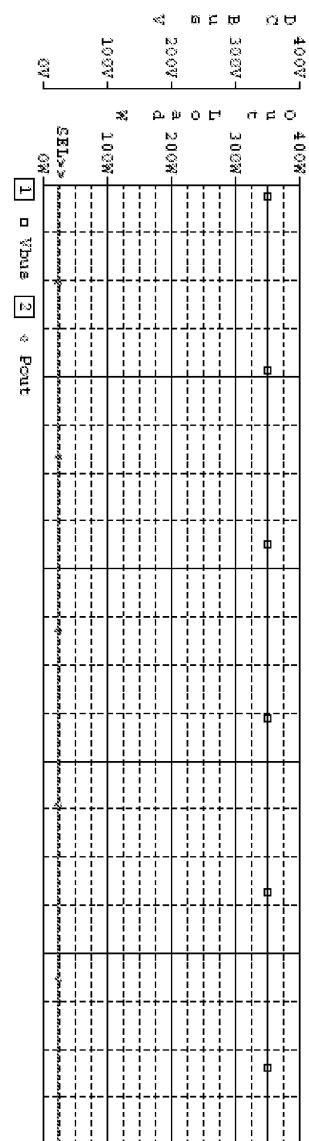

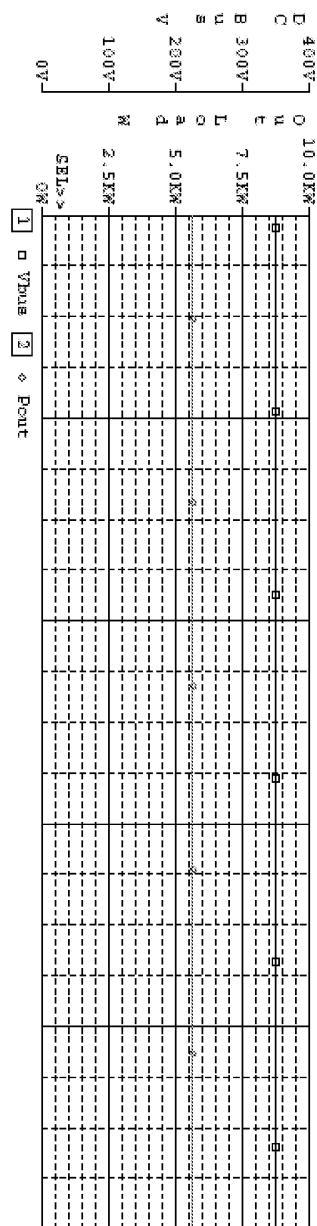

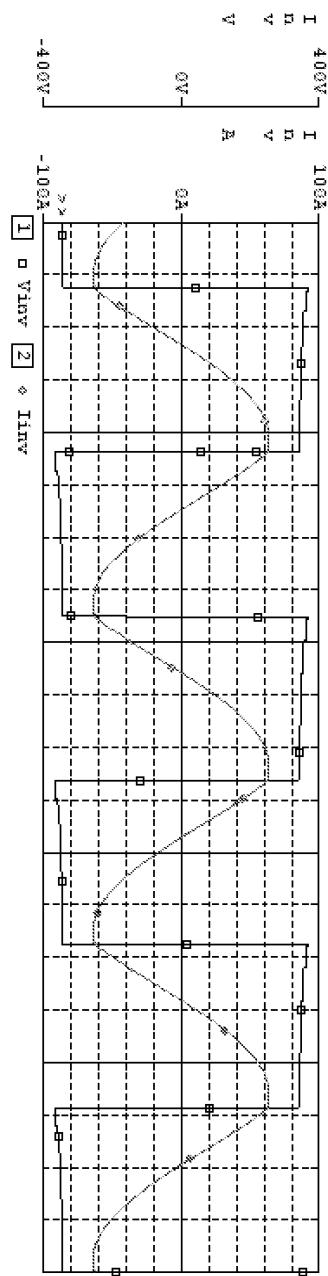

- [0070] 예 1-경부하(Light Load)

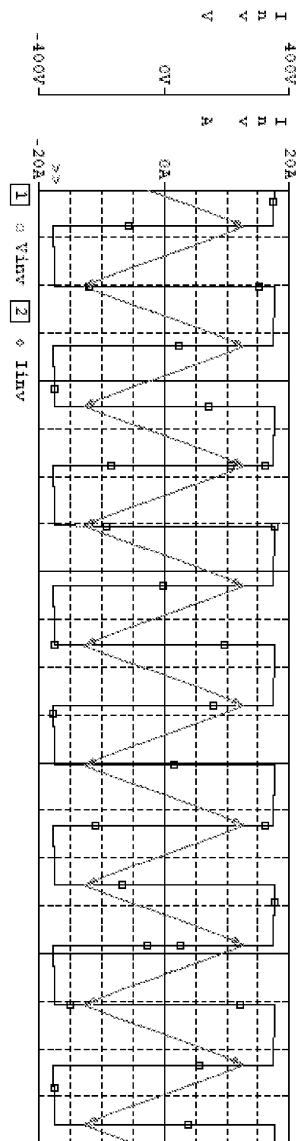

- [0071] 경부하에서 전류 루프에 대한 시뮬레이션 결과는 도 11a 내지 도 11c에 도시되며, 경부하에서 전류 루프에 대한 실험 결과는 도 11d에 도시된다. 도 11a는 Vbus가 350V에 설정되었음을 보여주고, 경부하 상태는 출력 부하 전력이 25W 미만(5kW 시스템의 최대 출력의 5% 오존 농도의 ~250V 출력 전력 경부하 상태와 비교하여)임을 보여준다. 도 11b는 인버터 스테이지 출력 전압(Vinv)과 전류(Iinv)의 구성도를 도시한다. 도 11c는 전력 스테이지 출력 전압(Vout)과 전류(Iout)의 구성도를 도시한다(즉, 오존 셀로 공급되는 전압과 전류). 도 11d는 실험 시스템과 관련하여 인버터 스테이지 출력 전압 Vinv과 전류 Iinv의 스코프 파형을 도시하며, 여기서 Vbus=300V, Ibus=0.8A, Pin=240W이다. 도 11c에 설명되고 도 11d에 도시된 파형에서 확인할 수 있듯이, PWM과 FM 제어의 조합은 경부하에서도 소프트 스위칭을 가능하게 한다. 시뮬레이션 파형이 0.5% Iset이었고 오존을 발생하는 공정 제한조건으로 인해 실험이 Iset의 ~5%까지 였으므로, 시뮬레이션 및 측정 결과 파형과 관련한 구성도의 스케일은 균일하지 않음을 유의해야 한다.

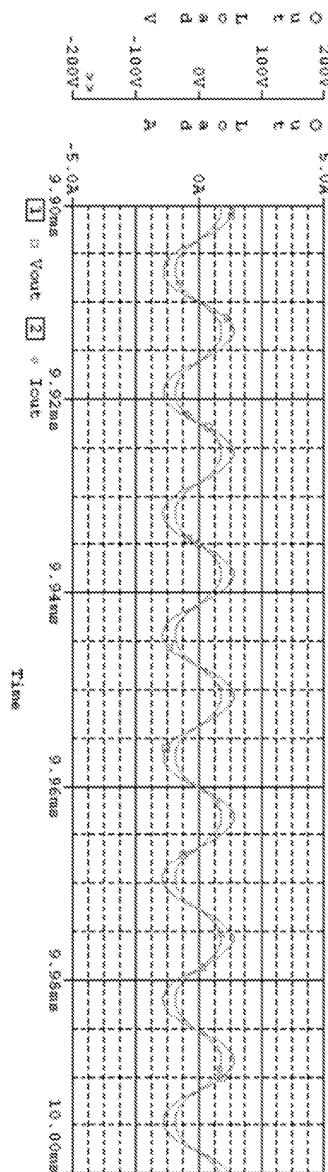

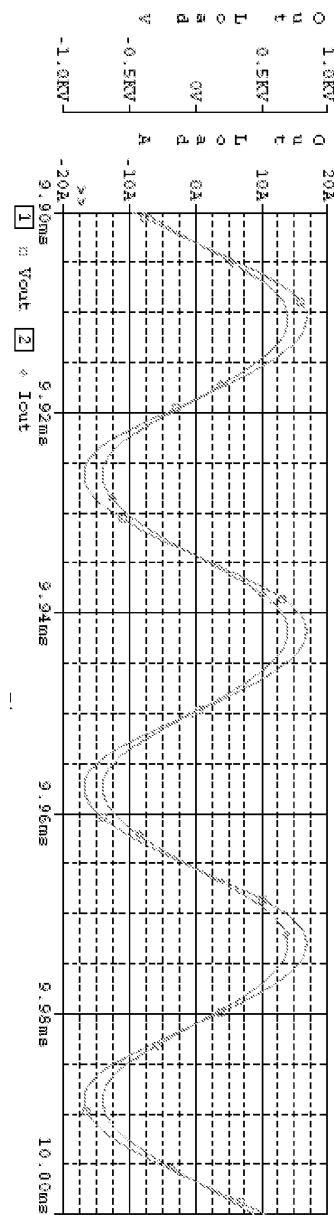

- [0072] 예2-전부하(Full Load)

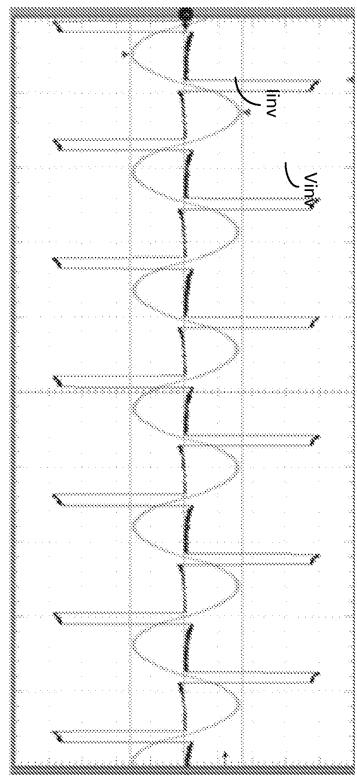

- [0073] 전부하에서 전류 루프에 대한 시뮬레이션 결과가 도 12a 내지 도 12c에 도시되고, 전부하의 110%에서 전류 루프에 대한 실험 결과는 도 11d에 도시된다. 도 12a는 Vbus가 350V였음을 도시하고, 전부하 상태는 약 5.5kW인 출력 부하 전력을 보여준다(단일 스테이지). 도 12b는 인버터 스테이지 출력 전압(Vinv)과 전류(Iinv)의 구성도를 도시한다. 도 12c는 전력 스테이지 출력 전압(Vout)과 전류(Iout)의 구성도를 도시한다(즉, 오존 셀로 공급되는 전압과 전류). 도 12d는 실험 시스템과 관련하여 인버터 스테이지 출력 전압 Vinv과 전류 Iinv의 스코프 파형을 도시하며, 여기서 Vbus=300V, Ibus=18.3A, Pin=~5.5kW이다. 도 12c에 설명되고 도 12d에 도시된 파형에서 확인할 수 있듯이, PWM과 FM 제어의 조합은 소프트 스위칭 및 증가된 출력 전력을 가능하게 한다.

- [0074] 본 명세서에서 "일 실시예", "실시예", "예시적인 실시예", "제 2 실시예" 등으로 언급하는 것들은 언급된 실시예와 연계하여 설명된 특정 특징, 구조 또는 특성이 본 발명의 적어도 한 실시예에 포함된다는 것을 의미한다. 여러 곳에서 이러한 표현이 나타나더라도 이것이 모두 반드시 동일한 실시예를 지칭하는 것은 아니다. 또한, 본원에 개시된 모든 발명 또는 발명의 실시예의 모든 요소 또는 제한조건은 (개별적으로 또는 임의의 조합으로) 임의의 및/또는 모든 다른 요소 또는 제한조건과 조합될 수 있거나 또는 본원에 개시된 임의의 다른 발명이나 그 실시예와 조합될 수 있고, 이러한 조합은 모두 제한없이 본 발명의 범주내에 있는 것으로 고려된다.

- [0075] 본원에 개시된 예들과 실시예는 단지 예시를 목적으로 하는 것임을 이해해야 하며, 그 견지에서 다양한 수정과 변경이 당업자에게 제안될 것이고 이러한 다양한 수정과 변경은 본 출원의 사상과 범주내에 포함되는 것임을 이해해야 한다.

## 도면

## 도면1a

## 도면1b

## 도면2a

## 도면2b

## 도면3

## 도면4

## 도면5a

## 도면5b

## 도면6a

## 도면6b

## 도면7

## 도면8

도면9

도면10

### 도면11a

도면11b

도면11c

도면11d

도면12a

도면12b

도면 12c

도면12d