(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4588312号

(P4588312)

(45) 発行日 平成22年12月1日(2010.12.1)

(24) 登録日 平成22年9月17日(2010.9.17)

|                             |                             |

|-----------------------------|-----------------------------|

| (51) Int.Cl.                | F 1                         |

| G 0 9 F   9/30   (2006.01)  | G 0 9 F   9/30   3 3 8      |

| H 0 1 L   27/32   (2006.01) | G 0 9 F   9/30   3 6 5 Z    |

| H 0 5 B   33/10   (2006.01) | H 0 5 B   33/10             |

| H 0 1 L   51/50   (2006.01) | H 0 5 B   33/14           A |

請求項の数 6 (全 36 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2003-402468 (P2003-402468)  |

| (22) 出願日  | 平成15年12月2日 (2003.12.2)        |

| (65) 公開番号 | 特開2005-164880 (P2005-164880A) |

| (43) 公開日  | 平成17年6月23日 (2005.6.23)        |

| 審査請求日     | 平成18年12月1日 (2006.12.1)        |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 前川 慎志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 藤井 厳<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 納 光明<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 安西 彩<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

最終頁に続く

(54) 【発明の名称】発光装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板200表面にZnOまたはTiO<sub>2</sub>を形成し、

前記ZnOまたは前記TiO<sub>2</sub>上に、スイッチング用TFT230のゲート201、駆動用TFT231のゲート202、及び電流制御用TFT232のゲート203を液滴吐出法または印刷法により形成し、

前記スイッチング用TFT230のゲート201、前記駆動用TFT231のゲート202及び前記電流制御用TFT232のゲート203を覆うゲート絶縁膜205を形成し、

前記ゲート絶縁膜205上に発光素子238の第1の電極206を液滴吐出法または印刷法により形成し、

前記ゲート絶縁膜205を介して、前記スイッチング用TFT230のゲート201、前記駆動用TFT231のゲート202及び前記電流制御用TFT232のゲート203上に、非晶質半導体膜、セミアモルファス半導体膜又は多結晶半導体膜207を形成し、

前記非晶質半導体膜、セミアモルファス半導体膜又は多結晶半導体膜207を介して、前記スイッチング用TFT230のゲート201、前記駆動用TFT231のゲート202及び前記電流制御用TFT232のゲート203上に、第1の保護膜208、第2の保護膜209及び第3の保護膜210をそれぞれ形成し、

レジストマスク211を液滴吐出法または印刷法により形成し、当該レジストマスク211を用いて前記非晶質半導体膜、セミアモルファス半導体膜又は多結晶半導体膜207

10

20

をエッチングして、

前記スイッチング用 TFT230 のチャネル形成領域となる半導体膜 212 を、

前記駆動用 TFT231 及び前記電流制御用 TFT232 のチャネル形成領域となる半導体膜 213 を、それぞれ形成し、

前記ゲート絶縁膜 205 を選択的に除去して前記電流制御用 TFT232 のゲート 203 の一部を露出させ、

前記スイッチング用 TFT230 のチャネル形成領域となる半導体膜 212 、前記駆動用 TFT231 及び前記電流制御用 TFT232 のチャネル形成領域となる半導体膜 213 、前記電流制御用 TFT232 のゲート 203 の露出させた領域及び前記第 1 の電極 206 上に一導電型の不純物が添加された半導体膜 214 を形成し、

前記一導電型の不純物が添加された半導体膜 214 上に、第 1 の配線 215 、第 2 の配線 216 、第 3 の配線 217 、第 4 の配線 218 、第 5 の配線 219 及び第 2 の電源線 241 を液滴吐出法または印刷法により形成し、

前記第 1 の配線 215 は信号線 215 であり、前記第 5 の配線 219 は第 1 の電源線 219 であり、

前記第 1 の配線 215 、前記第 2 の配線 216 、前記第 3 の配線 217 、前記第 4 の配線 218 及び前記第 5 の配線 219 をマスクとして前記一導電型の不純物が添加された半導体膜 214 をエッチングして、

前記第 1 の配線 215 下に、前記スイッチング用 TFT230 のソース及びドレインの一方である半導体膜 220 を、

前記第 2 の配線 216 下に、前記スイッチング用 TFT230 のソース及びドレインの他方である半導体膜 221 を、

前記第 3 の配線 217 下に、前記駆動用 TFT231 のソース及びドレインの一方であり、前記第 1 の電極 206 と電気的に接続される半導体膜 223 を、

前記第 4 の配線 218 下に、前記駆動用 TFT231 のソース及びドレインの他方であるとともに前記電流制御用 TFT232 のソース及びドレインの一方である半導体膜 224 を、

前記第 5 の配線 219 下に、前記電流制御用 TFT232 のソース及びドレインの他方である半導体膜 225 を、それぞれ形成し、

前記スイッチング用 TFT230 、前記駆動用 TFT231 、前記電流制御用 TFT232 を覆うとともに前記第 1 の電極 206 の端部を覆って絶縁膜からなる隔壁 233 を形成し、前記第 1 の電極 206 上の前記隔壁に覆われていない領域には開口部 234 が形成され、

前記開口部 234 において前記第 1 の電極 206 に接するように電界発光層 235 を形成し、

前記電界発光層 235 を覆うように第 2 の電極 236 を形成し、

前記開口部 234 において、前記第 1 の電極 206 、前記電界発光層 235 及び前記第 2 の電極 236 が重なって前記発光素子 238 が形成され、

前記スイッチング用 TFT230 はビデオ信号の画素への入力を制御するものであり、

前記駆動用 TFT231 は前記発光素子 238 に供給する電流値を制御するものあり、

前記電流制御用 TFT232 は前記発光素子 238 への電流の供給の有無を選択するものであり、

前記発光素子 238 の第 1 の電極 206 は、前記駆動用 TFT231 のソース及びドレインの一方と電気的に接続され、

前記駆動用 TFT231 のソース及びドレインの他方は、前記電流制御用 TFT232 のソース及びドレインの一方であり、

前記電流制御用 TFT232 のソース及びドレインの他方は、前記第 1 の電源線 219 に電気的に接続され、

前記駆動用 TFT231 のゲート 202 は前記第 2 の電源線 241 に電気的に接続され

10

20

30

40

50

、前記スイッチング用TFT230のソース及びドレインの一方は前記信号線215に電気的に接続され、ソース及びドレインの他方は前記電流制御用TFT232のゲート203に電気的に接続されていることを特徴とする発光装置の作製方法。

【請求項2】

請求項1において、

前記第2の配線216をマスクとして前記一導電型の不純物が添加された半導体膜214をエッティングすることにより前記電流制御用TFT232のゲート203の露出させた領域上には前記スイッチング用TFT230のソース及びドレインの他方である半導体膜221及び前記第2の配線216が形成されることを特徴とする発光装置の作製方法。

10

【請求項3】

請求項1又は請求項2において、

前記一導電型の不純物はn型を付与する不純物であることを特徴とする発光装置の作製方法。

【請求項4】

請求項1乃至請求項3のいずれか1項において、

前記駆動用TFT231におけるチャネル幅に対するチャネル長の比は、前記電流制御用TFT232におけるチャネル幅に対するチャネル長の比よりも大きくなるように形成することを特徴とする発光装置の作製方法。

【請求項5】

20

請求項1乃至請求項4のいずれか1項において、

前記第2の電極236及び前記電界発光層235のいずれかは、液滴吐出法を用いて形成することを特徴とする発光装置の作製方法。

【請求項6】

請求項1乃至請求項5のいずれか1項において、

前記印刷法はオフセット印刷法またはスクリーン印刷法であることを特徴とする発光装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

30

本発明は、電流を発光素子に供給するための手段と発光素子とを、複数の各画素に有する発光装置及び発光装置の作製方法に関する。

【背景技術】

【0002】

発光素子は自ら発光するため視認性が高く、液晶表示装置(LCD)で必要なバックライトが要らず薄型化に最適であると共に、視野角にも制限が無い。そのため発光素子を用いた発光装置は、CRTやLCDに代わる表示装置として注目されており、近年では携帯電話やデジタルスチルカメラ等の電子機器に搭載されるなど、実用化が行なわれている。

【0003】

発光装置は、パッシブマトリクス型とアクティブマトリクス型とに分類できる。アクティブマトリクス型はビデオ信号の入力後も発光素子への電流の供給をある程度維持することができるので、パネルの大型化、高精細化に柔軟に対応することができ、今後の主流となりつつある。具体的に提案されている、アクティブマトリクス型発光装置における画素の構成は、発光装置のメーカーによって異なっており、それぞれに特色のある技術的工夫が凝らされているが、通常少なくとも、発光素子と、画素へのビデオ信号の入力を制御する薄膜トランジスタ(TFT)と、該発光素子に電流を供給するためのTFTとが各画素に設けられている。

40

【発明の開示】

【発明が解決しようとする課題】

【0004】

50

ところで、画素へのビデオ信号の入力を制御する TFT のオフ電流が大きいと、他の画素に入力されるビデオ信号の電位の変化に伴い、発光素子に供給する電流値を制御する TFT のゲート電極・ソース領域間電圧（以下、ゲート電圧とする） $V_{gs}$  が変動しやすい。このゲート電圧  $V_{gs}$  の変動を防ぐためには、該 TFT のゲート電極・ソース領域間に設けられた容量素子の容量を大きくしたり、画素へのビデオ信号の入力を制御する TFT のオフ電流を低く抑えたりする必要がある。しかし、容量素子の占有面積を大きくすることは、塵埃などに起因する電極間のリークの発生確率を高め、よって歩留まりの低下に繋がるので望ましくない。また、画素へのビデオ信号の入力を制御する TFT のオフ電流を低く抑えること、且つ、大きな容量を充電するためにオン電流を高くすることの両方を満たすように、TFT の作製工程を最適化するには、コストと時間を要し、困難な課題である。さらに発光素子に供給する電流を制御する TFT のゲート電圧  $V_{gs}$  は、ゲート電極につく寄生容量に起因して、他の TFT のスイッチングや信号線、走査線の電位の変動等に伴って、変動し易いという問題もある。

#### 【0005】

また一般的にアクティブマトリクス型の発光装置は、パターニングにリソグラフィ法が用いられている。リソグラフィ法を用いる場合、フォトレジストの成膜、露光、現像、エッチング、剥離などの一連の工程を行なう必要があるため、作製工程が複雑になり、コストが高くなる。さらにリソグラフィ法には高価な露光用のマスク（フォトマスク）が必要であることも、発光装置の作製に費やされるコストが抑えられない一因になっている。そして、成膜後、エッチングにより除去されてしまう部分は結局廃棄されてしまうので、材料が無駄であり、コスト削減という観点から好ましくない。

#### 【0006】

また、パネルが大型化されると必然的に配線が長くなるため、配線抵抗により信号が遅延するという問題が生じる。この場合、配線を厚くして断面積を広げれば、配線抵抗を下げることができ、よって信号の遅延を回避できると考えられる。しかし、リソグラフィ法を用いて配線を形成する場合、配線の厚さはせいぜい  $200 \sim 400 \text{ nm}$  程度であり、それ以上厚いとエッチングの工程に時間がかかるて望ましくない。

#### 【0007】

本発明は上述した問題に鑑み、工程数を抑えたより簡単な作製工程を用いて形成することができ、なおかつ、容量素子の面積を抑えつつ、発光素子に供給する電流を制御する TFT のゲート電圧  $V_{gs}$  の変動によって引き起こされる発光素子の輝度のばらつきを抑えることができる発光装置の提案を課題とする。さらに本発明は、配線の作製工程に費やされる時間を抑えつつ、大型化に伴う配線抵抗の上昇を抑えることができる発光装置及び発光装置の作製方法の提案を課題とする。

#### 【課題を解決するための手段】

#### 【0008】

本発明では、発光素子に供給する電流の値を決める TFT（駆動用 TFT）に加え、スイッチング素子として機能する TFT（電流制御用 TFT）を駆動用 TFT に直列に接続する。そして少なくとも画像を表示するための期間においては、ゲート電極に固定の電位を与えて、常に電流を流せる状態にしておく。また、電流制御用 TFT は線形領域で動作させ、そのゲート電極の電位を、画素に入力されるビデオ信号で制御する。

#### 【0009】

電流制御用 TFT を線形領域で動作させることで、そのソース領域・ドレイン領域間電圧（ドレイン電圧） $V_{ds}$  は発光素子に加わる電圧  $V_{el}$  に対して非常に小さくなり、ゲート電圧  $V_{gs}$  の僅かな変動が、発光素子に流れる電流に影響しにくくなる。そして駆動用 TFT のゲート電極の電位は、ビデオ信号によって制御されず、固定されている。よって、前記電流制御用 TFT のゲート電極・ソース領域間に設けられた容量素子の容量を大きくしたり、画素へのビデオ信号の入力を制御する TFT のオフ電流を低く抑えたりしなくても、発光素子に流れる電流が変動しにくくなる。また発光素子に流れる電流は、電流制御用 TFT のゲート電極につく寄生容量による影響も受けない。そして、電流制御用 TFT

10

20

30

40

50

FTは発光素子への電流の供給の有無を選択するのみであって、発光素子に流れる電流の値は、駆動用 TFT により決定される。このため、ばらつき要因が減り、画質を大いに高めることができる。また、画素へのビデオ信号の入力を制御する TFT のオフ電流を低く抑えるためにプロセスを最適化しなくとも良いので、TFT の作製工程を簡略化することができ、コスト削減、歩留まり向上に大きく貢献することができる。

#### 【0010】

なお本発明では、駆動用 TFT を飽和領域で動作させるのが望ましいが、線形領域で動作させても良い。飽和領域では線形領域に比べて、ドレイン電流がゲート電極・ソース領域間の電圧（ゲート電圧） $V_{gs}$  の僅かな変動に対して、ドレイン電流が大きく影響しやすい。しかし本発明では、駆動用 TFT を飽和領域で動作させても、駆動用 TFT のゲート電極の電位が固定されているので、ゲート電圧  $V_{gs}$  が変動しない。駆動用 TFT を飽和領域で動作させることで、ドレイン電流がドレイン領域・ソース領域間電圧（以下、ドレイン電圧とする） $V_{ds}$  によって変化せず、 $V_{gs}$  のみによって定まるようになるので、発光素子の劣化に伴って  $V_{el}$  が大きくなる代わりに  $V_{ds}$  が小さくなっても、ドレイン電流の値は比較的一定に保たれる。よって、電界発光材料の劣化に伴う発光素子の輝度の低下や輝度むらの発生を抑えることができる。

#### 【0011】

なお、駆動用 TFT におけるチャネル幅  $W$  に対するチャネル長  $L$  の値を、電流制御用 TFT におけるチャネル幅  $W$  に対するチャネル長  $L$  の値よりも大きくする。上記構成によつて、駆動用 TFT の特性の違いに起因する、画素間における発光素子の輝度のばらつきをさらに抑えることができる。

#### 【0012】

また本発明では、上記構成を有する発光装置を、スクリーン印刷法、オフセット印刷法に代表される印刷法、または液滴吐出法を用いて形成する。なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。上記印刷法、液滴吐出法を用いることで、露光用のマスクを用いずとも、信号線、走査線に代表される各種配線、TFT のゲート電極、発光素子の電極などを形成することが可能になる。ただし、本発明の発光装置は、パターンを形成する全ての工程に、印刷法または液滴吐出法を用いる必要はない。よって、例えば配線及びゲート電極の形成には印刷法または液滴吐出法を用い、半導体膜のパターニングにはリソグラフィ法を用いる、というように、少なくとも一部の工程において印刷法または液滴吐出法を用いていれば良く、リソグラフィ法も併用していても良い。またパターニングの際に用いるマスクは、印刷法または液滴吐出法で形成しても良い。

#### 【0013】

なお本発明の発光装置は、発光素子が封止された状態にあるパネルと、該パネルにコントローラを含む IC 等を実装した状態にあるモジュールとを含む。さらに本発明は、該発光装置を作製する過程において、発光素子が完成する前の一形態に相当する素子基板を範疇に含めていても良い。具体的に素子基板は、電流を発光素子に供給するための手段（TFT）を複数の各画素に有している。そして素子基板は、発光素子の第 1 の電極のみが形成された状態であっても良いし、第 1 の電極となる導電膜を形成した後であって、パターニングして第 1 の電極を形成する前の状態であっても良いし、あらゆる形態があつてはまる。

#### 【0014】

また本明細書において発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には OLE D (Organic Light Emitting Diode) や、FED (Field Emission Display) に用いられている MIM 型の電子源素子（電子放出素子）等が含まれる。

#### 【発明の効果】

#### 【0015】

本発明では、容量素子の面積を抑えつつ、発光素子に供給する電流を制御する駆動用 TFT

10

20

30

40

50

F T のゲート電圧  $V_g$  の変動によって引き起こされる発光素子の輝度のばらつきを抑えることができる。

【0016】

また本発明では液滴吐出法、印刷法を用いてパターンを形成することで、リソグラフィ法で行なわれるフォトレジストの成膜、露光、現像、エッチング、剥離などの一連の工程を簡略化することができる。また、液滴吐出法、印刷法だと、リソグラフィ法と異なり、エッチングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、発光装置の作製に費やされるコストを抑えることができる。

【0017】

さらに、リソグラフィ法とは異なり、配線を形成するためにエッチングを行なう必要がない。よって、配線を形成する工程に費やされる時間をリソグラフィ法の場合に比べて著しく短くすることが可能である。特に配線の厚さを  $0.5 \mu m$  以上、より望ましくは  $2 \mu m$  以上で形成する場合、配線抵抗を抑えることができるので、配線の作製工程に費やされる時間を抑えつつ、発光装置の大型化に伴う配線抵抗の上昇を抑えることができる。

【発明を実施するための最良の形態】

【0018】

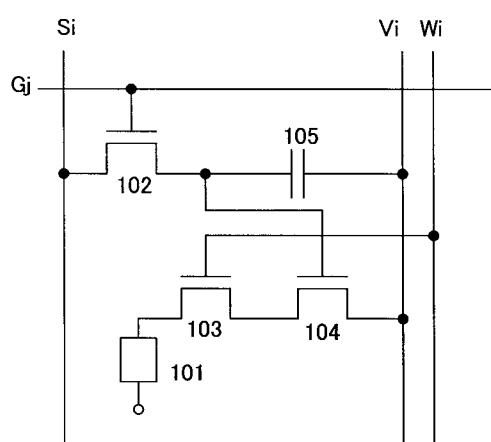

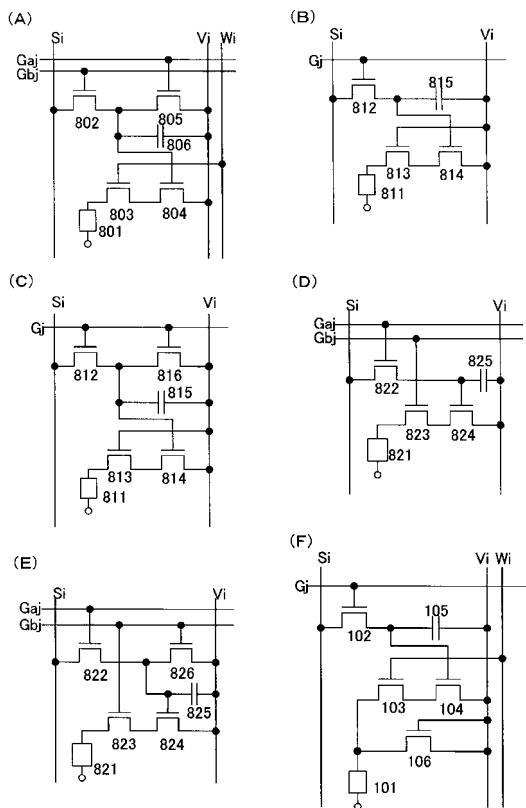

図1に、本発明の発光装置が有する画素の一形態を示す。図1に示す画素は、発光素子101と、ビデオ信号の画素への入力を制御するためのスイッチング素子として用いるTFT(スイッチング用TFT)102と、発光素子101に供給される電流の値を制御する駆動用TFT103と、発光素子101への電流の供給の有無を選択する電流制御用TFT104とを有している。さらに本実施の形態のように、ビデオ信号の電位を保持するための容量素子105を画素に設けていても良い。

【0019】

図1では、スイッチング用TFT102、駆動用TFT103及び電流制御用TFT104は同じ極性であるが、極性はn型であっても、p型であってもどちらでも良い。ただし、TFTにセミアモルファス半導(微結晶半導体)体または非晶質半導体を用いる場合、p型よりもn型の方が高い移動度が得られるので、スイッチング用TFT102、駆動用TFT103及び電流制御用TFT104を全てn型にすることが望ましい。本実施の形態では、スイッチング用TFT102、駆動用TFT103及び電流制御用TFT104が全てn型の場合について説明する。アモルファス半導体、セミアモルファス半導体を用いたTFTは多結晶半導体を用いたTFTよりも作製工程が少ない分、コスト、歩留まりを高くすることができるというメリットを有している。また半導体膜の成膜後に結晶化の工程を設ける必要がないので、比較的パネルの大型化が容易である。

【0020】

セミアモルファス半導体とは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体を含む膜である。このセミアモルファス半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を  $0.5 \sim 20 nm$  として非単結晶半導体中に分散させて存在せしめることが可能である。セミアモルファス半導体は、そのラマンスペクトルが  $520 cm^{-1}$  よりも低波数側にシフトしており、またX線回折ではSi結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。また、未結合手(ダングリングボンド)の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体(SAS)と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。

【0021】

また本実施の形態では、駆動用TFT103を飽和領域動作させる例について説明するが、線形領域で動作させても良い。また、スイッチング用TFT102及び電流制御用TFT104は線形領域で動作させる。駆動用TFT103にはエンハンスマント型TFTを用いてもよいし、ディプリーション型TFTを用いてもよい。

10

20

30

40

50

## 【0022】

スイッチング用 TFT102 のゲート電極は、走査線  $G_j$  ( $j = 1 \sim y$ ) に接続されている。スイッチング用 TFT102 のソース領域とドレイン領域は、一方が信号線  $S_i$  ( $i = 1 \sim x$ ) に、もう一方が電流制御用 TFT104 のゲート電極に接続されている。駆動用 TFT103 のゲート電極は第 2 の電源線  $W_i$  ( $i = 1 \sim x$ ) に接続されている。そして駆動用 TFT103 及び電流制御用 TFT104 は、第 1 の電源線  $V_i$  ( $i = 1 \sim x$ ) から供給される電流が、駆動用 TFT103 及び電流制御用 TFT104 のドレイン電流として発光素子 101 に供給されるように、第 1 の電源線  $V_i$  ( $i = 1 \sim x$ ) と、発光素子 101 とに接続されている。本実施の形態では、電流制御用 TFT104 のソース領域が第 1 の電源線  $V_i$  ( $i = 1 \sim x$ ) に接続され、駆動用 TFT103 のドレイン領域が発光素子 101 の第 1 の電極に接続される。10

## 【0023】

なお駆動用 TFT103 のソース領域を第 1 の電源線  $V_i$  ( $i = 1 \sim x$ ) に接続し、電流制御用 TFT104 のドレイン領域を発光素子 101 の第 1 の電極に接続してもよい。

## 【0024】

発光素子 101 は第 1 の電極と、第 2 の電極と、第 1 の電極と第 2 の電極の間に形成された電界発光層とを有している。第 1 の電極と第 2 の電極は、いずれか一方が陽極に、他方が陰極に相当する。駆動用 TFT103 が  $n$  型である場合、第 1 の電極が陰極、第 2 の電極が陽極であることが望ましい。逆に、駆動用 TFT103 が  $p$  型である場合、第 1 の電極が陽極、第 2 の電極が陰極であることが望ましい。本実施の形態では駆動用 TFT103 が  $n$  型であるので、第 1 の電極が陰極、第 2 の電極が陽極の場合について説明する。20

## 【0025】

容量素子 105 が有する 2 つの電極は、一方は第 1 の電源線  $V_i$  ( $i = 1 \sim x$ ) に接続されており、もう一方は電流制御用 TFT104 のゲート電極に接続されている。容量素子 105 は、電流制御用 TFT104 のゲート電圧を保持するために設けられている。なお図 1 では容量素子 105 を設ける構成を示したが、本発明はこの構成に限定されず、容量素子 105 を設けずに電流制御用 TFT104 のゲート容量を用いて、電流制御用 TFT104 のゲート電圧を保持するようにしても良い。

## 【0026】

次に、図 1 に示した画素の駆動方法について説明する。図 1 に示す画素は、その動作を書き込み期間、保持期間とに分けて説明することができる。図 2 (A) に、書き込み期間において電流制御用 TFT104 がオンの場合の動作を、図 2 (B) に、書き込み期間において電流制御用 TFT104 がオフの場合の動作を示す。また図 2 (C) に、保持期間において電流制御用 TFT104 がオンの場合の動作を、図 2 (D) に、保持期間において電流制御用 TFT104 がオフの場合の動作を示す。なお、図 2 (A) ~ 図 2 (D) では動作を分かり易くするために、スイッチング用 TFT102 と、電流制御用 TFT104 とを単にスイッチとして示す。30

## 【0027】

まず書き込み期間において、走査線  $G_j$  ( $j = 1 \sim y$ ) が選択されると、走査線  $G_j$  ( $j = 1 \sim y$ ) にゲート電極が接続されているスイッチング用 TFT102 がオンになる。そして、信号線  $S_i$  ( $i = 1 \sim x$ ) に入力されたビデオ信号が、スイッチング用 TFT102 を介して電流制御用 TFT104 のゲート電極に入力される。電流制御用 TFT104 は、入力されたビデオ信号の電位によりスイッチングが制御される。一方、駆動用 TFT103 のゲート電極には、電流制御用 TFT104 のゲート電圧が供給される。駆動用 TFT103 がオンになるような高さの電位が、第 2 の電源線  $W_i$  ( $i = 1 \sim x$ ) から常に与えられている。40

## 【0028】

なお本実施の形態では、書き込み期間及び保持期間において、第 1 の電源線  $V_i$  ( $i = 1 \sim x$ ) と発光素子 101 の第 2 の電極とには、それぞれ高さの異なる電位を与えるようにし、該 2 つの電位は、駆動用 TFT103 及び電流制御用 TFT104 がオンのときに、発光素子 101 に順方向バイアスの電流が供給される程度の高さに設定する。よって、50

図2(A)に示すように電流制御用TFT104がオンになると、発光素子101へ電流が供給され、発光素子101が発光する。また図2(B)に示すように電流制御用TFT104がオフになると、発光素子101への電流の供給は停止し、発光素子101は非発光の状態となる。

【0029】

なお本発明では上述したように、書き込み期間において電流制御用TFT104がオンのときに、ビデオ信号に従って発光素子を発光させる必要は必ずしもない。例えば書き込み期間において、電流制御用TFT104のスイッチングに関わらず、発光素子101への電流の供給を止めておいても良い。具体的には、発光素子101の第2の電極と第1の電源線Viの間の電位差を埋めれば良い。または、発光素子101をダイオードに見立てたときに、発光素子101が有する一対の電極間に逆方向バイアスの電圧がかけられるよう、第2の電極と第1の電源線Vi( $i = 1 \sim x$ )の間の電位差を設定すれば良い。或いは、発光素子101に流れる電流の経路をスイッチ等で遮断しても良い。この場合、電流制御用TFT104がオンになっていても、オフになっていても、書き込み期間においては発光素子101への電流の供給は停止する。よって書き込み期間において、全ての発光素子101は非発光の状態となる。

【0030】

次に、走査線Gj( $j = 1 \sim y$ )の電位を制御することでスイッチング用TFT102をオフにすることで、書き込み期間において書き込まれたビデオ信号の電位が保持され、保持期間が開始される。

【0031】

保持期間では、発光素子101の第2の電極と、第1の電源線Vi( $i = 1 \sim x$ )の間に、電流制御用TFT104がオンであるならば発光素子101に順方向バイアスの電流が供給されるような電位差を設ける。そしてさらに、電流制御用TFTがオンであるならば発光素子に流れる電流の経路が確保されている状態にする。

【0032】

よって、ビデオ信号によって電流制御用TFT104がオンになる場合は、図2(C)に示すように、発光素子101に電流が供給される。発光素子101に流れる電流は、駆動用TFT103のドレイン電流と、発光素子101の電圧電流特性によって決まる。そして発光素子101は、供給される電流に見合った高さの輝度で発光する。逆に、書き込み期間において電流制御用TFT104をオフにした場合、図2(D)に示すように、ビデオ信号の電位は容量素子105によって保持されているので、発光素子101への電流の供給は停止しており、発光素子101は非発光の状態となる。

【0033】

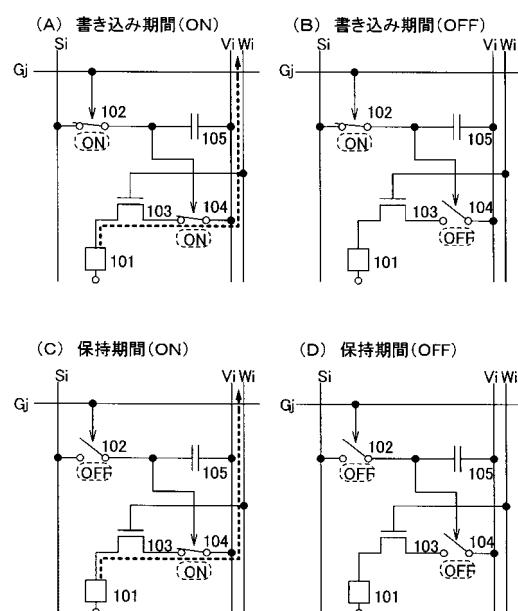

なお図1に示した画素において、発光素子101の第2の電極と第1の電源線Vi( $i = 1 \sim x$ )の間の電位差を埋めることで、発光素子101への電流の供給を止めるスイッチの構成の一例を、図3(A)に示す。ただし図3(A)では、第1の電極が陰極、第2の電極が陽極の場合を示す。図3(A)に示すように、スイッチ110を切り替えることで、書き込み期間においては第1の電源線Viと、発光素子101の第2の電極とに電位Vssを与える、保持期間においては発光素子101に順方向バイアスの電流が供給されるように、発光素子101の第2の電極に電位Vddを、第1の電源線Viに電位Vssを与えることができる。ただしVdd > Vssとする。なお第1の電極が陽極、第2の電極が陰極の場合は、書き込み期間において第1の電源線Viと、発光素子101の第2の電極とに電位Vddを与える、保持期間において発光素子101に順方向バイアスの電流が供給されるように、発光素子101の第2の電極に電位Vssを、第1の電源線Viに電位Vddを与えるようにする。

【0034】

また、図1に示した画素において、発光素子101に流れる電流の経路を遮断することで、発光素子101への電流の供給を止める場合のスイッチの構成を、図3(B)に示す。ただし図3(B)では、第1の電極が陰極、第2の電極が陽極の場合を示す。図3(B)

10

20

30

40

50

)に示すように、書き込み期間においてはスイッチ111をオフすることで、発光素子101に流れる電流の経路を遮断して第2の電極をフローティングにし、保持期間においてはスイッチ111をオンにすることで、発光素子101に流れる電流の経路を確保し、発光素子101に順方向バイアスの電流が供給されるようにすることができる。

【0035】

なおビデオ信号がデジタルの場合、発光素子が発光する時間を制御することで階調を表示しても良いし(時間階調方式)、または発光素子が発光する面積で階調を表示しても良い(面積階調方式)。例えば本実施の形態において時間階調方式を用いる場合、1フレーム期間に、ビデオ信号の各ビットに対応する書き込み期間と保持期間を設ける。そして、1フレーム期間内で、発光素子が発光した書き込み期間と保持期間のトータルの長さをビデオ信号で制御することで、階調を表示することができる。なお書き込み期間において、ビデオ信号の電位に関わらず発光素子を全て非発光の状態にする駆動方法の場合は、1フレーム期間内で、発光素子が発光した保持期間のトータルの長さをビデオ信号で制御することで、階調を表示することができる。

10

【0036】

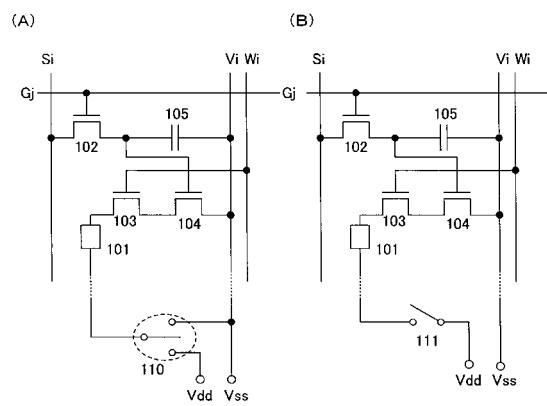

次に、本発明の発光装置の、より具体的な構成とその作製方法について、図4～図7を用いて説明する。

【0037】

まず図4(A)に示すように、TFT及び発光素子を形成する基板200を用意する。具体的に基板200は、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、SUS基板を含む金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。基板200の表面を、CMP法などの研磨により平坦化しておいても良い。

20

【0038】

上述した基板200の表面に、液滴吐出法、印刷法を用いて形成される導電膜または絶縁膜の、密着性を高めるための前処理を施す。密着性を高めることができる方法として、具体的には、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を基板200の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属、金属化合物を基板200の表面に付着させる方法、基板200の表面に大気圧下または減圧下においてプラズマ処理を施し、表面改質を行なう方法などが挙げられる。また、上記導電膜または絶縁膜との密着性が高い金属として、チタン、チタン酸化物の他、3d遷移元素であるSc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Znなどが挙げられる。また金属化合物として、上述した金属の酸化物、窒化物、酸窒化物などが挙げられる。上記有機系の絶縁膜として、例えばポリイミド、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む絶縁膜(以下、シロキサン系絶縁膜と呼ぶ)等が挙げられる。シロキサン系絶縁膜は、置換基に水素の他、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有していても良い。

30

【0039】

なお、基板200に付着させる金属または金属化合物が導電性を有する場合、半導体素子の正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば1～10nmとなるように制御したり、該金属または金属化合物を酸化により部分的に、または全体的に絶縁化したりすれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッチングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させるのではなく、液滴吐出法、印刷法、ゾル-ゲル法などを用いて特定の領域にのみ選択的に付着させても良い。なお金属または金属化合物は、基板200の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であっても良い。

40

50

## 【0040】

本実施の形態では、光触媒反応により密着性を高めることができるZnOまたはTiO<sub>2</sub>などの光触媒を基板200の表面に付着させる。具体的には、ZnOまたはTiO<sub>2</sub>を溶媒に分散させ、基板200の表面に撒布したり、Znの化合物またはTiの化合物を基板200の表面に付着させた後、酸化させたり、ゾル-ゲル法を用いたりすることで、結果的にZnOまたはTiO<sub>2</sub>を基板200の表面に付着させることができる。

## 【0041】

次に密着性を高めるための前処理が施された基板200の表面上に、液滴吐出法または各種印刷法を用いて、ゲート電極201～203を形成する。具体的に、ゲート電極201～203には、Ag、Au、Cu、Pdなどの金属、金属化合物を1つまたは複数有する導電材料を用いる。なお、分散剤により凝集を抑え、溶液に分散させることができるならば、Cr、Mo、Ti、Ta、W、Alなどの金属、金属化合物を1つまたは複数有する導電材料を用いることも可能である。また液滴吐出法または各種印刷法による導電材料の成膜を複数回行なうことで、複数の導電膜が積層されたゲート電極を形成することも可能である。また例えば、CuをAgでコートした導電粒子なども用いることが可能である。

10

## 【0042】

液滴吐出法を用いる場合、有機系または無機系の溶媒に該導電材料を分散させたものを、ノズルから滴下した後、室温において乾燥または焼成することで、形成することができる。具体的に本実施の形態では、テトラデカンにAgを分散させた溶液を滴下し、200～300で1min～50hr焼成することで溶媒を除去し、ゲート電極201～203を形成する。有機系の溶媒を用いる場合、上記焼成を酸素雰囲気下で行なうことで、効率的に溶媒を除去することができ、ゲート電極201～203の抵抗をより下げることができる。なお図示しないが、この工程でゲート電極201に接続した走査線も、同時に形成することができる。

20

## 【0043】

なお、液滴吐出法を用いた場合、パターンの精度は、液滴1ドットあたりの吐出量、該溶液の表面張力、液滴が滴下される基板200の表面の撥水性などに依存する。そのため、所望するパターンの精度に合わせて、これらの条件を最適化することが望ましい。

## 【0044】

30

ここで、液滴吐出法でAgを吐出する前に、酸化チタンを基板の表面に付着させた場合における、Agの密着性の評価について説明する。まずガラス基板上にスパッタ法を用いてチタンを1～5nmの膜厚で成膜した。そして230の焼成により成膜したチタンを酸化し、酸化チタンとした。このとき、酸化チタンで形成されている膜のシート抵抗を測定したところ、装置の測定可能の下限値 $1 \times 10^{-6}$ よりも低くなつたため、十分絶縁性が高いことが確認された。

## 【0045】

次に、液滴吐出法を用いてAgを16箇所のエリアに滴下した後、230で焼成した。なお焼成後、16箇所の各エリアに形成された、短冊形のAg膜の寸法は、長さ1cm、幅200～300μm、厚さ400～500nmとなった。

40

## 【0046】

上記Ag膜が形成された基板に、カプトン(R)テープを貼った後、該テープを剥がしてAg膜の密着性を確認したところ、テープを剥がした後もAg膜の剥離は見られなかつた。また上記Ag膜が形成された基板を、0.5wt%のHF水溶液に1分間浸した後、流水洗浄を行なうことで膜の密着性を確認したところ、全てのAg膜が剥がれず基板上に残存していた。なお、チタン酸化膜を溶媒に分散させた溶液を、基板の表面に撒布することで、酸化チタンを基板の表面に付着させた場合も、同様の結果が得られた。ちなみに、素のガラス基板、表面をCMP研磨したガラス基板、非晶質珪素膜、窒化珪素膜または酸化珪素膜を形成したガラス基板を用いた場合には、若干の違いはあるものの、いずれも數本程度しかAg膜は残存しなかつた。従つて、酸化チタンにより高い密着性が得られてい

50

ると考えられる。

【0047】

次に、ゲート電極201～203を覆うようにゲート絶縁膜205を形成する。ゲート絶縁膜205は、例えば酸化珪素、窒化珪素または窒化酸化珪素等の絶縁膜を用いることができる。ゲート絶縁膜205は、単層の絶縁膜を用いても良いし、複数の絶縁膜を積層していても良い。本実施の形態では、窒化珪素、酸化珪素、窒化珪素が順に積層された絶縁膜を、ゲート絶縁膜205として用いる。また成膜方法は、プラズマCVD法、スパッタ法などを用いることができる。低い成膜温度でゲートリーク電流を抑えることができる緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。また窒化アルミニウムをゲート絶縁膜205として用いることができる。窒化アルミニウムは熱伝導率が比較的高く、TFTで発生した熱を効率的に発散させることができる。10

【0048】

次に図4(B)に示すように、発光素子が有する第1の電極206をゲート絶縁膜205上に形成する。なお本実施の形態では、第1の電極206が陰極、後に形成される第2の電極236が陽極に相当するが、本発明はこの構成に限定されない。第1の電極206が陽極、第2の電極236が陰極に相当していても良い。

【0049】

陰極は、仕事関数の小さい金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることができる。具体的には、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、これらを含む合金(Mg:Ag、Al:Li、Mg:Inなど)、およびこれらの化合物(CaF<sub>2</sub>、CaN)の他、YbやEr等の希土類金属を用いることができる。また電子注入層を設ける場合、Alなどの他の導電層を用いることも可能である。また陰極側から光を取り出す場合は、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)などその他の透光性酸化物導電材料を用いることが可能である。ITO及び酸化珪素を含む酸化インジウムスズ(以下、ITSOとする)や、酸化珪素を含んだ酸化インジウムに、さらに2～20%の酸化亜鉛(ZnO)を混合したものを用いても良い。透光性酸化物導電材料を用いる場合、後に形成される電界発光層235に電子注入層を設けるのが望ましい。また透光性酸化物導電材料を用いざとも、陰極を光が透過する程度の膜厚(好ましくは、5nm～30nm程度)で形成することで、陰極側から光を取り出すことができる。この場合、該陰極の上または下に接するように透光性酸化物導電材料を用いて透光性を有する導電層を形成し、陰極のシート抵抗を抑えるようにしても良い。20

【0050】

本実施の形態では、陽極に相当する第1の電極206として、Mg:Agを用いる。なお第1の電極206は、スパッタ法、液滴吐出法または印刷法を用いて形成することができる。液滴吐出法または印刷法を用いる場合、マスクを用いなくても第1の電極206を形成することができる。またスパッタ法を用いる場合でも、リソグラフィ法において用いるレジストを、液滴吐出法または印刷法で形成することで、露光用のマスクを別途用意しておく必要がなくなり、よってコストの削減に繋がる。30

【0051】

なお第1の電極206は、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体で拭净し、研磨しても良い。またCMP法を用いた研磨後に、陰極の表面に紫外線照射、酸素プラズマ処理などを行ってもよい。

【0052】

次に図4(C)に示すように、第1の半導体膜207を形成する。第1の半導体膜207は非晶質(アモルファス)半導体またはセミアモルファス半導体(SAS)で形成することができる。また多結晶半導体膜を用いていても良い。本実施の形態では、第1の半導体膜207としてセミアモルファス半導体を用いる。セミアモルファス半導体は、非晶質半導体よりも結晶性が高く高い移動度が得られ、また多結晶半導体と異なり結晶化させる40

ための工程を増やすことも形成することができる。

【0053】

非晶質半導体は、珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ が挙げられる。この珪化物気体を、水素、水素とヘリウムで希釈して用いても良い。

【0054】

またSASも珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、 $\text{SiH}_4$ であり、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪化物気体を希釈して用いることで、SASの形成を容易なものとすることができます。希釈率は2倍～1000倍の範囲で珪化物気体を希釈することが好ましい。またさらに、珪化物気体中に、 $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$ などの炭化物気体、 $\text{GeH}_4$ 、 $\text{GeF}_4$ などのゲルマニウム化気体、 $\text{F}_2$ などを混入させて、エネルギー bandwidth幅を1.5～2.4 eV、若しくは0.9～1.1 eVに調節しても良い。SASを第1の半導体膜として用いたTFTは、 $1 \sim 10 \text{ cm}^2/\text{Vsec}$ や、それ以上の移動度を得ることができる。

10

【0055】

また異なるガスで形成されたSASを複数積層することで、第1の半導体膜を形成しても良い。例えば、上述した各種ガスのうち、弗素原子を含むガスを用いて形成されたSASと、水素原子を含むガスを用いて形成されたSASとを積層して、第1の半導体膜を形成することができる。

20

【0056】

グロー放電分解による被膜の反応生成は減圧下または大気圧下で行なうことができる。減圧下で行なう場合、圧力は概略 $0.1 \text{ Pa} \sim 133 \text{ Pa}$ の範囲で行なえば良い。グロー放電を形成するための電力は $1 \text{ MHz} \sim 120 \text{ MHz}$ 、好ましくは $13 \text{ MHz} \sim 60 \text{ MHz}$ の高周波電力を供給すれば良い。圧力は概略 $0.1 \text{ Pa} \sim 133 \text{ Pa}$ の範囲、電源周波数は $1 \text{ MHz} \sim 120 \text{ MHz}$ 、好ましくは $13 \text{ MHz} \sim 60 \text{ MHz}$ とする。基板加熱温度は300以下でよく、好ましくは $100 \sim 250$ とする。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は $1 \times 10^{20} \text{ atoms/cm}^3$ 以下とすることが望ましく、特に、酸素濃度は $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下とする。

30

【0057】

なお、 $\text{Si}_2\text{H}_6$ と、 $\text{GeF}_4$ または $\text{F}_2$ とを用いて半導体膜を形成する場合、半導体膜のより基板に近い側から結晶が成長するので、基板に近い側ほど半導体膜の結晶性が高い。よって、ゲート電極が第1の半導体膜よりも基板により近いボトムゲート型のTFTの場合、第1の半導体膜のうち基板に近い側の結晶性が高い領域をチャネル形成領域として用いることができるので、移動度をより高めることができ、適している。

【0058】

また、 $\text{SiH}_4$ と、 $\text{H}_2$ とを用いて半導体膜を形成する場合、半導体膜の表面により近い側ほど大きい結晶粒が得られる。よって、第1の半導体膜がゲート電極よりも基板により近いトップゲート型のTFTの場合、第1の半導体膜のうち基板から遠い側の結晶性が高い領域をチャネル形成領域として用いることができるので、移動度をより高めることができ、適している。

40

【0059】

また、SASは、価電子制御を目的とした不純物を意図的に添加しないときには弱いn型の導電型を示す。これは、アモルファス半導体を成膜するときよりも高い電力のグロー放電を行なうため酸素が半導体膜中に混入しやすいためである。そこで、TFTのチャネル形成領域を設ける第1の半導体膜に対しては、p型を付与する不純物を、この成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物としては、代表的には硼素であり、 $\text{B}_2\text{H}_6$ 、 $\text{BF}_3$ などの不純物気体を $1 \text{ ppb}$

50

$m \sim 1000 \text{ ppm}$  の割合で珪化物気体に混入させると良い。例えば、 $p$  型を付与する不純物としてボロンを用いる場合、該ボロンの濃度を  $1 \times 10^{14} \sim 6 \times 10^{16} \text{ atoms/cm}^3$  とすると良い。

【0060】

次に、第1の半導体膜207のうち、チャネル形成領域となる部分と重なるように、第1の半導体膜207上に保護膜208～210を形成する。保護膜208～210は液滴吐出法または印刷法を用いて形成しても良いし、CVD法、スパッタ法などを用いて形成しても良い。保護膜208～210といて、酸化珪素、窒化珪素、窒化酸化珪素などの無機絶縁膜、シロキサン系絶縁膜などを用いることができる。またこれらの膜を積層し、保護膜208～210として用いても良い。本実施の形態では、プラズマCVD法で形成された窒化珪素、液滴吐出法で形成されたシロキサン系絶縁膜を積層して、保護膜208～210として用いる。この場合、窒化珪素のパターニングは、液滴吐出法で形成されたシロキサン系絶縁膜をマスクとして用い行なうことができる。

10

【0061】

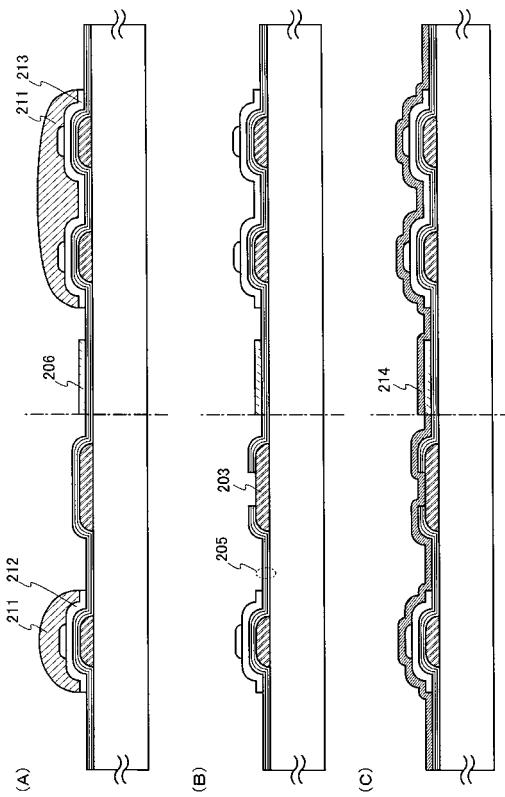

次に図5(A)に示すように、第1の半導体膜207のパターニングを行なう。第1の半導体膜207のパターニングは、リソグラフィ法を用いても良いし、液滴吐出法または印刷法で形成されたレジストをマスクとして用いても良い。後者の場合、露光用のマスクを別途用意しておく必要がなくなり、よってコストの削減に繋がる。本実施の形態では、液滴吐出法で形成されたレジスト211を用い、パターニングする例を示す。なおレジスト211は、ポリイミド、アクリルなどの有機樹脂を用いることができる。そして、レジスト211を用いたドライエッティングにより、パターニングされた第1の半導体膜212、213が形成される。

20

【0062】

次に図5(B)に示すように、ゲート絶縁膜205の一部をエッティングにより選択的に除去し、ゲート電極203の一部を露出させる。ゲート絶縁膜205のエッティングには、リソグラフィ法を用いても良いし、液滴吐出法または印刷法で形成されたレジストをマスクとして用いても良い。後者の場合、露光用のマスクを別途用意しておく必要がなくなり、よってコストの削減に繋がる。

【0063】

次に図5(C)に示すように、パターニング後の第1の半導体膜212、213を覆うように、第2の半導体膜214を形成する。第2の半導体膜214には、一導電型を付与する不純物を添加しておく。nチャネル型のTFTを形成する場合には、第2の半導体膜214に、n型を付与する不純物、例えばリンを添加すれば良い。具体的には、珪化物気体にPH<sub>3</sub>などの不純物気体を加え、第2の半導体膜214を形成すれば良い。一導電型を有する第2の半導体膜214は、第1の半導体膜212、213と同様にセミアモルファス半導体、非晶質半導体で形成することができる。

30

【0064】

なお本実施の形態では、第2の半導体膜214を第1の半導体膜212、213と接するように形成しているが、本発明はこの構成に限定されない。第1の半導体膜212、213と第2の半導体膜214の間に、LDD領域として機能する第3の半導体膜を形成しておいても良い。この場合、第3の半導体膜は、セミアモルファス半導体または非晶質半導体で形成する。そして、第3の半導体膜は、導電型を付与するための不純物を意図的に添加しなくとも、もともと弱いn型の導電型を示す。よって第3の半導体膜には、導電型を付与するための不純物を添加してもしなくても、LDD領域として用いることができる。

40

【0065】

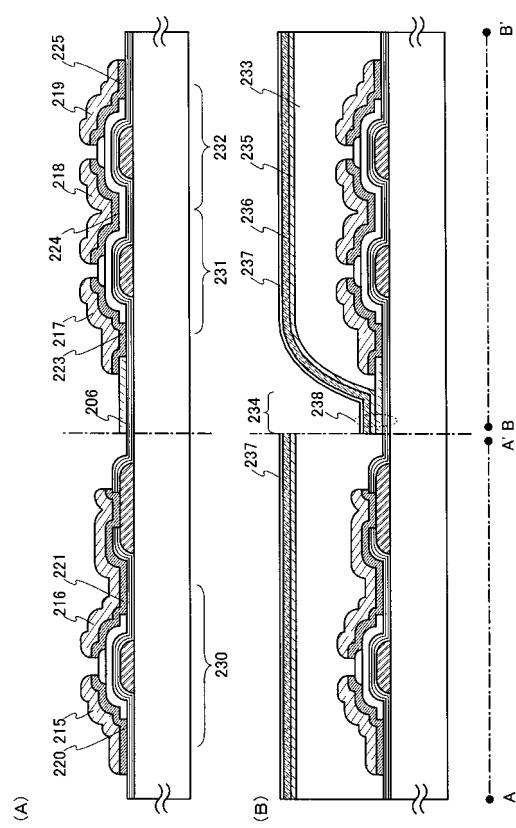

次に図6(A)に示すように、配線215～219を液滴吐出法または印刷法を用いて形成し、該配線215～219をマスクとして用い、第2の半導体膜214をエッティングする。第2の半導体膜214のエッティングは、真空雰囲気下もしくは大気圧雰囲気下におけるドライエッティングで行なうことができる。上記エッティングにより、第2の半導体膜2

50

14からソース領域またはドレイン領域として機能する、第2の半導体220～225が形成され、さらに第1の電極206の一部が露出される。第2の半導体膜214をエッティングする際、保護膜208～210によって、第1の半導体膜212、213がオーバーエッティングされるのを防ぐことができる。

【0066】

配線215～219は、ゲート電極201～203と同様に形成することができる。具体的には、Ag、Au、Cu、Pdなどの金属、金属化合物を1つまたは複数有する導電材料を用いる。液滴吐出法を用いる場合、有機系または無機系の溶媒に該導電材料を分散させたものを、ノズルから滴下した後、室温において乾燥または焼成することで、形成することができる。分散剤により凝集を抑え、溶液に分散させることができるとすれば、Cr、Mo、Ti、Ta、W、Alなどの金属、金属化合物を1つまたは複数有する導電材料を用いることも可能である。焼成は酸素雰囲気下で行ない、配線215～219の抵抗を下げるようにしておきたい。また液滴吐出法または各種印刷法による導電材料の成膜を複数回行なうことで、複数の導電膜が積層された配線215～219を形成することも可能である。

【0067】

上記工程によって、スイッチング用TFT230、駆動用TFT231、電流制御用TFT232が形成される。

【0068】

次に図6(B)に示すように、スイッチング用TFT230と、駆動用TFT231と、電流制御用TFT232と、第1の電極206の端部とを覆うように、隔壁233を形成する。隔壁233は、有機樹脂膜、無機絶縁膜またはシロキサン系絶縁膜を用いて形成することができる。有機樹脂膜ならば、例えばアクリル、ポリイミド、ポリアミドなど、無機絶縁膜ならば酸化珪素、窒化酸化珪素などを用いることができる。特に感光性の有機樹脂膜を隔壁233に用い、第1の電極206上に開口部234を形成し、その開口部234の側壁が連続した曲率を持って形成される傾斜面となるように形成することで、第1の電極206と後に形成される第2の電極236とが接続してしまうのを防ぐことができる。このとき、マスクを液滴吐出法または印刷法で形成することができる。また隔壁233自体を、液滴吐出法または印刷法で形成することもできる。なお隔壁233は開口部234を有している。

【0069】

次に電界発光層235を形成する前に、隔壁233及び第1の電極206に吸着した水分や酸素等を除去するために、大気雰囲気下で加熱処理または真空雰囲気下で加熱処理(真空ベーク)を行なっておきたい。具体的には、基板の温度を200～450、好ましくは250～300で、0.5～20時間程度、真空雰囲気下で加熱処理を行なう。望ましくは $3 \times 10^{-7}$  Torr以下とし、可能であるならば $3 \times 10^{-8}$  Torr以下とするのが最も望ましい。そして、真空雰囲気下で加熱処理を行なった後に電界発光層を成膜する場合、電界発光層を成膜する直前まで当該基板を真空雰囲気下に置いておくことで、信頼性をより高めることができる。また真空ベークの前または後に、第1の電極206に紫外線を照射してもよい。

【0070】

なお、本実施の形態では、後に形成されるパッシベーション膜237を窒化珪素で形成しており、該パッシベーション膜237と、ITOで形成された第2の電極206とが接している。このように、窒化珪素または窒化酸化珪素を含む絶縁膜上に接するように、ITOなどの透光性酸化物導電材料と酸化珪素を含む導電膜を用い、発光素子の第1の電極または第2の電極を形成することで、上述したどの材料の組み合わせよりも、発光素子の輝度を高めることができる。なお、第1の電極206にITOを用いた場合、含まれる酸化珪素によって水分が付着しやすいので、上述した真空ベークは特に有効である。

【0071】

そして、隔壁233の開口部234において第1の電極206と接するように、電界発

10

20

30

40

50

光層 235 を形成する。電界発光層 235 は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、陰極に相当する第 1 の電極 206 上に、電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なお第 1 の電極 206 が陽極に相当する場合は、電界発光層 235 を、ホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層して形成する。

#### 【0072】

なおモノクロの画像を表示する場合、もしくは白色の発光素子とカラーフィルターを用いてカラーの画像を表示する場合、電界発光層 235 の構造は全ての画素において同じである。三原色の光をそれぞれ発する 3 つの発光素子を用いてカラーの画像を表示する場合、電界発光層 235 は、対応する色ごとに材料、積層する層または膜厚を変えて塗り分けても良い。電界発光層を塗り分ける場合、液滴吐出法は材料の無駄がなく、工程も簡素化できるので、非常に有効である。なおカラーは、混色を用いたフルカラーであっても良いし、単一の色相を有する複数の画素を特定のエリアごとに配したエリアカラーであっても良い。

10

#### 【0073】

なおカラーフィルターは、特定の波長領域の光を透過させることができる着色層と、場合によっては該着色層に加え、可視光を遮蔽することができる遮蔽膜とを有する場合がある。そしてカラーフィルターは、発光素子を封止するためのカバー材上に形成する場合もあれば、素子基板に形成する場合もありうる。いずれの場合においても、着色層または遮蔽膜は、印刷法または液滴吐出法を用いて形成することが可能である。

20

#### 【0074】

また電界発光層 235 は、高分子系有機化合物、中分子系有機化合物、低分子系有機化合物、無機化合物のいずれを用いていても、液滴吐出法で形成することが可能である。また中分子系有機化合物、低分子系有機化合物、無機化合物は蒸着法で形成しても良い。

#### 【0075】

そして電界発光層 235 を覆うように、第 2 の電極 236 を形成する。本実施の形態では、第 2 の電極 236 は陽極に相当する。第 2 の電極 236 の作製方法は、蒸着法、スパッタ法、液滴吐出法などを材料に合わせて使い分けることが好ましい。

#### 【0076】

30

陽極には、酸化インジウムスズ (ITO)、酸化亜鉛 (ZnO)、酸化インジウム亜鉛 (IZO)、ガリウムを添加した酸化亜鉛 (GZO) などその他の透光性酸化物導電材料を用いることが可能である。ITO 及び酸化珪素を含む酸化インジウムスズ (以下、ITSO とする) や、酸化珪素を含んだ酸化インジウムに、さらに 2 ~ 20 % の酸化亜鉛 (ZnO) を混合したものを用いても良い。また陽極として上記透光性酸化物導電材料の他に、例えば TiN、ZrN、Ti、W、Ni、Pt、Cr、Ag、Al 等の 1 つまたは複数からなる単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との三層構造等を用いることができる。ただし透光性酸化物導電材料以外の材料で陽極側から光を取り出す場合、光が透過する程度の膜厚 (好ましくは、5 nm ~ 30 nm 程度) で形成する。

40

#### 【0077】

隔壁 233 の開口部 234 において、第 1 の電極 206 と電界発光層 235 と第 2 の電極 236 が重なり合うことで、発光素子 238 が形成されている。

#### 【0078】

なお、発光素子 238 からの光の取り出しが、第 1 の電極 206 側からであっても良いし、第 2 の電極 236 側からであっても良いし、その両方からであっても良い。上記 3 つの構成にうち、目的とする構成に合わせて、陽極、陰極それぞれの材料及び膜厚を選択するようにする。本実施の形態のように第 2 の電極 236 側から光の取り出す場合、第 1 の電極 206 側から光の取り出す場合に比べて、より低い消費電力でより高い輝度を得ることができる。

50

## 【0079】

なお発光素子 238 を覆うようにパッシベーション膜 237 を形成しても良い。パッシベーション膜 237 は、水分や酸素などの発光素子の劣化を促進させる原因となる物質を、他の絶縁膜と比較して透過させにくい膜を用いる。代表的には、例えば DLC 膜、窒化炭素膜、RFスパッタ法、CVD 法などで形成された窒化珪素膜等を用いるのが望ましい。また、例えば窒化炭素膜と窒化珪素を積層した膜、ポリスチレンを積層した膜など、をパッシベーション膜 237 として用いても良い。また上述した水分や酸素などの物質を透過させにくい膜と、該膜に比べて水分や酸素などの物質を透過させやすいが内部応力の低い膜とを積層させて、パッシベーション膜 237 として用いることも可能である。本実施の形態では窒化珪素を用いる。パッシベーション膜 237 として窒化珪素を用いる場合、低い成膜温度で緻密なパッシベーション膜 237 を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、パッシベーション膜 237 中に混入させると良い。

10

## 【0080】

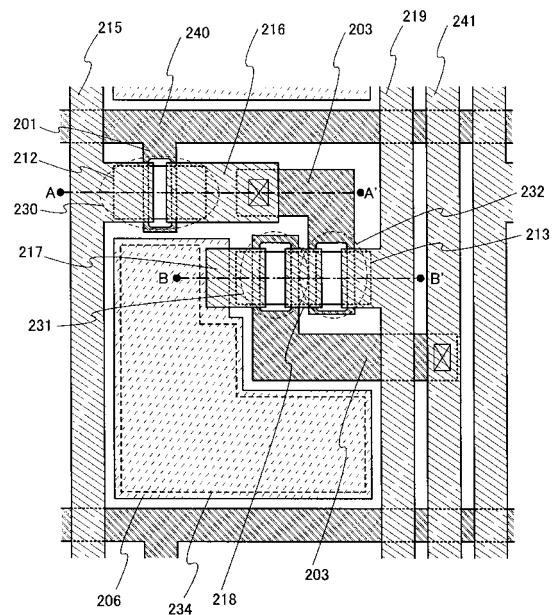

図 7 に、図 6 (B) に示す発光装置の上面図を示す。図 7 は、図 6 (B) の A - A' における断面図に相当する。なお図 7 では構造をより分かりやすくするため、電界発光層 235、第 2 の電極 236、パッシベーション膜 237 は省略して図示する。配線 215 は信号線として機能する。配線 216 は、ゲート電極 203 と接続している。またゲート電極 201 は、走査線 240 と電気的に接続されている。また配線 219 は第 1 の電源線として機能する。第 2 の電源線 241 は、配線 215 ~ 219 と同じ導電膜から形成されており、ゲート電極 203 と接続されている。開口部 234 において第 1 の電極 206 が一部露出している。

20

## 【0081】

なお実際には、図 6 (B) に示す状態まで完成したら、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（ラミネートフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好ましい。

## 【0082】

なお本実施の形態では、画素部を形成する工程について説明したが、セミアモルファス半導体を第 1 の半導体膜として用いる場合、走査線駆動回路を画素部と同じ基板上に形成することが可能である。またアモルファス半導体を用いた TFT で画素部を形成し、該画素部が形成された基板に別途形成された駆動回路を貼り付けても良い。

30

## 【0083】

なお図 4 ~ 図 7 では、ゲート電極 203 の一部を露出させるためのゲート絶縁膜 205 のエッチングに、リソグラフィ法を用いたり、液滴吐出法または印刷法で形成されたレジストをマスクとして用いたりしているが、本発明はこの構成に限定されない。例えば、第 2 の半導体膜に接する配線をマスクとして用いてゲート絶縁膜 205 をエッチングし、ゲート電極 203 の一部を露出させても良い。この場合ゲート絶縁膜のエッチングを行なった後、液滴吐出法を用いて、ゲート電極 203 の露出した部分と、マスクとして用いた配線とを接続するような導電膜を形成しても良い。また例えば、ゲート絶縁膜 205 を形成する前に、ゲート電極 203 の一部と重なるようにピラーを形成しておいても良い。ピラーは、ピラーを形成したい領域に、導電材料を含む溶液を、液滴が重なるように複数回滴下することで形成できる。そしてゲート絶縁膜 205 は、ピラーと重なる部分において膜厚が著しく薄くなるため、該ゲート絶縁膜 205 上に形成された配線とピラーとを電気的に接続することができる。

40

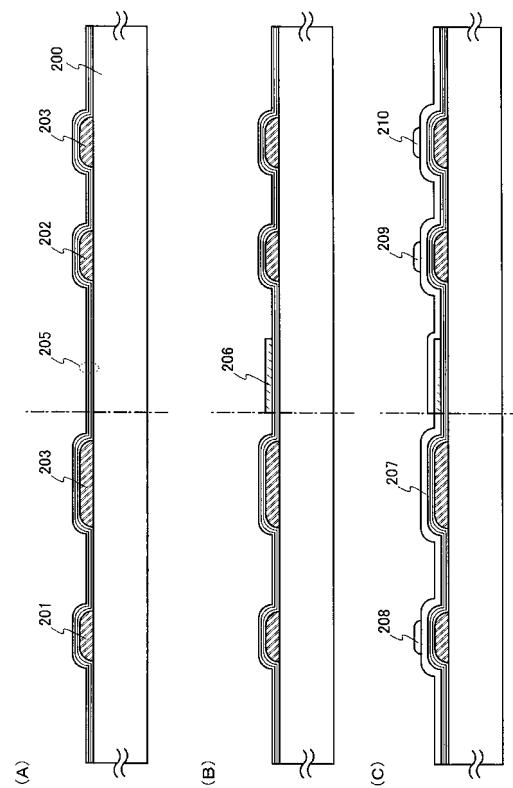

## 【0084】

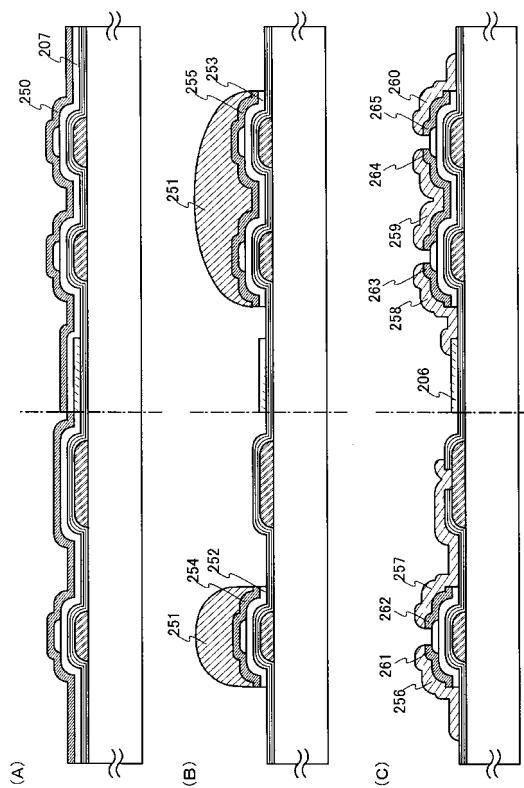

また図 4 ~ 図 7 では、第 1 の半導体膜と第 2 の半導体膜を別々の工程でパターニングしているが、本発明の発光装置はこの作製方法に限定されない。次に図 8 を用いて、第 1 の半導体膜と第 2 の半導体膜を同一のマスクを用いてパターニングする例について説明する。

## 【0085】

まず上述した作製方法に従って、図 4 (C) に示す状態まで同様に作製する。次に図 8

50

(A) に示すように、第1の半導体膜207をパターニングする前に、第2の半導体膜250を成膜する。LDD領域として用いる第3の半導体膜を形成する場合は、第1の半導体膜207を形成した後、第3の半導体膜を形成し、それから第2の半導体膜250を形成する。次に図8(B)に示すように、液滴吐出法または印刷法で形成したレジスト251をマスクとして用い、第1の半導体膜207及び第2の半導体膜250をパターニングする。図8(B)において、252、253はパターニング後の第1の半導体膜、254、255はパターニング後の第2の半導体膜に相当する。

【0086】

次に図8(C)に示すように、液滴吐出法または印刷法で配線256～260を形成する。そして配線256～260をマスクとして用い、第2の半導体膜254、255を更にパターニングすることで、ソース領域またはドレイン領域として機能する第2の半導体膜261～265が形成される。そして後は、図4～図7に示した作製方法と同様に、隔壁、電界発光層、第2の電極を形成することができる。

【0087】

図8に示した作製方法を用いる場合、第1の電極206と配線258とが直接接するので、該接続部分における接触抵抗を低くすることができる。

【0088】

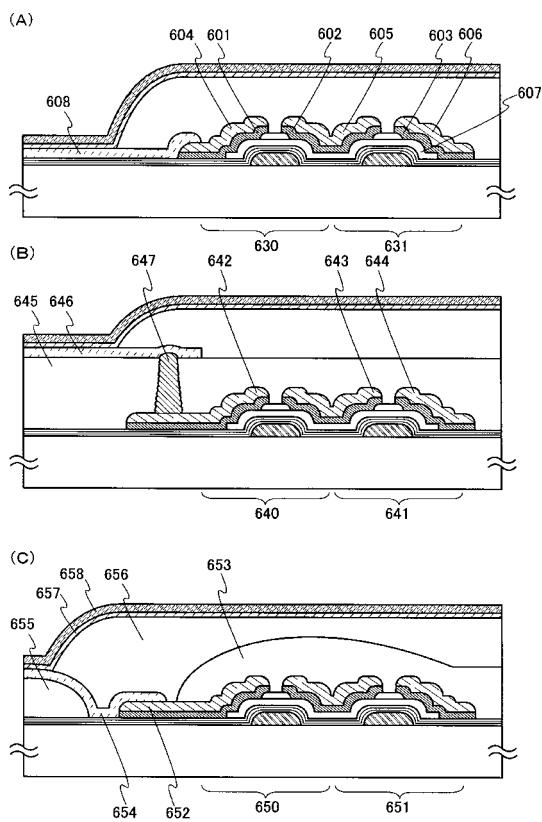

また図4～図7に示した作製方法及び図8に示した作製方法では、第2の半導体膜と、該第2の半導体膜に接している配線とを形成する前に、第1の電極を形成している例を示しているが、本発明はこの構成に限定されない。図9(A)に、図4～図7に示した作製方法において、第2の半導体膜と、該第2の半導体膜に接している配線とを形成した後に、第1の電極を形成した、画素の断面図を示す。ただし図9(A)では、駆動用TFT630、電流制御用TFT631を示す。

【0089】

図9(A)において、601～603は、ソース領域またはドレイン領域として機能する第2の半導体膜に相当し、第2の半導体膜601上に接するように配線604が、第2の半導体膜602上に接するように配線605が、第2の半導体膜603上に接するように配線606が形成されている。なお図9(A)では、第1の半導体膜607と第2の半導体膜601～603とを、図4～図7に示した場合のように、異なるマスクを用いたパターニングにより形成しているが、本発明はこの構成に限定されず、図8の場合のように同じマスクを用いてパターニングしていても良い。そして図9(A)では、配線604上に接するように、第1の電極608が形成されている。図9(A)に示すように、第2の半導体膜601～603と、該第2の半導体膜601～603に接している配線604～606を形成した後に、第1の電極608を形成することで、第2の半導体膜601～603のパターニングの際にドライエッチングを用いても、第1の電極608の表面が荒れるのを防ぐことができる。

【0090】

また図4～図7、図8、図9(A)では、第1の電極をゲート絶縁膜上に形成しているが本発明はこの構成に限定されない。図9(B)に、TFTを覆って層間絶縁膜を形成し、該層間絶縁膜上に第1の電極を形成した場合の、画素の断面図を示す。ただし図9(B)では、駆動用TFT640、電流制御用TFT641を示す。図9(B)では、駆動用TFT640と、電流制御用TFT641と、駆動用TFT640、電流制御用TFT641のソース領域またはドレイン領域と接続された配線642～644とが、層間絶縁膜645によって覆われており、該層間絶縁膜645上に第1の電極646が形成されている。層間絶縁膜645は、有機樹脂膜、無機絶縁膜またはシリコン系絶縁膜を用いて形成することができる。層間絶縁膜645に、低誘電率材料(low-k材料)と呼ばれる材料を用いていても良い。そして第1の電極646と配線611とは、層間絶縁膜645のコントクトホール内に形成されたピラー647を通して電気的に接続されている。

【0091】

図9(B)では、該ピラー647は層間絶縁膜645を形成する前に液滴吐出法を用い

10

20

30

40

50

て形成されている。具体的には、導電材料を含む溶液を同じポイントに滴下し、液滴を重ねることでピラー 647 を形成する。ピラー 647 に用いる導電材料として、ITO、ITO に代表される透光性酸化物導電材料を用いることができる。そして、ピラー 647 を形成した後に層間絶縁膜 645 をスピンドルコート法などの塗布法で形成し、次に層間絶縁膜 645 の表面をエッチングすることでピラー 647 を露出させる。そして該ピラー 647 と接するように、層間絶縁膜 645 上に第 1 の電極 646 を形成する。なお層間絶縁膜 645 の表面は第 1 の電極 646 の表面に凹凸が形成されないように、平坦化されていることが望ましい。よって液滴吐出法を用いて層間絶縁膜 645 を形成する場合、液滴を吐出した後に気体を吹き付けてその表面を平坦化した後、焼成するように形成しても良い。

## 【0092】

10

なお図 9 (B) では、層間絶縁膜 645 を形成する前にピラー 647 を形成しているが、層間絶縁膜 645 を形成した後にピラー 647 を形成しても良い。この場合、層間絶縁膜 645 にコンタクトホールを形成し、液滴吐出法を用いて該コンタクトホールに導電材料を含む溶液を滴下することで、ピラー 647 を形成する。コンタクトホールの形成は、ドライエッチングを用いても、ウェットエッチングを用いてもどちらでも良い。また、層間絶縁膜を形成する前に、コンタクトホールを形成する領域に撥液性を有する有機材料を液滴吐出法または印刷法などを用いて塗布しておいても良い。この場合、層間絶縁膜を形成した後、撥液性を有する有機材料を除去することで、エッチングを行なわずともコンタクトホールを形成することができる。撥液性を有する有機材料として、ポリビニルアルコール (PVA)、フルオロアルキルシラン (FAS)などを用いることができる。また撥液性を有する有機材料の除去は、水による洗浄、CF<sub>4</sub>、O<sub>2</sub>などを用いたドライエッチングで行なうことができる。

## 【0093】

20

また層間絶縁膜は、液滴吐出法を用いて形成しても良い。図 9 (C) に、液滴吐出法を用いて層間絶縁膜を形成した場合の、画素の断面図を示す。ただし図 9 (C) では、駆動用 TFT 650、電流制御用 TFT 651 を示す。図 9 (C) では、駆動用 TFT 650、電流制御用 TFT 651 が第 1 の層間絶縁膜 653 に覆われており、第 1 の層間絶縁膜 653 は液滴吐出法を用いて形成されている。駆動用 TFT 650 のソース領域またはドレン領域のいずれか一方に接続された配線 652 は、第 1 の層間絶縁膜 653 と完全に重なってはおらず、一部露出している。また第 1 の層間絶縁膜 655 は、第 1 の層間絶縁膜 653 と同様に液滴吐出法を用いて形成されており、該第 1 の層間絶縁膜 653 を覆うように第 1 の電極 654 が形成されている。そして配線 652 の一部露出している部分は第 1 の電極 654 と接しており、該接している部分を覆うように更に第 2 の層間絶縁膜 656 が形成されている。

30

## 【0094】

第 2 の層間絶縁膜 656 は、第 1 の層間絶縁膜 655 と重なる領域に開口部を有しており、該開口部において、第 1 の電極 654 と、第 2 の層間絶縁膜 656 上に形成された電界発光層 657 と、第 2 の電極 658 とが重なり、発光素子を形成している。

## 【0095】

40

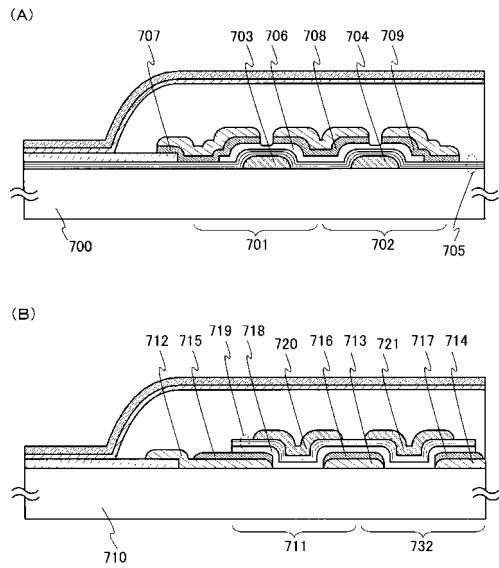

また図 4 乃至図 9 に示す発光装置では、TFT の第 1 の半導体膜と第 2 の半導体膜の間に保護膜を形成しているが、本発明はこの構成に限定されず、図 4 乃至図 9 の場合において、保護膜は必ずしも形成しなくて良い。図 10 (A) に、保護膜を形成していない場合の、画素の断面図を示す。ただし図 10 (A) では、駆動用 TFT 701、電流制御用 TFT 702 を示す。図 10 (A) に示す駆動用 TFT 701、電流制御用 TFT 702 は、基板 700 上に形成されたゲート電極 703、704 と、該ゲート電極 703、704 を覆うように形成されたゲート絶縁膜 705 と、該ゲート電極 703、704 と重なるようにゲート絶縁膜 705 上に形成された第 1 の半導体膜 706 と、第 1 の半導体膜 706 と接する第 2 の半導体膜 707 ~ 709 とを有している。エッチングにより第 2 の半導体膜 707 ~ 709 を形成する際、SF<sub>6</sub>、NF<sub>3</sub>、CF<sub>4</sub>などのフッ化物気体を用いてエッチングガスとして用いる。そしてこのエッチングでは、第 1 の半導体膜 706 とのエッチ

50

ングの選択比がとれないので、処理時間を適宜調整して行なうこととなる。このエッチングにより、第1の半導体膜706が一部露出する。

【0096】

図10(A)のように保護膜を形成せず、第1の半導体膜706と第2の半導体膜707～709を、同じマスクを用いてパターニングする場合、ゲート絶縁膜705と、第1の半導体膜706と、第2の半導体膜707～709とを、大気に触れさせることなく連続して形成することが可能である。すなわち、大気成分や大気中に浮遊する汚染物質に汚染されることなく各積層界面を形成することができるので、TFT特性のばらつきを低減することができる。

【0097】

また図4乃至図9、図10(A)では、ゲート電極が第1の半導体膜よりも基板側に形成されているが、本発明はこの構成に限定されない。図10(B)に、第1の半導体膜がゲート電極よりも基板側に形成されている場合の、画素の断面図を示す。ただし図10(B)では、駆動用TFT711、電流制御用TFT732を示す。図10(B)において、基板710上に配線712～714が形成されており、また配線712～714上に接するように、第2の半導体膜715～717が形成されており、第2の半導体膜715～717上に接するように第1の半導体膜718が形成されている。そして第1の半導体膜718上にはゲート絶縁膜719が形成されており、第1の半導体膜718と重なるように該ゲート絶縁膜719上にゲート電極720、721が形成されている。

【0098】

なお、上記図4～図7、図8、図6、図10に示したTFTは、いずれもソース領域またはドレイン領域として機能する第2の半導体膜を用いているが、第2の半導体膜は必ずしも形成する必要はない。この場合、配線が直接第1の半導体膜と接続され、該配線がソース領域またはドレイン領域として機能する。特に図10(B)に示したTFTは、第2の半導体膜を用いない場合、第2の半導体膜715～717を形成するためのパターニングに用いるマスクが不要になるので、大幅に工程数を削減することができる。

【0099】

また、上記図4～図7、図8、図6、図10に示した発光装置では、駆動用TFTと電流制御用トランジスタとで1つの第1の半導体膜を共有している例を示しているが、本発明はこの構成に限定されない。駆動用TFTと電流制御用トランジスタとが、それぞれ独立した第1の半導体膜を用いていても良い。

【0100】

なお上記図4～図7、図8、図6、図10に示した発光装置において、駆動用TFT、電流制御用TFT、スイッチング用TFTはマルチゲート構造を有していても良い。マルチゲート構造とは、直列に接続され、なおかつゲート電極が接続された複数のTFTが、第1の半導体膜を共有しているような構成を意味する。マルチゲート構造とすることで、TFTのオフ電流を低減させることができる。

【実施例1】

【0101】

本実施例では、本発明の発光装置において、画素に形成されるTFTの構成について説明する。

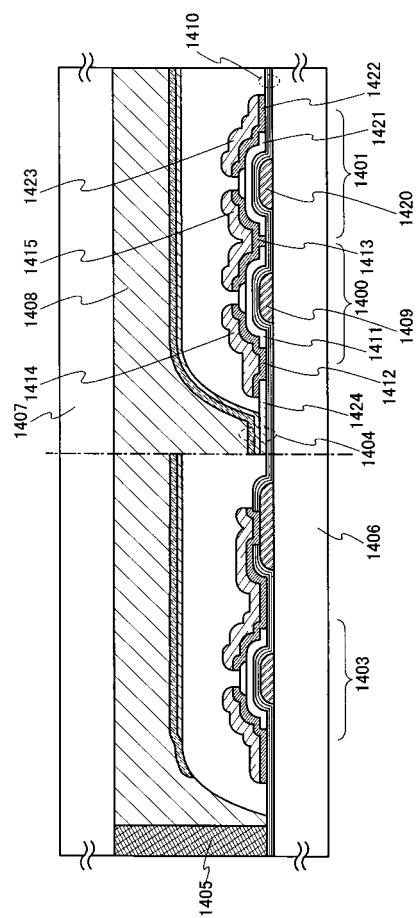

【0102】

図11に、本実施例の画素の断面図を示す。図11において、1400は駆動用TFT、1401は電流制御用TFTに相当し、1402はスイッチング用TFTに相当し、1403は発光素子に相当する。駆動用TFT1400、電流制御用TFT1401、スイッチング用TFT1402、発光素子1404は、シール材1405によって、基板1406とカバー材1407の間ににおいて、充填材1408と共に密封されている。

【0103】

駆動用TFT1400は、ゲート電極1409と、ゲート電極1409上に形成されたゲート絶縁膜1410と、ゲート絶縁膜1410上に形成された第1の半導体膜1411

10

20

30

40

50

と、第1の半導体膜1411上に形成された第2の半導体膜1412、1413とを有している。電流制御用TFT1401は、ゲート電極1420と、ゲート電極1420上に形成されたゲート絶縁膜1410と、ゲート絶縁膜1410上に形成された第1の半導体膜1421と、第1の半導体膜1421上に形成された第2の半導体膜1413、1422とを有している。また1414、1415、1423は、第2の半導体膜1412、1413、1422にそれぞれ接続された配線に相当する。配線1414は発光素子1404の第1の電極1424に接続されている。

#### 【0104】

なお図14では、図6(B)に示した発光装置において、駆動用TFT、電流制御用TFTがそれぞれ独立した第1の半導体膜を有している構造を示したが、本発明はこの構成に限定されない。例えば、図8～図10に示した発光装置において、駆動用TFT、電流制御用TFTがそれぞれ独立した第1の半導体膜を有していても良い。

10

#### 【実施例2】

#### 【0105】

本実施例では、本発明の発光装置が有する画素の、図1とは異なる形態について説明する。

#### 【0106】

図12(A)に示す画素は、発光素子801と、スイッチング用TFT802と、駆動用TFT803と、電流制御用TFT804と、書き込まれたビデオ信号の電位を消去するためのTFT(消去用TFT)805とを有している。上記素子に加えて容量素子806を画素に設けても良い。また、駆動用TFT803にはエンハンスマント型TFTを用いてもよいし、ディブリーション型TFTを用いてもよい。

20

#### 【0107】

スイッチング用TFT802のゲート電極は、第1の走査線Gaj(j=1～y)に接続されている。スイッチング用TFT802のソース領域とドレイン領域は、一方が信号線Si(i=1～x)に、もう一方が電流制御用TFT804のゲート電極に接続されている。また消去用TFT805のゲート電極は、第2の走査線Gb(j=j=1～y)に接続されており、ソース領域とドレイン領域は、一方が第1の電源線Vi(i=1～x)に、他方が電流制御用TFT804のゲート電極に接続されている。駆動用TFT803のゲート電極は第2の電源線Wi(i=1～x)に接続されている。そして駆動用TFT803及び電流制御用TFT804は、発光素子801に供給される電流が、駆動用TFT803及び電流制御用TFT804のドレイン電流として第1の電源線Vi(i=1～x)に供給されるように、第1の電源線Vi(i=1～x)、発光素子801と接続されている。本実施例では、電流制御用TFT804のソース領域が第1の電源線Vi(i=1～x)に接続され、駆動用TFT803のドレイン領域が発光素子801の第1の電極に接続される。なお駆動用TFT803のソース領域を第1の電源線Vi(i=1～x)に接続し、電流制御用TFT804のドレイン領域を発光素子801の第1の電極に接続してもよい。容量素子806が有する2つの電極は、一方は第1の電源線Vi(i=1～x)に接続されており、もう一方は電流制御用TFT804のゲート電極に接続されている。

30

#### 【0108】

発光素子801は陽極と、陰極と、陽極と陰極の間に設けられた電界発光層とを有する。図12(A)のように駆動用TFT803及び電流制御用TFT804がn型である場合、第1の電極を陰極、第2の電極を陽極とするのが望ましい。

#### 【0109】

図12(A)に示す画素は、その動作を書き込み期間、保持期間、消去期間とに分けて説明することができる。書き込み期間と保持期間におけるスイッチング用TFT802、駆動用TFT803及び電流制御用TFT804の動作については、図1の場合と同様である。

#### 【0110】

40

50

消去期間では、第2の走査線G<sub>b</sub>j (j = 1 ~ y)が選択されて消去用TFT805がオンになり、電源線V1 ~ Vxの電位が消去用TFT805を介して電流制御用TFT804のゲート電極に与えられる。よって、電流制御用TFT804がオフになるため、発光素子801に強制的に電流が供給されない状態を作り出すことができる。

#### 【0111】

図12(B)に、本実施例における画素の別の構成を示す。図12(B)に示す画素は、発光素子811と、スイッチング用TFT812と、駆動用TFT813と、電流制御用TFT814とを有している。さらに本実施例のように、ビデオ信号の電位を保持するための容量素子814を画素に設けても良い。駆動用TFT813にはエンハンスマント型TFTを用いても良いし、ディプリーション型TFTを用いても良い。電流制御用TFT814は線形領域で動作させる。 10

#### 【0112】

スイッチング用TFT812のゲート電極は、走査線Gj (j = 1 ~ y)に接続されている。スイッチング用TFT812のソース領域とドレイン領域は、一方が信号線Si (i = 1 ~ x)に、もう一方が電流制御用TFT814のゲート電極に接続されている。駆動用TFT813のゲート電極は電源線Vi (i = 1 ~ y)に接続されている。そして駆動用TFT813及び電流制御用TFT814は、発光素子811に供給される電流が、駆動用TFT813及び電流制御用TFT814のドレイン電流として電源線Vi (i = 1 ~ x)に供給されるように、電源線Vi (i = 1 ~ x)、発光素子811と接続されている。本実施例では、電流制御用TFT814のソース領域が電源線Vi (i = 1 ~ x)に接続され、駆動用TFT813のドレイン領域が発光素子811の第1の電極に接続される。なお本実施例では、駆動用TFT813のソース領域が電源線Vi (i = 1 ~ x)に接続され、電流制御用TFT814のドレイン領域が発光素子811の第1の電極に接続されていても良い。容量素子814が有する2つの電極は、一方は電源線Vi (i = 1 ~ x)に接続されており、もう一方は電流制御用TFT814のゲート電極に接続されている。 20

#### 【0113】

発光素子811は陽極と、陰極と、陽極と陰極の間に設けられた電界発光層とを有する。図12(B)のように駆動用TFT813及び電流制御用TFT814がn型である場合、第1の電極を陰極、第2の電極を陽極とするのが望ましい。 30

#### 【0114】

次に、図12(C)に、図12(B)に示した画素において、電流制御用TFT814を強制的にオフするためのTFT(消去用TFT)816を設けた画素の回路図を示す。なお図12(C)では、図12(B)において既に説明した素子については、同じ符号を付す。消去用TFT816は、ゲート電極が第2の走査線G<sub>b</sub>に接続されており、ソース領域とドレイン領域は、一方が電流制御用TFT814のゲート電極に、他方が電源線Viに接続されている。消去用TFT816はn型であってもp型であってもどちらでも良い。

#### 【0115】

図12(D)に、本実施例における画素の別の構成を示す。図12(D)に示す画素は、発光素子821と、スイッチング用TFT822と、駆動用TFT823と、電流制御用TFT824とを有している。さらに本実施例のように、ビデオ信号の電位を保持するための容量素子825を画素に設けても良い。駆動用TFT823は、飽和領域動作させても良いし、線形領域で動作させても良い。スイッチング用TFT822及び電流制御用TFT824は線形領域で動作させる。駆動用TFT823にはエンハンスマント型TFTを用いても良いし、ディプリーション型TFTを用いてもよい。 40

#### 【0116】

スイッチング用TFT822のゲート電極は、第1の走査線G<sub>a</sub>j (j = 1 ~ y)に接続されている。スイッチング用TFT822のソース領域とドレイン領域は、一方が信号線Si (i = 1 ~ x)に、もう一方が電流制御用TFT824のゲート電極に接続されて 50

いる。駆動用 TFT 823 のゲート電極は第 2 の走査線 Gbj ( j = 1 ~ y ) に接続されている。そして駆動用 TFT 823 及び電流制御用 TFT 824 は、電源線 Vi ( i = 1 ~ x ) から供給される電流が、駆動用 TFT 823 及び電流制御用 TFT 824 のドレイン電流として発光素子 821 に供給されるように、電源線 Vi ( i = 1 ~ x ) 、発光素子 821 と接続されている。本実施例では、電流制御用 TFT 824 のソース領域が電源線 Vi ( i = 1 ~ x ) に接続され、駆動用 TFT 823 のドレイン領域が発光素子 821 の第 1 の電極に接続される。なお本実施例では、駆動用 TFT 823 のソース領域が電源線 Vi ( i = 1 ~ x ) に接続され、電流制御用 TFT 824 のドレイン領域が発光素子 821 の第 1 の電極に接続されていても良い。容量素子 825 が有する 2 つの電極は、一方は電源線 Vi ( i = 1 ~ x ) に接続されており、もう一方は電流制御用 TFT 824 のゲート電極に接続されている。10

#### 【 0117 】

発光素子 821 は陽極と陰極と、陽極と陰極との間に設けられた電界発光層とを有する。図 12 ( D ) のように駆動用 TFT 823 及び電流制御用 TFT 824 が n 型である場合、第 1 の電極を陰極、第 2 の電極を陽極とするのが望ましい。

#### 【 0118 】

次に、図 12 ( E ) に、図 12 ( D ) に示した画素において、電流制御用 TFT 824 を強制的にオフするための TFT ( 消去用 TFT ) 826 を設けた画素の回路図を示す。なお図 12 ( E ) では、図 12 ( D ) において既に説明した素子については、同じ符号を付して示す。消去用 TFT 826 は、ゲート電極が第 2 の走査線 Gbj に接続されており、ソース領域とドレイン領域は、一方が電流制御用 TFT 824 のゲート電極に、他方が電源線 Vi に接続されている。消去用 TFT 826 は n 型であっても p 型であってもどちらでも良い。20

#### 【 0119 】

なお、第 1 の電源線 Vi のレイアウトは、図 1 に示した構成に限定されない。例えば図 13 ( A ) に示すように、信号線 Si を共有している画素間で、駆動用 TFT 103 のゲート電極を、複数の配線で電気的に接続し、該複数の配線及び駆動用 TFT 103 のゲート電極を第 1 の電源線 Vi として機能させても良い。なお図 13 ( A ) では、図 1 において既に説明した素子については、同じ符号を付して示す。図 13 ( A ) の駆動用 TFT 103 を示す回路記号は、ゲート電極の異なる 2 点にコンタクト領域を設けた TFT を表したものであり、接続関係が通常と異なるため、特にこの様に表した。30

#### 【 0120 】

また同様に、第 1 の電源線 Vi のレイアウトは、図 12 ( A ) に示した構成に限定されない。例えば図 13 ( B ) に示すように、信号線 Si を共有している画素間で、駆動用 TFT 803 のゲート電極を、複数の配線で電気的に接続し、該複数の配線及び駆動用 TFT 803 のゲート電極を第 1 の電源線 Vi として機能させても良い。なお図 13 ( B ) では、図 12 ( A ) において既に説明した素子については、同じ符号を付して示す。図 13 ( B ) の駆動用 TFT 803 を示す回路記号は、ゲート電極の異なる 2 点にコンタクト領域を設けた TFT を表したものであり、接続関係が通常と異なるため、特にこの様に表した。40

#### 【 0121 】

次に図 12 ( F ) に、図 1 に示した画素において、発光素子 101 に逆方向バイアスの電圧を印加するための TFT ( 逆バイアス用 TFT ) 106 を設けた画素の回路図を示す。なお図 12 ( F ) では、図 1 において既に説明した素子については、同じ符号を付して示す。逆バイアス用 TFT 106 は、ソース領域またはドレイン領域のいずれか一方が発光素子 101 の第 1 の電極に、もう一方が第 1 の電源線 Vi に接続されている。なお図 12 ( F ) では、ソース領域またはドレイン領域のいずれか一方が第 1 の電源線 Vi に接続されているが、本発明はこの構成に限定されない。いずれか一方が第 2 の電源線 Wi に接続されても良いし、別用意された他の配線に接続されても良い。また、逆バイアス用 TFT 106 は、ゲート電極が第 1 の電源線 Vi に接続されている。なお図 12 ( F )50

) では、逆バイアス用 TFT106 のゲート電極が第 1 の電源線 V<sub>i</sub> に接続されているが、本発明はこの構成に限定されない。逆バイアス用 TFT106 のゲート電極が第 2 の電源線 W<sub>i</sub> に接続されていても良いし、別用意された他の配線に接続されていても良い。ただし逆バイアス用 TFT106 は、順方向バイアスの電圧の印加時に、ゲート電極の電位がソース領域の電位と同じか、もしくはソース領域の電位よりも低くなるようにする。なお逆バイアス用 TFT106 は n 型であっても p 型であってもどちらでも良い。

【 0122 】

逆バイアス用 TFT106 を設けることで、駆動用 TFT103 、電流制御用 TFT104 の動作に関わりなく、発光素子 101 に逆方向バイアスの電圧を確実に印加することができる。また逆方向バイアスの電圧を発光素子 101 に印加することで、発光素子 101 の信頼性を高めることができる。また、第 1 の電極と第 2 の電極間ににおいてショートの原因となっている塵埃等を焼き切る事ができるので、歩留まりを高めることができる。

【 実施例 3 】

【 0123 】

次に図 14 を用いて、発光素子の構成について説明する。本発明における発光素子の素子構成を、図 14 に模式的に示す。

【 0124 】

図 14 に示す発光素子は、基板 500 上に形成された第 1 の電極 501 と、第 1 の電極 501 上に形成された電界発光層 502 と、電界発光層 502 上に形成された第 2 の電極 503 とを有する。なお実際には、基板 500 と第 1 の電極 501 の間には、各種の層または半導体素子などが設けられている。

【 0125 】

本実施例では、第 1 の電極 501 が陰極、第 2 の電極が陽極の場合について説明するが、第 1 の電極 501 が陽極、第 2 の電極が陰極であっても良い。陽極、陰極に用いる具体的な材料については、既に説明してあるので、ここでは電界発光層 502 の具体的な構成について説明する。

【 0126 】

電界発光層 502 は単数または複数の層で構成されている。複数の層で構成されている場合、これらの層は、キャリア輸送特性の観点から正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層などに分類することができる。なお各層の境目は必ずしも明確である必要はなく、互いの層を構成している材料が一部混合し、界面が不明瞭になっている場合もある。各層には、有機系の材料、無機系の材料を用いることが可能である。有機系の材料として、高分子系、中分子系、低分子系のいずれの材料も用いることが可能である。なお中分子系の材料とは、構造単位の繰返しの数（重合度）が 2 から 20 程度の低重合体に相当する。

【 0127 】

正孔注入層と正孔輸送層との区別は必ずしも厳密なものではなく、これらは正孔輸送性（正孔移動度）が特に重要な特性である意味において同じである。便宜上正孔注入層は陽極に接する側の層であり、正孔注入層に接する層を正孔輸送層と呼んで区別する。電子輸送層、電子注入層についても同様であり、陰極に接する層を電子注入層と呼び、電子注入層に接する層を電子輸送層と呼んでいる。発光層は電子輸送層を兼ねる場合もあり、発光性電子輸送層とも呼ばれる。図 14 では、第 1 ~ 第 5 の層 504 ~ 508 を電界発光層 502 が有している場合を例示している。第 1 ~ 第 5 の層 504 ~ 508 は、第 1 の電極 501 から第 2 の電極 503 に向かって順に積層されている。

【 0128 】

第 1 の層 504 は電子注入層として機能するため、電子注入性の高い材料を用いるのが望ましい。具体的には、LiF 、 CsF などのアルカリ金属ハロゲン化物や、CaF<sub>2</sub> のようなアルカリ土類ハロゲン化物、Li<sub>2</sub>O などのアルカリ金属酸化物のような絶縁体の超薄膜がよく用いられる。また、リチウムアセチルアセトネート（略称：Li（acac）<sub>2</sub> ）や 8 - キノリノラト - リチウム（略称：Li<sub>2</sub>q ）などのアルカリ金属錯体も有効である

10

20

30

40

50

。また、モリブデン酸化物 ( $\text{MoO}_x$ ) やバナジウム酸化物 ( $\text{VO}_x$ ) 、ルテニウム酸化物 ( $\text{RuO}_x$ ) 、タンゲステン酸化物 ( $\text{WO}_x$ ) 等の金属酸化物またはベンゾオキサゾール誘導体と、アルカリ金属、アルカリ土類金属、または遷移金属のいずれか一または複数の材料とを含むようにしても良い。また酸化チタンを用いていても良い。

#### 【0129】

第2の層505は電子輸送層として機能するため、電子輸送性の高い材料を用いることが望ましい。具体的には、 $\text{Alq}_3$ に代表されるような、キノリン骨格またはベンゾキノリン骨格を有する金属錯体やその混合配位子錯体などを用いることができる。具体的には、 $\text{Alq}_3$ 、 $\text{Almq}_3$ 、 $\text{BeBq}_2$ 、 $\text{BALq}$ 、 $\text{Zn}(\text{BOX})_2$ 、 $\text{Zn}(\text{BTZ})_2$ などの金属錯体が挙げられる。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール (PBD)、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン (OXD-7)などのオキサジアゾール誘導体、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニリル)-1,2,4-トリアゾール (TAZ)、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニリル)-1,2,4-トリアゾール (p-EtTAZ)などのトリアゾール誘導体、TPBIのようなイミダゾール誘導体、バソフェナントロリン (BPhen)、バソキュプロイン (BCP)などのフェナントロリン誘導体を用いることができる。

#### 【0130】

第3の層506は発光層として機能するため、イオン化ポテンシャルが大きく、かつバンドギャップの大きな材料を用いるのが望ましい。具体的には、例えば、トリス(8-キノリノラト)アルミニウム ( $\text{Alq}_3$ )、トリス(4-メチル-8-キノリノラト)アルミニウム ( $\text{Almq}_3$ )、ビス(10-ヒドロキシベンゾ[ ]-キノリナト)ベリリウム ( $\text{BeBq}_2$ )、ビス(2-メチル-8-キノリノラト)-(4-ヒドロキシ-ビフェニリル)-アルミニウム ( $\text{BALq}$ )、ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛 ( $\text{Zn}(\text{BOX})_2$ )、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛 ( $\text{Zn}(\text{BTZ})_2$ )などの金属錯体を用いることができる。また、各種蛍光色素(クマリン誘導体、キナクリドン誘導体、ルブレン、4,4-ジシアノメチレン、1-ピロン誘導体、スチルベン誘導体、各種縮合芳香族化合物など)も用いることができる。白金オクタエチルポルフィリン錯体、トリス(フェニルピリジン)イリジウム錯体、トリス(ベンジリデンアセトナート)フェナントレンユーロピウム錯体などの発光材料も用いることができる。

#### 【0131】

また、第3の層506に用いるホスト材料としては、上述した例に代表されるホール輸送材料や電子輸送材料を用いることができる。また、4,4'-N,N'-ジカルバゾリルビフェニル(略称:CBP)などのバイポーラ性の材料も用いることができる。

#### 【0132】

第4の層507は、正孔輸送層として機能するため、正孔輸送性が高く、結晶性の低い公知の材料を用いることが望ましい。具体的には芳香族アミン系(すなわち、ベンゼン環-窒素の結合を有するもの)の化合物が好適であり、例えば、4,4'-ビス[N-(3-メチルフェニル)-N-フェニルアミノ]ビフェニル (TPD) や、その誘導体である4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]ビフェニル (-NPD) などがある。4,4',4''-トリス(N,N-ジフェニルアミノ)トリフェニルアミン (TDATA) や、MTDATAなどのスターバースト型芳香族アミン化合物も用いることができる。また4,4',4'''-トリス(N-カルバゾリル)トリフェニルアミン(略称:TCTA)を用いても良い。また高分子材料としては、良好な正孔輸送性を示すポリ(ビニルカルバゾール)などを用いることができる。

#### 【0133】

第5の層508は、正孔注入層として機能するため、正孔輸送性を有し、なおかつイオン化ポテンシャルが比較的小さく、正孔注入性が高い材料を用いるのが望ましい。大別す

10

20

30

40

50

ると金属酸化物、低分子系有機化合物、および高分子系有機化合物に分けられる。金属酸化物であれば、例えば、酸化バナジウム、酸化モリブデン、酸化ルテニウム、酸化アルミニウムなど用いることができる。低分子系有機化合物であれば、例えば、m-MTATAに代表されるスターバースト型アミン、銅フタロシアニン（略称：Cu-Pc）に代表される金属フタロシアニン、フタロシアニン（略称：H<sub>2</sub>-Pc）、2,3-ジオキシエチレンチオフェン誘導体などを用いることができる。低分子系有機化合物と上記金属酸化物とを共蒸着させた膜であっても良い。高分子系有機化合物であれば、例えば、ポリアニリン（略称：Pan）、ポリビニルカルバゾール（略称：PVK）、ポリチオフェン誘導体などの高分子を用いることができる。ポリチオフェン誘導体の一つであるポリエチレンジオキシチオフェン（略称：PEDOT）にポリスチレンスルホン酸（略称：PSS）をドープしたものを用いても良い。また、ベンゾオキサゾール誘導体と、TCQn、FeCl<sub>3</sub>、C<sub>60</sub>またはF<sub>4</sub>TQNのいずれか一または複数の材料とを併せて用いても良い。

10

#### 【0134】

上記構成を有する発光素子において、第1の電極501と第2の電極503の間に電圧を印加し、電界発光層502に順方向バイアスの電流を供給することで、第3の層506から光を発生させ、該光を第1の電極501側から、または第2の電極503側から取り出すことができる。なお、電界発光層502は、必ずしもこれら第1～第5の層を全て有している必要はない。本発明では、少なくとも発光層として機能する第3の層506を有していれば良い。また必ずしも第3の層506からのみ発光が得られるわけではなく、第1～第5の層に用いられる材料の組み合わせによっては、第3の層506以外の層から発光が得られる場合もある。また、第3の層506と第4の層507の間に正孔プロック層を設けても良い。

20

#### 【0135】

なお色によっては、燐光材料の方が蛍光材料よりも、駆動電圧を低くすることができ、信頼性も高い場合がある。そこで、三原色の各色に対応する発光素子を用いて、フルカラーの表示を行なう場合は、蛍光材料を用いた発光素子と、燐光材料を用いた発光素子とを組み合わせて、各色の発光素子における劣化の度合いを揃えるようにしても良い。

#### 【0136】

図14では、第1の電極501が陰極、第2の電極503が陽極である場合について示しているが、第1の電極501が陽極、第2の電極503が陰極である場合、第1～第5の層504～508は逆に積層される。具体的には、第1の電極501上に第5の層508、第4の層507、第3の層506、第2の層505、第1の層504が順に積層される。

30

#### 【0137】

なお電界発光層502のうち、第2の電極503に最も近い層（本実施例では第5の層508）に、エッティングされにくい材料を用いることで、電界発光層502上に第2の電極503をスパッタ法で形成する際に、第2の電極503に最も近い層に与えられるスパッタダメージを軽減させることができる。エッティングされにくい材料とは、例えばモリブデン酸化物（MoO<sub>x</sub>）やバナジウム酸化物（VO<sub>x</sub>）、ルテニウム酸化物（RuO<sub>x</sub>）、タンゲステン酸化物（WO<sub>x</sub>）等の金属酸化物、またはベンゾオキサゾール誘導体を用いることができる。これらは蒸着法によって形成されることが好ましい。

40

#### 【0138】

例えば、第1の電極が陰極、第2の電極が陽極の場合、前記電界発光層のうち最も陽極に近い、ホール注入性またはホール輸送性を有する層として、上述したエッティングされにくい材料を用いる。具体的に、ベンゾオキサゾール誘導体を用いる場合は、当該ベンゾオキサゾール誘導体と、TCQn、FeCl<sub>3</sub>、C<sub>60</sub>またはF<sub>4</sub>TQNのいずれか一または複数の材料とを含む層を、最も陽極に近くなるように形成する。

#### 【0139】

また例えば、第1の電極が陽極、第2の電極が陰極の場合、前記電界発光層のうち最も陰極に近い、電子注入性または電子輸送性を有する層として、上述したエッティングされに

50

くい材料を用いる。具体的に、モリブデン酸化物を用いる場合は、当該モリブデン酸化物と、アルカリ金属、アルカリ土類金属、または遷移金属のいずれか一または複数の材料とを含む層を、最も陰極に近くなるように形成する。またベンゾオキサゾール誘導体を用いる場合は、当該ベンゾオキサゾール誘導体と、アルカリ金属、アルカリ土類金属、または遷移金属のいずれか一または複数の材料とを含む層を、最も陰極に近くなるように形成する。なお、金属酸化物とベンゾオキサゾール誘導体を共に用いていても良い。

#### 【0140】

上記構成により、第2の電極として、スパッタ法で形成した透明導電膜、例えばインジウム錫酸化物 (ITO) や珪素を含有したインジウム錫酸化物 (ITSO)、酸化インジウムに 2 ~ 20 % の酸化亜鉛 (ZnO) を混合したIZO (Indium Zinc O<sub>xide</sub>) 等を用いても、電界発光層が有する有機物を含む層への、スパッタダメージを抑えることができ、第2の電極を形成するための物質の選択性が広がる。

#### 【実施例4】

#### 【0141】

本実施例では、発光装置とICとの接続方法の一実施例について説明する。

#### 【0142】

図15(A)、図15(B)に、チップ状のIC (ICチップ)を、画素部が形成された素子基板に実装する様子を示す。図15(A)では、基板6001上に画素部6002と、走査線駆動回路6003とが形成されている。そして、ICチップ6004に形成された信号線駆動回路が、基板6001に実装されている。具体的には、ICチップ6004に形成された信号線駆動回路が、基板6001に貼り合わされ、画素部6002と電気的に接続されされている。また6005はFPCであり、画素部6002と、走査線駆動回路6003と、ICチップ6004に形成された信号線駆動回路とに、それぞれ電源電位、各種信号等が、FPC6005を介して供給される。

#### 【0143】

図15(B)では、基板6101上に画素部6102と、走査線駆動回路6103とが形成されている。そして、ICチップ6104に形成された信号線駆動回路が、基板6101に実装されたFPC6105に更に実装されている。画素部6102と、走査線駆動回路6103と、ICチップ6104に形成された信号線駆動回路とに、それぞれ電源電位、各種信号等が、FPC6105を介して供給される。

#### 【0144】

ICチップの実装方法は、特に限定されるものではなく、公知のCOG方法やワイヤボンディング方法、或いはTAB方法などを用いることができる。またICチップを実装する位置は、電気的な接続が可能であるならば、図15に示した位置に限定されない。また、図15では信号線駆動回路のみをICチップで形成した例について示したが、走査線駆動回路をICチップで形成しても良いし、またコントローラ、CPU、メモリ等をICチップで形成し、実装するようにしても良い。また、信号線駆動回路や走査線駆動回路全体をICチップで形成するのではなく、各駆動回路を構成している回路の一部だけを、ICチップで形成するようにしても良い。

#### 【0145】

なお、駆動回路などの集積回路を別途ICチップで形成して実装することで、全ての回路を画素部と同じ基板上に形成する場合に比べて、歩留まりを高めることができ、また各回路の特性に合わせたプロセスの最適化を容易に行なうことができる。

#### 【0146】

なお図15では示していないが、画素部が形成されている基板上に、保護回路を設けていても良い。保護回路により放電経路を確保することができるので、信号及び電源電圧が有する雑音や、何らかの理由によって絶縁膜にチャージングされた電荷によって、基板に形成された半導体素子が劣化あるいは絶縁破壊されるのを防ぐことができる。具体的に図15(A)の場合、FPC6005と画素部6002とを電気的に接続している配線に、保護回路を接続することができる。またさらに、FPC6005と信号線駆動回路600

10

20

30

40

50

4とを電気的に接続している配線、FPC6005と走査線駆動回路6003とを電気的に接続している配線、信号線駆動回路6004と画素部6002とを電気的に接続している配線(信号線)、走査線駆動回路6003と画素部6002とを電気的に接続している配線(走査線)に、それぞれ保護回路を接続することができる。

【実施例5】

【0147】

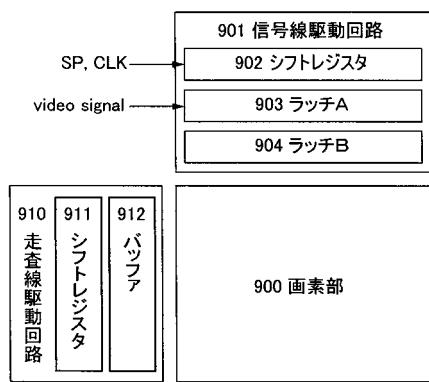

次に、本発明の発光装置に用いられる駆動回路の構成について説明する。図16に、本発明の発光装置のブロック図を示す。図16において信号線駆動回路901は、シフトレジスタ902、ラッチA903、ラッチB904を有している。走査線駆動回路910は、シフトレジスタ911、バッファ912を有している。また900は画素部に相当する。なお走査線を2本(第1の走査線、第2の走査線)有する発光装置の場合、走査線駆動回路を2つ有していても良い。

10

【0148】

シフトレジスタ902には、クロック信号(CLK)、スタートパルス信号(SP)が入力されている。クロック信号(CLK)とスタートパルス信号(SP)が入力されると、シフトレジスタ902においてタイミング信号が生成され、一段目のラッチA903に順に入力される。ラッチA903にタイミング信号が入力されると、該タイミング信号に同期して、ビデオ信号が順にラッチA903に書き込まれ、保持される。なお、図16ではラッチA903に順にビデオ信号を書き込んでいると仮定するが、本発明はこの構成に限定されない。複数のステージのラッチA903をいくつかのグループに分け、グループごとに並行してビデオ信号を入力する、いわゆる分割駆動を行っても良い。なおこのときのグループの数を分割数と呼ぶ。例えば4つのステージごとにラッチをグループに分けた場合、4分割で分割駆動すると言う。

20

【0149】

ラッチA903に含まれる全てのステージのラッチへの、ビデオ信号の書き込みが一通り終了するまでの時間を、ライン期間と呼ぶ。実際には、上記ライン期間に水平帰線期間が加えられた期間をライン期間に含むことがある。

【0150】

1ライン期間が終了すると、2段目のラッチB904にラッチ信号(Latch Signal)が供給され、該ラッチ信号に同期してラッチA903に保持されているビデオ信号が、ラッチB904に一斉に書き込まれ、保持される。ビデオ信号をラッチB904に送出し終えたラッチA903には、再びシフトレジスタ902からのタイミング信号に同期して、次のビデオ信号の書き込みが順次行われる。この2順目の1ライン期間中には、ラッチB904に書き込まれ、保持されているビデオ信号が信号線に入力される。

30

【0151】

次に、走査線駆動回路910の構成について説明する。走査線駆動回路910は、シフトレジスタ911、バッファ912を有している。また場合によってはレベルシフタを有していても良い。走査線駆動回路910において、シフトレジスタ911にクロック信号(CLK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファ912において緩衝増幅され、対応する走査線に供給される。走査線には、1ライン分の画素のスイッチング用TFTまたは消去用TFTのゲートが接続されている。そして、1ライン分の画素のTFTを一斉にオンにしなくてはならないので、バッファ912は大きな電流を流すことが可能なものが用いられる。

40

【0152】

なお、図16に示す構成は、本発明の発光装置の一形態を示したに過ぎず、信号線駆動回路と走査線駆動回路の構成はこれに限定されない。例えば、本発明で用いる信号線駆動回路、走査線駆動回路は、シフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を用いても良い。

【実施例6】

【0153】

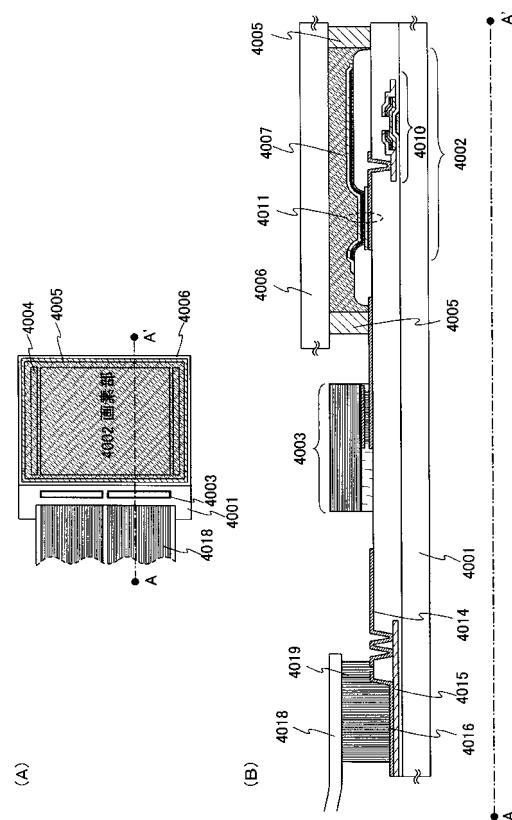

本実施例では、本発明の発光装置の一形態に相当するパネルの外観について、図17を用いて説明する。図17は、素子基板上に形成されたTFT及び発光素子を、カバー材との間にシール材によって封止した、パネルの上面図であり、図17(B)は、図17(A)のA-A'における断面図に相当する。

【0154】

素子基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上にカバー材4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、素子基板4001とシール材4005とカバー材4006とによって、充填材4007と共に密封されている。また素子基板4001上のシール材4005によって囲まれている領域とは異なる領域に、信号線駆動回路4003が形成されたICが実装されている。10

【0155】

また素子基板4001上に設けられた画素部4002と、走査線駆動回路4004は、TFTを複数有しており、図17(B)では、画素部4002に含まれるTFT4010とを例示している。また4011は発光素子に相当し、TFT4010のソース領域またはドレイン領域と電気的に接続されている。

【0156】

また、別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、図17(B)に示す断面図では図示されていないが、引き回し配線4014及び4015を介して、接続端子4016から供給されている。接続端子4016、引き回し配線4014、4015は、いずれも液滴吐出法または印刷法で形成することができる。20

【0157】

接続端子4016は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

【0158】

なお、素子基板4001、カバー材4006としては、ガラス、金属(代表的にはステンレス)、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。30

【0159】

但し、発光素子4011からの光の取り出し方向に位置する基板には、カバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

【0160】

また、充填材4007としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。40

【0161】

また充填材4007を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、カバー材4006と素子基板4001との間に、充填材4007と共に、吸湿性物質または酸素を吸着しうる物質を設けておいても良い。吸湿性物質または酸素を吸着しうる物質を設けることで、発光素子4011の劣化を抑制できる。

【0162】

なお図17では、信号線駆動回路4003を別途形成し、素子基板4001に実装して50

いる例を示しているが、本実施例はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

【0163】

本実施例は、他の実施例に記載した構成と組み合わせて実施することが可能である。

【実施例7】

【0164】

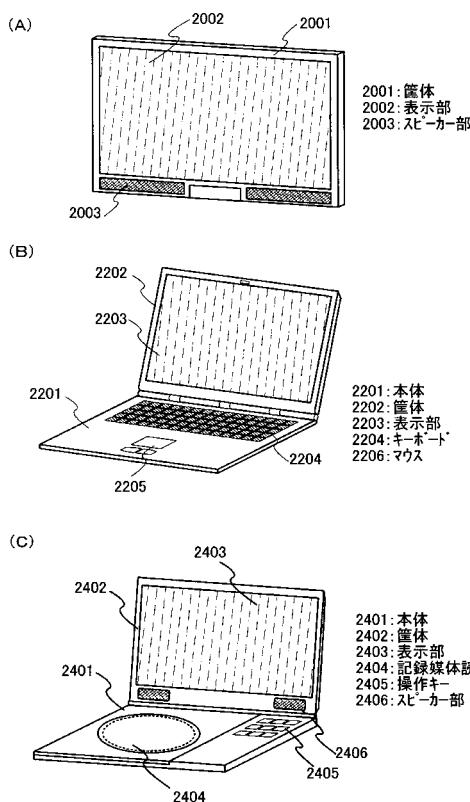

本発明の発光装置を用いることができる電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（代表的にはDVD : Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）などが挙げられる。特に本発明の発光装置は、画素数を増やしても、充電時間の増加を抑えることができ、また面積あたりのコストを抑えることができる。よって本発明の発光装置は、比較的大型のパネルが用いられる電子機器に特に適している。これら電子機器の具体例を図18に示す。

10

【0165】

図18(A)は表示装置であり、筐体2001、表示部2002、スピーカー部2003等を含む。本発明の発光装置は、表示部2002に用いることができる。発光装置は自発光型であるためバックライトが不要なく、液晶ディスプレイよりも薄い表示部とすることができます。なお、表示装置には、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。なお表示装置に発光装置を用いる場合、発光素子が有する第1の電極または第2の電極において外光が反射することで、鏡面のように像を写してしまふのを防ぐために、偏光板を設けておいても良い。

20

【0166】

図18(B)はノート型パソコンコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、マウス2205等を含む。本発明の発光装置は、表示部2203に用いることができる。

30

【0167】

図18(C)は記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）であり、本体2401、筐体2402、表示部2403、記録媒体(DVD等)読み込み部2404、操作キー2405、スピーカー部2406等を含む。記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明の発光装置は、表示部2403に用いることができる。

【0168】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は、実施例1～6に示したいずれの構成の発光装置を用いても良い。

40

【実施例8】

【0169】

本実施例では、液滴吐出法を用いて形成される配線及び電極の一実施例について説明する。

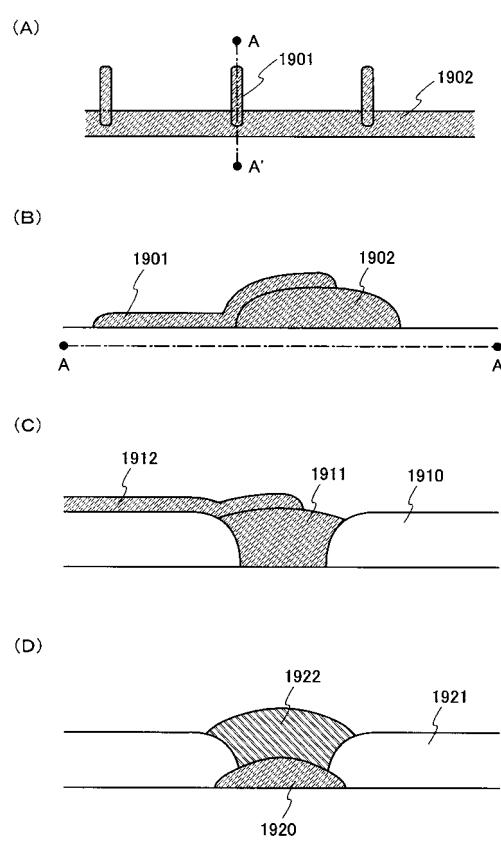

【0170】

図19(A)に、ゲート電極1901と、該ゲート電極に接続された走査線1902の上面図を示す。また図19(A)のA-A'における断面図を、図19(B)に示す。図19(A)では、ゲート電極1901に比べて配線抵抗を抑え、スループットを高めることができ望ましく、なおかつレイアウトの精密さがゲート電極1901ほど要求されない走査線1902を、ゲート電極1901よりも太い線幅で形成する。また逆に、走査線1902に比べてレイアウトされる距離が短く、なおかつレイアウトの精密さが要求されるゲー

50

ト電極 1901 を、走査線 1902 よりも細い線幅で形成する。線幅の制御は、液滴 1 ドットあたりの吐出量、該溶液の表面張力、液滴が滴下される表面の撥水性などを最適化することで行なうことが可能である。

【0171】

図 19 (A) に示すように、形成する配線または電極に合わせてノズルを切り替えることで、スループットを向上させ、また形成される半導体素子の特性を高めることができる。なお図 19 (A) では、走査線とゲート電極とで線幅を変えるためにノズルを切り替える例について示したが、本実施例はこの構成に限定されない。レイアウトの精密さが要求される配線または電極と、配線抵抗の低減またはスループットの向上が重要視される配線または電極とでノズルを切り替えることで、スループットを向上させ、また形成される半導体素子の特性を高めることができる。

10

【0172】

図 19 (A) に示すように、配線または電極の形成する際に走査方向を切り替えたり、ノズルを切り替えたりする場合、先に形成された配線または電極に紫外線を照射してから、次の配線または電極を形成しても良い。上記構成により、先に形成された配線または電極の表面の密着性が高められて、ゲート電極 1901 と走査線 1902 とが剥離しにくい。この場合、焼成は配線または電極を形成することに行なっても良いし、互いに接する配線または電極を全て形成してから行なっても良い。

【0173】

なお図 19 (A) では、平坦な面にゲート電極 1901 と走査線 1902 とを形成する例について説明したが、本発明はこの構成に限定されない。例えば、図 19 (C) に示すように、層間絶縁膜 1910 の開口部に走査線 1911 を形成し、層間絶縁膜 1910 上に走査線 1911 と接するゲート電極 1912 を形成するようにしても良い。図 19 (C) の場合、開口部を有する層間絶縁膜 1910 を液滴吐出法で形成した後、該開口部に走査線 1911 を液滴吐出法で形成しても良いし、層間絶縁膜 1910 と走査線 1911 とを並行して液滴吐出法で形成しても良い。

20

【0174】

なお配線は 2 層の導電層で形成されていても良い。図 19 (D) に示すように、平坦な面に液滴吐出法で導電層 1920 を形成した後、開口部において導電層 1920 が露出するように層間絶縁膜 1921 を液滴吐出法で形成する。そして該開口部において導電層 1920 と接するように、液滴吐出法を用いて導電層 1922 を形成する。導電層 1920 と導電層 1922 とを合わせて、走査線、信号線などの 1 つの配線として用いることができる。

30

【図面の簡単な説明】

【0175】

【図 1】本発明の発光装置が有する画素の回路図。

【図 2】本発明の発光装置が有する画素の動作を、模式的に示した図。

【図 3】本発明の発光装置が有する画素の回路図。

【図 4】本発明の発光装置の作製方法を示す図。

【図 5】本発明の発光装置の作製方法を示す図。

40

【図 6】本発明の発光装置の作製方法を示す図。

【図 7】本発明の発光装置が有する画素の上面図。

【図 8】本発明の発光装置の作製方法を示す図。

【図 9】本発明の発光装置が有する画素の断面図。

【図 10】本発明の発光装置が有する画素の断面図。

【図 11】本発明の発光装置が有する画素の断面図。

【図 12】本発明の発光装置が有する画素の回路図。

【図 13】本発明の発光装置が有する画素の回路図。

【図 14】本発明の発光装置が有する発光素子の構成を示す図。

【図 15】本発明の発光装置が有する素子基板の斜視図。

50

【図16】本発明の発光装置の構成を示すブロック図。

【図17】本発明の発光装置の上面図及び断面図。

【図18】本発明の発光装置を用いた電子機器の図。

【図19】本発明の発光装置の作製方法を示す図。

【図1】

101 発光素子

102 スイッチング用TFT

103 駆動用TFT

104 電流制御用TFT

105 容量素子

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 山崎 優

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 福本 良太

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 田井 伸幸

(56)参考文献 特開2002-149112(JP,A)

特開2003-317961(JP,A)

特開2003-058077(JP,A)

特開2003-015548(JP,A)

特開2003-318192(JP,A)

特開2001-343933(JP,A)

特開2003-280556(JP,A)

特開2003-332070(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09F 9/30

H01L 27/32

H01L 51/50

H05B 33/10