(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-313163

(P2006-313163A)

(43) 公開日 平成18年11月16日(2006.11.16)

(51) Int.C1.

GO1S 7/282 (2006.01)

F1

GO1S 7/282

テーマコード(参考)

A 5J070

審査請求 未請求 請求項の数 10 O L (全 15 頁)

(21) 出願番号 特願2006-129402 (P2006-129402)

(22) 出願日 平成18年5月8日 (2006.5.8)

(31) 優先権主張番号 11/120770

(32) 優先日 平成17年5月3日 (2005.5.3)

(33) 優先権主張国 米国(US)

(71) 出願人 503084750

メイコム インコーポレイテッド

アメリカ合衆国、マサチューセッツ州 O

1854, ローウェル, ポーチュケット

ブールバード 1011

(74) 代理人 000227995

タイコエレクトロニクスアンプ株式会社

(72) 発明者 アラン ピーター ジェンkins

アメリカ合衆国 O1450 マサチュー

セッツ州 グロートン ロングリーロード

351

(72) 発明者 ロバート イアン グレシャム

アメリカ合衆国 O2144 マサチュー

セッツ州 サマーズビル プロムフィール

ドロード 30

最終頁に続く

(54) 【発明の名称】短電子パルス発生装置及びその方法

## (57) 【要約】

【課題】正確に遅延したパルスを簡単で低成本で発生させる短電子パルス発生装置及び発生方法の提供。

【解決手段】本発明の方法及び装置は、部分的にはアナログ正弦波電圧であり、部分的には選択可能な直流電極である変形差動トリガを使用して、短電子パルスを発生させる。本装置は、デジタル差動ベースバンドパルス発生器(38)と、第1電圧値を有する第1のほぼ一定電圧を発生器の第1入力端子に供給する定電圧電源(42)とを具備する。周期的電圧電源(40)は、定電圧電源(42)及び周期的電圧電源(40)間の差が発生器(60)のスイッチング閾値とほぼ等しいとパルスが発生するように、時間変化電圧を発生器(60)の第2入力端子に供給する。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

基準時点から正確に決定された遅延時間によりそれぞれ分離された第1連の短電子パルスを発生する装置であって、

デジタル差動ベースバンドパルス発生器(38, 60)と、

第1電圧値を有する第1のほぼ一定電圧を前記発生器(38, 60)の第1入力端子に供給する定電圧電源(42)と、

周期的電圧電源であって、前記定電圧及び周期的電圧間の差が前記発生器のスイッチング閾値とほぼ等しいとパルスが発生するように、時間変化電圧を前記発生器の第2入力端子に供給する周期的電圧電源(40)と

を具備することを特徴とする、第1連の短電子パルスを発生する装置。10

**【請求項 2】**

前記定電圧電源(42)が第2値を有する第2定電圧を供給することにより、前記第1連の短電子パルスの前記時間遅延を、前記定電圧の前記第1値及び前記第2値の間の差に比例した量だけ変化させることを特徴とする請求項1記載の装置。

**【請求項 3】**

前記周期的電圧が値を増加する際に前記パルスが生成され、

前記定電圧及び前記周期的電圧の間の差がほぼ0に等しくなることを特徴とする請求項1記載の装置。20

**【請求項 4】**

前記周期的電圧は正弦波であることを特徴とする請求項3記載の装置。

**【請求項 5】**

前記正弦波は1~100MHzの範囲の周波数を有することを特徴とする請求項4記載の装置。20

**【請求項 6】**

前記発生器(38, 60)は、差動NANDゲート(14)及び差動ANDゲート(12)を具備し、

該差動ゲート(12, 14)は、前記発生器の入力端子が、前記NANDゲート(14)の入力端子の組及び前記ANDゲート(12)の第1組の入力端子の双方に接続されるように接続され。30

前記NANDゲート(14)の出力端子は前記ANDゲートの第2組の入力端子に接続され、

前記ANDゲートの出力端子は前記発生器の出力端子であることを特徴とする請求項1記載の装置。

**【請求項 7】**

前記発生器(38, 60)は第2の差動ANDゲート(36)をさらに具備し、

該第2の差動ANDゲートは、前記発生器の入力端子が前記第2の差動ANDゲートの入力端子の組に接続されるよう接続され、

前記第2の差動ANDゲートの出力端子は前記NANDゲートの前記入力端子の組に接続されていることを特徴とする請求項6記載の増幅器。40

**【請求項 8】**

第2デジタル差動ベースバンドパルス発生器(62)と、

第2のほぼ一定電圧を前記第2発生器(62)の第1入力端子に供給する第2定電圧電源(42)とをさらに具備し、

前記第2定電圧及び前記周期的電圧間の差が前記発生器(62)のスイッチング閾値とほぼ等しいとパルスが発生するように、前記周期的電圧電源が前記時間変化電圧を前記発生器の第2入力端子に供給することにより、各々が前記第1連のパルスの対応するパルスから正確に決定された第2遅延時間を有する第2連の短電子パルスを発生し、

前記第2遅延時間は、前記第1及び第2の定電圧間の差に比例することを特徴とする請求項1記載の装置。50

**【請求項 9】**

基準時点から正確に決定された遅延時間により各々分離された第1連の短電子パルスを発生する方法であって、

第1電圧値を有する第1のほぼ一定電圧を提供する工程と、

周期的時間変化電圧を提供する工程と、

前記定電圧及び前記周期的変化電圧間の差がデジタル差動ベースバンドパルス発生器(38, 62)のスイッチング閾値とほぼ等しいとパルスが発生するように、前記定電圧及び前記周期的時間変化電圧を前記発生器の入力端子に印加する工程とを具備することを特徴とする短電子パルスを発生する方法。

**【請求項 10】**

前記第1のほぼ一定電圧の第2値を選択する工程をさらに具備することにより、前記第1連の短電子パルスの前記遅延時間を、前記第1のほぼ一定電圧の前記第1値及び前記第2値間の差にほぼ比例する量だけ変更することを特徴とする請求項9記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はパルスの電子的発生の方法及び装置に関し、より詳細には高解像度レーダで使用に適する非常に短い幅のパルスの電子的発生に関する。

**【背景技術】****【0002】**

自動車業界は、自動速度制御システム(AICC)、補助装置、後方接近警報システム、エアバッグの衝突前作動を容易にするシステム、停止・前進/都会車速制御システム、及び側面衝撃の状況におけるエアバッグの衝突前起動を容易にするシステムを含む多くの用途のために、自動車内に衝突回避レーダを設置することに熱心である。

**【0003】**

これらの用途を技術的に実行できるレーダシステムは例えば「商業用及び産業用の低コスト、高解像度レーダ」と題する特許文献1に記載されている。これらのシステムは、発生される2つの同じ短パルスを要求することが代表的である。第1短パルスは送信されて、対象物で反射される。第2短パルスは、レーダ送信器から戻る往復時間と等しい時間だけ遅延する。遅延した第2短パルスは、戻った送信パルスと混合されたゲートローカル発振器としてレーダシステムの受信チャンネルで使用される。この結果、送信信号及び遅延信号間の位相差を示す直流値となる。この位相差は、戻り信号の正確な遅延時間及びいかなるドップラ偏移を得るよう分析でき、対象物の射程及び速度の双方を与える。異なる距離にある対象物を検出するために、レーダ送信器から対象物へ進み戻る第1パルスにより取られる時間と合致するように、遅延した第2パルスの遅延時間を正確に変えられることが必要である。そのようにして、遅延したパルスは、レーダの射程内で全ての可能な対象物距離に対して戻る送信パルスと同時に、ミキサに到達する。

**【特許文献1】米国特許6067040号明細書****【特許文献2】米国特許6720908号明細書****【特許文献3】米国特許6087972号明細書****【特許文献4】米国特許6639543号明細書****【特許文献5】米国特許6388609号明細書****【特許文献6】米国特許6614390号明細書****【発明の開示】****【発明が解決しようとする課題】****【0004】**

上述の特許の名称にもかかわらず、このようなレーダシステムが直面する共通の問題が実施をコスト高にする。コスト高の主な理由は、比較的短距離(2~50m)にわたって高解像の距離計測(1~10cm)が必要であることから生ずる。この要求事項は、約125ピコ秒の時間段階の参照に対して正確に遅延できる非常に短パルスを発生する必要性に翻訳さ

10

20

30

40

50

れる。このようなパルスが発生し、従来のデジタルクロック及び高速カウンタを使用して制御されると、約10GHzの未加工クロック速度が必要である。このようなクロックはコスト高であり、実施するには複雑である。

【課題を解決するための手段】

【0005】

本発明の種々の典型的実施形態は、基準時点から正確に決定された遅延時間によりそれぞれ分離された第1連の短電子パルスを発生する装置に関する。本装置は、デジタル差動ベースバンドパルス発生器と、第1電圧値を有する第1のほぼ一定電圧を発生器の第1入力端子に供給する定電圧電源とを具備する。周期的電圧電源は、定電圧電源及び時間変化電圧電源間の差が発生器のスイッチング閾値とほぼ等しいとパルスが発生するように、時間変化電圧を発生器の第2入力端子に供給する。

10

【0006】

本発明の別の典型的な実施形態において、基準時点から正確に決定された遅延時間により各々分離された第1連の短電子パルスを発生する方法が提供される。第1電圧値を有する第1のほぼ一定電圧が提供され、周期的時間変化電圧が提供される。定電圧及び時間変化電圧はデジタル差動ベースバンドパルス発生器の入力端子に印加されるので、定電圧及び時間変化電圧間の差がデジタルパルス発生器のスイッチング閾値とほぼ等しいと、パルスが発生する。

20

【0007】

簡潔に述べると、本発明は、デジタル及びアナログ回路のコンセプトの組合せを適用することにより、基準マークからの微小変化できるオフセット時間と有する時間的に短い電磁パルスを発生する方法及び装置を提供する。このようなパルスは、1個のパルスが対象物に送信され、第2のほぼ同じパルスがゲートローカル発信器として使用される、パルス化されたレーダシステムで有用である。第2パルスは、第1パルスがレーダ送信器から目的物へ進み戻るほぼ往復時間である時間だけ第1パルスに対して遅延しなければならない。異なる距離で目的物を検出するために、第1パルスに対して第2パルスの時間遅延を正確に変えることが必要である。本発明は、このようなシステムにおいて必要とされる正確に遅延したパルスを提供する簡単で低コストの方法である。

20

【0008】

本方法の典型的な一実施形態において、正確に決定された遅延時間により分離された一連の短電子パルスは、部分的にはアナログ正弦波電圧であり、部分的には選択可能な直流定電圧である変形された差動トリガを有するデジタル論理回路の適当な組合せを駆動することにより発生される。この差動トリガ電圧は、ベースバンドパルス発生器への入力として印加される。一実施形態において、ベースバンドパルス発生器は、入力がNANDゲートの入力及びANDゲートの一入力の双方へ供給されるように接続された差動NANDゲート及び差動ANDゲートから形成される。この組合せの論理回路の真理表は、出力が全入力状態に対してオフ状態にあることを示す。しかし、NANDゲートの作動の遅延のため、入力がオフ状態からオン状態に切り換わると、ANDゲートは、両ゲートがオンである短い時間を経るので、ANDゲートは短い時間オン状態にある。従来のデジタル回路において、この短いオン信号は、正の誤作動(glitch)すなわちエラーとして扱われる。この用途の回路において、このデジタルエラーはアナログパルスになる。また、作動入力正弦波の基準点に対するこのパルスのタイミングは、作動入力の一定部分の電圧値をえることにより正確且つ制御可能に変化させることができる。

30

【0009】

本発明の好適な一実施形態において、急速に切り換わるSiGe CMLゲート、及び部分的には正弦波であり部分的には選択可能な定電圧である変形差動入力は、GHz以下のクロックを使用して自動車レーダ用途での使用に適する制御可能なオフセット時間で一連の正確な形状の短パルスの発生に使用される。

40

【0010】

本発明は、基準マークからの微小変化できる時間的オフセットと有する時間的に短い電

50

磁パルスを発生するためにデジタル及びアナログ回路コンセプトの組合せを使用する方法及び装置を提供する。

【0011】

このような時間的に短い変化可能なオフセット電磁パルス発生器は、例えば微小時間ベースの基準を生成するのに使用できるパルスベースの高解像レーダーシステムにかなり重要である。パルス発生器は、ユニットコストは重要なファクタであり、比較的短い距離にわたって高解像度が要求される自動車レーダーシステム等の用途に特に適する。

【0012】

自動車レーダーシステムでの使用に適するコヒーレントパルスレーダーシステムは、発生される2個の同じ短パルスを要求する。第1短パルスは送信され、対象物から反射される。第2短パルスは、レーダ送信器からの往復時間に等しい時間だけ遅延する。戻りの送信パルスと混合される第2の遅延短パルスは、ゲートローカル発信器としてレーダーシステムの受信チャンネルで使用され、信号間の位相差を示す直流値を得る。このようなシステムは、対象物の射程及び速度の双方が戻り信号の遅延時間及びいかなるドップラ偏移の双方を分析することにより計測されることを可能にする。

【0013】

第2パルスは、第1パルスがレーダ送信器から目的物へ進み戻る往復時間だけ第1パルスに対して遅延しなければならない。異なる距離で目的物を検出するために、第1パルスに対して第2パルスの時間遅延を正確に変えることが必要である。本発明は、このようなシステムにおいて必要とされる正確に遅延したパルスを提供する簡単で低成本の方法である。

【0014】

このような自動車用レーダーシステムは、代表的には25mmのオーダーの距離で解像するために、約125ピコ秒の時間段階で発生されるパルスを必要とする。このようなパルスが従来のデジタルクロック及び高速カウンタを使用して発生されると、約10GHzの未加工クロック速度が必要である。このようなクロックはコスト高であり、実施するには複雑である。

【0015】

本発明の方法を組み込んだ典型的な一実施形態により、例えば100MHzのトリガライン及びアナログ直流電圧を使用して約5.6ピコ秒 / mVのオフセット時間感度で2ナノ秒までの全オフセット時間で適当なパルスを発生できる。正弦波トリガラインを使用すると、全オフセット時間は、オフセット時間感度の対応する減少で、低い周波数トリガラインを使用することにより増加することができる。平坦又は一定の離間部品を有する鋸歯波、三角波等のより複雑なトリガライン形状により、大きな全オフセット時間が達成できる一方、要求された性能窓に対してオフセット感度を維持する。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照して本発明を説明し、可能な限り、同様の符号は同様の要素を表わす。

【0017】

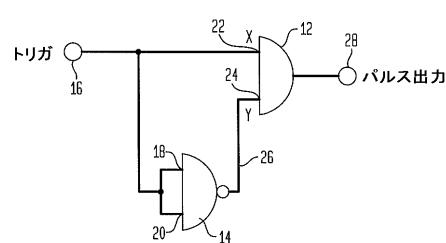

図1は、入力端子16と、出力端子28及び入力端子22, 24を有するANDゲート12と、出力端子26及び入力端子22, 24を有するNANDゲート14とを具備する単純ベースバンドパルス発生器10を示す概略図である。入力端子16は、ANDゲートの入力22及びNANDゲートゲートの入力端子18, 20に接続されている。NANDゲートの出力端子26はANDゲートの入力端子24に接続されている。

【0018】

図2は、単純ベースバンドパルス発生器10の要素、すなわちANDゲート及びNANDゲート要の二進法論理真理表である。ANDゲートは、両方の入力が二進法で1(オン)の場合にのみ二進法で1(オン)を出力する。NANDゲートは、両方の入力が二進法で1(オン)の場合にのみ二進法で0(オフ)を有する。

10

20

30

40

50

## 【0019】

図3は、時間の関数として単純ベースバンドパルス発生器10での3時点での電圧により論理状態を示す。特に、折れ線30は第1ANDゲート入力22でのトリガ電圧の論理状態を示し、折れ線32は第2ANDゲート24での論理状態を示し、折れ線34はANDゲート出力28での論理状態を示す。簡単のために、折れ線は、ANDゲート作動が遅延をもたらさないかのようにNANDゲート作動により生ずるが整合している遅延を示している。この単純化は、本明細書に記載されている作動理論に影響を及ぼさず、図及びその説明を大きく簡素化する。

## 【0020】

$t_0$ の時点で、トリガ電圧は、オフ状態すなわち二進法で0で表わされる。この結果、NANDゲートの両入力18, 20もオフ状態にあるので、NANDゲートの出力26及びANDゲートの入力24はオン状態にある。従って、 $t_0$ の時点で単純ベースバンドパルス発生器10の出力はオフ状態にある。 $t_1$ の時点でトリガ電圧は状態を変え始め、 $t_2$ の時点までに、トリガ電圧はANDゲートの入力22と同様にオン状態になる。NANDゲート20の状態を変化するのに有限の時間を要するので、 $t_2$ の時点で、NANDゲートの出力26及びANDゲートの入力24はオン状態のままである。従って、ANDゲート28は、NANDゲートの出力26が状態を変え始める $t_3$ の時点になって初めてオンに切り換わる。 $t_4$ の時点までにNANDゲートの両入力18, 20がオン状態にあるため、NANDゲートの出力26はオフ状態に切り換わり、ANDゲートの出力28もオフ状態に切り換わる。NANDゲートの出力26はオフ状態のままであるので、入力端子16でのトリガ電圧が $t_5$ の時点でオフに切り換わる場合であっても、ANDゲートの出力28はオフ状態のままである。NANDゲートの出力26がオン状態に切り換わる $t_6$ の時点までに、ANDゲートの入力22はオフ状態にあるので、出力28は継続してオフ状態のままである。この結果、ベースバンドパルス発生器10は、約 $t_5 - t_2$ の著しく大きな時間幅を有する初期パルスから約 $t_3 - t_2$ の時間幅を有する短パルスを発生する。

## 【0021】

好適な一実施形態において、ベースバンドパルス発生器10は、適当な容量負荷を有する差動電流モード論理(CML)(エミッタ結合論理としても知られる)回路として実施される。従来のデジタル論理設計において、 $t_2$ 及び $t_3$ 間の短パルスは、立ち上がり縁、スイッチングの誤作動(グリッチ)であると考えられている。ベースバンドパルスの幅は、ANDゲートの2個の入力22, 24間の差動時間遅延に関係する。ベースバンドパルスの忠実さは論理ゲートのスイッチング速度に関係する。

## 【0022】

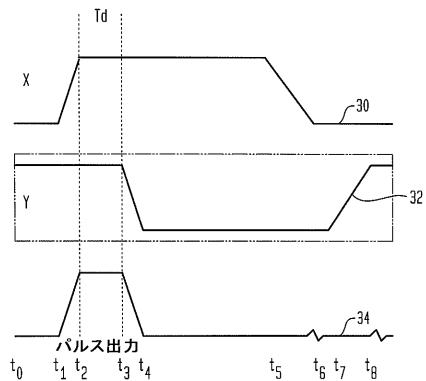

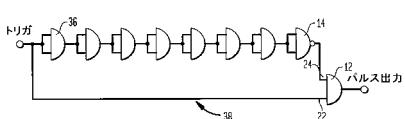

図4は、ANDゲートの2個の入力22, 24間に由来する長い遅延、従って幅広のパルス幅を与えるために追加のANDゲート36を有する実際のベースバンドパルス発生器38を示す概略図である。

## 【0023】

図5は、ベースバンドパルス発生器38のシリコン・ゲルマニウム(SiGe)CMLダイの写真である。SiGe技術は、シリコン及びゲルマニウムの格子構造が4%の寸法差を有するという事実に依拠している。シリコン上に薄いゲルマニウムのエピタキシャル層を成長させることにより、直下のシリコン格子が伸びて、キャリア移動度及びスイッチング速度を大きくする結果となる。このようにして、本質的には従来技術であるシリコン製造技法を用いて、低コストで高速トランジスタがシリコン基板上に製造できる。低コストで高速のトランジスタを提供することに加えて、SiGe技術は、従来の相補型金属酸化膜半導体(CMOS)要素と共に集積回路内に高速トランジスタを含ませることを可能にするという付加的な魅力を有する。

## 【0024】

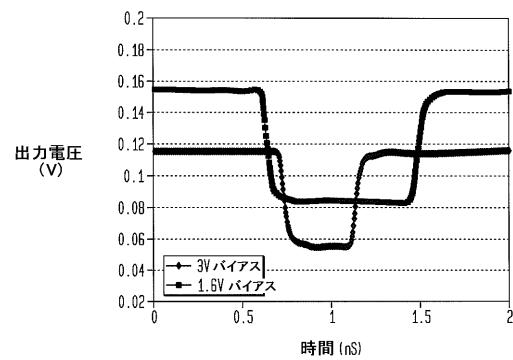

図6は、時間の関数として計測した図4のベースバンドパルス発生器38の差動SiGeCMLの実施の出力電圧を示す。

## 【0025】

10

20

30

40

50

差動ベースバンドパルス発生器（B B P G）38の従来の作動では、差動信号がB B P Gの入力端子に印加される、すなわち入力電圧が実質的に同時であるが位相が180°ずれて変化するので、一方の入力電圧が増加すると、他方が減少する。このようにして、ほぼ一定電流が維持され、高速の差動スイッチングとなる。このような差動回路において、デバイスの平均分子運動エネルギー（K T）に関係する閾値を差動電圧が交差すると、論理回路の状態が変化する。

#### 【0026】

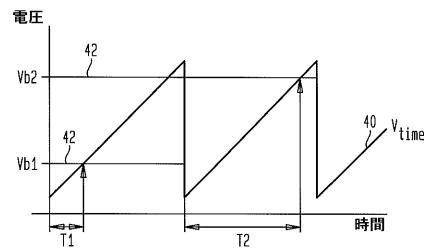

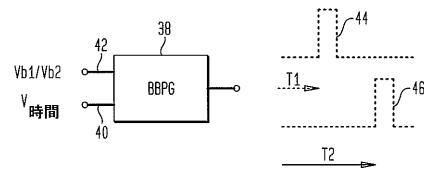

対照的に、図7は、各差動入力端子に非同期電圧を印加することにより、変形比較器モードで作動するよう差動ベースバンドパルス発生器（B B P G）38が形成される、本発明の一実施形態を示す。このようなシステムにおいて、定電圧42を変更することにより、基準時間からのパルスの遅延時間を変化させることができる。これにより、例えばゲートパルス化レーダシステムで必要な変化可能な遅延ゲートパルスを与える単純で正確な方法が提供される。このようなシステムにおける非遅延パルスの往復時間にほぼ等しい時間だけ遅延パルスが遅延すると、異なる距離にある目的物を検出するために異なる時間遅延を必要とする。

#### 【0027】

特に周期的な時間変化電圧40は差動入力の一入力端子に印加されるのに対し、選択可能な値を有する定電圧42は他の入力端子に印加される。定電圧42が低い値Vb1を有する場合、差動電圧は、B B P Gがパルスを発生する時間で周期的な時間変化電圧の最小になった後の遅延時間T1後、ほぼ0になる。定電圧42が高い値Vb2を有する場合、差動電圧は、B B P Gがパルスを発生する時間で周期的な時間変化電圧の最小になった後の遅延時間T2後、ほぼ0になる。

#### 【0028】

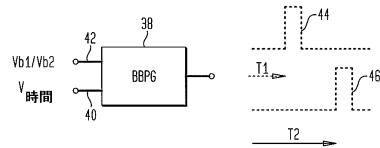

図8は、変形比較器モードで作動すると共に、制御可能に変化するオフセット時間で出力パルスを発生する差動ベースバンドパルス発生器（B B P G）38を示す概略図である。

#### 【0029】

周期的な時間変化電圧は差動B B P G 38の一方の差動入力端子に印加されるのに対し、他方の差動入力端子は定電圧42が保たれる。この定電圧42が低い値Vb1を有する場合、各パルス44が周期的電圧40における基準点からのオフセット時間T1を有する一連のパルス44が発生される。基準点は、例えば正弦波の最小値であってもよい。定電圧42が高い値Vb2を有する場合、各パルス46が大きなオフセット時間T2を有する一連のパルス46が発生される。一定すなわち直流バイアス電圧を変化させることにより、パルスのオフセット時間を制御可能に変化させることができる。

#### 【0030】

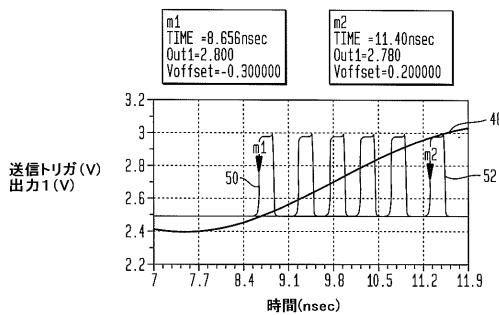

図9は、各々が異なる定電圧42の値により発生された異なる遅延時間有する6個のシミュレーションされたパルスを示す。このグラフは、システムの単一出力を表わすものではなく、定電圧の6個の異なる配列により発生された6個の異なるパルスの出力を組み合わせて重ねたものである。各パルス50は、正弦波48の立ち上がり縁が定電圧51を交差する際に発生されるものとして示される。上述したように、B B P G 38の論理ゲートへの入力は、一方の入力が基準入力であり他方の入力が周期的時間変化トリガ入力である差動トリガ電圧を有すると、回路は比較器として機能する。周期的時間変化トリガ電圧の絶対値レベルが他方の入力の閾値バイアスを交差すると、論理回路は状態を変え、パルスを発生する。図9において、時間変化電圧48は、2.4Vから4Vまで変化する100MHz、0.4Vの正弦波の一部である。タイミングオフセット電圧51は、-0.3Vから+0.2Vまでの範囲にわたって0.1Vきざみで段階があり、図示の6パルスとなる。これにより、5.6ピコ秒/mVのオフセット時間と等価の2.8ナノ秒の全オフセット時間差が提供される。約8.7ナノ秒の最小オフセット時間を有するパルス50は、約-0.3Vのオフセット電圧により発生される。約11.4ナノ秒の最大オフセット時間を有するパルス52は、約0.2Vのオフセット電圧により発生される。

10

20

30

40

50

## 【0031】

正弦波トリガ電圧の最小値に関するパルスのオフセット時間は、トリガラインの振幅と同様にトリガラインの変化（勾配又は周波数のいずれか）の割合の関数である。タイミングジッタ、すなわち発生されたパルスのオフセット時間の変動又はエラーは、定電圧のノイズ（直流バイアスレベルとしても知られる）と同様に例えばトリガラインの信号のいかなる位相ノイズにも関連する。図9の例において、例えば直流バイアス線の2mVノイズ信号は約10ピコ秒のタイミングジッタを発生する。

## 【0032】

変形B B P Gの特定の実施については、所与の温度、直流バイアスレベルが変化できる範囲が固定される。図9の例において、例えば、直流バイアスレベルが変化できる範囲は約500mVに固定される。しかし、周期的時間変化トリガラインの波形の振幅を変化させると、勾配、特にバイアス電圧揺れの両極端で見られる勾配が変化する。従って、振幅変動は、トリガラインの振幅変調（A M）の結果としてタイミングジッタに寄与する。また、振幅変動は直流バイアス電圧のオフセット時間の非線形依存にも寄与する。

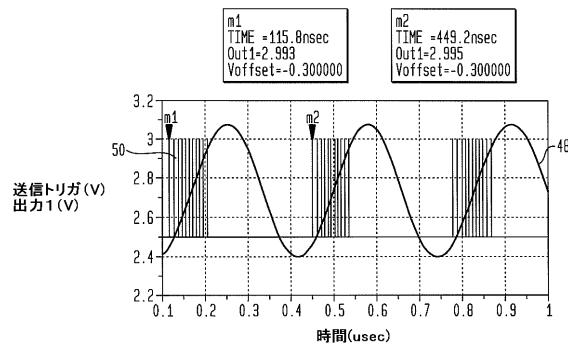

## 【0033】

図10は、典型的な3MHz P R F正弦波トリガ電圧48の3周期に重ねられた、シミュレーションされた一連のパルス50を示す。この正弦波トリガ電圧48は、送信チップ上に送信（Tx）及び受信（Rx）トリガラインの双方に供給できる。パルス50は、異なるオフセット電圧用のベースバンドパルス発生器（B B P G）回路により発生される例えば300ピコ秒のパルスである。上述したように、トリガ電圧48及びバイアスオフセット電圧間の差がB B P Gスイッチング状態のデジタル成分となる閾値を正弦波トリガ電圧48の正の傾斜の縁が交差する毎に、1個のパルスが発生される。閾値は、例えば0.5Vの範囲にわたって50mV刻みでバイアス電圧オフセットを調整することにより調整可能である。これらの典型的な値では、約15mの射程に対応して約100ナノ秒の範囲調整がある。（射程dは、 $d = v \cdot t$ として計算できる。ここで、 $t = 100/2$ ナノ秒、vは光速である。）この100ナノ秒範囲を500ピコ秒刻みでカバーするために、約200の射程ビンを要し、バイアス電圧オフセットは2.5mVの段階の刻みにできることを要する。これは、例えば0~3Vの範囲にわたって作動する、すなわちビット当たり0.7mVを与える12ビットデジタル・アナログコンバータ（D A C）により提供可能である。この例において、要求される電圧段階はレンジビン増分当たり3ビットを可能にする。このようなレーダシステムの一義的な射程は、この例では3MHzであるP R Fにより固定され、次に（マーカーm1およびm2の間の距離として示される）約334ナノ秒である射程間隔となる。これは、約50mの一義的な射程を生み出す。このようなシステムの解像度は、約1ビットのD A Cのノイズ源を仮定することにより見積もることができる。このノイズは、約170ピコ秒のパルスのオフセット時間ジッタとなるか、又はレンジのおよそ1/3となる。170ピコ秒のジッタは、およそ50mmのレンジエラーを与える。

## 【0034】

上述した数字は典型的な数字であり、当業者であれば容易に適当に変えることができる。B B P G回路のパルス幅は、例えば上述した技術を用いて300~102ナノ秒のレンジで選択することができる。

## 【0035】

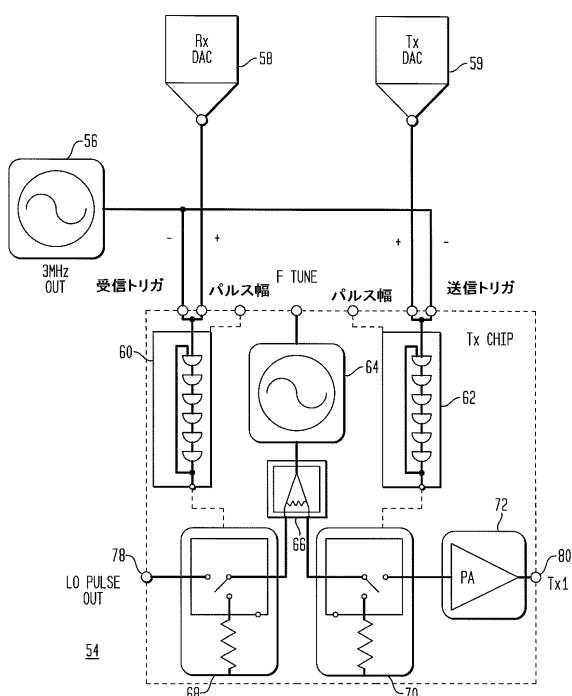

図11は、本発明による高解像度レーダ（H R R）送信及び受信パルス発生器54の典型的な実施形態を示す。このパルス発生器は、正弦波パルス受信周波数P R F発生器56、受信デジタル・アナログコンバータ（R x D A C）58、送信デジタル・アナログコンバータ（T x D A C）59、受信差動ベースバンドパルス発生器（B B P G）60、送信差動B B P G62、送信無線周波数（R F）発生器64、スプリッタ回路66、受信パルス形成器68、送信パルス形成器70及び電力増幅器72を具備する。

## 【0036】

端子80での出力信号は、レーダから対象物まで送信されるコヒーレントなパルス変調信号である。端子78での出力信号は、レーダから対象物までの往復時間に等しい時間だ

10

20

30

40

50

け遅延する、送信信号の低電力コピーである。戻った送信パルス及び遅延したパルスは、それらの間の任意の位相差に比例する直流信号を与えるためにレーダ受信チャンネルで混合される。この混合された信号は、対象物の射程及び速度の双方を得るために使用可能である。

【0037】

正弦波パルス受信周波数P R F発生器56の出力は、受信差動B B P G 6 0及び送信差動B B P G 6 2の各々の一方の入力端子に印加される。受信D A C 5 8の出力は、受信D A C 5 8の他方の入力端子に印加される。送信D A C 5 9の出力は、送信差動B B P G 6 2の他方の入力端子に印加される。

【0038】

受信差動B B P G 6 0により形成される受信パルスの列は、R F発生器64から1個のR F信号を変調する受信パルス形成器68へ供給される。次に、受信パルス形成器68からの変調R F信号は受信パルス出力端子78に供給される。

【0039】

送信差動B B P G 6 2により形成される送信パルスの列は、R F発生器64から1個のR F信号を変調する送信パルス形成器79へ供給される。次に、送信パルス形成器70からの変調R F信号は、送信パルス出力端子80に供給される前に適当な電力増幅器72に供給される。

【0040】

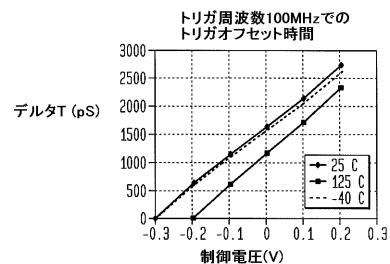

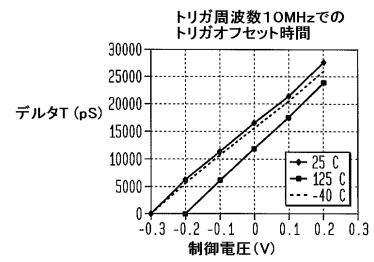

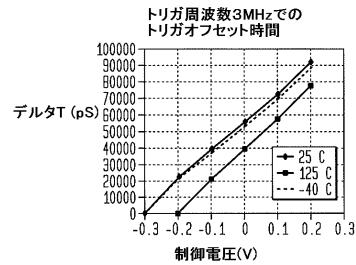

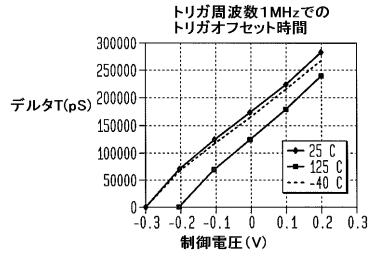

図12は、100MHz P R F用の制御電圧の関数としてピコ秒でのトリガオフセット時間20をとった3本のグラフである。図12の3本のグラフは、異なる3温度、すなわち摂氏25°、摂氏40°及び摂氏125°に対してシミュレーションした結果を表わす。

【0041】

図13ないし図15は、図12と同様のグラフを示すが、P R Fの周波数がそれぞれ10MHz、3MHz及び1MHzのグラフである。

【0042】

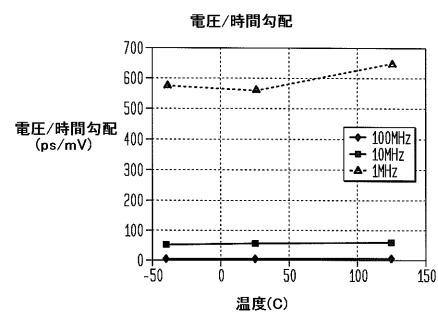

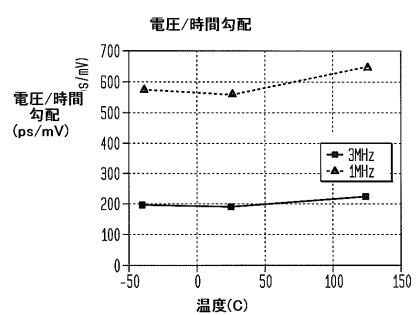

図16は、3通りのパルス繰返し周波数に対して温度の関数としてのオフセット時間の勾配を示す。性能指数は単位がピコ秒/mVである勾配を表わす。これは、100MHz、10MHz、1MHzのP R Fについて摂氏の温度に対してグラフが作成されている。

【0043】

図17は、図16と同様のグラフを示すが、P R Fの周波数が3MHz及び1MHzのグラフである。

【0044】

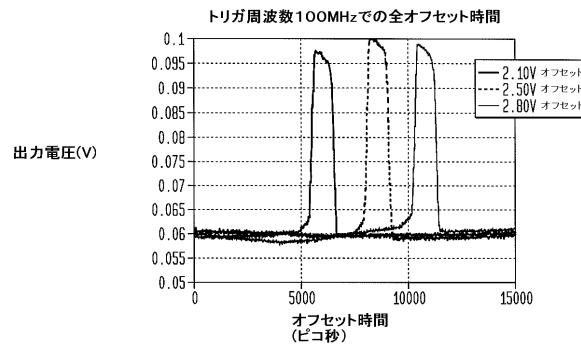

図18は、ベースバンドパルス発生器38の差動SiGe C M Lの実施の計測結果を示す。直流オフセットバイアス電圧は一方の差動入力に印加され、100MHz正弦波低位相ノイズは他方の差動入力に印加され、正弦波は+10dBmに固定されている。出力パルスのグラフは、直流オフセットバイアス電圧の3個の値、すなわち2.1V、2.5V及び2.8Vに対して示される。計測は10MHz基準を使用して起動され、この基準信号に対するオフセット時間は、種々の直流オフセットバイアス電圧の絶対遅延時間として記録された。

【0045】

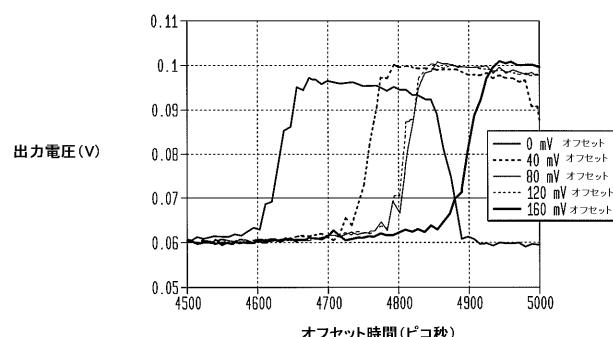

図19は、同じ100MHz正弦波を有するベースバンドパルス発生器38の差動SiGe C M Lの実施の別の計測結果を示す。図19において、微小オフセット時間は、直流オフセットバイアス電圧の微小段階を使用して得られる。270ピコ秒の遅延は、160mVの直流オフセットバイアス電圧を使用して得られる。図19において明白な計測ジッタは、部分的には印加された直流オフセット電圧の変化を生ずるバイアスラインの接触プローブの接触抵抗の小さな変化のためであり、部分的には10MHz基準波形の若干の変動のためである。結果が示すように、125ピコ秒の微小オフセット時間有する100MHzの立ち上がり時間のトリガラインは達成可能である。

【0046】

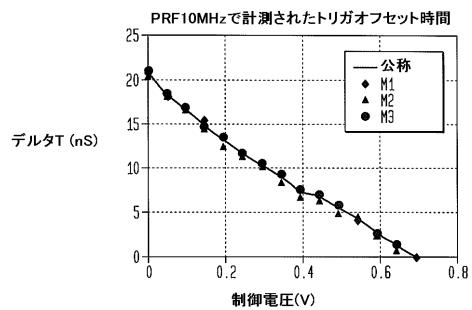

図20は、10MHz正弦波に対して制御電圧の関数としてのオフセット時間を示す。3連

10

20

30

40

50

統計測は、計測の散らばりを示す。

【0047】

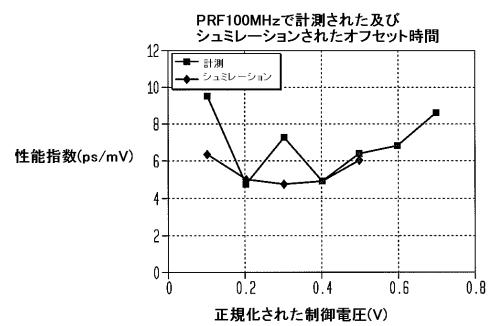

図21は、100MHzトリガ周波数に対して計測結果及びシミュレーション結果の比較を示す。Ps/mVとして表わされる性能指數の形態の時間偏移勾配は、正規化された制御電圧すなわち直流オフセットバイアス電圧に対してグラフが作成されている。計測データにはいくらか散らばりがあるが、シミュレーション結果及び計測結果はかなりよく一致する。

【0048】

図示の結果は1MHz～100MHzでの結果であるが、10kHzまで及び10GHzまでの周波数を含む他の周波数範囲で上述のシステム及び方法が適用できることを当業者であれば容易に理解されよう。

10

【0049】

上述した多くの特定結果が主に正弦波形を使用して示されたが、上述のシステム及び方法が鋸歯波形、三角波形、平坦又は一定間隔成分を有する三角波形などの他の周期的波形を操作するために容易に適合可能であることを当業者であれば容易に理解されよう。

【図面の簡単な説明】

【0050】

【図1】単純ベースバンドパルス発生器を示す概略図である。

【図2】単純ベースバンドパルス発生器の要素用の論理真理表である。

【図3】時間の関数として図1の単純ベースバンドパルス発生器内の3時点での電圧を示すタイミングチャートである。

20

【図4】ベースバンドパルス発生器の一実施形態を示す概略図である。

【図5】差動ベースバンドパルス発生器を実施するSiGe CMLのダイを示す写真である。

【図6】時間の関数として差動ベースバンドパルス発生器のSiGe CMLの実施の計測された出力電圧を示すタイミングチャートである。

【図7】出力パルスの時間的なタイミングを変化させることができる比較モードでの作動用の差動ベースバンドパルス発生器に印加される入力電圧を示すタイミングチャートである。

【図8】変形比較器モードで作動すると共に、変化する時間的オフセットで出力パルスを発生するベースバンドパルス発生器を示す概略図である。

30

【図9】6個のオフセット遅延により発生される6個の時間的オフセットパルス、及び正弦波電圧の立ち上がりエッジのシミュレーションを示すタイミングチャートである。

【図10】正弦波トリガラインの3周期の正弦波、及び複数のバイアスオフセット電圧により発生される時間的オフセットパルスを示すタイミングチャートである。

【図11】高解像レーダ送信及び受信パルス発生器の代表的実施を示す概略図である。

【図12】種々のトリガライン用のシミュレーション結果を示すグラフである。

【図13】種々のトリガライン用のシミュレーション結果を示すグラフである。

【図14】種々のトリガライン用のシミュレーション結果を示すグラフである。

【図15】種々のトリガライン用のシミュレーション結果を示すグラフである。

【図16】温度に対する種々のトリガラインの性能指數対温度のシミュレーション結果を示すグラフである。

40

【図17】温度に対する種々のトリガラインの性能指數対温度のシミュレーション結果を示すグラフである。

【図18】時間の関数として種々のオフセット電圧用に計測されたパルス幅を示すタイミングチャートである。

【図19】時間の関数として種々のオフセット電圧用に計測されたパルス幅を示すタイミングチャートである。

【図20】制御電圧の関数としての計測されたパルスオフセット時間を示すグラフである。

【図21】計測された性能指數と、正規化された制御電圧に対する性能指數のシミュレー

50

ションとの比較を示すグラフである。

【符号の説明】

【0 0 5 1】

1 2 A N D ゲート

1 4 N A N D ゲート

3 6 第2差動A N D ゲート

3 8 , 6 0 , 6 2 差動ベースバンドパルス発生器

4 0 周期的電圧電源

4 2 定電圧電源

【図 1】

【図 2】

|   |   | AND | NAND |

|---|---|-----|------|

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

| 0 | 0 | 0   | 1    |

【図 3】

【図 4】

【図5】

【図6】

【図9】

【図10】

【図7】

【図8】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

F ターム(参考) 5J070 AB01 AC02 AE01 AF03 AK02 AK22