(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4573921号

(P4573921)

(45) 発行日 平成22年11月4日(2010.11.4)

(24) 登録日 平成22年8月27日(2010.8.27)

|               |                           |

|---------------|---------------------------|

| (51) Int.Cl.  | F 1                       |

| HO 1 L 21/324 | (2006.01) HO 1 L 21/324 R |

| HO 1 L 21/316 | (2006.01) HO 1 L 21/324 P |

| HO 1 L 21/365 | (2006.01) HO 1 L 21/324 Z |

| HO 1 L 29/78  | (2006.01) HO 1 L 21/316 X |

|               | HO 1 L 21/316 P           |

請求項の数 5 (全 15 頁) 最終頁に続く

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願平11-12664                  |

| (22) 出願日  | 平成11年1月21日(1999.1.21)        |

| (65) 公開番号 | 特開2000-216165(P2000-216165A) |

| (43) 公開日  | 平成12年8月4日(2000.8.4)          |

| 審査請求日     | 平成18年1月13日(2006.1.13)        |

|           |                                                           |

|-----------|-----------------------------------------------------------|

| (73) 特許権者 | 308014341<br>富士通セミコンダクター株式会社<br>神奈川県横浜市港北区新横浜二丁目10番<br>23 |

| (74) 代理人  | 100105337<br>弁理士 真鍋 深                                     |

| (74) 代理人  | 100072833<br>弁理士 柏谷 昭司                                    |

| (74) 代理人  | 100075890<br>弁理士 渡邊 弘一                                    |

| (74) 代理人  | 100110238<br>弁理士 伊藤 喬郎                                    |

| (72) 発明者  | 佐藤 豪一<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内               |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコンからなる基体上に堆積したゲート酸化膜上にゲート電極を形成したのち、触媒からなる抵抗発熱体に窒素含有ガスを吹きつけ、前記抵抗発熱体と窒素含有ガスとの接触反応によって窒素含有ガスの少なくとも一部を分解し、分解によって生成された活性種の雰囲気中に前記ゲート酸化膜を晒すことを特徴とする半導体装置の製造方法。

## 【請求項 2】

前記酸化膜が、SiO<sub>2</sub>膜、SiON膜、或いは、CeO<sub>2</sub>膜の内のいずれかであることを特徴とする請求項1記載の半導体装置の製造方法。

## 【請求項 3】

前記ゲート電極の側壁に側壁酸化膜を形成した後に、再び前記分解によって生成された活性種の雰囲気中に前記側壁酸化膜を晒すことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

## 【請求項 4】

前記側壁酸化膜が、SiO<sub>2</sub>膜、SiON膜、或いは、TEOS-NSG膜の内のいずれかであることを特徴とする請求項3記載の半導体装置の製造方法。

## 【請求項 5】

前記窒素含有ガスが、アンモニア、アジ化水素、窒素、窒素ハロゲン化物、或いは、窒素酸化物の内のいずれかであることを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は半導体装置の製造方法に関するものであり、特に、半導体基板と絶縁膜との界面状態及び絶縁膜の膜質を改善するための熱処理方法に特徴のある半導体装置の製造方法に関するものである。

**【0002】****【従来の技術】**

近年の半導体集積回路装置の高集積化、微細化の進展に伴い、半導体集積回路装置を構成するMISFET（金属-絶縁体-半導体FET）も微細化が要求され、微細化に伴って低電圧化が要請されるためにゲート絶縁膜の厚さを薄くする必要が生じるが、ゲート絶縁膜として従来のMISFETの様にSiO<sub>2</sub>膜を用いた場合、SiO<sub>2</sub>膜を4nm程度まで薄膜化すると、膜厚の均一性の保持が難しくなるのに加え、リーク電流の増大やゲート電極にドープする不純物がチャネル領域に突き抜ける現象などが顕在化し、MISFETの特性に深刻な影響を及ぼすようになってきた。

10

**【0003】**

この様な問題を解決するために、ゲート絶縁膜として、SiO<sub>2</sub>膜の代わりにSiO<sub>2</sub>膜より比誘電率の大きなシリコン窒化膜（SiN<sub>x</sub>膜、化学量論比的にはSi<sub>3</sub>N<sub>4</sub>膜）や、SiON膜の適用が検討されている。

即ち、SiN膜或いはSiON膜は比誘電率が大きいので、SiO<sub>2</sub>膜より厚い膜厚のSiN膜或いはSiON膜を用いても、同等のゲート特性を得ることができるためである。

20

**【0004】**

従来のSiON膜の作製方法としては、N<sub>2</sub>Oガスを用いたものや、熱酸化膜を形成したのち、高温の窒素雰囲気中に基板をさらす方法が用いられているが、これらのプロセスは、いずれも800以上の中温プロセスであるため、この様な高温プロセスによってゲート絶縁膜となるSiON膜を形成した場合には、しきい値電圧V<sub>th</sub>調整用にチャネル領域にドープした不純物をSiN膜の堆積工程において再分布させることになり、短チャネル効果の悪化、即ち、ソース-ドレイン領域間のパンチスルーや誘発することになる。

また、この様な高温プロセスは、近年のウェハの大口径化に対しては、ウェハの反りをもたらし、加工精度の低下を引き起こすという問題もある。

30

**【0005】**

この様な高温プロセスの問題点に鑑み、低温プロセスであるプラズマCVD（PCVD）法やJVD（Jet Vapor Deposition）法の適用が試みられており、例えばYale大学、Jet Process Corp.、或いは、モトローラ社においては、EOT（Equivalent Oxide Thickness：等価酸化膜厚）換算で、2~5nmのSiN膜をJVD法で成膜することが研究されており、特に、モトローラ社においては、0.35μmデバイスへの応用研究が行われ、良好な結果を示している。

なお、EOT（等価酸化膜厚）とは、比誘電率をSiO<sub>2</sub>膜と同じ3.9であるとして、C-V特性から算出した絶縁膜の膜厚である。

40

**【0006】**

また、本発明者の一人である松村等は、低温プロセス化のために触媒CVD法を用いたシリコン系薄膜の堆積方法を提案しており（例えば、特開平8-250438号公報、特開平10-83988号公報、或いは、応用物理、Vol.66, No.10, pp.1094-1097, 1997参照）、また、本発明者の一人である和泉は、触媒CVD装置を用いた基板表面の窒化法を提案している（Applied Physics Letters, Vol.71, No.10, pp.1371-1372, September, 1997参照）。

**【0007】**

しかし、この様なPCVD法、JVD法、或いは、触媒CVD法によって成膜したSiN

50

膜或いはSiON膜は、堆積しただけでは膜質が必ずしも良くなく、C-V特性においてヒステリシスループが見られるという問題がある。このC-V特性においてヒステリシスループが見られるということは、Si/SiN界面或いはSi/SiON界面に活性な多数のダングリング・ボンドが存在し、チャネル特性に影響を与えるということを意味する。

【0008】

したがって、この様な低温SiON膜等の低温成長絶縁膜の膜質を改善するためには、800程度の高温におけるN<sub>2</sub>雰囲気中でアニールを行う必要が生じ、結局は全体としては高温プロセスになってしまうことになる。

【0009】

さらに、低温SiON膜の膜質を改善するために、プラズマプロセスを用いてSiON膜内へ窒素を導入することも検討されているが、プラズマによるSiON膜へのダメージ、或いは、シリコン基板へのダメージが懸念されている。

【0010】

一方、ゲート絶縁膜としてSiO<sub>2</sub>膜等の酸化膜を用いた場合にも、しきい値電圧V<sub>th</sub>調整用にチャネル領域にドープした不純物の再分布による短チャネル効果の悪化、即ち、ソース-ドレイン領域間のパンチスルーを防止するためには、SiO<sub>2</sub>膜等の酸化膜を低温で堆積させる必要があるが、そうすると上述の様にSi/SiO<sub>2</sub>膜の界面に多数の活性なダングリング・ボンドが発生し、チャネル特性に影響を与えるという問題が発生する。

【0011】

そこで、本発明者は、この様な事情を前提として、低温成膜したSiN膜の膜質を改善するための低温アニール方法を提案しているので、以下に説明する。

まず、(100)面を主面とするn型シリコン基板の表面をRCA洗浄によって清浄化したのち、触媒CVD装置内において、n型シリコン基板の温度を300とした状態で、原料ガスとしてSiH<sub>4</sub>を1.1sccm、NH<sub>3</sub>を50~60sccm流して真空容器内のガス圧を0.01Torrとし、n型シリコン基板との間隔が3.7cmとなるように配置したタンゲステン触媒体に交流電源から680Wの交流電力を投入して1800~1900に加熱し、この加熱されたタンゲステン触媒体にNH<sub>3</sub>及びSiH<sub>4</sub>を接触させることによってNH<sub>3</sub>及びSiH<sub>4</sub>を分解して活性種を生成し、この活性種をn型シリコン基板の表面で反応させることによってSiN膜を堆積させる。

【0012】

引き続いて、同じ真空容器内で(in-situ)、SiH<sub>4</sub>の供給を停止し、NH<sub>3</sub>のみを50~60sccm供給してガス圧を0.013Torrとした以外は成膜工程と同じ条件で、活性種を生成し、この活性種を含む雰囲気中でSiN膜を、例えば、1時間熱処理することによって改質されたSiN膜を形成する。

なお、この場合の活性種は、NH<sub>3</sub>が分解して形成された各種のラジカル等から構成されており、その中でも、Nラジカルが最も多く、次いで、N<sub>2</sub>ラジカルが多いものである。

【0013】

この場合、NH<sub>3</sub>による触媒アニール処理を行わない前のSiN膜のEOTは4.06nmと見積もられ、また、界面準位密度D<sub>u</sub>は8.63×10<sup>11</sup>cm<sup>-2</sup>eV<sup>-1</sup>であるのに対して、NH<sub>3</sub>による触媒アニール処理を行った後のSiN膜のEOTは3.80nmと見積もられ、履歴特性も改善されており、また、界面準位密度D<sub>u</sub>は3.53×10<sup>11</sup>cm<sup>-2</sup>eV<sup>-1</sup>と処理前の1/2以下に低減していた。

【0014】

また、NH<sub>3</sub>が分解されて生成した活性種中の低温アニール処理前のEOTが2.97nmのSiN膜のリーク電流に比べて、低温アニール処理後のEOTが2.78nmのSiN膜においては、2桁以上電流密度が小さくなっている。また、絶縁耐圧も向上している。

【0015】

一方、この様な高温プロセスやプラズマのダメージを伴わない絶縁膜の他の形成方法とし

10

20

30

40

50

て、低温プロセスで絶縁膜を成膜したのち触媒で活性化したガス雰囲気中で400～700の温度でアニールすることが提案されている（例えば、特開平8-78695号公報参照）。

#### 【0016】

この提案においては、熱処理を行う反応室内、或いは、それとは独立の反応室内にメッシュ状の触媒を配置し、原料ガスをメッシュ状の触媒を透過させることによって活性化し、活性化した活性種、即ち、ラジカルにより結晶性Si膜/酸化珪素膜界面のシリコン-水素結合(Si-H)をシリコン-窒素結合(Si-N)に置き換えることによって、酸化膜の膜質を改善しようとするものであり、全体を700以下の低温プロセスで行うことができる。

10

#### 【0017】

例えば、上記提案においては、TFTを構成する結晶性Si膜の表面にプラズマCVD法によってゲート絶縁膜となる厚さ20～150nm、例えば、100nmの酸化珪素膜を堆積させたのち、反応室内に水素を導入し、350で2時間アニールしたのち、200～600の温度において触媒となる還元ニッケル網によって活性化したN<sub>2</sub>Oを反応室内に導入し、400～700において1時間熱処理を行うことによって、酸化珪素膜中、及び、酸化珪素膜と結晶性Si膜の界面における水素を酸化或いは窒化によって減少させて酸化珪素膜の膜質及び界面の特性を向上することが開示されている。

20

#### 【0018】

また、上記提案においては、TFTを構成する結晶性Si膜の表面にスパッタリング法によってゲート絶縁膜となる厚さ20～150nm、例えば、100nmの酸化珪素膜を堆積させたのち、触媒となる白金網によって活性化したN<sub>2</sub>Oを用いて500～650において1時間熱処理を行うことによって、酸化珪素膜中、及び、酸化珪素膜と結晶性Si膜の界面における水素を酸化或いは窒化によって減少させて酸化珪素膜の膜質及び界面の特性を向上することが開示されている。

30

#### 【0019】

さらに、上記提案においては、TFTを構成する結晶性Si膜の表面にECR-CVD法によってゲート絶縁膜となる厚さ120nmの酸化珪素膜を堆積させたのち、触媒となるTiを吸着させた粒状或いは粉状のシリカゲルによって、Arによって1～5%に希釈されたNH<sub>3</sub>を活性化し、1時間のアニールを施すことによって酸化珪素膜を窒化し、次いで、触媒によって活性化したN<sub>2</sub>Oを用いて500～650において1時間熱処理を行うことによって、窒化された酸化珪素膜と結晶性Si膜の界面の特性を向上することが開示されている。

#### 【0020】

##### 【発明が解決しようとする課題】

しかし、上述の触媒CVD装置を用いたNH<sub>3</sub>の活性種による低温熱処理の場合には、SiN膜の膜質の改善或いは界面状態の改善についてしか開示されておらず、SiO<sub>2</sub>膜等の他の絶縁膜の膜質或いは界面状態の改善については示唆されていないものである。

30

#### 【0021】

また、特開平8-78695号公報に記載されている触媒で活性化したガスを用いて低温アニールする方法の場合には、基本的には窒化による膜質或いは界面状態の改善を前提としているが、PCVD法やECR-CVD法によって堆積した酸化珪素膜を、メッシュ状或いは粒状の触媒を備えた別の反応室内で400～700の温度で熱処理するものであり、製造装置系の構成が複雑化するとともに、低温プロセスといつても400以上の温度を必要とするという問題がある。

40

#### 【0022】

したがって、本発明は、低温で成膜した絶縁膜を低温アニールによって改質し、また、製造装置系の構成を簡素化することを目的とする。

#### 【0023】

##### 【課題を解決するための手段】

50

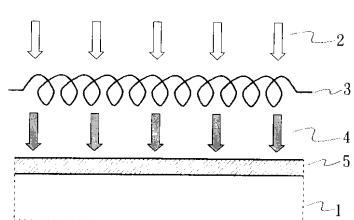

図1は本発明の原理的構成の説明図であり、この図1を参照して本発明における課題を解決するための手段を説明する。

図1参照

(1) 本発明は、半導体装置の製造方法において、シリコンからなる基体1上に堆積したゲート酸化膜上にゲート電極を形成したのち、触媒からなる抵抗発熱体3に窒素含有ガスを吹きつけ、抵抗発熱体3と窒素含有ガスとの接触反応によって窒素含有ガスの少なくとも一部を分解し、分解によって生成された活性種4の雰囲気中にゲート酸化膜を晒すことを特徴とする。

【0027】

(2) また、本発明は、上記(1)において、酸化膜が、 $\text{SiO}_2$ 膜、 $\text{SiON}$ 膜、或いは、 $\text{CeO}_2$ 膜の内のいずれかであることを特徴とする。 10

【0028】

この様に、触媒からなる抵抗発熱体3により活性化した活性種4を用いて $\text{SiO}_2$ 膜、 $\text{SiON}$ 膜、或いは、 $\text{CeO}_2$ 膜等の酸化膜をアニールすることによって、例えば、300以下の低温プロセスのみで、基体1-酸化膜の界面にNを導入することができ、それによって、界面のダングリング・ボンドをNによって終端させて界面特性を改善することができる。

また、触媒を抵抗発熱体3によって構成することによって、触媒をアニール処理装置内に設けることができ、それによって、製造装置系を簡素化することができる。

なお、本発明における基体1とは、シリコン基板、基板上に成膜したシリコン堆積層、或いは、金属を意味するものである。 20

【0029】

特に、活性種4の雰囲気中における低温アニール処理をゲート電極の形成後に行うことによって、PMA(ポスト・メタル・アニール)工程を兼ねることができ、それによって、製造工程数を低減することができる。

【0030】

(3) また、本発明は、上記(1)または(2)において、ゲート電極の側壁に側壁酸化膜を形成した後に、再び分解によって生成された活性種4の雰囲気中に前記側壁酸化膜を晒すことを特徴とする。 30

【0031】

この様に、活性種4の雰囲気中における界面の窒化処理を、ゲート電極の側壁に側壁酸化膜、即ち、サイドウォールを形成した後に行うことによって、ゲート電極の両側のサイドウォールとシリコン基板との界面の特性を改善することができ、それによって、耐圧を改善することができる。

【0032】

(4) また、本発明は、上記(3)において、側壁酸化膜が、 $\text{SiO}_2$ 膜、 $\text{SiON}$ 膜、或いは、TEOS(Tetra-Ethyl-Ortho-Silicate)-NSG(Non-Doped Silicate Glass)膜の内のいずれかであることを特徴とする。

【0033】

(5) また、本発明は、上記(1)乃至(5)のいずれかにおいて、窒素含有ガスが、アンモニア、アジ化水素、窒素、窒素ハロゲン化物、或いは、窒素酸化物の内のいずれかであることを特徴とする。 40

【0034】

この様に、界面に窒素を導入する触媒アニール工程に用いる窒素含有ガスとしては、アンモニア( $\text{NH}_3$ )、アジ化水素( $\text{HN}_3$ )、窒素、 $\text{NHC}_1$ 等の窒素ハロゲン化物、或いは、 $\text{N}_2\text{O}$ 、 $\text{NO}$ 、 $\text{NO}_2$ 等の窒素酸化物のいずれを用いても良い。

【0036】

【発明の実施の形態】

ここで、本発明の各実施の形態を説明するが、各実施の形態の製造工程を説明する前に、

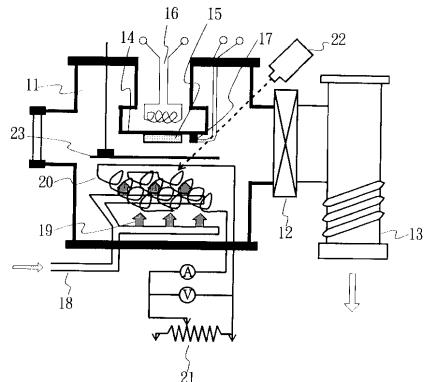

図2を参照して、本発明の実施の形態に用いる触媒CVD装置を説明する。

図2参照

図2は、本発明の各実施の形態に用いる触媒CVD装置の概念的構成図であり、反応室となる真空容器11には弁12を介して拡散ポンプ13が接続されており、この拡散ポンプ13によって反応生成物或いは未反応の原料ガス19が排気される。

【0037】

また、真空容器11の上部中央には、基板ホルダー14が設けられており、この基板ホルダー14にはサセプタ等によって保持された試料15が固着されており、また、基板ホルダー14の凹部には試料を加熱するためにヒーター16が設けられており、試料15の温度は熱電対17によって監視される。

10

【0038】

また、試料15に対向するように、原料ガス19を吹き出すためのノズルを有するガス供給管18及びタングステン触媒体20を配置し、両者の間にシャッター23を設けておき、タングステン触媒体20には交流電源21から、700W程度、例えば、680Wの交流電力が供給され、タングステン触媒体20の抵抗発熱体線温度は1800～1900程度の高温になる。

なお、タングステン触媒体20の抵抗発熱体線温度は、コイル状のタングステン触媒体20の電気抵抗の温度依存性からまず見積もられるが、真空容器11に設けた石英窓(図示せず)を介して電子式の赤外放射温度計22によって見積もられる。

【0039】

20

この高温のタングステン触媒体20に原料ガス19が吹きつけられて、原料ガス19とタングステン触媒体20とが接触することによって、原料ガス19が分解してラジカル等の活性種が形成され、シャッター23を開きこの活性種を含む雰囲気中に試料15が晒されることによって、成膜或いはアニール処理が行われる。

なお、この場合、タングステン触媒体20からの熱輻射による基板温度の上昇が危惧されるが、試料15とタングステン触媒体20との間の距離を5cm程度とした場合には、熱輻射による温度上昇は数10以内であるので、低温化の観点からは問題とならない(必要ならば、応用物理, Vol. 66, No. 10, pp. 1094-1097, 1997参照)。

【0040】

30

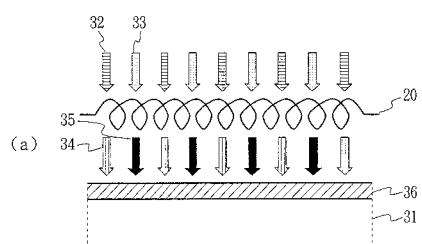

次に、図3及び図4を参照して、本発明の前提となる参考例1を説明するが、まず、図3を参照して、本発明の前提となる参考例1の製造工程を説明する。

図3(a)参照

まず、(100)面を正面とするn型シリコン基板31の表面をRCA洗浄によって清浄化したのち、図2に示した触媒CVD装置内において、n型シリコン基板31の温度を300とした状態で、原料ガス19としてSiH<sub>4</sub>33を1.1sccm、NH<sub>3</sub>32を50～60sccm流して真空容器11内のガス圧を0.01Torrとし、n型シリコン基板31との間隔が3.7cmとなるように配置したタングステン触媒体20に交流電源21から680Wの交流電力を投入して1800～1900に加熱し、この加熱されたタングステン触媒体20にNH<sub>3</sub>32及びSiH<sub>4</sub>33を接触させることによってNH<sub>3</sub>32及びSiH<sub>4</sub>33を分解して活性種34, 35を生成し、この活性種34, 35をn型シリコン基板31の表面で反応させることによって、厚さが、例えば、5nmのNリッチのSiON膜36が堆積される。

40

なお、この場合、SiN膜ではなくSiON膜36が形成される理由は必ずしも明らかではないが、配管ガス等に混入したO<sub>2</sub>が原因であると推測される。

【0041】

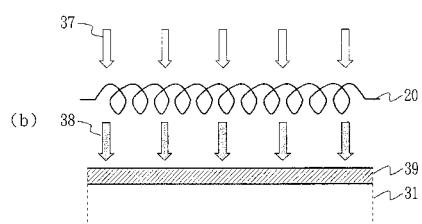

図3(b)参照

引き続いて、同じ真空容器11内で(in-situ)、NH<sub>3</sub>32及びSiH<sub>4</sub>33の供給を停止し、H<sub>2</sub>37を50sccm供給してガス圧を0.01Torrとした以外は成膜工程と同じ条件で、活性種38を生成し、この活性種38を含む雰囲気中でSiON

50

膜 3 6 を、例えば、10 分間熱処理することによって改質された SiON 膜 3 9 を形成する。

なお、この場合の活性種 3 8 は、H<sub>2</sub> 3 7 が分解して形成されたラジカル等から構成されている。

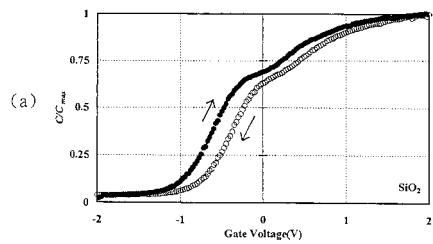

【0042】

次に、図 4 を参照して、本発明の前提となる参考例 1 の H<sub>2</sub> 処理による界面状態の改善効果を説明する。

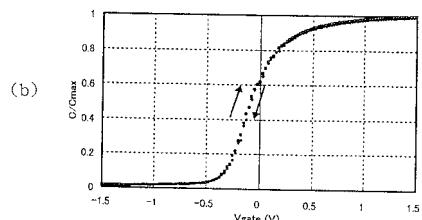

図 4 ( a ) 参照

図 4 ( a ) は、H<sub>2</sub> による触媒アニール処理を行わない前の SiON 膜 3 6 の C - V 特性を示す図であり、C - V 特性にヒステリシスループが見られるので、n 型シリコン基板 3 1 と SiON 膜 3 6 との界面に活性なダングリング・ボンド等が発生し、界面準位密度が高密度になっていることが理解される。

【0043】

図 4 ( b ) 参照

図 4 ( b ) は、H<sub>2</sub> による触媒アニール処理を行った後の SiON 膜 3 9 の C - V 特性を示す図であり、この C - V 特性にヒステリシスループがほとんど見られないので、ダングリング・ボンドが活性化した水素によって終端され、界面準位密度が大幅に低減していることが理解される。

なお、これらの C - V 特性の測定に際しては、A 1 電極を形成するだけで、PMA 処理は行っていない。

【0044】

この様に、H<sub>2</sub> を触媒からなる抵抗発熱体によって分解して生成した活性種中での低温アニール処理によって、n 型シリコン基板 / SiON 膜界面のダングリング・ボンドが H によって終端されるので界面準位密度を大幅に低減することができ、それによって、リーク電流が減少し、且つ、絶縁耐圧も向上するので、特性の優れた MISFET を製造することができる。

【0045】

また、参考例 1 の場合には、この様な触媒アニール処理を 400 未満の低温で、特に、300 以下の低温において行うことができるので、しきい値電圧制御のためにチャネル領域に注入した不純物の再分布を抑制することができ、短チャネル効果の悪化を防止することができる。

【0046】

なお、この様な 400 未満でのアニール処理によっても SiON 膜の界面状態の改質が可能になる理由は、必ずしも明らかでないが、従来例のような単なるメッシュ状の触媒ではなく、1800 ~ 1900 の高温になった抵抗発熱体のタンゲステン触媒体 20 を用いたことにより、H<sub>2</sub> が効率的に分解されるためと考えられる。

【0047】

また、参考例 1においては、触媒アニール処理を行う SiON 膜を触媒 CVD 法によって成膜し、且つ、同じ装置内で引き続いて (in-situ) 触媒アニール処理を行っているので、成膜装置とアニール装置を共通化することができ、さらに、触媒として抵抗発熱体を用いているので、触媒をアニール装置内に設けることができ、それによって、製造装置系の構成を簡素化することができる。

【0048】

次に、図 5 を参照して本発明の前提となる参考例 2 を説明するが、H<sub>2</sub> 処理の条件は上記の参考例 1 と同様であるので、製造工程の図示は省略する。

まず、(100) 面を正面とする n 型シリコン基板の表面を RCA 洗浄によって清浄化したのち、n 型シリコン基板の温度を 50 とした状態で、スパッタリング法によって厚さが 10 nm の SiO<sub>2</sub> 膜を堆積させる。

【0049】

次いで、図 2 に示した触媒 CVD 装置を用いて、n 型シリコン基板の温度を 300 とし

10

20

30

40

50

た状態で、原料ガスとして  $H_2$  を 50 sccm 供給して真空容器内のガス圧を 0.01 Torr とし、n 型シリコン基板との間隔が 3.7 cm となるように配置したタンゲステン触媒体に交流電源から 680 W の交流電力を投入して 1800 ~ 1900 に加熱し、この加熱されたタンゲステン触媒体に  $H_2$  を接触させて活性種を生成し、この活性種を含む雰囲気中で  $SiO_2$  膜を、例えば、10 分間熱処理することによって改質された  $SiO_2$  膜を形成する。

【0050】

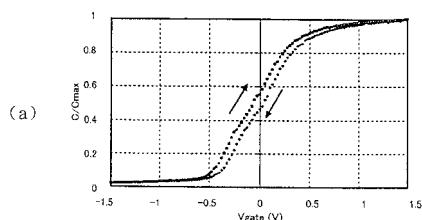

図 5 (a) 参照

図 5 (a) は、 $H_2$  による触媒アニール処理を行わない前の  $SiO_2$  膜の C - V 特性を示す図であり、C - V 特性にヒステリシスループが見られるので、n 型シリコン基板と  $SiO_2$  膜との界面に活性なダングリング・ボンド等は発生し、界面準位密度が高密度になっていることが理解される。

10

【0051】

図 5 (b) 参照

図 5 (b) は、 $H_2$  による触媒アニール処理を行った後の改質された  $SiO_2$  膜の C - V 特性を示す図であり、この C - V 特性にヒステリシスループがほとんど見られないので、ダングリング・ボンドが活性化した水素によって終端され、界面準位密度が大幅に低減していることが理解され、また、C - V 特性の形状自体からは、膜質も改善されていることが理解される。

なお、これらの C - V 特性の測定に際しては、Al 電極を形成するだけで、PMA 処理は行っていない。

20

【0052】

この様に、 $H_2$  処理の効果は、 $SiO_2$  膜に対しても効果的であることが理解され、したがって、ゲート酸化膜として  $SiO_2$  膜を用いた場合にも、触媒によって活性化した  $H_2$  による低温処理によって、チャネルドープした不純物を再分布させることなく界面準位密度を大幅に低減することができ、それによって、リーク電流が減少し、且つ、絶縁耐圧も向上するので、特性の優れた MOSFET を製造することができる。

【0053】

次に、図 6 を参照して本発明の前提となる参考例 3 を説明するが、 $H_2$  処理の条件は上記の参考例 1 と同様であるので、製造工程の図示は省略する。

30

まず、(111) 面を正面とする p 型シリコン基板の表面を RCA 洗浄によって清浄化したのち、p 型シリコン基板の温度を 600 とした状態で、スパッタリング法によって厚さが 20 nm の  $CeO_2$  膜を堆積させる。

【0054】

次いで、図 2 に示した触媒 CVD 装置を用いて、p 型シリコン基板の温度を 300 とした状態で、原料ガスとして  $H_2$  を 50 sccm 供給して真空容器内のガス圧を 0.01 Torr とし、p 型シリコン基板との間隔が 3.7 cm となるように配置したタンゲステン触媒体に交流電源から 680 W の交流電力を投入して 1800 ~ 1900 に加熱し、この加熱されたタンゲステン触媒体に  $H_2$  を接触させて活性種を生成し、この活性種を含む雰囲気中で  $CeO_2$  膜を、例えば、10 分間熱処理することによって改質された  $CeO_2$  膜を形成する。

40

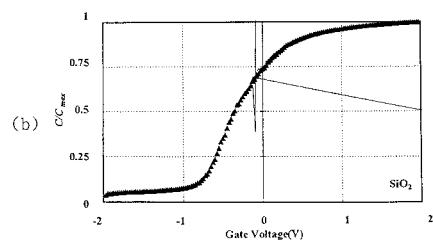

【0055】

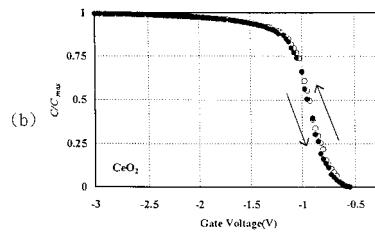

図 6 (a) 参照

図 6 (a) は、 $H_2$  による触媒アニール処理を行わない前の  $CeO_2$  膜の C - V 特性を示す図であり、C - V 特性にヒステリシスループが見られるので、p 型シリコン基板と  $CeO_2$  膜との界面に活性なダングリング・ボンド等は発生し、界面準位密度が高密度になっていることが理解される。

【0056】

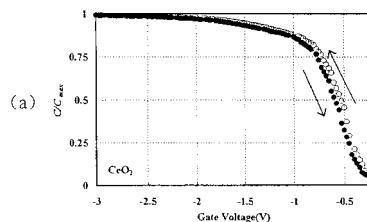

図 6 (b) 参照

図 6 (b) は、 $H_2$  による触媒アニール処理を行った後の改質された  $CeO_2$  膜の C - V

50

特性を示す図であり、このC-V特性にヒステリシスループがほとんど見られないので、ダングリング・ボンドが活性化した水素によって終端され、界面準位密度が大幅に低減していることが理解され、また、C-V特性の曲線形状自体からは、膜質も改善されていることが理解される。

なお、これらのC-V特性の測定に際しては、Al電極を形成するだけで、PMA処理は行っていない。

#### 【0057】

この様に、H<sub>2</sub>処理の効果は、CeO<sub>2</sub>膜に対しても効果的であることが理解され、したがって、ゲート酸化膜として比誘電率(12)の高いCeO<sub>2</sub>膜を用いた場合にも、触媒によって活性化したH<sub>2</sub>による低温処理によって、チャネルドープした不純物を再分布させることなく界面準位密度を大幅に低減することができ、それによって、リーク電流が減少し、且つ、絶縁耐圧も向上する。したがって、膜厚の比較的厚いCeO<sub>2</sub>膜をゲート絶縁膜として用いることによって、微細で特性の優れたMOSFETを再現性良く製造することができる。

#### 【0058】

以上、参考例1乃至参考例3を説明してきたが、H<sub>2</sub>による触媒アニール処理は、SiN膜とシリコン基板との界面状態の改善にも適用されるものであり、また、H<sub>2</sub>の代わりに、NH<sub>3</sub>、HN<sub>3</sub>、N<sub>2</sub>O等の窒素含有ガスを用いても良いものであり、窒素含有ガスを用いた場合には、SiON膜、SiO<sub>2</sub>膜、或いは、CeO<sub>2</sub>膜の界面状態を改善することができるとともに、膜質も改善することが可能になる。

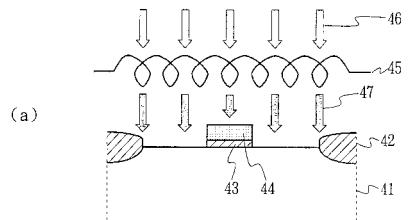

#### 【0059】

以上を前提として、次に、図7を参照して、触媒アニールを行う時期に特徴のある第1及び第2の実施の形態を簡単に説明するが、まず、図7(a)を参照して、触媒アニールをゲート電極の形成後に行う本発明の第1の実施の形態を説明する。

##### 図7(a)参照

まず、p型シリコン基板41をパッド酸化膜を介して設けた窒化膜パターン(いずれも図示せず)をマスクとして選択酸化することによって素子分離酸化膜42を形成したのち、窒化膜パターン及びパッド酸化膜を除去し、次いで、上記の第1の実施の形態と同様に触媒CVD法を用いてゲート絶縁膜となる厚さが、例えば、5nmのSiON膜及び、ゲート電極となるドープトポリシリコン膜を順次堆積させ、次いで、ドープトポリシリコン膜及びSiON膜をパターニングすることによってゲート電極44及びゲート絶縁膜43を形成する。

#### 【0060】

次いで、上記の参考例1と同じ条件において、H<sub>2</sub>46を交流電源から680Wの交流電力を投入して1800~1900に加熱したタンゲステン触媒体45に接触させて活性種47を生成し、この活性種47を含む雰囲気中でゲート絶縁膜43及びゲート電極44を、例えば、10分間熱処理することによって改質されたSiON膜からなるゲート絶縁膜43とするとともに、ゲート電極44のPMA処理とする。

#### 【0061】

この様に、本発明の第1の実施の形態においては、ゲート電極44に対するPMA処理を兼ねるH<sub>2</sub>処理によってp型シリコン基板41/ゲート絶縁膜43の界面準位密度を低減しているので、少ない製造工程数で短チャネル効果の悪化のないMISFETを製造することができる。

#### 【0062】

この第1の実施の形態においてはゲート絶縁膜としてSiON膜を用いているが、ゲート絶縁膜として、SiO<sub>2</sub>膜、CeO<sub>2</sub>膜、或いは、SiN膜を用いても良く、これらのSiO<sub>2</sub>膜、CeO<sub>2</sub>膜、或いは、SiN膜をH<sub>2</sub>による触媒アニールすることによって界面特性を改善することができる。

#### 【0063】

また、この場合の触媒アニールは、H<sub>2</sub>に限られるものではなく、アンモニア(NH<sub>3</sub>)

10

20

30

40

50

、アジ化水素 ( $\text{HN}_3$ ) 、窒素、  $\text{NHCl}_2$  等の窒素ハロゲン化物、或いは、  $\text{N}_2\text{O}$  、  $\text{NO}$  、  $\text{NO}_2$  等の窒素酸化物等の窒素含有ガスを用いても良いものであり、この様な窒素含有ガスを用いることによって、界面のダングリング・ボンドをNで終端することができ、且つ、ゲート絶縁膜43の誘電率も高めることができる。

#### 【0064】

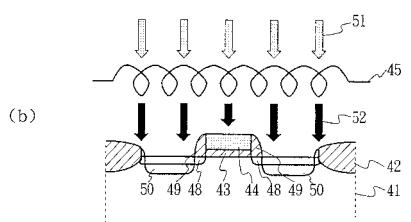

次に、図7(b)を参照して、触媒アニールをサイドウォールの形成後に行う本発明の第2の実施の形態を説明する。

##### 図7(b)参照

まず、p型シリコン基板41をパッド酸化膜を介して設けた窒化膜パターン(いずれも図示せず)をマスクとして選択酸化することによって素子分離酸化膜42を形成したのち、窒化膜パターン及びパッド酸化膜を除去し、次いで、上記の参考例と同様に触媒CVD法を用いてゲート絶縁膜となる厚さが、例えば、5nmのSiON膜及び、ゲート電極となるドープトポリシリコン膜を順次堆積させ、次いで、ドープトポリシリコン膜及びSiON膜をパターニングすることによってゲート電極44及びゲート絶縁膜43を形成する。

#### 【0065】

次いで、ゲート電極44をマスクとしてAsイオンを注入することによって浅いn<sup>-</sup>型のLDD(Lightly Doped Drain)領域48を形成したのち、低温CVD法を用いて全面にSiO<sub>2</sub>膜を堆積させ、次いで、異方性エッチングを施すことによってゲート電極44の側壁にサイドウォール49を形成する。

#### 【0066】

次いで、サイドウォール49をマスクとしてAsイオンを深く注入することによってn<sup>+</sup>型ソース・ドレイン領域50を形成したのち、NH<sub>3</sub>51を50~60sccm供給してガス圧を0.013Torrとした以外は上記の参考例1と同様の条件で1800~1900に加熱したタンゲステン触媒体45にNH<sub>3</sub>51を接触させて活性種52を生成し、この活性種52を含む雰囲気中でサイドウォール49を、例えば、1時間熱処理することによってサイドウォール49とp型シリコン基板41との界面のダングリング・ボンドをNによって終端させ、界面準位密度を低減するとともに、サイドウォール49の膜質も改善することができ、それによって、リーコ電流を低減し、絶縁耐圧を高めることができる。

#### 【0067】

なお、この場合、ゲート絶縁膜43の触媒アニールについては、上記の参考例1乃至参考例3の様にゲート絶縁膜43の堆積直後に行っても良いし、或いは、上記の第1の実施の形態の様にゲート電極44のパターニング直後に行っても良いものであり、いずれの時点にも行わない場合には、サイドウォール49に対する触媒アニール工程がゲート絶縁膜43に対する触媒アニール工程を兼ねることになる。

#### 【0068】

また、この第2の実施の形態においては、触媒アニールの原料ガスとしてNH<sub>3</sub>を用いているがNH<sub>3</sub>に限られるものではなく、HN<sub>3</sub>、窒素、NHCl<sub>2</sub>等の窒素ハロゲン化物、或いは、N<sub>2</sub>O、NO、NO<sub>2</sub>等の窒素酸化物等の窒素含有ガスを用いても良いものである。

#### 【0069】

また、この第2の実施の形態においては、サイドウォール49をSiO<sub>2</sub>膜によって形成しているが、SiO<sub>2</sub>膜に限られるものではなく、触媒CVD法等によって形成されたSiON膜、或いは、O<sub>3</sub>-TEOS(Tetra-Ethyl-Ortho-Silicate)ガスを用いたTEOS-NSG(Non Doped Silicate Glass)膜を用いても良いものである。

#### 【0070】

また、この第2の実施の形態においてもゲート絶縁膜としてSiON膜を用いているが、ゲート絶縁膜として、SiO<sub>2</sub>膜、CeO<sub>2</sub>膜、或いは、SiN膜を用いても良く、こ

10

20

30

40

50

これらの  $\text{SiO}_2$  膜、 $\text{CeO}_2$  膜、或いは、 $\text{SiN}$  膜に窒素含有ガスによる触媒アニールを施すことによって、界面特性及び膜質を改善することができる。

【0071】

以上、本発明の各実施の形態を説明してきたが、本発明においては、高温に加熱される抵抗発熱体を触媒として用いているので、より低温におけるアニール処理が可能となり、それによって、不純物の再分布を問題にすることなく絶縁膜の膜質改善或いは界面状態の改善が可能になる。

また、触媒として抵抗発熱体を用いることによって触媒をアニール処理を行う真空容器内に設けることができるので、装置構成が簡素化される。

【0072】

なお、本発明は実施の形態に記載した構成・条件に限られるものではなく、各種の変更が可能である。

例えば、本発明の主要な特徴点は触媒アニール工程にあるものであり、触媒アニール処理の対象となる絶縁膜の堆積方法は、上記の各実施の形態に記載した方法に限られるものではない。

【0073】

また、上記の各実施の形態の説明においては、触媒作用のある抵抗発熱体をタングステン触媒体によって構成しているが、タングステン(W)に限られるものではなく、トリア含有タングステン、 $\text{Pt}$ 、 $\text{Pa}$ 、 $\text{Mo}$ 、 $\text{Si}$ 、 $\text{Ta}$ 、 $\text{Ti}$ 、 $\text{Va}$ 、 $\text{SiC}$ 、或いは、 $\text{Ti}$ 酸化物を用いても良いものである。

【0074】

また、図2に示した触媒CVD装置において、タングステン触媒体20は、コイル状になっているが、インダクタンス特性を利用している訳ではないので、コイル状に限られるものではなく、また、印加電力も交流電力に限られるものではなく、直流電力でも良い。

【0075】

また、上記の各実施の形態の説明においては、n型シリコン基板或いはp型シリコン基板等のバルクシリコン基板を用いているが、バルクシリコン基板に限られるものではなく、シリコン基板等の基板上にエピタキシャル成長させた単結晶シリコン膜、或いは、絶縁基板上に堆積させた多結晶シリコン膜或いはアモルファスシリコン膜をレーザアニールによって結晶化した結晶性シリコン膜にも適用されるものであり、したがって、TFTのゲート絶縁膜の形成工程等に適用されるものである。

【0076】

また、本発明の触媒アニール処理は、300以下の温度で行えるので、低温プロセス化により寄与するものであるが、必ずしも、300以下に限られるものではなく、不純物の再分布等に関する条件が緩和される場合には、300以上の温度で触媒アニール処理を行っても良いものであり、例えば、PMA処理を兼ねる場合には、400未満の温度で行えば良い。

【0077】

【発明の効果】

本発明によれば、高温に加熱される抵抗発熱体からなる触媒によって $\text{H}_2$ 等の原料ガスを分解し、分解によって生成した活性種の雰囲気中で低温アニール処理することによって界面状態及び膜質を改善しているので、不純物の再分布を抑制することができ、それによって特性の優れたMISFETをバラツキなく製造することができるようになり、高集積度半導体集積回路装置の微細化・高性能化に寄与するところが大きい。

【図面の簡単な説明】

【図1】本発明の原理的構成の説明図である。

【図2】本発明の各実施の形態に用いる触媒CVD装置の概念的構成図である。

【図3】本発明の前提となる参考例1の製造工程の説明図である。

【図4】本発明の前提となる参考例1の $\text{H}_2$ 処理による界面特性の改善効果の説明図である。

10

20

30

40

50

【図5】 本発明の前提となる参考例2のH<sub>2</sub>処理による界面特性の改善効果の説明図である。

【図6】 本発明の前提となる参考例3のH<sub>2</sub>処理による界面特性の改善効果の説明図である。

【図7】 本発明の第1及び第2の実施の形態の製造工程の説明図である。

【符号の説明】

|     |                            |    |

|-----|----------------------------|----|

| 1   | 基体                         | 10 |

| 2   | 水素ガス                       |    |

| 3   | 抵抗発熱体                      |    |

| 4   | 活性種                        |    |

| 5   | 絶縁膜                        |    |

| 1 1 | 真空容器                       |    |

| 1 2 | 弁                          |    |

| 1 3 | 拡散ポンプ                      |    |

| 1 4 | 基板ホルダー                     |    |

| 1 5 | 試料                         |    |

| 1 6 | ヒーター                       |    |

| 1 7 | 熱電対                        |    |

| 1 8 | ガス供給管                      |    |

| 1 9 | 原料ガス                       | 20 |

| 2 0 | タンゲステン触媒体                  |    |

| 2 1 | 交流電源                       |    |

| 2 2 | 赤外放射温度計                    |    |

| 2 3 | シャッター                      |    |

| 3 1 | n型シリコン基板                   |    |

| 3 2 | NH <sub>3</sub>            |    |

| 3 3 | SiH <sub>4</sub>           |    |

| 3 4 | 活性種                        |    |

| 3 5 | 活性種                        |    |

| 3 6 | SiON膜                      | 30 |

| 3 7 | H <sub>2</sub>             |    |

| 3 8 | 活性種                        |    |

| 3 9 | SiON膜                      |    |

| 4 1 | p型シリコン基板                   |    |

| 4 2 | 素子分離酸化膜                    |    |

| 4 3 | ゲート絶縁膜                     |    |

| 4 4 | ゲート電極                      |    |

| 4 5 | タンゲステン触媒体                  |    |

| 4 6 | H <sub>2</sub>             |    |

| 4 7 | 活性種                        | 40 |

| 4 8 | LDD領域                      |    |

| 4 9 | サイドウォール                    |    |

| 5 0 | n <sup>+</sup> 型ソース・ドレイン領域 |    |

| 5 1 | NH <sub>3</sub>            |    |

| 5 2 | 活性種                        |    |

【図1】

本発明の原理的構成の説明図

- 1: 基体

2: 水素ガス

3: 抵抗発熱体

4: 活性種

5: 絶縁膜

【図2】

本発明の各実施の形態に用いる触媒CVD装置の概念的構成図

- |            |               |

|------------|---------------|

| 11: 真空容器   | 18: ガス供給管     |

| 12: フランジ   | 19: 原料ガス      |

| 13: 拡散ポンプ  | 20: タングステン触媒体 |

| 14: 基板ホルダー | 21: 交流電源      |

| 15: 試料     | 22: 赤外放射温度計   |

| 16: ヒーター   | 23: シャッター     |

| 17: 熱電対    |               |

【図3】

本発明の前提となる参考例1の製造工程の説明図

- 20: タングステン触媒体 35: 活性種

31: n型シリコン基板 36: SiON膜

32: NH<sub>3</sub> 37: H<sub>2</sub>

33: SiH<sub>4</sub> 38: 活性種

34: 活性種 39: SiON膜

【図4】

本発明の前提となる参考例1のH<sub>2</sub>処理による界面特性の改善効果の説明図

【図5】

本発明の前提となる参考例2のH<sub>2</sub>処理による

界面特性の改善効果の説明図

【図6】

本発明の前提となる参考例3のH<sub>2</sub>処理による

界面特性の改善効果の説明図

【図7】

本発明の第1及び第2の実施の形態の製造工程の説明図

41: p型シリコン基板

47: 活性種

42: 素子分離酸化膜

48: LDD領域

43: ゲート絶縁膜

49: サイドウォール

44: ゲート電極

50: n<sup>+</sup>型ソース・ドレイン領域

45: タングステン触媒

51: NH<sub>3</sub>

46: H<sub>2</sub>

52: 活性種

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 21/365

H 0 1 L 29/78 3 0 1 T

(72)発明者 和泉 亮

石川県能美郡辰口町旭台 1 - 5 0 大学宿舎 C - 5 2

(72)発明者 松村 英樹

石川県金沢市南四十万 3 - 9 3

審査官 池渕 立

(56)参考文献 特開平 0 8 - 0 7 8 6 9 5 ( J P , A )

特開平 1 0 - 0 8 3 9 8 8 ( J P , A )

特開平 1 1 - 3 4 0 2 2 5 ( J P , A )

特開 2 0 0 0 - 2 1 6 1 6 3 ( J P , A )

(58)調査した分野(Int.Cl., DB名)

H01L 21/324

H01L 21/316

H01L 21/318

H01L 29/786

H01L 21/336

H01L 29/78