RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 511 827**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 81 16072**

(54) Carte d'interface pour le calibrage et la sélection de données saisies dans un central téléphonique électromécanique.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 04 M 3/22.

(22) Date de dépôt ..... 21 août 1981.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 8 du 25-2-1983.

(71) Déposant : DESPREZ Pierre, DUEZ Joël et PICOT Georges. — FR.

(72) Invention de : Pierre Desprez, Joël Duez et Georges Picot.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Cabinet Martinet,

62, rue des Mathurins, 75008 Paris.

- 1 -

CARTE D'INTERFACE POUR LE CALIBRAGE ET LA SELECTION DE DONNEES

SAISIES DANS UN CENTRAL TELEPHONIQUE ELECTROMECANIQUE.

L'invention concerne une carte d'interface destinée à calibrer sous la commande d'un calculateur numérique (notamment d'un microcalculateur à microprocesseur), des données analogiques saisies dans un central téléphonique (particulièrement un central électromécanique), à sélectionner certaines d'entre elles et à les coder pour les transmettre au calculateur.

La saisie des données dans les centraux téléphoniques pose des problèmes différents selon qu'il s'agit de centraux électromécaniques ou de centraux électroniques. Ces derniers disposent déjà, en règle générale, de calculateurs électroniques de commande auxquels on peut affecter des tâches supplémentaires telles que le traitement des données d'exploitation (opérations de taxation, statistiques de fonctionnement, etc...) avec d'autant plus de facilité que ces données sont déjà la plupart du temps dans un état numérique ou logique qui permet de les traiter directement au moyen du calculateur. Par contre, dans les centraux électromécaniques, ces données sont normalement présentes sous la forme de tensions normalement comprises entre -100 et +100 volts. En outre, il peut se présenter momentanément des surtensions élevées provoquées par l'ouverture de contacts de relais, par la foudre, etc... et qui peuvent atteindre des valeurs de l'ordre de 1.500 volts. C'est pourquoi il est nécessaire d'insérer entre un central électromécanique et le calculateur

numérique électronique chargé de l'exploitation des données des circuits d'interface destinés à calibrer les signaux analogiques de données prélevés, à les sélectionner selon leur origine et à les coder sous la forme de signaux binaires au 5 niveau logique (par exemple le niveau TTL). Ces circuits sont regroupés sur des cartes munies notamment de bornes d'entrée des signaux reçus du central, de bornes de sortie des signaux destinés au calculateur, et de bornes d'entrée de signaux logiques de commande reçus du calculateur pour permettre notamment de sélectionner au moins une carte parmi une pluralité 10 de cartes et au moins une chaîne de traitement de signaux (calibrage, sélection, codage) parmi une pluralité de chaînes de traitement constituant les circuits de la carte.

L'invention concerne une telle carte d'interface du 15 genre comprenant, à la manière connue :

- un nombre  $NP$  de bornes d'entrée de signaux analogiques de données, à connecter à autant de points de saisie de données du central,

- un nombre  $n$  de bornes d'entrée de bits d'adresse numérique de signaux de données, à connecter respectivement à  $n$  sorties de bits d'adressage du calculateur,  $n$  étant le nombre de bits nécessaires pour adresser un signal analogique de données parmi  $N$ ,

un générateur de tensions d'écrêtage délivrant par 25 deux sorties deux tensions continues dites d'écrêtage,

- un nombre  $NP$  de réseaux de calibrage de niveaux analogiques à diodes et résistances, chacun desdits réseaux ayant une entrée de signaux analogiques de données connectée à une borne déterminée d'entrée de signaux analogiques de données 30 de la carte, deux entrées de tension d'écrêtage respectivement connectées aux deux sorties dudit circuit d'écrêtage et une sortie délivrant lesdits signaux analogiques de données dont les niveaux sont transposés entre deux limites définies par lesdites tensions d'écrêtage,

35 - un nombre  $P$  de sélecteurs de signaux analogiques ayant chacun d'une part  $N$  entrées de signaux analogiques dont chacune est connectée à la sortie de l'un des  $NP$  réseaux de calibrage, la totalité des  $NP$  bornes d'entrée de signaux analogiques de la carte étant ainsi répartie en  $P$  groupes de  $N$  bornes dont

- 3 -

chacun est respectivement connecté en parallèle au groupe de N entrées de signaux analogiques de l'un des P sélecteurs par l'intermédiaire d'un groupe de N réseaux d'écrêtage, d'autre part n entrées de bits d'adressage respectivement connectées aux n bornes d'entrée de bits d'adressage de la carte, enfin une sortie de signaux analogiques, ces P sélecteurs étant ainsi adressés simultanément par lesdits bits d'adressage pour livrer simultanément passage aux P signaux analogiques calibrés de données délivrés aux P entrées ayant le même rang dans le groupe de N entrées de signaux calibrés de chaque sélecteur,

- un générateur délivrant au moins une tension continue dite de seuil,

- un nombre P de comparateurs de seuils de tension ayant chacun d'une part une entrée de signaux analogiques connectée à la sortie de signaux analogiques calibrés de l'un des P sélecteurs et au moins une entrée de seuil connectée audit générateur de tension de seuil, chacun de ces P comparateurs délivrant un seuil logique de valeur logique déterminée lorsque le niveau du signal analogique admis à ladite entrée de signaux analogiques est supérieur à ladite tension de seuil,

- une borne d'entrée de bit d'inhibition à connecter à une sortie de bit d'inhibition du calculateur,

- enfin un nombre P de circuits inhibiteurs ayant chacun au moins une entrée de signal logique connectée à la sortie de l'un des P comparateurs, une entrée de bit d'inhibition connectée à la borne d'entrée de bit d'inhibition de la carte et au moins une sortie de signal logique connectée à une borne de sortie de la carte, la présence d'un bit d'inhibition à ladite porte d'entrée interdisant par conséquent la transmission aux bornes de sortie de la carte des signaux logiques délivrés par les P comparateurs.

On connaît déjà une carte d'interface de ce genre, notamment par la demande de brevet français enregistrée le 11 Août 1976 sous le numéro F 76.24572.

L'objet de l'invention est une carte d'interface du même genre offrant, par rapport à la carte que l'on vient de décrire, les avantages suivants :

- 4 -

- faculté de commander au moyen du calculateur la valeur des tensions d'écrêtage délivrées aux réseaux de calibrage en vue, soit de réaliser le calibrage des signaux analogiques d'entrée, soit de tester les chaînes auxquelles appartiennent ces réseaux,

- faculté donnée à l'utilisateur de tester individuellement lesdits réseaux de calibrage,

- faculté de commander au moyen du calculateur la valeur de la tension de seuil délivrée ou des tensions de seuils délivrées aux comparateurs,

- possibilité de coder par un nombre binaire délivré au calculateur la position du niveau du signal délivré par un comparateur par rapport à une pluralité de seuils, c'est-à-dire de coder des valeurs discrètes de ce niveau,

15 - mise en haute impédance de toutes les sorties d'une carte qui reçoit le signal d'inhibition, permettant de connecter en parallèle à une pluralité de sorties communes toutes les sorties d'une pluralité de cartes,

20 - plus grande facilité de réalisation par le regroupement de réseaux de calibrage dans des circuits hybrides de faible encombrement qui économisent une partie du câblage et permettent de juxtaposer un grand nombre de cartes dans un même bâti.

Pour obtenir ces différents avantages, la carte d'interface de l'invention est notamment caractérisée en ce que:

25 - le générateur de tension d'écrêtage inclut des moyens pour commander la valeur des tensions d'écrêtage qu'il délivre par la valeur d'au moins un bit de calibrage délivré par au moins une borne d'entrée de bit de calibrage de la carte à connecter à au moins une sortie de bit de calibrage du calculateur,

30 - chaque réseau de calibrage comprend en outre une entrée permettant l'application d'une tension de polarisation destinée à imposer à la sortie dudit réseau une tension déterminée et détectable lorsque l'entrée de signaux analogiques dudit réseau est "en l'air",

35 - le générateur de tension de seuil est un circuit sélecteur de tension de seuil délivrant au moins une tension continue dont la valeur est commandée par la valeur d'un bit présent à au moins une borne de commande de sélection de seuil

- 5 -

de la carte à connecter à au moins une sortie de bit de sélection de seuil du calculateur,

- chaque circuit inhibiteur est un circuit logique à trois états dont la sortie est mise à l'état "haute impédance" lors-

5 que le bit d'inhibition est présent à son entrée de bit d'in-

hibition,

- les réseaux de calibrage sont regroupés en circuits hy-

brides dont chacun comprend une pluralité de réseaux de cali-

brage dont les résistances sont appliquées sur un support

10 commun et dont chaque paire de diodes est contenue dans un

micro-boitier fixé au support.

En variante, une pluralité de comparateurs de seuils est connectée à la sortie de chacun des P sélecteurs de si-

gnaux analogiques et un encodeur dont les entrées sont connec-

15 tées aux sorties de ces comparateurs délivre au calculateur le nombre de bits nécessaires pour coder la position du ni-

veau du signal délivré par ledit sélecteur par rapport aux différents seuils assignés auxdits comparateurs.

D'autres dispositions et avantages de l'invention apparaîtront à l'examen des exemples de réalisation décrits ci-après, en référence aux dessins annexés dans lesquels :

- la figure 1 est un diagramme général de blocs illustrant le mode de connexion entre un central téléphonique et un calculateur par l'intermédiaire d'une pluralité de cartes d'inter-

face conformes ou non à l'invention;

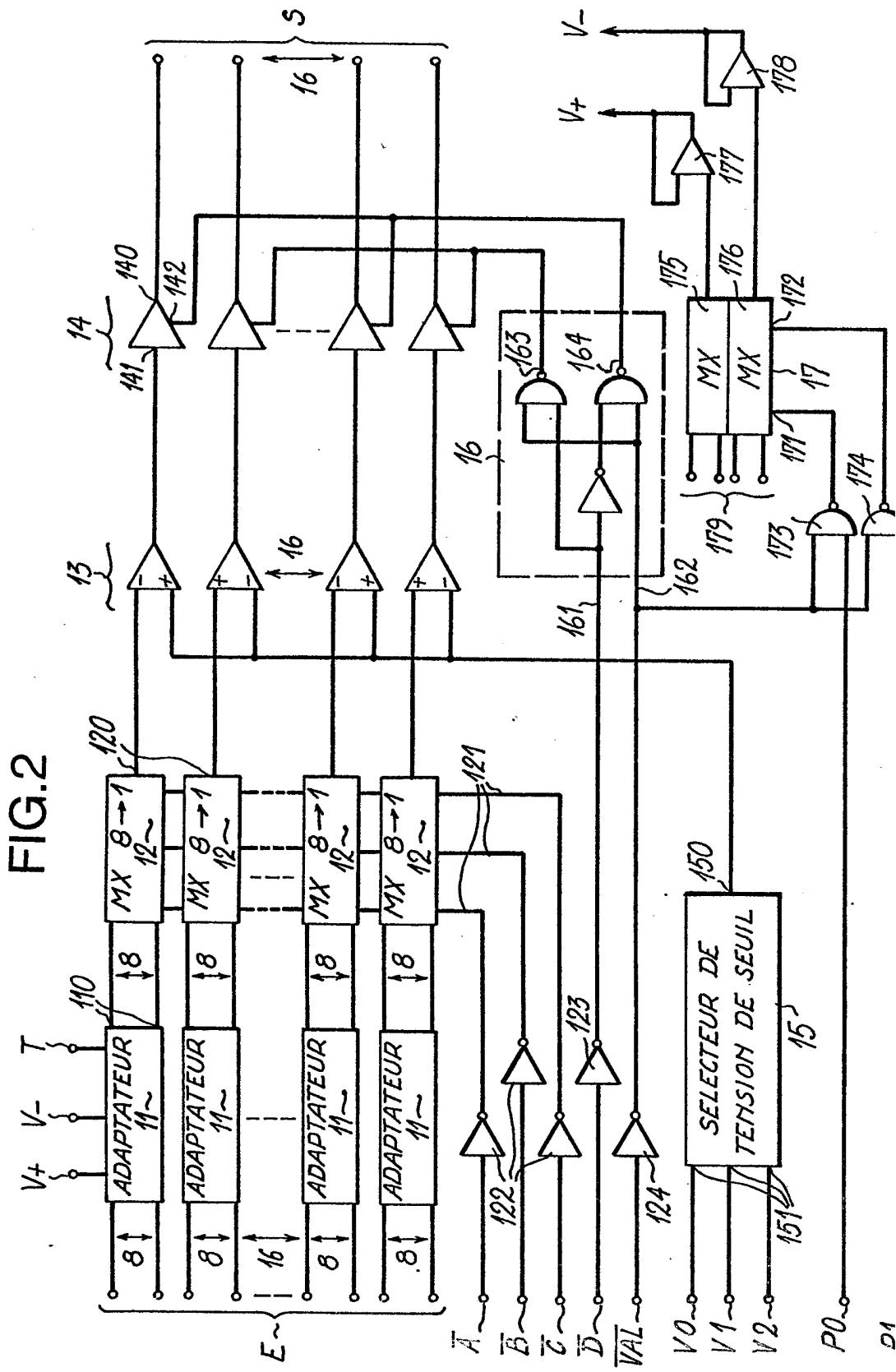

- la figure 2 est un schéma d'un premier exemple de réali-

sation d'une carte d'interface de l'invention;

- la figure 3 est un schéma d'un exemple de réalisation d'un réseau de calibrage conforme à l'invention équipant la

30 dite carte;

- la figure 4 est un diagramme de brochage d'un circuit hybride contenant une pluralité de tels réseaux;

- la figure 5 représente la caractéristique d'un tel ré-

seau;

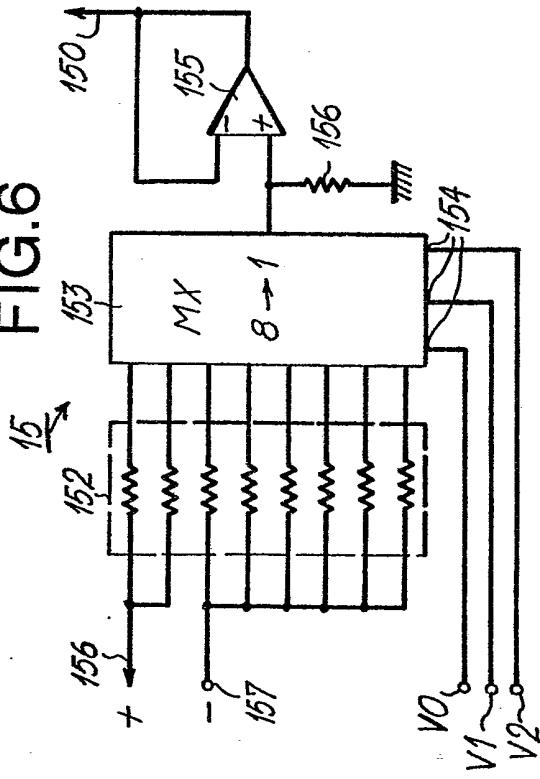

35 - la figure 6 est un diagramme de blocs d'un sélecteur de tensions de seuil équipant ladite carte et

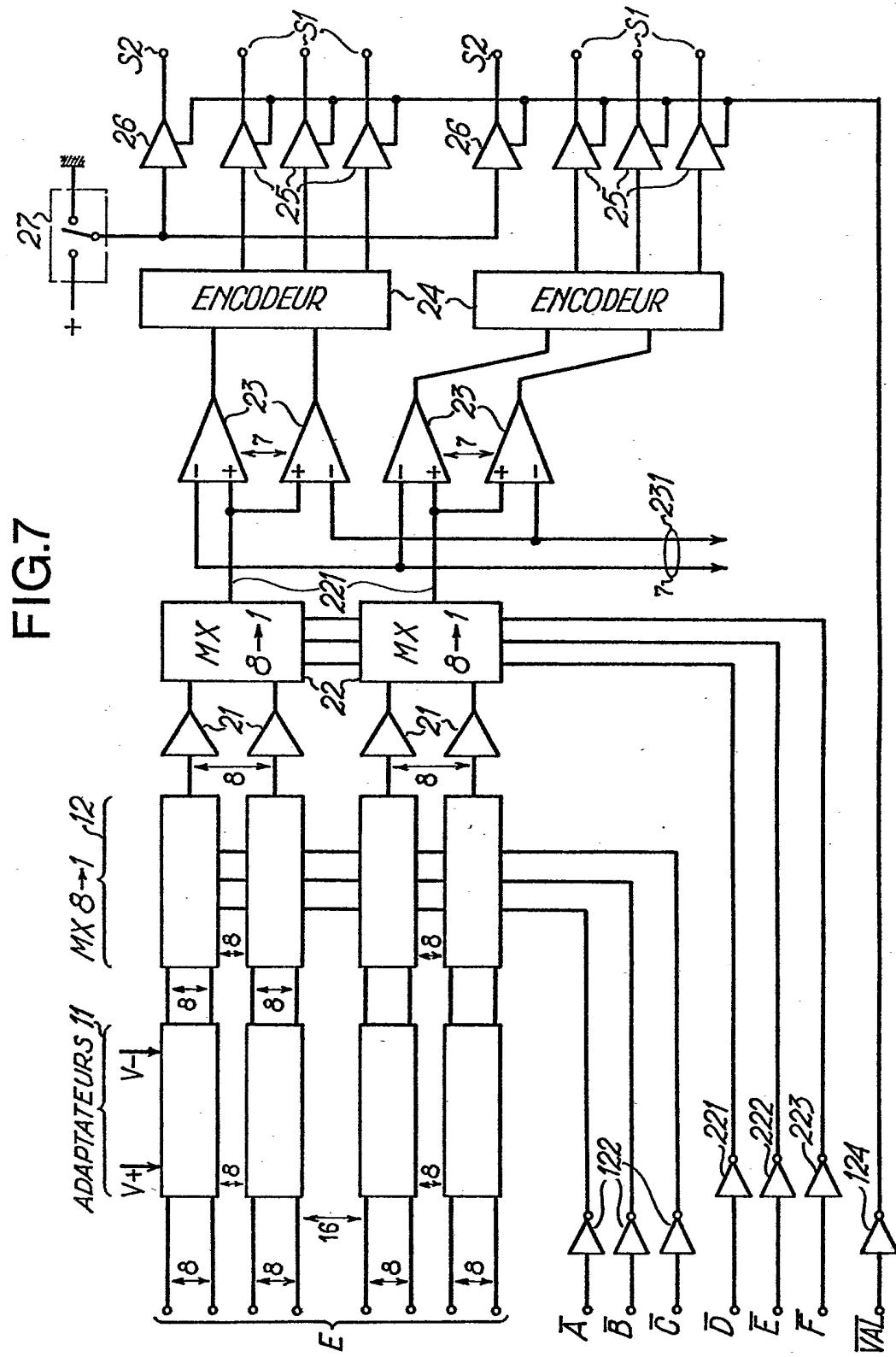

- la figure 7 est un schéma d'un deuxième exemple de réa-

lisation d'une carte d'interface selon l'invention.

D'une façon générale, ces figures ne montrent que les circuits dont la mention est nécessaire à la compréhension de l'invention, à l'exclusion de ceux qui sont indispensables au fonctionnement mais dont la réalisation est à la portée de 5 l'homme de l'art (alimentations notamment).

Les indices numériques qui flanquent des flèches verticales disposées entre des liaisons ou des circuits connectés en parallèle indiquent les nombres de ces liaisons ou de ces circuits.

10 On considère d'abord la figure 1. Des liaisons parallèles L délivrent à une pluralité de cartes d'interface I des signaux analogiques de service prélevés en divers points du central téléphonique C. Les cartes d'interface I, conformes à l'invention, élaborent et transmettent au calculateur 15 numérique N, par l'intermédiaire du bus B, des signaux logiques ou numériques correspondant à ces signaux de service.

Le calculateur N délivre aux cartes I, par l'intermédiaire du même bus B, des bits d'adressage, de test, de validation et de commande de seuil.

20 On considère maintenant la figure 2. La carte d'interface I conforme à l'invention qu'elle représente est munie de :

- 128 entrées de signaux de service E dont chacune est connectée à une liaison L (fig.1) et qui sont réparties en 16 groupes de 8 entrées,

- 10 entrées de signaux binaires connectées au bus B, à savoir 4 entrées de bits d'adresse  $\bar{A}$ ,  $\bar{B}$ ,  $\bar{C}$  et  $\bar{D}$ , une entrée de bit de validation  $\overline{VAL}$ , 3 entrées de bits V0, V1 et V2 destinées à définir la valeur d'une tension de seuil et 2 entrées 30 de bits P0 et P1 dont chacune permet de définir une tension de polarisation ou de calibrage,

- enfin 16 sorties S de signaux logiques dont 8 seulement doivent délivrer à un instant donné au bus B à l'intention du calculateur N (fig.1), un octet parallèle définissant l'état 35 de 8 points du central C.

La carte de la figure 2 comprend 16 chaînes d'adaptation et de sélection dont chacune, destinée à calibrer et à sélectionner les signaux des 8 entrées E d'un même groupe à l'intention d'une sortie S, est constituée par :

- 7 -

- un circuit d'adaptation 11 comprenant 8 réseaux parallèles élémentaires de calibrage reliant respectivement une entrée E à une sortie de circuit 110 et dont chacun transpose le niveau de tension du signal d'entrée, normalement compris 5 entre -100 et +100 volts, dans les limites définies par les tensions présentes aux bornes V+ et V- du circuit,

- un multiplexeur analogique 12 utilisé comme sélecteur de signal et comportant 8 entrées de signaux analogiques respectivement connectées aux 8 sorties 110 du circuit 11, une 10 sortie 120 de signal sélectionné et 3 entrées de bits de sélection respectivement connectées aux bornes d'entrée de sélection  $\bar{A}$ ,  $\bar{B}$  et  $\bar{C}$  de la carte par 3 liaisons 121 et par 3 inverseurs logiques 122,

- un comparateur de seuil 13 dont l'entrée (+) est connectée à la sortie 120 du multiplexeur 12, et dont l'entrée (-) est connectée à la sortie 150 d'un circuit de sélection de seuil 15 délivrant une tension de seuil dont le niveau est commandé par les 3 bits présents aux entrées 151 respectivement connectées aux 3 bornes d'entrée de bits de sélection de 20 seuil V0, V1 et V2 de la carte,

- enfin un circuit logique de sortie 14 à 3 états dont l'entrée de signal 141 est connectée à la sortie du comparateur 13 et dont l'entrée de commande 142 (de mise en haute impédance) est connectée à l'une des deux sorties 163 ou 164 25 d'un circuit logique de commande 16 doté de deux entrées de bits de commande 161 et 162 respectivement connectées à la borne d'entrée  $\bar{D}$  et à la borne d'entrée  $\overline{VAL}$  de la carte par l'intermédiaire d'inverseurs logiques 123 et 124.

La carte de la figure 2 comporte en outre un sélecteur de tensions d'écrêtage ou de test constitué par un double multiplexeur analogique 17 ayant une entrée de commande 171 connectée en parallèle à l'inverseur 124 et à la borne d'entrée de carte P0 par l'intermédiaire d'une porte NON-ET 173 et une entrée de commande 172 connectée en parallèle à 35 l'inverseur 124 et à la borne P1 par l'intermédiaire d'une autre porte NON-ET 174. Ce double multiplexeur a deux sorties 175 et 176 qui sélectionnent respectivement les tensions -V+ et V- parmi celles délivrées à une pluralité d'entrées 179 et les délivrent aux entrées correspondantes de chaque cir-

- 8 -

cuit d'adaptation 11 par l'intermédiaire d'amplificateurs opérationnels 177 et 178. Le rôle de ces derniers est de minimiser l'effet des capacités parasites dues au double multiplexeur 170 afin de réduire autant que possible le temps 5 d'établissement des valeurs V+ et V-.

On donne maintenant quelques explications supplémentaires sur ces différents circuits.

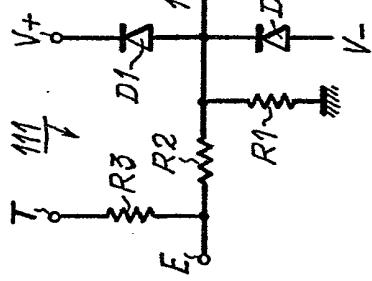

On considère la figure 3 qui montre le schéma de principe de l'un des 8 réseaux parallèles élémentaires 111 10 dont l'assemblage constitue un circuit adaptateur 11. Il comprend :

- une résistance R2 insérée entre l'entrée E (fig.2) et la sortie 110,

- une résistance R1 connectant la sortie 110 à la masse,

- 15 - une résistance R3 connectant à l'entrée E une entrée POL de tension de polarisation (valeur -48V pour l'application considérée),

- enfin d'une part une diode D1 dont l'anode est connectée à la sortie 110 et la cathode à l'entrée V+ et d'autre part 20 une diode D2 dont la cathode est connectée à la sortie 110 et l'entrée à l'entrée V-.

On désignera les tensions appliquées aux entrées E, T, V+ et V- par ces mêmes symboles et les valeurs des résistances R1, R2 et R3 par ces mêmes symboles. La valeur de la 25 tension présente à la sortie 110 est évidemment égale à E ( $R_1 / (R_1 + R_2)$ ). Les valeurs R1 et R2 sont choisies de telle sorte que cette tension varie dans les limites admissibles par le multiplexeur 12 qui suit dans le schéma (fig. 2) lorsque la tension E ne dépasse pas sa valeur nominale 30 maximale.

Si les tensions V+ et V- fournies par le double multiplexeur 17 sont respectivement les mêmes que les tensions d'alimentation du multiplexeur 12 (par exemple +15V et -15V), les diodes D1 et D2 protègent celui-ci en écrétant le 35 signal présent à la sortie 110 lorsqu'il excède ces valeurs. Mais si ces tensions ont toutes deux une même valeur située dans la gamme de tensions admissibles par ledit multiplexeur 12, les diodes injectent cette valeur dans ce multiplexeur et permettent de tester la chaîne analogique. L'entrée POL

- 9 -

permet quant à elle de vérifier l'état de l'entrée E. En effet, si celle-ci est "en l'air", la sortie 110 est portée au potentiel POL ( $R_1 / (R_1 + R_2 + R_3)$ ) parfaitement défini et détectable.

5            Quant à l'impédance d'entrée du réseau, elle est conditionnée par les valeurs absolues de  $R_1$ ,  $R_2$  et  $R_3$  que l'on a intérêt à rendre aussi élevées que possible dans les limites permises par la technologie adoptée. Avantageusement, l'invention prévoit de réaliser les adaptateurs 11 en technologie hybride. Chaque adaptateur 11 de la figure 2 est constitué en fait par deux circuits hybrides dont chacun associe 10 4 réseaux élémentaires 111. Les résistances sont constituées par des dépôts sur substrat d'alumine. Un ajustage au laser permet d'obtenir une précision meilleure que  $5 \cdot 10^{-3}$  pour les 15 rapports des valeurs de ces résistances. Chaque paire de diodes est logée dans un micro-boîtier reporté sur l'hybride, lui-même logé dans un boîtier du genre "single-in-line".

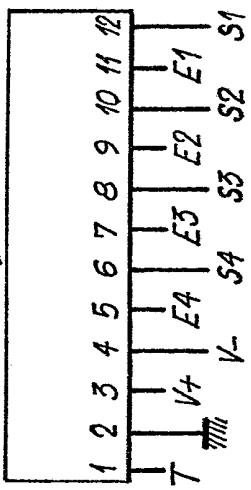

La figure 4 montre le brochage de ce boîtier 11B. Les connexions 1, 2, 3 et 4 correspondent respectivement à 20 l'entrée POL, à la masse, à l'entrée V+ et à l'entrée V-. Les 4 entrées de signal E1, E2, E3 et E4 et les 4 sorties de signal S1, S2, S3 et S4 alternent sur les broches suivantes. L'hybride doit en effet pouvoir supporter sur deux quelconques de ses entrées de signal des tensions de sonnerie 25 (80 VE, 50 Hz) en opposition de phase et il est donc préférable que les entrées ne soient pas connectées à des broches voisines.

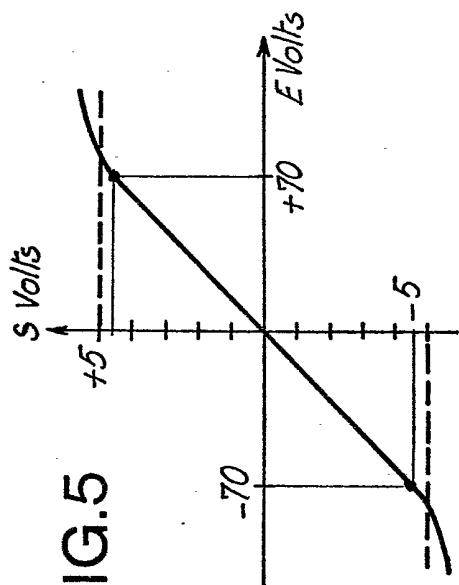

La figure 5 donne un exemple de courbe caractéristique d'un réseau élémentaire 111 dans lequel les résistances 30 ont les valeurs  $R_1=15$  K et  $R_2=R_3=220$  K et les diodes sont du type 1N4118, pour des tensions V+ et V- respectivement égales à +5V et -5V. La tension d'entrée E est reportée en abscisses et la tension de sortie S en ordonnées. La partie rectiligne de la courbe s'étend entre  $E = -70V$  ( $S = -4,4V$ ) et  $E = +70V$  35 ( $S = +4,4V$ ). Au-delà de ces valeurs s'étend la zone de protection (écrêtage) obtenue au moyen des diodes. La pente de la partie rectiligne est proportionnelle à  $R_1 / (R_1 + R_2)$  compte tenu des échelles adoptées.

- 10 -

On considère maintenant la figure 6 qui montre le schéma d'un exemple de réalisation, conforme à l'invention, du sélecteur de tension de seuil 15 de la fig.1. Celui-ci comprend :

- 5      - un réseau 152 de 8 résistances parallèles dont les valeurs sont choisies par l'utilisateur et dont chacune est connectée à l'une ou l'autre d'une source de tension positive 156 ou négative 157,

- 10     - un multiplexeur analogique 153 à une sortie et à 8 entrées de signal respectivement connectées aux sorties des 8 diviseurs de réseau 152 et dont les trois entrées d'adressage 154 sont respectivement connectées aux trois entrées de cartes V0, V1 et V2,

- 15     - enfin un amplificateur opérationnel 155 dont seule l'entrée (+) est utilisée et est connectée à la sortie du multiplexeur 153 elle-même connectée à la masse par la résistance 156 et dont la sortie 150 est connectée en parallèle aux entrées (-) de tous les comparateurs 13 (fig.2).

Chaque résistance du réseau 152 forme ainsi avec la résistance de charge 156 un diviseur de tension dont les caractéristiques sont imposées par les valeurs des trois bits des entrées V0, V1 et V2, valeurs déterminées par le calculateur N (fig.1). Le rôle de l'amplificateur 155 est de minimiser le temps d'acquisition de la tension de seuil simultanément délivrée aux comparateurs 13.

On considère maintenant le rôle du circuit logique 16 (fig.2) en ce qui concerne la commande des circuits logiques 14 à trois états. On précise tout d'abord que l'état logique de la sortie 140 d'un circuit 14 est le même que l'état logique de son entrée 141 (c'est-à-dire 1 ou 0) si l'entrée 142 est à l'état zéro. Si celle-ci est portée à l'état 1, la sortie 140 est à l'état "haute impédance" quel que soit l'état de l'entrée 141.

La sortie 163 est connectée aux entrées 142 de tous les circuits logiques de rang impair (ou pair). La sortie 164 est connectée aux entrées 142 de tous les circuits logiques de rang pair (ou impair). Il résulte de la constitution du circuit 16 illustré sur la figure 2 que :

- 11 -

- la sortie 163 est à l'état 0 si l'entrée  $\bar{D}$  et l'entrée  $\bar{VAL}$  sont toutes deux à l'état 0, ladite sortie 163 étant à l'état 1 dans tous les autres cas,

5 - la sortie 164 est à l'état 0 si l'entrée  $\bar{D}$  est à l'état 1 et l'entrée  $\bar{VAL}$  à l'état 0, ladite sortie 164 étant à l'état 1 dans tous les autres cas.

Il s'ensuit que l'état de la sortie 140 d'un circuit logique à trois états 14 de rang impair (ou pair) suit l'état de la sortie du comparateur 13 associé seulement si 10 les entrées de carte  $\bar{D}$  et  $\bar{VAL}$  sont à l'état 0. Si l'une quelconque des entrées  $\bar{D}$  et  $\bar{VAL}$  est à l'état 1, ladite sortie 140 est à l'état "haute impédance".

Il s'ensuit également que la sortie 140 d'un circuit logique à trois états 14 de rang pair (ou impair) suit 15 l'état de la sortie du comparateur 13 associé seulement si l'entrée de carte  $\bar{D}$  est à l'état 1 et l'entrée  $\bar{VAL}$  à l'état 0. Si l'entrée  $\bar{D}$  est à l'état 0 ou l'entrée  $\bar{VAL}$  est à l'état 1, ladite sortie 140 est à l'état "haute impédance".

La carte de la figure 2 est ainsi dotée des moyens 20 de commander par le calculateur N, au moyen des quatre bornes  $\bar{A}$ ,  $\bar{B}$ ,  $\bar{C}$ ,  $\bar{D}$  la sélection d'un groupe d'entrées (8 entrées E) sur 16 et la mise en haute impédance des sorties S correspondant aux 15 groupes d'entrées non sélectionnés. Elle est en outre dotée des moyens de commander par le même calculateur N 25 au moyen de la borne  $\bar{VAL}$ , la mise en haute impédance de toutes les sorties de la carte.

On remarque que l'adressage par les 4 bits  $\bar{A}$ ,  $\bar{B}$ ,  $\bar{C}$ ,  $\bar{D}$  permet de sélectionner 8 entrées E sur 128, soit 1 sur 16, mais que la présence du circuit logique 16 permet d'utiliser 30 des multiplexeurs 12 du genre 8 vers 1 alors que son absence imposerait l'utilisation de multiplexeurs du genre 16 vers 1.

On remarque aussi que celles des entrées des portes NON-ET 173 et 174 qui ne sont pas connectées aux entrées P0 et P1 (bits de sélection de tension de polarisation) sont 35 connectées à la sortie de l'inverseur 124. La mise de l'entrée  $\bar{VAL}$  à l'état 1 qui, comme on vient de le voir, inhibe toutes les sorties S des chaînes de sélection de groupes d'entrées, interdit donc en même temps l'application des tensions de test V+ et V- aux circuits adaptateurs 11 de la carte considérée.

- 12 -

Enfin, si l'on se reporte à la définition générale de l'invention données au début de la présente description, on constate que, dans le cas de la carte de la fig.2,  $N=8$ ,  $P=16$ ,  $NP=128$  et  $n=4$ .

- 5        On considère maintenant la figure 7 qui donne le schéma d'une deuxième forme de réalisation d'une carte conforme à l'invention. Cette carte comprend, comme la précédente, 16 chaînes d'adaptation et de sélection comportant chacune 8 entrées E, 1 circuit d'adaptation 11, 1 multiplexeur 12.

- 10      Les tensions d'écrêtage ou de test V+ et V- sont délivrées par un dispositif identique à celui de la fig.2 (entrées de carte P0 et P1, portes NON-ET 173 et 174, double multiplexeur 170, amplificateurs opérationnels 177 et 178) qui n'est pas représenté dans ladite figure 7.

- 15      Par contre, les 16 multiplexeurs 12 sont répartis en deux groupes de 8. Les sorties des multiplexeurs 12 de chaque groupe sont connectées en parallèle aux entrées d'un multiplexeur 22 identique par l'intermédiaire d'amplificateurs opérationnels 21 destinés là encore à minimiser les

- 20      temps d'acquisition. Chacun des multiplexeurs 22 est adressé au moyen de 3 bits  $\bar{D}$ ,  $\bar{E}$ ,  $\bar{F}$  délivrés par des entrées de carte portant les mêmes repères et respectivement inversés par 3 inverseurs logiques 221, 222 et 223. Les 16 groupes d'entrée E sont donc en définitive connectés, par l'intermédiaire des

- 25      multiplexeurs 12 et 22, à seulement deux liaisons 221 (sorties des multiplexeurs 22) et chacune de ces liaisons achemine 1 signal sur 64, sélectionné au moyen de 6 bits d'adressage délivrés par le calculateur N (fig.1).

Chacune des deux liaisons 221 est connectée en parallèle aux entrées (+) de 7 comparateurs de seuil 23 identiques aux comparateurs 13 de la fig.2. Il existe donc 14 comparateurs 23 répartis en deux groupes. L'entrée (-) d'un comparateur de chaque groupe est connectée à une liaison d'un groupe de 7 liaisons 231. Chacune de ces liaisons est

35      connectée à une source de tension continue (non représentée) dont la valeur est déterminée au gré de l'utilisateur.

Dans chaque groupe, les sorties de chacun des 7 comparateurs 23 sont connectées aux 7 entrées d'un encodeur 24

- 13 -

à trois sorties qui permet de coder sur trois bits parallèles la situation du signal transposé et sélectionné par rapport aux seuils déterminés au moyen des 7 comparateurs 23 et des 7 liaisons 231. Chaque ensemble constitué par un encodeur 24 5 et par les 7 comparateurs 23 associés constitue donc un comparateur à seuils multiples de niveaux variables au gré de l'utilisateur.

Chacune des sorties d'un encodeur 24 est connectée à une sortie de carte S1 par l'intermédiaire d'un circuit 10 logique à trois états 25. A chacun des groupes de trois circuits 25 connecté à un même encodeur 24 est associé un circuit logique à trois états 26 dont l'entrée est connectée à un circuit d'émission de bits de service représenté par un commutateur 27 et dont la sortie est connectée à une sortie 15 de carte S2. Tous les circuits logiques à trois états 25 et 26 peuvent être mis simultanément dans l'état "haute impédance" par une liaison de commande reliée à l'entrée de carte VAL par l'intermédiaire de l'inverseur logique 124.

En définitive, l'adressage commandé sur 6 bits par 20 le calculateur N au moyen des entrées A, B, C, D, E, F permet de sélectionner deux signaux sur les 128 présents aux entrées E et conformés par les adaptateurs 11, de comparer les niveaux de ces deux signaux aux 7 seuils déterminés au moyen des comparateurs 23 et les liaisons 231, et de délivrer par l'ensemble 25 des 8 liaisons S1 et S2 un octet parallèle comprenant deux groupes de 3 bits d'état de signal et deux bits de service. La commande de l'entrée VAL par le calculateur N permet de mettre toutes les sorties S1 et S2 dans l'état "haute impédance" ce qui donne la possibilité de monter en 30 sorties communes une pluralité de cartes et de sélectionner l'une des cartes de ladite pluralité.

Si l'on compare à la carte de la fig.2 celle de la fig.7, on remarque que, pour cette dernière,  $N=64$ ,  $P=2$ ,  $NP=128$  et  $n=6$ . Elle ne permet de sélectionner que deux entrées E sur 128 au moyen de 6 bits mais, en revanche, elle permet de coder 8 niveaux discrets de signaux transposés.

Revendications.

- 1.- Carte d'interface pour le calibrage et la sélection programmée de données saisies dans un central téléphonique électromécanique en vue de leur transmission à un calculateur numérique et logique, du genre comprenant :

- 5 - un nombre NP de bornes d'entrée de signaux analogiques de données, à connecter à autant de points de saisie de données du central,

- un nombre n de bornes d'entrée de bits d'adresse numérique de signaux de données, à connecter respectivement à n sorties de bits d'adresse du calculateur, n étant le nombre de bits nécessaires pour adresser un signal analogique de données parmi N,

- un générateur délivrant par deux sorties deux tensions continues d'écrêtage ou de test,

- 15 - un nombre NP de réseaux de calibrage de niveaux analogiques à diodes et résistances, chacun desdits réseaux ayant une entrée de signaux analogiques de données connectée à une borne déterminée d'entrée de signaux analogiques de données de la carte, deux entrées de tension respectivement connectées aux 20 deux sorties dudit générateur et une sortie délivrant lesdits signaux analogiques de données dont les niveaux sont transposés entre deux limites définies par lesdites tensions d'écrêtage,

- un nombre P de sélecteurs de signaux analogiques ayant 25 chacun d'une part N entrées de signaux analogiques dont chacune est connectée à la sortie de l'un des NP réseaux de calibrage, la totalité des NP bornes d'entrée de signaux analogiques de la carte étant ainsi répartie en P groupes de N bornes dont chacun est respectivement connecté en parallèle 30 au groupe de N entrées de signaux analogiques de l'un des P sélecteurs par l'intermédiaire d'un groupe de N réseaux d'écrêtage, d'autre part n entrées de bits d'adressage respectivement connectées aux n bornes d'entrée de bits d'adressage de la carte, enfin une sortie de signaux analogiques, 35 ces P sélecteurs étant ainsi adressés simultanément par lesdits bits d'adressage pour livrer simultanément passage aux P signaux analogiques calibrés délivrés aux P entrées ayant

- 15 -

- le même rang dans le groupe de N entrées de signaux calibrés de chaque sélecteur,

- un générateur délivrant au moins une tension continue dite "de seuil",

- 5 - un nombre P de comparateurs de seuils de tension ayant chacun une entrée de signaux analogiques connectée à la sortie de signaux analogiques calibrés de l'un des P sélecteurs et au moins une entrée de seuil connectée audit générateur de tension de seuil, chacun de ces P comparateurs délivrant un signal logique de valeur logique déterminée lorsque le niveau du signal analogique admis à ladite entrée de signaux analogiques est supérieur à ladite tension de seuil,

- 10 - une borne d'entrée de bit d'inhibition à connecter à une sortie de bit d'inhibition du calculateur,

- 15 - un nombre P de circuits inhibiteurs ayant chacun au moins une entrée de signal logique connectée à la sortie de l'un des P comparateurs, une entrée de bit d'inhibition connectée à la borne d'entrée de bit d'inhibition de la carte et au moins une sortie de signal logique connectée à une borne de sortie de la carte, la présence d'un bit d'inhibition à ladite borne d'entrée de la carte interdisant par conséquent la transmission aux bornes de sortie de la carte des signaux logiques délivrés par les P comparateurs,

- 20 caractérisée en ce que ledit générateur de tensions d'écrêtage ou de test inclut des moyens (17) pour commander la valeur desdites tensions d'écrêtage par la valeur d'au moins un bit de calibrage délivré par au moins une borne d'entrée (PO) de bit de calibrage de la carte à connecter à au moins une sortie de bit de calibrage du calculateur.

- 25 2.- Carte d'interface selon la revendication 1, caractérisée en ce que chaque réseau de calibrage (11) comprend en outre une entrée (POL) de tension de polarisation destinée à imposer à la sortie dudit réseau une tension connue et détectable lorsque l'entrée (E) de signaux analogiques dudit réseau est "en l'air".

- 30 3.- Carte d'interface selon la revendication 1 ou la revendication 2, caractérisée en ce qu'elle comporte en outre des moyens (173,174) d'inhiber la délivrance desdites tensions d'écrêtage ou de test aux réseaux de calibrage (111)

- 16 -

lorsque le bit d'inhibition est présent à l'entrée VAL de bit d'inhibition.

- 4.- Carte d'interface selon l'une quelconque des revendications 1 à 3, caractérisée en ce que le générateur de tensions de seuil est un circuit sélecteur de tensions de seuil (15) délivrant au moins une tension continue dont la valeur est commandée par la valeur d'un bit présent à au moins une borne d'entrée de commande de sélection de seuil ( $V_0$ ) de la carte à connecter à au moins une sortie de bit de sélection de seuil du calculateur.

- 5.- Carte d'interface selon la revendication 4, caractérisée en ce que le circuit sélecteur de tension de seuil (15) comprend une pluralité de sources de tension continue (152) et un multiplexeur analogique (153) muni d'une pluralité d'entrées de tensions de seuil respectivement connectées auxdites sources et du nombre d'entrées de commande nécessaires pour sélectionner une source parmi ladite pluralité de sources, lesdites entrées de commande étant connectées à autant de bornes d'entrée de bits de commande de sélection de seuil ( $V_0, V_1, V_2$ ) de la carte, à connecter à autant de sorties de bits de sélection de seuil du calculateur.

- 6.- Carte d'interface selon l'une quelconque des revendications 1 à 3, caractérisée en ce qu'elle comporte, connectée à la sortie de chacun des  $P$  sélecteurs de signaux analogiques, une pluralité de comparateurs de seuils (23) auxquels est connecté un encodeur (24) qui délivre le nombre de bits nécessaires pour coder la position du niveau du signal délivré par ledit sélecteur par rapport aux seuils assignés auxdits comparateurs.

- 7.- Carte d'interface selon l'une quelconque des revendications 1 à 6, caractérisée en ce que chaque circuit inhibiteur est un circuit logique à trois états (14) dont la sortie (140) est mise à l'état "haute impédance" lorsque le bit d'inhibition est présent à son entrée de bit d'inhibition (142).

- 8.- Carte d'interface selon la revendication 2 ou selon la revendication 2 et l'une quelconque des revendications 3 à 7, caractérisée en ce que chaque réseau de calibrage (111) est du genre comprenant deux diodes ( $D_1, D_2$ ) en série formant

- 17 -

une paire de diodes dont l'une des bornes reçoit une des tensions d'écrêtage ( $V_+$ ) et dont l'autre reçoit l'autre tension ( $V_-$ ), le point commun desdites diodes étant connecté à la masse par une première résistance ( $R_1$ ), à l'entrée (E) du réseau par une deuxième résistance ( $R_2$ ) et étant connecté directement à la sortie (110) dudit réseau.

9.- Carte d'interface selon la revendication 8, caractérisée en ce que chaque réseau de calibrage (111) comporte en outre une entrée (POL) de tension de polarisation connectée à l'entrée (E) dudit réseau par une troisième résistance ( $R_3$ ).

10.- Carte d'interface selon la revendication 8 ou la revendication 9, caractérisée en ce que les réseaux de calibrage (111) sont regroupés en circuits hybrides dont chacun comprend une pluralité de réseaux de calibrage dont les résistances sont appliquées sur un support commun et dont chaque paire de diodes est contenue dans un micro-boîtier fixé au support.

11.- Circuit hybride pour une carte d'interface conforme à la revendication 10.

FIG.1

FIG.3

FIG.4

1/3

FIG.5

FIG.6

2/3

3/3