【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第4区分

【発行日】平成17年11月24日(2005.11.24)

【公開番号】特開2005-78766(P2005-78766A)

【公開日】平成17年3月24日(2005.3.24)

【年通号数】公開・登録公報2005-012

【出願番号】特願2003-311393(P2003-311393)

【国際特許分類第7版】

G 1 1 C 16/02

G 1 1 C 16/04

【F I】

G 1 1 C 17/00 6 0 1 B

G 1 1 C 17/00 6 2 1 A

G 1 1 C 17/00 6 2 2 E

G 1 1 C 17/00 6 0 1 U

【手続補正書】

【提出日】平成17年9月30日(2005.9.30)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

電気的書き換え可能な不揮発性メモリセルが配列されて、複数ページで構成される少なくとも一つのブロックを有するセルアレイと、

前記セルアレイのページ単位或いは連続する複数ページからなるサブブロック単位でのデータ消去を制御するコントローラとを備え、

前記セルアレイは、二値データ列で表されてその下位ビット側の“0”データの数が累積値を示すデータ消去回数を記憶する消去管理領域を有し且つ、

前記消去管理領域が記憶するデータ消去回数は、前記ブロック内の選択ページについてのデータ消去前に前記ブロックの複数ページを選択状態とするチェック読み出し動作で読み出され、データ消去後に更新されたデータ消去回数が前記選択ページに書き込まれることを特徴とする不揮発性半導体記憶装置。

【請求項2】

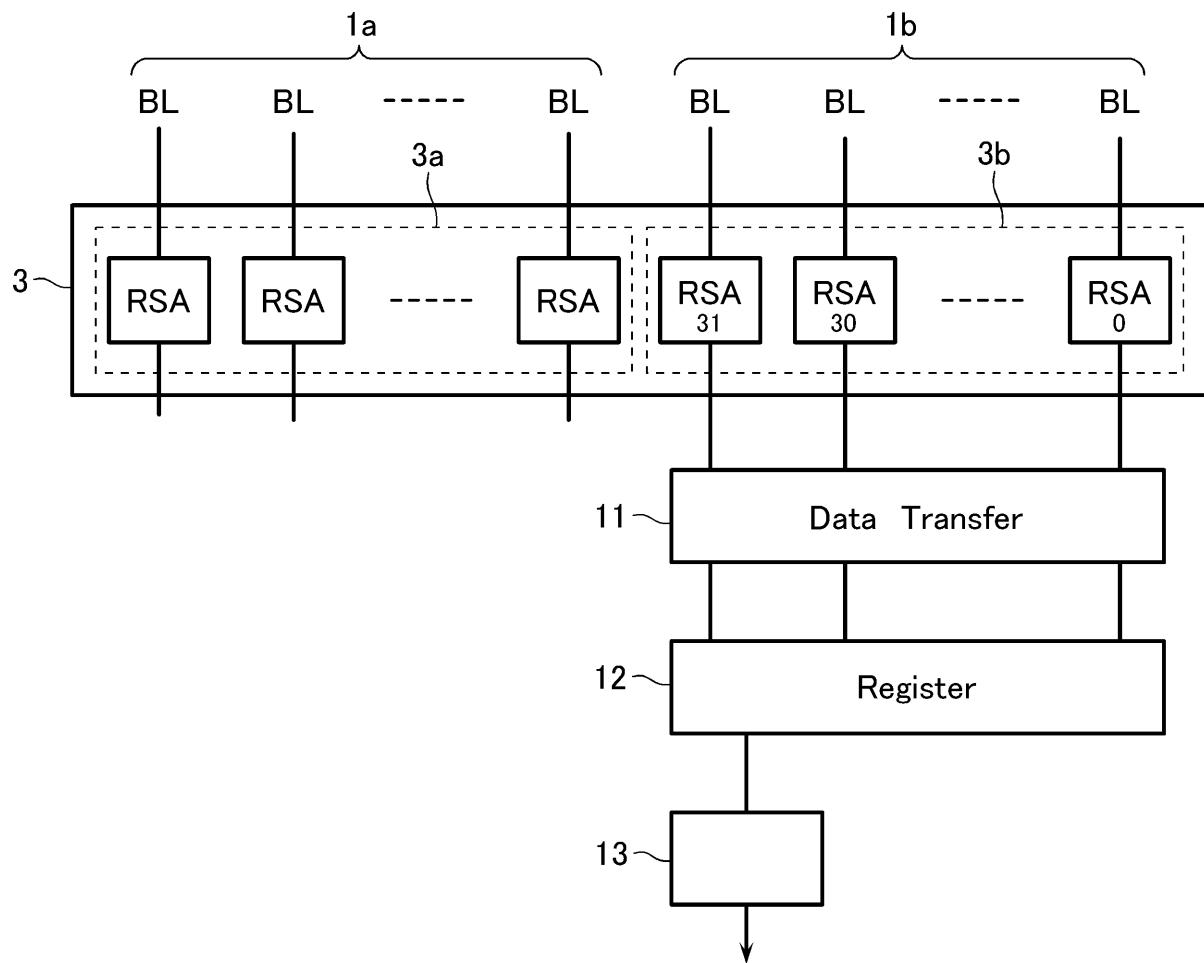

前記セルアレイのページ単位のデータ読み出し及び書き込みを行うためのセンスアンプ回路と、

データ消去前に前記消去管理領域から前記センスアンプ回路に読み出されたデータ消去回数を一時保持するためのレジスタ回路と、

前記センスアンプ回路に読み出されたデータ消去回数を前記レジスタ回路に転送すると共に、データ消去後に前記レジスタ回路が保持するデータ消去回数に1を加算して更新されたデータ消去回数を前記センスアンプ回路に転送するように構成されたデータ転送回路と、

前記レジスタ回路に転送されたデータ消去回数が許容最大値に達したか否かを判定する判定回路とを有する

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。

【請求項3】

前記データ転送回路は、

第1のタイミング信号により活性化されて前記センスアンプ回路に読み出されたデータ消去回数を各ビット並列に前記レジスタ回路に転送する読み出し転送バッファと、

第2のタイミング信号により活性化されて、データ消去回数データを1ビットずつ上位側にシフトすると共に、前記データ消去回数データの最下位ビットとなる“0”データを加算して更新された消去回数を前記センスアンプ回路に転送する書き込み転送バッファとを有する

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

制御ゲートがそれぞれ異なるワード線に接続されて直列接続された複数の電気的書き換え可能な不揮発性メモリセルにより構成されるNANDセルユニットを配列して構成され、1ワード線に接続される複数のメモリセルの集合が1ページ又は2ページとなり、ワード線方向に並ぶ複数のNANDセルユニットの集合が1ブロックとなり、ワード線方向にノーマルデータ領域と冗長領域とに分けられ、前記冗長領域に、ブロック内の累積されたデータ消去回数がそのブロック内の最も最近にデータ消去のために選択されたページに書き込まれるセルアレイと、

前記セルアレイのページ単位のデータ読み出し及び書き込みを行うための、前記ノーマルデータ領域と冗長領域にそれぞれ対応するノーマルセンスアンプ回路と冗長センスアンプ回路を有するセンスアンプ回路と、

前記セルアレイのページ単位或いは連続する複数ページからなるサブブロック単位でのデータ消去を制御するコントローラと、

データ消去前に前記セルアレイの冗長領域から前記冗長センスアンプ回路に読み出されたデータ消去回数を一時保持するためのレジスタ回路と、

前記冗長センスアンプ回路に読み出されたデータ消去回数を前記レジスタ回路に転送すると共に、データ消去後に前記レジスタ回路が保持するデータ消去回数に1を加算して更新されたデータ消去回数を前記冗長センスアンプ回路に転送するように構成されたデータ転送回路と、

前記レジスタ回路に転送されたデータ消去回数が最大値に達したか否かを判定する判定回路とを有する

ことを特徴とする不揮発性半導体記憶装置。

【請求項5】

前記冗長領域が記憶するデータ消去回数は、二値データ列で表されてその下位ビット側の“0”データの数が累積値を示すものであり、

前記冗長領域が記憶するデータ消去回数は、前記ブロック内の選択ページについてのデータ消去前に前記ブロック内の複数ワード線を選択するチェック読み出し動作で前記冗長センスアンプ回路に読み出され、データ消去後に更新されたデータ消去回数が前記冗長センスアンプ回路に書き戻されて前記選択ページの冗長領域に書き込まれることを特徴とする請求項4記載の不揮発性半導体記憶装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0030

【補正方法】変更

【補正の内容】

【0030】

具体的に、最下位ビット対応の書き込み転送バッファ22<sub>0</sub>の入力端はV<sub>SS</sub>に固定され、その出力端は冗長センスアンプRSA0のノードN<sub>0</sub>に接続されている。以下、書き込み転送バッファ22<sub>j</sub> (j = 1 ~ 31)の入力端は、レジスタREG<sub>j-1</sub>に接続され、出力端は冗長センスアンプRSA<sub>j</sub>のノードN<sub>j</sub>に接続されている。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0031

【補正方法】変更

【補正の内容】

【0 0 3 1】

このような書き込み転送バッファ 2\_2\_j により、最下位ビット対応の冗長センスアンプ RSA 0 のノード N 0 には常に、Vss (即ち書き込みデータ “0”) が転送される。また、レジスタ回路 1\_2 に読み出された HC 値の “0” データは、1 ビット上位側にシフトされた状態で冗長センスアンプ回路 3\_b に書き戻される。即ち、ページ消去前に冗長センスアンプ RSA\_j に読み出された冗長領域 1\_b の HC データは、ページ消去後、“0” が一つ増えた状態に更新される。

【手続補正 4】

【補正対象書類名】図面

【補正対象項目名】図 4

【補正方法】変更

【補正の内容】

【図 4】