(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294472

(P2005-294472A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 21/301

H01L 21/3205

H01L 21/66

F 1

H01L 21/78

H01L 21/66

H01L 21/88

H01L 21/78

テーマコード(参考)

4M106

5F033

L

E

S

Q

審査請求 未請求 請求項の数 11 O L (全 17 頁)

(21) 出願番号

特願2004-106331 (P2004-106331)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100110928

弁理士 速水 進治

(72) 発明者 副島 康志

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

F ターム(参考) 4M106 AA01 AA07 AB12 AB15 AB17

5F033 GG02 HH07 HH09 HH11 HH19

VV01 XX31

(54) 【発明の名称】半導体装置、半導体ウェーハ、およびこれらの製造方法

## (57) 【要約】

【課題】 ダイシング領域に配線層を有する半導体装置の信頼性を向上させる。

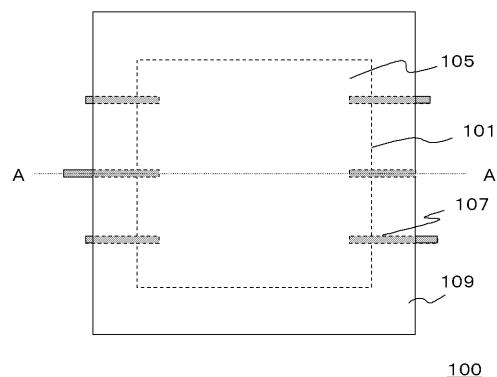

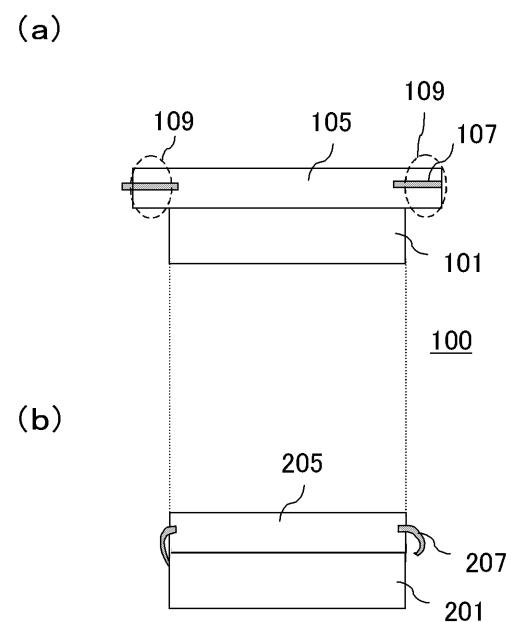

【解決手段】 シリコン基板101の素子形成面に絶縁層105が設けられ、絶縁層105がシリコン基板101の端面から突出した張出部109を有する半導体装置100において、張出部109は絶縁層105中に埋設されたCuの配線107を有する。

【選択図】 図1

(a)

(b)

100

**【特許請求の範囲】****【請求項 1】**

半導体基板と、前記半導体基板の素子形成面上に設けられた絶縁膜と、

を有し、

前記素子形成面に、

複数の素子領域と、

前記複数の素子領域を分離し、一方の素子領域と他方の素子領域との間を接続する配線

を含むダイシング領域と、

が設けられ、

前記ダイシング領域において、前記半導体基板が除去されるとともに、前記絶縁膜

の少なくとも一部を有することを特徴とする半導体ウェーハ。

10

**【請求項 2】**

請求項 1 に記載の半導体ウェーハにおいて、前記ダイシング領域には、前記絶縁膜中に

導電プラグが設けられていることを特徴とする半導体ウェーハ。

**【請求項 3】**

請求項 2 に記載の半導体ウェーハにおいて、複数の前記導電プラグが、前記ダイシング

領域に沿って列状に設けられていることを特徴とする半導体ウェーハ。

**【請求項 4】**

請求項 1 乃至 3 いずれかに記載の半導体ウェーハにおいて、前記ダイシング領域の幅が

2  $\mu\text{m}$  以上であることを特徴とする半導体ウェーハ。

20

**【請求項 5】**

請求項 1 乃至 4 いずれかに記載の半導体ウェーハが前記ダイシング領域で分割されてな

ることを特徴とする半導体チップ。

**【請求項 6】**

半導体基板と、

前記半導体基板の素子形成面上に設けられた絶縁膜と、

を有し、

前記絶縁膜は、前記半導体基板の外周縁よりも外方向へ張り出した張出部を有し、

前記張出部の内部に配線が含まれていることを特徴とする半導体チップ。

30

**【請求項 7】**

請求項 6 に記載の半導体チップにおいて、前記張出部が前記半導体基板の前記外周縁か

ら 1  $\mu\text{m}$  以上張り出していることを特徴とする半導体チップ。

**【請求項 8】**

半導体基板の素子形成面上に、絶縁膜中に配線が埋設された配線層を形成する工程と、

前記半導体基板の前記素子形成面側を支持基板に固定する工程と、

前記支持基板に固定した状態で、前記半導体基板の裏面の側から、前記配線の設けられ

た領域のうち所定の領域を選択的に薄化し、ダイシング領域を形成する工程と、

を含むことを特徴とする半導体ウェーハの製造方法。

**【請求項 9】**

請求項 8 に記載の半導体ウェーハの製造方法において、配線層を形成する前記工程は、

前記ダイシング領域において、前記絶縁膜中に導電プラグを埋設する工程を含むことを特

徴とする半導体ウェーハの製造方法。

40

**【請求項 10】**

請求項 9 に記載の半導体ウェーハの製造方法において、導電プラグを埋設する前記工程

は、前記ダイシング領域に沿って複数の前記導電プラグを形成する工程を含むことを特

徴とする半導体ウェーハの製造方法。

**【請求項 11】**

請求項 8 乃至 10 いずれかに記載の半導体ウェーハの製造方法により半導体ウェーハを

得る工程と、

前記半導体基板の前記裏面をダイシングシートに接合する工程と、

50

前記ダイシングシートに接合された前記半導体基板の前記素子形成面から前記支持基板を除去する工程と

前記半導体ウェーハに応力を付与し、前記ダイシング領域にて前記半導体ウェーハを破断させ、前記半導体ウェーハを複数の半導体チップに分離する工程と、

を含むことを特徴とする半導体チップの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、半導体ウェーハ、およびこれらの製造方法に関する。

【背景技術】

【0002】

従来、ウェーハ上に複数形成された半導体装置を個々の装置に分離する方法として、ダイシングやエッチングが用いられている。この種の技術が、特許文献1に記載されている。同文献に記載の方法では、まず、回路が形成されたウェーハの表面をテープ部材に貼り付ける。この状態でウェーハの裏面を研磨し、薄化する。そして、研磨された裏面において、個々の半導体素子に相当する領域にレジスト層を形成し、裏面側からエッチングを行うことにより、ウェーハを個々の半導体素子に分離する。この方法を用いると、ウェーハにおいて半導体素子として使用可能な領域を増大することができるとしている。また、この方法を用いると、裏面研削により生じたウェーハのクラックを除去し、実装後の信頼性を向上させる工程ができるとされている。

【0003】

一方、特許文献2には、ウェーハ上の複数のLSIを配線で接続した構成が開示されている。LSI間に配線を形成することにより、複数のLSIを同時に検査することができるとされている。

【0004】

【特許文献1】特開2002-93752号公報

【特許文献2】特開昭62-171137号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところが、たとえば特許文献2に記載の検査目的の場合のように、ウェーハ上の複数の半導体装置の配線による接続が求められる場合、ダイシング時にも切断領域に配線が残されていることとなる。この場合、ダイシングによりウェーハを複数の半導体チップに分離する際に、残存している配線を確実に切断することおよび切断された配線によるショート等がチップに生じないようにすることが求められる。ところが、ダイシング領域に配線が存在している場合、配線をウェーハのエッチングとともに除去することが困難であった。また、ダイシングによって機械的に破断することは可能であるが、この場合、切断により配線が引き伸ばされること等により切断面から突出することがあった。このため、突出した配線が半導体基板に接触して不具合を生じさせることにより、半導体装置の信頼性を低下させる懸念があった。

【0006】

本発明は、上記事情に鑑みなされたものであり、その目的は、ダイシング領域に配線層を有する半導体装置の信頼性を向上させる技術を提供することにある。

【課題を解決するための手段】

【0007】

本発明によれば、半導体基板と、前記半導体基板の素子形成面上に設けられた絶縁膜と、を有し、前記素子形成面に、複数の素子領域と、前記複数の素子領域を分離し、一方の素子領域と他方の素子領域との間を接続する配線を含むダイシング領域と、が設けられ、前記ダイシング領域において、前記半導体基板が除去されているとともに、前記絶縁膜の少なくとも一部を有することを特徴とする半導体ウェーハが提供される。

10

20

30

40

50

**【 0 0 0 8 】**

本発明においては、ダイシング領域において当該半導体基板ウェーハが薄化されているため、機械的応力によりダイシング領域の配線を確実に破断することが可能な構成となっている。また、ダイシング領域において、半導体基板を除去しつつ、配線を有する絶縁膜の一部を残しているため、絶縁膜が半導体基板の端面から張り出して張出部となる構成を実現することができる。これにより、チップ分離後、配線の半導体基板への接触が抑制される。

**【 0 0 0 9 】**

なお、本発明において、ダイシング領域において、半導体基板は完全に除去されていなくても、実質的に除去されればよい。実質的に除去されているとは、半導体ウェーハに面方向の応力を付与した際に、ダイシング領域において半導体ウェーハが破断される程度に除去されていることをいう。

**【 0 0 1 0 】**

また、本発明において、ダイシング領域内の絶縁膜中に前記配線が設けられた構成とすることができる。また、配線は、たとえば、一方の素子形成領域から当該一方の素子形成領域に隣接する他方の素子形成領域にわたって形成された構成とすることができます。

**【 0 0 1 1 】**

本発明の半導体ウェーハにおいて、前記ダイシング領域には、前記絶縁膜中に導電プラグが設けられている構成とすることができます。こうすることにより、ダイシング領域に配線が設けられている場合であってもさらに確実にダイシング可能な構成とすることができます。

**【 0 0 1 2 】**

本発明の半導体ウェーハにおいて、複数の前記導電プラグが、前記ダイシング領域に沿って列状に設けられていてもよい。こうすることにより、所定の位置で確実に破断可能な構成とすることができます。

**【 0 0 1 3 】**

本発明の半導体ウェーハにおいて、前記ダイシング領域の幅が $2 \mu m$ 以上であってもよい。こうすることにより、ダイシングをさらに安定的に行うことができる。また、絶縁膜が半導体基板の端面から張り出して張出部となる構成を確実に実現することができる。

**【 0 0 1 4 】**

本発明によれば、前記半導体ウェーハが前記ダイシング領域で分割されてなることを特徴とする半導体チップが提供される。

**【 0 0 1 5 】**

この構成によれば、ダイシング領域の半導体基板が除去されているため、絶縁膜中が半導体基板の外周縁から外方向に張り出した構成となっている。このため、配線の半導体基板への接触が抑制された構成となっている。よって、製造安定性および信頼性に優れた構成となっている。

**【 0 0 1 6 】**

本発明によれば、半導体基板と、前記半導体基板の素子形成面上に設けられた絶縁膜と、を有し、前記絶縁膜は、前記半導体基板の外周縁よりも外方向へ張り出した張出部を有し、前記張出部の内部に配線が含まれていることを特徴とする半導体チップが提供される。

**【 0 0 1 7 】**

この構成においては、絶縁膜が半導体基板の中心から外方へ張り出した形状を有する、すなわち、半導体チップは絶縁膜から主としてなる庇状の張出部を有する。このため、配線が張出部の端面から突出している場合にも、突出した配線の半導体基板への接触が抑制された構成となっている。よって、これらの接触によるリーク電流の発生等の不具合が抑制され、信頼性に優れた構成となっている。

**【 0 0 1 8 】**

本発明の半導体チップにおいて、前記張出部が前記半導体基板の前記外周縁から $1 \mu m$

10

20

30

40

50

以上突出している構成とすることができる。こうすることにより、半導体チップの信頼性をさらに向上させることができる。

#### 【0019】

本発明によれば、半導体基板の素子形成面上に、絶縁膜中に配線が埋設された配線層を形成する工程と、前記半導体基板の前記素子形成面側を支持基板に固定する工程と、前記支持基板に固定した状態で、前記半導体基板の裏面の側から、前記配線の設けられた領域のうち所定の領域を選択的に薄化し、ダイシング領域を形成する工程と、を含むことを特徴とする半導体ウェーハの製造方法が提供される。

#### 【0020】

この構成によれば、薄化されたダイシング領域が形成されるため、配線が設けられた領域においても安定的なダイシングが可能な構成となっている。また、絶縁膜が半導体基板の端面から張り出して張出部となる構成の半導体チップが得られる半導体ウェーハを安定的に製造可能である。

#### 【0021】

本発明の半導体ウェーハの製造方法において、配線層を形成する前記工程は、前記ダイシング領域において、前記絶縁膜中に導電プラグを埋設する工程を含んでもよい。こうすることにより、配線層を所定の位置で安定的に破断可能な構成とすることができる。また、導電プラグは素子形成領域の接続プラグと同時に形成可能なため、別個の工程を設けることなく作製可能である。このため、簡便な方法である。

#### 【0022】

本発明の半導体ウェーハの製造方法において、導電プラグを埋設する前記工程は、前記ダイシング領域に沿って複数の前記導電プラグを形成する工程を含んでもよい。こうすることにより、配線層を所定の位置でさらに確実に破断可能な構成とすることができる。

#### 【0023】

本発明によれば、前記半導体ウェーハの製造方法により半導体ウェーハを得る工程と、前記半導体基板の前記裏面をダイシングシートに接合する工程と、前記ダイシングシートに接合された前記半導体基板の前記素子形成面から前記支持基板を除去する工程と、記前記半導体ウェーハに応力を付与し、前記ダイシング領域にて前記半導体ウェーハを破断させ、前記半導体ウェーハを複数の半導体チップに分離する工程と、を含むことを特徴とする半導体チップの製造方法が提供される。

#### 【0024】

この方法によれば、ダイシングシートを引き延ばして半導体ウェーハを破断させるため、簡易な方法で複数の半導体チップを安定的に得ることができる。また、破断の際に、配線層の端面から配線が突出した場合にも、突出した配線が半導体基板に接触しないようにすることができる。このため、信頼性に優れた半導体チップを確実に得ることができる。

#### 【0025】

なお、本発明において、半導体ウェーハは、分離後、当該ダイシングシートから除去可能な状態でダイシングシートに接合されている。

#### 【0026】

本発明の半導体チップの製造方法において、半導体ウェーハに応力を付与する前記工程は、前記ダイシングシートを引き延ばす工程を含んでもよい。こうすることにより、簡便な方法でダイシング領域において確実にシリコンウェーハをさらに確実に破断することができる。

#### 【発明の効果】

#### 【0027】

以上説明したように本発明によれば、半導体基板の端面から張り出した形状の絶縁膜を有し、張出部に配線を有する構成とすることにより、ダイシング領域に配線層を有する半導体装置の信頼性を向上させる技術が実現される。

#### 【発明を実施するための最良の形態】

#### 【0028】

10

20

30

40

50

以下、本発明の実施形態について図面を参照して説明する。なお、すべての図面において、共通の構成要素には同一の符号を付し、以下の説明において共通する説明を適宜省略する。また、以下の実施形態において、シリコンウェーハやシリコン基板の素子形成面の側を上または表とし、素子形成面の反対側の面（裏面）を下または裏とする。

#### 【0029】

##### (第一の実施形態)

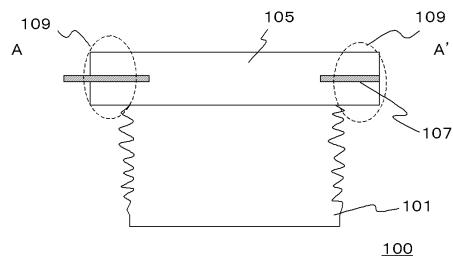

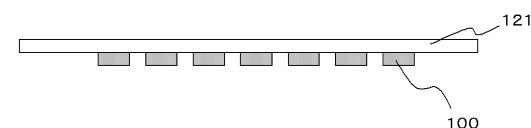

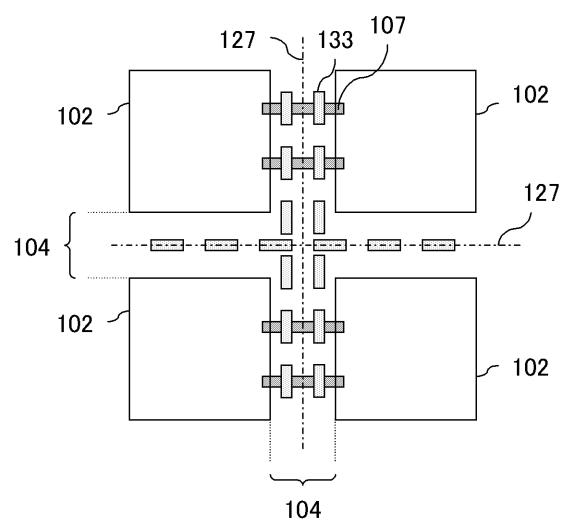

図1(a)および図1(b)は、本実施形態に係る半導体装置の構成を模式的に示す図である。図1(a)は半導体装置100の断面図であり、図1(b)は平面図である。図1(a)は、図1(b)のA-A'断面を示している。図1(a)および図1(b)に示したように、半導体装置100は、シリコン基板101の素子形成面に絶縁層105が設けられた構成である。シリコン基板101の素子形成面にシリコン酸化膜が形成され、その表面に絶縁層105が設けられてもよい。絶縁層105は、複数の絶縁膜の積層体であって、配線層を有する。配線層は、絶縁膜中に埋設されたCuの配線107を有する。シリコン基板101の端面から、絶縁層105が張り出しており、張出部109が設けられている。すなわち、絶縁層105は、シリコン基板101の端面から突出した張出部109を有する。配線107は、張出部109中に設けられている。

#### 【0030】

張出部109のシリコン基板101の端面からの長さは、たとえば1μm以上、好ましくは2μm以上とすることができる。こうすることにより、後述するダイシングにより半導体装置100を得る際の配線107の飛び出しによる半導体装置100のショート等の不具合の発生を確実に抑制することができる。また、張出部109がシリコン基板101の端面から張り出している距離は、たとえば5μm以下とすることができる。こうすることにより、シリコンウェーハ上の半導体装置100の集積度を向上させることができる。また、絶縁層105の厚さはたとえば3~10μm程度とすることができます。

#### 【0031】

なお、図1(a)および図1(b)に、先端が絶縁層105の側断面から突出している配線107が示されているが、突出している必要はない。突出している場合、配線107の突出部分の長さは、張出部109の長さよりも小さいことが好ましい。

#### 【0032】

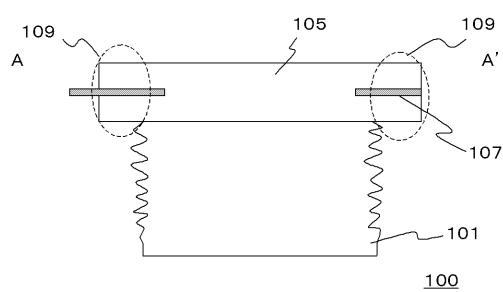

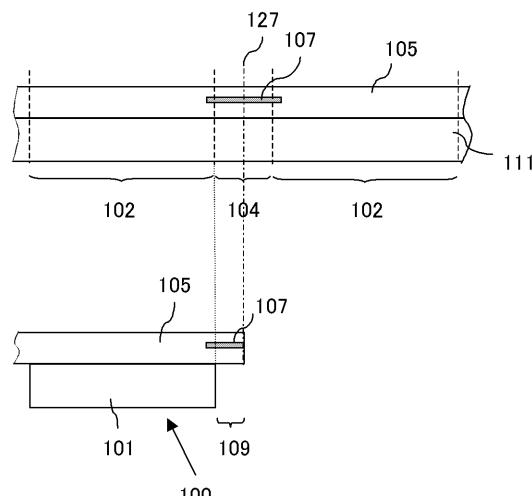

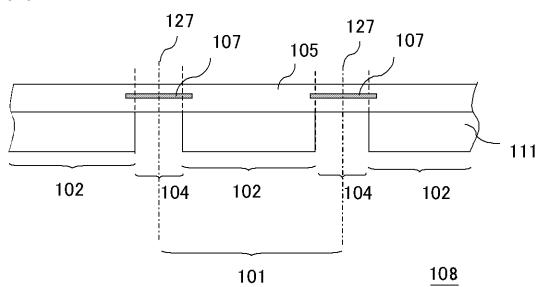

図13は、本実施形態に係る半導体ウェーハの構成を模式的に示す断面図である。図13に示した半導体ウェーハ108は、半導体基板であるシリコンウェーハ111の素子形成面に絶縁層105が設けられた構成である。半導体ウェーハ108は、複数の素子領域102および複数のダイシング領域104を有する。

#### 【0033】

半導体ウェーハ108では、ダイシング領域104において、シリコンウェーハ111が除去されている。また、ダイシング領域104において、絶縁層105を有している。また、ダイシング領域104には、配線107が設けられている。配線107は、ダイシング領域104内の絶縁層105に埋設されており、複数の素子領域102の一方と他方との間を接続している。

#### 【0034】

このように構成された半導体ウェーハ108において、ダイシングライン127でダイシング領域104を破断すると、図1(a)および図1(b)に示した半導体装置100が複数得られる。

#### 【0035】

次に、図1に示した半導体装置100の作製方法を説明する。半導体装置100は、1枚のシリコンウェーハに複数個同時に形成され、ダイシングされることにより得られる。図2、図3(a)~図3(d)、図4(a)~図4(d)、図5、図6、および図7(a)~図7(c)は、本実施形態に係る半導体装置100の製造工程を説明する断面図である。以下、これらの図を用いて半導体装置100の製造手順を説明する。

#### 【0036】

10

20

30

40

50

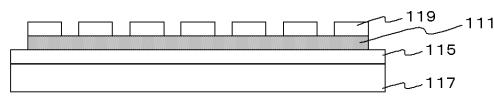

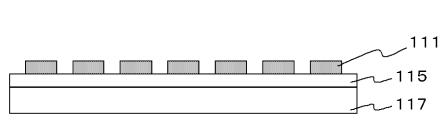

まず、図2に示したように、シリコンウェーハ111表面の素子形成面に、所定の素子や配線107を有する層を形成し、複数の素子領域102およびこれらを区画するダイシング領域104を設ける。シリコンウェーハ111の素子形成面には、シリコン酸化膜として自然酸化膜(不図示)が形成されている。シリコンウェーハ111の厚さは、たとえば、1mm程度とする。

#### 【0037】

配線107は絶縁層105中に設けられ、その一部は、複数の半導体装置100にわたって形成され、これらを接続している。絶縁層105が複数の配線層を有する多層配線構造を有していてもよい。なお、図2において、上の図はウェーハの構成を示し、下の図は、ウェーハの構成に対応して得られる半導体装置100の構成を示している。

10

#### 【0038】

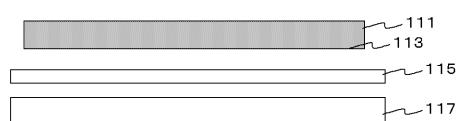

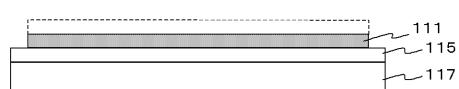

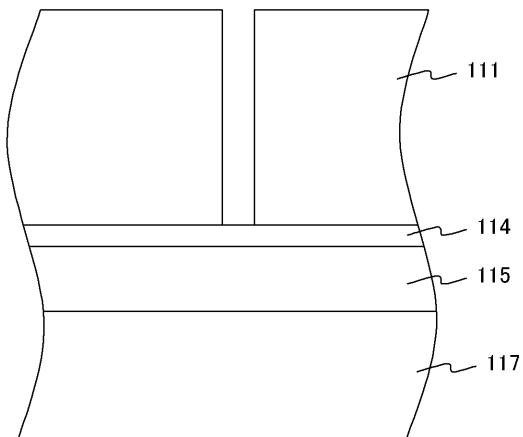

次に、シリコンウェーハ111をダイシングする。なお、図3(a)～図3(d)および図4(a)～図4(d)においては、シリコンウェーハ111上の絶縁層105を不図示とした。ただし、図4(b)および図4(c)では、シリコンウェーハ111の素子形成面に設けられた絶縁層105の一部である絶縁層114を示した。また、図3(a)では、シリコンウェーハ111の絶縁層105が設けられている側の面すなわち素子形成面113を示した。

#### 【0039】

まず、ガラスからなる支持板117上に、粘着テープ115およびシリコンウェーハ111をこの順に積層する(図3(a))。このとき、シリコンウェーハ111の素子形成面113を粘着テープ115に接合する。そして、粘着テープ115を介してシリコンウェーハ111と支持板117を接着する(図3(b)の点線)。

20

#### 【0040】

粘着テープ115は基材とその両面に形成された粘着層から構成されている。粘着テープを構成する基材としては、たとえば、ポリオレフィン系樹脂、ポリエステル系樹脂などが用いられる。さらに具体的には、たとえばポリエチレンテレフタレート等とすることができます。

30

#### 【0041】

また、粘着層は、基材の一方の面に設けられた硬化層と、他方の面に設けられた発泡層とからなる。粘着層を構成する粘着剤としては、たとえば、アクリル系エマルジョン型粘着剤、アクリル系溶剤型粘着剤、ウレタン系粘着剤などが用いられる。硬化層に用いられる粘着剤は、たとえば紫外線等の照射により硬化する光硬化性の材料とすることができる。また、剥離層に用いられる粘着剤は、紫外線等の照射により発泡して剥離する光剥離性の材料とすることができる。また、硬化層の硬化波長領域と剥離層の剥離波長領域とが異なるようにこれらの材料が選択される。

30

#### 【0042】

シリコンウェーハ111と支持板117とを接合させる際には、粘着テープ115の発泡面をシリコンウェーハ111側に設け、硬化面を支持板117側に設ける。

#### 【0043】

また、支持板117は、シリコンウェーハ111の薄化加工のプロセスにおける、熱、薬剤、外力などに対する耐性を備えている材料であればよく、たとえば、石英基板やパイレックス(登録商標)基板等のガラス基板とすることができます。また、ガラス基板以外の材料としてもよい。たとえば、アクリル樹脂などのプラスチックス等の基板を用いてもよい。シリコンウェーハ111を支持板117に固定することにより、後述するシリコンウェーハ111の薄化加工時の反りや外力による破損等を抑制することができる。

40

#### 【0044】

次に、シリコンウェーハ111を裏面研削により薄化する(図3(b))。裏面研削は、機械的研磨により行う。研削後のシリコンウェーハ111の厚さは適宜選択することができるが、たとえば、30～200μm程度、さらに具体的には、たとえば100μmとすることができる。

50

## 【0045】

次に、シリコンウェーハ111の裏面側に、素子領域102を被覆しダイシング領域104を開口部とするレジストパターン119を形成する(図3(c))。

## 【0046】

開口部すなわちダイシング領域104の幅は、張出部109のシリコン基板101の端面からの距離に応じて適宜設定することができるが、たとえば2μm以上とすることができます。こうすることにより、半導体装置100に張出部109を安定的に形成することができる。

## 【0047】

また、ダイシング領域104の幅は、たとえば7μm以下、好ましくは5μm以下とすることができる。こうすることにより、半導体装置100の小型化が可能となる。また、シリコン基板101中の素子領域102の集積度を高めることができる。10

## 【0048】

また、張出部109の張り出している領域の長さすなわちシリコン基板101の端面からの距離は、ダイシング領域104の幅の1/3~2/3の長さ、さらに具体的には、ダイシング領域104の幅の1/2程度の長さとすることができます。こうすれば、張出部109の端面から配線107が突出した場合にも、突出した配線107がシリコン基板101に接触しないようにすることができます。

## 【0049】

そして、レジストパターン119をマスクとするエッチングによりシリコンウェーハ111を選択的に除去し、選択的に薄化する(図3(d))。なお、このときのエッチングは、シリコンと絶縁膜の選択比が高い条件で行うものとする。ここで、シリコンウェーハ111の表面には絶縁層105が設けられ、絶縁層105にはダイシング領域104において配線107が形成されている。このため、エッチングは、配線107(図5では不図示)の設けられた絶縁層105にて停止する。20

## 【0050】

エッチングは、たとえばボッシュ法を用い、保護膜の形成によりシリコンウェーハ111の壁面やレジストパターンを保護しながら行ってもよい。この場合、SF<sub>6</sub>とO<sub>2</sub>の同時照射とC<sub>4</sub>F<sub>8</sub>の照射とを交互に行い、エッチングを行う。

## 【0051】

図5は、図3(d)に示した断面の一部を拡大した図である。図3(d)には示していないが、図4に示したように、ダイシング領域104において、シリコンウェーハ111の素子形成面側には、貫通孔は形成されずに絶縁層105の一部であって配線107を有する絶縁層114が残存している。30

## 【0052】

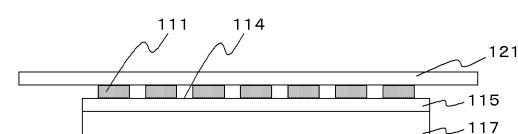

次に、レジストパターン119をドライエッチングによりシリコンウェーハ111の裏面から除去する(図4(a))。そして、シリコンウェーハ111の裏面をダイシングテープ121に接着する(図4(b))。

## 【0053】

ダイシングテープ121の大きさは、シリコンウェーハ111と同一もしくはそれよりも大きな寸法とすることが好ましい。こうすれば、これらを接着した際に、ダイシングテープ121の端部がシリコンウェーハ111の外周部分から離れて位置するようになることができる。このような構成にあれば、図6および図7(a)~図7(c)を用いて後述する工程で、シリコンウェーハ111を複数の半導体装置100に安定的に分離することができる。40

## 【0054】

ダイシングテープ121は、基材の片面に粘着層として前述の硬化層が設けられたテープとすることができます。硬化層の材料として、紫外線硬化材料を用いることができる。ダイシングテープ121の各構成部材は、たとえば粘着テープ115の各構成部材に利用可能な材料とすることができます。また、ダイシングテープ121は、面内方向に引き延ばす50

ことが容易な材料とすることができる。こうすれば、後述するダイシング領域 104 の分離を簡便な方法で確実に行うことができる。

#### 【0055】

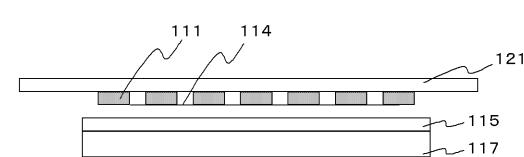

そして、ダイシングテープ 121 に固定したシリコンウェーハ 111 を、支持板 117 および粘着テープ 115 から剥離する（図 4（c））。これにより、シリコンウェーハ 111 が支持板 117 からダイシングテープ 121 に転写される。たとえば、紫外線照射により剥離する粘着テープ 115 を用いている場合には、支持板 117 側から光照射を行うことにより剥離する。この状態では、絶縁層 114 の残存により、シリコンウェーハ 111 が複数の半導体装置 100 に分離されておらず、一体の状態である。

#### 【0056】

次に、ダイシングテープ 121 を引き延ばすことにより、シリコン基板 101 に応力を付与し、薄化した素子領域 102 の絶縁層 114 を破断する。これにより、複数の半導体装置 100 がダイシングテープ 121 上に接着された状態となる（図 4（d））。ダイシングテープ 121 から半導体装置 100 を剥離することにより、半導体装置 100 が図 1 に示した半導体装置 100 が得られる。

#### 【0057】

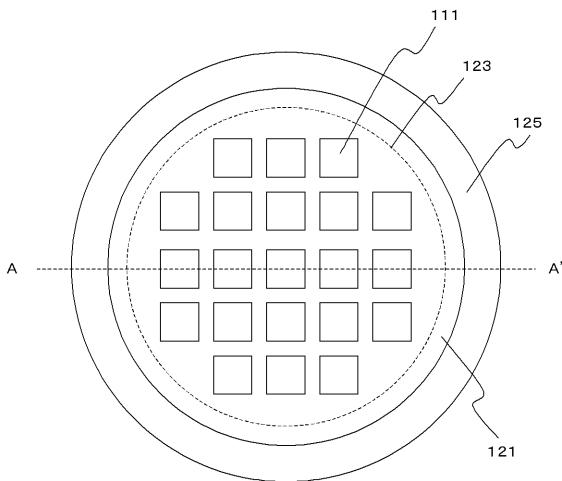

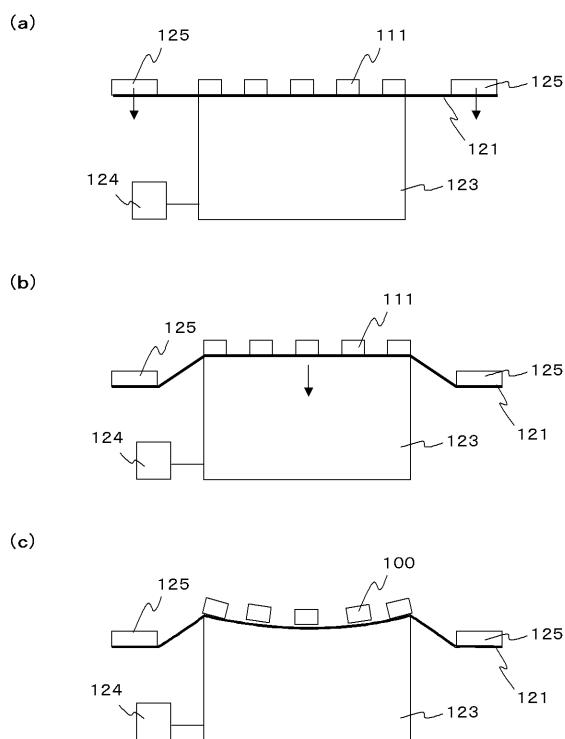

図 6 および図 7（a）～図 7（c）は、シリコンウェーハ 111 をダイシング領域 104 にて切斷して複数の半導体装置 100 に分離する手順を模式的に示す図である。図 6 は、シリコンウェーハ 111 をダイシング装置に設置した様子を模式的に示す平面図である。また、図 7（a）～図 7（c）は、図 6 の A-A' 断面図である。これらの図を参照して、シリコンウェーハ 111 のダイシング方法を以下説明する。

#### 【0058】

まず、シリコンウェーハ 111 とダイシングテープ 121 の接合体をステージ 123 上にほぼ水平に設置する。ダイシングテープ 121 のシリコンウェーハ 111 との界面と反対側の面をステージ 123 と接触させる。ステージ 123 の断面積はダイシングテープ 121 の断面積より小さい。また、ステージ 123 はポンプ 124 に接続し、内部を減圧可能な構成となっている。また、ステージ 123 の上面は、開口部を有する。また、ダイシングテープ 121 の周縁部上に押さえリング 125 が設けられる（図 6、図 7（a））。押さえリング 125 は、たとえば管状の金属板とすることができる。

#### 【0059】

次に、図 7（a）中に矢印で示したように、押さえリング 125 を鉛直下方向に押し下げる（図 7（b））。このとき、シリコンウェーハ 111 が接着されたダイシングテープ 121 はステージ 123 上に載置されているため、その 111 表面に反り等は生じない。

#### 【0060】

次に、図 7（b）中に矢印で示したように、ポンプ 124 を駆動させてステージ 123 の内部を減圧する。ステージ 123 の上面には開口部（不図示）が設けられているため、減圧により、ステージ 123 上のダイシングテープ 121 はステージ 123 の内部に向かって力が加わる。このため、ダイシングテープ 121 の底面が凹状に湾曲し、引き延ばされる。このとき、ダイシングテープ 121 に接着されたシリコンウェーハ 111 にが加わることにより、一体の状態であったシリコンウェーハ 111 は、薄化された絶縁層 114 にて破断される。このとき、ダイシング領域 104 における絶縁層 114 に埋設された配線 107 も機械的に破断される。こうして、一枚のシリコンウェーハ 111 が複数の半導体装置 100 に分離される（図 7（c））。

#### 【0061】

そして、ダイシングテープ 121 から分離されたチップを取り外すことにより、図 1 に示した半導体装置 100 を得ることができる。

#### 【0062】

次に、半導体装置 100 の効果を説明する。

半導体装置 100 は、シリコン基板 101 の外周縁から絶縁層 105 から張り出した張出部 109 が形成されている。また、絶縁層 105 の端面に配線 107 が露出した構成と

10

20

30

40

50

なっている。張出部 109 が形成されているため、作製時のダイシング（図 7（c））において、配線 107 が引き延ばされ、シリコン基板 101 の端面から突出した場合にも、突出した配線 107 がシリコン基板 101 に接触しない構成となっている。このため、半導体装置としての信頼性に優れた構成となっている。また、簡便なプロセスで製造可能であり、歩留まりの良好な半導体装置となっている。この効果は、配線 107 の材料が Cu や Al 等の比較的高度の小さい金属である場合に顕著に発揮される。

#### 【0063】

また、半導体装置 100 は、裏面研削を行った後に、シリコンウェーハ 111 の選択的なエッチングによりシリコンウェーハ 111 の一部を除去し、ダイシングテープ 121 に転写する方法を用いて製造される。このため、ダイシング領域 104 の絶縁層 105 中に配線 107 が埋設された構成でありながら、シリコンウェーハ 111 に機械的な力を付与して容易に複数の半導体装置 100 に分割可能である。よって、半導体装置 100 の製造時のダイシング時の削り屑の発生等が抑制された構成であり、製造安定性に優れる。10

#### 【0064】

本実施形態に係る半導体装置 100 の構成は、たとえば、チップサイズの小さいマイクロコンピューター等に好適に適用される。このようなチップでは、信頼性試験の際にテスターの針あてが困難であるため、複数のチップの間を配線で接続し、ボンディングパッドを用いて測定されることが多い。この場合にも、張出部 109 を設けることにより、ダイシングされた端面から突出した配線がシリコン基板 101 に接触しないようにすることができます。20

#### 【0065】

次に、本実施形態に係る半導体装置 100（図 1）を、従来の半導体装置と対比してさらに説明する。図 8（a）および図 8（b）は本実施形態に係る半導体装置 100 および従来の半導体装置をそれぞれ模式的に示す断面図である。20

#### 【0066】

図 8（b）に示したように、従来の半導体装置は、絶縁層 205 がシリコン基板 201 の端面から張り出していない。このため、切断面に配線 207 が形成されている場合、これが端面に露出してシリコン基板 201 と接触しやすい構成となっている。また、ダイシング領域に配線 207 が存在していると、従来の方法でエッチングにより従来の半導体装置を得るのは困難であった。また、シリコンウェーハからダイシングにより従来の半導体装置を得る場合、ダイシング時に配線 207 の端部が引き延ばされて突出しやすい。このとき、絶縁層 205 とシリコン基板 201 の端面の位置が揃った従来の構成では、図 8（b）に示したように、配線 207 の配線部分がシリコン基板 201 に接触しやすい。このため、リーク電流が生じる等の不具合が生じる懸念があった。30

#### 【0067】

これに対し、図 8（a）に示したように、本実施形態に係る半導体装置 100 は、シリコン基板 101 よりも絶縁層 105 が突出しているため、配線 107 の端部が突出した場合にも配線 107 がシリコン基板 101 に接触しにくい構成となっている。なお、図 8（a）では、図 1（a）の構成に対応させ、図中左側の張出部 109 に設けられた配線 107 が絶縁層 105 の端面から突出しており、図中右側の張出部 109 に設けられた配線 107 が絶縁層 105 の端面から突出していない構成を例示したが、配線 107 の突出の有無に制限はない。また、従来、配線 107 がダイシング領域 104 にある場合にはエッチングにより分割して半導体装置 100 を得ることは困難であったが、半導体装置 100 は、シリコンウェーハ 111 を部分的に除去した後、ダイシングテープ 121 を引き延ばしてダイシング領域 104 を破断して得られるため、製造容易性に優れた構成となっている。40

#### 【0068】

なお、本実施形態において、ダイシング領域 104 の切断方法は図 6 および図 7（a）～図 7（c）を用いて前述した方法には限られない。ダイシングテープ 121 を他の方法により面方向に引き延ばしたり、曲げたりすることによってもシリコンウェーハ 111 を50

切断し、半導体装置 100 を得ることができる。

#### 【0069】

なお、本実施形態において、半導体基板 101 の端面全面に張出部 109 が形成されている構成を例に説明をしたが、半導体装置 100 は、少なくとも配線 107 が絶縁層 105 の端面に露出している領域において、張出部 109 を有していればよい。シリコン基板 101 全面に張出部 109 を設けることにより、ダイシングをさらに確実に行うことが可能となり、製造安定性を顕著に向上させることができる。

#### 【0070】

##### (第二の実施形態)

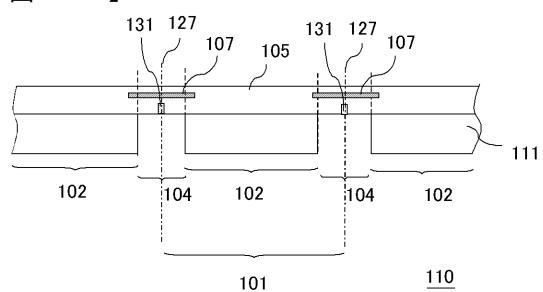

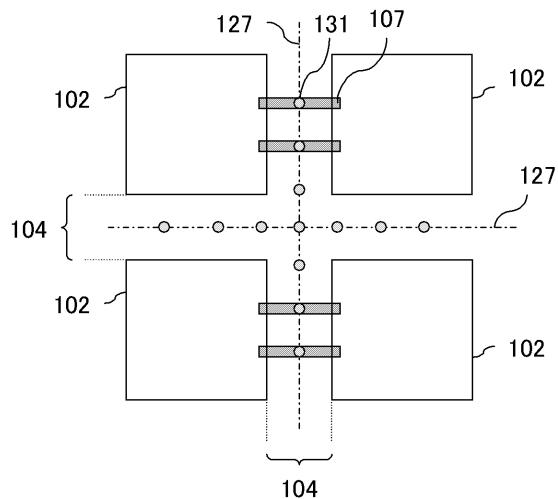

本実施形態では、図 1 に示した半導体装置 100 が得られる半導体ウェーハの構成の別の例を示す。図 14 は、本実施形態に係る半導体ウェーハの構成を模式的に示す断面図である。図 14 に示した半導体ウェーハ 110 の基本構成は、第一の実施形態において図 13 に示した半導体ウェーハと同様であるが、ダイシング領域 104 において、絶縁層 105 中にダイシング用プラグ 131 が設けられた点が異なる。本実施形態では、第一の実施形態と異なる部分を中心に、以下説明する。

#### 【0071】

図 14 に示した半導体ウェーハ 110 において、ダイシング用プラグ 131 は、ダイシング領域 104 内の絶縁層 105 に埋設されている。図 14 では、ダイシング用プラグ 131 は配線 107 よりもシリコンウェーハ 111 の素子形成面に近い側に設けられている。また、図 14 では、配線 107 は、ダイシングライン 127 上に設けられている。

#### 【0072】

半導体ウェーハ 110 では、ダイシング領域 104 にダイシング用プラグ 131 が設けられている。このため、ダイシングの際に、ダイシング用プラグ 131 を起点として破断が生じる。よって、図 13 に示した半導体ウェーハ 108 よりもさらに容易にダイシング可能な構成となっている。

#### 【0073】

また、素子領域 102 の端部からダイシング用プラグ 131 までの距離を適宜選択してダイシング用プラグ 131 を設けることにより、ダイシングの位置を調節することができる。このため、半導体ウェーハ 110 を分離して半導体装置 100 を得る際に、素子領域 102 の端部からダイシング用プラグ 131 までの距離に応じて半導体装置 100 の張出部 109 の長さを調節することが可能な構成となっている。よって、ダイシング時に露出した配線 107 が半導体装置 100 のシリコン基板 101 に接触することがさらに確実に抑制された構成となっている。

#### 【0074】

次に、半導体ウェーハ 110 のダイシング領域 104 におけるダイシング用プラグ 131 の配置についてさらに詳細に説明する。

#### 【0075】

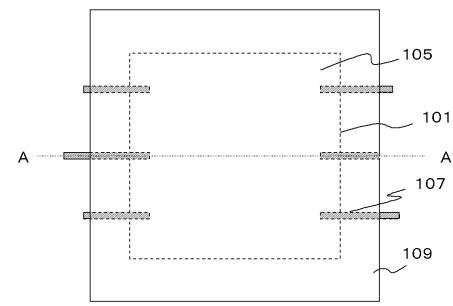

図 9 は、シリコンウェーハ 111 に形成された複数の素子領域 102 およびこれを隔てるダイシング領域 104 の一部の構成を模式的に示す平面図である。図 9 に示したように、ダイシング用プラグ 131 をダイシングライン 127 上に形成してもよい。ダイシング用プラグ 131 は絶縁膜が積層された絶縁層 105 中のどの層に設けてもよく、分割して得られる半導体装置 100 の設計に応じて所定の工程で形成することができる。

#### 【0076】

また、ダイシング用プラグ 131 の形状に特に制限はなく、円柱、橢円中、角柱等の柱状体等することができるが、素子領域 102 に形成される接続プラグと同じ形状とすることができる。こうすれば、ダイシング用プラグ 131 は、絶縁層 105 中に接続プラグを作製するときに、素子領域 102 中の孤立プラグとして同時に形成されるため、独立した手順を設けることなく確実に張出部 109 の張り出している領域の長さを調節することができる。

#### 【0077】

10

20

30

40

50

図9に示したシリコンウェーハ111をダイシング領域104の幅中心のダイシングライン127で切断すると、素子領域102の外周にダイシング領域104の一部が残存する形状の半導体装置100に分割される。ダイシング用プラグ131をダイシングライン127に沿って設けることにより、配線107を有する絶縁層105が設けられたシリコンウェーハ111を分割する際に、ダイシング用プラグ131の近傍で確実に破断させることができる。このため、素子領域102の外部に残存するダイシング領域104の幅を、素子領域102からダイシング用プラグ131程度の幅となるように調節することが可能である。よって、分割により生成する半導体装置100の張出部109のシリコン基板101の端面からの長さを確実に調節することができる。

## 【0078】

なお、図9に示したように、ダイシングライン127上に設けられるダイシング用プラグ131を、配線107上に形成することにより、配線107をさらに確実に破断することができる。

## 【0079】

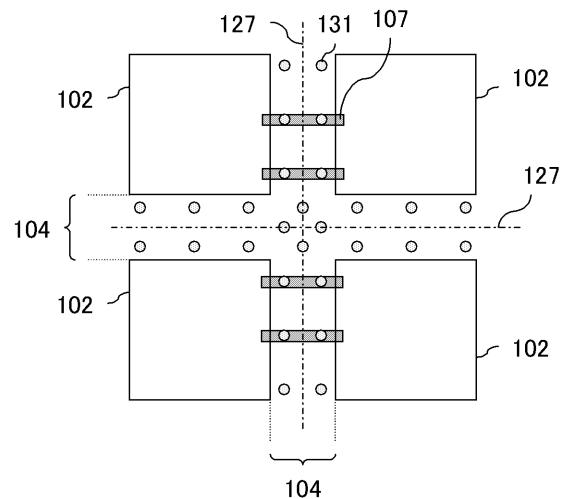

図10～図12は、張出部109を調節するのに適したシリコンウェーハ111の別の構成を示す図である。

図10は、ダイシングライン127に平行に二列のダイシング用プラグ131を設けたシリコンウェーハ111の構成を示す図である。図11に示したように、複数のダイシング用プラグ131の列をダイシング領域104に配置することにより、隣接する素子領域102を分割して得られる複数の半導体装置100に形成される張出部109のシリコン基板101の端面からの長さをそれぞれ所定の長さにさらに確実に調節することができる。

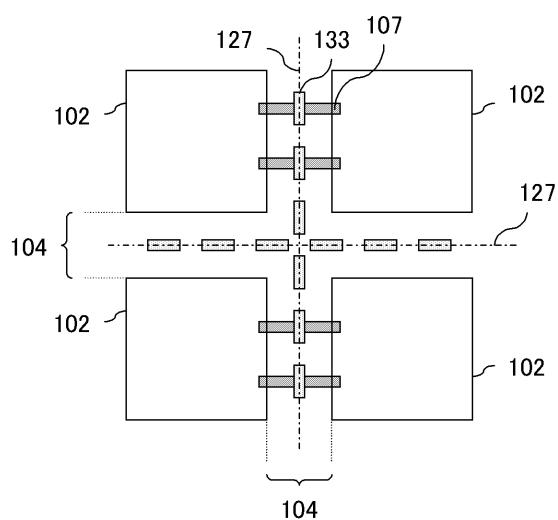

## 【0080】

図11は、ストライプ状のダイシング用プラグ133をダイシングライン127上に設けた例である。ストライプ状の柱状体をダイシングライン127の延在方向に沿って延在させることにより、配線107がダイシング領域104に設けられたシリコンウェーハ111についても、さらに確実にダイシングを行うことができる。

## 【0081】

また、図12は、配線107を有するダイシング領域104に、ストライプ状のダイシング用プラグ133を二列に配置した例である。こうすれば、ダイシング領域104のうち配線107を有する領域のダイシングをさらに確実に行うことができる。また、張出部109がシリコン基板101の端面から張り出している長さを所定の長さにさらに確実に調節することができる。

## 【0082】

以上、発明の好適な実施形態を説明した。しかし、本発明は上述の実施形態に限定されず、当業者が本発明の範囲内で上述の実施形態を変形可能なことはもちろんである。

## 【0083】

たとえば、以上の実施形態においては、半導体基板としてシリコン基板を用いたが、GaN基板等の化合物半導体基板としてもよい。

## 【0084】

また、以上の実施形態においては、配線107としてCuを用いたが、導電率の高い他の金属を用いてもよい。たとえば、Al、Ni、W等の金属を用いてもよい。また、ダイシングライン127近傍において、配線107の幅を他の領域よりも細くしてもよい。こうすれば、配線107をさらに確実に切斷することができる。

## 【実施例】

## 【0085】

本実施例では、第一の実施形態に記載の方法を用いて、張出部109を有する半導体装置100(図1)を作製した。裏面研削前のシリコンウェーハ111の厚さを1mmとし、裏面研削後のシリコンウェーハ111の厚さを200μmとした。また、粘着テープ115およびダイシングテープ121として、それぞれ積水化学社製セルファおよびリンテ

ック社製 Adw ill - D を用いた。配線 107 の材料は Cu とした。

#### 【0086】

ダイシング領域 104 の幅を 5 μm としてダイシングを行ったところ、シリコン基板 101 の端面から平均 2 μm 突出した張出部 109 を有する半導体装置 100 が得られた。張出部 109 中の Cu 配線は、一部絶縁層 105 の端面から突出していたが、シリコン基板 101 には接触していなかった。これより、本発明の方法を用いて簡便なプロセスで配線 107 とシリコン基板 101 が接触しない構成の半導体装置 100 を得ることができた。

#### 【図面の簡単な説明】

#### 【0087】

【図 1】第一の実施形態に係る半導体装置の構成を模式的に示す図である。

【図 2】図 1 の半導体装置の製造工程を説明する断面図である。

【図 3】図 1 の半導体装置の製造工程を説明する断面図である。

【図 4】図 1 の半導体装置の製造工程を説明する断面図である。

【図 5】図 1 の半導体装置の製造工程を説明する断面図である。

【図 6】図 1 の半導体装置の製造工程を説明する平面図である。

【図 7】図 1 の半導体装置の製造工程を説明する断面図である。

【図 8】第一の実施形態に係る半導体装置と従来の半導体装置の構成を示す断面図である。

。

【図 9】第二の実施形態に係る半導体ウェーハの構成を模式的に示す平面図である。

【図 10】第二の実施形態に係る半導体ウェーハの構成を模式的に示す平面図である。

【図 11】第二の実施形態に係る半導体ウェーハの構成を模式的に示す平面図である。

【図 12】第二の実施形態に係る半導体ウェーハの構成を模式的に示す平面図である。

【図 13】本実施形態に係る半導体ウェーハの構成を模式的に示す断面図である。

【図 14】本実施形態に係る半導体ウェーハの構成を模式的に示す断面図である。

#### 【符号の説明】

#### 【0088】

100 半導体装置

101 シリコン基板

102 素子領域

104 ダイシング領域

105 絶縁層

107 配線

108 半導体ウェーハ

109 突出部

110 半導体ウェーハ

111 シリコンウェーハ

113 素子形成面

114 絶縁層

115 粘着テープ

117 支持板

119 レジストパターン

121 ダイシングテープ

123 ステージ

124 ポンプ

125 リング

127 ダイシングライン

131 ダイシング用プラグ

133 ダイシング用プラグ

10

20

30

40

【図1】

(a)

(b)

【図2】

【図3】

(a)

(b)

(c)

(d)

【図4】

(a)

(b)

(c)

(d)

【図5】

【図6】

【図7】

【図8】

【 図 9 】

【 図 1 0 】

【図11】

【図12】

【図13】

【図14】