(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5346435号

(P5346435)

(45) 発行日 平成25年11月20日(2013.11.20)

(24) 登録日 平成25年8月23日(2013.8.23)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/78 29/78

616K 616T

H01L 29/786 (2006.01)

H01L 29/78 29/78

617K 627C

請求項の数 7 (全 24 頁)

|              |                               |           |                                                                                                                                                        |

|--------------|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-305394 (P2006-305394)  | (73) 特許権者 | 512187343<br>三星ディスプレイ株式会社<br>Samsung Display Co., Ltd.<br>大韓民国京畿道龍仁市器興区三星二路95<br>95, Samsung 2 Ro, Gih<br>eung-Gu, Yongin-City<br>, Gyeonggi-Do, Korea |

| (22) 出願日     | 平成18年11月10日 (2006.11.10)      |           |                                                                                                                                                        |

| (65) 公開番号    | 特開2007-208237 (P2007-208237A) |           |                                                                                                                                                        |

| (43) 公開日     | 平成19年8月16日 (2007.8.16)        |           |                                                                                                                                                        |

| 審査請求日        | 平成21年11月9日 (2009.11.9)        |           |                                                                                                                                                        |

| (31) 優先権主張番号 | 10-2006-0010831               | (74) 代理人  | 100121382                                                                                                                                              |

| (32) 優先日     | 平成18年2月3日 (2006.2.3)          | (72) 発明者  | 弁理士 山下 託嗣<br>林 郡 基<br>大韓民国忠清南道天安市双龍洞2045現代ホームタウンアイパーク114-303                                                                                           |

| (33) 優先権主張国  | 韓国 (KR)                       |           |                                                                                                                                                        |

| (31) 優先権主張番号 | 10-2006-0012147               |           |                                                                                                                                                        |

| (32) 優先日     | 平成18年2月8日 (2006.2.8)          |           |                                                                                                                                                        |

| (33) 優先権主張国  | 韓国 (KR)                       |           |                                                                                                                                                        |

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板とその製造方法、及び、薄膜トランジスタ基板製造用のマスク

## (57) 【特許請求の範囲】

## 【請求項 1】

多数のゲートラインと、

前記ゲートラインと交差する多数のソースラインと、

前記多数のソースラインおよびゲートラインによって定義される多数の画素領域にそれ

ぞれ提供される多数の画素電極、および前記多数のゲートラインの何れか一つと接続されたゲート電極、前記多数のソースライン

の何れか一つと接続されたソース電極および前記多数の画素電極の一つと接続されたド

レーン電極を含み、前記多数の画素電極それぞれに提供される多数の薄膜トランジスタを

含み、活性層が前記多数の薄膜トランジスタそれぞれの前記ソース電極およびドレーン電極の

間に提供されたチャネル領域内で露出され、前記活性層は、前記チャネル領域から延長されて前記チャネル領域の外側に突出する

とき、前記活性層は、前記ソースラインの幅の30%以下の長さで突出し、前記多数のソース電極は、前記対応するソースラインから延長された第1突出部および

第2突出部を含み、前記第1突出部は、前記ゲート電極の縁と部分的に重複され、第1突

出部の長さは、第2突出部の長さより短く、前記ゲート電極は、前記ドレーン電極の方向に前記ゲート電極の一部を突出させた突起

部を含み、前記突起部は、前記ドレーン電極の縁と部分的に重複する薄膜トランジスタ基

板。

## 【請求項 2】

前記第1突出部の長さは、前記第2突出部の長さと異なり、

前記第1突出部と前記ゲート電極との間の重畠面積は、前記第2突出部と前記ゲート電極との間の重複面積と異なる請求項1に記載の薄膜トランジスタ基板。

## 【請求項 3】

前記ドレーン電極は、前記画素電極と接続されるドレーンコンタクトホールを含み、前記ドレーンコンタクトの下部には光遮断部が提供される請求項1又は2のいずれか1つに記載の薄膜トランジスタ基板。

## 【請求項 4】

前記多数のソース電極それぞれは、前記ソースラインと実質的にU字-形状を形成するために対応するソースラインから延長された第1突出部および第2突出部を含み、前記ドレーン電極の一部は、前記第1突出部および第2突出部の間の領域内に延長され、

前記第1突出部の長さは、前記第2突出部の長さと異なり、

前記第1突出部と前記ゲート電極との間の重複面積は、前記第2突出部と前記ゲート電極との間の重複面積と異なる請求項1から3のいずれか1つに記載の薄膜トランジスタ基板。

## 【請求項 5】

多数のゲートラインと、

前記ゲートラインと交差する多数のソースラインと、

前記多数のソースラインおよびゲートラインによって定義される多数の画素領域にそれ

ぞれ提供される多数の画素電極、および

前記多数のゲートラインの何れか一つと接続されたゲート電極、前記多数のソースラインの何れか一つと接続されたソース電極および前記多数の画素電極の一つと接続されたドレーン電極を含み、前記多数の画素電極それぞれに提供される多数の薄膜トランジスタを

含み、

活性層が前記多数の薄膜トランジスタそれぞれの前記ソース電極およびドレーン電極の間に提供されたチャネル領域内で露出され、

前記活性層は、前記チャネル領域から延長されて前記チャネル領域の外側に突出するとき、前記活性層は、前記ソースラインの幅の30%以下の長さで突出し、

前記多数のソース電極は、前記対応するソースラインから延長された第1突出部および第2突出部を含み、前記第1突出部は、前記ゲート電極の縁と部分的に重畠され、第1突出部の長さは、第2突出部の長さより短く、

前記ソース電極は、ゲート電極と部分的に重複する第1突出部および第2突出部とこれらを接続する接続部を含み、前記接続部と前記第1突出部および第2突出部と前記ゲート電極の重複面積は、前記ドレーン電極と前記ゲート電極の重複面積と同一である、薄膜トランジスタ基板。

## 【請求項 6】

多数のゲートラインと、

前記ゲートラインと交差する多数のソースラインと、

前記多数のソースラインおよびゲートラインによって定義される多数の画素領域にそれ

ぞれ提供される多数の画素電極、および

前記多数のゲートラインの何れか一つと接続されたゲート電極、前記多数のソースラインの何れか一つと接続されたソース電極および前記多数の画素電極の一つと接続されたドレーン電極を含み、前記多数の画素電極それぞれに提供される多数の薄膜トランジスタを

含み、

前記ゲート電極は、前記ドレーン電極の方向に前記ゲート電極の一部を突出させた突起部を含み、前記突起部は、前記ドレーン電極の縁と部分的に重複し、

活性層は、前記ソースライン、前記ソース電極および前記ドレーン電極の下部に形成され、

前記活性層は、前記多数の薄膜トランジスタそれぞれのソースおよびドレーン電極の間

10

20

30

40

50

に提供されるチャネル領域内で露出し、

前記多数のソース電極それぞれは、前記ソースラインと実質的にU字-形状を形成するために対応するソースラインから延長された第1突出部および第2突出部を含み、前記ドレーン電極の一部は、前記第1突出部および第2突出部の間の領域内に延長され、

前記突起部は、第1および第2突起を含み、前記第1突起は、前記ドレーン電極の一縁と部分的に重複し、前記第2突起は、前記ドレーン電極の他縁と部分的に重複する薄膜トランジスタ基板。

#### 【請求項 7】

多数のゲートラインと、

前記ゲートラインと交差する多数のソースラインと、

10

前記多数のソースラインおよびゲートラインによって定義される多数の画素領域にそれぞれ提供される多数の画素電極、および

前記多数のゲートラインの何れか一つと接続されたゲート電極、前記多数のソースラインの何れか一つと接続されたソース電極および前記多数の画素電極の一つと接続されたドレーン電極を含み、前記多数の画素電極それぞれに提供される多数の薄膜トランジスタを含み、

前記ソース電極は、前記ゲート電極と部分的に重複する第1突出部および第2突出部とこれらを接続する接続部を含み、

前記接続部および前記第1突出部および第2突出部と前記ゲート電極の重複面積は、前記ドレーン電極と前記ゲート電極の重複面積と同一である薄膜トランジスタ基板。

20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、薄膜トランジスタ基板とその製造方法に関し、特に薄膜トランジスタ基板製造用のマスクに関する。

#### 【背景技術】

#### 【0002】

薄膜トランジスタ基板は、液晶表示装置（LCD）等の薄型表示装置で表示パネルとして利用される。薄膜トランジスタ基板では、一般にマトリックス状に配列された画素のそれぞれに一つずつ薄膜トランジスタ（TFT）が形成され、そのスイッチングにより各画素の含む素子の電極に対して個別に信号が印加される。例えば液晶表示装置では通常、薄膜トランジスタ基板に、画素電極、ストレージキャパシタ、及び薄膜トランジスタなどが画素ごとに形成されている。薄膜トランジスタ基板は更に、共通電極などが形成された共通電極基板に、両基板の間に封入された液晶層を隔てて対向している。画素電極と共通電極との間に電圧を印加し、両電極間に挟まれた液晶層の配向状態を変化させることで、各画素の光透過率を制御する。それにより、所望の画像を表示パネルに再現する。

30

#### 【0003】

薄膜トランジスタ基板では一般に、透明なガラス基板の上に、複数のゲートラインとソースラインとが形成されている。ゲートラインとソースラインとが交差する領域のそれぞれには薄膜トランジスタが設けられている。ゲートラインとソースラインとで区切られた領域、すなわち画素のそれぞれには画素電極が形成され、薄膜トランジスタのドレイン端子に接続されている。ゲートラインを介して薄膜トランジスタのゲート電極にゲート電圧が外部から印加されると、薄膜トランジスタがターンオンする。そのとき、薄膜トランジスタのソース電極に接続されたソースラインを通して外部から伝わるデータ信号が、薄膜トランジスタのドレイン電極に対して印加され、更に画素電極に伝わる。特に液晶表示装置では、このように画素電極に対して印加されたデータ信号により、画素電極と共通電極との間の電圧が変化する。

40

#### 【特許文献1】特開2005-303119号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

50

## 【0004】

薄膜トランジスタでは一般に、オフ時でもドレイン電極とソース電極との間に漏れ電流（オフ電流）が流れる。オフ電流は表示装置の省電力化を阻む。更に、過大なオフ電流は表示パネルに潜像を与え、その高画質化を阻む。従って、薄膜トランジスタ基板では薄膜トランジスタのオフ電流が極力抑えられねばならない。しかし、従来の薄膜トランジスタ基板では、各薄膜トランジスタのドレイン電極とソース電極との間のチャンネル領域より外に、ドレイン電極とソース電極との間に電子を移動させ得る領域（漏れ領域）が比較的広く生じている。画素電極とソース電極との間では一般に、漏れ領域を流れる電流の経路がチャンネル領域を流れる経路より短いので、オフ電流が漏れ領域を通ることで増大する。更に、漏れ領域に照射された光がキャリアを生成するので、漏れ領域は光に起因するオフ電流も増大させる。

10

## 【0005】

以上のことから、薄膜トランジスタ基板でのオフ電流の抑制には漏れ領域の縮小が有効である。しかし、従来の薄膜トランジスタ基板の製造方法では、漏れ領域を狭めることが困難であるので、漏れ領域を流れるオフ電流の増大を抑えることが困難である。

本発明は、ソース電極とドレイン電極との間の漏れ領域を縮小することにより、オフ電流の経路長を増大させ、且つ、薄膜トランジスタに照射された光によるキャリアの生成を抑え、その結果、オフ電流の更なる低減を実現できる薄膜トランジスタ基板とその製造方法、の提供を目的とする。

## 【課題を解決するための手段】

20

## 【0006】

本発明による薄膜トランジスタ基板は、複数のゲートラインとそれに交差する複数のソースライン、ゲートラインとソースラインとにより区切られた複数の画素領域のそれぞれに設けられた画素電極、及び、画素領域のそれぞれに設けられた薄膜トランジスタを備えている。ここで、薄膜トランジスタは、ゲートラインに接続されたゲート電極、ソースラインに接続されたソース電極、及び画素電極に接続されたドレイン電極を有する。

## 【0007】

本発明の一つの観点による薄膜トランジスタ基板では特に、薄膜トランジスタのソース電極とドレイン電極との間に設けられたチャンネル領域に活性層が露出し、その活性層の露出部分がチャンネル領域から外に、ソースラインの幅に対して所定の割合（好ましくは30%）以下の幅まで突出している。

30

## 【0008】

本発明の別の観点による薄膜トランジスタ基板では特に、ソース電極が、ゲート電極の周縁部に沿って延びた、互いに長さの異なる第1の突出部と第2の突出部、及び、第1の突出部と第2の突出部との間を接続する接続部、を備えている。その場合、好ましくは、ドレイン電極の一部が第1の突出部と第2の突出部との間の領域に延び、チャンネル領域が、そのドレイン電極の一部とソース電極との間に設けられ、チャンネル領域内に活性層が露出している。更に好ましくは、第1の突出部の一部がゲート電極の周縁部に重なり、第1の突出部が第2の突出部よりも短い。

## 【0009】

40

本発明の他の観点による薄膜トランジスタ基板では特に、ゲート電極が、ドレイン電極に向かって突出した突起部を備え、その突起部の一部が、ドレイン電極の周縁部に重なっている。

本発明の更に他の観点による薄膜トランジスタ基板では特に、ドレイン電極が、画素電極に接続されたドレインコンタクトを備え、そのドレインコンタクトの下地に光遮断部が設けられている。

本発明の更に異なる観点による薄膜トランジスタ基板では特に、ソース電極が、ゲート電極に一部が重なっている第1の突出部と第2の突出部、及び、第1の突出部と第2の突出部との間を接続する接続部、を備え、ゲート電極とソース電極との間の重なり部分の面積が、ゲート電極とドレイン電極との間の重なり部分の面積に等しい。

50

## 【0010】

本発明の一つの観点による薄膜トランジスタ基板の製造方法は、

基板の上にゲート電極とそれに接続されたゲートラインとを形成するステップ、

基板の上に、ゲート絶縁膜、活性層、及び導電性膜を順番に積層するステップ、

導電性膜の上に感光膜を塗布してパターニングし、ソース電極形成領域、ソースライン

形成領域、ドレイン電極形成領域、及びチャンネル形成領域、を有する感光膜マスクパターンを形成するステップ、

感光膜マスクパターンをマスクとして用いてエッチングを行い、ソース電極形成領域、

ソースライン形成領域、ドレイン電極形成領域、及びチャンネル形成領域を除く領域から

導電性膜と活性層とを除去するステップ、

感光膜マスクパターンを薄くしてチャンネル形成領域を除去し、そのチャンネル形成領域

の下地にある導電性膜を露出させるステップ、並びに、

チャンネル形成領域が除去された感光膜マスクパターンをマスクとして用いてエッチング

を行い、導電性膜の露出部分を除去するステップ、を備えている。

## 【0011】

ここで、ソース電極形成領域は、第1の突出部、第2の突出部、及びそれらの間を接続

する接続部を有する。ソースライン形成領域はソース電極形成領域に接続されている。ド

レイン電極形成領域では、その一部がソース電極形成領域の第1の突出部と第2の突出部

との間の領域に延びている。チャンネル形成領域は、そのドレイン電極形成領域の一部と

ソース電極との間の領域に設けられ、ソース電極形成領域とドレイン電極形成領域とのい

ずれよりも薄い。

## 【0012】

導電性膜の露出部分を除去するステップでは、ソース電極形成領域の第1の突出部、第

2の突出部、及び接続部のそれぞれに下地にはソース電極が形成され、ソースライン形成

領域の下地には、ソース電極に接続されたソースラインが形成され、ドレイン電極形成領域

の下地にはドレイン電極が形成され、ソース電極とドレイン電極との間には、活性層が

露出したチャンネル領域が形成される。特に、活性層の露出部分がチャンネル領域から外

に、ソースライン形成領域の幅に対して所定の割合（好ましくは30%）以下の幅まで突出

している。

## 【0013】

本発明の別の観点による薄膜トランジスタ基板の製造方法は、

基板の上にゲート電極とゲートラインとを形成するステップ、

基板の上に、ゲート絶縁膜、活性層、及び導電性膜を形成するステップ、

導電性膜の上に感光膜を塗布してパターニングし、ソース電極形成領域、ソースライン

形成領域、ドレイン電極形成領域、及びチャンネル形成領域、を有する感光膜マスクパターンを形成するステップ、

感光膜マスクパターンをマスクとして用いてエッチングを行い、ソース電極形成領域、

ソースライン形成領域、ドレイン電極形成領域、及びチャンネル形成領域を除く領域から

導電性膜と活性層とを除去するステップ、

感光膜マスクパターンを薄くしてチャンネル形成領域を除去し、そのチャンネル形成領域

の下地にある導電性膜を露出させるステップ、並びに、

チャンネル形成領域が除去された感光膜マスクパターンをマスクとして用いてエッチング

を行い、導電性膜の露出部分を除去するステップ、を備えている。

## 【0014】

ここで、ソース電極形成領域は、第1の突出部、第2の突出部、及びそれらの間を接続

する接続部を有し、特に、それら二つの突出部の長さが異なる。ソースライン形成領域は

ソース電極形成領域に接続されている。ドレイン電極形成領域では、その一部がソース電

極形成領域の第1の突出部と第2の突出部との間の領域に延びている。チャンネル形成領域

はドレイン電極形成領域のその一部とソース電極形成領域との間に設けられ、ソース電

極形成領域とドレイン電極形成領域とのいずれよりも薄い。

10

20

30

40

50

## 【0015】

本発明の他の観点による薄膜トランジスタ基板の製造方法は、

基板の上に、突起部を含むゲート電極と、それに接続されたゲートラインとを形成する

ステップ、

基板の上に、ゲート絶縁膜、活性層、及び導電性膜を形成するステップ、並びに、

導電性膜と活性層とをパターニングすることにより、ソース電極、ソースライン、及び

、ゲート電極の突起部の一部に周縁部が重なっているドレイン電極、を形成するステップ

、を備えている。

## 【0016】

本発明の更に他の観点による薄膜トランジスタ基板の製造方法は、

基板の上に、ゲート電極、それに接続されたゲートライン、及び光遮断部を形成するス

テップ、

基板の上に、ゲート絶縁膜、活性層、及び導電性膜を形成するステップ、並びに、

導電性膜と活性層とをパターニングすることにより、光遮断部の上にドレインコンタクト

とそれに接続されたドレイン電極とを形成し、かつソース電極とソースラインとを形成

するステップ、を有する。

## 【0017】

本発明の更に異なる観点による薄膜トランジスタ基板の製造方法は、

基板の上にゲート電極とそれに接続されたゲートラインとを形成するステップ、

基板の上に、ゲート絶縁膜、活性層、及び導電性膜を形成するステップ、並びに、

導電性膜と活性層とをパターニングすることにより、ソース電極、それに接続されたソ

ースライン、及びドレイン電極を形成し、ゲート電極とソース電極との間の重なり部分の

面積を、ゲート電極とドレイン電極との間の重なり部分の面積に等しくするステップ、を

備えている。

## 【0018】

本発明の一つの観点による薄膜トランジスタ基板製造用のマスクは、

薄膜トランジスタのソース電極とソースラインとが形成されるべき基板の領域に対向す

るソース遮光部、

薄膜トランジスタのドレイン電極が形成されるべき基板の領域に対向するドレイン遮光

部、及び、

薄膜トランジスタのチャンネル領域が形成されるべき基板の領域に対向する半透過部、

を備えている。特に、そのマスクを基板に重ねたとき、半透過部が、チャンネル領域が形

成されるべき基板の領域の外に、ソースラインの幅に対して所定の割合（好ましくは30%

）以下の幅まで突出している。好ましくは、ソース遮光部が、第1の突出部、第2の突出

部、及びそれらの間を接続する接続部を備え、ドレイン遮光部の一部がソース遮光部の第

1の突出部と第2の突出部との間に延び、半透過部がそのドレイン遮光部の一部とソース

遮光部との間の領域に設けられている。

## 【0019】

本発明の別の観点による薄膜トランジスタ基板製造用のマスクは、

薄膜トランジスタのソース電極とソースラインとが形成されるべき基板の領域に対向す

るソース遮光部、

薄膜トランジスタのドレイン電極が形成されるべき基板の領域に対向するドレイン遮光

部、及び、

ソース遮光部とドレイン遮光部との間に挟まれた半透過部、を備えている。特に、ソ

ース遮光部が、長さの異なる第1の突出部と第2の突出部、及びそれらの間を接続する接

続部を備えている。好ましくは、第1の突出部の一部が、薄膜トランジスタのゲート電極が

形成されるべき基板の領域の周縁部に対向し、第1の突出部が第2の突出部よりも短い。

好ましくは、半透過部が第1の突出部と第2の突出部との各先端に向かって延び、第1の

突出部の先端は第2の突出部の先端より、半透過部からの距離が長い。その他に、第1の

突出部と第2の突出部との各先端が半透過部から同じ距離にあっても良い。

10

20

30

40

50

## 【0020】

本発明による他の観点による薄膜トランジスタ基板製造用のマスクは、

薄膜トランジスタのゲート電極とゲートラインとが形成されるべき基板の領域に対向する胴体、及び、その胴体から、薄膜トランジスタのドレイン電極が形成されるべき基板の領域に対向する領域に向かって突出した突起部、を含むゲート電極遮光部、を備えている。好ましくは、突起部が第1の突起と第2の突起とを備え、各突起の一部が、薄膜トランジスタのドレイン電極が形成されるべき基板の領域の周縁部に対向する。

本発明による更に他の観点による薄膜トランジスタ基板製造用のマスクは、

薄膜トランジスタのゲート電極とゲートラインとが形成されるべき基板の領域に対向するゲート遮光部、及び、

薄膜トランジスタのドレイン電極に接続されたドレインコンタクトが形成されるべき基板の領域に対向するドレインコンタクト遮光部、を備えている。

10

## 【0021】

本発明の更に異なる観点による薄膜トランジスタ基板製造用のマスクは、

ゲート電極とドレイン電極との他に、第1の突出部と第2の突出部、及びそれらの間を接続する接続部、を含むソース電極、を有する薄膜トランジスタ基板、の製造に用いられる。このマスクは特に、ゲート電極が形成されるべき基板の領域に対向するゲート電極遮光部、を備えている。好ましくは、そのマスクを基板に重ねたとき、ソース電極の第1の突出部、第2の突出部、及び接続部のそれぞれが形成されるべき基板の領域とゲート電極遮光部との間の重なり部分の面積の和が、薄膜トランジスタのドレイン電極が形成されるべき基板の領域とゲート電極遮光部との間の重なり部分の面積に等しい。

20

## 【0022】

本発明の上記とは異なる観点による薄膜トランジスタ基板製造用のマスクは、

薄膜トランジスタのソース電極とソースラインとが形成されるべき基板の領域に対向するソース遮光部、

薄膜トランジスタのドレイン電極が形成されるべき基板の領域に対向するドレイン遮光部、及び、

ソース遮光部とドレイン遮光部との間に挟まれた半透過部、を備えている。特に、ソース遮光部が、ドレイン遮光部より幅の狭い第1の突出部と第2の突出部、及びそれらの間を接続する接続部、を備えている。更に、そのマスクを基板に重ねたとき、ソース遮光部の第1の突出部、第2の突出部、及び接続部のそれと薄膜トランジスタのゲート電極との間の重なり部分の面積の和が、ゲート電極とドレイン遮光部との間の重なり部分の面積に等しい。

30

## 【発明の効果】

## 【0023】

本発明の一つの観点による薄膜トランジスタ基板では、薄膜トランジスタのチャンネル領域に露出した活性層が、チャンネル領域から外には、ソースラインの幅に対して所定の割合（好ましくは30%）以下の幅までしか突出していない。このような活性層の露出部分の制御は、薄膜トランジスタ基板の製造時に用いられるマスクのソース遮光部とドレイン遮光部との間に挟まれた半透過部を調節することで可能である。従って、ソース電極とドレイン電極との間では、活性層の上記の突出部分から成る、チャンネル領域以外のキャリアの移動可能領域（すなわち漏れ領域）が縮小する。その結果、薄膜トランジスタのオフ電流の経路長が増大し、照射される光をキャリアに変換する領域が縮小する。こうして、オフ電流が抑えられる。

40

## 【0024】

本発明の別の観点による薄膜トランジスタ基板では、ゲート電極の周縁部に部分的に重なっているソース電極の第1の突出部を第2の突出部より短くすることで、照射される光をキャリアに変換する領域を縮小している。その結果、オフ電流が抑えられる。

本発明の他の観点による薄膜トランジスタ基板では、ゲート電極の突出部がドレイン電極の周縁部の外側に照射される光を弱める。その結果、その光から変換されるキャリアの

50

量が低減するので、オフ電流が抑えられる。

本発明の更に他の観点による薄膜トランジスタ基板では、ドレインコンタクトの下地に光遮断部を設け、ドレインコンタクトに照射される光を弱めている。その結果、その光から変換されるキャリアの量が低減するので、オフ電流が抑えられる。

#### 【0025】

本発明の更に異なる観点による薄膜トランジスタ基板では、ゲート電極とソース電極との間の重なり部分の面積が、ドレイン電極とゲート電極との間の重なり部分の面積に等しいので、各重なり部分の寄生キャパシタンスに差が生じない。その結果、その差に起因する薄膜トランジスタのオフ時における漏れ電流、すなわちオフ電流が抑えられる。

#### 【発明を実施するための最良の形態】

10

#### 【0026】

以下、添付図面に基づき、本発明の好適な実施の形態について詳細に説明する。

#### <第1の実施形態>

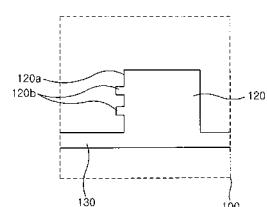

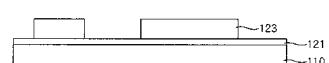

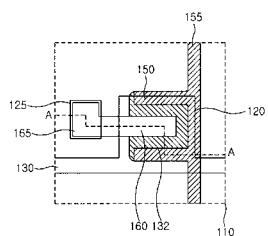

図1は、本発明の第1の実施形態によるゲート電極を形成するためのマスクの平面図であり、図2～図4は、本発明の第1の実施形態によるゲート電極の形成を説明するために、図1の折線A-Aに沿って切り取った断面図であり、図5は、本発明の第1の実施形態によるゲート電極が形成された基板の平面図である。以下、図1～図5に基づき、本発明の第1の実施形態を説明する。

#### 【0027】

先ず、図2に示すように、透光性の絶縁基板110の上に第1の導電性膜121を形成し、その上部に第1の感光膜122を塗布する。このとき、CVD法、PVD法及びスピッタリング法などを用いた蒸着方法により、第1の導電性膜121を形成する。第1の導電性膜121は、Cr、MoW、Cr/AI、Cu、AI(Nd)、Mo/AI、Mo/AI(Nd)及びCr/AI(Nd)のうちいずれか一つを用いて形成することが好ましい。

20

#### 【0028】

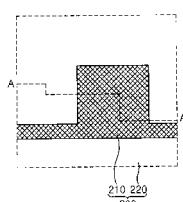

次に、図2に示すように、第1の導電性膜121と第1の感光膜122が塗布された基板の上に第1のマスク200を整列させ、その後、第1のマスク200を通して露光を行い、図3に示すように、ゲート電極領域以外の領域が開放された第1の感光膜マスクパターン123を形成することが好ましい。図1に示すように、第1のマスク200は、ゲートライン領域及びゲート電極領域の光を遮蔽する遮光部210と、それ以外の領域の光を透過させる透光部220と、を備える。尚、遮光部210と透光部220は、透光性の絶縁基板110の上に形成された第1の感光膜122の特性に応じ、各領域が変更されても良い。図1においては、ゲートラインの一辺から突き出た矩形部分にゲート電極領域が設けられることが好適である。このような構造の第1のマスク200を基板110の上に整列させて露光と現像を行い、第1の導電性膜121の上に第1の感光膜マスクパターン123を形成する。第1の感光膜マスクパターン123は、図1に示す遮光部210と同じパターンに設けられることが好ましい。

30

#### 【0029】

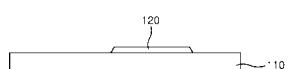

第1の感光膜マスクパターン123を所定のベーク工程により硬化させた後、これをエッチングマスクとしてエッチング工程を行うことで第1の導電性膜121を除去し、図4及び図5に示すように、ゲート電極120とゲートライン130を形成することが好ましい。ゲート電極120の形成後、所定のストリップ工程により第1の感光膜マスクパターン123を除去することが好ましい。

40

#### 【0030】

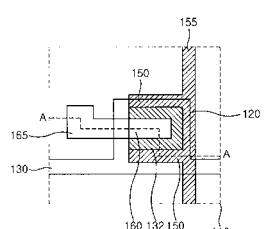

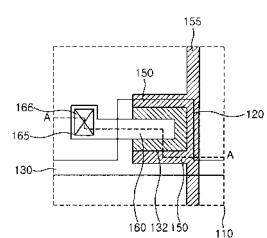

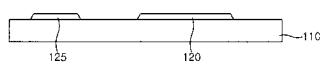

図6は、本発明の第1の実施の形態によるソース及びドレイン電極を形成するためのマスクの平面図であり、図7～図10は、第1の実施形態によるソース及びドレイン電極形成を説明するために、図6の折線A-Aに沿って切り取った断面図であり、図11は、本発明の第1の実施形態によるソース及びドレイン電極が形成された基板の平面図である。以下、図6～図11に基づき、本発明の第1の実施形態を説明する。

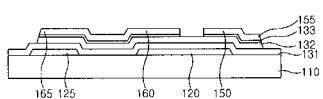

#### 【0031】

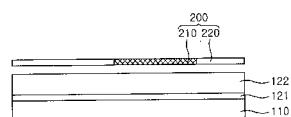

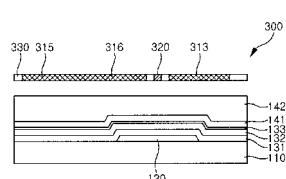

先ず、図7では、図5に示した、ゲート電極120及びゲートライン130が形成された基板11

50

0の上に、PECVD法、スパッタリング法などを用いた蒸着方法によりゲート絶縁膜131を形成する。このとき、ゲート絶縁膜131は、酸化シリコンまたは窒化シリコンを含む無機絶縁物質を用いて形成することが好ましい。ゲート絶縁膜131の上には、上記の蒸着方法により、活性層132、オーミック接触層133、及び第2の導電性膜141を順番に積層する。活性層132は、非晶質シリコン層を用いて形成し、オーミック接触層133は、シリサイド、若しくは、N型不純物が高濃度でドープされた非晶質シリコン層を用いて形成し、第2の導電性膜141は、Mo、Al、Cr、Tiのうち少なくとも一つの金属単一層または多重層を用いて形成することが好ましい。第1の実施形態においては、第2の導電性膜141としてMo/Al/Mo構造の薄膜を用いることが好適である。もちろん、第2の導電性膜141を第1の導電性膜121と同じ物質を用いて形成してもよい。

10

### 【0032】

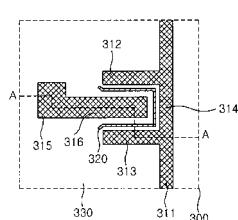

次に、第2の導電性膜141の上に第2の感光膜142を塗布する。その後、第2の感光膜142が塗布された基板110の上に第2のマスク300を整列させ、これを用いて露光を行い、図8に示すような第2の感光膜マスクパターン143を形成する。第2の感光膜マスクパターン143では好ましくは、ソース/ドレイン電極領域、ソースライン領域、及びチャンネル領域以外の領域が開放され、チャンネル領域に所定の段差が形成されている。第2のマスク300は、図6に示すように、ソース電極領域とドレイン電極領域とを遮蔽する遮光部311、312、313、314、315、316、ソース電極とドレイン電極との間のチャンネル領域に設けられた半透過部320、並びに、ソース電極領域、ドレイン電極領域、及びチャンネル領域以外の領域に設けられた透光部330、を備える。

20

### 【0033】

遮光部はソース遮光部311、312、313、314とドレイン遮光部315、316とを備えることが好ましい。遮光部は、クロムなどの光の透過を防ぐ物質から製作することが好ましい。ソース遮光部は、ソースライン遮光部311とソース電極遮光部312、313、314とを備える。ソースライン遮光部311は、ゲートライン130と直交するソースライン領域を遮蔽する。ソース電極遮光部312、313、314は、ソースラインからゲート電極130の上部に向けて延び、凹部形状のソース電極領域を遮蔽する。ソース電極遮光部312、313、314は、ソースライン遮光部311から突出した第1突出部312と第2の突出部313、及び二つの突出部312、313の間を接続する接続部314を備える。このとき、接続部314は、ソースライン遮光部311を介し、隣のソース電極遮光部312、313、314の間を接続する接続部314に接続されることが好ましい。ドレイン遮光部はドレインコンタクト遮光部315とドレイン電極遮光部316とを備える。ドレインコンタクト遮光部315は、画素領域に設けられ、かつ画素電極に接続されるドレインコンタクト領域を遮蔽する。ドレイン電極遮光部316は、ドレインコンタクトからソース電極の凹部の内側に延びたドレイン電極領域の一部を遮蔽する。このとき、ドレイン電極遮光部316は、第1の突出部312及び第2の突出部313と平行に延び、接続部314とは垂直に延びている。

30

### 【0034】

半透過部320は、ソース電極遮光部312、313、314とドレイン電極遮光部316とが隣り合う領域の間に設けられることが好ましい。半透過部320は、スリット、若しくはハーフトーン処理により形成されることが好ましい。第1の実施形態においては、ソース電極遮光部312、313、314の第1の突出部312、第2の突出部313、及び接続部314により設けられた凹部の内側に、ドレイン電極遮光部316の一部が延びている。半透過部320は、第1の突出部312、又は第2の突出部313とドレイン電極遮光部316との間、及び接続部314とドレイン電極遮光部316との間に形成されることが好ましい。半透過部320は、上記の凹部の内側に沿って折り曲げられた線状に製作されることが好ましい。そして、図示のごとく、線状の半透過部320の両先端はそれぞれ、第1の突出部312、及び第2の突出部313に向けて折り曲げられている。それにより、露光時に光が凹部の内側に入ることを防ぐ。半透過部320の先端にある折り曲げられた部分は凹部の幅方向の範囲を外れないことが好ましい。

40

### 【0035】

上述のように、第1の実施形態における第2のマスク300では、ドレイン電極遮光部316

50

の一部がソース電極遮光部312、313、314に囲まれて形成され、これらの間の領域に半透過部320が設けられている。半透過部320を介して基板110にチャンネル領域を形成することにより、十分な長さのチャンネル領域を確保することが可能になる。更に、ドレイン電極遮光部316とソース電極遮光部312、313、314とが対向する凹部領域の内側に半透過部320を設けることにより、ソース電極150とドレイン電極160とが対向する領域以外の領域にチャンネル領域が拡張される現象を防ぐことができる。これにより、キャリアが移動可能な領域の面積が狭められるので、オフ電流が低減する。その上、薄膜トランジスタに光が照射される場合、活性層の内側では、光子により生成された電子がトラップされ、薄膜トランジスタのオフ時にドレイン電極とソース電極との間の電圧差によりコンダクションバンドに注入される。第1の実施形態のようにチャンネル領域の拡張が防止されれば、ゲート電極の周縁領域、特にゲート電極とドレインコンタクトとの間の領域では、照射された光により誘導されるオフ電流が抑えられる。また、チャンネル領域の拡張を防いで、電子の平均自由行程を拡大させて、オフ電流を低減することができる。

【0036】

上記構造の第2のマスク300を、第2の導電性膜141の上に第2の感光膜142が塗布された基板110の上に整列させた後に露光を行うと、透光部330では光が透過してその下の第2の感光膜142が露光されてその化学的な特性が変わる。一方、遮光部311、312、313、314、315、316に対向する基板110の領域を覆う第2の感光膜142は露光されないので、その化学的な特性が変わらない。更に、半透過部320では光の一部のみが透過してその下の第2の感光膜142の一部のみが露光される。それにより、第2の感光膜142の上側領域の化学的な特性が変わる。露光後、第2のマスク300を基板110から除去して現像を行うと、図8に示すように、化学的な特性が変わった透光部330の下にあった感光膜は除去され、遮光部311、312、313、314、315、316の下にあった感光膜は除去されずに残り、半透過部320の下にあった感光膜は、遮光部311、312、313、314、315、316の下にあった感光膜よりも薄くなる。この後、ベーク工程を行い、パターニングされた第2の感光膜を硬化させ、段差を有する第2の感光膜マスクパターン143を形成する。このような段差を有する第2の感光膜マスクパターン143の形成では、上述の半透過部320を有する半透過マスクの他に、回折露光部を有する回折露光マスクが用いられても良い。

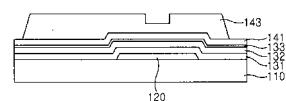

【0037】

第2の感光膜マスクパターン143をエッチングマスクとしてエッチング工程を行い、第2の導電性膜141、オーミック接触層133、及び活性層132の露出部分を順番に除去する。そのエッチング工程では、先ず、ウェットエッチングを行って第2の導電性膜141を除去し、その後、ドライエッチングを行ってオーミック接触層133及び活性層132を除去することが好ましい。

その後、第2の感光膜マスクパターン143を薄くし、図9に示すように、段差領域、すなわち、チャンネル領域が露出した第2の感光膜マスクパターン144を形成する。好ましくは、化学溶液を用いたウェットストリップ工程により第2の感光膜マスクパターン143を薄くする。その他に、O<sub>2</sub>プラズマを用いたアッシング工程により第2の感光膜マスクパターン143を全体的に薄くしても良い。

【0038】

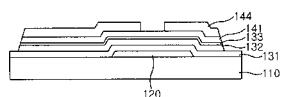

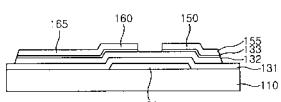

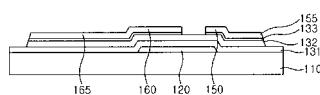

チャンネル領域が露出した第2の感光膜マスクパターン144をエッチングマスクとしてエッチング工程を行い、チャンネル領域の第2の導電性膜141及びオーミック接触層133を除去する。その後、ストリップ工程を行い、残留する第2の感光膜マスクパターンを除去する。それにより、図10に示すように、ソース電極150、ソースライン155、ドレイン電極160、及びドレインコンタクト165が形成され、ソース電極150とドレイン電極160との間には、活性層132の露出部分からチャンネル領域が形成される。こうして、ゲート電極120の上にソース電極150及びドレイン電極160が形成され、ソース電極とドレイン電極とが隣り合う領域の間に活性層が設けられた薄膜トランジスタが製作される。

【0039】

ソース電極150とドレイン電極160とは上述の第2のマスク300の遮光部311、312、313、

10

20

30

40

50

314、315、316と同じパターンに製作される。ソース電極150とドレイン電極160との間の領域には活性層132が露出している。特に、活性層132の露出部分から成るチャンネル領域はソース電極150とドレイン電極160との間の領域に設けられている。活性層の露出部分は更に、チャンネル領域から外に、ソースライン155の幅に対して30%以下の幅で突出していることが好ましい。もちろん、ソース電極150の先端から突出していないことが一層好ましい。この活性層132の突出範囲は、露光、現像、及びエッチング工程などの工程マージンはもとより、図6に示された第2のマスク300の半透過部320の先端の折り曲げ形状などの要因により変わりうる。好ましくは、その最大の突出幅がソースライン155の幅に対して30%以下である。第1の実施形態による薄膜トランジスタ基板の製作では更に、活性層132が（ソース電極及びソースライン用の）第2の導電性膜141と同時にパターニングされるので、ソースラインの側面に活性層の一部が露出する。そのとき、露出する活性層の幅は、ソースラインの幅の30%以内に調節され、工程マージンが確保されている。

#### 【0040】

オフ電流とは、薄膜トランジスタのオフ状態でドレインコンタクト領域の電子が活性層132を介してソース電極150に流れる現象を称する。もし活性層132がチャンネル領域から外にソースライン155の幅に対して30%以上突出していれば、この突出部により電子が移動し易くなるので、オフ電流が増大する。しかし、第1の実施形態では、活性層の突出部が最適化され、電子の移動可能な領域が狭められると共に、オフ電流の経路長が延ばされているので、オフ電流が抑制される。従って、本発明の第1の実施形態による薄膜トランジスタ基板は、表示装置での潜像現象の改善に有効である。

#### 【0041】

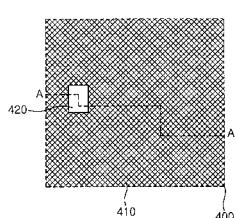

図12は、本発明の第1の実施形態によるドレインコンタクトを形成するためのマスクの平面図であり、図13～図15は、本発明の第1の実施形態によるドレインコンタクトの形成を説明するために、図12の折線A-Aに沿って切り取った断面図であり、図16は、本発明の第1の実施形態によるドレインコンタクトが形成された基板の平面図である。以下、図12～図16に基づき、本発明の第1の実施形態を説明する。

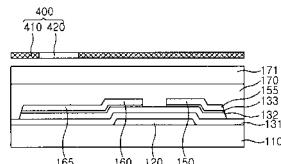

#### 【0042】

先ず、図11に示されている、薄膜トランジスタが設けられた透光性の絶縁基板110の上に、図13に示すように保護膜170を形成し、その上に第3の感光膜171を塗布する。保護膜170としては、有機絶縁膜及び無機絶縁膜を用いることができ、第1の実施形態においては、シリコン窒化膜またはシリコン酸化膜を用いることが好ましい。図13に示すように、第3の感光膜171が塗布された基板110の上に第3のマスク400を整列させて露光を行い、図14に示すように、ドレインコンタクト領域が開放された第3の感光膜マスクパターン172を形成することが好ましい。図12に示す第3のマスク400は、ドレインコンタクト領域に向けて光を透過させる透光部420と、それ以外の領域に向かう光を遮蔽する遮光部410と、を備える。このような構造の第3のマスク400を用いて露光を行うと、露光された領域では第3の感光膜171の化学的な性質が変わる。化学的な性質が変わった第3の感光膜171を現像により除去した後、残りの第3の感光膜171をベーク工程により硬化させ、図14に示すように、第3の感光膜マスクパターン172を形成することが好適である。その後、図15に示すように、第3の感光膜マスクパターン172をエッチングマスクとしてエッチング工程を行うことで保護膜170を除去し、下地のドレインコンタクト165を露出させるドレインコンタクトホール166を形成することが好ましい。次に、ストリップ工程により第3の感光膜マスクパターン172を除去することが好ましい。

#### 【0043】

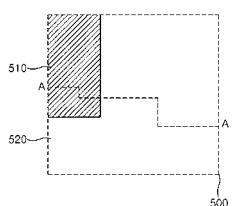

図17は、本発明の第1の実施形態による画素電極の形成のためのマスクの平面図であり、図18及び図19は、本発明の第1の実施形態による画素電極の形成を説明するために、図17の折線A-Aに沿って切り取った断面図である。図20は、本発明の第1の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図であり、図21は、図20の折線A-Aに沿って切り取った断面図である。以下、図17～図21に基づき、本発明の第1の実施形態を説明する。

10

20

30

40

50

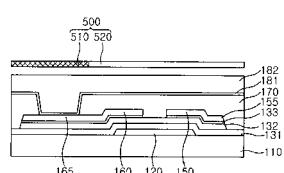

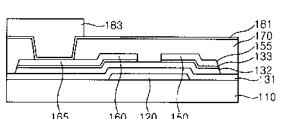

## 【0044】

先ず、図18を参照すると、図16に示したドレインコンタクトホール166が設けられた保護膜170の上に第3の導電性膜181を形成し、その上に第4の感光膜182を塗布する。第3の導電性膜181としては、透明な導電性材質であるITO(indium tin oxide)またはIZO(indium zinc oxide)を用いることが好ましい。その後、第4の感光膜182が塗布された基板110の上に第4のマスク500を整列させて露光を行い、図19に示すように、画素領域以外の領域が開放された第4の感光膜マスクパターン183を形成することが好ましい。図17に示す第4のマスク500は、画素電極領域に照射される光を遮蔽する遮光部510と、それ以外の領域に照射される光を透過させる透光部520と、を備える。上述の第4のマスク500を用いて露光を行うと、露光された領域では第4の感光膜182の化学的な性質が変わる。その後、現像工程を行うと、露光された領域の感光膜が除去される。ベーク工程を行うと、図19に示すように、第4の感光膜マスクパターン183が形成されることが好ましい。その後、第4の感光膜マスクパターン183をエッチングマスクとしてエッチング工程を行い、第4の導電性膜181を除去し、ストリップ工程により第4の感光膜マスクパターン183を除去する。それにより、図20及び図21に示すように、薄膜トランジスタのドレイン電極160に接続された画素電極180を有する(好ましくは液晶表示装置用の)薄膜トランジスタ基板が製作される。

## 【0045】

液晶表示装置の製造ではその後、カラーフィルタと共通電極とが設けられた共通電極基板を薄膜トランジスタ基板に封合し、それら二枚の基板の間に液晶層を注入して液晶表示パネルを製作する。

上記のように、第1の実施形態による薄膜トランジスタは、ソース電極とドレイン電極との間の領域に露出した活性層の範囲を最適化することにより、ソース電極とドレイン電極との間にキャリアが移動可能な領域の面積を低減させる。それにより、その領域に照射された光によるキャリアの生成を抑え、かつ漏れ電流の経路長を増大させることにより、オフ電流を低減できる。

## 【0046】

## &lt;第2の実施形態&gt;

本発明の実施形態は上述の第1の実施形態に限定されることはない。以下に述べる第2の実施形態のように、ソース電極の第1の突出部を第2の突出部よりも短くすることで、ゲート電極の周縁部での光によるキャリアの生成、及びそれにより誘導されるオフ電流を抑えることができる。以下、本発明の第2の実施形態による薄膜トランジスタ基板を含む液晶表示装置の製造方法を説明する。尚、後述の説明のうち、上述の説明と重複する部分については、上述の説明を援用する。

## 【0047】

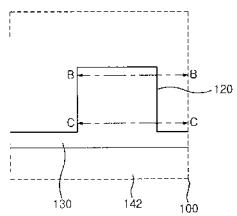

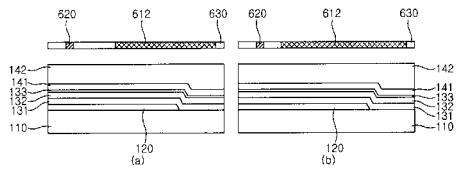

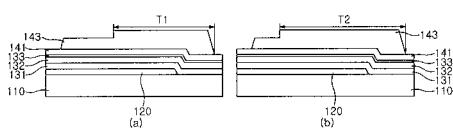

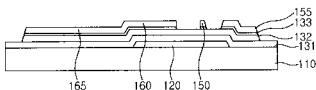

図22は、本発明の第2実施の形態によるソース及びドレイン電極を形成するためのマスクの平面図であり、図23は、本発明の第2実施の形態による活性層及びソースドレイン用の導電性膜が形成された基板の平面図であり、図24A～図26Aは、図22及び図23の直線B-Bに沿って切り取った断面図であり、図24B～図26Bは、図22及び図23の直線C-Cに沿って切り取った断面図である。図27は、本発明の第2の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図である。図28は、本発明の第2の実施形態の変形例によるソース及びドレイン電極を形成するためのマスクの平面図である。

## 【0048】

図22～図28を参照すると、第1の実施形態のように、基板110の上にゲート電極120及びゲートライン130を形成し、その上に、ゲート絶縁膜131、活性層132、オーミック接触層133、及び第2の導電性膜141を順番に積層する。第2の導電性膜141の上に第2の感光膜142を塗布した後、基板110の上に第2の実施形態によるマスク600を整列させ、露光及び現像を行うことで第2の感光膜マスクパターン143を形成する。第2の感光膜マスクパターン143では好ましくは、ソース/ドレイン電極領域及びチャンネル領域以外の領域が開放され、チャンネル領域に所定の段差が形成されている。

## 【0049】

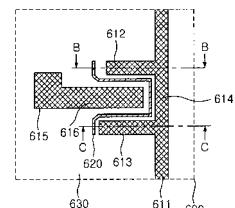

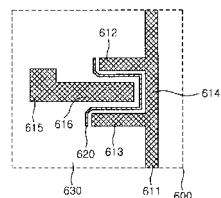

第2の実施形態による、ソース電極及びドレイン電極の形成のためのマスク600は、図2に示すように、遮光部611、612、613、614、615、616と、チャンネル領域に設けられた半透過部620と、ソース電極領域、ドレイン電極領域及びチャンネル領域以外の領域に設けられた透光部630と、を備える。遮光部はソース遮光部611、612、613、614とドレイン遮光部615、616とを含む。

## 【0050】

ソース遮光部は、ソースライン遮光部611、第1の突出部612、第2の突出部613、及び接続部614を含む。ソースライン遮光部611は、ゲートライン130と直交するソースライン領域を遮蔽する。第1の突出部612は、ソースライン遮光部611からゲート電極120の上側の周縁部の領域に延びている。第2の突出部613は、ソースライン遮光部611からゲート電極120の下側の内部に突出している。接続部614は、第1の突出部612と第2の突出部613との間を接続している。第2の実施形態においては特に、第1の突出部612が第2の突出部613よりも短く製作される。このように、ソース遮光部の第1の突出部612を第2の突出部より短くすれば、図27に示すように、ゲート電極120の上側の周縁部に重なるソース電極150の第1の突出部151を短く製作できる。それにより、ゲート電極120の上側の周縁部では、光によるキャリアの生成、及びそれにより誘導されるオフ電流の増大を防ぐことができる。好ましくは、ソース遮光部の第1の突出部612は第2の突出部613より0.1μm～3μmほど短く製作される。

## 【0051】

ドレイン遮光部は、ドレインコンタクト遮光部615とドレイン電極遮光部616とを備えている。ドレイン電極遮光部616の一部は、ドレインコンタクト遮光部615から、ソース電極遮光部の第1突出部612、第2の突出部613、及び接続部614により形成された凹形状の領域の内側に延びている。

## 【0052】

半透過部620は、ドレイン電極遮光部616とソース電極遮光部611、612、613、614とが対向する領域に、折り曲げられた線状に設けられている。好ましくは、半透過部620の両先端がそれぞれ、ソース電極遮光部の第1の突出部612と第2の突出部613とに向かって延びている。このように、半透過部620は、ドレイン電極遮光部616とソース電極遮光部611、612、613、614との間の領域に設けられ、それらの間にチャンネル領域を形成することができる。更に、半透過部620の先端が第1の突出部612と第2の突出部613とに向かって延びているので、パターン密度の低い画素領域に照射された光がチャンネル領域に入り込む現象を防ぐことができる。第2の実施形態においては、図22及び図24に示すように、半透過部620の一方の先端と第1の突出部612との間の距離が、他方の先端と第2の突出部613との間の距離とは異なるように製作されても良い。その他に、図28の変形例のように、それらの距離を等しくしても良い。そのように、第1の突出部612の長さのみを変化させ、又は半透過部620と第1の突出部612との両方の長さを変化させることにより、キャリアの移動可能な領域の面積と電流の経路長との両方を調節できる。

## 【0053】

上記のような構造のマスク600を、図24に示すように、基板110の上に整列させる。その後、露光を行い、マスク600を除去して現像を行う。それにより、図25に示すように、段差を有する感光膜マスクパターン143を形成する。そのとき、図示のごとく、第1の突出部612に対向する感光膜マスクパターン143の長さT1が第2の突出部613に対向する感光膜マスクパターン143の長さT2よりも短いことが分かる。

## 【0054】

図26に示すように、感光膜マスクパターン143をエッチングマスクとして用いてエッチングを行い、第2の導電性膜141、オーミック接触層133、及び活性層132の露出部分を順番に除去する。更に、感光膜マスクパターン143を薄くし、その後、それを用いたエッチングにより、第2の導電性膜141とオーミック接触層133とを除去し、図27に示すように、ソース電極150、ソースライン155、ドレインコンタクト165、及びドレイン電極160を形成

10

20

30

40

50

する。ソース電極150は、ゲート電極120の上層に向かって延び、かつ互いに離れている第1の突出部151と第2の突出部152、及びそれらの間を接続する接続部153、を有する。ソースライン155はソース電極150に接続されている。ドレインコンタクト165は画素領域に形成されている。ドレイン電極160は、ソース電極150の第1の突出部151と第2の突出部152との間の領域に延びている。ソース電極150とドレイン電極160との間の領域には活性層132の一部が露出し、薄膜トランジスタのチャンネル領域として働く。

#### 【0055】

このようにして製造された薄膜トランジスタは、略矩形にパターニングされたゲート電極120、ソース電極150（第1の突出部151、第2の突出部152、及び接続部153）、並びに、第1の突出部151と第2の突出部152との間の領域に延びているドレイン電極160、を備え、第1の突出部151が第2の突出部152よりも短い。更に、第1の突出部151の一部がゲート電極120の一辺に重なり、第2の突出部152はゲート電極120の上に設けられる。それにより、第2の突出部152の下地にある活性層132には光が当たらない。一方、ゲート電極120の境界領域に位置する第1の突出部151の下地にある活性層132では、光子の侵入により漏れ電流が生じる。更に、薄膜トランジスタがオン状態である間にドレイン電極160に蓄積された電子が、薄膜トランジスタのオフ時に、第1の突出部151の下地にある活性層132を介してソース電極150に移動し、オフ電流を発生させる。しかし、第2の実施形態においては、第1の突出部151が短いので、ドレイン電極160からソース電極150へ流れるオフ電流を低減させることができる。その上、ゲート電極120とドレインコンタクト165との間の領域では、光子によるキャリア生成に伴う漏れ電流の経路が長いので、光子により誘導されるオフ電流が抑えられる。

#### 【0056】

##### <第3の実施形態>

本発明の実施形態は上記のものには限定されない。以下に述べる第3の実施形態では、ドレイン電極に向かってゲート電極の一部を突出させることで、光により誘導されるオフ電流を抑えることができる。以下、本発明の第3の実施形態による薄膜トランジスタを含む液晶表示装置の製造方法を説明する。尚、後述の説明のうち、上述の説明と重複する部分については、上述の説明を援用する。

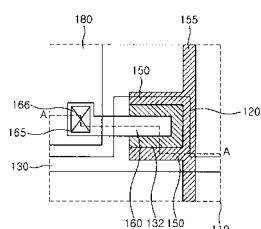

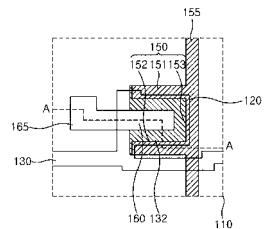

#### 【0057】

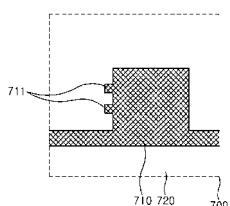

図29は、本発明の第3の実施形態によるゲート電極の形成のためのマスクの平面図であり、図30は、本発明の第3の実施形態によるゲート電極が形成された基板の平面図であり、図31は、本発明の第3の実施形態によるソース及びドレイン電極を形成するためのマスクの平面図であり、図32は、本発明の第3の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図であり、図33は、本発明の第3の実施形態の変形例によるゲート電極の形成のためのマスクの平面図である。

#### 【0058】

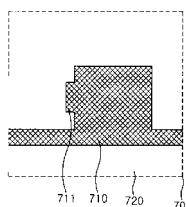

図29～図33を参照すると、第3の実施形態によるゲート電極用のマスク700を、ゲート電極用の導電性膜121及び第1の感光膜122が形成された基板110の上に整列させる。その後、露光及び現像を行い、感光膜マスクパターン（図示せず）を製作し、それを用いたエンジニアリング工程により、図30に示すように、ドレイン電極に向かって突出した突起部120bを有するゲート電極120と、それに接続されたゲートライン130とを形成することが好ましい。

#### 【0059】

ゲート電極用のマスク700は、図29に示すように、ゲートライン領域とゲート電極領域とを遮光する遮光部710、及びそれら以外の領域で開放された透光部720を備えている。遮光部710は、ドレイン電極に向かって突出した突起部711を備えている。突起部711は二つの領域に分けられ、後続の工程により製作されるドレイン電極160の各周縁部に重なるように製作されている。もちろん、本発明の実施形態はこれに限定されるものではなく、突起部が図33に示すように、单一の領域に製作されても良い。ここで、図32に示すように、ドレイン電極160の幅W1を1とした場合、二つの突起部711のそれぞれの幅は0.1～2である。

10

20

30

40

50

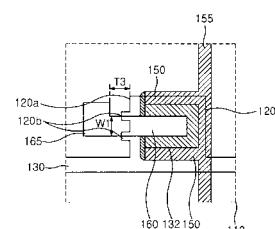

ことが好ましい。一方、ゲート電極120とドレインコンタクト165との間の距離T3を1とした場合、突起部711の長さは0.1~0.9であることが好ましい。このとき、ドレイン電極に重なっている突起部の部分の面積は、突起部全体の面積の10%~90%であることが好ましい。更に、第3の実施形態による突起部の長さと幅とはそれぞれ、0.1μm~3μmであることが好適である。このような構造のゲート電極用のマスク700を用いて製作されたゲート電極の形状は、図30に示すように、ゲートライン130に接続された矩形の胴体120aと、胴体120aからドレイン電極160に向かって突出した突起部120bとを有する。

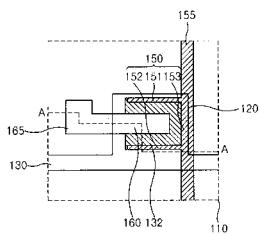

#### 【0060】

その後、上述のように、突起部120bを含むゲート電極120の上に、ゲート絶縁膜131、活性層132、オーミック接触層133、及び第2の導電性膜141を順番に積層する。第2の導電性膜141の上に第2の感光膜を塗布した後、図31に示すようなマスク800を用いて露光及び現像を行い、第2の感光膜マスクパターンを形成する。更に、第2の感光膜マスクパターンをエッティングマスクとして用いてエッティング工程を行った後、第2の感光膜マスクパターンを除去すると、図32に示すように、ドレイン電極160に向かって突出した突起部120bを有するゲート電極120、ゲート電極120の上に設けられたソース電極150、及び、突起部120bに一部が重なっているドレイン電極160、を含む薄膜トランジスタが製作される。薄膜トランジスタのゲート電極120はゲートライン130に接続され、ソース電極150はソースライン155に接続され、ドレイン電極160はドレインコンタクト165に接続されている。

#### 【0061】

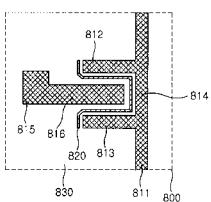

図31に示すように、第2のマスク800は、ソース電極領域とドレイン電極領域とを遮光する遮光部811、812、813、814、815、817、ソース電極とドレイン電極との間のチャンネル領域に設けられた半透過部820、並びに、ソース電極領域、ソースライン領域、ドレイン電極領域、及びチャンネル領域以外の領域に設けられた透光部830を備える。透光部830は、Crなどの光を遮断する物質を用いて製作されることが好ましい。尚、図31に示すように、第3の実施形態による遮光部811、812、813、814、815、817の構造と役割とは、図6に示されたものと同様であるので、それらの説明については図6に示されたものの説明を援用する。

#### 【0062】

ソース電極遮光部は、第1の突出部812と第2の突出部813、及びそれらの間を接続する接続部814を備え、ドレイン電極遮光部816は、ソース電極遮光部の第1の突出部812、第2の突出部813、及び接続部814によって形成された凹形領域の内側に延びている。半透過部820は、その凹形領域の内側に、折り曲げられた線状で形成されている。好ましくは、図31に示すように、折り曲げられた線状の半透過部820の各先端は、第1突出部812と第2の突出部813とのそれぞれに向かって折り曲げられている。それにより、凹形領域の内側に照射された光が漏れ電流を誘導する現象を防ぐことができる。好ましくは、半透過部820の先端が第1の突出部812と第2の突出部813との各幅だけ延びている。

#### 【0063】

第3の実施形態による薄膜トランジスタは、ドレインコンタクト165に向かって突出した突起部120bをゲート電極120に設けることで、ゲート電極120とドレインコンタクト165との間の領域に照射された光によるキャリアの生成、及びそれにより誘導されるオフ電流を低減させることができる。これは、突起部が光の透過可能な領域の面積を狭める結果、活性層に侵入する光の量を低減させることができるためである。

#### 【0064】

##### <第4の実施形態>

本発明の実施形態は上述のものには限定されない。以下に述べる第4の実施形態では、ドレインコンタクトの下地にある活性層に照射される光を遮蔽する光遮断部が設けられ、その光によるキャリアの生成、及びそれにより誘導されるオフ電流を低減させることができる。以下、本発明の第4の実施形態による薄膜トランジスタを含む液晶表示装置の製造方法を説明する。尚、後述の説明のうち、上述の説明と重複する部分については、上述の説明を援用する。

10

20

30

40

50

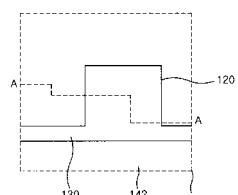

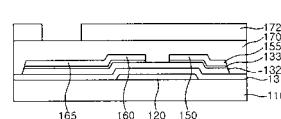

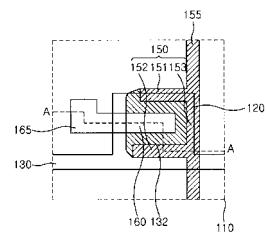

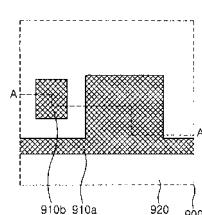

## 【0065】

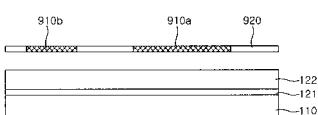

図34は、本発明の第4の実施形態によるゲート電極及び光遮断部を形成するためのマスクの平面図であり、図35～図37は、本発明の第4の実施形態によるゲート電極及び光遮断部の形成を説明するために、図34の折線A-Aに沿って切り取った断面図であり、図38は、本発明の第4の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図であり、図39は、図38の折線A-Aに沿って切り取った断面図である。

## 【0066】

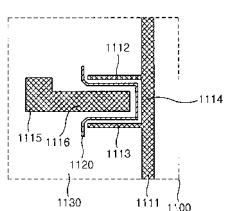

図34～図39を参照すると、第4の実施形態によるゲート電極及び光遮断部を形成するために、マスク900と基板110とを設ける。その基板110の上には、ゲート電極用の第1の導電性膜121が形成され、その上に感光膜122が塗布されている。

10

マスク900は、図34に示すように、ゲート電極とゲートライン領域とを遮光するゲート遮光部910a、ドレインコンタクト領域を遮光するドレインコンタクト遮光部910b、及び、遮光部910a、910bの領域を除く領域で開放された透光部920、を備えている。ドレインコンタクト遮光部910bは好ましくは、ドレインコンタクト領域と同じ形状に製作され、更に、ドレインコンタクト領域に光が照射されないように、ドレインコンタクト領域よりも広い面積で製作される。ドレインコンタクト領域のサイズを1とした場合、ドレインコンタクト遮光部910bのサイズは1～1.5とすることが好適である。

## 【0067】

上述のマスク900を、感光膜122が塗布された基板110の上に整列させた後、露光と現像とを行い、図36に示すように、遮光部910a、910bに対応するパターン形状を有する第1の感光膜マスクパターン123を製作する。その後、第1の感光膜マスクパターン123をエッチングマスクとして利用してエッチング工程を行い、第1の導電性膜121を除去し、感光膜マスクパターン123を除去する。こうして、ゲート電極120とゲートライン130とに加え、ドレインコンタクト165の下地に光遮断部125を形成する。

20

## 【0068】

ゲート電極120及び光遮断部125が設けられた基板110の上に、ゲート絶縁膜131、活性層132、オーミック接触層133、及び第2の導電性膜141を順番に積層する。第2の導電性膜141の上に第2の感光膜を塗布した後、図31に示す第3の実施形態による、ソース電極及びドレイン電極用のマスクを用いた露光及び現像を行い、第2の感光膜マスクパターンを形成する。その後、第2の感光膜マスクパターンを用いたエッチング工程を行い、図38及び図39に示すように、ゲート電極120の上にソース電極150を形成し、それに接続されたソースライン155を形成し、光遮断部125の上にドレインコンタクト165を形成し、ドレインコンタクト165からゲート電極120の上に延びているドレイン電極160を形成する。

30

## 【0069】

このように、第4の実施形態においては、ドレインコンタクト165の下地に光遮断部125を設けることで、ドレインコンタクトの下地に設けられた活性層132へ照射される光を遮断することができ、その光によるキャリアの生成、及びそれにより誘導されるオフ電流を抑えることができる。すなわち、光に曝される活性層132の面積を最小化することで、その光により誘導されるオフ電流を抑えることができる。

## 【0070】

40

## &lt;第5の実施形態&gt;

本発明の実施形態は上記のものには限定されない。以下に述べる第5の実施形態では、ゲート電極に重なっているソース電極とドレイン電極との各部分の面積を等しくすることで薄膜トランジスタのオフ電流を抑えることができる。以下、本発明の第5の実施形態による薄膜トランジスタを含む液晶表示装置の製造方法を説明する。尚、後述の説明のうち、上述の説明と重複する部分については、上述の説明を援用する。

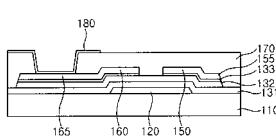

## 【0071】

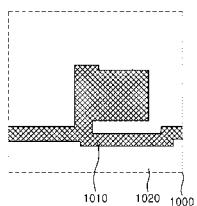

図40は、本発明の第5の実施形態によるゲート電極を形成するためのマスクの平面図であり、図41は、本発明の第5の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図であり、図42は、図41の折線A-Aに沿って切り取った断面図である。

50

図40～図42を参照すると、第5の実施形態では、ドレイン電極とソース電極とのそれぞれに重なる部分の面積が同じであるゲート電極の形成のために、図40に示すマスク1000を基板110の上に整列させる。ここで、基板110の上には、ゲート電極用の第1の導電性膜121が形成され、その上に、第1の感光膜122が塗布されている。その後、マスク1000を用いて露光と現像とを行い、第1の感光膜マスクパターンを形成する。更に、第1の感光膜マスクパターンをエッチングマスクとして用いてエッチング工程を行い、ゲート電極120を形成する。ゲート電極120が形成された基板110の上に、ゲート絶縁膜131、活性層132、オーム接觸層133、及び第2の導電性膜141を順番に積層する。第2の導電性膜141の上に第2の感光膜を塗布した後、図31に示す第3の実施形態によるソース電極及びドレイン電極用のマスクを用いた露光及び現像を行い、第2の感光膜マスクパターンを形成する。

10

#### 【0072】

第2の感光膜マスクパターンを用いたエッチング工程を行い、図41及び図42に示すように、ゲート電極120、ソース電極150、及びドレイン電極160を含む薄膜トランジスタを製作する。そのとき、ソース電極150は、第1の突出部151と第2の突出部152、及びそれらの突出部151、152の間を接続する接続部153を備えている。更に、第1の突出部151、第2の突出部152、及び接続部153の各内側の一部がゲート電極120に重なっている。ドレイン電極160は、ソース電極150の第1の突出部151と第2の突出部152との間の領域に延びている。第5の実施形態においては、ソース電極150の第1の突出部151、第2の突出部152、及び接続部153のそれぞれがゲート電極120に重なっている部分の面積の和が、ドレイン電極160とゲート電極120との間の重なり部分の面積に等しい。そのためには、図40に示すように、ゲート電極の形成のためのマスク1000では、ソース電極150に重なる遮光部1010の領域を狭くすることが好適である。ドレイン電極160とゲート電極120との間の重なり部分の面積を1とした場合、第1の突出部151と第2の突出部152とのそれぞれがゲート電極120と重なっている領域の面積は0.1～0.8であり、接続部153とゲート電極120との間の重なり部分の面積は0.1～0.8であるように、ゲート電極120をパターニングすることが好ましい。

20

#### 【0073】

ソース電極は、第1の突出部、第2の突出部、及び接続部のそれぞれでゲート電極に重なっているので、単一の接続部のみでゲート電極に重なっているドレイン電極より、重なり部分の面積が大きい。それにより、ソース電極とゲート電極との間に寄生するキャパシタの容量が、ドレイン電極とゲート電極との間に寄生するキャパシタの容量よりも大きい。一般には、それらの寄生キャパシタ間の容量差によりオフ電流が生じる。しかし、第5の実施形態においては、ソース電極とドレイン電極とのそれぞれがゲート電極に同じ面積だけ重なっているので、上記のような寄生キャパシタの容量差がなく、従って、オフ電流を防ぐことが可能である。また、順方向と逆方向との間でのバイアス電流差を防ぐことができる。

30

#### 【0074】

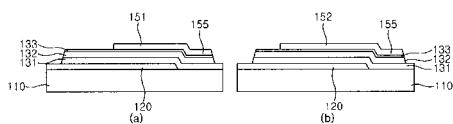

第5の実施形態においては、上記のものに限定されることなく、以下に述べるように、ソース電極の突出部の幅を狭くすることで、ソース電極及びドレイン電極のそれぞれがゲート電極と同じ面積だけ重なるようにもできる。図43は、本発明の第5の実施形態の変形例によるソース及びドレイン電極の形成のためのマスクの平面図であり、図44は、本発明の第5の実施形態の変形例による液晶表示装置の薄膜トランジスタ領域の平面図であり、図45は、図44の折線A-Aに沿って切り取った断面図である。

40

#### 【0075】

図43～図45に示すように、ソース電極150の第1の突出部151と第2の突出部152との各幅を狭く製作し、ソース電極150とゲート電極120との間の重なり部分の面積を、ドレイン電極160とゲート電極120との間の重なり部分の面積に等しくすることが好ましい。そのため、図43に示すように、ソース及びドレイン電極の形成のためのマスク1100では、ソース電極遮光部の第1の突出部1112と第2の突出部1113との各幅がドレイン電極遮光部1116の幅よりも狭く製作されている。そのようなマスク1100を基板110の上に整列させる。こ

50

ここで、基板110の上には、ゲート電極120がパターニングされ、その上に、ゲート絶縁膜131、活性層132、オーミック接触層133、及び第2の導電性膜134が順番に積層され、更に第2の感光膜141が塗布されている。マスク1100を用いて露光と現像とを行い、第2の感光膜マスクパターンを形成し、これを用いてエッチング工程を行い、ソース電極150、ソースライン155、ドレイン電極160、及びドレインコンタクト165を形成して薄膜トランジスタを製作する。

#### 【0076】

ソース電極150は、第1の突出部151、第2の突出部152、及びそれらの間を接続する接続部153を有する。ソースライン155は接続部153に接続されている。ドレインコンタクト165はドレイン電極160に接続されている。更に、ドレイン電極160とゲート電極120との間の重なり部分の面積は、ソース電極150とゲート電極120との間の重なり部分の面積に等しい。好ましくは、ドレイン電極160とゲート電極120との間の重なり部分の面積を1とした場合、ソース電極150の第1の突出部151と第2の突出部152とのそれぞれとゲート電極120との間の重なり部分の面積は0.1～0.6であり、接続部153とゲート電極120との間の重なり部分の面積は0.1～0.8である。

#### 【0077】

このように、第5の実施形態においては、ソース電極の突出部の幅を狭く製作してソース電極とゲート電極との間の重なり部分の面積を、ドレイン電極とゲート電極との間の重なり部分の面積と等しくすることで、ソース電極とゲート電極との間の寄生キャパシタの容量を、ドレイン電極とゲート電極との間の寄生キャパシタの容量と等しくし、それらの容量差によるオフ電流を防ぐことができる。

#### 【0078】

上記の説明では、各実施形態を個別に説明したが、それぞれの実施形態は種々に組み合わせて実現可能である。

以上、本発明の実施形態を詳細に説明したが、当業者にとって、特許請求の範囲に記載された技術的な思想から逸脱することなく、本発明の実施形態を種々に変形し、かつ修正することは可能であろう。従って、それらの変形や修正も当然に、本発明の技術的範囲に属すると解されるべきである。

#### 【図面の簡単な説明】

#### 【0079】

【図1】本発明の第1の実施形態によるゲート電極を形成するためのマスクの平面図。

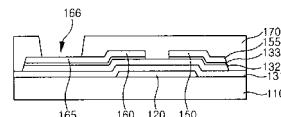

【図2】図1に示されているマスクを基板に重ねた状態を示す、図1の折線A-Aに沿って切り取った断面図。

【図3】図2に示されているように露光された基板の現像後の状態を示す、図1の折線A-Aに沿って切り取った断面図。

【図4】図3に示されている基板にエッチングを行った後の状態を示す、図1のA-A線に沿って切り取った断面図。

【図5】本発明の第1の実施形態によるゲート電極が形成された基板の平面図。

【図6】本発明の第1の実施形態によるソース及びドレイン電極を形成するためのマスクの平面図。

【図7】図6に示されているマスクを基板に重ねた状態を示す、図6の折線A-Aに沿って切り取った断面図。

【図8】図7に示されているように露光された基板の現像後の状態を示す、図6の折線A-Aに沿って切り取った断面図。

【図9】図8に示されている感光膜を薄くした後の状態を示す、図6の折線A-Aに沿って切り取った断面図。

【図10】図9に示されている基板にエッチングを行った後の状態を示す、図6の折線A-Aに沿って切り取った断面図。

【図11】本発明の第1の実施形態によるソース及びドレイン電極が形成された基板の平面図。

10

20

30

40

50

【図12】本発明の第1の実施形態によるドレインコンタクトを形成するためのマスクの平面図。

【図13】図12に示されているマスクを基板に重ねた状態を示す、図12の折線A-Aに沿って切り取った断面図。

【図14】図13に示されているように露光された基板の現像後の状態を示す、図12の折線A-Aに沿って切り取った断面図。

【図15】図14に示されている基板にエッチングを行った後の状態を示す、図12の折線A-Aに沿って切り取った断面図。

【図16】本発明の第1の実施形態によるドレインコンタクトが形成された基板の平面図。

10

【図17】本発明の第1の実施形態による画素電極の形成のためのマスクの平面図。

【図18】図17に示されているマスクを基板に重ねた状態を示す、図17の折線A-Aに沿って切り取った断面図。

【図19】図18に示されているように露光された基板の現像後の状態を示す、図17の折線A-Aに沿って切り取った断面図。

【図20】本発明の第1の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図。

【図21】図20の折線A-Aに沿って切り取った断面図。

【図22】本発明の第2の実施形態によるソース及びドレイン電極を形成するためのマスクの平面図。

20

【図23】本発明の第2の実施形態による活性層及びソースドレイン用の導電性膜が形成された基板の平面図。

【図24】図22に示されているマスクを基板に重ねた状態を示す、図22及び図23の直線B-Bに沿って切り取った断面図(a)と、図22及び図23の直線C-Cに沿って切り取った断面図(b)。

【図25】図24に示されているように露光された基板の現像後の状態を示す、図22及び図23の直線B-Bに沿って切り取った断面図(a)と、図22及び図23の直線C-Cに沿って切り取った断面図(b)。

【図26】図25に示されている基板にエッチングを行った後の状態を示す、図22及び図23の直線B-Bに沿って切り取った断面図(a)と、図22及び図23の直線C-Cに沿って切り取った断面図(b)。

30

【図27】本発明の第2の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図。

【図28】本発明の第2の実施形態の変形例によるソース及びドレイン電極を形成するためのマスクの平面図。

【図29】本発明の第3の実施形態によるゲート電極の形成のためのマスクの平面図。

【図30】本発明の第3の実施形態によるゲート電極が形成された基板の平面図。

【図31】本発明の第3の実施形態によるソース及びドレイン電極を形成するためのマスクの平面図。

【図32】本発明の第3の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図。

40

【図33】本発明の第3の実施形態の変形例によるゲート電極の形成のためのマスクの平面図。

【図34】本発明の第4の実施形態によるゲート電極及び光遮断部を形成するためのマスクの平面図。

【図35】図34に示されているマスクを基板に重ねた状態を示す、図34の折線A-Aに沿って切り取った断面図。

【図36】図35に示されているように露光された基板の現像後の状態を示す、図34の折線A-Aに沿って切り取った断面図。

【図37】図36に示されている基板にエッチングを行った後の状態を示す、図34の折線A

50

- Aに沿って切り取った断面図。

【図38】本発明の第4の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図。

【図39】図38の折線A-Aに沿って切り取った断面図。

【図40】本発明の第5の実施形態によるゲート電極を形成するためのマスクの平面図。

【図41】本発明の第5の実施形態による液晶表示装置の薄膜トランジスタ領域の平面図。

【図42】図41の折線A-Aに沿って切り取った断面図。

【図43】本発明の第5の実施形態の変形例によるソース及びドレイン電極の形成のためのマスクの平面図。

【図44】本発明の第5の実施形態の変形例による液晶表示装置の薄膜トランジスタ領域の平面図。

【図45】図44の折線A-Aに沿って切り取った断面図。

【符号の説明】

【0080】

110：基板

120：ゲート電極

132：活性層

150：ソース電極

160：ドレイン電極

200、300、400、500、600、700、800、900、1000、1100：マスク

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図17】

【図18】

【図19】

【図13】

【図14】

【図15】

【図16】

【図20】

【図21】

【図22】

【図23】

【図27】

【図24】

【図28】

【図25】

【図29】

【図26】

【図30】

【図31】

【図34】

【図32】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

---

フロントページの続き

(72)発明者 李 鍾 煥

大韓民国京畿道安山市東安区達安洞セッピヨルアパート602-1705

(72)発明者 李 洪 雨

大韓民国忠清南道天安市鳳鳴洞チョンソル3次アパート301-906

(72)発明者 金 容 照

大韓民国ソウル特別市西大門区弘恩洞現代アパート202-906

(72)発明者 李 庸 羽

大韓民国ソウル特別市龍山区厚岩洞143-36

審査官 鈴木 聰一郎

(56)参考文献 特開2000-164886(JP, A)

特開平09-152625(JP, A)

特開2003-140189(JP, A)

特開2005-173613(JP, A)

特開2003-066488(JP, A)

特開昭64-012577(JP, A)

特開平07-176754(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786