(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4931939号

(P4931939)

(45) 発行日 平成24年5月16日(2012.5.16)

(24) 登録日 平成24年2月24日(2012.2.24)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 21/316 | (2006.01) | HO1L 21/316 | M    |

| HO1L 29/78  | (2006.01) | HO1L 29/78  | 301G |

| HO1L 21/283 | (2006.01) | HO1L 21/283 | B    |

| HO1L 29/423 | (2006.01) | HO1L 29/58  | G    |

| HO1L 29/49  | (2006.01) | HO1L 21/316 | S    |

請求項の数 6 (全 34 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2008-558451 (P2008-558451)  |

| (86) (22) 出願日 | 平成19年2月27日 (2007.2.27)        |

| (65) 公表番号     | 特表2009-529789 (P2009-529789A) |

| (43) 公表日      | 平成21年8月20日 (2009.8.20)        |

| (86) 國際出願番号   | PCT/US2007/062841             |

| (87) 國際公開番号   | W02007/106660                 |

| (87) 國際公開日    | 平成19年9月20日 (2007.9.20)        |

| 審査請求日         | 平成22年2月17日 (2010.2.17)        |

| (31) 優先権主張番号  | 60/781,508                    |

| (32) 優先日      | 平成18年3月9日 (2006.3.9)          |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 11/614,019                    |

| (32) 優先日      | 平成18年12月20日 (2006.12.20)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                  |

|-----------|----------------------------------|

| (73) 特許権者 | 390040660                        |

|           | アプライド マテリアルズ インコーポレ              |

|           | イテッド                             |

|           | APPPLIED MATERIALS, INCORPORATED |

|           | アメリカ合衆国 カリフォルニア州 95              |

|           | 054 サンタクララ バウアーズ ア               |

|           | ペニー 3050                         |

| (74) 代理人  | 100109726                        |

|           | 弁理士 園田 吉隆                        |

| (74) 代理人  | 100101199                        |

|           | 弁理士 小林 義教                        |

| (74) 代理人  | 100107456                        |

|           | 弁理士 池田 成人                        |

最終頁に続く

(54) 【発明の名称】半導体デバイスを形成する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスを形成する方法であって、

基板の表面上に所望の厚さを持つ誘電体層を形成するステップと、

低エネルギー・パッタリングプロセスを用いて、該誘電体層の該厚さの少なくとも一部

内に第一物質の濃度勾配を形成するステップと、

を含み、該低エネルギー・パッタリングプロセスが、

R F ジェネレータを用いて R F エネルギーを低エネルギー・パッタリングチャンバの処理領域に第一 R F 周波数と第一 R F 電力でパルスするステップと、

該処理領域内に配置されたターゲットに D C ソースアセンブリから分配される D C 電圧 10

をパルスするステップと、

該ターゲットから除去された該第一物質の量が該誘電体層内に配置されうるように該パルスした R F エネルギーと該パルスした D C 電圧とを同期するステップと、

該誘電体層と該第一物質を、窒素を含む R F プラズマにさらすステップと、

該誘電体層の上に第二物質を堆積させるステップと、

を含む、方法。

## 【請求項 2】

該第一物質が、ジルコニウム、ハフニウム、ランタン、ストロンチウム、鉛、イットリウム、及びバリウムからなる群より選ばれる、請求項 1 に記載の方法。

## 【請求項 3】

該誘電体層が、二酸化シリコン、酸化ハフニウム、酸化ジルコニウム、ハフニウムシリケイトオキシド、酸化ランタン、及び酸化アルミニウムからなる群より選ばれる物質を含有する、請求項1に記載の方法。

**【請求項4】**

窒素を含むR F プラズマに該誘電体層をさらす前に該誘電体層内に第三物質の量を配置するステップであって、該第三物質が、ハフニウム、ランタン、アルミニウム、チタン、ジルコニウム、ストロンチウム、鉛、イットリウム、及びバリウムからなる群より選ばれる元素を含有する、ステップを更に含む、請求項1に記載の方法。

**【請求項5】**

該誘電体層と該第一物質と該第三物質を酸化環境にさらすステップであって、該酸化環境が熱酸化プロセス又はプラズマ酸化プロセスを用いる、ステップを更に含む、請求項4に記載の方法。 10

**【請求項6】**

該第二物質が、多結晶シリコン、タンタル、窒化タンタル、炭化タンタル、タングステン、窒化タングステン、窒化シリコンタンタル、ハフニウム、アルミニウム、ルテニウム、コバルト、チタン、ニッケル、及び窒化チタンからなる群より選ばれる物質を含有する、請求項1に記載の方法。

**【発明の詳細な説明】**

**【発明の背景】**

**【0001】**

**発明の分野**

[0001]本発明の実施形態は、一般的には、高k誘電体層を形成する方法及び装置に関する。より詳細には、本発明の実施形態は、ゲート誘電体層を形成する方法に関する。 20

**【0002】**

**関連技術の説明**

[0002]集積回路は、トランジスタ、キャパシタ、レジスタのような多くの、例えば、何百万というデバイスから構成されている。電界効果トランジスタのようなトランジスタは、典型的には、ソース、ドレイン、ゲートスタックを含んでいる。ゲートスタックは、典型的には、シリコン基板、ゲート誘電体のような基板と、ゲート誘電体上に、多結晶シリコンのようなゲート電極とを含む。ゲート誘電体層は、二酸化シリコン(SiO<sub>2</sub>)のような誘電物質、又はSiON、SiN、酸化ハフニウム(HfO<sub>2</sub>)、ケイ酸ハフニウム(HfSiO<sub>2</sub>)、酸窒化ハフニウムシリコン(HfSiON)、酸化ジルコニウム(ZrO<sub>2</sub>)、ケイ酸ジルコニウム(ZrSiO<sub>2</sub>)、チタン酸バリウムストロンチウム(BaSrTiO<sub>3</sub>又はBST)、チタン酸ジルコン酸鉛(Pb(ZrTi)O<sub>3</sub>又はPZT)等の誘電率が4.0を超える高k誘電物質から形成される。しかしながら、膜スタックは、他の物質から形成された層を含むことができることは留意すべきである。 30

**【0003】**

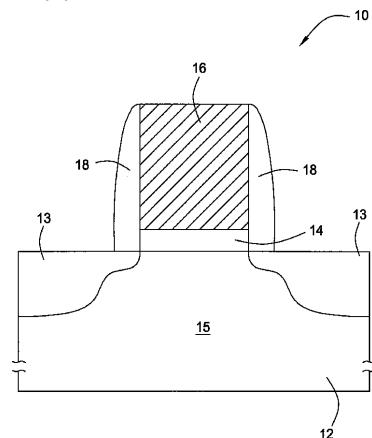

[0003]図1Aは、ゲート誘電体層14を組み込んでいるFET(電界効果トランジスタ)を示す断面図である。図面は、ゲート誘電体層14とゲート電極16が配置されている基板12を示している。側壁スペーサ18は、ゲート誘電体層14とゲート電極16の垂直側壁に隣接して示されている。ソース/ドレイン接合部13は、ゲート電極16の対向する垂直側壁にほぼ隣接して基板12内に形成されている。 40

**【0004】**

[0004]集積回路サイズとその上のトランジスタのサイズの縮小するにつれて、トランジスタの速度を上げるために必要とされるゲート駆動電流が増加してきた。駆動電流は、ゲート容量が増大するにつれて増加する。容量 = kA / d、ここで、kはゲートの誘電率であり、dは誘導体の厚さであり、Aはデバイスの面積である。ゲート容量と駆動電流を増加させる方法は、誘電体の厚さを減少させるとともにゲート誘電体の誘電率を上げることである。

**【0005】**

10

20

30

40

50

[0005] SiO<sub>2</sub>ゲート誘電体の厚さを20オングストローム未満に縮小することは試みられてきた。しかしながら、20オングストローム未満のSiO<sub>2</sub>ゲート誘電体の使用により、しばしばゲート性能と耐久性に対して望ましくない影響が生じることがわかった。例えば、ホウ素ドープされたゲート電極からのホウ素は、薄いSiO<sub>2</sub>ゲート誘電体を通って下に横たわるシリコン基板に浸透することができる。また、ゲートによって消費される電力量が増加する薄い誘電体において、典型的には、ゲート漏れ電流、即ち、トンネル電流が増加する。薄いSiO<sub>2</sub>ゲート誘電体は、NMOSホットキャリヤ劣化の影響を受けやすいものであり、誘電体全体に進む高エネルギーキャリヤがチャネルを損傷又は破壊することができる。薄いSiO<sub>2</sub>ゲート誘電体もまた、PMOS負バイアス温度不安定性(NBTI)の影響を受けやすいものであり、ここで、閾値電圧又は駆動電流は、ゲートの動作と共にドリフトする。

#### 【0006】

[0006] MOSFET(金属酸化物半導体電界効果トランジスタ)におけるゲート誘電体層として用いるのに適した誘電体層を形成する方法は、窒素含有プラズマの酸化シリコン薄膜を窒化することを含む。誘電率を上げるためにゲート酸化物の正味の窒素含量を増加させることは、いくつかの理由から望ましい。例えば、酸化物誘電体の大半は、プラズマ窒化物形成プロセスの間に窒素を容易に組み込むことができ、開始酸化物より酸化物換算膜厚(EOT)を減少させる。このことにより、窒化されていない酸化物誘電体と同一のEOTでFETの動作中のトンネリングのためにゲート漏れの減少をもたらすことができる。同時に、このような窒素含量の増加は、誘電体の厚さがF-Nトンネリング電流範囲にあるとすれば、続いての処理動作中にFowler-Nordheim(F-N)トンネリング電流によって誘導される損傷を減少させることができる。ゲート酸化物の正味の窒素含量を増加させる他の利点は、窒化ゲート誘電体がゲートエッチングアンダカットの問題により耐性があり、ゲートエッジの欠陥状態と漏れ電流を減少させることである。

#### 【0007】

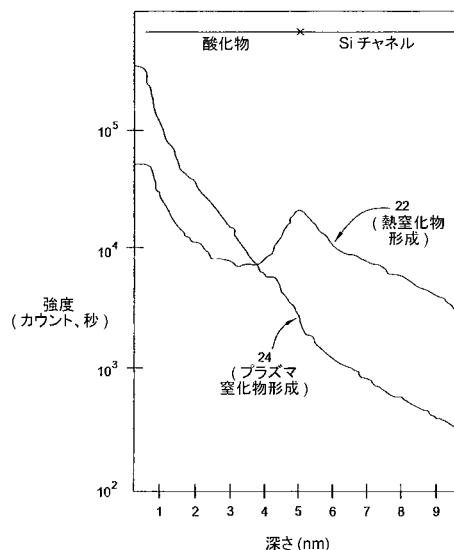

[0007] "Plasma Nitridation For Reduced Leakage Gate Dielectric Layers"と称する2003年8月26日発行の米国特許第6,610,615号において、McFaddenらは、熱とプラズマ双方の窒化プロセスに対する酸化シリコン膜の窒素プロファイルを比較している(図1Bを参照のこと)。窒化酸化物膜は、シリコン基板上に配置されている。図1Bは、更に、酸化物膜の下の結晶シリコンの窒素プロファイルを示している。熱的に窒化された酸化物の窒素プロファイルデータ22は、酸化物層の上面における第一窒素濃度、酸化物においてより深いほぼ低下している窒素濃度、酸化物-シリコン接合部における窒素の接合部蓄積、最後に基板への距離と共にほぼ低下している窒素濃度勾配を示している。対照的に、プラズマ窒化プロセスが、酸化物層の上面から酸化物-シリコン接合部を通って基板へ本質的に単調に低下している窒素プロファイル24を生じることを見ることができる。熱窒化プロセスにおいて見られる望ましくない窒素の接合部蓄積は、窒素プラズマのイオン衝撃で生じない。更に、基板の窒素濃度は、すべての深さで熱窒化プロセスで達成されるより低い。

#### 【0008】

[0008]前述のように、ゲート電極-ゲート酸化物接合部で増加している窒素濃度の利点は、多結晶シリコンゲート電極からゲート酸化物への又はゲート酸化物を通るホウ素のようなドーパントの外側への拡散が減少することである。このことにより、例えば、ホウ素ドープされた多結晶シリコンゲート電極から内側に拡散されたホウ素によって引き起こされるゲート酸化物の大半で欠陥を減少させることによってデバイスの信頼性が改善される。ゲート酸化物-シリコンチャネル接合部における窒素含量を減少させる他の利点は、固定電荷密度と接合部状態密度の低下である。これにより、チャネル移動度と相互コンダクタンスが改善される。それ故、プラズマ窒素プロセスは、熱窒化プロセスより有利である。

#### 【0009】

[0009]半導体デバイスが小さくなるにつれて、シリコン窒化ゲート酸化物層のサイズが

10

20

30

40

50

実用限界に達してきた。しかしながら、窒化された二酸化シリコンゲート誘電体のより小さな物理的厚さ（10オングストロームから）への縮小化とともに、更に、ゲート漏れが実用的デバイス用途の許容し得ないレベルまで増加した。デバイスサイズの減少の要求が依然としてあるので、新規なゲート誘電物質及び/又はプロセスが求められている。

#### 【0010】

[0010]二酸化シリコン（ $\text{SiO}_2$ ）の高k誘電型物質による置換には、課題がある。例えば、高k誘電物質は、典型的には、炭素含有前駆物質と他の汚染物質が堆積された膜内に組み込ませる傾向がある、化学気相堆積（CVD）又は原子層堆積（ALD）技術を用いて堆積される。炭素と他の汚染物質は、ゲート誘電体層の誘電特性に不利な影響する。また、化学気相堆積（CVD）又は原子層堆積（ALD）堆積高k膜とチャネル領域の間の接合部の品質は、二酸化シリコン層ほどロバストでない。10

#### 【0011】

[0011]それ故、当該技術において誘電特性の改善とより小さいEOTを有するゲート誘電体層を形成するための方法及び装置が求められている。

#### 【発明の概要】

#### 【0012】

[0012]本発明は、一般的には、半導体デバイスを形成する方法であって、基板の表面上に所望の厚さを持つ誘電体層を形成するステップと、誘電体層内に低エネルギー・パッタリングプロセスを用いて形成された誘電体層の厚さの少なくとも一部を通る濃度勾配を形成する量の第一物質を堆積するステップであって、低エネルギー・パッタリングプロセスが第一RF周波数と第一RF電力のRFエネルギーを低エネルギー・パッタリングチャンバの処理領域へ供給するので、ターゲットの第一物質が誘電体層内に配置され得る、前記ステップと、誘電体層の上に第二物質を堆積させるステップと、を含む、前記方法を提供する。20

#### 【0013】

[0013]本発明の実施形態は、更に、高k誘電体層を形成するための装置であって、搬送領域を形成する一つ以上の壁と搬送領域に位置決めされた搬送ロボットを持つ搬送チャンバと、搬送チャンバに結合され且つ窒化チャンバの第一処理領域において基板の表面上に窒化物を形成するように構成されたプラズマ窒化チャンバ（ここで、プラズマ窒化チャンバは、第一処理領域と電気的に連通しているRFソースと、第一処理領域と選択的に連通している窒素含有ガスソースとを備える）と、ロボットと搬送可能に連通している搬送チャンバに結合された第一低エネルギー・プラズマ処理チャンバ（ここで、第一低エネルギー・プラズマ処理チャンバは、第二処理領域を形成する一つ以上の壁を備える）と、第二処理領域にさらされた表面を持つターゲット（ここで、ターゲットは、第一物質を含む）と、第一RF周波数でエネルギーを供給するよう適合された第一RFジェネレータと、第二処理領域に位置決めされた基板支持体とを備える、前記装置を提供する。30

#### 【0014】

[0014]本発明の実施形態は、更に、高k誘電体層を形成するための装置であって、処理領域を形成する一つ以上の壁、処理領域にさらされる表面を持つターゲット、処理領域に面する少なくとも一つの基板を持つ基板支持体（ここで、基板支持体は、誘電体層が基板の表面上に形成された基板を支持するように適合されている）と、ターゲットと電気的に連通し、約1MHz～約200MHzの周波数で第一エネルギー量をターゲットに分配することによって処理領域における容量結合プラズマを維持するように構成されている第一ジェネレータ（ここで、第一ジェネレータは、物質がそこからスパッタされ得るようにターゲットの表面上にバイアスを生じるように構成されている）と、第一ジェネレータによつてターゲットに分配される周波数を制御するように構成されたコントローラとを備える、前記装置を提供する。40

#### 【0015】

[0015]本発明の実施形態は、更に、高k誘電体層を形成するための装置であって、処理領域を形成する一つ以上の壁と、処理領域にさらされた表面を持ち且つDC電源と連通し50

ているターゲットと、処理領域と第一ジェネレータと電気的に連通している第一コイル(ここで、第一コイルと第一ジェネレータは、ターゲットの表面に隣接した処理領域においてプラズマを生成するように構成されている)と、処理領域に位置決めされた基板支持体を備える、前記装置を提供する。

**【0016】**

[0016]本発明の実施形態は、更に、低エネルギー・パッタリングプロセスを用いて高k誘電体層を形成するための方法であって、低エネルギー・パッタリングプロセスが、プラズマ処理チャンバの処理領域において誘電体層がその上に形成された基板を位置決めするステップと、低エネルギー・パッタリングプロセスを用いて誘電体層内に第一物質を配置するステップであって、低エネルギー・パッタリングプロセスが、複数のRFエネルギー・パルスを第一RFジェネレータから第一物質を含むターゲットに分配する工程を含み、ここで、各パルスのRFエネルギーが第一RF周波数で分配される、前記ステップと、複数のDCパルスをDCソースアセンブリからのターゲットに分配するステップであって、複数のRFエネルギー・パルスと複数のDCパルスが同期化されている、前記ステップを含む、前記方法を提供する。

**【0017】**

[0017]本発明の実施形態は、更に、低エネルギー・パッタリングプロセスを用いて高k誘電体層を形成する方法であって、低エネルギー・パッタリングプロセスを用いて高k誘電体層を形成するステップであって、低エネルギー・パッタリングプロセスが、プラズマ処理チャンバの処理領域に誘電体層がその上に形成された基板を位置決めする工程を含む、前記ステップと、低エネルギー・パッタリングプロセスを用いて誘電体層内に第一物質を配置するステップであって、低エネルギー・パッタリングプロセスが、第一RFジェネレータから処理領域と電気的に連通しているコイルに複数のRFエネルギー・パルスを分配する工程を含み、ここで、RFエネルギーが第一RF周波数と第一電力で分配される、前記ステップと、複数のDCパルスをDCソースアセンブリからの第一物質を含むターゲットに分配するステップであって、複数のRFエネルギー・パルスと複数のDCパルスが同期化されている、前記ステップを含む、前記方法を提供する。

**【0018】**

[0018]本発明の実施形態は、更に、低エネルギー・パッタリングプロセスを用いて高k誘電体層を形成するステップであって、低エネルギー・パッタリングプロセスが、プラズマ処理チャンバの処理領域において誘電体層がその上に形成された基板の位置決めする工程を含む、前記ステップと、低エネルギー・パッタリングプロセスを用いて誘電体層内に第一物質を配置するステップであって、低エネルギー・パッタリングプロセスが、第一の複数のRFエネルギー・パルスを第一周波数での第一RFジェネレータから処理領域と電気的に連通しているコイルに分配する工程を含む、前記ステップと、第二の複数のRFエネルギー・パルスを第二周波数での第一RFジェネレータから処理領域と電気的に連通しているターゲットに分配するステップであって、複数のRFエネルギー・パルスと複数のDCパルスが同期化されている、前記ステップを含む、前記方法を提供する。

**【0019】**

[0019]本発明の上記特徴が詳細に理解され得るように、上で簡単にまとめた本発明のより具体的な説明は、実施形態によって参照することができ、それらの一部は添付の図面に示されている。しかしながら、添付の図面は、単に本発明の典型的な実施形態を示しているだけであるので、本発明の範囲を制限するものとみなされるべきでなく、本発明は他の等しく有効な実施形態を許容し得るものであることは留意すべきである。

**【詳細な説明】**

**【0020】**

[0043]本発明は、一般的には、基板上に高品質誘電体ゲート層を形成するように適合される方法及び装置を提供する。実施形態は、標準窒化プロセスの代わりに金属プラズマ処理プロセスを用いて基板上に高誘電率層を形成する方法を企図するものである。実施形態は、更に、二酸化シリコンのようなゲート誘電体層に対するイオン衝撃損傷を減少させる

10

20

30

40

50

とともに下に横たわるシリコンへの金属原子の混入を避けるために比較的低エネルギーの金属イオンを“注入する”ように適合された装置を企図するものである。本発明の実施形態は、ロジックデバイス又はメモリデバイスのような半導体デバイスの形成に有用なものである。

#### 【0021】

##### 高誘電率トランジスタゲートの製造方法

[0044] デバイス製造プロセスの現在の技術状況では、漏れ電流が少ない 5 - 10 オングストローム EOT を持つゲート誘電体層を製造することが困難である。65 nm ~ 90 nm のトランジスタノードの 10 - 16 オングストローム EOT のプロセスの現在の技術状況では、プラズマ窒化プロセスが用いられている。しかしながら、窒化された二酸化シリコンゲート誘電体層がより薄い物理的厚さ、例えば 10 オングストロームに縮小されるのにつれて、ゲート漏れは、実用的デバイス用途に許容し得ないレベルに増加することがある。ゲート漏れの問題をより小さい誘電体層の厚さで解決するために、プラズマ窒化プロセスを高 k 誘電体酸化物又はケイ酸塩を形成する堆積プロセスで置き換えるためにハフニウム (Hf)、ランタン (La)、アルミニウム (Al)、チタン (Ti)、ジルコニウム (Zr)、ストロンチウム (Sr)、鉛 (Pb)、イットリウム (Y)、又はバリウム (Ba) のような物質を含有する以下のプロセスを用いることができる。

10

#### 【0022】

[0045] 本発明は、薄いゲート誘電体厚さが約 5 ~ 10 オングストロームの（電気的）酸化物換算膜厚 (EOT) であるロジックタイプ用途の電界効果トランジスタにおけるゲート誘電体を製造するための方法を企図するものである。本発明は、また、ゲート誘電体層が約 10 オングストローム ~ 30 オングストロームの（電気的）酸化物換算膜厚 (EOT) であるメモリタイプ用途の電界効果トランジスタにおけるゲート誘電体層を製造するための方法を企図するものである。このプロセスは、統合した半導体デバイスや回路の製造に用いることができる。

20

#### 【0023】

##### ゲート酸化物層形成方法及び装置

[0046] 45 ナノメートル (nm) 以下の MOS タイプデバイスに見られる共通のゲート性能の問題を解決しようと努力して、フェルミ準位ピンニング又は閾値電圧ピンニングのような欠陥を減少及び/又は除去する新規なプロセスが生成された。一般に、プロセスは、高 k 誘導体を形成するステップと、その後堆積された高 k 物質の表面を終了させて、ゲート電極と高 k 誘電物質との間の良好な接合部を形成するステップとを含む。本発明の実施形態は、また、高 k 誘電物質を形成し、高 k 誘電物質の表面を終了させ、一つ以上の後処理ステップを行い、多結晶シリコン及び/又は金属ゲート層を形成するように適合されるクラスタツールを提供する。

30

#### 【0024】

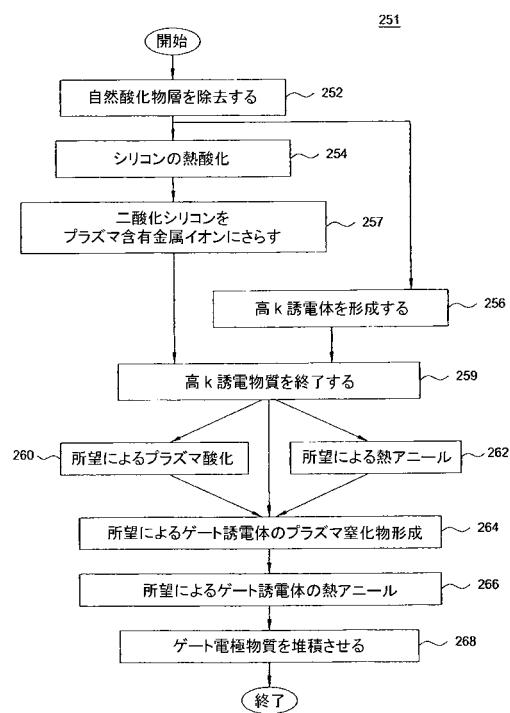

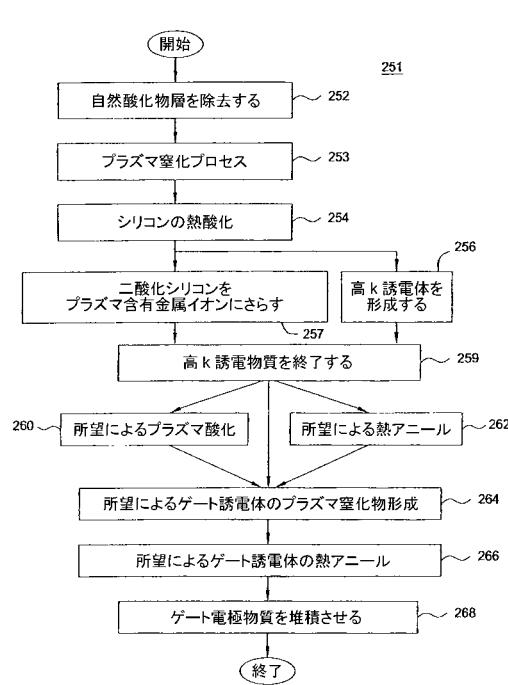

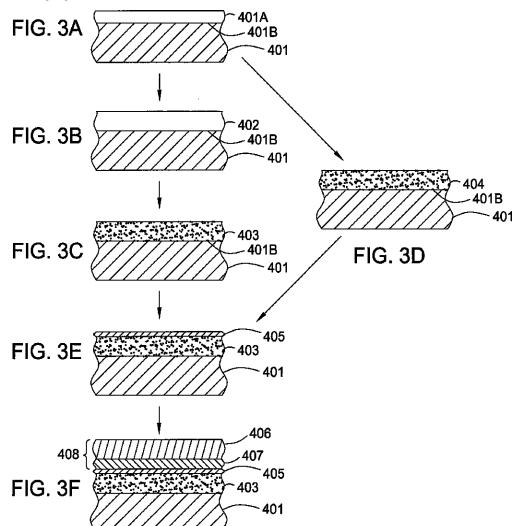

[0047] 図 2A は、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するために用いられる一連の方法ステップを含有するプロセス順序 251 を示す図である。プロセス順序 251 は、一般的には、例示的な MOS タイプデバイスのゲート構造を形成するために基板の上に行われる処理ステップを含む。図 3A - 図 3F は、ゲート酸化物層とゲートが図 2A に示したプロセス順序 251 におけるステップを用いて形成される基板 401 の領域を示す図である。図 3A - 図 3F の画像は、一定の比率で縮小して示されてなく、例示のために単純化されている。プロセス順序 251 の少なくとも一部は、図 7 に示したもののような統合した半導体基板処理システム（即ち、クラスタツール）における処理リアクタを用いて行うことができる。

40

#### 【0025】

[0048] プロセス順序 251 は、ステップ 252 から始まり、ステップ 268 に進む。ステップ 252 で、シリコン (Si) 基板 401（例えば 200 mm ウエハ、300 mm 半導体ウエハ）を準備し、基板の表面から（図 3A）から自然酸化物層 401A（例えば、二酸化シリコン (SiO<sub>2</sub>)）を除去するための洗浄液にさらす。一実施形態において、

50

自然酸化物層 401A を、フッ化水素 (HF) と脱イオン (DI) 水を含む洗浄液を用いて除去する。一実施形態において、洗浄液は、約 20 ~ 約 30 の温度に維持される約 0.1 ~ 約 10 質量 % の HF を含有する水溶液である。一例において、洗浄液は、約 25 の温度で維持される約 0.5 wt % の HF を含む。ステップ 252 で、基板 401 を洗浄液に浸漬することができ、その後、脱イオン水ですすぐことができる。ステップ 252 は、処理の間、超音波エネルギーの分配を含むことができる单一基板処理チャンバか又は複数基板バッチタイプ処理チャンバ内で行うことができる。或いは、ステップ 252 は、統合処理システム 600 (図 7) の单一基板湿式洗浄リアクタを用いて行うこともできる。他の実施形態において、自然酸化物層 401A は、RCA 洗浄法を用いて除去することができる。ステップ 252 の完了時に、基板 401 を真空ロードロック又は窒素 (N<sub>2</sub>) でバージされた環境に入れる。或いは、ステップ 252 は、統合処理システム 600 (図 7) の单一基板湿式洗浄リアクタを用いて行うことができる。

10

## 【0026】

[0049]ステップ 254 で、熱酸化物 (SiO<sub>2</sub>) 層 402 を基板 401 (図 3B) の洗浄した表面 401B 上で成長させる。一般に、熱酸化物層 402 の厚さは、約 3 ~ 約 35 オングストロームである。ロジックタイプの用途において、熱酸化物層 402 の厚さは、約 6 ~ 約 15 オングストロームであるのがよく、メモリタイプの用途において、熱酸化物層 402 厚さは、約 15 ~ 約 40 オングストロームであるのがよい。本発明の実施形態は、熱酸化物層の厚さが 35 オングストロームより大きくてもよい用途に用いることができる。熱酸化ステップ 254 によって、シリコン誘電体接合部上に形成する二酸化シリコン (SiO<sub>2</sub>) の副層が形成されることになる。ステップ 254 は、堆積される誘電体層 (例えば、図 3D における高 k 誘電体層 404) の上の誘電体 / シリコン接合部の品質と信頼性を改善し、表面 401B の下のチャネル領域の電荷キャリヤの移動度も増大させると考えられる。ステップ 254 は、図 7 に示した統合処理システム 600 における基板処理チャンバ 614A-614F の一つに位置決めされた急速熱処理 ( RTP ) リアクタを用いて行うことができる。一つの適切な RTP チャンバは、カリフォルニアのサンタクララの Applied Materials 社から入手できる RADIANCE (登録商標) RTP チャンバである。一例において、6 オングストローム二酸化シリコン (SiO<sub>2</sub>) 膜は、酸素 (O<sub>2</sub>) ガスの流量が 2 s 1 m である 18 秒、750 、2 トールのプロセスを用いて基板 401 の表面 401B 上に形成される。この例において、熱酸化物層 402 の形成でプロセスチャンバに噴射される反応性ガスは酸素であるが、ある場合には不活性キャリヤガスをプロセスチャンバに加えて、所望のチャンバ圧を得ることができる。或いは、ある場合には、ステップ 254 で、一酸化窒素 (NO) や亜酸化窒素 (N<sub>2</sub>O) のような反応性ガス、又は水素 (H<sub>2</sub>) / 酸素 (O<sub>2</sub>) や亜酸化窒素 (N<sub>2</sub>O) / 水素 (H<sub>2</sub>) のような反応性ガス混合物を用いることが望ましいことがある。

20

30

## 【0027】

[0050]ステップ 257 で、高 k 誘電体層 403 を形成するのに望ましい物質で熱酸化物層をドープするために用いられる金属イオン含有プラズマに熱酸化物層 402 をさらす。ステップ 257 で形成される高 k 誘電体層 403 は、ハフニウム (Hf) 、ランタン (La) 又は他の同様の物質でドープされる二酸化シリコン層であるのがよい。一実施形態において、低エネルギー堆積プロセスは、以下で参照される、図 4A - 図 4C 及び図 4F によって記載されるチャンバと同様のプロセスチャンバを用いて行われる。一実施形態において、処理領域 522 に分配された RF エネルギーを用いてプラズマを生成し、その後、ターゲット (例えば、図 4A の符号 505 又は図 4B の符号 571) 上にカソードバイアスを形成してそこからの物質をスペッタすることによってドーパント物質を熱酸化物層 402 に分配することが望ましい。一態様において、スペッタされた又はイオン化された物質を熱酸化物層 402 内の所望範囲の深さに注入させるために基板支持体 562 を RF バイアスにかけるか、DC バイアスにかけるか、又は接地することが望ましい。他の態様において、自己バイアスを生成するためにプラズマに相対して基板支持体 562 間に生じる電圧が、熱酸化物層 402 に衝撃するイオン化された物質のエネルギーを減少させるほど

40

50

低いように基板支持体 562 を電気的に“浮遊させる”ことが望ましい。低エネルギー物質を分配して熱酸化物層 402 をドープする種々の方法は、図 4A - 図 4F 及び図 5A - 図 5C と共に以下に記載される。チャンバ圧、RF 電力、パルスDC 電力、基板支持体 562 に印加されたバイアス及び/又は処理時間の注意深い制御によって、熱酸化物層 402 におけるドーパント量とドーパント物質の濃度と深さとを制御することができる。一実施形態において、プラズマとしては、アルゴンイオンと、ハフニウムハフニウム、ランタン、アルミニウム、チタン、ジルコニア、ストロンチウム、鉛、イットリウム、バリウムのような金属イオンを含有してもよいだけでなく、一つ以上の所望による不活性ガスを含有してもよい。典型的な不活性ガスとしては、ネオン( Ne )、ヘリウム( He )、クリプトン( Kr )、キセノン( Xe )、窒素( Ne )等が挙げられるのがよい。一例において、熱酸化物層 402 は、約 5 ~ 約 30 原子パーセント( 原子% )のハフニウム( Hf )でドープされる。一般的には、熱酸化物層 402 及びシリコンチャネル表面( 例えば、表面 401B )との間の接合部の前に数オングストローム又は少なくとも数オングストロームのゼロ近くになるように、熱酸化物層 402 のドーパント濃度を低下させることができ。一例において、処理チャンバ( 図 4A における符号 500 )の誘導結合変形例を用いた場合、10 原子% ( 平均 ) 濃度のハフニウム( Hf )が、-150VDC をハフニウムターゲット( 符号 505 )に印加し且つ“浮遊している”基板ペデスタルを用いて 5 % 負荷サイクルを用いた 13.56MHz の周波数と 50 ワットの電力で RF エネルギーをコイル( 符号 509 )に分配する 180 秒と 10 ミリトルのチャンバ圧プロセス( 例えば、主としてアルゴンガス )を用いて熱酸化物層 402 内に配置される。他の例において、図 4G に示されたものと同様のプロセス構成を用いた場合、7 原子% 濃度( 平均 )のハフニウム( Hf )が、約平均 100 ワットの RF 電力( 即ち、~5 % の負荷サイクルと~2000W ピーク RF 電力 )をハフニウム含有ターゲット 505 に印加し且つ“浮遊している”基板ペデスタルを用いて 13.56MHz の周波数で約 100 ワット平均 RF 電力( 即ち、~5 % の負荷サイクルと~2000W ピーク RF 電力 )をコイル 509 に印加する 180 秒と 10 ミリトルのチャンバ圧プロセス( 主としてアルゴンガス )を用いて熱酸化物層内に配置される。一実施形態において、ステップ 257 で熱酸化物層 402 に対する損傷を防止するために、平均 RF 電力を約 1000W 未満のレベルに保持する。他の実施形態において、ステップ 257 で用いられる平均 RF 電力は、約 200W 未満である。他の実施形態において、更に、ステップ 257 で用いられる平均 RF 電力は、約 50W 未満である。一実施形態において、ステップ 257 は、図 7 に示した統合処理システム 600 における基板処理チャンバ 614A - 614F の一つに位置決めされた低エネルギー プラズマ処理チャンバ( 例えば、処理チャンバ 500 又はプロセスチャンバ 501 )を用いて行われる。

#### 【 0028 】

[0051] 一実施形態において、図 2A と図 3D に示されるように、ステップ 254 とステップ 257 を用いて熱酸化物層 402 から高 k 誘電体層 403 を形成する代わりに、金属有機化学気相堆積( MOCVD )プロセス、原子層堆積( ALD )プロセス又は他の同様の堆積プロセスを用いて基板 401 の表面 401B 上に高 k 誘電体層 404 を堆積させるために代替ステップ 256 を行うことができる。高 k 誘電体層 404 は、酸化ジルコニア( ZrO<sub>2</sub> )、酸化ハフニウム( Hf<sub>x</sub>O<sub>y</sub> )、ハフニウムシリケイトオキシド( Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>y</sub> )、酸化ランタン( La<sub>2</sub>O<sub>3</sub> )、及び/又は酸化アルミニウム( Al<sub>2</sub>O<sub>3</sub> )を含有するのがよいが、これらに限定されない。ステップ 256 は、例えば、 Applied Materials 社から入手できる Centura ALD High-K システムのような原子層堆積システムを用いて行うことができる。図 7 に示した統合処理システム 600 における基板処理チャンバ 614A - 614F の一つに ALD タイプリアクタを位置決めすることができる。

#### 【 0029 】

[0052] ステップ 259 で、プラズマ堆積プロセスを行うことによって高 k 誘電体層 403 、或いは高 k 誘電体層 404 の表面を終了して、終端領域 405 を形成する。一般に、

層物質を堆積させ及び/又は高 k 誘電体層 403、又は高 k 誘電体層 404 をドープすることによって終端領域 405 を形成する。酸化ランタン (La<sub>2</sub>O<sub>3</sub>) 又は酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>) のような不動態化物質を含有する終端領域 405 の添加は、表面を不動態化し、従来の A L D 又は M o C V D 高 k 膜に一般に見られる問題、フェルミ準位ピンニング又は閾値電圧シフトを解決すると考えられる。一実施形態において、高 k 誘電体層 403、又は高 k 誘電体層 404 は、約 0.1 ~ 約 10 原子% のランタン (La)、及び/又は約 0.1 ~ 約 10 原子% のアルミニウム (Al) でドープされる。他の実施形態において、高 k 誘電体層 403、又は高 k 誘電体層 404 は、約 0.25 ~ 約 5 原子% のランタン (La) 及び/又は約 1 ~ 約 10 原子% のアルミニウム (Al) でドープされる。高 k 誘電体層 403 又は高 k 誘電体層 404 のドーパント濃度を低下させることが望ましいので、高 k 誘電体層 403、又は高 k 誘電体層 404 内に数オングストロームだけ広がると考えられる。一実施形態において、以下の図 4A - 図 4C に記載されるプロセスチャンバを用いてランタン (La) ドーパントを高 k 誘電体層 403 に入る。一例において、-1000 V DC をランタンターゲット (例えば、図 4A における符号 505) に適用し且つ “浮遊している” 基板ペデスタルを用いて 5 % 負荷サイクルを用いた 13.56 MHz の周波数と 50 W の電力で RF エネルギーをコイルに分配する、120 秒と 10 ミリトルのチャンバ圧プロセス (例えば、主にアルゴンガス) を用いた 10 原子% のハフニウムドープされた高 k 誘電体層 403 に 0.5 原子% (平均) 濃度のランタン (La) を入れる。

## 【0030】

[0053] 一実施形態において、ステップ 259 は、図 4A - 図 4C に示した処理チャンバ 500 又はプロセスチャンバ 501 と同様のプロセスチャンバで行うことができる。この構成において、終端領域 405 は、ステップ 257 で上記プロセスと同様の、低エネルギー注入タイププロセスを行うことによって形成される。一態様において、処理領域 522 に分配された RF エネルギーを用いてプラズマを生成し、その後、ターゲット 505 上にカソードバイアスを形成してそこから物質をスパッタすることによって、ドーパント物質を高 k 誘電体層 403 の上部のほとんどの領域に分配する。スパッタされイオン化された物質を高 k 誘電体層 403 に注入させるために、基板支持体 562 は RF バイアスをかけても、DC バイアスをかけても、接地されても、浮遊してもよい。低エネルギー物質を分配して高 k 誘電体層 403 をドープする種々の方法は、以下の図 4A - 図 4F と図 5A - 図 5C と共に後述される。それ故、チャンバ圧、RF 電力、パルス DC バイアス、基板支持体 562 に印加される所望によるバイアス及び/又は処理時間を注意深く制御することによって、高 k 誘電体層におけるドーパント量とドーパント物質の濃度と深さを制御することができる。一実施形態において、ドーパントは、アルミニウム含有物質、ランタン含有物質、又は他の同様の物質である。

## 【0031】

[0054] 一実施形態において、ステップ 259 は、図 7 に示した統合処理システム 600 の基板処理チャンバ 614A - 614F の一つに位置決めされた処理チャンバ 500 を用いて行うことができる。一態様において、ステップ 259 を行うために用いられる処理チャンバ 500 は、ステップ 257 を行うために用いられるプロセスチャンバと異なる処理チャンバである。他の実施形態において、統合処理システム 600 に取り付けられている単一処理チャンバ 500 は、ステップ 257 とステップ 259 を行うために用いられるが、各ステップは、処理チャンバ 500 の処理領域 522 に配置される異なるターゲット物質を用いて行われる。

## 【0032】

[0055] ステップ 259 の他の実施形態において、終端領域 405 は、スパッタリングプロセスを行うことにより高 k 誘電体層 403 の表面上に堆積される物質の追加の層であるのがよい。一態様において、スパッタリングプロセスは、図 4A - 図 4C に示した処理チャンバ 500 又はプロセスチャンバ 501 と同様のプロセスチャンバを用いて行われる。この構造において、終端領域 405 は、処理領域 522 へ分配される RF エネルギーを用

いてプラズマを生成させ、その後、ターゲット 505 上にカソードバイアスを形成して、そこから物質をスパッタすることにより、高 k 誘電体層 403 の最上部上にターゲット物質を堆積させることによって形成される。基板支持体 562 は、高 k 誘電体層 403 に注入するスパッタされイオン化された物質のエネルギーと深さを制御するために R F バイアスがかけられても、接地されても、又は電気的に浮遊してもよい。一実施形態において、堆積された層は、アルミニウム (A1)、ランタン (La)、又は他の適切な物質を含有する。

### 【0033】

[0056]一実施形態において、所望によるステップ 260 は、酸素含有 R F プラズマを用いて、さらされた物質を酸化して、それらを誘電体物質に変換する。一例において、高 k 誘電体層 403、高 k 誘電体層 404 及び/又は終端領域 405 は、酸素含有プラズマにさらして、酸化アルミニウム又は酸化ランタンを形成する。他の実施形態において、プラズマは、窒素 ( $N_2$ ) を含有し、 $O_2$ 、NO、 $N_2O$  のような一つ以上の酸化ガスを含有してもよい。プラズマは、また、アルゴン (Ar) やヘリウム (He) のような一つ以上の所望による不活性ガスを含有してもよい。ステップ 260 は、例えば、統合処理システム 600 (図 7) の減結合プラズマ窒化 (DPN) プラズマリアクタを用いて行うことができる。一実施形態において、プラズマ酸化ステップの代わりに熱酸化ステップを用いて、さらされた物質を酸化して、それを誘電物質に変換する。一例において、プラズマ酸化プロセスは、さらされた物質を酸化させるために、約 100 sccm の窒素流量と約 100 sccm の酸素流量を用いて 5 % の負荷サイクルと 1000 W ピーク電力 (即ち、平均電力 50 W) を 13.56 MHz の R F 周波数で 30 秒間用いて行われる。

### 【0034】

[0057]一代替的実施形態において、所望によるステップ 262 は、ステップ 260 の代わりに用いられる。ステップ 262 において、高 k 誘電体層 403、又は高 k 誘電体層 404 と、基板 401 は、約 600 ~ 1100 の間の温度でアニールされる。約 600 ~ 800 の温度で行われるアニールのようなより低い温度のアニールは、ハフニウムとシリコン (Si)、酸素 ( $O_2$ )、又はそれらの双方とのような前に堆積された物質の結晶化を防止するために有利に用いることができる。ステップ 262 は、統合処理システム 600 の RADIANCE (登録商標) 又は RTPXE+ リアクタのような適切な熱アニールチャンバ、又は単一基板炉或いはバッチ炉を用いて行うことができる。ステップ 262 により、高 k 誘電体層 403 又は終端領域 405 にシリケートサブレイヤーが形成される。一実施形態において、ステップ 262 は、約 600 ~ 約 1100 の基板表面温度と、約 0.1 ~ 約 50 トールのプロセスチャンバ圧を維持しつつ、約 2 ~ 約 5000 sccm の酸素 ( $O_2$ ) と約 100 ~ 約 5000 sccm の一酸化窒化 (NO) の少なくとも一つを供給することによって行われ、所望によりいずれのガスも窒素 ( $N_2$ ) と混合されてもよい。プロセスは、約 5 - 180 秒間行うことができる。一例において、ステップ 262 は、60 sccm の流量の酸素 ( $O_2$ ) ガスと 940 sccm の流量の窒素 ( $N_2$ ) ガスを持つ、15 秒、900 、1 トールプロセスである。他の例において、約 1000 の温度と約 1 トールの圧力で約 15 秒間プロセスチャンバを維持しつつ、 $O_2$  を約 200 sccm (例えば、約 200 mT の酸素分圧) で供給し、窒素 ( $N_2$ ) を約 800 sccm で供給する。更に他の例において、NO は、チャンバを約 1000 の温度と約 0.5 トールの圧力で約 15 秒間維持しつつ、約 500 sccm で供給される。

### 【0035】

[0058]一実施形態において、ステップ 256、257、又は 259 のいずれかを行った後、ステップ 260 又は 262 はいずれも行われない。プロセス順序 251 の一実施形態において、ステップ 260 又は 259 と同様の酸化ステップは、終端領域 405 が高 k 誘電体層 403 の上に堆積される前に、ステップ 257 で堆積されたドーパント物質を再酸化するために、ステップ 257 と 259 の間で行うことができる。

### 【0036】

[0059]ステップ 264 で終端領域 405 と高 k 誘電体層 403、又は高 k 誘電体層 40

10

20

30

40

50

4は、これらの領域における窒素量を増やすために窒素プラズマ中で処理される。プロセスは、約10～約2000 sccmの窒素( $N_2$ )、約20～約500の基板ペデスター温度、約5～約200ミリトルの反応チャンバの圧力を与えることによって、DNPリアクタを用いて行うことができる。高周波(RF)プラズマは、例えば、約13.56 MHz又は60MHzで、連続波(CW)か又は約3～5kWまでのパルスプラズマ電源を用いて励起される。パルスの間、ピークRF電力、周波数、負荷サイクルは、典型的には、それぞれ、約10～3000W、約10kHz、2%～100%の範囲で選択される。このプロセスは、約1秒～180秒間行うことができる。一例において、 $N_2$ は、約200 sccmで供給され、約1000WのピークRF電力は、約10kHzで約5%の負荷サイクルでパルスされ、約25の温度と約10～約80ミリトルの圧力で15秒～180秒間誘導性プラズマソースに印加される。プラズマは、他のプラズマソースの中で、準遠隔プラズマソース、誘導性プラズマソース、又はラジアルラインスロットアンテナ(RLSA)ソースを用いて生成される。代替的実施形態において、CW及び/又はマイクロ波電力ソースを用いて、窒素含量が高い領域を形成することができる。

#### 【0037】

[0060]ステップ266で、基板401は、基板401上に形成される層の間の漏れ電流を減少するためにアニールすることができ、表面401Bの下のチャネル領域における電荷キャリヤの移動度を増大させるだけでなく、形成されたデバイスの信頼性が改善される。ステップ266は、基板401上に形成される層内の欠陥の数を減少させることを援助し得る。ステップ266でステップ264において形成された窒化層をアニールするか又は不活性化する作用もまた、ホウ素ドープされた多結晶シリコンゲート電極からのホウ素の拡散に対する有効なバリアの形成を促進することを援助する。ステップ266は、統合処理システム600のRADIANCE(登録商標)又は RTPXE(登録商標)リアクタのような適切な熱アニールチャンバ、又は単一基板炉或いはバッチ炉を用いて行うことができる。一実施形態において、ステップ266のアニールプロセスは、約800～約1100の基板表面温度と、約0.1～約50トルの反応チャンバの圧力を維持しつつ、約2～約5000 sccmの流量の酸素( $O_2$ )と約100～約5000 sccmの流量の一酸化窒素( $NO$ )の少なくとも一つを供給することによって行うことができ、所望によりガスを窒素( $N_2$ )と混合してもよい。プロセスは、約5～180秒間行われるのがよい。一実施形態において、酸素( $O_2$ )ガスは、約1000の温度と約0.1トルの圧力で約15秒間維持しつつ、約500 sccmで供給される。一実施形態において、ステップ266は、上記ステップ262に用いられたものと同様のプロセス法を用いる。

#### 【0038】

[0061]ステップ260、262、264又は266の完了時に、形成された層の上に一つ以上の層が堆積されて、ステップ268を用いて形成されたMOSデバイスのゲート領域、又はゲート電極を形成する。ステップ268の一実施形態において、多結晶シリコン層は、ゲート電極を提供するために上記層の上のゲート領域に堆積される。一例において、多結晶シリコン層は、従来の多結晶シリコン堆積プロセスを用いて堆積される。一実施形態において、多結晶シリコン堆積チャンバ(図示せず)は、統合処理システム600の一部である。一実施形態において、多結晶シリコンは、図7に示される統合処理システム600の基板処理チャンバ614A-614Fの一つを備える、Applied Materials社から入手できるCentura CVDリアクタのようなCVD又はALDリアクタを用いてプロセス順序251で形成された層の上に堆積される。

#### 【0039】

[0062]ステップ268の他の実施形態において、図3Fに示したように、ゲート領域408は、薄い金属層407と多結晶シリコン層406のような複数の導電層を含有する。一実施形態において、ゲート領域408は、従来の多結晶シリコンゲート物質より高いキャリヤ濃度を持つゲート物質を提供するためのプロセス順序251で形成された層の上に堆積される薄い金属層407を含有する。薄い金属層407は、約5～約200オングス

10

20

30

40

50

トロームの厚さを持つのがよい。一実施形態において、薄い金属層 407 は、タンタル (Ta)、窒化タンタル (Ta<sub>N</sub>)、炭化ランタン (LaC)、タングステン (W)、窒化タングステン (WN)、窒化シリコンタンタル (TaSiN)、ハフニウム (Hf)、アルミニウム (Al)、ルテニウム (Ru)、コバルト (Co)、チタン (Ti)、ニッケル (Ni)、窒化アルミニウムチタン (TiAlN)、窒化ルテニウム (RuN)、窒化ハフニウム (HfN)、ケイ化ニッケル (NiSi)、窒化チタン (TiN) 又は他の適切な物質のような金属を含有する。薄い金属層 407 は、図 7 に示した統合処理システム 600 に取り付けられている処理チャンバ 500 (図 4A) 又はプロセスチャンバ 501 (図 4B - 図 4C) を用いて有利に形成することができる。この構成において、薄い金属層 407 は、RF エネルギーを用いてプラズマを生成し、ターゲットにバイアスをかけてそこからの金属をスパッタし、その後、所望により基板支持体 562 (図 4A - 4B) にバイアスをかけてもよく、スパッタされイオン化された金属物質をあらかじめ形成された層の上に堆積させることによりプロセス順序 251 で形成された層の上にターゲット物質を堆積させることによって形成される。スパッタ堆積プロセスを動かすための RF エネルギーの使用は、非常に少量の物質を基板表面上に確実に堆積させることを可能にする。反対に、薄い金属層を形成するのに充分低いレベルまで堆積速度を低下させるのに必要とされるスパッタリング (DC) 電圧の印加が、通常はスパッタリングプラズマを持続しないので、従来の物理気相堆積、又はスパッタリング技術は、薄い物質層を確実に堆積させる能力が大幅に制限される。他の実施形態において、薄い金属層 407 は、従来の CVD、PECVD 又は ALD プロセスを用いて形成することができる。

#### 【0040】

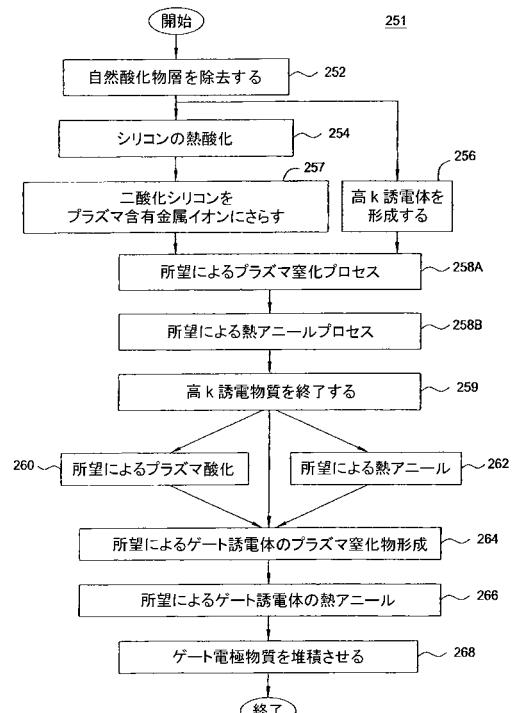

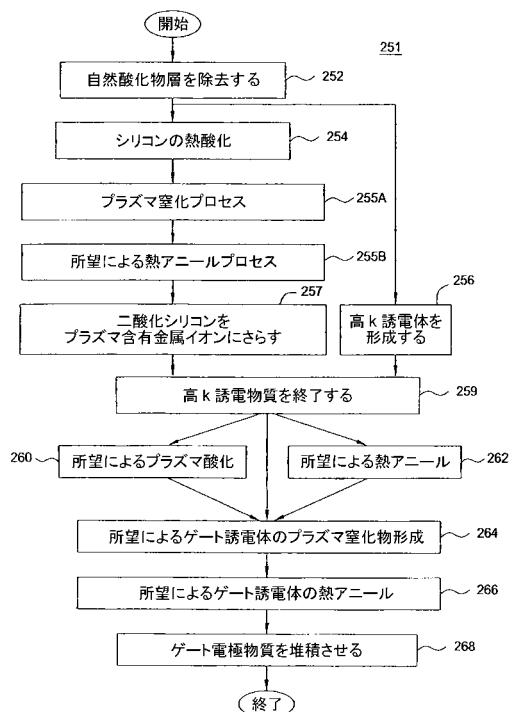

[0063] 図 2B は、プロセス順序 251 の他の実施形態を示す図である。図 2B に示したプロセス順序 251 は、二つの所望によるステップ 258A 及び/又は 258B の少なくとも一つがステップ 257、又はステップ 256 とステップ 259 の間に加えられる以外は、図 2A に示された方法のステップと同じである。一実施形態において、ステップ 254、256 又は 257 の一つで形成された高 k 誘電体層 403、又は高 k 誘電体層 404 に見られる物質の一つ以上を窒化するためにプラズマ窒化ステップがプロセス順序 251 に加えられる。一例において、ステップ 258B、262、又は 266 のような続いてのアニールステップで、高 k 誘電体層 403、又は高 k 誘電体層 404 に見られるハフニウム物質の結晶化を防止するためにプラズマ窒化プロセスを用いて窒化ハフニウム含有層を形成することは望ましいことである。一実施形態において、ステップ 258A は、ステップ 264 と共に本明細書に記載されるプロセスを用いて行われる。

#### 【0041】

[0064] 一実施形態において、所望による熱アニールステップ、ステップ 258B は、形成された高 k 誘電体層 403 又は高 k 誘電体層 404 における欠陥や応力を減少させて形成されたデバイスの信頼性を改善するためにプロセス順序 251 に加えられる。一実施形態において、ステップ 258B は、ステップ 262 及び/又はステップ 266 と共に本明細書に記載されるプロセスを用いて行われる。一実施形態において、ステップ 258B は、上記ステップ 258A を行った後に終了する。一例において、ステップ 258B は、酸素 (O<sub>2</sub>) ガスの流量が 60 sccm で窒素 (N<sub>2</sub>) ガスの流量が 940 sccm である、15 秒、900、1 トールのプロセスである。

#### 【0042】

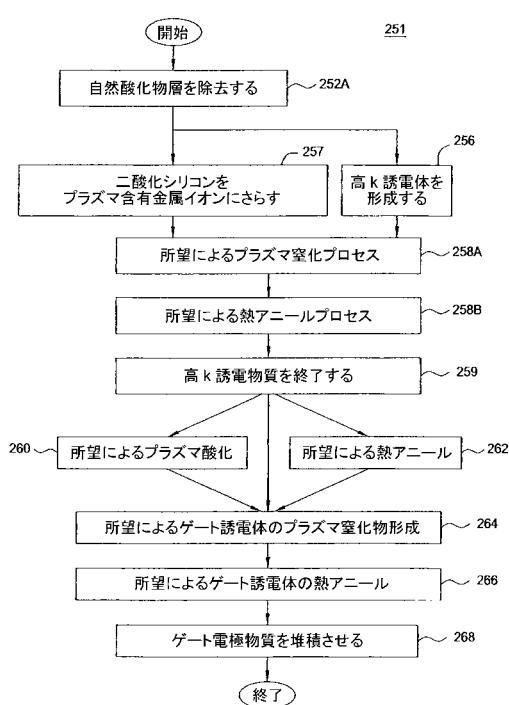

[0065] 図 2C は、プロセス順序 251 の他の実施形態を示す図である。図 2C に示したプロセス順序 251 は、ステップ 253 がステップ 252 とステップ 254 の間に加えられ、ステップ 256 がステップ 254 の後に行われる以外は図 2A に示したステップと同じである。この実施形態において、プラズマ窒化ステップ、ステップ 253 を、ステップ 252 で自然酸化物層を除去した後にプロセス順序 251 に加えて、ステップ 254 又はステップ 256 を行う前に基板表面を窒化する。窒化されたシリコン基板表面は、続いての熱酸化ステップ (ステップ 254) で形成される酸化シリコン層の表面に又は酸化シリコン層の近くに残る望ましい酸窒化シリコン (SiON) を形成することを援助すると考

えられる。形成された二酸化シリコン層の表面に又は二酸化シリコン層の近くに残る Si O N 層の形成は、続いてのプロセスステップでゲート電極物質（ステップ 268）のゲート誘電体層への拡散を最小にすることを援助することができる。ステップ 256 と 254 がこの実施形態で行われる順序は、ステップ 256 を用いて高 k 誘電体層を堆積させる前に酸窒化シリコン（SiON）接合層を形成することを可能にするために変更し、高 k 誘電体層とデバイスのチャネル領域の間の接合部の特性を改善することを援助する。ステップ 253 は、カリフォルニアのサンタクララの Applied Materials 社から入手できる DPN リアクタで行うことができる。一例において、ステップ 253 は、25 W 平均 RF 電力（500W ピーク RF 電力の 5% 負荷サイクル）、N<sub>2</sub> の 200 sccm のガス流量、25 の基板温度を用いて、10 秒、70 ミリトールプロセスを用いる。また、プロセス順序 251 の一実施形態において、ステップ 254 は、ステップ 253 で行われた窒化されたシリコン表面の望ましい特質が保持されることを確実にするように変えられる。この場合、高品質誘電体膜が形成されることを確実にするためにステップ 254 で酸素と共に窒素（N<sub>2</sub>）のような他の反応性ガスをプロセスチャンバに噴射することは望ましいことである。一例において、酸窒化シリコン（SiON）膜は、15 sccm の流量の酸素（O<sub>2</sub>）ガスと、5 s1m 流量の窒素（N<sub>2</sub>）ガスを持つ 30 秒、1050、5 トール（即ち、15 ミリトールの酸素分圧）のプロセスに続いて、0.5 s1m 流量の酸素（O<sub>2</sub>）ガスと 4.5 s1m 流量の窒素（N<sub>2</sub>）ガスを 15 秒間の変更ガス設定を用いて表面 401B 上に形成される。

## 【0043】

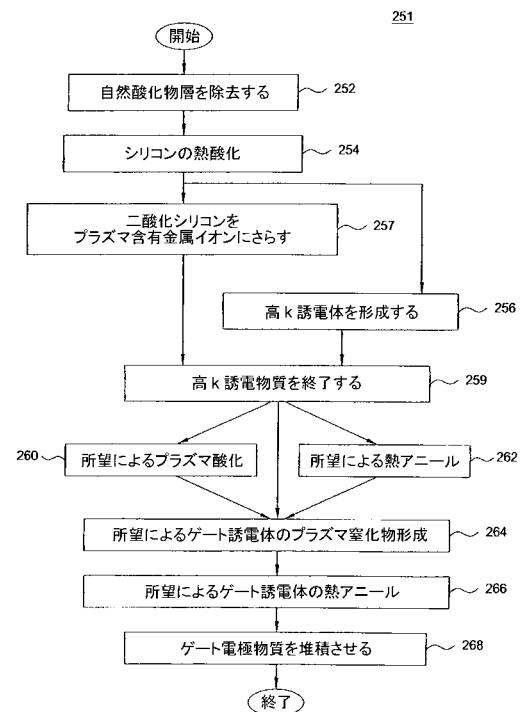

[0066] 図 2D は、プロセス順序 251 の他の実施形態を示す図である。図 2D に示したプロセス順序 251 は、二つの所望によるステップ 255A 又はステップ 255B がステップ 254 と 257 の間に加えることができる以外は、図 2A に示したステップと同じである。一実施形態において、所望によるプラズマ窒化ステップ、ステップ 255A をステップ 254 とステップ 257 の間に加え、ステップ 254 で形成された熱酸化物層の最上面を窒化して、SiON 層を形成する。SiON 層は、ゲート電極物質がゲート誘電体層に拡散することを防止する拡散バリヤとして作用することができる。一例において、ステップ 255A は、50W 平均 RF 電力（1000W ピークの RF 電力の 5% の負荷サイクル）、N<sub>2</sub> の 200 sccm のガス流量、約 25 の基板温度を用いる 30 秒、10 ミリトールプロセスを用いる。

## 【0044】

[0067] 図 2D を参照すると、一実施形態において、所望による熱アニールステップ、ステップ 255B をプロセス順序 251 に加えて、形成された高 k 誘電体層 403 の欠陥と応力を減少させて、形成されたデバイスの信頼性を改善する。一例において、ステップ 255B のアニールプロセスは、約 1050 の基板温度と、約 1 ~ 約 5 トールの反応チャンバの圧力を維持しつつ、約 15 sccm の流量の酸素（O<sub>2</sub>）と約 500 sccm の流量の窒素（N<sub>2</sub>）の少なくとも一つを供給することによって行うことができる。他の実施形態において、ステップ 255B は、ステップ 262 及び/又はステップ 266 と共に本明細書に記載されたプロセスを用いて行われる。一実施形態において、ステップ 255B は、上記ステップ 255 を行った後に完了する。

## 【0045】

[0068] 図 2E は、プロセス順序 251 の他の実施形態を示す図である。図 2E に示したプロセス順序 251 は、ステップ 254 が除去され、ステップ 252 を変更して（新しいステップ 252A）、湿式洗浄プロセスが酸化シリコン含有接合層を形成することを可能にする以外、図 2A に示したステップと同じである。この実施形態において、新しいステップ 252A は、洗浄し、湿式洗浄プロセスを用いて基板の表面 401B 上に酸化物層を意図的に形成する。新しいステップ 252A は、カリフォルニア、サンタクララの Applied Materials 社から入手できる Emerison<sup>TM</sup> チャンバ内で行うことができる。一例において、4 ~ 5 オングストロームの酸化物層は、ステップ 252A で、基板を希フッ化水素酸（HF）浴に 8 分間浸漬し、その後、50 で 6 分間維持される

10

20

30

40

50

標準洗浄 1 ( S C 1 ) 浴 ( 例えは、 < 5 容積 % の水酸化アンモニウム ( N H<sub>4</sub> O H ) / < 3 容積 % の過酸化水素 ( H<sub>2</sub> O<sub>2</sub> ) / 残量の D I 水 ) 内で洗浄し浸漬し、その後、基板を D I 水を含有するメガソニック作動タンク ( 即ち、 1 5 0 0 W ) 内で所望される時間すすぐことにより形成される。他の例において、酸化物層は、オゾン ( O<sub>3</sub> ) 含有洗浄液を用いる湿式洗浄プロセスによって形成することができる。

#### 【 0 0 4 6 】

[0069] 図 2 F は、プロセス順序 2 5 1 の他の実施形態を示す図である。図 2 F に示したプロセス順序 2 5 1 は、ステップ 2 5 6 がステップ 2 5 4 の後に行われる以外、図 2 A に示したステップと同じである。この実施形態において、ステップ 2 5 6 とステップ 2 5 4 が行われる順序は、ステップ 2 5 6 で薄い二酸化シリコン ( S i O<sub>2</sub> ) 層 ( 例えは、 < 1 0 オングストローム ) が高 k 誘電体層を堆積する前に形成されることを可能にするように変更されている。一実施形態において、薄い高 k 誘電体層 4 0 4 は、 A L D タイプの堆積プロセスを用いて、ステップ 2 5 4 で成長する熱酸化物層 4 0 2 上に堆積させる。この構成は、完全なスタックの望ましい誘電特性を示しつつ、ステップ 2 5 4 で形成された薄い二酸化シリコン層がデバイスの誘電体層とチャネル領域の間の接合で良好な誘電体 / チャネル領域接合部を与えるので有用であると考えられる。

10

#### 【 0 0 4 7 】

##### 設計のハードウェア態様

[0070] 上述したように、上記ステップ 2 5 7 とステップ 2 5 9 と共に記載されたプラズマ処理プロセスを用いて高 k 誘電体層を形成することは望ましい。大きなプラズマ電位、例えば、数十ボルト程度で用いるプラズマプロセスは、薄いゲート誘電体層に対する損傷を引き起こし、衝撃金属原子が形成された M O S デバイスの下に横たわるチャネル領域に混入することさえ引き起こし得る。二酸化シリコンのような誘電体層に対する損傷又は金属原子の下に横たわる領域への混入は、デバイス性能の低下と漏れ電流の増加のために望ましくない。下記の種々の実施形態は、プラズマ処理プロセスを用いてゲート誘電体層を確実に形成するために使用し得る。このような金属プラズマ処理を行うために用いることができる種々の装置の例は、図 4 A - 4 C と図 4 F と共に以下に記載する。

20

#### 【 0 0 4 8 】

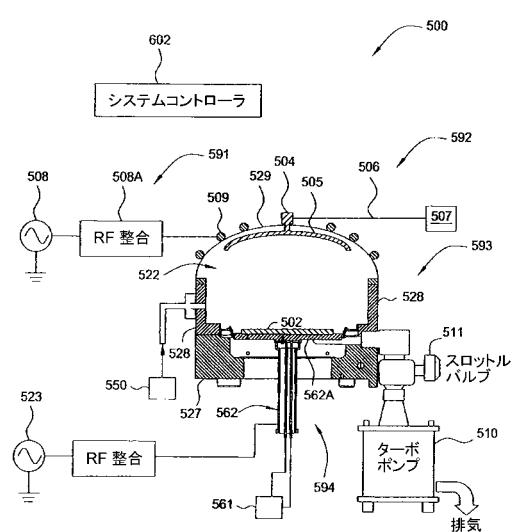

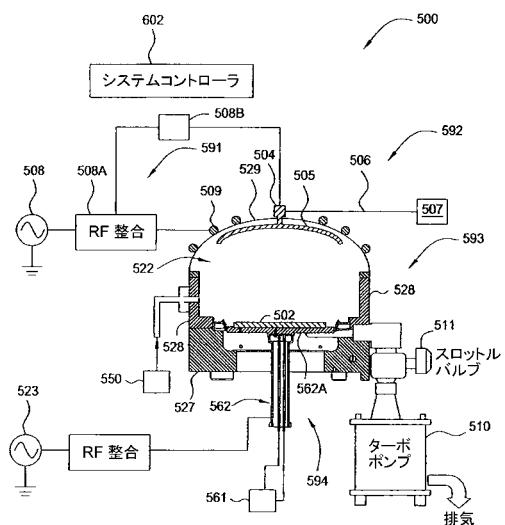

##### 誘導結合プラズマ処理チャンバ

[0071] 図 4 A は、上記ステップ 2 5 7 及び / 又は 2 5 9 のプロセスを行うために使用し得るプラズマ処理チャンバ 5 0 0 の一実施形態の概略断面図を示す図である。この構成において、処理チャンバ 5 0 0 は、処理領域 5 2 2 において、基板 4 0 1 ( 図 3 A ) のような基板 5 0 2 を処理することができる誘導結合プラズマ処理チャンバである。一実施形態において、処理チャンバ 5 0 0 は、誘導結合 R F ソースを用いる、サンタクララの Appled M a t e r i a l s 社から入手できる変更されたプラズマ窒化 ( D P N ) チャンバである。

30

#### 【 0 0 4 9 】

[0072] 処理チャンバ 5 0 0 は、通常は、誘導 R F ソースアセンブリ 5 9 1 、 D C ソースアセンブリ 5 9 2 、ターゲット 5 0 5 、システムコントローラ 6 0 2 、プロセスチャンバアセンブリ 5 9 3 、及び基板支持アセンブリ 5 9 4 を含有する。プロセスチャンバアセンブリ 5 9 3 は、通常は、プラズマプロセスがその中で行うことができるよう処理領域 5 2 2 内に真空を形成し得る要素を含有する。一般に、プロセスチャンバアセンブリ 5 9 3 は、処理領域 5 2 2 を密封するチャンバベース 5 2 7 とチャンバ壁 5 2 8 とチャンバリッド 5 2 9 を含有する。処理領域 5 2 2 は、チャンバベース 5 2 7 及び / 又はチャンバ壁 5 2 8 を通って処理領域 5 2 2 に接続される真空ポンプ 5 1 0 の使用によって所望の真空圧に排気され得る。一般に、チャンバ壁 5 2 8 とチャンバベース 5 2 7 は、アルミニウム、又は他の適切な物質のような金属から形成することができる。一実施形態において、チャンバ壁 5 2 8 は、ターゲット 5 0 5 からスパッタされた物質がチャンバ壁 5 2 8 上に載ることを防止する取り外し可能なチャンバシールド ( 図示せず ) を持つことができる。

40

#### 【 0 0 5 0 】

[0073]誘導 R F ソースアセンブリ 5 9 1 は、通常は、チャンバリッド 5 2 9 に隣接して位置決めされているコイル 5 0 9 に接続される R F ジェネレータ 5 0 8 と R F 整合 5 0 8 A を含有する。一実施形態において、R F ジェネレータ 5 0 8 は、約 0 ~ 約 3 0 0 0 W で、約 4 0 0 k H z ~ 約 2 0 M H z の周波数で作動させることができる。一例において、R F ジェネレータ 5 0 8 は、1 3 . 5 6 M H z の周波数で動作させる。チャンバリッド 5 2 9 は、通常は、誘導 R F ソースアセンブリ 5 9 1 から分配される R F エネルギーが処理領域 5 2 2 でプラズマを形成するように適応される誘電体要素（例えば、石英、セラミック物質）である。一実施形態において、コイル 5 0 9 は、処理領域 5 2 2 に生成されるプラズマがスパッタプロセスでターゲットの活性面の近くに形成されるようにターゲット 5 0 5 の近くに位置決めすることができる。活性表面の近くのプラズマの制御は、低エネルギー 10 スパッタ堆積プロセスの間でスパッタされるターゲットの領域の近くのプラズマ密度を制御することを援助することができる。この構成は、コイル 5 0 9 によって生成されたプラズマのために、極端に薄いゲート誘電体層の望まれていないプラズマ衝撃の量を減少させるのに有用なものである。

#### 【 0 0 5 1 】

[0074]一実施形態において、チャンバリッド 5 2 9 は、真空シールされた電気的フィードスルー 5 0 4 が処理領域に位置決めされているターゲット 5 0 5 と接触させることを可能にするように変更される。この構成において、同軸ケーブル 5 0 6 を真空シールされたフィードスルー 5 0 4 に接続して、エネルギーを D C 電源 5 0 7 から分配して、プラズマに生成したイオンが物質をターゲットから基板 5 0 2 にスパッタさせる。図 5 A - 図 5 C 20 と共に以下に記載される一態様において、システムコントローラ 6 0 2 は、R F ジェネレータ 5 0 8 からの出力と D C ソース 5 9 2 アセンブリから分配される D C 電力を同期させるために用いられる。一実施形態において、ターゲット 5 0 5 は純粋な物質又はハフニウム (H f) 、ランタン (L a) 、アルミニウム (A l) 、チタン (T i) 、ジルコニウム (Z r) 、ストロンチウム (S r) 、鉛 (P b) 、イットリウム (Y) 、又はバリウム (B a) のグループより選択される元素を含有する合金から形成することができる。

#### 【 0 0 5 2 】

[0075]一態様において、プロセスチャンバアセンブリ 5 9 3 は、また、チャンバベース 5 2 7 とチャンバ壁 5 2 8 とチャンバリッド 5 2 9 によって形成された処理領域 5 2 2 に一つ以上のプロセスガスを分配するように適合されたガス分配システム 5 5 0 を含有する。処理領域 5 2 2 の圧力は、ガス分配システム 5 5 0 とスロットバルブ 5 1 1 によって調節される真空ポンプ 5 1 0 のポンピング速度によって分配されたガス流量を調整するために用いられるシステムコントローラ 6 0 2 の使用によって制御され得る。一態様において、処理中のチャンバ圧は、約 5 ミリトール ~ 約 1 0 0 ミリトールである。 30

#### 【 0 0 5 3 】

[0076]基板支持アセンブリ 5 9 4 は、通常は、基板支持部材 5 6 2 A を含有する基板支持体 5 6 2 を含む。基板支持部材 5 6 2 A は、基板を処理中に活発に保持するために使用し得る慣用の静電チャックであっても簡単な基板支持ペデスタルであってもよい。温度コントローラ 5 6 1 は、通常は、熱交換機（図示せず）に結合される埋め込まれた抵抗加熱素子又は流体冷却チャネルのような慣用の手段の使用による温度コントローラ 5 6 1 によって所望の温度設定に基板支持部材 5 6 2 A を加熱及び/又は冷却するように適合される。一態様において、温度コントローラ 5 6 1 は、動作させ、基板支持部材 5 6 2 A 上に位置決めされた約 2 0 ~ 約 8 0 0 の温度に加熱するように適合される。処理の間、基板支持体 5 6 2 は、処理領域 5 2 2 において基板 5 0 2 の表面に生成されたプラズマ内に有するイオンを引っぱるための基板支持体 5 6 2 の部分に R F バイアスが印加され得るように R F ジェネレータに接続するのがよい。一実施形態において、基板支持部材 5 6 2 A は、基板 5 0 2 のイオン衝撃損傷を最小にするためにプラズマプロセスの間、接地されるか、D C バイアスをかけるか、又は電気的に浮遊している。 40

#### 【 0 0 5 4 】

[0077]R F エネルギーを R F ジェネレータ 5 0 8 から処理領域 5 2 2 に分配すると、イ 50

オン化される処理領域においてガス原子を生じる。その後、プラズマ内のイオン化された原子は、物質がターゲット 505 からスパッタされるとともに基板 502 の表面に載ることができるように DC ソースアセンブリ 592 によってターゲット 505 に印加されたカソードバイアスのためにターゲット 505 に引きつけられる。誘導 RF ソースアセンブリ 591 から分配された RF エネルギーと DC ソースアセンブリ 592 から印加された DC バイアスの干渉と相互作用を減少させる努力において、干渉が最小であり、堆積速度、膜均一性、膜質が最大にされたときに最小化できるように、DC ソースアセンブリ 592 及び RF ソースアセンブリ 591 から分配されたエネルギー パルスを同期することがしばしば望ましい。プラズマを励起するために誘導 RF ソースをパルスすると、低電子温度と、低エネルギー プラズマを生成し維持することによって基板の表面に対する損傷を引き起こす高プラズマ電位と関連した問題を改善する。一般に、パルス RF 誘導プラズマによって生成されるイオンは、プラズマ内に位置決めされた基板を損傷しない低イオンエネルギー(例えば、< 10 eV)でイオンを得る。このことは、2003年6月12日出願の共同譲渡された米国特許第 6,831,021 号により完全に記載され、この開示内容は本明細書に援用されている。アルゴン (Ar)、ネオン (Ne)、クリプトン (Kr)、又はキセノン (Xe) のようなほとんどの不活性ガスの低イオンエネルギーは、ハフニウム (Hf)、ランタン (La) 又は他の重金属又は誘電物質から製造されるターゲットから原子をスパッタするほどパルス RF ソースから充分なエネルギーを得ない。例えば、アルゴン プラズマについては、Hf と La ターゲットのスパッタリング閾値エネルギーは、それぞれ 42.3 eV と 25.5 eV であり、ゲート酸化物へのイオン注入の安全なイオンエネルギーは、通常は 10 eV 未満である。つまり、RF 誘導プラズマについて、ゲート誘電体層の形成するのに安全である充分低いイオンエネルギーは、ターゲット物質から所望の金属イオンをスパッタするほど充分高くない。それ故、スパッタリングプロセスを行うための DC ソースアセンブリ 592 からターゲットに印加した DC バイアスを用いることが求められている。種々のパルス堆積プロセスの様態を、図 5A - 図 5C と共に以下に記載する。

#### 【0055】

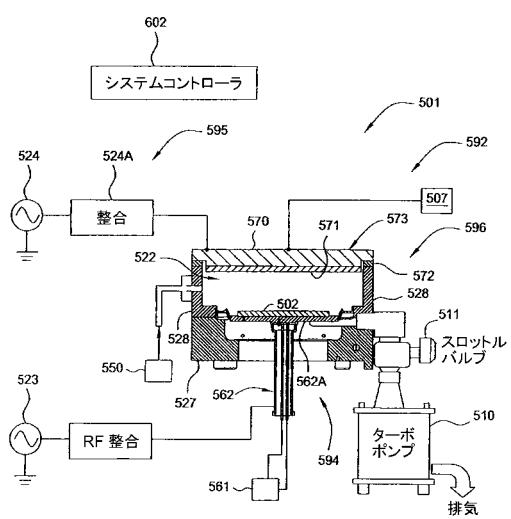

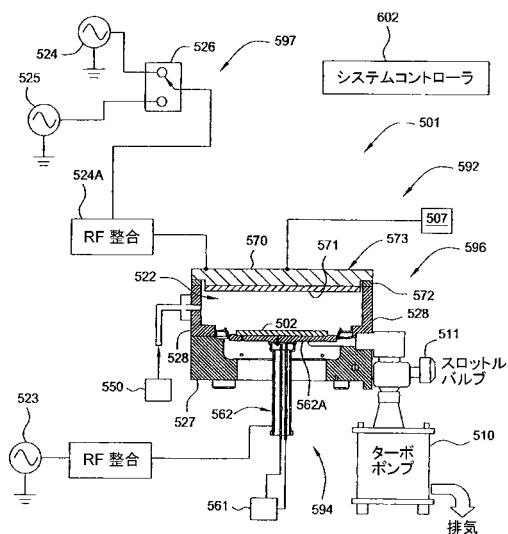

##### 容量結合プラズマ処理チャンバ

[0078] 図 4B - 図 4C は、上記ステップ 257 及び/又は 259 に記載したプロセスを行うために使用し得るプラズマ処理チャンバの他の実施形態の概略断面図を示す図である。この構成において、プロセスチャンバ 501 は、処理領域 522 において基板 502 を処理することができる容量結合プラズマ処理チャンバである。プロセスチャンバ 501 は、通常は、VHF ソースアセンブリ 595 と、ターゲットアセンブリ 573 と、システムコントローラ 602 と、プロセスチャンバアセンブリ 596 と、基板支持アセンブリ 594 とを含有する。この構成において、容量結合プラズマは、ターゲット 571 に接続される VHF ソースアセンブリ 595 の使用によってプロセスチャンバアセンブリ 596 内に含有するターゲット 571 と接地チャンバ壁 528 との間の処理領域 522 に形成される。プロセスアセンブリ 596 は、通常は、チャンバリッド 529 をチャンバ壁 528 上に密封して位置決めされるターゲットアセンブリ 573 と電気絶縁体 572 に置き換えた以外は、上の図 4A と共に記載された要素のすべてを含有する。プロセスチャンバアセンブリ 596 及び基板支持アセンブリ 594 内の要素は、処理チャンバ 500 によって記載されたものと同一か又は同様のものであり、そのように、適切な場合には同様の符号を用い、下で繰り返さない。

#### 【0056】

[0079] 図 4B を参照すると、一実施形態において、VHF ソースアセンブリ 595 は、ターゲットアセンブリ 573 の一つ以上の部分を通って処理領域 522 に RF エネルギーを分配するように適合される RF ソース 524 と整合 524A を含有する。ターゲットアセンブリ 573 は、通常は、バッキングプレートアセンブリ 570 とターゲット 571 を含有する。バッキングプレート 570 は、プロセス中の熱交換器(図示せず)とターゲット物質の充分な使用を促進するとともに堆積均一性を高めるように適合されるマグネットロ

ンアセンブリ（図示せず）から分配された流体ヘターゲットを冷却する流体チャネル（図示せず）を含有してもよい。

#### 【0057】

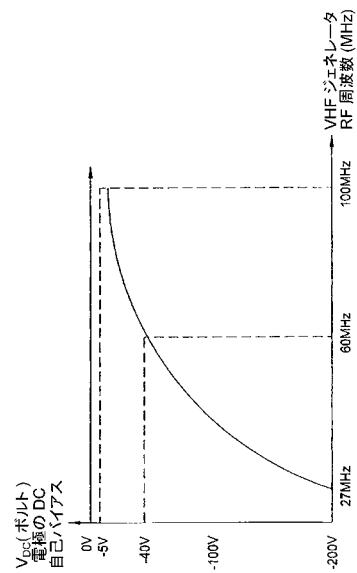

[0080] プロセスチャンバ 501 の動作中、VHF ソースアセンブリ 595 は、ターゲット 571 が形成される物質内の原子が基板 502 の表面上に堆積され得るようにターゲット 571 にバイアスをかけるために用いられる。一実施形態において、VHF ソースアセンブリ 595 内の RF ソース 524 は、約 1 ~ 約 200 MHz の RF 周波数で約 0.01 ~ 約 5 キロワット (kW) の電力でターゲットアセンブリ 573 を通して処理領域 522 に電力を分配するように適合される。一実施形態において、プラズマによって生成されたイオンがターゲット 571 の表面から物質をスパッタさせるプラズマシース全体の電圧低下のために、VHF ソースアセンブリ 595 を用いて、充分なエネルギーを供給する容量結合ターゲット 571 上に自己バイアスを生成させる。VHF ソースを用いてバイアスがかけられる容量結合電極、又はターゲットは、通常は、アノードとカソード（例えば、ターゲット 571）の表面積の差のために、自己バイアス電圧に達する。ターゲット 571 が処理中に達する自己バイアス電圧は、ターゲット 571 のスパッタ速度を最適化するよう調整され得る。図 4E は、自己バイアス電圧と周波数とのグラフを示す図である。グラフは、通常は、次第により高い周波数でバイアスがかけられたときの電極の自己バイアス電圧に対する周波数の影響を示している。周波数が増加するにつれて自己バイアス電圧の大きさが減少する傾向なので、VHF ソースアセンブリ 595 の周波数が増加することによってターゲットに衝突するイオンのエネルギーが減少され得る。例えば、27 MHz の周波数で RF 信号を用いてバイアスがかけられるターゲットは、アルゴンを用いて 50 ミリトルの圧力と 300 W の RF 電力でわずかに約 10 V の電圧を持つ。他の例において、ターゲット上の DC バイアスは、約 400 W の一定の RF 電力を用いて約 60 MHz ~ 約 100 MHz の RF 周波数を変動させることによって約 -50 V ~ 約 -20 V に変動させ得る。

#### 【0058】

[0081] VHF 範囲の RF 周波数でターゲット 571 にエネルギーを分配すると、ターゲット 571 に分配される周波数の変動と RF 電力の変動の関数としてターゲット上の DC バイアスの変動が減少するために、より低い RF 周波数で行われるプロセスに対してステップ 257 及び/又は 259 のプロセス結果が改善され得る。DC バイアスの変動を減少させることは、低電力スパッタリング動作を行う場合に重要であり得る。それ故、RF エネルギーと電力の周波数の制御することによって、例えば、所望の負荷サイクル（下記）でターゲット 571 に電力を分配することによって、ターゲットの DC バイアスが正確に且つ繰り返して行うことができる。DC バイアスの正確で精密な制御は、極端に薄いゲート誘電体層をドープするプロセスが正確に且つ繰り返し行われ得ることを確実にする。

#### 【0059】

[0082] 図 4D を参照すると、一例において、スパッタリングガスが主としてアルゴン (Ar) であり、ターゲットがランタン (La) から製造される場合には、ターゲット表面からランタン原子をスパッタするのに必要とされるエネルギーは、少なくとも 25.5 eV である。このことは、ランタン原子の一部がターゲット表面からスパッタされることを確実にするためにターゲット上に生じた自己バイアス電圧が約 25.5 eV のイオンエネルギーを生成するのに充分高いことが必要であることを意味する。それ故、ターゲット 571 に分配される周波数と電力（例えば、ワット）を制御することによって、スパッタ速度、ガス原子イオンエネルギー、スパッタ原子のイオンエネルギー、基板上に堆積される原子のエネルギーが制御され得る。また、プロセスの間、基板支持体 562 に対するバイアスは、スパッタされた原子が、ゲート誘電体層上に堆積するか又はゲート誘電体層内に注入するのにつれて持つエネルギーを制御するために調整され得る。

#### 【0060】

[0083] 一般に、スパッタプロセスは、約 1 sccm ~ 約 500 sccm のアルゴン流量を用いた 1 ミリトル ~ 100 ミリトルの範囲のチャンバ圧と約 20 ~ 約 800 の

10

20

30

40

50

ヒータ温度でプロセスチャンバ 501 内で行うことができる。望ましくは、基板温度は、約 200 ~ 300 である。RF ソース 254 の励起周波数は、ターゲット物質がプラズマに、また、基板表面にスパッタさせる正しい自己バイアス DC 電圧を得るために約 1 MHz ~ 約 200 MHz に調整され得る。好ましくは、RF ソース 254 の励起周波数は、約 27 MHz ~ 約 100 MHz の周波数、より好ましくは約 30 MHz ~ 約 60 MHz の周波数に調整され得る。一例において、ランタンターゲットの場合、60 MHz の周波数が所望のスパッタリングエネルギーと低エネルギー・プラズマを維持することを得るように選択され得る。一実施形態において、基板 502 の表面とターゲット 571 の表面との間の空間を調整して、基板表面上に堆積するスパッタされた原子の均一性とエネルギーを調整することは望ましいものである。一態様において、堆積プロセス中にターゲット 571 の表面に相対して基板 502 の空間を調整して、ゲート酸化物層のスパッタ物質の深さを及び/又は堆積均一性を調整することは望ましいものである。10

#### 【0061】

[0084] 図 4C は、プロセスチャンバ 501 の第二実施形態を示す図であり、図 4B に示した VHF ソースアセンブリ 595 が、プロセス中に異なる時間で異なるスパッタリング特性を与える異なる周波数及び/又は電力でプロセスチャンバ 501 の処理領域 522 にエネルギーを分配するようにそれぞれ適合される二つの RF ジェネレータ 524、525 を含有するデュアル VHF ソースアセンブリ 597 に置き換えられている。図 4C に示したプロセスチャンバ 501 は、通常は、ターゲットアセンブリ 573 に接続された RF ソース 524 と、第二 RF ソース 525 と、RF スイッチ 526 と、整合 524A を含有する。この構成において、デュアル VHF ソースアセンブリ 597 からのターゲットアセンブリ 573 に分配されるエネルギーは、RF スイッチ 526 の使用によって RF ソース 524 と第二 RF ソース 525 との間でスイッチが切り替えられ得る。スイッチ 526 の状態は、システムコントローラ 602 によって制御される。この実施形態は、最初の導入の間又は長いアイドルタイムの後にターゲット基板上に形成することができる酸化物を除去するために高速開始シージングを必要とするターゲット物質に有用なものである。より低い周波数ソース（例えば、約 27 MHz 以下）にスイッチを切り替える能力は、高自己バイアス DC 電圧がターゲット 571 上に形成することを可能にし、より高速なターゲットスパッタリング速度につながる。従って、開始処理後、高い周波数（約 60 MHz）ソースにスイッチを切り替えてスパッタリング速度を減少させ、且つスパッタされた原子イオンエネルギーを小さくすることによって、デュアル VHF ソースアッセンブリ 597 の出力を変化させることができるので、基板表面上のゲート誘電体層に対する潜在的損傷が減少する。一例において、RF ソース 524 は、約 27 MHz の周波数で 0 ~ 約 2000 ワットの電力での RF エネルギーを分配することができ、第二の RF ソース 525 は、約 40 ~ 約 200 MHz の周波数において 0 ~ 約 500 ワットの電力で RF エネルギーで分配することができる。2030

#### 【0062】

[0085] 一実施形態において、DC ソースアッセンブリ 592 は、任意により、ターゲットアセンブリ 573 に接続してプラズマ処理ステップで一つ以上の DC エネルギーパルスを分配してもよい。DC バイアスを、VHF ソースアセンブリ（例えば、符号 595 と 597）から分配された VHF 信号の上に重ね合わせてもよい。ターゲット 571 に印加される DC 電圧は、スパッタリングプロセスでターゲット 571 に衝突するイオン化されたガス原子のエネルギーをより直接制御するために使用し得る。40

#### 【0063】

[0086] 一実施形態において、上記のように、処理の間、RF、又は VHF、バイアスが、プラズマ内に存在するイオンを基板 502 の表面に引っ張るために基板支持体 562 の一部に印加され得るよう基板支持体 562 を RF ジェネレータ 523 に接続することができる。一実施形態において、基板支持部材 562A は、基板 502 のイオン衝撃損傷を最小にするためにプラズマプロセスの間、接地されるか、DC バイアスがかけられるか、又は電気的に浮遊している。50

## 【0064】

パルスプラズマ処理

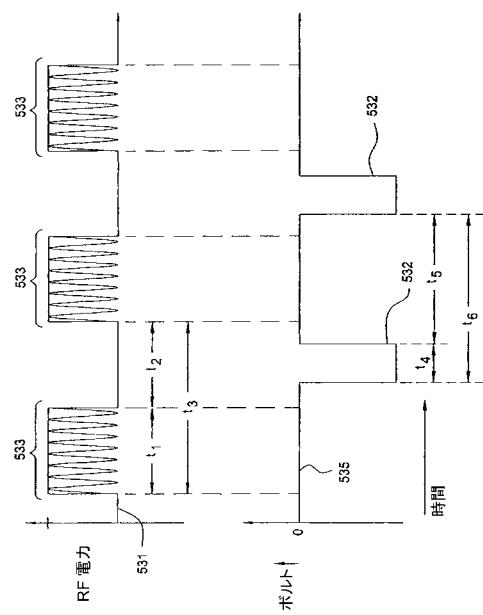

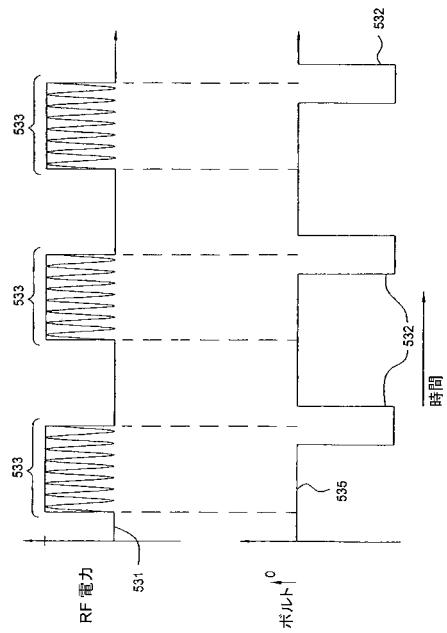

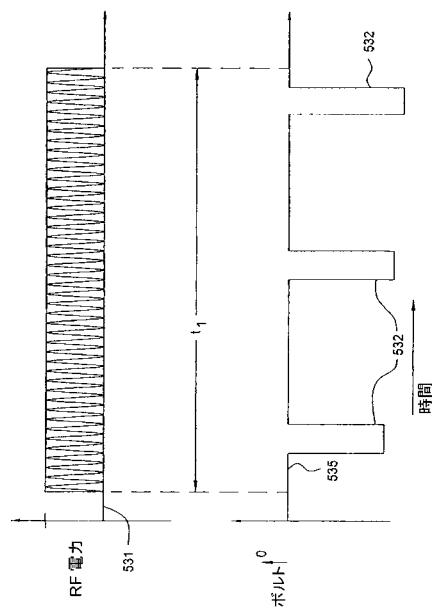

[0087] 図 5 A - 図 5 C は、上記ステップ 257 及び/又は 259 で図 4 A に示したターゲット 505、又は図 4 B に示したターゲット 571 から基板 502 の表面に、スパッタされた物質を堆積するために使用し得る種々のパルスプラズマプロセスの図表示である。図 パルスプラズマプロセスは、図 5 A - 図 5 C に示されるように、通常は、誘導 RF ソース アセンブリ 591 又は VHF ソースアセンブリ（即ち、デュアル VHF ソースアセンブリ 597 の VHF ソースアセンブリ 595）の使用による時間の関数として処理領域 522 に分配される一連の連続エネルギー パルスと、DC ソースアセンブリ 592 からのターゲットに分配される DC エネルギー パルスである。図 5 A は、誘導 RF ソースアセンブリ 591 又は VHF ソースアセンブリ 595 によって分配される RF エネルギー 531 と、DC ソースアセンブリ 592 から分配される DC 電圧 535 が、時間の関数としてプロットされるプロセスを示す図である。図 5 A は、時間の関数として、誘導 RF ソースアセンブリ 591 又は VHF ソースアセンブリ 595 によって分配される RF エネルギー 531 のプロットと、ターゲットに分配される DC 電圧 535 のプロットを示すので、DC と、RF、又は VHF（以後 RF / VHF）パルスが同期される一実施形態を示す図である。この実施形態において、RF エネルギー 531 と DC 電圧 535 のパルスは、同時に印加されないように同期されている。一般に、DC パルス 532 は、プラズマに存在する RF / VHF 励起イオンに瞬間的な引力を供給し、充分なエネルギーでターゲット 505 に向かって加速するイオンがターゲットからプラズマに物質をスパッタさせる。ターゲット表面を励起するスパッタ物質は、パルスされた RF / VHF パルス 533 で処理領域 522 に形成されるプラズマへ入り、その後、イオン化することができる。基板支持部材 562A が RF / VHF バイアスされているか、接地されているか、又は浮遊しているかによって、イオン化されたスパッタ原子は、基板表面近くに生成されたプラズマシースによるエネルギー設定で基板表面に分配され得る。ほとんどの場合、DC 電圧パルス（又は DC 電流パルス）が、所望のイオン密度とスパッタ速度が低エネルギー バイアスを用いたときに達成され得ることを確実にするために分配される場合、処理チャンバ内に充分なプラズマがあるよう R / VHF パルス 533 の終わりを同期することが望ましい。

## 【0065】

[0088] 図 5 A の参照を続けると、通常は、特に誘導結合プラズマチャンバの設計において、ターゲットからの原子をスパッタするのに充分なエネルギーを持たない RF / VHF パルス 533 でイオンを生成することが望ましいので、スパッタ原子のエネルギーがターゲットへの DC バイアスの印加によってより容易に制御され得る。場合によっては、スパッタされたターゲット原子が促進され、基板が位置決めされるペデスタルに印加された低電位バイアスの使用による低エネルギーで基板表面に注入され得るようにイオン化するために RF / VHF パルスの使用が望ましいものである。一態様において、DC 電圧パルス（又は DC 電流パルス）のターゲットへの印加は、DC エネルギー印加のために、プラズマに生成されたイオンのエネルギーがプラズマエネルギーの正味の増加を減少させることによってより容易に制御されることを可能にするためにパルス RF / VHF オフサイクルと同期される。DC パルス電圧は、ドーピングプロセスのプラズマにターゲット物質をスパッタするためにアルゴンイオンに充分なエネルギーを供給する値で印加することができる。

## 【0066】

[0089] システムコントローラ 602 が、所望のプラズマ密度とスパッタ堆積速度とプラズマイオンエネルギーを達成するために RF / VHF パルス 533 と DC パルス 532 を負荷サイクルを同期するために使用し得ることは留意すべきである。図 5 A を参照すると、RF エネルギー 531 のパルスの全周期 ( $t_3$ ) で割った“オン”時間 ( $t_1$ ) である負荷サイクルは、所望の平均密度のプラズマが制御されること確実にするように最適化され得ることが留意される。また、DC 電圧 535 のパルスの全周期 ( $t_6$ ) で割った“オン”時間 ( $t_4$ ) である負荷サイクルは、所望の平均堆積速度が達成されることを確実に

するために最適化され得ることが留意される。

#### 【0067】

[0090]図4B-図4Cと図5A-図5Cを参照すると、一実施形態において、VHFソースアセンブリ595は、1Hz～50kHzのパルス周波数と0.1～99%の負荷サイクルでのパルス方式に設定される。この構成において、平均プラズマ密度とイオンエネルギーを低下させつつ、処理領域522に形成されたプラズマを生成し維持するためにパルスVHFソースが用いられる。システムコントローラ602は、負荷サイクルと、パルスの周波数と、RFエネルギーの規模（即ち、RF電力）と、RFエネルギーの周波数を調整して、プラズマイオンとスパッタされた物質のエネルギーを制御するために使用し得る。一実施形態において、基板表面に低エネルギー・スパッタ物質を分配するために、システムコントローラ602を用いて、約1%～約50%の負荷サイクルでコイル509（図4A）にRFエネルギーを分配する。或いは、一実施形態において、RFエネルギーを約1%～約50%の負荷サイクルでターゲット571（図4B）に分配することによって低エネルギー・スパッタ物質を基板の表面に分配する。ある場合には、プラズマ内のイオンに分配されるエネルギーを最小にするために、コイル509（図4A）又はターゲット（図4B）に分配される負荷サイクルを約1%～約10%に保つことが望ましい。

10

#### 【0068】

[0091]図5Bは、RFソースアセンブリ591又はVHFソースアセンブリ（即ち、デュアルVHFソースアセンブリ597のVHFソースアセンブリ595）から分配されるパルスRFエネルギー531の少なくとも一部の間にDCパルス532が分配される、パルスプラズマプロセスの他の実施形態を示す図である。更に他の実施形態において、図5Cに示されるように、RFエネルギー531は、時間 $t_1$ の周期の一定のレベルに維持され、パルスDC電圧535は、RFエネルギーが“オン”の間、ターゲット505に分配される。分配された信号の間の可能ないかなる干渉も減少させるためにDCパルス532中のRFエネルギー531の大きさを減少させることが望ましいことであることは留意すべきである。一実施形態において、プロセスのRF/VHFプラズマ生成及び/又はパルスDCスパッタリング段階の種々の部分でその上に位置決めされた基板にイオンを引き付けるバイアスを生成するために用いられるRFジェネレータ523（図4A）を用いて基板支持体562にバイアスをかけることは望ましいことである。

20

#### 【0069】

[0092]他の実施形態において、プラズマ中に生成されたイオンがターゲット物質をスパッタするほど充分なエネルギーを持たないようにRF/VHFエネルギーをパルスすることは望ましい。この場合、ターゲットに印加されるDCバイアスは、ターゲット物質のスパッタリングを促進するために使用し得る。

30

#### 【0070】

[0093]一実施形態において、パルスRF/VHF信号を基板支持体562に加えて、基板表面を通じてプラズマを生成し維持する。それ故、一実施形態において、同期されたDCパルスはターゲット571に分配され、同期されたVHFパルスは基板支持体562に分配されてゲート誘電体にドープするプラズマにターゲット物質をスパッタする。

40

#### 【0071】

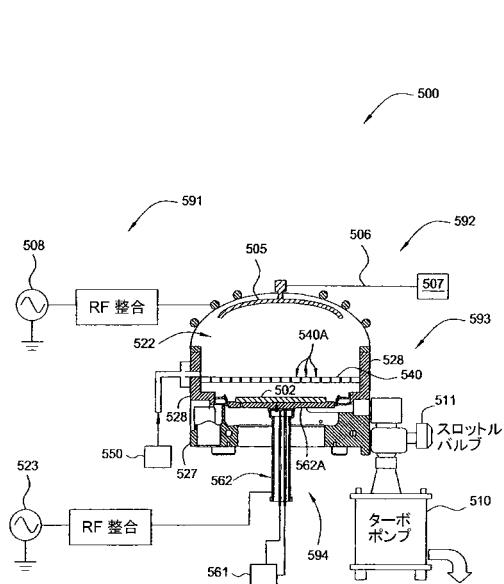

##### 接地されたコリメータの設計

[0094]図4Fは、ゲート誘電体層の金属プラズマ処理、即ち、ドープされたゲート誘電体層を形成する低エネルギー・スパッタリングプロセスに用いることができる処理チャンバー500の他の実施形態の概略断面図を示す図である。この実施形態において、接地されたコリメータ540は、帯電した金属イオンを捕獲するために基板502とターゲット505の間に取り付けられる。接地されたコリメータ540の追加は、基板502へ達するよう主として中性のスパッタされた原子を促進させ、基板表面上の金属薄層、潜在的には単一の单層を形成する。コリメータは、通常は、中性原子と場合によりいくつかのイオンがターゲット近くの処理領域から基板表面に通過させることを可能にする接地されたプレート全体に分配される複数の穴540Aを含有する接地されたプレート又はワイヤメッシュ50

ユである。中性原子のエネルギーが、通常は、ターゲット表面から原子をスパッタするのに必要とされる一部のエネルギーであり、中性原子がプラズマ電位に影響されないので、この方法によるゲート誘電体の表面上のこのような層を堆積させると、通常は、非常に小さいイオン衝撃損傷が生じる。その後、この金属層を、続いて形成された酸化物膜に組み込むことができるので、金属又は窒素イオンの注入と付随する問題、例えば、シリコン損傷や基板の下に横たわるシリコン層への金属の浸透を含まず高誘電率又は“高k”誘電体層が生成される。当業者は、図4Bと図4Cに示されるプロセスチャンバ501が、基板表面を衝突してゲート誘電体層の損傷を減少させる前に、プラズマ中大きなパーセントの帯電パーティクルを捕捉する同じ機能を達成するために、ターゲット571と基板502の表面の間に接地されたコリメータ540を含有するように構成され得ることを理解する。

10

### 【0072】

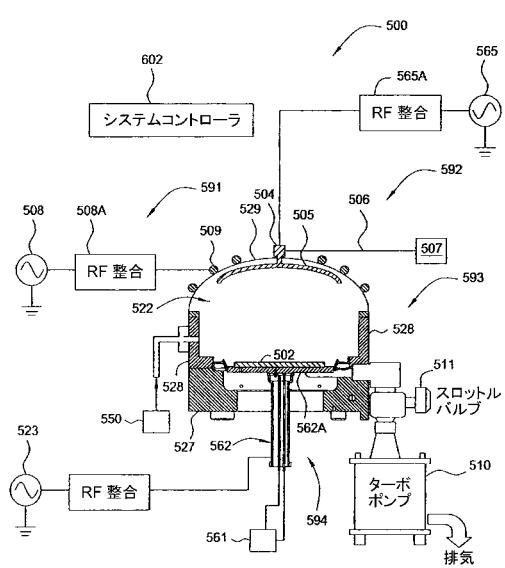

#### 別のプロセスチャンバの設計

[0095]図4Gは、ゲート誘電体層の金属プラズマ処理、即ち、ドープされたゲート誘電体層を形成するための低エネルギー・スパッタリングプロセスに用いることができる処理チャンバ500の他の実施形態の概略断面図を示す図である。処理チャンバ500の一実施形態において、誘導ソースアセンブリ591の出力がターゲット505に接続されるのでプラズマはコイル509と容量結合ターゲット505の使用によって処理領域522に生成することができる。一実施形態において、ターゲット505は、電力がRF整合508Aを通じてジェネレータ508によって分配される場合に共鳴を達成するサイズであるコイル508Bを通じてRF整合508Aの出力に結合する。図4Aを参照すると、ターゲット505のRFバイアスを加えると、ターゲット505に分配されるRF周波数とRF電力がDCバイアス、従ってターゲット505に衝突するイオンエネルギーを制御させつつ、コイル509がプラズマを生成し形成することが可能になる。また、所望の負荷サイクルでパルスされ得る誘導結合プラズマ生成要素と容量結合プラズマ生成要素の使用により、ターゲット（即ち、自己バイアス）に印加されるDCバイアス、スパッタ速度、スパッタイオンエネルギーがより容易に制御せ得ることが可能になる。チャンバ圧、RF周波数、RF電力、負荷サイクル、基板支持体562に印加されるバイアス及び/又は処理時間のより注意深い制御によって、誘電体層におけるスパッタされた物質の量とスパッタされた物質の濃度と深さを制御することができる。単一のRFジェネレータ508とRF整合508Aの使用は、チャンバコストとシステムの複雑性を減少させる。一実施形態において、DCパルスがRFジェネレータ508によって分配されるRFパルスの間或いはRFパルス間においてターゲット505に分配され得るようにDCソースアセンブリ593がターゲット505に結合する。

20

### 【0073】

[0096]図4Hに示した、他の実施形態において、RFエネルギーをターゲット505に供給する別々のRFジェネレータ565とRF整合565Aを持つことは望ましいが、コイル509はRFジェネレータ508とRF整合508Aの使用によって別々にRFバイアスがかけられる。この構成において、新しいRF整合565AとRFジェネレータ565は、システムコントローラ602の使用によって誘導結合ソースアセンブリ591要素から別々に制御され得る。一態様において、DCソースアセンブリ592は、DCパルスが誘導結合RFソースアセンブリ591及び/又はRFジェネレータによって分配される或いはRFパルス間においてターゲット505に分配され得るように、ターゲット505に結合される。

30

### 【0074】

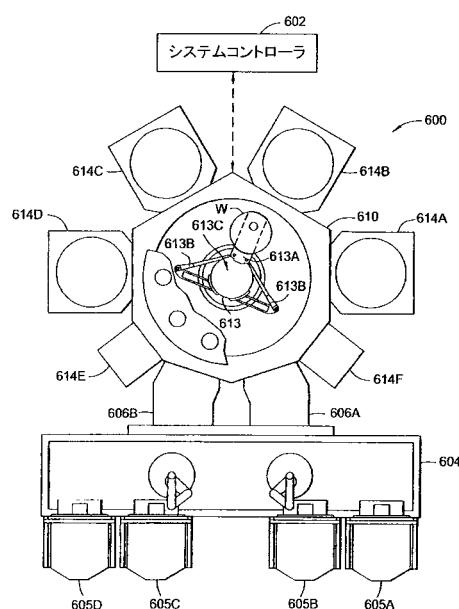

#### プラズマプロセスシステム

[0097]上記図4A-図4C、及び図4Fのような一つ以上のプラズマ処理チャンバは、図7に示した統合処理システム600のようなマルチチャンバ、マルチプロセス基板処理プラットフォームに有益に統合され得る。本発明から利益を得るために適合させができる統合処理システムの例は、1999年3月16日出願の共同譲渡された米国特許第5,882,165号；1993年2月16日出願の米国特許第6,440,261号；20

40

50

02年8月27日出願の米国特許第6,440,261号に記載され、これらの開示内容は本明細書に全体で援用されている。統合処理システム600には、ファクトリインターフェース604、ロードポート605A-D、システムコントローラ602、真空ロードロック606A、608B、搬送チャンバ610、複数の基板処理チャンバ614A-614Fが含まれるのがよい。基板処理チャンバ614A-Fの一つ以上は、上記図2-5と共に本明細書に記載されるプラズマ処理を行うために用いられる処理チャンバ500及び/又は一つ以上のプロセスチャンバ501のようなプラズマ処理チャンバとして構成されるのがよい。他の実施形態において、統合処理システム600には、六つを超えるプロセスチャンバが含まれるのがよい。

## 【0075】

10

[0098]本発明の様態によれば、統合処理システム600は、通常は、複数のチャンバとロボットを備え、好ましくは、統合処理システム600において行われる種々の処理法と順序を制御し行うようにプログラムされたシステムコントローラ602を備え付けている。システムコントローラ602は、通常は、システム全体の制御と自動化を容易にするよう設計され、典型的には、中央処理装置(CPU)(図示せず)、メモリ(図示せず)、支援回路(又はI/O)(図示せず)が含まれるのがよい。CPUは、種々のシステム機能、チャンバプロセスとサポートハードウェア(例えば、デテクタ、ロボット、モータ、ガスソースハードウェア)を制御するための産業の設定に用いられるとともにシステムとチャンバプロセス(例えば、チャンバ温度、プロセス順序の処理能力、チャンバ処理時間、I/O信号等)をモニタするコンピュータプロセッサの任意の形式の一つであるのがよい。ロボット613は、ロードロックチャンバ606A又は606Bから614A-Fの位置に取り付けられた種々のプロセスチャンバの一つに基板を搬送する搬送チャンバ610内の中央に配置される。ロボット613は、通常は、ロボット駆動アセンブリ613Cに取り付けられるブレードアセンブリ613A、アームアセンブリ613Bを含有する。ロボット613は、システムコントローラ602から送られたコマンドの使用によって種々の処理チャンバに基板“W”を搬送するように適合される。本発明から利益を得るよう適合されるのがよいロボットアセンブリは、1994年8月30日出願の“Two-axis magnetically coupled robot”と称する共同譲渡された米国特許第5,469,035号；1994年4月11出願の“Robot Assembly”と称する米国特許第5,447,409号；2000年4月14日出願の“Robot For Handling Semiconductor Substrates”と称する第6,379,095号に記載され、これらの開示内容は本明細書に全体で援用されている。複数のスリットバルブ(図示せず)は、本明細書に記載されたプロセス順序の間、各チャンバが真空プロセスを行うために別々に排気されてもよいように、搬送チャンバ610からプロセスチャンバ614A-614Fのそれぞれを選択的に分離するように用いることができる。

20

## 【0076】

30

[0099]プラズマチャンバを統合処理システム600に組み込む重要な利点は、連続プロセスステップが空気にさらされずに基板上で行うことができることがある。これにより、図2-図5と共に上記の基板の表面上にスパッタされた原子を堆積させるようなプロセスが新たに堆積された極端に薄い金属層を酸化させずに行わせることが可能になる。安定化アニールを行う前に新たに堆積された物質の制御されない酸化もまた、アニールステップを行うことができるプロセスチャンバを含む統合処理システム600に複数のプロセスチャンバを組み込むことによって避けられる。統合システムは、非統合プロセスに存在しない周囲の酸素ソースに基板をさらさないことによって、高k誘電体層403、又は高k誘電体層404内に見られる物質(例えば、ドーパント物質)の酸化を防止する。従って、非統合プロセスに見られる汚染は、デバイス製造プロセスの再現性と平均デバイス性能へ直接影響し得る。

40

## 【0077】

[0100]統合処理システム600の一実施形態において、基板処理チャンバ614A又は

50

ファクトリインタフェース 604 に接続したチャンバは、プロセスステップ 252 で上述した R C A 洗浄を行うように構成されるのがよい。その後、自然酸化物層 401A (図 3 A を参照のこと) の除去の後、基板は、処理チャンバチャンバ 614B で行われる慣用の急速熱酸化 (R P O) プロセス、プラズマ増強型化学気相堆積 (P E C V D)、又は A L D を用いてその上に形成された誘電体層 (例えば、熱酸化物層 402、高 k 誘電体層 404) を持つことができる。基板処理チャンバ 614 と 614D は、プロセスステップ 257 と 259 を行うために上記処理チャンバ 500 及び/又はプロセスチャンバ 501 と同様のプラズマ処理チャンバとして構成される。それ故、プラズマプロセスは、真空中で基板の維持しつつ、処理チャンバ 614C と 714D 内の基板上で行うことができ、それにより、自然酸化物が基板上に配置された種々の層上で再成長することが防止される。このことは、さらされた層がランタンのような酸素に対する親和性が高い物質を含有する場合に特に重要なことである。一態様において、ステップ 260 は、基板処理チャンバ 614D 内で形成された金属表面を酸化するために基板処理チャンバ 614E 内の基板上で連続して行われる。代替的態様において、ステップ 262 は、基板処理チャンバ 614E 内に置かれた R T P チャンバ内で行うことができる。その後、A p p l i e d M a t e r i a l s から入手できる D P N プロセスのようなプラズマ窒化プロセス (ステップ 264) が、処理チャンバ 614F 内で行われるのがよい。他の態様において、ステップ 266 は、利用可能であれば、基板処理チャンバ 614E、又は基板処理チャンバ 614F に置かれた R T P チャンバ内で行うことができる。

## 【0078】

[0101]他の実施形態において、ステップ 252 (即ち、自然酸化物除去ステップ) とステップ 254 (即ち、熱酸化層堆積ステップ) は、異なるシステムで行うことができる。この実施形態において、基板処理チャンバ 614A と 614B は、プロセスステップ 257 と 259 を行うために処理チャンバ 500 及び/又はプロセスチャンバ 501 と同様のプラズマ処理チャンバとして構成されてもよい。一態様において、ステップ 260 は、基板処理チャンバ 614B 内で行った金属表面を酸化するために基板処理チャンバ 614C 内の基板上で連続して行われる。或いは、他の態様において、ステップ 262 は、R T P チャンバ 614 で行うことができる。A p p l i e d M a t e r i a l s から入手できる D P N プロセスのようなプラズマ窒化プロセス (ステップ 264) は、基板処理チャンバ 614D 内に位置決めされた処理チャンバ内で行うことができる。一態様において、ステップ 266 は、利用可能であれば、R T P チャンバ 614E 又は基板処理チャンバ 614C 内で行うことができる。一態様において、ステップ 260 が基板処理チャンバ 614C 内で完了した後、表面窒化ステップは、基板の真空から取り出されることなく空気にさらされることなく、基板処理チャンバ 614D 内で行うことができる。

## 【0079】

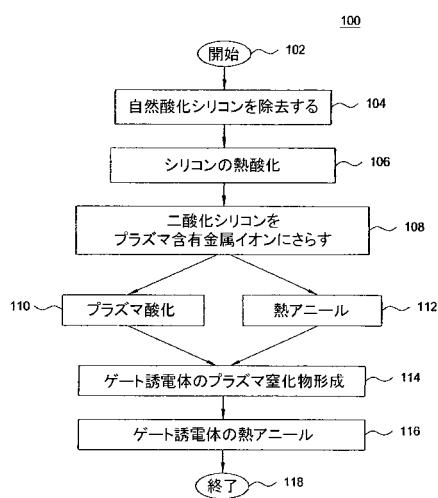

ゲート酸化物層を形成する別法

[0102]図 6A は、本発明の一実施形態に従って電界効果トランジスタのゲート誘電体の製造する方法 100 を示す図であるプロセスフローダイアグラムである。方法 100 には、例示的な C M O S 電界効果トランジスタのゲート構造の製造で基板上で行われるプロセスステップが含まれる。図 6A は、方法 100 の完全なプロセスを図でまとめたものを示す図である。方法 100 の少なくとも一部は、統合半導体基板プロセスシステム (即ち、クラスタツール) の処理リアクタを用いて行うことができる。一つのこのような処理システムは、カリフォルニア、サンタクララの A p p l i e d M a t e r i a l s 社から入手できる C E N T U R A (登録商標) 統合処理システムである。

## 【0080】

[0103]図 6B - 図 6G は、ゲート構造が図 6A の方法を用いて製造される一連の基板の概略断面図を示す図である。図 6B - 図 6G の断面図は、トランジスタのより大きいゲート構造 (図示せず) におけるゲート誘電体を製造するために行われた個々の処理ステップに関する。図 6B - 6G の像は、一定の比率で縮小されてなく、説明のために単純化されている。

## 【0081】

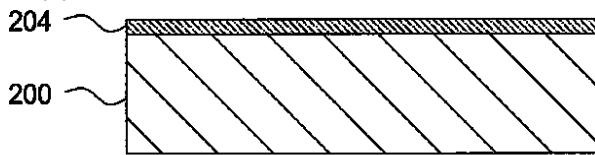

[0104]方法100は、ステップ102から開始し、ステップ118に進む。最初に図6Aと図6Bを参照すると、ステップ104で、シリコン(Si)基板200を準備し(例えば、200mmウエハ、300mmウエハ)、基板表面から自然酸化物(SiO<sub>2</sub>)層204を除去するために溶液にさらされる。一実施形態において、層204を、フッ化水素(HF)と脱イオン(DI)水(即ち、フッ化水素酸溶液)を含む洗浄液を用いて除去する。一実施形態において、洗浄液は、約20～約30の温度で維持される約0.1～約10質量%のHFを含有する水溶液である。他の実施形態において、洗浄液は、約25の温度に維持される約0.5wt%のHFを持つ。ステップ104で、基板200は、洗浄液内に浸漬され、脱イオン水ですすぐことができる。ステップ104は、プロセスの間、超音波エネルギーの分配を含むことができる単一基板処理チャンバ或いは複数の基板バッチタイププロセスチャンバで行うことができる。或いは、ステップ104は、統合処理システム600(図7)の単一基板湿式洗浄リアクタを用いて行うこともできる。他の実施形態において、層204は、RCA洗浄法を用いて除去することができる。ステップ104の完了時に、基板200は、真空ロードロック又は窒素(N<sub>2</sub>)パージ環境に置かれる。10

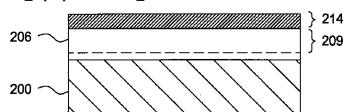

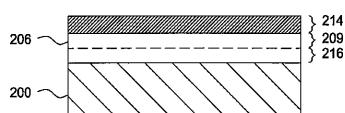

## 【0082】

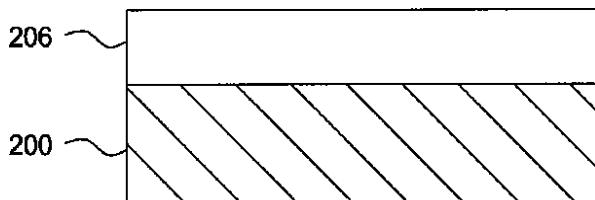

[0105]ステップ106において、熱酸化物(SiO<sub>2</sub>)層206は、基板200(図6C)上で成長する。一般に、熱酸化物層206は、約3オングストローム～約35オングストロームの厚さを持つものである。一実施形態において、熱酸化物層206の厚さは、約6オングストローム～約15オングストロームである。ステップ106で熱酸化物層を堆積させるプロセスは、図7に示した統合処理システム600上に位置決めされたRADIANCE(登録商標) RTPリアクタのようなRTPリアクタを用いて行うことができる。RADIANCE(登録商標) RTPリアクタは、カリフォルニア、サンタクララのApplied Materials社から入手できる。20

## 【0083】

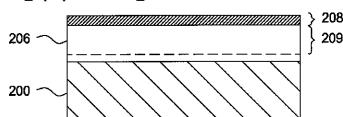

[0106]ステップ108において、熱酸化物層206は、金属イオン含有プラズマへさらされる。説明的に、ステップ108は、基板200上にシリコン金属酸化物、ケイ酸塩、酸窒化物膜の金属サブレイヤー層209を形成する(図6D)。一実施形態において、膜厚が約1オングストローム～約5オングストロームである金属層208は、ステップ108で熱酸化物層206の表面上に有利に形成することができる。一実施形態において、金属イオン含有プラズマは、不活性ガスとハフニウム又はランタンのような少なくとも一つの金属イオンを含有する。不活性ガスは、アルゴンだけでなく、ネオン(Ne)、ヘリウム(He)、クリプトン(Kr)、又はキセノン(Xe)のような一つ以上の所望による不活性ガスを含有する。一態様において、金属イオン含有プラズマは、窒素(N<sub>2</sub>)ガスを含有するのがよい。30

## 【0084】

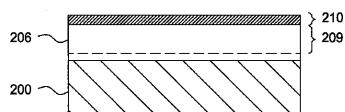

[0107]ステップ110で、熱酸化物層206を酸素含有プラズマにさらして、適用できる場合に金属サブレイヤー209と金属層208を酸化し、誘導体領域210に変換する(図6E)。他の実施形態において、プラズマは、窒素(N<sub>2</sub>)だけでなく、O<sub>2</sub>、NO、N<sub>2</sub>Oのような一つ以上の酸化ガスを含有するのがよい。プラズマは、アルゴン(Ar)、ネオン(Ne)、ヘリウム(He)、クリプトン(Kr)、又はキセノン(Xe)のような一つ以上の不活性ガスを含有してもよい。ステップ110は、例えば、統合処理システム600のプラズマ窒化(DPN)プラズマリアクタを用いて行うことができる(図7)。40

## 【0085】

[0108]ステップ112がステップ110の代わりに用いられる代替的実施形態において、基板200は、約800～約1100の温度でアニールされる。ステップ112は、統合処理システム600のRADIANCE(登録商標)又はRTPXE<sup>+</sup>リアクタのような適切な熱アニールチャンバ、又は単一基板炉或いはバッチ炉を用いて行うことができ50

る。熱酸化ステップ 112 は、誘電物質を含有絶する誘導体領域 210 の形成することになる。一態様において、誘導体領域 210 は、シリケート物質を含有するのがよい。一実施形態において、約 800 ~ 約 1100 の基板表面温度と、約 0.1 ~ 約 50 トールの反応チャンバ内圧力を維持しつつ、ステップ 112 のアニールプロセスは、酸素 ( $O_2$ ) ガスを約 2 ~ 約 5000 sccm の流量で、一酸化窒素 ( $NO$ ) を約 100 から約 500 0 sccm の間の流量で供給し、所望により窒素 ( $N_2$ ) と混合されてもよいガスを供給することによって行うことができる。アニールプロセスは、約 5 ~ 約 180 秒間行うことができる。一例において、チャンバを約 1000 の温度と約 0.1 トールの圧力で約 15 秒間維持しつつ、窒素酸化物 ( $NO$ ) を約 500 sccm の流量で供給する。

#### 【0086】

[0109]ステップ 114 で、基板 200 の表面を窒素プラズマにさらして形成された構造の最上面の窒素量を高めるために、窒化層 214 を形成する(図 6F)。窒素 ( $N_2$ ) を約 10 - 2000 sccm、約 20 - 5000 の基板ペデスタル温度、約 5 - 1000 ミリトルの反応チャンバの圧力で供給することによって DPN リアクタを用いてプロセスを形成することができる。高周波 (RF) プラズマは、約 3 - 5 kWまでの連続波 (CW) 又はパルスプラズマ電源を用いて、例えば、13.56 MHz で励起される。パルスの間、ピーク RF 電力、周波数、負荷サイクルは、典型的には、それぞれ約 10 - 3000 W、約 2 - 100 kHz、2 - 100 % の範囲で選択される。このプロセスは、約 1 - 180 秒間行われるのがよい。一実施形態において、 $N_2$  は、約 200 sccm で供給され、約 1000 W のピーク RF 電力は、約 10 kHz で負荷サイクルが約 5 % でパルスされ、約 25 の温度と約 100 - 80 ミリトルの圧力で 15 - 180 秒間誘導性プラズマソースに適用される。プラズマは、他のプラズマソースの中でも、準遠隔プラズマソース、誘導プラズマソース、又はラジアルラインスロットアンテナ (RLSA) ソースを用いて製造され得る。代替的実施形態において、CW のソース及び/又はパルスマイクロ波電力は、窒化層 214 を形成するために用いることができる。窒化層 214 は、誘電体領域 210 の最上面に形成されるのがよい(図 6E)。

#### 【0087】

[0110]ステップ 116 で、ゲート誘電体層 206、214、209 と基板 200 をアニールする。ステップ 116 は、層 206、214、209 の漏れ電流の減少を改善し、二酸化シリコン ( $SiO_2$ ) サブレイヤー 216 の下のチャネル領域内の荷電キャリヤの移動度を増加するだけでなく、ゲート誘電体全体の信頼性を改善する。ステップ 116 は、統合処理システム 300 の RADIANC E (登録商標) 又は RTPXE<sup>+</sup> リアクタのような適切な熱アニールチャンバ又は単一基板炉或いはバッチ炉を用いて行うことができる。熱酸化ステップ 116 により、二酸化シリコン ( $SiO_2$ ) サブレイヤー 216 が形成され、シリコン誘導体膜接合部上に形成する(図 6G)。ステップ 116 は、二酸化シリコン ( $SiO_2$ ) サブレイヤー 216 の下のチャネル領域における荷電キャリヤの移動度を増加するだけでなく、誘電体 / シリコン接合部の信頼性を改善する。

#### 【0088】

[0111]一実施形態において、約 800 - 1100 の基板表面温度と、約 0.1 - 50 トールの反応チャンバの圧力を維持しつつ、ステップ 116 のアニールプロセスは、約 2 - 5000 sccm の酸素 ( $O_2$ ) と約 100 - 5000 sccm の一酸化窒素 ( $NO$ ) の少なくとも一つを供給し、任意により窒素 ( $N_2$ ) と混合してもよいガスを供給することによって行うことができる。プロセスは、約 5 - 180 秒間行うことができる。一例において、チャンバを約 1000 の温度と約 0.1 トールの圧力で約 15 秒間維持しつつ、酸素 ( $O_2$ ) を約 500 sccm で供給する。

#### 【0089】

[0112]ステップ 116 の完了後、ステップ 118 で、方法 100 が終了する。集積回路の製造において、方法 100 は、漏れ電流の減少を改善した極端に薄いゲート誘電体を有

10

20

30

40

50

利に形成し、チャネル領域における電荷キャリヤの移動度を増大する。

【0090】

[0113]上記は本発明の実施形態に関するが、本発明の他の多くの実施形態は、本発明の基本的な範囲から逸脱せずに構成されてもよく、本発明の範囲は以下の特許請求の範囲によって決定される。

【図面の簡単な説明】

【0091】

【図1A】図1A（従来の技術）は、FETの概略断面図であり、本発明に従って製造され得る。

【図1B】図1B（従来の技術）は、二次イオン質量分析計に基づいて、従来の熱室化プロセスと従来のプラズマ室化プロセスに対する窒素濃度プロファイルを示すグラフである。

10

【図2A】図2Aは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法を示すプロセスフローダイアグラムである。

【図2B】図2Bは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法を示すプロセスフローダイアグラムである。

【図2C】図2Cは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法を示すプロセスフローダイアグラムである。

【図2D】図2Dは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法を示すプロセスフローダイアグラムである。

20

【図2E】図2Eは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法を示すプロセスフローダイアグラムである。

【図2F】図2Fは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法を示すプロセスフローダイアグラムである。

【図3A】図3Aは、ゲート構造が図2Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図3B】図3Bは、ゲート構造が図2Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図3C】図3Cは、ゲート構造が図2Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

30

【図3D】図3Dは、ゲート構造が図2Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図3E】図3Eは、ゲート構造が図2Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図3F】図3Fは、ゲート構造が図2Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図4A】図4Aは、本発明の他の実施形態のプラズマ処理チャンバを示す概略断面図である。

【図4B】図4Bは、本発明の他の実施形態のプラズマ処理チャンバを示す概略断面図である。

40

【図4C】図4Cは、本発明の他の実施形態のプラズマ処理チャンバを示す概略断面図である。

【図4D】図4Dは、本発明の一実施形態のハフニウムとランタンのターゲットの種々の特性を示す理論計算表である。

【図4E】図4Eは、本発明の一実施形態の容量結合プラズマ処理チャンバの自己バイアス電圧と周波数のグラフである。

【図4F】図4Fは、本発明の一実施形態のプラズマ処理チャンバの概略断面図を示す図である。

【図4G】図4Gは、本発明の一実施形態のプラズマ処理チャンバの概略断面図を示す図である。

50

【図4H】図4Hは、本発明の一実施形態のプラズマ処理チャンバの概略断面図を示す図である。

【図5A】図5Aは、本発明の他の実施形態に従ってターゲットに印加されたパルスRF/VHF励起エネルギーとパルスDC電圧のオフサイクルのタイミングを示す図である。

【図5B】図5Bは、本発明の他の実施形態に従ってターゲットに印加されたパルスRF/VHF励起エネルギーとパルスDC電圧のオフサイクルのタイミングを示す図である。

【図5C】図5Cは、本発明の他の実施形態に従ってターゲットに印加されたパルスDC電圧パルスとRF/VHF励起エネルギーのオフサイクルのタイミングを示す図である。

【図6A】図6Aは、本発明の一実施形態の電界効果トランジスタのゲート誘電体を製造するための方法100を示すプロセスフローダイアグラムである。

【図6B】図6Bは、ゲート構造が図6Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図6C】図6Cは、ゲート構造が図6Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図6D】図6Dは、ゲート構造が図6Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図6E】図6Eは、ゲート構造が図6Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図6F】図6Fは、ゲート構造が図6Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図6G】図6Gは、ゲート構造が図6Aの方法を用いて製造される基板の一連の概略断面図を示す図である。

【図7】図7は、本発明の一実施形態の統合処理システムを示す図である。

#### 【符号の説明】

#### 【0092】

10 ... 電界効果トランジスタ、 12 ... 基板、 13 ... ソース / ドレイン接合部 14 ... ゲート誘電体層、 16 ... ゲート電極、 18 ... 側壁スペーサ、 200 ... 基板、 204 ... 層、 206 ... 熱酸化物層、 208 ... 金属層、 209 ... 金属サブレイヤー、 210 ... 誘電体領域、 214 ... 窒化層、 401 ... 基板、 401A ... 自然酸化物層、 401B ... 洗浄表面、 402 ... 热酸化物層、 403 ... 高k誘電体層、 404 ... 高k誘電体層、 405 ... 終端領域、 407 ... 薄い金属層、 500 ... 処理チャンバ、 501 ... プロセスチャンバ、 502 ... 基板、 504 ... 電気的フィードスルー、 505 ... ターゲット、 506 ... 同軸ケーブル、 507 ... DC電源、 508 ... RFジェネレータ、 509 ... コイル、 510 ... 真空ポンプ、 511 ... スロットルバルブ、 522 ... 処理領域、 523 ... RFジェネレータ、 524 ... RFソース、 525 ... RFジェネレータ、 526 ... RFスチッチ、 527 ... チャンバベース、 528 ... チャンバ壁、 529 ... チャンバリッド、 531 ... RFエネルギー、 532 ... DCパルス、 533 ... RF/VHFパルス、 535 ... DC電圧、 540 ... コリメータ、 540A ... 穴、 550 ... ガス分配システム、 561 ... 温度コントローラ、 562 ... 基板支持体、 562A ... 基板支持部材、 571 ... ターゲット、 572 ... 電気絶縁体、 573 ... ターゲットアセンブリ、 591 ... 誘導RFソース、 592 ... DCソースアセンブリ、 593 ... プロセスチャンバアセンブリ、 594 ... 基板支持アセンブリ、 595 ... VHFソースアセンブリ、 596 ... プロセスチャンバアセンブリ、 597 ... VHFソースアセンブリ、 600 ... 統合処理システム、 602 ... システムコントローラ、 604 ... ファクトリインタフェース、 605A ... ロードポート、 606A ... ロードロックチャンバ、 606B ... ロードロックチャンバ、 610 ... 搬送チャンバ、 613 ... ロボット、 614A-614F ... 基板処理チャンバ、 571 ... ターゲット。

10

20

30

40

【図 1 A】

FIG. 1A

(PRIOR ART)

【図 1 B】

【図 2 A】

【図 2 B】

【図2C】

【図2D】

【図2E】

【図2F】

【図 3 A - F】

【図 4 A】

【図 4 B】

【図 4 C】

【図4D】

【 図 4 E 】

| HTタービネット |       | Laタービネット  |                            |

|----------|-------|-----------|----------------------------|

| 使用ガス     | 質量    | エネルギー質量係数 | スパッタリング<br>エネルギー輸送<br>質量係数 |

| Ar       | 40    | 0.999     | 42.3                       |

| Kr       | 83.8  | 0.871     | 26.12                      |

| Xe       | 131.3 | 0.977     | 25.65                      |

【図4F】

【図4G】

【図 4 H】

【図 5 A】

【図 5 B】

【図 5 C】

【図 6 A】

【図 6 B】

FIG. 6B

【図 6 C】

FIG. 6C

【図 6 D】

FIG. 6D

【図 6 E】

FIG. 6E

【図 6 F】

FIG. 6F

【図 6 G】

FIG. 6G

【図 7】

## フロントページの続き

|                         |                 |

|-------------------------|-----------------|

| (51)Int.Cl.             | F I             |

| H 01 L 21/318 (2006.01) | H 01 L 21/318 M |

|                         | H 01 L 21/318 A |

|                         | H 01 L 21/316 C |

(31)優先権主張番号 11/614,022

(32)優先日 平成18年12月20日(2006.12.20)

(33)優先権主張国 米国(US)

(31)優先権主張番号 11/614,027

(32)優先日 平成18年12月20日(2006.12.20)

(33)優先権主張国 米国(US)

## 早期審査対象出願

(72)発明者 チュア, タイ チェン

アメリカ合衆国, カリフォルニア州, クーパティーノ, カレ デ バルセロナ 19351

(72)発明者 ハン, スティーヴン

アメリカ合衆国, カリフォルニア州, サニーベール, マンゴ アヴェニュー 915

(72)発明者 リウ, パトリシア エム

アメリカ合衆国, カリフォルニア州, サラトガ, ベルグローヴ サークル 18813

(72)発明者 佐藤 達也

アメリカ合衆国, カリフォルニア州, クーパティーノ, アパートメント 7, パークウッド ドライヴ 10270

(72)発明者 ピーターソン, アレックス エム

アメリカ合衆国, カリフォルニア州, サン ホゼ, アパートメント 7207, コールマン ロード 1035

(72)発明者 トドロヴ, ヴァレンティン

アメリカ合衆国, カリフォルニア州, フレモント, ナンバー202, ウルコット コモン 3300

(72)発明者 ホランド, ジョン ピー

アメリカ合衆国, カリフォルニア州, サン ホゼ, カラヴァエラス アヴェニュー 1565

審査官 大塚 徹

(56)参考文献 特開2006-005370 (JP, A)

特開2002-164343 (JP, A)

特開2003-297814 (JP, A)

特開昭61-137370 (JP, A)

特開2002-314074 (JP, A)

特開平11-229132 (JP, A)

特開2003-068731 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/314-21/32