(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-165535

(P2006-165535A)

(43) 公開日 平成18年6月22日(2006.6.22)

| (51) Int.C1.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>HO1L 21/822</b> (2006.01) | HO1L 27/04 | L 4M104     |

| <b>HO1L 27/04</b> (2006.01)  | HO1L 21/90 | A 5B035     |

| <b>HO1L 21/768</b> (2006.01) | HO1L 29/78 | 613B 5F033  |

| <b>HO1L 29/786</b> (2006.01) | HO1L 29/78 | 627D 5F038  |

| <b>HO1L 21/336</b> (2006.01) | HO1L 27/10 | 431 5F083   |

審査請求 未請求 請求項の数 25 O L (全 61 頁) 最終頁に続く

|              |                              |          |                     |

|--------------|------------------------------|----------|---------------------|

| (21) 出願番号    | 特願2005-327968 (P2005-327968) | (71) 出願人 | 000153878           |

| (22) 出願日     | 平成17年11月11日 (2005.11.11)     |          | 株式会社半導体エネルギー研究所     |

| (31) 優先権主張番号 | 特願2004-328295 (P2004-328295) |          | 神奈川県厚木市長谷398番地      |

| (32) 優先日     | 平成16年11月11日 (2004.11.11)     | (72) 発明者 | 安部 寛子               |

| (33) 優先権主張国  | 日本国 (JP)                     |          | 神奈川県厚木市長谷398番地 株式会社 |

| (31) 優先権主張番号 | 特願2004-328298 (P2004-328298) |          | 半導体エネルギー研究所内        |

| (32) 優先日     | 平成16年11月11日 (2004.11.11)     | (72) 発明者 | 湯川 幹央               |

| (33) 優先権主張国  | 日本国 (JP)                     |          | 神奈川県厚木市長谷398番地 株式会社 |

|              |                              | (72) 発明者 | 半導体エネルギー研究所内        |

|              |                              | (72) 発明者 | 野村 亮二               |

|              |                              |          | 神奈川県厚木市長谷398番地 株式会社 |

|              |                              | (72) 発明者 | 半導体エネルギー研究所内        |

|              |                              | (72) 発明者 | 山崎 舜平               |

|              |                              |          | 神奈川県厚木市長谷398番地 株式会社 |

|              |                              |          | 半導体エネルギー研究所内        |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

絶縁層上に設けられたトランジスタと、

前記トランジスタのソース配線又はドレイン配線として機能する導電層と、

前記トランジスタに重畳する記憶素子と、

アンテナとして機能する導電層とを有し、

前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、

アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層に設けられていることを特徴とする半導体装置

。

**【請求項 2】**

絶縁層上に設けられたトランジスタと、

前記トランジスタに重畳する記憶素子と、

アンテナとして機能する導電層とを有し、

前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、

アンテナとして機能する前記導電層と、前記第1の導電層とは同じ層に設けられていることを特徴とする半導体装置。

**【請求項 3】**

絶縁層上に設けられたトランジスタと、

前記トランジスタに重畳する記憶素子と、

アンテナとして機能する導電層とを有し、

前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、

アンテナとして機能する前記導電層と、前記第2の導電層とは同じ層に設けられていることを特徴とする半導体装置。

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、前記記憶素子は、前記トランジスタの一部に重畳することを特徴とする半導体装置。

**【請求項 5】**

第1の素子形成層と、第2の素子形成層と、前記1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を含む接着層とを有し、

前記第1の素子形成層は、絶縁層上に設けられたトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記トランジスタ上に設けられたアンテナとして機能する導電層とを有し、

前記第2の素子形成層は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが積層された記憶素子を有し、

前記第1の導電層又は前記第2の導電層と、前記トランジスタのソース配線又はドレイン配線として機能する導電層とは、導電性粒子を介して接続されることを特徴とする半導体装置。

**【請求項 6】**

素子形成層と、アンテナとして機能する導電層が設けられた基板と、前記素子形成層及び前記基板を接着し、且つ導電性粒子を含む接着層とを有し、

前記素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、

前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層と、

前記第2のトランジスタに重畳し、且つ、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層された記憶素子とを有し、

アンテナとして機能する前記導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層とは、導電性粒子を介して接続されることを特徴とする半

10

20

30

40

50

導体装置。

【請求項 7】

第1の素子形成層と、第2の素子形成層と、前記1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を含む接着層とを有し、

前記第1の素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、

前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層と、前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層とを有し、

前記第2の素子形成層は、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層された記憶素子、並びにアンテナとして機能する導電層と有し、

10

アンテナとして機能する前記導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層とは、前記導電性粒子を介して接続し、

前記記憶素子の第1の導電層又は前記第2の導電層と、前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層とは、前記導電性粒子を介して接続されることを特徴とする半導体装置。

【請求項 8】

基板上に設けられたトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタ上に設けられたアンテナとして機能する導電層を有する第1の素子形成層と、

20

前記基板又は前記第1の素子形成層上において、接着層を介して設けられると共に、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子を有する第2の素子形成層とを有し、

前記記憶素子の第1の導電層又は前記第2の導電層と、前記トランジスタのソース配線又はドレイン配線として機能する導電層とは、前記導電性部材を介して接続されることを特徴とする半導体装置。

【請求項 9】

素子形成層と、アンテナとして機能する導電層が設けられた基板と、前記素子形成層及び前記基板を接着し、且つ導電性粒子を有する接着層とを有し、

前記素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、

30

前記第1及び第2のトランジスタを覆う層間絶縁層と、

前記層間絶縁層に設けられた開口部を介して前記第1のトランジスタのソース領域又はドレイン領域に接続し、且つ、前記絶縁層と前記層間絶縁層の各々に設けられた開口部を介して前記素子形成層の裏面に露出する前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層と、

前記第2のトランジスタと、前記第2のトランジスタに重畠し、且つ、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子と、を有し、

前記アンテナとして機能する導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層の露出部とは、前記接着層の前記導電性粒子を介して接続することを特徴とする半導体装置。

【請求項 10】

第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を有する接着層とを有し、

40

前記第1の素子形成層は、絶縁層上に設けられたトランジスタと、

前記トランジスタを覆う層間絶縁層と、

前記層間絶縁層に設けられた開口部を介して前記トランジスタのソースドレイン領域に接続し、且つ、前記絶縁層と前記層間絶縁層の各々に設けられた開口部を介して前記第1の素子形成層の裏面に露出する前記トランジスタのソース配線又はドレイン配線として機能する導電層と、

アンテナとして機能する導電層と、を有し、

前記第2の素子形成層は、第1の導電層、有機化合物層又は相変化層、及び第2の導電

50

層が積層される記憶素子を有し、

前記記憶素子の第1の導電層又は第2の導電層と、前記トランジスタのソース配線又はドレイン配線として機能する導電層の露出部とは、前記接着層の前記導電性粒子を介して電気的に接続することを特徴とする半導体装置。

【請求項 1 1】

第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を有する接着層とを有し、

前記第1の素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、

前記第1及び第2のトランジスタを覆う層間絶縁層と、

前記層間絶縁層に設けられた開口部を介して前記第1及び第2のトランジスタのソース領域又はドレイン領域に接続し、且つ、前記絶縁層と前記層間絶縁層の各々に設けられた開口部を介して前記第1の素子形成層の裏面に露出する第1及び第2のトランジスタのソース配線又はドレイン配線として機能する第1の導電層及び第2の導電層と、を有し、

前記第2の素子形成層は、アンテナとして機能する導電層と、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子とを有し、

前記記憶素子の第1の導電層又は第2の導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層の露出部とは、前記接着層の前記導電性粒子を介して電気的に接続し、

前記アンテナとして機能する導電層と前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層の露出部とは、前記接着層の前記導電性粒子を介して接続することを特徴とする半導体装置。

【請求項 1 2】

第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を有する第1の接着層と、アンテナとして機能する導電層を有する基板と、前記第2の素子形成層及び前記基板を接着し、且つ、導電性粒子を有する第2の接着層とを有し、

前記第1の素子形成層は、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子を有し、

前記第2の素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、

前記第1及び第2のトランジスタを覆う層間絶縁層と、

前記層間絶縁層に設けられた開口部を介して前記第1のトランジスタのソース領域又はドレイン領域に接続し、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層と、

前記層間絶縁層に設けられた開口部を介して前記第2のトランジスタのソース領域又はドレイン領域に接続し、且つ前記絶縁層と前記層間絶縁層の各々に設けられた開口部を介して前記第1の素子形成層の裏面に露出するトランジスタのソース配線又はドレイン配線として機能する第2の導電層と、を有し、

前記記憶素子の第1の導電層又は第2の導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層とは、前記第1の接着層の前記導電性粒子を介して電気的に接続し、

前記アンテナとして機能する導電層と前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層の露出部とは、前記接着層の前記導電性粒子を介して接続することを特徴とする半導体装置。

【請求項 1 3】

請求項1乃至請求項12のいずれか一項において、前記記憶素子に接続されるトランジスタ、第1のトランジスタ、又は第2のトランジスタは、薄膜トランジスタであることを特徴とする半導体装置。

【請求項 1 4】

請求項1乃至請求項13のいずれか一項において、前記記憶素子に接続されるトランジスタは、有機半導体トランジスタであることを特徴とする半導体装置。

10

20

30

40

50

**【請求項 15】**

請求項1乃至請求項14のいずれか一項において、前記絶縁層は、酸化珪素層であることを特徴とする半導体装置。

**【請求項 16】**

請求項1乃至請求項15のいずれか一項において、前記記憶素子は、光学的作用により電気抵抗値が変化することを特徴とする半導体装置。

**【請求項 17】**

請求項1乃至請求項15のいずれか一項において、前記記憶素子は、電気的作用により抵抗値が変化することを特徴とする半導体装置。

**【請求項 18】**

請求項14において、前記有機化合物層は、光酸発生剤がドーピングされた共役高分子材料からなることを特徴とする半導体装置。

**【請求項 19】**

請求項17において、前記有機化合物層は、電子輸送材料又はホール輸送材料からなることを特徴とする半導体装置。

**【請求項 20】**

請求項1乃至請求項15のいずれか一項において、前記相変化層は、結晶状態と非晶質状態の間で可逆的に変化する材料を有することを特徴とする半導体装置。

**【請求項 21】**

請求項20において、前記相変化層は、ゲルマニウム、テルル、アンチモン、硫黄、スズ、金、ガリウム、セレン、インジウム、タリウム、コバルト、又は銀から選択された複数を有することを特徴とする半導体装置。

**【請求項 22】**

請求項15において、前記相変化層は、第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料を有することを特徴とする半導体装置。

**【請求項 23】**

請求項22において、前記相変化層は、銀、亜鉛、銅、アルミニウム、ニッケル、インジウム、アンチモン、セレン、又はテルルから選択された複数を有する材料であることを特徴とする半導体装置。

**【請求項 24】**

請求項15において、前記相変化層は、非晶質状態から結晶状態にのみ変化する材料を有することを特徴とする半導体装置。

**【請求項 25】**

請求項24において、前記相変化層は、テルル、酸化テルル、アンチモン、セレン、又はビスマスから選択された複数を有する材料であることを特徴とする半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、データの送受信が可能な半導体装置及びその作製方法に関する。

**【背景技術】****【0002】**

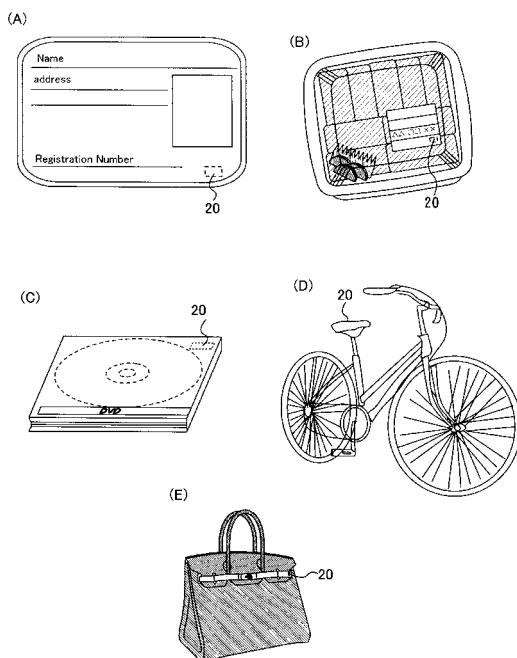

近年、絶縁表面上に複数の回路が集積され、様々な機能を有する半導体装置の開発が進められている。また、アンテナを設けることにより、無線によるデータの送受信が可能な半導体装置の開発が進められている。このような半導体装置は、無線チップ( I D タグ、 I C タグ、 I C チップ、 R F ( R a d i o F r e q u e n c y ) タグ、無線タグ、電子タグ、 R F I D ( R a d i o F r e q u e n c y I d e n t i f i c a t i o n ) タグともよばれる ) とよばれ、既に一部の市場で導入されている。

**【発明の開示】**

10

20

30

40

50

## 【発明が解決しようとする課題】

## 【0003】

基板上に集積する様々な回路として、データを記憶する記憶回路（単にメモリともよぶ）を設けると、より高機能で、付加価値が高い半導体装置を提供することができる。記憶回路としては、DRAM (Dynamic Random Access Memory)、SRAM (Static Random Access Memory)、FeRAM (Ferroelectric Random Access Memory)、マスクROM (Mask Read Only Memory)、EPROM (Electrically Programmable Read Only Memory)、EEPROM (Electrically Erasable and Programmable Read Only Memory)、フラッシュメモリなどが挙げられる。このうち、DRAM、SRAMは揮発性の記憶回路であり、電源をオフするとデータが消去されてしまうため、電源をオンする度にデータを書き込む必要がある。FeRAMは不揮発性の記憶回路であるが、強誘電体層を含む容量素子を用いているため、作製工程が増加してしまう。マスクROMは、簡単な構造であるが、製造工程でデータを書き込む必要があり、追記することはできない。EPROM、EEPROM、フラッシュメモリは、不揮発性の記憶回路ではあるが、2つのゲート電極を含む素子を用いているため、作製工程が増加してしまう。

## 【0004】

上記の実情を鑑み、本発明は、不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置及びその作製方法の提供を課題とする。

## 【課題を解決するための手段】

## 【0005】

本発明の一は、絶縁層上に設けられたトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記トランジスタに重畠する記憶素子と、アンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層に設けられていることを特徴とする半導体装置である。

## 【0006】

本発明の一は、絶縁層上に設けられたトランジスタと、前記トランジスタに重畠する記憶素子と、アンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と、前記第1の導電層とは同じ層に設けられていることを特徴とする半導体装置である。

## 【0007】

本発明の一は、絶縁層上に設けられたトランジスタと、前記トランジスタに重畠する記憶素子と、アンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と、前記第2の導電層とは同じ層に設けられていることを特徴とする半導体装置である。

## 【0008】

本発明の一は、第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を含む接着層とを有し、前記第1の素子形成層は、絶縁層上に設けられたトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記トランジスタ上に設けられたアンテナとして機能する導電層とを有し、前記第2の素子形成層は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが積層された記憶素子を有し、前記第1の導電層又は前記第2の導電層と、前記トランジスタのソース配線又はドレイン配線として機能する導電層とは、導電性粒子を介して接続されることを特徴とする半導体装置である。

10

20

30

40

50

## 【0009】

本発明の一は、素子形成層と、アンテナとして機能する導電層が設けられた基板と、前記素子形成層及び前記基板を接着し、且つ導電性粒子を含む接着層とを有し、前記素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層と、前記第2のトランジスタに重畠し、且つ、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層された記憶素子とを有し、アンテナとして機能する前記導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層とは、導電性粒子を介して接続されることを特徴とする半導体装置である。

## 【0010】

本発明の一は、第1の素子形成層と、第2の素子形成層と、前記1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を含む接着層とを有し、前記第1の素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層と、前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層とを有し、前記第2の素子形成層は、第1の導電層、有機化合物層又は相変化層、及び第2の導電層とが積層された記憶素子、並びにアンテナとして機能する導電層を有し、アンテナとして機能する前記導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層とは、前記導電性粒子を介して接続し、前記記憶素子の第1の導電層又は前記第2の導電層と、前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層とは、前記導電性粒子を介して接続されることを特徴とする半導体装置である。

## 【0011】

本発明の一は、基板上に設けられたトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタ上に設けられたアンテナとして機能する導電層を有する第1の素子形成層と、前記基板又は前記第1の素子形成層上において、接着層を介して設けられると共に、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子を有する第2の素子形成層とを有し、前記記憶素子の第1の導電層又は前記第2の導電層と、前記トランジスタのソース配線又はドレイン配線として機能する導電層とは、前記導電性部材を介して接続されることを特徴とする半導体装置である。

## 【0012】

本発明の一は、素子形成層と、アンテナとして機能する導電層が設けられた基板と、前記素子形成層及び前記基板を接着し、且つ導電性粒子を有する接着層とを有し、前記素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、前記第1及び第2のトランジスタを覆う層間絶縁層と、前記層間絶縁層に設けられた開口部を介して前記第1のトランジスタのソース領域又はドレイン領域に接続し、且つ、前記絶縁層と前記層間絶縁層の各々に設けられた開口部を介して前記素子形成層の裏面に露出する前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層と、前記第2のトランジスタと、前記第2のトランジスタに重畠し、且つ、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子と、を有し、前記アンテナとして機能する導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する導電層の露出部とは、前記接着層の前記導電性粒子を介して接続することを特徴とする半導体装置である。

## 【0013】

本発明の一は、第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を有する接着層とを有し、前記第1の素子形成層は、絶縁層上に設けられたトランジスタと、前記トランジスタを覆う層間絶縁層と、前記層間絶縁層に設けられた開口部を介して前記トランジスタのソース領域又はドレイン領域に接続し、且つ、前記絶縁層と前記層間絶縁層の設けられた開口部を介して前記第1の素子形成層の裏面に露出する前記トランジスタのソース配線又はドレイン配線とし

10

20

30

40

50

て機能する導電層と、アンテナとして機能する導電層と、を有し、前記第2の素子形成層は、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子を有し、前記記憶素子の第1の導電層又は第2の導電層と、前記トランジスタのソース配線又はドレイン配線として機能する導電層の露出部とは、前記接着層の前記導電性粒子を介して電気的に接続することを特徴とする半導体装置である。

## 【0014】

本発明の一は、第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を有する接着層とを有し、前記第1の素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、前記第1及び第2のトランジスタを覆う層間絶縁層と、前記層間絶縁層に設けられた開口部を介して前記第1及び第2のトランジスタのソース領域又はドレイン領域に接続し、且つ、前記絶縁層と前記層間絶縁層の設けられた開口部を介して前記第1の素子形成層の裏面に露出する第1及び第2のトランジスタのソース配線又はドレイン配線として機能する第1の導電層及び第2の導電層と、を有し、前記第2の素子形成層は、アンテナとして機能する導電層と、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子とを有し、前記記憶素子の第1の導電層又は第2の導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層の露出部とは、前記接着層の前記導電性粒子を介して電気的に接続し、前記アンテナとして機能する導電層と前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層の露出部とは、前記接着層の前記導電性粒子を介して接続することを特徴とする半導体装置である。

## 【0015】

本発明の一は、第1の素子形成層と、第2の素子形成層と、前記第1の素子形成層及び前記第2の素子形成層を接着し、且つ導電性粒子を有する第1の接着層と、アンテナとして機能する導電層を有する基板と、前記第2の素子形成層及び前記基板を接着し、且つ、導電性粒子を有する第2の接着層とを有し、前記第1の素子形成層は、第1の導電層、有機化合物層又は相変化層、及び第2の導電層が積層される記憶素子を有し、前記第2の素子形成層は、絶縁層上に設けられた第1及び第2のトランジスタと、前記第1及び第2のトランジスタを覆う層間絶縁層と、前記層間絶縁層に設けられた開口部を介して前記第1のトランジスタのソース領域又はドレイン領域に接続し、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層と、前記層間絶縁層に設けられた開口部を介して前記第2のトランジスタのソース領域又はドレイン領域に接続し、且つ前記絶縁層と前記層間絶縁層の設けられた開口部を介して前記第1の素子形成層の裏面に露出するトランジスタのソース配線又はドレイン配線として機能する第2の導電層と、を有し、前記記憶素子の第1の導電層又は第2の導電層と、前記第1のトランジスタのソース配線又はドレイン配線として機能する第1の導電層とは、前記第1の接着層の前記導電性粒子を介して電気的に接続し、前記アンテナとして機能する導電層と前記第2のトランジスタのソース配線又はドレイン配線として機能する第2の導電層の露出部とは、前記接着層の前記第2の導電性粒子を介して接続することを特徴とする半導体装置である。

## 【0016】

上記構成を有する本発明の半導体装置において、記憶素子には、トランジスタが接続されていることを特徴とする。また、記憶素子に接続されたトランジスタは、MOSトランジスタ、薄膜トランジスタ、又は有機半導体トランジスタであることを特徴とする。

## 【0017】

また、記憶素子は、上記トランジスタ、第1のトランジスタ、又は第2のトランジスタの一部又は全部に重畳することを特徴とする。

## 【0018】

また、絶縁層は、酸化珪素層であることを特徴とする。

## 【0019】

また、記憶素子において、有機化合物層が、光酸発生剤がドーピングされた共役高分子材料、電子輸送材料、又はホール輸送材料からなる場合、記憶素子は、光学的作用または電

10

20

30

40

50

気的作用により不可逆的に電気抵抗が変化し、記憶素子の電極間隔距離が変化することを特徴とする。電気抵抗を変化させる前の有機化合物層の膜厚は、5～60nm、好ましくは10～20nmである。

【0020】

また、記憶素子が含む前記相変化層は、結晶状態と非晶質状態の間で可逆的に変化する材料、第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料、又は非晶質状態から結晶状態にのみ変化する材料からなることを特徴とする。

【0021】

また、上記構成を有する本発明の半導体装置は、電源回路、クロック発生回路、データ復調/変調回路、制御回路、及びインターフェイス回路から選択された1つ又は複数を有することを特徴とする。

【発明の効果】

【0022】

本発明の半導体装置は、複数のトランジスタに重畳する記憶素子を有することを特徴とし、上記特徴により、小型で高集積化された半導体装置を提供することができる。

【0023】

また、本発明の半導体装置は、複数のトランジスタを有する素子形成層上に、記憶素子を有する基板又はアンテナとして機能する導電層を有する基板を貼り合わせる構成を有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる。

【0024】

また、本発明は、一対の導電層間に有機化合物層又は相変化層が挟まれた単純な構造の記憶素子を有することを特徴とし、上記特徴により、記憶素子の作製が簡単であるために安価な半導体装置及びその作製方法を提供することができる。また、高集積化が容易なため、大容量の記憶回路を有する半導体装置及びその作製方法を提供することができる。

【0025】

また、本発明の半導体装置が含む記憶回路において、一対の導電層間に有機化合物層が挟まれた記憶素子を有する場合、光学的作用又は電気的作用によりデータの書き込みを行うものであり、不揮発性であって、データの追記が可能であることを特徴とする。上記特徴により、書き換えによる偽造を防止することができ、新たなデータを追加して書き込むことができる。つまり、書き換え不可の記憶回路を有する半導体装置を提供することができる。

【0026】

また、本発明の半導体装置が含む記憶回路において、一対の導電層間に相変化層が挟まれた記憶素子を有する場合、記憶素子は不揮発性であるため、データを保持するための電池を内蔵する必要がなく、小型、薄型、軽量の半導体装置の提供を実現する。また、相変化層として不可逆的な材料を用いれば、データの書き換えを行うことはできない。このため、偽造を防止し、セキュリティを確保した半導体装置を提供することができる。

【0027】

従って、高機能化と高付加価値化を実現した半導体装置及びその作製方法を提供することができる。

【発明を実施するための最良の形態】

【0028】

本発明の実施の形態について図面を参照して説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0029】

(実施形態1)

本実施形態の半導体装置の構成について、図1、7、及び15を参照して説明する。図1

10

20

30

40

50

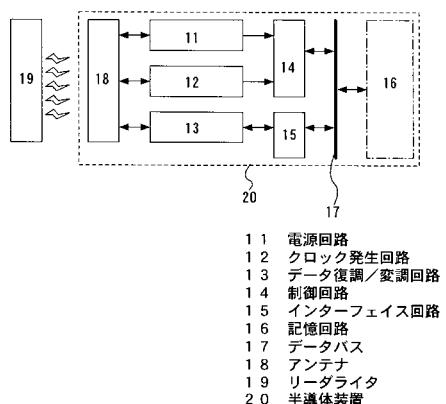

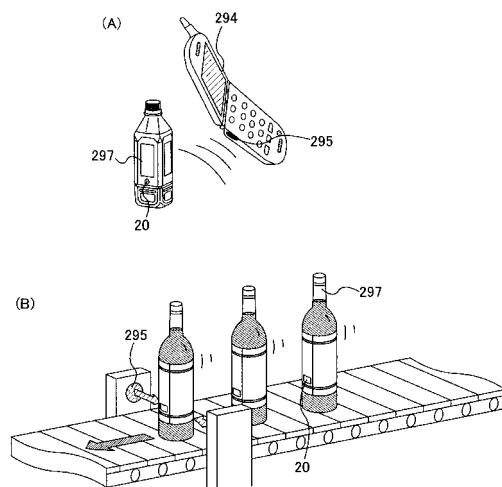

5に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の回路を制御する制御回路14、インターフェイス回路15、記憶回路16、データバス17、アンテナ(アンテナコイル)18を有する。

#### 【0030】

電源回路11は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種電源を生成する回路である。クロック発生回路12は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種クロック信号を生成する回路である。データ復調/変調回路13は、リーダライタ19と交信するデータを復調/変調する機能を有する。制御回路14は、記憶回路16を制御する機能を有する。アンテナ18は、電磁界或いは電波の送受信を行う機能を有する。リーダライタ19は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、半導体装置は上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウェアといった他の要素を追加した構成であってもよい。

#### 【0031】

記憶回路16は、一対の導電層間に有機化合物層又は相変化層が挟まれた記憶素子を有することを特徴とする。なお、記憶回路16は、一対の導電層間に有機化合物層又は相変化層が挟まれた記憶素子のみを有していてもよいし、他の構成の記憶回路を有していてもよい。他の構成の記憶回路とは、例えば、DRAM、SRAM、FeRAM、マスクROM、PROM、EPROM、EEPROM及びフラッシュメモリから選択される1つ又は複数に相当する。

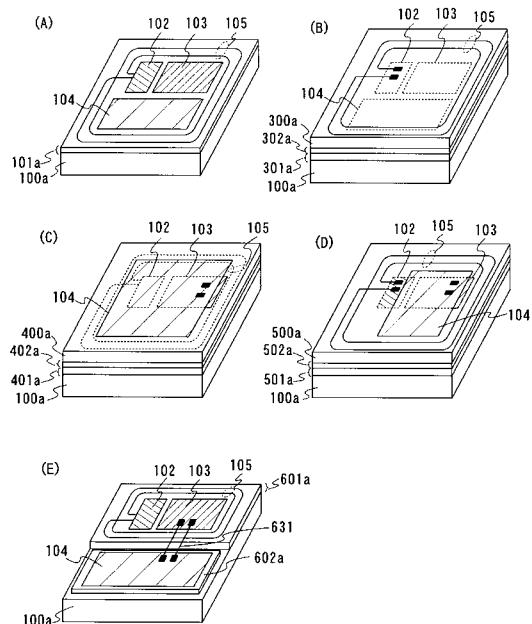

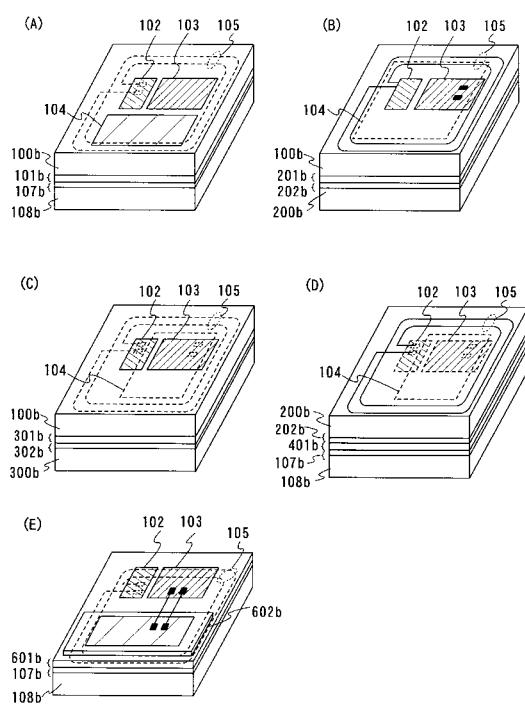

#### 【0032】

本実施形態の半導体装置20の斜視図について、図7(A)を用いて説明する。本実施形態の半導体装置は、図7(A)に示すように、基板上に複数の回路が集積された構成を有する。ここでは、基板100a上に複数のトランジスタを有する素子形成層101aが形成されており、複数のトランジスタを有する素子形成層101aは、代表的には複数のTFTを有する領域102、103と、記憶素子を有する領域104と、複数のTFTを有する領域102、103及び記憶素子を有する領域104の周囲に設けられたアンテナとして機能する導電層105とで構成されている。

#### 【0033】

なお、以下の実施形態では、複数のトランジスタを有する素子形成層は、TFTを有する領域102、103で構成されている例を示すが、TFTに限定されるものではなく、MOSトランジスタのように単結晶基板に形成されるトランジスタを用いて複数のトランジスタを有する素子形成層を形成することができる。この場合、基板100aは半導体単結晶基板となる。また、絶縁層と単結晶半導体層とが積層されたSOI(silicon on insulator)基板を用いることができる。さらには、有機半導体トランジスタを用いて複数のトランジスタを有する素子形成層を形成することができる。

#### 【0034】

複数のTFTを有する領域102、103は様々な回路を構成する。複数のTFTを有する領域102の代表例としては、電源回路、クロック発生回路、データ復調/変調回路等のアンテナが受信する電磁波を処理する通信回路が設けられている。また、複数のTFTを有する領域103の代表例としては、他の回路を制御する制御回路、インターフェイス回路等を有する。

#### 【0035】

また、アンテナとして機能する導電層105は、通信回路を構成する複数のTFTを含む領域102と接続する。

#### 【0036】

また、記憶素子を含む領域104は、データを記憶する記憶回路を構成し、記憶素子及び当該記憶素子を動作させる回路等を有する。記憶素子を含む領域104は、制御回路、インターフェイス回路等を構成する複数のTFTを有する領域103と接続される。

10

20

30

40

50

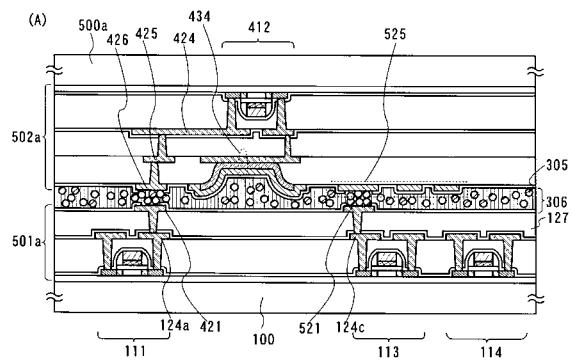

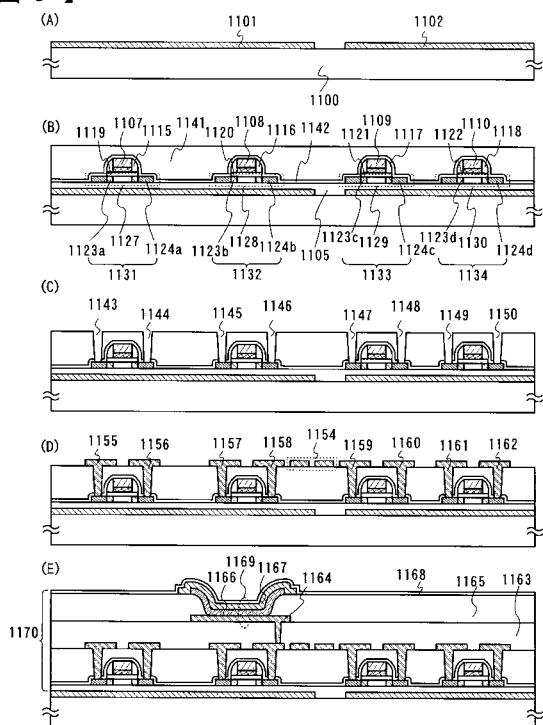

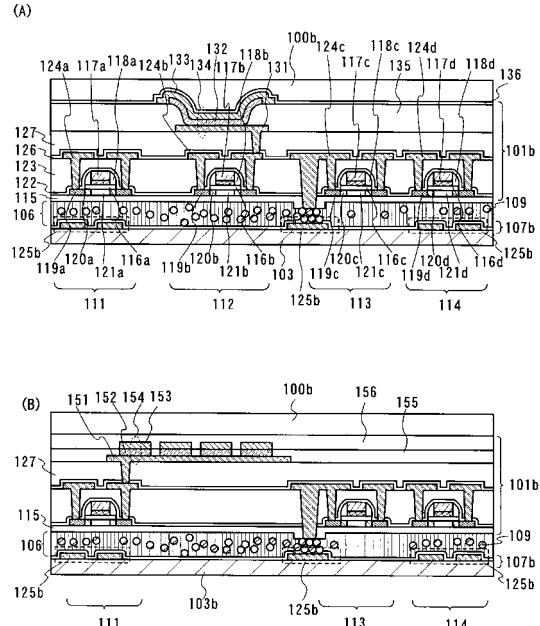

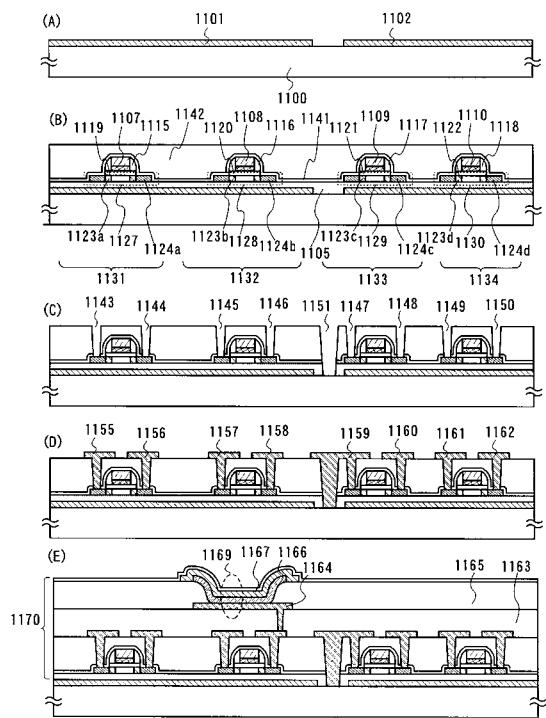

## 【0037】

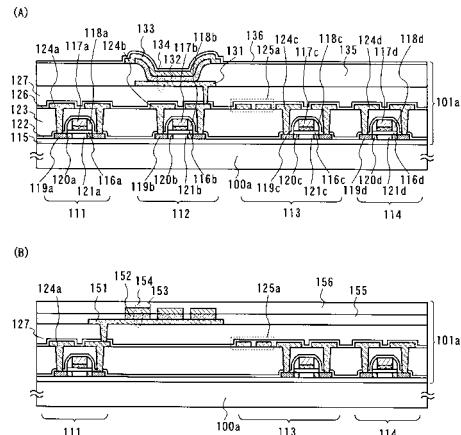

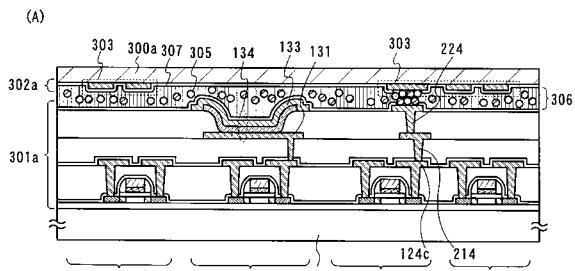

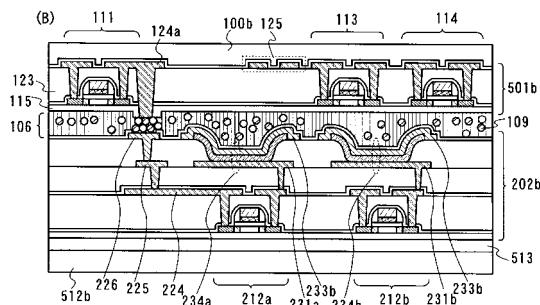

次に、図7(A)に示す構成を有する半導体装置の断面構造について、図1(A)を用いて説明する。基板100a上に複数のトランジスタを有する素子形成層101aが形成されている。ここでは、複数のトランジスタを有する素子形成層101aとして、記憶素子を動作させる回路を構成するTFT111(図7(A)の記憶素子を有する領域104の一部)、記憶素子のスイッチング用のTFT112(図7(A)の記憶素子を有する領域104の一部)、電源回路、クロック発生回路、データ復調/変調回路等のアンテナで受信した信号を処理する回路を構成するTFT113(図7(A)の複数のTFTを有する領域102の一部)、制御回路、インターフェイス等の回路を構成するTFT114(図7(A)の複数のTFTを有する領域103の一部)を示す。

10

## 【0038】

これらのTFTは、pチャネル型TFT、nチャネル型TFT等を適宜組み合わせて構成することが可能である。ここでは、それぞれの回路を構成するTFTをnチャネル型TFTで示す。

## 【0039】

TFT111～114は、基板100a上に絶縁層115を介して設けられている。TFTは、半導体領域、ゲート絶縁膜116a～116d、ゲート電極117a～117d、ゲート電極の側壁に設けられたサイドウォール118a～118dで構成される。半導体層は、ソース領域及びドレイン領域119a～119d、低濃度不純物領域120a～120d、チャネル形成領域121a～121dで構成される。また、低濃度不純物領域120a～120dは、サイドウォール118a～118dに覆われている。また、TFT111～114を覆う絶縁層122が形成されている。絶縁層122は、パッシベーション膜として機能し、外部からの不純物、代表的にはアルカリ金等の汚染物質をブロックする効果があり、TFTが汚染されることはなく、信頼性が向上したTFT111～114を提供することができる。なお、パッシベーション膜としては、窒化珪素膜、窒化酸化珪素膜又は酸化窒化珪素膜等が挙げられる。

20

## 【0040】

なお、TFT111～114の半導体層は、非晶質半導体、微結晶半導体、多結晶半導体、有機半導体等のいずれの半導体を活性層として用いてもよいが、良好な特性のトランジスタを得るために、金属元素を触媒として結晶化した半導体層、レーザ照射法により結晶化した半導体層を用いるとよい。また、プラズマCVD法により、SiH<sub>4</sub>/F<sub>2</sub>ガス、SiH<sub>4</sub>/H<sub>2</sub>ガス(Arガス)を用いて形成した半導体層や、前記半導体層にレーザ照射を行ったものを半導体層として用いるとよい。

30

## 【0041】

また、TFT111～114は、200度から600度の温度(好適には350度から550度)で結晶化した結晶質半導体層(低温ポリシリコン層)や、600度以上の温度で結晶化した結晶質半導体層(高温ポリシリコン層)を用いることができる。なお、基板上に高温ポリシリコン層を作成する場合は、ガラス基板では熱に脆弱な場合があるので、石英基板を使用するとよい。TFT111～114の半導体層(特にチャネル形成領域)には、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>～ $1 \times 10^{22}$  atoms/cm<sup>3</sup>の濃度、好適には $1 \times 10^{19}$  atoms/cm<sup>3</sup>～ $5 \times 10^{20}$  atoms/cm<sup>3</sup>の濃度で、水素又はハロゲン元素を添加するとよい。そうすると、欠陥が少なく、クラックが生じにくい活性層を得ることができる。

40

## 【0042】

また、TFT111～114の半導体層の厚さは、20nm～200nm、好ましくは40nm～170nm、さらに好ましくは45nm～55nm、さらに好ましくは50nmとするとよい。そうすると、折り曲げても、クラックが生じにくい素子形成層101aを提供することができる。

## 【0043】

また、TFT111～114の半導体層を構成する結晶は、キャリアの流れる方向(チ

50

ヤネル長方向)と平行に延びる結晶粒界を有するように形成するとよい。また、TFT111~114のS値(サブスレッシュホールド値)は0.35V/sec以下(好ましくは0.09~0.25V/sec)、移動度 $10\text{ cm}^2/\text{Vs}$ 以上の特性を有するとよい。このような半導体層は、連続発振レーザや、10MHz以上、好ましくは60~100MHzで動作するパルスレーザを半導体層に照射して形成することが可能である。

#### 【0044】

低濃度不純物領域やソース領域及びドレイン領域には、p型又はn型の導電型を付与する元素が添加されている。ここでは、ソース領域及びドレイン領域119a~119d及び低濃度不純物領域120a~120dには、n型の導電型を付与する不純物元素を、イオン注入法やイオンドープ法で自己整合的に添加して形成することができる。

10

#### 【0045】

なお、ここでは、TFT111~114が低濃度不純物領域120a~120dやサイドウォール118a~118dを有する構成を示すが、本発明はこの構成に制約されない。必要がなければ低濃度不純物領域やサイドウォールは設けなくてもよい。

#### 【0046】

また、半導体層として、公知の有機半導体材料を適宜用いることができる。代表例としては、骨格が共役二重結合から構成される電子共役系の高分子材料が望ましい。代表的には、ポリチオフェン、ポリ(3-アルキルチオフェン)、ポリチオフェン誘導体、ペンタセン等の可溶性の高分子材料を用いることができる。

20

#### 【0047】

その他にも、可溶性の前駆体を成膜した後で処理することにより半導体層を形成することができる。なお、このような前駆体を経由する有機半導体材料としては、ポリチエニレンビニレン、ポリ(2,5-チエニレンビニレン)、ポリアセチレン、ポリアセチレン誘導体、ポリアリレンビニレンなどがある。

#### 【0048】

前駆体を有機半導体に変換する際には、加熱処理だけではなく塩化水素ガスなどの反応触媒を添加することがなされる。また、これらの可溶性有機半導体材料を溶解させる代表的な溶媒としては、トルエン、キシレン、クロロベンゼン、ジクロロベンゼン、アニソール、クロロホルム、ジクロロメタン、ブチルラクトン、ブチルセルソルブ、シクロヘキサン、NMP(N-メチル-2-ピロリドン)、シクロヘキサン、2-ブタノン、ジオキサン、ジメチルホルムアミド(DMF)または、THF(テトラヒドロフラン)などを適用することができる。

30

#### 【0049】

また、TFT111~114と、パッシベーション膜として機能する絶縁層122を覆うように、絶縁層123が設けられており、これらの絶縁層123は、表面を平坦化するために設けられている。ソース配線又はドレイン配線として機能する導電層124a~124dは、ソース領域及びドレイン領域119a~119dに接し、絶縁層122、123に設けられたコンタクトホールを充填する。また、ソース配線又はドレイン配線として機能する導電層124a~124dと同時に形成された層で、アンテナとして機能する導電層125aが形成される。導電層125aは、TFT113のソース配線又はドレイン配線として機能する導電層124cに接続する。導電層124a~124d、125を覆うように、絶縁層126、127が設けられている。これらの絶縁層126、127は、表面を平坦化する目的と、TFT111~114及び導電層124a~124d、125を保護する目的で設けられている。

40

#### 【0050】

また、TFT111~114において、少なくともTFT113、114は、リングオシレータ(9段インバータ)レベルで1MHz以上、好適には10MHz以上(3~5Vにて)の特性を有する。又は、ゲートあたりの周波数特性を100kHz以上、好適には1MHz以上(3~5Vにて)を有する。

#### 【0051】

50

なお、後述するが、TFT111～114上に積層する記憶素子134は、その構造によつては、レーザ光を用いた光学的作用によりデータの書き込みを行う。その場合、レーザ光から、TFT111～114を保護するために、絶縁層127、及び後に形成される絶縁層135を遮光性がある絶縁性材料により形成する。遮光性がある絶縁性材料とは、例えば、公知の絶縁性材料に、カーボン粒子、金属粒子、顔料や着色料等を添加して攪拌した後、必要に応じて濾過を行つた材料、又は、カーボン粒子等が均一に混合されるように、界面活性剤や分散剤を添加した材料等である。このような絶縁性材料は、スピンドル法で形成するとよい。

#### 【0052】

また、絶縁層127上に記憶素子134が設けられている。記憶素子は、TFT112の一部又は全部に重畳することを特徴とする。当該構造により、狭い面積の半導体装置に記憶素子を高い密度で集積することが可能である。

#### 【0053】

絶縁層127上に、第1の導電層131、有機化合物層又は相変化層132、第2の導電層133が順に積層されており、この積層体が記憶素子134に相当する。隣接する有機化合物層又は相変化層132の間には、絶縁層135が設けられている。第1の導電層131は、TFT112のソース配線又はドレイン配線として機能する導電層124bと接続する。第2の導電層133上には、絶縁層136が設けられている。なお、TFT112は記憶素子のスイッチング用のTFTとして機能する。

#### 【0054】

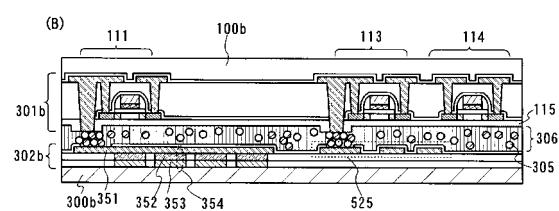

次に、図1(A)の各記憶素子にスイッチング用のTFTが設けられた記憶回路、即ちアクティブマトリクス型の記憶回路を有する半導体装置の代わりに、パッシブ型の記憶回路を有する半導体装置の断面構造について、図1(B)を用いて説明する。より詳しくは、図1(A)に示した半導体装置と比較すると、記憶素子134の構造及びそれに接続されるTFTが異なる半導体装置の断面構造について説明する。

#### 【0055】

絶縁層127上に、TFT111のソース配線又はドレイン配線として機能する導電層124aに接続するように、第1の導電層151が設けられ、第1の導電層151に接するように有機化合物層又は相変化層152が設けられ、有機化合物層又は相変化層152に接するように第2の導電層153が設けられている。第1の導電層151と、有機化合物層又は相変化層152と、第2の導電層153との積層体が記憶素子154に相当する。隣接する有機化合物層又は相変化層152の間には、絶縁層155が設けられている。記憶素子154上には、絶縁層156が設けられている。

#### 【0056】

なお、第1の導電層151は共通電極として機能し、第1の導電層151を用いて複数の記憶素子154が形成される。

#### 【0057】

図1(B)に示す記憶素子154は、各記憶素子154にスイッチング用のTFTが接続されておらず、記憶素子を動作させる回路を構成するTFT111に直接接続される。

#### 【0058】

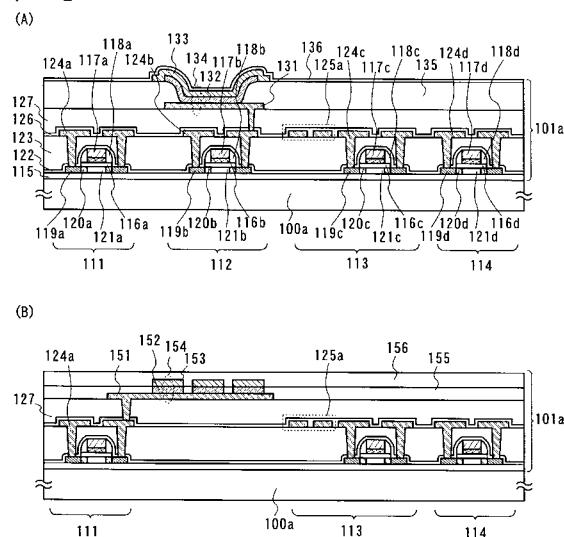

また、図1(A)及び(B)においては、基板上に複数のトランジスタを有する素子形成層101aが形成された半導体装置の断面図について説明しているが、これに限定されない。例えば、基板上に剥離層を設け、剥離層上に複数のトランジスタを有する素子形成層101aを形成した後、複数のトランジスタを有する素子形成層101aを剥離層から剥離し、図2(A)に示すように、基板200a上に接着層201を介して複数のトランジスタを有する素子形成層101aを貼り合わせても良い。なお剥離方法としては、(1)基板と複数のトランジスタを有する素子形成層の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化して、当該複数のトランジスタを有する素子形成層を物理的に剥離する方法、(2)基板と複数のトランジスタを有する素子形成層の間に水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッティングにより当該非晶質珪素膜を除去するこ

10

20

30

40

50

とで、当該複数のトランジスタを有する素子形成層を剥離する方法、(3)複数のトランジスタを有する素子形成層が形成された基板を機械的に削除する、又は溶液によるエッチングで除去する方法、(4)基板と複数のトランジスタを有する素子形成層の間に剥離層及び金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化し、剥離層の一部を溶液やCF<sub>3</sub>等のガスによるエッチングで除去した後、脆弱化された金属酸化膜において物理的に剥離する方法等を用いればよい。

#### 【0059】

また、基板200aとしては、可撓性があり、薄くて軽いプラスチック基板を用いることが好ましく、具体的には、PET(ポリエチレンテレフタレート)、PEN(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、ポリフタールアミド等からなる基板を用いることができる。また、ラミネートフィルム(ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなる)、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどを用いることができる。

#### 【0060】

ラミネートフィルムは、熱圧着により、被処理体と封止処理が行われるものであり、封止処理を行う際には、ラミネートフィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により接着する。基板200aの表面には接着層が設けられていてもよいし、接着層が設けられていてもよい。

#### 【0061】

接着層201は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層である。

#### 【0062】

上記のように、剥離した複数のトランジスタを有する素子形成層101aを、可撓性があり、薄くて軽いプラスチック基板に貼り合わせると、厚さが薄く、軽く、落下しても割れにくい半導体装置を提供することができる。また、曲面や異形の形状上に貼り合わせることが可能となり、多種多様の用途が実現する。例えば、薬の瓶のような曲面上に、本発明の半導体装置を密着して貼り合わせることができる。さらに、基板を再利用すれば、安価な半導体装置の提供を実現する。

#### 【0063】

また、図2(B)に示すように、記憶素子134の第1の導電層131と同時に形成された導電層で、アンテナとして機能する導電層215aを形成してもよい。このとき、アンテナとして機能する導電層215は、ソース配線又はドレイン配線として機能する導電層124cと接続する。

#### 【0064】

更には、図2(C)に示すように、記憶素子134の第2の導電層133と同時に形成された導電層で、アンテナとして機能する導電層225aを形成してもよい。このとき、アンテナとして機能する導電層225aは、導電層214を介してソース配線又はドレイン配線として機能する導電層124cと接続する。

#### 【0065】

なお、図2(A)～(C)に示す半導体装置は、図1(B)に示すような、スイッチング用のTFTが各記憶素子に設けられていない記憶素子を有するパッシブマトリクス型の記憶回路を有する半導体装置にも適応することが可能である。

#### 【0066】

本発明の半導体装置は、複数のTFTを有する素子形成層上に、記憶素子を積層した構成を有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる

。また、TFTのソース配線又はドレイン配線、記憶素子の導電層の何れかと同時に、アンテナとして機能する導電層を形成するため、工程数を削減することが可能であり、スループットを向上させることが可能である。

【0067】

上記構成を有する半導体装置において、記憶素子は、一対の導電層（第1の導電層と第2の導電層）間に有機化合物層又は相変化層が挟まれた単純な構造を有することを特徴とする。上記特徴により、作製が簡単であるために安価な半導体装置及びその作製方法を提供することができる。また、高集積化が容易なため、大容量の記憶回路を有する半導体装置及びその作製方法を提供することができる。

【0068】

また、本発明の半導体装置が含む記憶回路は、光学的作用又は電気的作用によりデータの書き込みを行うものであり、不揮発性であって、データの追記が可能であることを特徴とする。上記特徴により、書き換えによる偽造を防止することができ、新たなデータを追加して書き込むことができる。従って、高機能化と高付加価値化を実現した半導体装置及びその作製方法を提供することができる。

【0069】

（実施形態2）

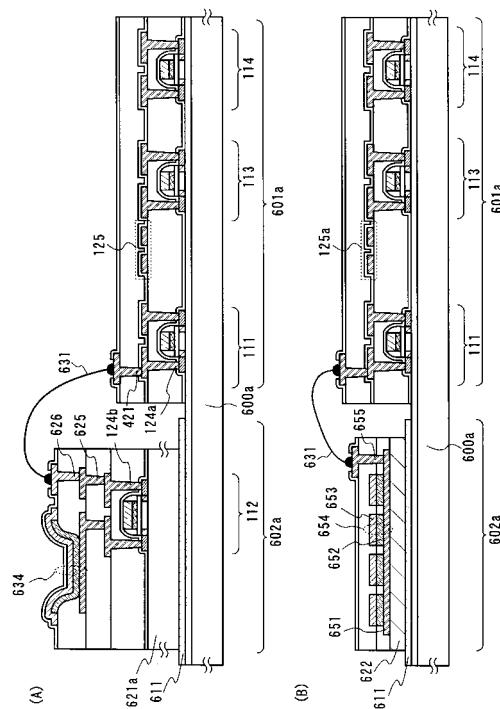

本実施形態では、上記実施形態とは異なる本発明の半導体装置の構成について、図3、7を参照して説明する。

【0070】

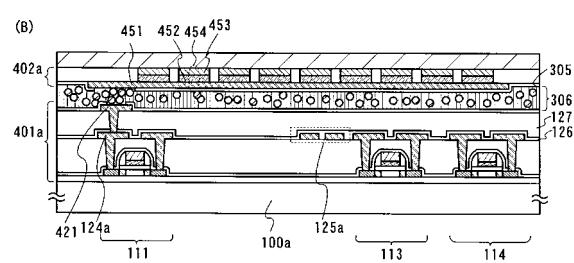

本実施形態の半導体装置は、図7（B）に示すように、第1の基板100a上に形成された複数のトランジスタを有する素子形成層301aと、第2の基板300a上に形成されたアンテナとして機能する導電層105を有する素子形成層302aとが、接着層で貼り合わせられた構成を有する。

【0071】

ここでは、複数のトランジスタを有する素子形成層301aは、代表的には複数のTFTを有する領域102、103と、記憶素子を有する領域104で構成される。また、素子形成層302aに形成されるアンテナとして機能する導電層105は、素子形成層301aに形成される通信回路を構成する複数のTFTを有する領域102と、図示しないが導電性粒子で接続されている。

【0072】

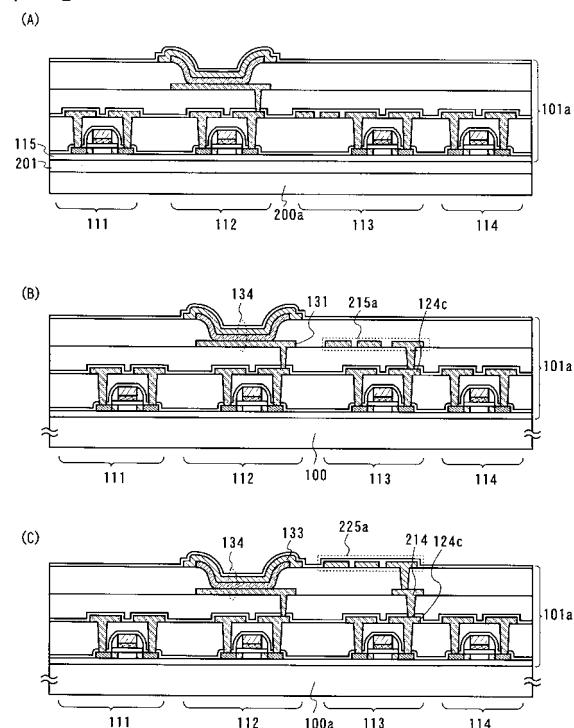

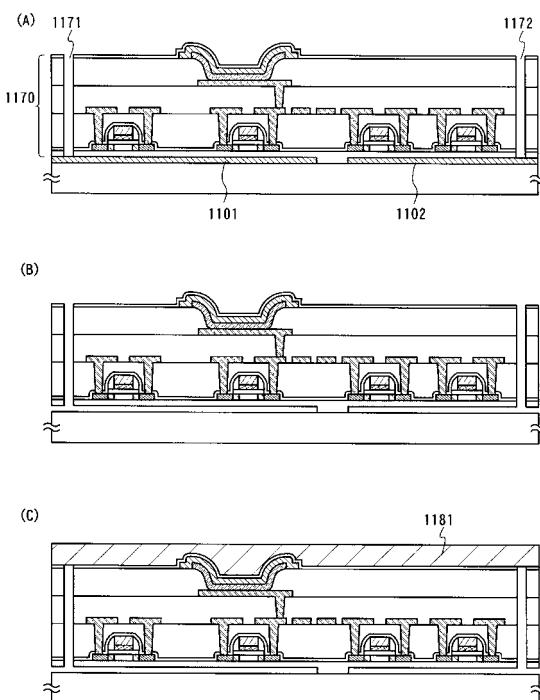

上記の図7（B）に示す構成を有する本発明の半導体装置の断面構造について、図3を用いて説明する。

【0073】

図3（A）に示すように、本実施形態の半導体装置は、第1の基板100a上に形成された複数のトランジスタと記憶素子を有する素子形成層301aと、第2の基板300a上に形成されたアンテナとして機能する導電層303aを有する素子形成層302aとが、接着層306で貼り合わせられた構成を有する。

【0074】

複数のTFTと記憶素子を有する素子形成層301aは、TFT111～114を有する。これらのTFT111～114の構造は上述した通りであり、また、記憶素子134は、図1（A）に示す記憶素子134と同じ構造を用いて形成することができ、TFT112の一部又は全部に重畠することにより、狭い面積の半導体装置に記憶素子を高い密度で集積することが可能である。

【0075】

基板100aに形成された、複数のTFT111～114及び記憶素子134を有する素子形成層301aと、基板300aに形成された導電層303を有する素子形成層302aは、導電性粒子305を含む接着層306により貼り合わせられている。また、TFT113のソース配線又はドレイン配線として機能する導電層124cは、導電層214を介して、導電層224に接続される。導電層224は接続端子として機能する。また、

10

20

30

40

50

導電層 214 は、記憶素子 134 の第 1 の導電層 131 と同時に形成される導電層である。また、導電層 224 は、記憶素子 134 の第 2 の導電層 133 と同時に形成される導電層である。さらに、接続端子として機能する導電層 224 と、アンテナとして機能する導電層 303 とは、導電性粒子 305 を介して電気的に接続されている。

## 【0076】

なお、アンテナとして機能する導電層 303 が設けられた第 2 の基板 300a は、基板 200a と同様の基板を用いることが可能である。また、基板 300a 及び導電層 303 表面に絶縁層 307 を形成しても良い。ただし、TFT113 の接続端子として機能する導電層 224 と接続する領域は、導電層 303 が露出されている。

## 【0077】

接着層 306 は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含み、導電性粒子 305 が分散されている。このような接着剤を異方性導電接着剤という。導電性粒子 305 は、金、銀、銅、パラジウム、又は白金から選ばれた一元素、若しくは複数の元素で形成される。また、これらの元素の多層構造を有する粒子でも良い。導電性粒子 305 は、直径が 1 ~ 100 nm、好ましくは 5 ~ 50 nm である場合、一つ又は複数の導電性粒子 305 と導電層 303、224 が接続する。この場合、一つ又は複数の導電性粒子 305 で導電層 303 と導電層 224 の間隔を保持する。

## 【0078】

また、図 37 に示すように、直径が 0.5 ~ 10 μm、好ましくは 1 ~ 5 μm の導電性粒子 308 が含まれる接着層 306 を用いても良い。この場合、導電層 303 と導電層 224 は、垂直方向に押しつぶされた形状の導電性粒子 309 で接続される。このときは、押しつぶされた導電性粒子 309 で導電層 303 と導電層 224 の間隔を保持する。

## 【0079】

また、樹脂で形成された粒子の表面に、金、銀、銅、パラジウム、又は白金から選ばれた一元素、若しくは複数の元素で形成される薄膜が形成された導電性粒子を用いてもよい。さらには、異方性導電接着剤の代わりに、ベースフィルム上にフィルム状に形成された異方性導電フィルムを転写して用いても良い。異方性導電フィルムも、異方性導電接着剤と同様の導電性粒子が分散されている。

## 【0080】

図 3 (A) に示す記憶素子 134 は、スイッチング用の TFT112 が、各記憶素子 134 に設けられている。即ち、アクティブマトリクス型の記憶回路を有する半導体装置である。なお、図 3 (B) に示すように、第 1 の導電層 151、有機化合物層又は相変化層 152、第 2 の導電層 153 で構成される記憶素子 154 を設けることも可能である。この構造では、図 1 (B) と同様に記憶素子 154 には各スイッチング用の TFT が接続されておらず、TFT111 に直接接続されている。また、第 1 の導電層 151 は共通電極として機能し、第 1 の導電層 151 を用いて複数の記憶素子 154 が形成されており、パッシブマトリクス型の記憶回路を有する半導体装置である。

## 【0081】

さらには、本実施形態においても、図 2 (A) に示すように、接着層 201 を介して基板 200a 上に複数のトランジスタを有する素子形成層 301a を設けても良い。

## 【0082】

本発明の半導体装置は、複数の TFT を有する素子形成層上に、記憶素子を含む層を積層した構成を有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる。また、複数のトランジスタと記憶素子を有する素子形成層を形成する工程とアンテナとして機能する導電層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、アンテナそれが形成された時点で、各回路の性能を確認し、選別して、複数のトランジスタを有する素子形成層や、アンテナを電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

## 【0083】

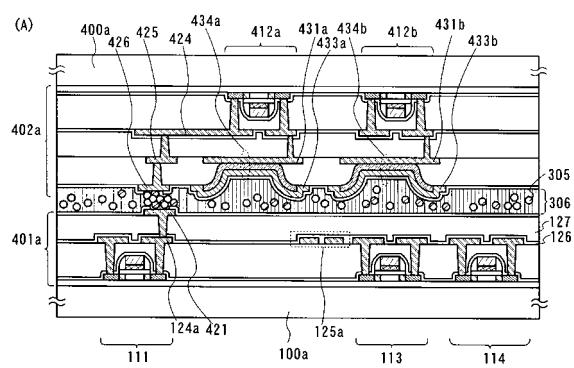

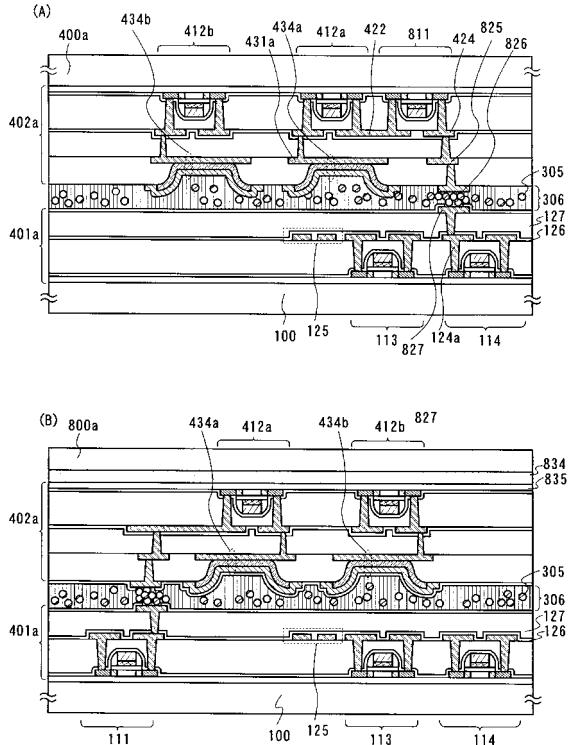

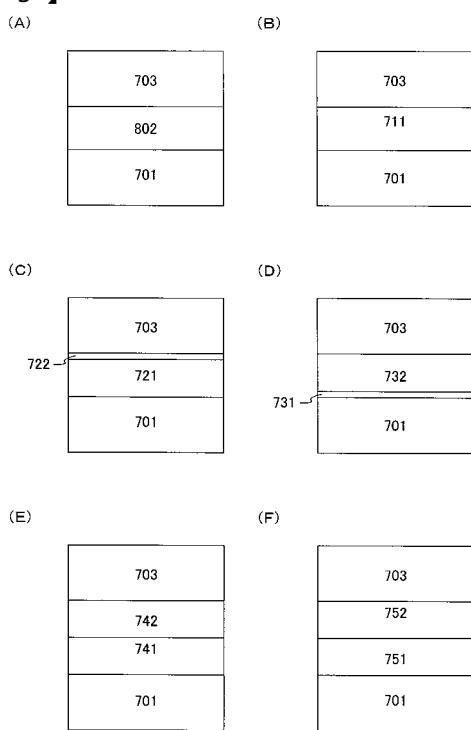

## (実施形態3)

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について、図4及び図7を用いて説明する。より詳しくは、図3に示した半導体装置と比較すると、アンテナを有する導電層の代わりに、記憶素子を有する素子形成層402aが形成された基板が貼り合わせられた構造の半導体装置の断面構造について説明する。

## 【0084】

本実施形態の半導体装置は、図7(C)に示すように、第1の基板100a上に形成された複数のトランジスタを有する素子形成層401aと、第2の基板400a上に形成された記憶素子を有する素子形成層402aとが、接着層で貼り合わせられた構成を有する。

## 【0085】

ここでは、複数のトランジスタを有する素子形成層401aは、代表的には複数のTFTを有する領域102、103と、アンテナとして機能する導電層125aを有する。また、記憶素子を有する素子形成層402aは、記憶素子を有する領域104で構成される。また、記憶素子を有する領域104は、制御回路、インターフェイス等を構成する複数のTFTを含む領域103と、図示しないが導電性粒子で接続されている。

## 【0086】

上記の図7(C)に示す構成を有する本発明の半導体装置の断面構造について、図4を用いて説明する。

## 【0087】

図4(A)に示すように、基板100a上には、アンテナとして機能する導電層及び複数のトランジスタを有する素子形成層401aが形成され、アンテナとして機能する導電層及び複数のトランジスタを有する素子形成層401aはTFT111、113、114を有し、これらのTFTの構造は上述した通りである。また、基板400a上に記憶素子を有する素子形成層402aが形成されている。図4(A)においては、記憶素子434a、434bそれぞれに、スイッチング用のTFT412a、412bが接続されている。即ち、スイッチング用のTFT412a、412bのソース配線又はドレイン配線の一方に記憶素子の第1の導電層431a、431bが接続されている。また、スイッチング用のTFT412a、412bのソース配線又はドレイン配線の他方は、記憶素子の第1の導電層又は第2の導電層と同時に形成された導電層と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層424の他方は、導電層425を介して導電層426と接続している。なお、導電層425は、記憶素子の第1の導電層431a、431bと同時に形成された導電層であり、導電層426は、記憶素子の第2の導電層433a、433bと同時に形成された導電層である。

## 【0088】

また、複数のトランジスタを有する素子形成層401a及び記憶素子を有する素子形成層402aが接着層306で接着されている。

## 【0089】

また、記憶素子のスイッチング用のTFT412aのソース配線又はドレイン配線として機能する導電層424と、記憶素子を動作させる回路を構成するTFT111のソース配線又はドレイン配線として機能する導電層124aとは、導電性粒子305、及び導電層421、425、426を介して電気的に接続されている。

## 【0090】

なお、記憶素子の構成によつては、記憶素子を有する素子形成層402aに対して、レーザ光を用いた光学的作用によりデータの書き込みを行う場合がある。そのような場合、記憶素子を有する素子形成層402aにおいて、スイッチング用のTFT412a、412bと、記憶素子434a、434bそれが、重ならない領域を有するようにレイアウトをすることが必要である。

## 【0091】

10

20

30

40

50

図4(A)に示す記憶素子434a、434bは、それぞれスイッチング用のTFT412a、412bに接続される。即ち、アクティブマトリクス型の半導体装置である。なお、図4(B)に示すように、第1の導電層451、有機化合物層又は相変化層452、第2の導電層453で構成される記憶素子454を有する基板を貼り合わせることも可能である。また、第1の導電層451、有機化合物層又は相変化層452、第2の導電層453は、それぞれ実施形態1に示す第1の導電層151と、有機化合物層又は相変化層152と、第2の導電層153と同様の構造を用いることができる。この構造では、図1(B)と同様に記憶素子454には各スイッチング用のTFTが接続されておらず、記憶素子を動作させる回路を構成するTFT111に導電性粒子305を介して接続されている。また、第1の導電層451は共通電極として機能し、第1の導電層451を用いて複数の記憶素子454が形成されており、パッシブマトリクス型の記憶回路を有する半導体装置である。

10

20

30

40

#### 【0092】

また、上記実施形態において、複数のトランジスタを有する素子形成層401aに記憶素子を動作させる回路が形成されるが、これに限定されるものではない。例えば、記憶素子を有する素子形成層402aに記憶素子を動作させる回路が形成されてもよい。具体的には、図8(A)に示すように、記憶素子434a、434bとともに、記憶素子を動作させる回路を構成するTFT811を基板400a上に形成した後、記憶素子を有する素子形成層402aと複数のトランジスタを有する素子形成層401aと、導電性粒子305を有する接着層306で貼り合わせてもよい。このとき、記憶素子を動作させる回路を構成するTFT811のソース配線又はドレイン配線として機能する導電層424の一方と、TFT114のソース配線又はドレイン配線として機能する導電層124aの一方とが、導電性粒子305、及び導電層825、826、827を介して電気的に接続される。なお、導電層826は、TFT811のソース配線又はドレイン配線として機能する導電層424の一方と導電層825を介して接続されている。また、導電層826は、記憶素子の第2の導電層と同時に形成された導電層であり、導電層825は、記憶素子の第1の導電層と同時に形成された導電層である。

20

#### 【0093】

また、図4(A)において、記憶素子を有する素子形成層402aは基板400a上に形成された構造を有しているが、図8(B)に示すように、基板800a上に接着層834を介して記憶素子を有する素子形成層402aを貼り合せても良い。

30

#### 【0094】

本発明の半導体装置は、アンテナとして機能する導電層と複数のトランジスタを有する素子形成層上に、記憶素子を含む層を貼りあわせた構成を有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる。また、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子を有する素子形成層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子それが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子を電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

40

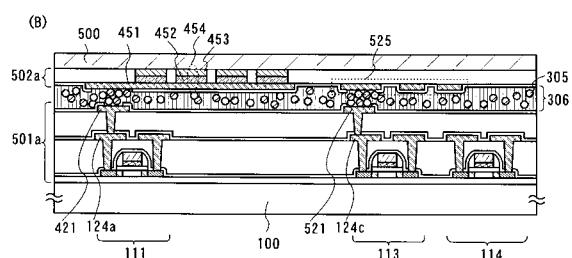

#### 【0095】

##### (実施形態4)

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について説明する。より詳しくは、複数のトランジスタを有する素子形成層に、記憶素子及びアンテナが形成された層を有する基板が貼り合わせられた構造の半導体装置の断面構造について、図5及び図7を用いて説明する。

#### 【0096】

本実施形態の半導体装置は、図7(D)に示すように、第1の基板100a上に形成された複数のトランジスタを有する素子形成層501aと、第2の基板500a上に形成さ

50

れた記憶素子及びアンテナを有する素子形成層 502a とが、接着層で貼り合わせられた構成を有する。

【0097】

ここでは、複数のトランジスタを有する素子形成層 501a は、代表的には複数の TFT を有する領域 102、103 を有する。また、記憶素子及びアンテナを有する素子形成層 502a は、記憶素子を有する領域 104 及びアンテナとして機能する導電層 105 で構成される。また、記憶素子を有する領域 104 は、制御回路、インターフェイス等を構成する複数の TFT を含む領域 103 と、図示しないが導電性粒子で接続されている。また、及びアンテナとして機能する導電層 105 は、通信回路を構成する複数の TFT を含む領域 102 と、図示しないが導電性粒子で接続されている。

10

【0098】

上記の図 7 (D) に示す構成を有する本発明の半導体装置の断面構造について、図 5 を用いて説明する。

【0099】

図 5 (A) に示すように、複数の TFT を有する素子形成層 501a は、TFT111、113、114 を有し、これらの TFT の構造は上述した通りである。また、基板 500a 上に記憶素子 434 及びアンテナとして機能する導電層 525 を有する素子形成層 502 が形成されている。図 5 (A) においては、記憶素子 434 に、スイッチング用の TFT412 が接続されている。即ち、スイッチング用の TFT412 のソース配線又はドレイン配線の一方に、記憶素子 434 の第 1 の導電層が接続されている。

20

【0100】

また、スイッチング用の TFT412 のソース配線又はドレイン配線の他方は、記憶素子の第 1 の導電層又は第 2 の導電層と同時に形成された導電層 425 と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層 424 の他方は、導電層 425 を介して導電層 426 と接続している。なお、導電層 426 は、記憶素子 434 の第 2 の導電層と同時に形成された導電層であり、接続端子として機能する。

20

【0101】

また、TFT412 のソース配線又はドレイン配線として機能する導電層 424 及び TFT111 のソース配線又はドレイン配線として機能する導電層 124a は、導電層 421、425、426 及び導電性粒子 305 を介して電気的に接続されている。

30

【0102】

また、記憶素子 434 の第 1 の導電層又は第 2 の導電層と同時に、アンテナとして機能する導電層 525 が形成される。導電層 525 は、TFT113 のソース配線又はドレイン配線として機能する導電層 124c と、導電性粒子 305 及び導電層 521 を介して電気的に接続される。また、導電層 521 は、アンテナとして機能する導電層 525 と接続するための接続端子として機能する。

【0103】

なお、記憶素子の構成によっては、記憶素子 434 に対して、レーザ光を用いた光学的作用によりデータの書き込みを行う場合がある。そのような場合、記憶素子及びアンテナを有する素子形成層 502a において、スイッチング用の TFT412 及び記憶素子 434、並びに導電層 424 及び記憶素子 434 が、重ならない領域を有するように、レイアウトをすることが必要である。

40

【0104】

図 5 (A) に示す記憶素子 434 は、スイッチング用の TFT412 に接続される。即ち、アクティブマトリクス型の半導体装置である。なお、図 5 (B) に示すように、第 1 の導電層 451、有機化合物層又は相変化層 452、第 2 の導電層 453 で構成される記憶素子 454 を有する基板 500 を貼り合わせることも可能である。また、第 1 の導電層 451、有機化合物層又は相変化層 452、第 2 の導電層 453 は、それぞれ実施形態 1 に示す第 1 の導電層 151 と、有機化合物層又は相変化層 152 と、第 2 の導電層 153 と同様の構造を用いることができる。この構造では、図 1 (B) と同様に、パッシブマトリクス

50

リクス型の記憶回路を有する半導体装置である。

【0105】

また、複数のトランジスタを有する素子形成層501aに記憶素子を動作させる回路を構成するTFT111が形成されるが、この構造に限定されない。記憶素子及びアンテナを有する素子形成層に記憶素子を動作させる回路が形成されてもよい。また、図5(A)において、記憶素子及びアンテナを有する素子形成層502aは基板500a上に形成された構造を有しているが、基板上に接着層を介して記憶素子及びアンテナを有する素子形成層502aを貼り合せても良い。さらには、複数のトランジスタを有する素子形成層501aは基板100a上に形成されているが、図2(A)に示すように基板200a上に接着層を介して複数のトランジスタを有する素子形成層501aを貼り合せても良い。

10

【0106】

本発明の半導体装置は、複数のTFTを有する素子形成層上に、記憶素子及びアンテナを含む素子形成層を接着層を介して積層した構成を有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる。また、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子及びアンテナを有する素子形成層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子、アンテナそれぞれが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子、アンテナを電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

20

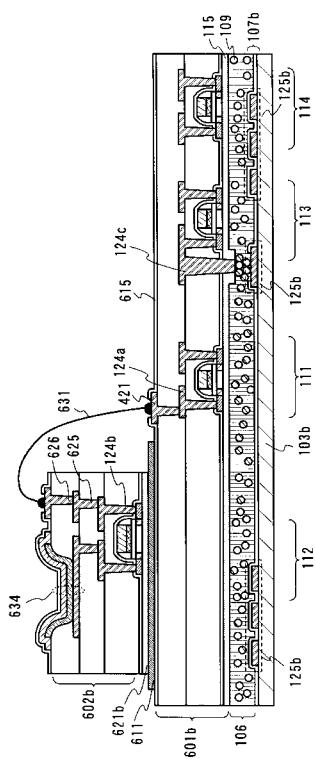

【0107】

(実施形態5)

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について説明する。より詳しくは、複数のトランジスタを有する素子形成層601aが形成される基板100a上に、記憶素子を有する素子形成層602aを搭載した構造の半導体装置の断面構造について、図6及び図7を用いて説明する。

【0108】

本実施形態の半導体装置は、図7(E)に示すように、基板100a上に形成された複数のトランジスタを有する素子形成層601aと基板100a上に、記憶素子を有する素子形成層602aが、接着層611で貼り合わせられた構成を有する。

30

【0109】

ここでは、複数のトランジスタを有する素子形成層601aは、代表的には複数のTFTを有する領域102、103及びアンテナとして機能する導電層105で構成される。また、記憶素子を有する素子形成層602aは、記憶素子を有する領域104で構成される。また、記憶素子を有する領域104は、制御回路、インターフェイス等を構成する複数のTFTを含む領域103と、導電部材631を用いて電気的に接続されている。

【0110】

上記の図7(E)に示す構成を有する本発明の半導体装置の断面構造について、図6を用いて説明する。

40

【0111】

図6(A)に示すように、複数のTFTを有する素子形成層601aは、TFT111、113、114を有し、これらのTFTの構造は上述した通りである。また、記憶素子を有する素子形成層602aが形成された基板621aが、基板100a上に接着層611を用いて搭載されている。図6(A)においては、記憶素子634に、スイッチング用のTFT112が接続されている。即ち、スイッチング用のTFT112のソース配線又はドレイン配線の一方に、記憶素子の第1の導電層が接続されている。また、スイッチング用のTFT112のソース配線又はドレイン配線の他方は、記憶素子の第1の導電層又は第2の導電層と同時に形成された導電層と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層124bの他方は、導電層625を介して導電層62

50

6と接続している。なお、導電層625は、記憶素子の第1の導電層と同時に形成された導電層であり、導電層626は、記憶素子の第2の導電層と同時に形成された導電層であり、接続端子として機能する。

【0112】

また、記憶素子を有する素子形成層602aに形成された記憶素子634のスイッチング用のTFT112と、複数のTFTを有する素子形成層601aに形成された記憶素子を動作させる回路を構成するTFT111とが、導電部材631で電気的に接続されている。ここでは、導電部材631をワイヤーを用い、ワイヤボンディング法によりTFT111とTFT112とを接続しているが、導電膜を成膜した後、所望の形状にエッチングして、導電部材631を形成してもよい。さらには、印刷法等の接続方法を用いることができる。

【0113】

図6(A)に示す記憶素子634は、スイッチング用のTFT112に接続される。即ち、アクティブマトリクス型の半導体装置である。なお、図6(B)に示すように、第1の導電層651、有機化合物層又は相変化層652、第2の導電層653で構成される記憶素子654が形成される基板622を、接着層611を用いて基板100a上に搭載することも可能である。この構造では、パッシブマトリクス型の記憶回路を有する半導体装置である。

【0114】

また、本実施形態では、記憶素子を有する素子形成層602aを基板100a上に搭載したが、これに限定されず、記憶素子及びアンテナを有する素子形成層や、アンテナを有する素子形成層を基板100a上に搭載しても良い。

【0115】

本発明の半導体装置は、複数のTFTを有する素子形成層と、記憶素子を含む層を同一基板上に有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる。また、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子を有する素子形成層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子それぞれが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子を電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

【0116】

(実施形態6)

本実施形態では、半導体装置の作製方法に関して図面を参照して説明する。ここでは、実施形態1の図2(A)で示す半導体装置の作製方法を示すが、各実施形態に示される半導体装置にそれぞれ、本実施形態を適宜適応することが可能である。

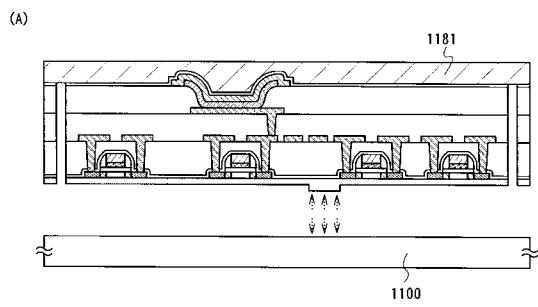

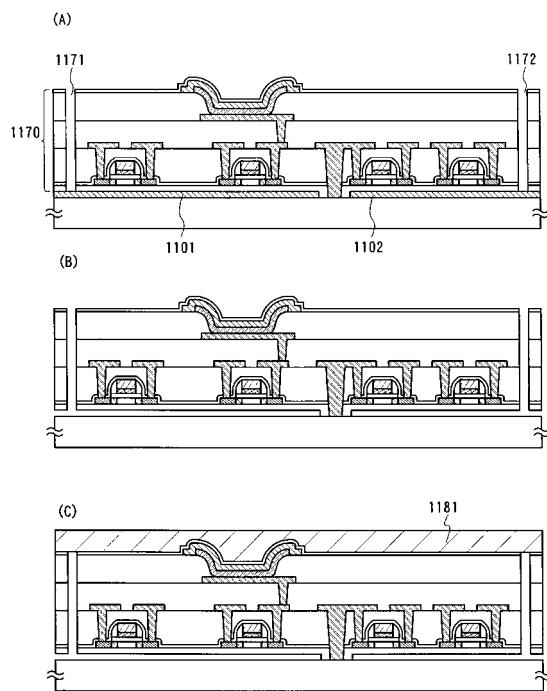

【0117】

図9(A)に示すように、基板1100の一表面上に、剥離層1101、1102を形成する。

【0118】

基板1100は、ガラス基板、石英基板、金属基板やステンレス基板の一表面上に絶縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いる。上記に挙げた基板1100には、大きさや形状に制約がないため、例えば、基板1100として、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。この利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。

【0119】

また、基板1100上に設けられる複数のトランジスタを有する素子形成層は、後に基板1100上から剥離される。従って、基板1100を再利用して、当該基板1100上

10

20

30

40

50

に新たに複数のトランジスタを有する素子形成層を形成してもよい。この結果、コストを削減することができる。なお、再利用する基板 1100 には、石英基板を用いることが好ましい。

【0120】

剥離層 1101、1102 は、基板 1100 の一表面に薄膜を形成した後、フォトリソグラフィ法により形成したレジストマスクを用いて選択的にエッチングして形成する。剥離層 1101、1102 は、スパッタリング法やプラズマ CVD 法等により、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、鉛 (Pb)、オスミウム (Os)、イリジウム (Ir)、珪素 (Si) から選択された元素、又は前記元素を主成分とする合金材料、又は前記元素を主成分とする化合物材料からなる層を、単層又は積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

【0121】

剥離層 1101、1102 が単層構造の場合、好ましくは、タンゲステン層、モリブデン層、又はタンゲステンとモリブデンの混合物を含む層を形成する。又は、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。

【0122】

剥離層 1101、1102 が積層構造の場合、好ましくは、1 層目としてタンゲステン層、モリブデン層、又はタンゲステンとモリブデンの混合物を含む層を形成し、2 層目として、タンゲステン、モリブデン又はタンゲステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物又は窒化酸化物を形成する。

【0123】

剥離層 1101、1102 として、タンゲステンを含む層とタンゲステンの酸化物を含む層の積層構造を形成する場合、タンゲステンを含む層を形成し、その上層に酸化珪素を含む層を形成することで、タンゲステン層と酸化珪素層との界面に、タンゲステンの酸化物を含む層が形成されることを活用してもよい。さらには、タンゲステンを含む層の表面を、熱酸化処理、酸素プラズマ処理、N<sub>2</sub>O プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行ってタンゲステンの酸化物を含む層を形成してもよい。これは、タンゲステンの窒化物、酸化窒化物及び窒化酸化物を含む層を形成する場合も同様であり、タンゲステンを含む層を形成後、その上層に窒化珪素層、酸化窒化珪素層、窒化酸化珪素層を形成するとよい。

【0124】

タンゲステンの酸化物は、WO<sub>X</sub> で表される。X は 2 < X < 3 の範囲内にあり、X が 2 の場合 (WO<sub>2</sub>)、X が 2.5 の場合 (W<sub>2</sub>O<sub>5</sub>)、X が 2.75 の場合 (W<sub>4</sub>O<sub>11</sub>)、X が 3 の場合 (WO<sub>3</sub>) などがある。タンゲステンの酸化物を形成するにあたり、上記に挙げた X の値に特に制約はなく、そのエッチングレートなどを基に決めるとい。但し、エッチングレートの最も良いものは、酸素雰囲気下で、スパッタリング法により形成するタンゲステンの酸化物を含む層 (WO<sub>X</sub>、0 < X < 3) である。従って、作製時間の短縮のために、剥離層として、酸素雰囲気下でスパッタリング法によりタンゲステンの酸化物を含む層を形成するとよい。

【0125】

また、上記の工程によると、基板 1100 に接するように剥離層 1101、1102 を形成しているが、本発明はこの工程に制約されない。基板 1100 に接するように下地となる絶縁層を形成し、その絶縁層に接するように剥離層 1101、1102 を設けてよい。

【0126】

10

20

30

40

50

次に、図9(B)に示すように、剥離層1101、1102を覆うように、下地となる絶縁層1105を形成する。絶縁層1105は、公知の手段(スパッタリング法やプラズマCVD法等)により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層で形成する。珪素の酸化物材料とは、珪素(Si)と酸素(O)を含む物質であり、酸化珪素、酸化窒化珪素、窒化酸化珪素等が該当する。珪素の窒化物材料とは、珪素と窒素(N)を含む物質であり、窒化珪素、酸化窒化珪素、窒化酸化珪素等が該当する。下地となる絶縁層は、基板1100からの不純物の侵入を防止するブロッキング膜として機能する。

#### 【0127】

次に、絶縁層1105上に、非晶質半導体層(例えば非晶質珪素を含む層)を形成する。この非晶質半導体層は、公知の手段(スパッタリング法、LPCVD法、プラズマCVD法等)により、25~200nm(好ましくは30~150nm)の厚さで形成する。続いて、非晶質半導体層を公知の結晶化法(レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とレーザ結晶化法を組み合わせた方法等)により結晶化して、結晶質半導体層を形成する。その後、得られた結晶質半導体層を所望の形状にエッチングして結晶質半導体層1127~1130を形成する。なお、剥離層1101、1102がタンゲステンの場合、当該加熱処理により、剥離層1101、1102及び絶縁層1105の界面において、タンゲステンの酸化物を形成することが可能である。

#### 【0128】

結晶質半導体層1127~1130の作製工程の具体例を挙げると、まず、プラズマCVD法を用いて、膜厚66nmの非晶質半導体層を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体層上に保持させた後、非晶質半導体層に脱水素化の処理(500、1時間)と、熱結晶化の処理(550、4時間)を行って結晶質半導体層を形成する。その後、必要に応じてレーザ光を照射して結晶性を向上させた後、フォトリソグラフィ法を用いて形成されたレジストマスクを用いてエッチングして結晶質半導体層1127~1130を形成する。

#### 【0129】

なお、レーザ結晶化法で結晶質半導体層1127~1130を形成する場合、連続発振またはパルス発振の気体レーザ又は固体レーザを用いる。気体レーザとしては、エキシマレーザ、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、Ti:サファイアレーザ等を用いる。固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を使ったレーザを用いる。

#### 【0130】

また、結晶化を助長する金属元素を用いて非晶質半導体層の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体層に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。そこで、結晶質半導体層上に、ゲッタリングサイトとして機能する非晶質半導体層を形成するとよい。ゲッタリングサイトとなる非晶質半導体層には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることができなスパッタリング法で形成するとよい。その後、加熱処理(RTA法やファーネスアニール炉を用いた熱アニール等)を行って、非晶質半導体層中に金属元素を拡散させ、続いて、当該金属元素を含む非晶質半導体層を除去する。そうすると、結晶質半導体層中の金属元素の含有量を低減又は除去することができる。

#### 【0131】

次に、結晶質半導体層1127~1130を覆う絶縁層を形成する。絶縁層は、プラズマCVD法やスパッタリング法等により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層して形成する。具体的には、酸化珪素を含む層、酸化窒化珪素を含む層、窒化酸化珪素を含む層を、単層で又は積層して形成する。

#### 【0132】

10

20

30

40

50

次に、絶縁層上に、第1の導電層と第2の導電層を積層して形成する。第1の導電層は、プラズマCVD法やスパッタリング法により、20~100nmの厚さで形成する。第2の導電層は、公知の手段により、100~400nmの厚さで形成する。第1の導電層と第2の導電層は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nd)等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。

### 【0133】

第1の導電層と第2の導電層との組み合わせの例を挙げると、窒化タンタル(TaN)層とタンゲステン(W)層、窒化タンゲステン(WN)層とタンゲステン層、窒化モリブデン(MoN)層とモリブデン(Mo)層等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、第1の導電層と第2の導電層を形成した後に、熱活性化を目的とした加熱処理を行うことができる。

### 【0134】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極を形成するためのエッチング処理を行って、ゲート電極として機能する導電層(ゲート電極層とよぶことがある)1107~1110を形成する。

### 【0135】

次に、結晶質半導体層1127~1130に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、N型不純物領域を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。また、P型を付与する不純物元素を添加して、P型不純物領域を形成してもよい。P型を付与する不純物元素は、例えばボロン(B)を用いる。

### 【0136】

次に、絶縁層と導電層1107~1110を覆うように、絶縁層を形成する。絶縁層は、公知の手段(プラズマCVD法やスパッタリング法)により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む層(無機層と表記することがある)や、有機樹脂などの有機材料を含む層(有機層と表記することがある)を、単層又は積層して形成する。好ましくは、絶縁層として、珪素の酸化物からなる層を形成する。

### 【0137】

次に、絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層1107~1110の側面に接する絶縁層(以下、サイドウォール絶縁層とよぶ)1115~1118を形成する(図9(B)参照)。サイドウォール絶縁層1115~1117は、後にソース領域及びドレイン領域を形成するためのドーピング用のマスクとして用いる。

### 【0138】

なお、サイドウォール絶縁層1115~1118を形成するためのエッチング工程により、絶縁層もエッチングされ、ゲート絶縁層1119~1122が形成される。ゲート絶縁層1119~1122は、導電層1107~1110及びサイドウォール絶縁層1115~1118と重なる層である。このように、ゲート絶縁層がエッチングされてしまうのは、ゲート絶縁層とサイドウォール絶縁層1115~1118の材料のエッチングレートが同じであるためであり、図9(B)ではその場合を示している。従って、ゲート絶縁層とサイドウォール絶縁層1115~1118の材料のエッチングレートが異なる場合には、サイドウォール絶縁層1115~1118を形成するためのエッチング工程を経ても、絶縁層が残存する場合がある。

### 【0139】

続いて、サイドウォール絶縁層1115~1118をマスクとして、結晶質半導体層1127~1130にN型を付与する不純物元素を添加して、第1のN型不純物領域(LDD領域ともよぶ)1123a~1123dと、第2のN型不純物領域(ソース領域及びド

10

20

30

40

50

レイン領域領域ともよぶ) 1124a ~ 1124d とを形成する。第1のN型不純物領域 1123a ~ 1123d が含む不純物元素の濃度は、第2のN型不純物領域 1124a ~ 1124d の不純物元素の濃度よりも低い。

【0140】

なお、第1のN型不純物領域 1123a ~ 1123d を形成するためには、ゲート電極を2層以上の積層構造とし、該ゲート電極がテーパ部を有するようなエッチングや異方性エッチングを行って該ゲート電極を構成する下層の導電層をマスクとして用いる手法と、サイドウォール絶縁層をマスクとして用いる手法がある。前者の手法を採用して形成された薄膜トランジスタは G O L D ( G a t e O v e r l a p p e d L i g h t l y D o p e d d r a i n ) 構造になる。本発明は、前者と後者のどちらの手法を用いてもよい。但し、後者のサイドウォール絶縁層をマスクとして用いる手法を用いると、LDD領域を確実に形成することができ、また、LDD領域の幅の制御が容易になるという利点がある。

10

【0141】

上記工程を経て、n型のTFT1131 ~ 1134 が完成する。

【0142】

n型のTFT1131 ~ 1134 は、LDD構造を有し、第1のn型不純物領域 (LDD領域ともよぶ。) と第2のn型不純物領域 (ソース領域及びドレイン領域ともよぶ。) とチャネル形成領域を含む活性層と、ゲート絶縁層と、ゲート電極として機能する導電層とを有する。

20

【0143】

次に、TFT1131 ~ 1134 を覆うように、単層又は積層で絶縁層を形成する。TFT1131 ~ 1134 を覆う絶縁層は、公知の手段 (SOG法、液滴吐出法等) により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等により、単層又は積層で形成する。シロキサン系の材料とは、例えば、シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基 (例えばアルキル基、芳香族炭化水素) が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

30

【0144】

図示する断面構造では、TFT1131 ~ 1134 を覆うように、絶縁層を2層積層して形成した場合を示し、1層目の絶縁層 1142 として窒化珪素を含む層を形成し、2層目の絶縁層 1141 として酸化珪素を含む層を形成する。さらには、2層目の絶縁層 1141 上に、3層目の絶縁層として酸化珪素を含む層を形成してもよい。

【0145】

なお、絶縁層 1141、1142 を形成する前、又は絶縁層 1141、1142 のうちの1つ又は複数の薄膜を形成した後に、半導体層の結晶性の回復や半導体層に添加された不純物元素の活性化、半導体層の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザアニール法又はRTA法などを適用するとよい。

40

【0146】

次に、図9 (C) に示すように、フォトリソグラフィ法により絶縁層 1141、1142 をエッチングして、第2のN型不純物領域 1124a ~ 1124d を露出させるコンタクトホール 1143 ~ 1150 を形成する。

【0147】

次に、図9 (D) に示すように、コンタクトホール 1143 ~ 1150 を充填するよう、導電層を形成し、当該導電層をパターン加工して、導電層 1154 ~ 1162 を形成する。導電層 1155 ~ 1162 は、TFTのソース配線又はドレイン配線として機能し、導電層 1154 はアンテナとして機能する。

【0148】

導電層 1154 ~ 1162 は、プラズマCVD法やスパッタリング法等により、チタン

50

(T<sub>i</sub>)、アルミニウム(A<sub>1</sub>)、ネオジウム(Nd)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。

【0149】

導電層1154～1162は、例えば、バリア層とアルミニウムシリコン(A<sub>1</sub>-Si)層とバリア層、バリア層とアルミニウムシリコン(A<sub>1</sub>-Si)層と窒化チタン(TiN)層とバリア層の積層構造を採用するとよい。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる層に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電層1154～1162を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また下層のバリア層を設けると、アルミニウムやアルミニウムシリコンと、結晶質半導体層との、良好なコンタクトをとることができる。また、チタンは、還元性の高い元素であるため、チタンからなるバリア層を形成すると、結晶質半導体層上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体層と良好なコンタクトをとることができる。

【0150】

次に、図9(E)に示すように、導電層1154～1162を覆うように、単層又は積層で絶縁層1163を形成する。導電層1154～1162を覆う絶縁層1163は、薄膜トランジスタを覆う絶縁層1142と同様の手法及び材料を用いて形成することができる。次に、導電層1154～1162を覆う絶縁層1163にコンタクトホールを形成し、第1の導電層1164を形成する。導電層1164は、後に形成される記憶素子の第1の導電層として機能する。なお、第1の導電層は薄膜トランジスタ1132を覆うように形成する。

【0151】

次に、第1の導電層1164の端部を覆うように絶縁層1165を形成した後、有機化合物層又は相変化層1166、第2の導電層1167を形成する。第1の導電層1164、有機化合物層又は相変化層1166、及び第2の導電層1167で記憶素子1169を構成する。この後、絶縁層1168を形成してもよい。当該絶縁層1168は、DLC(ダイヤモンドライカーボン)などの炭素を含む層、窒化珪素を含む層、窒化酸化珪素を含む層、有機材料(好ましくはエポキシ樹脂)を含む層等に相当する。なお、絶縁層は、保護層として機能するものであり、必要がなければ形成しなくてもよい。また、絶縁層1168として、膜厚の厚い(代表的には5～100μm、好ましくは5～50μm、更に好ましくは5～10μm)有機化合物からなる層を形成すると、剥離層1101、1102を除去した後でも、基板1100上の複数の素子に重みがつき、基板1100からの飛散を防止し、さらに、巻かれた形状になることがなく、素子の破壊や損傷を防止することができる。以下、TFT1131～1134及び記憶素子1169を含むを複数のトランジスタを有する素子形成層1170と示す。

【0152】

また、記憶素子の有機化合物層を、インクジェットに代表される液滴吐出法により形成してもよい。液滴吐出法を用いることにより、材料の利用効率を向上させて、作製工程を簡略化した半導体装置の作製方法を提供することができる。また、作製時間の短縮及び作製費用の低減を実現した半導体装置の作製方法を提供することができる。

【0153】

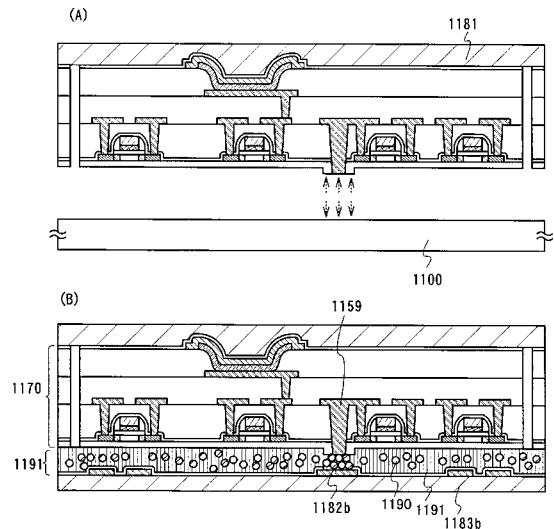

次に、図10(A)に示すように、剥離層1101、1102が露出するように、フォトリソグラフィ法により絶縁層1105、1141、1142、1163、1165、1168をエッチングして、開口部1171、1172を形成する。

【0154】

次に、図10(B)に示すように、開口部1171、1172にエッチング剤を導入し

10

20

30

40

50

て、剥離層 1101、1102を除去する。エッチング剤は、ウエットエッチングであれば、フッ酸を水やフッ化アンモニウムで希釈した混液、フッ酸と硝酸の混液、フッ酸と硝酸と酢酸の混液、過酸化水素と硫酸の混液、過酸化水素とアンモニウム水と水の混液、過酸化水素と塩酸と水の混液等を用いる。また、ドライエッチングであれば、フッ素等のハロゲン系の原子や分子を含む気体、又は酸素を含む気体を用いる。好ましくは、エッチング剤として、フッ化ハロゲン又はハロゲン間化合物を含む気体又は液体を使用する。例えば、フッ化ハロゲンを含む気体として三フッ化塩素 (C<sub>1</sub>F<sub>3</sub>) を使用する。

【0155】

次に、図10(C)に示すように、複数のトランジスタを有する素子形成層1170において記憶素子が形成されている面を、基体1181に接着させた後、複数のトランジスタを有する素子形成層1170を基板1100から完全に剥離する(図11(A)の断面図参照)。

【0156】

基体1181は、実施形態1で示される基板200aと同様の材料を用いることができる。

【0157】

次に、図11(B)に示すように、複数のトランジスタを有する素子形成層1170の他方の面を、接着剤1182aを用いて基板1183aに接着させる。

【0158】

基板1183aには、実施形態1で示される基板200aと同様の材料を用いることができる。

【0159】

次に、複数のトランジスタを有する素子形成層1170と基体1181とが接着したものを、スライシング装置やレーザ照射装置等を用いて分断する。

【0160】

上記工程を経て、非接触でデータを交信する機能を有する半導体装置が完成する。

【0161】

また、本実施形態では、複数のトランジスタを有する素子形成層1170と、基板1183とを接着させた後、分断して半導体装置を形成しているが、この工程に限定されない。複数のトランジスタを有する素子形成層1170と基体1181を接着し、分断した後、複数のトランジスタを有する素子形成層1170に、基板1183を接着してもよい。

【0162】

このように、本発明の半導体装置は、小型、薄型、軽量であり、フレキシブル性を有するために、多種多様の用途が実現し、物品に貼り付けても、その物品のデザイン性を損なうことがない。

(実施形態7)

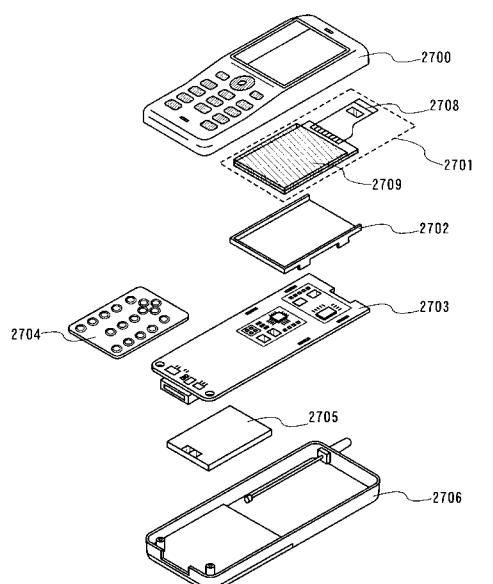

本実施形態の半導体装置の構成について、図26、27を参照して説明する。

【0163】

本実施形態の半導体装置の斜視図について、図26(A)を用いて説明する。本実施形態の半導体装置は、図26(A)に示すように、基板上に複数のトランジスタが集積された構成を有する。ここでは、複数のトランジスタを有する素子形成層101bと、基板108bに設けられたアンテナを有する素子形成層107bが形成されており、記憶素子と複数のトランジスタを有する素子形成層101bは、代表的には複数のTFTを有する領域102、103と、記憶素子を有する領域104とで構成されている。また、基板108b上にはアンテナとして機能する導電層105を有する素子形成層107bが形成されており、複数のトランジスタを有する素子形成層101bの裏面において、導電層105と接着層で貼り合わせられた構成を有する。ここで、複数のトランジスタを有する素子形成層101bの裏面とは、絶縁層が露出されている面をいう。

【0164】

10

20

30

40

50

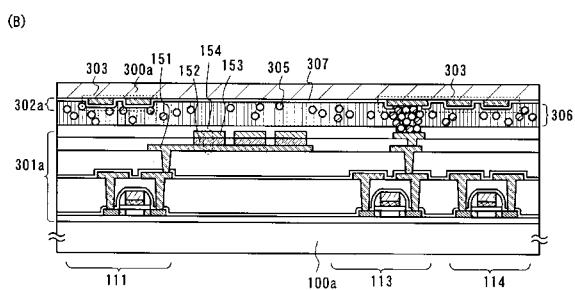

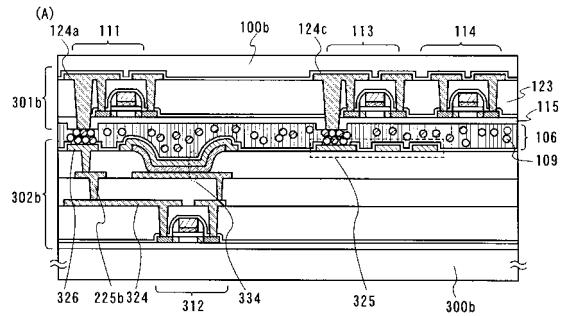

次に、図26(A)に示す構成を有する半導体装置の断面構造について、図27(A)を用いて説明する。複数のトランジスタを有する素子形成層101bが基板100bに設けられている。ここでは、複数の回路を有する素子形成層101bとして、記憶素子を動作させる回路を構成するTFT111(図26(A))の記憶素子を有する領域104の一部)、記憶素子のスイッチング用のTFT112(図26(A))の記憶素子を有する領域104の一部)、電源回路、クロック発生回路、データ復調/変調回路等のアンテナで受信した信号を処理する回路を構成するTFT113(図26(A))の複数のTFTを有する領域102の一部)、制御回路、インターフェイス等の回路を構成するTFT114(図26(A))の複数のTFTを有する領域103の一部)を示す。

## 【0165】

10

また、複数のトランジスタを有する素子形成層101bとアンテナを有する素子形成層107bは接着層106で貼り合わせられている。具体的には、絶縁層115とアンテナを有する素子形成層107bは接着層106で貼り合わせられている。また、素子形成層101bのTFT113のソース配線又はドレイン配線として機能する導電層124cと、素子形成層101bのアンテナとして機能する導電層125bは、接着層106の導電性粒子109を介して電気的に接続されている。

## 【0166】

20

TFT111~114は、基板100bと絶縁層115との間に設けられてまた、TFT111~114を覆う絶縁層122が形成されている。

## 【0167】

また、TFT111~114と、パッシベーション膜として機能する絶縁層122を覆うように、絶縁層123が設けられており、これらの絶縁層123は、表面を平坦化するために設けられている。ソース配線又はドレイン配線として機能する導電層124a~124dは、ソース領域及びドレイン領域119a~119dに接し、絶縁層123に設けられたコンタクトホールを充填する。また、TFT113のソース配線又はドレイン配線として機能する導電層124cの一方は、絶縁層115、122、123を貫通しており、素子形成層101の裏面に露出している。

## 【0168】

30

また、導電層124a~124d、125bを覆うように、絶縁層126、127が設けられている。これらの絶縁層126、127は、表面を平坦化する目的と、TFT111~114及び導電層124a~124d、125bを保護する目的で設けられている。

## 【0169】

また、絶縁層127上に記憶素子134が設けられている。

## 【0170】

40

絶縁層127上に、第1の導電層131、有機化合物層又は相変化層132、第2の導電層133が順に積層されており、この積層体が記憶素子134に相当する。隣接する有機化合物層又は相変化層132の間には、絶縁層135が設けられている。第1の導電層131は、TFT112のソース配線又はドレイン配線として機能する導電層124bと接続する。導電層133上には、絶縁層136が設けられている。なお、TFT112は記憶素子のスイッチング用のTFTとして機能する。また、その他の記憶素子それぞれにもスイッチング用のTFTが設けられている。この構造では、アクティブマトリクス型の記憶回路を有する半導体装置である。

## 【0171】

また、絶縁層136上には基板100bが設けられている。

## 【0172】

次に、図27(A)のトランジスタを設けた記憶素子の代わりに、スイッチング用のトランジスタを有しない記憶素子を有する半導体装置、即ちパッシブマトリクス型の記憶回路を有する半導体装置の断面構造について、図27(B)を用いて説明する。より詳しくは、図27(A)に示した半導体装置と比較すると、記憶素子154の構造が異なる半導体装置の断面構造について説明する。

50

## 【0173】

絶縁層127上に、TFT111のソース配線又はドレイン配線として機能する導電層124aに接続するように、第1の導電層151が設けられ、第1の導電層151に接するように有機化合物層又は相変化層152が設けられ、有機化合物層又は相変化層152に接するように第2の導電層153が設けられている。第1の導電層151と、有機化合物層又は相変化層152と、第2の導電層153との積層体が記憶素子154に相当する。隣接する有機化合物層又は相変化層152の間には、絶縁層155が設けられている。記憶素子154上には、絶縁層156が設けられている。

## 【0174】

本発明の半導体装置は、記憶素子と複数のトランジスタを有する素子形成層を形成する工程とアンテナとして機能する導電層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、記憶素子と複数のトランジスタを有する素子形成層や、アンテナそれが形成された時点で、各回路の性能を確認し、選別して、複数のトランジスタを有する素子形成層や、アンテナを電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

## 【0175】

## (実施形態8)

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について説明する。より詳しくは、図27に示した半導体装置と比較すると、アンテナを有する導電層の代わりに、記憶素子を有する素子形成層202bが形成された基板200bが貼り合わせられた構造の半導体装置の断面構造について説明する。

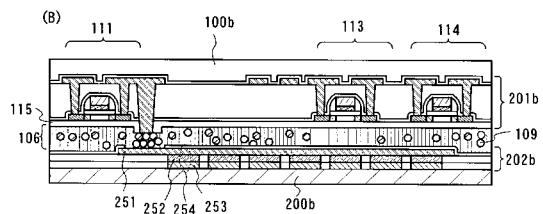

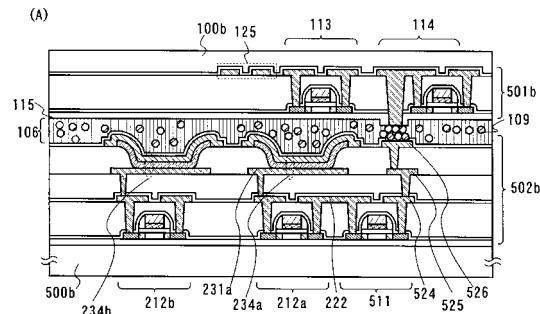

## 【0176】

本実施形態の半導体装置は、図26(B)に示すように、第1の基板100b上に設けられた複数のトランジスタを有する素子形成層201bと、第2の基板200b上に形成された記憶素子を有する素子形成層202bとが、樹脂層で貼り合わせられた構成を有する。

## 【0177】

ここでは、複数のトランジスタを有する素子形成層201bは、代表的には複数のTFTを有する領域102、103と、アンテナとして機能する導電層105を有する。また、記憶素子を有する素子形成層202bは、記憶素子を有する領域104で構成される。また、記憶素子を有する領域104は、制御回路、インターフェイス等を構成する複数のTFTを含む領域103と、図示しないが接着層の導電性粒子で接続されている。

## 【0178】

上記の図26(B)に示す構成を有する本発明の半導体装置の断面構造について、図28を用いて説明する。

## 【0179】

図28(A)に示すように、アンテナとして機能する導電層複数のトランジスタを有する素子形成層201bに基板100bが設けられ、複数のトランジスタを有する素子形成層201bはTFT111、113、114を有し、これらのTFTの構造は上述した通りである。また、TFT111のソース配線又はドレイン配線として機能する導電層124aは、裏面に露出している。

## 【0180】

また、基板200b上に記憶素子を有する素子形成層202bが形成されている。複数のトランジスタを有する素子形成層201bと記憶素子を有する素子形成層202bは接着層106で貼り合わせられている。具体的には、絶縁層115と記憶素子を有する素子形成層202bは接着層106で貼り合わせられている。図28(A)においては、記憶素子234a、234bそれぞれに、スイッチング用のTFT212a、212bが接続されている。即ち、スイッチング用のTFT212a、212bのソース配線又はドレイン配線の一方に記憶素子の第1の導電層231a、231bが接続されている。また、ス

10

20

30

40

50

イッティング用の TFT 212a、212b のソース配線又はドレイン配線の他方は、記憶素子の第1の導電層又は第2の導電層と同時に形成された導電層と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層 223 の他方は、導電層 225b を介して導電層 226 と接続している。なお、導電層 225b は、記憶素子 234a、234b の第1の導電層 231a、231b と同時に形成された導電層であり、導電層 26 は、記憶素子 234a、234b の第2の導電層 233a、233b と同時に形成された導電層である。

#### 【0181】

また、記憶素子のスイッティング用の TFT 212a のソース配線又はドレイン配線として機能する導電層 223 と、記憶素子を動作させる回路を構成する TFT 111 のソース配線又はドレイン配線として機能する導電層 124a とは、接着層 106 中の導電性粒子 109 を介して電気的に接続されている。

#### 【0182】

なお、記憶素子の構成によっては、記憶素子を有する素子形成層 202b に対して、レーザ光を用いた光学的作用によりデータの書き込みを行う場合がある。そのような場合、記憶素子を有する素子形成層 202b において、スイッティング用の TFT 212a、212b と、記憶素子 234a、234b それぞれが、重ならない領域を有するように、レイアウトをすることが必要である。

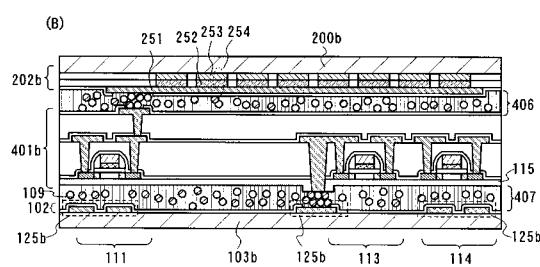

#### 【0183】

図 28 (A) に示す記憶素子 234a、234b は、スイッティング用の TFT 212a、212b が、各記憶素子 234a、234b に設けられた記憶素子を示す。この構造では、アクティブマトリクス型の記憶回路を有する半導体装置である。なお、図 28 (B) に示すように、第1の導電層 251、有機化合物層又は相変化層 252、第2の導電層 253 で構成される記憶素子 254 を有する基板を貼り合わせることも可能である。図 28 (B) においては、各記憶素子それぞれには、スイッティング用の TFT は設けられていないパッシブマトリクス型の記憶回路を示す。なお、第1の導電層 251、有機化合物層又は相変化層 252、第2の導電層 253 は、それぞれ実施形態 1 に示す第1の導電層 151 と、有機化合物層又は相変化層 152 と、第2の導電層 153 と同様の構造を用いることができる。

#### 【0184】

また、上記実施形態において、複数のトランジスタを有する素子形成層 201b に記憶素子を動作させる回路が形成されるが、これに限定される物ではない。例えば、記憶素子を有する素子形成層 202b に記憶素子を動作させる回路を構成する TFT 111 が形成されてもよい。具体的には、図 31 (A) に示すように、記憶素子 234a、234b とともに、記憶素子を動作させる回路を構成する TFT 511 を基板 500b 上に形成した後、記憶素子とアンテナを有する素子形成層 502b と、アンテナ及び複数のトランジスタを有する素子形成層 501b と、導電性粒子 109 を有する接着層 106 で貼り合せてもよい。このとき、記憶素子を動作させる回路を構成する TFT 511 のソース配線又はドレイン配線 524 の一方と接続する導電層 526 と、TFT 114 のソース配線又はドレイン配線 124d の一方とが、導電性粒子 109 を介して電気的に接続される。なお、導電層 526 は、TFT 511 のソース配線又はドレイン配線 524 の一方と導電層 525 を介して接続されている。また、導電層 526 は、記憶素子の第2の導電層と同時に形成された導電層であり、導電層 525 は、記憶素子の第1の導電層と同時に形成された導電層である。

#### 【0185】

また、図 28 (A) において、記憶素子を有する素子形成層 202b は基板 200b 上に形成された構造を有しているが、図 31 (B) に示すように、基板 512b 上に接着層 513 を介して記憶素子を有する素子形成層 202b を貼り合せてても良い。具体的には、基板上に剥離層を設け、剥離層上に複数のトランジスタを有する素子形成層 202b を形成した後、複数のトランジスタを有する素子形成層 202b を剥離層から剥離し、図 31

10

20

30

40

50

(B)に示すように、基板512b上に接着層513を介して複数のトランジスタを有する素子形成層202bを貼り合わせても良い。なお剥離方法としては、実施の形態1に示す剥離方法を適宜用いることが出来る。

【0186】

また、基板512bとしては、基板200aと同様の材料を用いることができる。接着層513は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。

【0187】

上記のように、剥離した複数のトランジスタを有する素子形成層を、可撓性があり、薄くて軽いプラスチック基板に貼り合わせると、厚さが薄く、軽く、落下しても割れにくい半導体装置を提供することができる。また、曲面や異形の形状の物上に貼り合わせることが可能となり、多種多様の用途が実現する。例えば、薬の瓶のような曲面上に、本発明の半導体装置を密着して貼り合わせることができる。さらに、基板を再利用すれば、安価な半導体装置の提供を実現する。

【0188】

本発明の半導体装置は、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子を有する素子形成層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子それそれが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子を電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

【0189】

(実施形態9)

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について説明する。より詳しくは、複数のトランジスタを有する素子形成層の裏面に、記憶素子及びアンテナが形成された層を有する基板が貼り合わせられた構造の半導体装置の断面構造について説明する。

【0190】

本実施形態の半導体装置は、図26(C)に示すように、基板100bに設けられた複数のトランジスタを有する素子形成層301bと、第2の基板300b上に形成された記憶素子及びアンテナを有する素子形成層302bとが、接着層で貼り合わせられた構成を有する。

【0191】

ここでは、複数のトランジスタを有する素子形成層301bは、代表的には複数のTFTを有する領域102、103を有する。また、記憶素子及びアンテナを有する素子形成層302bは、記憶素子を有する領域104及びアンテナとして機能する導電層105で構成される。また、記憶素子を有する領域104は、制御回路、インターフェイス等を構成する複数のTFTを含む領域103と、図示しないが導電性粒子で接続されている。また、及びアンテナとして機能する導電層105は、通信回路を構成する複数のTFTを含む領域102と、図示しないが接着層の導電性粒子で接続されている。

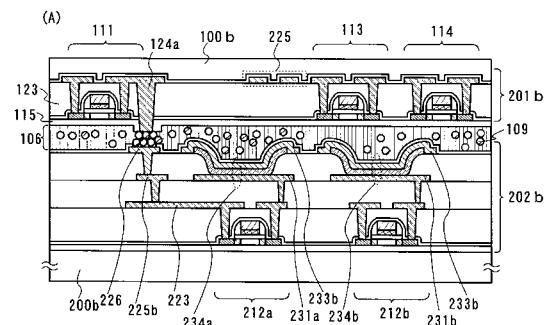

【0192】

上記の図26(C)に示す構成を有する本発明の半導体装置の断面構造について、図29を用いて説明する。

【0193】

図29(A)に示すように、複数のTFTを有する素子形成層301bは、TFT111、113、114を有し、これらのTFTの構造は上述した通りである。また、基板300b上に記憶素子334及びアンテナとして機能する導電層325を有する素子形成層302bが形成されている。図29(A)においては、記憶素子334に、スイッチング用のTFT312が接続されている。即ち、スイッチング用のTFT312のソース配線

10

20

20

30

40

50

又はドレイン配線として機能する導電層 324 の一方に、記憶素子 334 の第1の導電層が接続されており、アクティブマトリクス型の記憶回路を構成する。

【0194】

また、スイッチング用の TFT312 のソース配線又はドレイン配線の他方は、記憶素子の第1の導電層又は第2の導電層と同時に形成された導電層と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層 324 の他方は、導電層 225b を介して導電層 326 と接続している。なお、導電層 225b は、記憶素子の第1の導電層と同時に形成された導電層であり、導電層 326 は、記憶素子の第2の導電層と同時に形成された導電層であり、接続端子として機能する。

【0195】

また、複数の TFT を有する素子形成層 301b の裏面と、記憶素子及びアンテナを有する素子形成層 302b とは、導電性粒子 109 を有する接着層 106 で貼り合わせられている。即ち、絶縁層 115 と、記憶素子及びアンテナを有する素子形成層 302b とは、導電性粒子 109 を有する接着層 106 で貼り合わせられている。また、TFT113 のソース配線又はドレイン配線として機能する導電層 124c は裏面で露出されている。よって、TFT111 のソース配線又はドレイン配線として機能する導電層 124a は、導電性粒子 109 を介して、アンテナとして機能する導電層 325 と電気的に接続されている。

【0196】

また、記憶素子 334 の第1の導電層又は第2の導電層と同時に、アンテナとして機能する導電層 325 が形成される。導電層 325 は、TFT113 のソース配線又はドレイン配線として機能する導電層 124c と、導電性粒子 109 を介して電気的に接続される。なお、導電層 325 は導電層 326 と同時に形成される。

【0197】

なお、記憶素子の構成によつては、記憶素子 334 に対して、レーザ光を用いた光学的作用によりデータの書き込みを行う場合がある。そのような場合、記憶素子を有する素子形成層 302b において、スイッチング用の TFT312 及び記憶素子 334 、並びに導電層 325 及び記憶素子 434 が、重ならない領域を有するように、レイアウトをすることが必要である。

【0198】

図 29 (A) に示す記憶素子 334 は、スイッチング用の TFT312 が、各記憶素子に設けられた記憶素子を示す。なお、図 29 (B) に示すように、第1の導電層 351 、有機化合物層又は相変化層 352 、第2の導電層 353 で構成される記憶素子 354 及びアンテナとして機能する導電層 525 を有する基板 300b を貼り合わせることも可能である。

【0199】

また、複数のトランジスタを有する素子形成層 301b に記憶素子を動作させる回路を構成する TFT111 が形成されるが、これに限定される物ではない。記憶素子を有する素子形成層 302b に記憶素子を動作させる回路を構成する TFT が形成されてもよい。また、図 29 (A) において、記憶素子及びアンテナを有する素子形成層 302b は基板 300b 上に形成された構造を有しているが、基板 300b 上に接着層を介して記憶素子及びアンテナを有する素子形成層 302b を貼り合せてても良い。

【0200】

本発明の半導体装置は、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子及びアンテナを有する素子形成層を形成する工程を、独立に並行して行うことができる。従つて、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子、アンテナそれぞれが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子、アンテナを電気的に接続させ半導体装置を完成させることができる。従つて、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

10

20

30

40

50

## 【0201】

## (実施形態10)

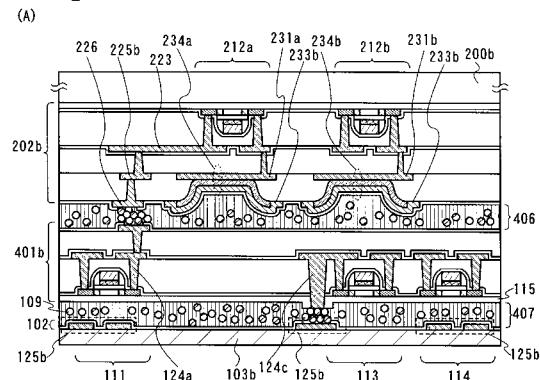

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について説明する。より詳しくは、複数のトランジスタを有する素子形成層401bを、アンテナが形成される基板及び記憶素子を有するが形成される基板で挟み込んだ構造の半導体装置の断面構造について、図26及び図30を用いて説明する。

## 【0202】

本実施形態の半導体装置は、図26(D)に示すように、基板108b上に形成されたアンテナとして機能する導電層を有する素子形成層107bと、基板200bに形成された記憶素子を有する素子形成層202bとを用いて、複数のトランジスタを有する素子形成層401bを挟み込んだ構造を有する。なお、複数のトランジスタを有する素子形成層401bと、アンテナとして機能する導電層を有する素子形成層202bとは、接着層で貼り合わせられており、複数のトランジスタを有する素子形成層401bと、アンテナとして機能する導電層を有する素子形成層107bとも接着層で貼り合わせられている。

## 【0203】

ここでは、複数のトランジスタを有する素子形成層401bは、代表的には複数のTFTを有する領域102、103を有する。また、記憶素子を有する素子形成層202bは、記憶素子を有する領域104で構成される。また、記憶素子を有する領域104は、制御回路、インターフェイス等を構成する複数のTFTを含む領域103と、図示しないが接着層中の導電性粒子で接続されている。

## 【0204】

また、アンテナとして機能する導電層105は、通信回路を構成する複数のTFTを含む領域102と、図示しないが接着層中の導電性粒子で接続されている。

## 【0205】

上記の図26(D)に示す構成を有する本発明の半導体装置の断面構造について、図30を用いて説明する。

## 【0206】

図30(A)に示すように、基板200b上に記憶素子を有する素子形成層202bが形成されている。複数のトランジスタを有する素子形成層401bと記憶素子を有する素子形成層202bは、導電性粒子109を有する接着層406で貼り合わせられている。また、複数のトランジスタを有する素子形成層401bは、TFT111、113、114を有し、これらのTFTの構造は上述した通りである。また、TFT111のソース配線又はドレイン配線として機能する導電層124aに接続する接続配線は、複数の薄膜トランジスタを有する素子形成層401bの表面に露出している。また、TFT111のソース配線又はドレイン配線として機能する導電層124cは、複数の薄膜トランジスタを有する素子形成層401bの裏面に露出している。

## 【0207】

図30(A)においては、記憶素子234a、234bそれぞれに、スイッチング用のTFT212a、212bが接続されている。即ち、スイッチング用のTFT212a、212bのソース配線又はドレイン配線の一方に記憶素子の第1の導電層231a、231bが接続されている。また、スイッチング用のTFT212a、212bのソース配線又はドレイン配線の他方は、記憶素子の第1の導電層又は第2の導電層と同時に形成された導電層225b、226と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層223の他方は、導電層225bを介して導電層226と接続している。

## 【0208】

また、記憶素子のスイッチング用のTFT212aのソース配線又はドレイン配線として機能する導電層223と、記憶素子を動作させる回路を構成するTFT111のソース配線又はドレイン配線として機能する導電層124aとは、導電性粒子109および導電層を介して電気的に接続されている。

10

20

30

40

50

## 【0209】

また、複数のトランジスタを有する素子形成層401bと、基板108bに形成された導電層125bを有する素子形成層107bは、導電性粒子109を含む接着層406により貼り合わせられている。また、TFT113のソース配線又はドレイン配線として機能する導電層124cは、アンテナとして機能する導電層125bと、接着層407中の導電性粒子109を介して電気的に接続されている。

## 【0210】

図30(A)に示す記憶素子234a、234bは、スイッチング用のTFT212a、212bが、設けられている。即ちアクティブマトリクス型記憶回路である。なお、図30(B)に示すように、第1の導電層251、有機化合物層又は相変化層252、第2の導電層253で構成される記憶素子254を有する基板を貼り合わせることも可能である。このような記憶素子はパッシブマトリクス型記憶回路を構成する。

## 【0211】

また、上記実施形態において、複数のトランジスタを有する素子形成層401bに記憶素子を動作させる回路が形成されるが、これに限定される物ではない。例えば、記憶素子を有する素子形成層202bに記憶素子を動作させる回路が形成されてもよい。

## 【0212】

また、図30(A)において、記憶素子を有する素子形成層202bは基板200bに形成された構造を有しているが、基板上に接着層を介して記憶素子を有する素子形成層202bを貼り合せても良い。

## 【0213】

本発明の半導体装置は、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子を有する素子形成層を形成する工程とアンテナとして機能する導電層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子、アンテナとして機能する導電層それが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子やアンテナとして機能する導電層を電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

## 【0214】

## (実施形態11)

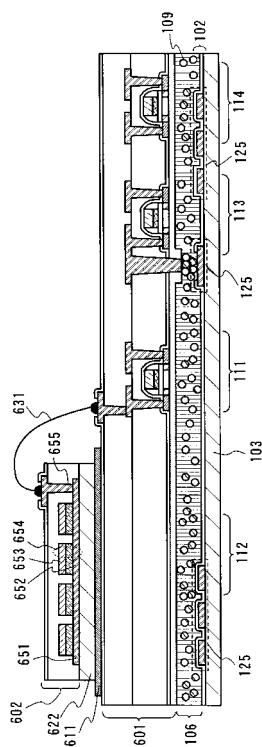

本実施形態では、上記実施形態の構成とは異なる本発明の半導体装置の断面構造について説明する。より詳しくは、アンテナとして機能する導電層を有する素子形成層107bを有する基板108b上に複数のトランジスタを有する素子形成層601bを設け、さらにその上に記憶素子を有する素子形成層602bを搭載した構造の半導体装置の断面構造について、図26及び図32を用いて説明する。

## 【0215】

本実施形態の半導体装置は、図26(E)に示すように複数のトランジスタを有する素子形成層601bとアンテナが形成された基板108bとが接着層で貼り合わせられた構成を有する。又、複数のトランジスタを有する素子形成層601b上に、記憶素子を有する素子形成層602bが、接着層で貼り合わせられた構成を有する。

## 【0216】

ここでは、複数のトランジスタを有する素子形成層601bは、代表的には複数のTFTを有する領域102、103及びアンテナとして機能する導電層105で構成される。また、記憶素子を有する素子形成層602は、記憶素子を有する領域104で構成される。また、記憶素子を有する領域104は、制御回路、インターフェイス等を構成する複数のTFTを含む領域103と、電気的に接続されている。

## 【0217】

上記の図26(E)に示す構成を有する本発明の半導体装置の断面構造について、図32を用いて説明する。

10

20

30

40

50

## 【0218】

図32に示すように、複数のTFTを有する素子形成層601bは、TFT111、113、114を有し、これらのTFTの構造は上述した通りである。また、記憶素子を有する素子形成層602bが形成された絶縁層621bが、絶縁層615上に接着層611を用いて搭載されている。

## 【0219】

また、複数のトランジスタを有する素子形成層601bとアンテナを有する素子形成層107bは接着層106で貼り合わせられている。具体的には、絶縁層115とアンテナを有する素子形成層107bは接着層106で貼り合わせられている。また、複数のトランジスタを有する素子形成層601bのTFT113のソース配線又はドレイン配線として機能する導電層124cと、素子形成層107bのアンテナとして機能する導電層125bは、接着層106の導電性粒子109を介して電気的に接続されている。

10

## 【0220】

図32においては、記憶素子634に、スイッチング用のTFT112が接続されている。即ち、スイッチング用のTFT112のソース配線又はドレイン配線の一方に、記憶素子634の第1の導電層が接続されている。また、スイッチング用のTFT112のソース配線又はドレイン配線の他方は、記憶素子の第1の導電層又は第2の導電層と同時に形成された導電層と接続されている。ここでは、ソース配線又はドレイン配線として機能する導電層124bの他方は、導電層625を介して導電層626と接続している。なお、導電層625は、記憶素子の第1の導電層と同時に形成された導電層であり、導電層626は、記憶素子の第2の導電層と同時に形成された導電層であり、接続端子として機能する。

20

## 【0221】

また、記憶素子を有する素子形成層602に形成された記憶素子634のスイッチング用のTFT112と、複数のTFTを有する素子形成層601bに形成された記憶素子を動作させる回路を構成するTFT111とが、導電部材631で電気的に接続されている。

## 【0222】

図32に示す記憶素子634は、スイッチング用のTFT112が、各記憶素子に設けられた記憶素子を示す。なお、図33に示すように、TFTを有する記憶素子の代わりに、第1の導電層651、有機化合物層又は相変化層652、第2の導電層653で構成される記憶素子654が形成される基板622を、接着層611を用いて基板103b上に搭載することも可能である。

30

## 【0223】

また、本実施形態では、記憶素子を有する素子形成層602を素子形成層601上に搭載したが、これに限定されず、記憶素子及びアンテナを有する素子形成層や、アンテナを有する素子形成層を素子形成層601上に搭載しても良い。

## 【0224】

本発明の半導体装置は、複数のTFTを有する素子形成層上に、記憶素子を含む層を積層した構成を有することを特徴とし、上記特徴により、小型の半導体装置を提供することができる。また、複数のトランジスタを有する素子形成層を形成する工程と、記憶素子を有する素子形成層を形成する工程、アンテナとして機能する導電層を形成する工程を、独立に並行して行うことができる。従って、本発明は短時間で効率よく半導体装置を作製することができる。また、複数のトランジスタを有する素子形成層や、記憶素子、アンテナとして機能する導電層それが形成された時点で、それぞれの性能を確認し、選別して、複数のトランジスタを有する素子形成層や記憶素子を電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

40

## 【0225】

(実施形態12)

50

本実施形態では、半導体装置の作製方法に関して図面を参照して説明する。ここでは、実施形態7の図27(A)で示す半導体装置の作製方法を示すが、各実施形態に示される半導体装置にそれぞれ、本実施形態を適宜適応することが可能である。

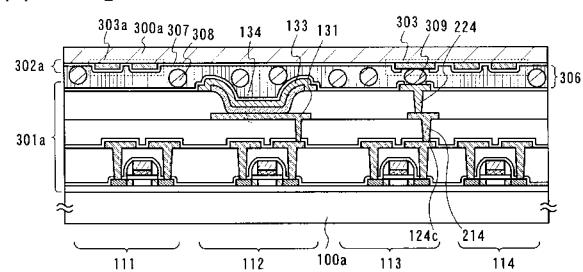

【0226】

図34(A)に示すように、実施の形態6と同様に、基板1100の一表面に、剥離層1101、1102を形成する。

【0227】

次に、図34(B)に示すように、実施の形態6と同様に、剥離層1101、1102を覆うように、下地となる絶縁層1105を形成する。次に、絶縁層1105上に、非晶質半導体層を形成した後、非晶質半導体層を公知の結晶化法により結晶化して、結晶質半導体層を形成する。その後、得られた結晶質半導体層を所望の形状にエッチングして結晶質半導体層1127～1130を形成する。次に、結晶質半導体層1127～1130を覆うゲート絶縁層を形成する。次に、ゲート絶縁層上に、第1の導電層と第2の導電層を積層して形成する。次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極を形成するためのエッチング処理を行って、導電層1107～1110を形成する。次に、結晶質半導体層1127～1130に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、N型不純物領域を形成する。次に、絶縁層と導電層1107～1110を覆うように、絶縁層1141を形成する。

10

【0228】

次に、実施の形態6と同様に、絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層1107～1110の側面に接するサイドウォール絶縁層1115～1118を形成する。なお、サイドウォール絶縁層1115～1118を形成するためのエッチング工程により、絶縁層もエッチングされ、ゲート絶縁層1119～1122が形成される。続いて、サイドウォール絶縁層1115～1118をマスクとして、結晶質半導体層1127～1130にN型を付与する不純物元素を添加して、第1のN型不純物領域(LDD領域ともよぶ)1123a～1123dと、第2のN型不純物領域(ソース領域及びドレイン領域ともよぶ)1124a～1124dとを形成する。第1のN型不純物領域1123a～1123dが含む不純物元素の濃度は、第2のN型不純物領域1124a～1124dの不純物元素の濃度よりも低い。

20

【0229】

上記工程を経て、n型のTFT1131～1134が完成する。

30

【0230】

次に、TFT1131～1134を覆うように、単層又は積層で絶縁層1142を形成する。

【0231】

次に、図34(C)に示すように、実施の形態6と同様に、フォトリソグラフィ法により絶縁層1141、1142をエッチングして、N型不純物領域1124a～1124dを露出させるコンタクトホール1143～1150を形成する。このときコンタクトホール1151は、絶縁層1141、1142とともに、絶縁層1105をもエッチングして、基板1100の一部を露出させる。

40

【0232】

次に、図34(D)に示すように、コンタクトホール1143～1151を充填するように、導電層を形成し、当該導電層をパターン加工して、導電層1155～1162を形成する。導電層1155～1162は、TFTのソース配線又はドレイン配線として機能する。また導電層1159は基板表面にまで達している。また、導電層1159は、剥離層1101、1102に接しておらず、絶縁層1105、1141、1142に接する。これは、剥離層1101、1102をエッチング剤により除去する際に、導電層1159がエッチング剤により除去されないようにするためである。

【0233】

次に、図34(E)に示すように、実施の形態6と同様に、導電層1155～1162

50

を覆うように、単層又は積層で絶縁層 1163 を形成する。導電層 1154 ~ 1162 を覆う絶縁層 1163 は、薄膜トランジスタを覆う絶縁層 1142 と同様の手法及び材料を用いて形成することができる。次に、導電層 1154 ~ 1162 を覆う絶縁層 1163 にコンタクトホールを形成し、導電層 1164 を形成する。導電層 1164 は、後に形成される記憶素子の第 1 の導電層として機能する。

【0234】

次に、導電層 1164 の端部を覆うように絶縁層 1165 を形成した後、有機化合物層又は相変化層 1166、導電層 1167 を形成する。導電層 1164、有機化合物層又は相変化層 1166、及び導電層 1167 で記憶素子 1169 を構成する。導電層 1164 は、記憶素子 1169 の第 2 の導電層として機能する。この後、絶縁層 1168 を形成してもよい。10

【0235】

次に、図 35 (A) に示すように、実施の形態 6 と同様に、剥離層 1101、1102 が露出するように、フォトリソグラフィ法により絶縁層 1105、1141、1142、1163、1168 をエッティングして、開口部 1171、1172 を形成する。

【0236】

次に、図 35 (B) に示すように、実施の形態 6 と同様に、開口部 1171、1172 にエッティング剤を導入して、剥離層 1101、1102 を除去する。

【0237】

次に、図 35 (C) に示すように、実施の形態 6 と同様に、複数のトランジスタを有する素子形成層 1170 において記憶素子が形成されている面を、基体 1181 に接着させて、複数のトランジスタを有する素子形成層 1170 と基体 1181 を接着させた後、複数のトランジスタを有する素子形成層 1170 を基板 1100 から完全に剥離する（図 36 (A) の断面図参照）。20

【0238】

次に、図 36 (B) に示すように、実施の形態 6 と同様に、複数のトランジスタを有する素子形成層 1170 の他方の面を、導電層 1182 が設けられた基板 1183 に接着させる。この際、導電性粒子 1900 を含む接着層 1191 を用いて接着する。また、TFT 1133 のソース配線又はドレイン配線として機能する導電層 1159 と、基板 1183 b 上の導電層 1182 b とが、導電性粒子 1190 で接するように、複数のトランジスタを有する素子形成層 1170 と基板 1183 b とを接着させる。30

【0239】

次に、複数のトランジスタを有する素子形成層 1170 と基体 1181、1183 b とが接着したものを、スライシング装置やレーザ照射装置等を用いて分断する。

【0240】

上記工程を経て、非接触でデータを交信する機能を有する半導体装置が完成する。

【0241】

また、本実施形態では、複数のトランジスタを有する素子形成層 1170 と、導電層を有する基板 1183 b とを接着させた後、分断して半導体装置を形成しているが、この工程に限定されない。複数のトランジスタを有する素子形成層 1170 と基体 1181 を接着し、分断した後、複数のトランジスタを有する素子形成層 1170 に、導電層 1182 を有する基板 1183 b を接着してもよい。40

【0242】

このように、本発明の半導体装置は、小型、薄型、軽量であり、フレキシブル性を有するため、多種多様の用途が実現し、物品に貼り付けても、その物品のデザイン性を損なうことがない。

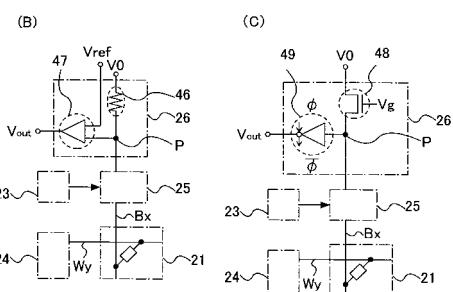

【0243】

(実施形態 13)

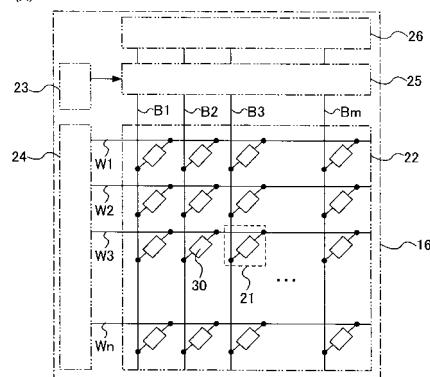

次に、本発明の半導体装置が有する記憶回路の構成とその動作について図面を参照して説明する。本発明の記憶回路は、メモリセル 21 がマトリクス状に設けられたメモリセル

アレイ 22 と、デコーダ 23、24 と、セレクタ 25 と、読み出し / 書き込み回路 26 を有する。メモリセル 21 は、記憶素子 30 を有する（図 12（A）参照）。

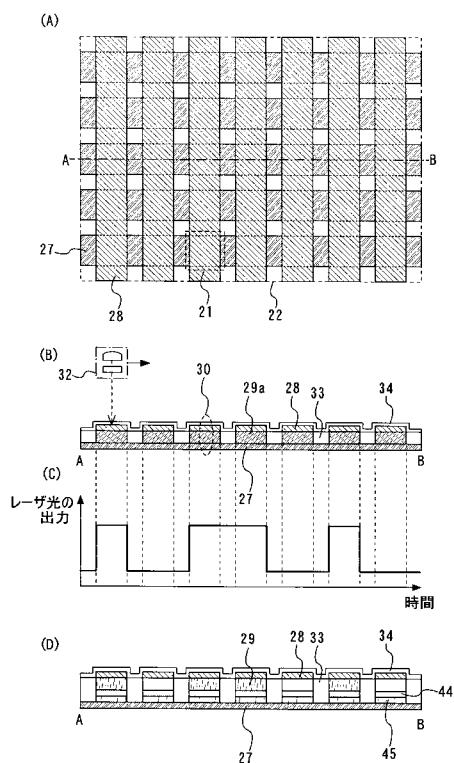

【0244】

記憶素子 30 は、ワード線  $W_y$  ( $1 \times n$ ) を構成する第 1 の導電層 27 と、ビット線  $B_x$  ( $1 \times m$ ) を構成する第 2 の導電層 28 と、第 1 の導電層 27 と、第 2 の導電層 28 の間に設けられた有機化合物層又は相変化層 29a を有する（図 13（A）参照）。図 13B に示すように、隣接する有機化合物層又は相変化層 29a の間には、絶縁層 33 が設けられる。また、記憶素子 30 上に、絶縁層 34 が設けられる。ワード線  $W_y$  を構成する第 1 の導電層 27 は、第 1 の方向に延在して設けられ、ビット線  $B_x$  を構成する第 2 の導電層 28 は、第 1 の方向と垂直な第 2 の方向に延在して設けられる。つまり、第 1 の導電層 27 と第 2 の導電層 28 はストライプ状に、互いに交差するように設けられる。

【0245】

なお、有機化合物層又は相変化層 29a の構成によっては、記憶素子 30 に対するデータの書き込みを光学的作用により行う場合がある。その場合、第 1 の導電層 27 と第 2 の導電層 28 のうち、一方又は両方は透光性を有することが必要である。透光性を有する導電層は、インジウム錫酸化物（ITO）等の透明な導電性材料を用いて形成するか、又は、透明な導電性材料でなくても、光を透過する厚さで形成する。

【0246】

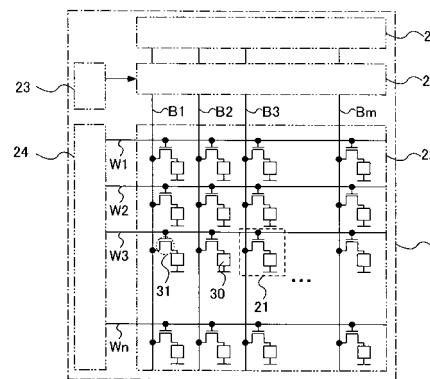

また、図 12（A）に示す等価回路図は、パッシブ型の場合であるが、メモリセル 21 にトランジスタ 31 を設けたアクティブ型を採用してもよい（図 14 参照）。その場合、スイッチング用のトランジスタ 31 のゲート電極はワード線  $W_y$  ( $1 \times n$ ) に接続され、ソース電極及びドレイン電極の一方はビット線  $B_x$  ( $1 \times m$ ) に接続され、ソース電極及びドレイン電極の他方は、記憶素子 30 の一方の導電層に接続する。

【0247】

有機化合物層又は相変化層 29a の代表例の一つとして、有機化合物材料が挙げられる。以下、有機化合物材料で形成される層を有機化合物層と示す。

【0248】

有機化合物層の代表的例としては、4、4' - ビス [ N - (1 - ナフチル) - N - フェニルアミノ ] - ビフェニル（略称：-NPD）や4, 4' - ビス [ N - (3 - メチルフェニル) - N - フェニルアミノ ] - ビフェニル（略称：TPD）や4, 4', 4''' - トリス (N, N - ジフェニルアミノ) - トリフェニルアミン（略称：TDATA）、4, 4', 4''' - トリス [ N - (3 - メチルフェニル) - N - フェニルアミノ ] - トリフェニルアミン（略称：MTDATA）や4, 4' - ビス (N - (4 - (N, N - ジ - m - トリルアミノ) フェニル) - N - フェニルアミノ) ビフェニル（略称：DNTPD）などの芳香族アミン系（即ち、ベンゼン環 - 窒素の結合を有する）の化合物やフタロシアニン（略称：H<sub>2</sub>Pc）、銅フタロシアニン（略称：CuPc）、バナジルフタロシアニン（略称：VOPc）等のフタロシアニン化合物等の正孔輸送性の高い物質を用いることができる。

【0249】

また、他にも有機化合物材料として、電子輸送性が高い材料を用いることができ、例えばトリス (8 - キノリノラト) アルミニウム（略称：Alq<sub>3</sub>）、トリス (4 - メチル - 8 - キノリノラト) アルミニウム（略称：Almq<sub>3</sub>）、ビス (10 - ヒドロキシベンゾ [h] - キノリナト) ベリリウム（略称：BeBq<sub>2</sub>）、ビス (2 - メチル - 8 - キノリノラト) - 4 - フェニルフェノラト - アルミニウム（略称：BA1q）等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料や、ビス [2 - (2 - ヒドロキシフェニル) ベンゾオキサゾラト] 亜鉛（略称：Zn (BOX)<sub>2</sub>）、ビス [2 - (2 - ヒドロキシフェニル) ベンゾチアゾラト] 亜鉛（略称：Zn (BTZ)<sub>2</sub>）などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2 - (4 - ビフェニリル) - 5 - (4 - tert - プチルフェニ

10

20

30

40

50

ル) - 1 , 3 , 4 - オキサジアゾール(略称: P B D)、1 , 3 - ビス[5 - (p - t e r t - ブチルフェニル) - 1 , 3 , 4 - オキサジアゾール - 2 - イル]ベンゼン(略称: O X D - 7)、3 - (4 - t e r t - ブチルフェニル) - 4 - フェニル - 5 - (4 - ビフェニリル) - 1 , 2 , 4 - トリアゾール(略称: T A Z)、3 - (4 - t e r t - ブチルフェニル) - 4 - (4 - エチルフェニル) - 5 - (4 - ビフェニリル) - 1 , 2 , 4 - トリアゾール(略称: p - E t T A Z)、バソフェナントロリン(略称: B P h e n)、バソキュプロイン(略称: B C P)等の化合物等を用いることができる。

### 【0250】

また、他にも有機化合物材料として、4 - ジシアノメチレン - 2 - メチル - 6 - (1 , 1 , 7 , 7 - テトラメチルジュロリジル - 9 - エニル) - 4 H - ピラン(略称: D C J T 10)、4 - ジシアノメチレン - 2 - t - ブチル - 6 - (1 , 1 , 7 , 7 - テトラメチルジュロリジル - 9 - エニル) - 4 H - ピラン、ペリフランテン、2 , 5 - ジシアノ - 1 , 4 - ビス(10 - メトキシ - 1 , 1 , 7 , 7 - テトラメチルジュロリジル - 9 - エニル)ベンゼン、N , N ' - ジメチルキナクリドン(略称: D M Q d)、クマリン6、クマリン545 T、トリス(8 - キノリノラト)アルミニウム(略称: A l q<sub>3</sub>)、9 , 9 ' - ビアントリル、9 , 10 - ジフェニルアントラセン(略称: D P A)や9 , 10 - ビス(2 - ナフチル)アントラセン(略称: D N A)、2 , 5 , 8 , 11 - テトラ - t - ブチルペリレン(略称: T B P)等が挙げられる。また、上記発光材料を分散してなる層を形成する場合に母体となる材料としては、9 , 10 - ジ(2 - ナフチル) - 2 - t e r t - ブチルアントラセン(略称: t - B u D N A)等のアントラセン誘導体、4 , 4 ' - ビス(N - カルバゾリル)ビフェニル(略称: C B P)等のカルバゾール誘導体、ビス[2 - (2 - ヒドロキシフェニル)ピリジナト]亜鉛(略称: Z n p p<sub>2</sub>)、ビス[2 - (2 - ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称: Z n B O X)などの金属錯体等を用いることができる。また、トリス(8 - キノリノラト)アルミニウム(略称: A l q<sub>3</sub>)、9 , 10 - ビス(2 - ナフチル)アントラセン(略称: D N A)、ビス(2 - メチル - 8 - キノリノラト) - 4 - フェニルフェノラト - アルミニウム(略称: B A l q)等を用いることができる。

### 【0251】

また、上記有機化合物に、酸化物半導体又は金属酸化物が添加されてもよい。酸化物半導体又は金属酸化物の具体例としては、モリブデン酸化物(M o O<sub>x</sub>)、バナジウム酸化物(V O<sub>x</sub>)、ルテニウム酸化物(R u O<sub>x</sub>)、タンゲステン酸化物(W O<sub>x</sub>)、コバルト酸化物(C o<sub>x</sub>)、ニッケル酸化物(N i O<sub>x</sub>)、銅酸化物(C u O<sub>x</sub>)等が挙げられる。この他、インジウム錫酸化物(I T O)や亜鉛酸化物(Z n O)等を用いることができる。

### 【0252】

また、有機化合物層には、光学的作用により、電気抵抗が変化する材料を用いることができる。例えば、光を吸収することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いることができる。共役高分子として、ポリアセチレン類、ポリフェニレンビニレン類、ポリチオフェン類、ポリアニリン類、ポリフェニレンエチレン類等を用いることができる。また、光酸発生剤としては、アリールスルホニウム塩、アリールヨードニウム塩、o - ニトロベンジルトシレート、アリールスルホン酸p - ニトロベンジルエステル、スルホニルアセトフェノン類、F e - アレン錯体P F<sub>6</sub>塩等を用いることができる。

### 【0253】

次に、上記構成を有する記憶回路にデータの書き込みを行う際の動作について説明する。データの書き込みは、光学的作用又は電気的作用により行う。なお、光学的作用とは、外部から光を照射することであり、電気的作用とは記憶素子の第1の導電層及び第2の導電層に所定以上の電圧を印加することである。

### 【0254】

メモリセル21にデータ「1」を書き込む場合、まず、デコーダ23、24およびセレク

10

20

30

40

50

タ25によってメモリセル21を選択する。具体的には、デコーダ24によって、メモリセル21に接続されるワード線W3に所定の電圧V2を印加する。また、デコーダ23とセレクタ25によって、メモリセル21に接続されるビット線B3を読み出し/書き込み回路26に接続する。そして、読み出し/書き込み回路26からビット線B3へ書き込み電圧V1を出力する。こうして、当該メモリセル21を構成する第1の導電層と第2の導電層の間には電圧Vw=V1-V2を印加する。電位Vwを適切に選ぶことで、当該導電層間に設けられた有機化合物層又は相変化層29を物理的もしくは電気的变化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の導電層と第2の導電層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよい。例えば、(V1、V2)=(0V、5~15V)あるいは(3~5V、-12~-2V)の範囲から適宜選べば良い。電圧Vwは5~15V、あるいは-5~-15Vとすればよい。

10

## 【0255】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。例えば、非選択のワード線および非選択のビット線を浮遊状態とすればよい。メモリセルを構成する第1の導電層と第2の導電層の間は、ダイオード特性など、選択性を確保できる特性を有する必要がある。

## 【0256】

一方、メモリセル21にデータ「0」を書き込む場合は、メモリセル21には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ23、24およびセレクタ25によってメモリセル21を選択するが、読み出し/書き込み回路26からビット線B3への出力電位を、選択されたワード線W3の電位あるいは非選択ワード線の電位と同程度とし、メモリセル21を構成する第1の導電層と第2の導電層の間に、メモリセル21の電気特性を変化させない程度の電圧(例えば-5~5V)を印加すればよい。

20

## 【0257】

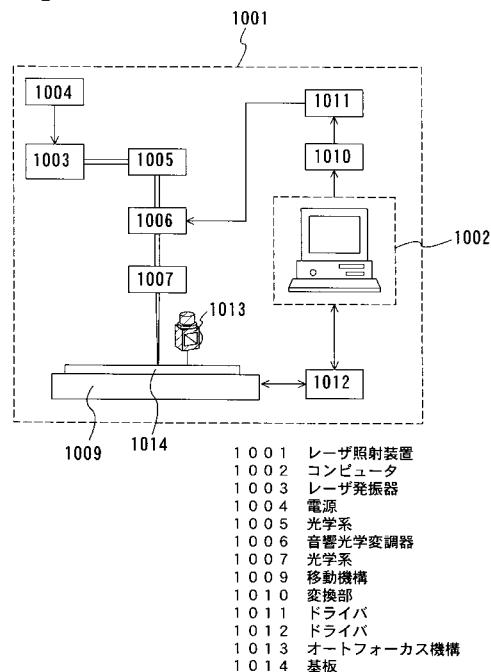

次に、光学的作用によりデータの書き込みを行う場合について説明する(図13(B)参照)。この場合、透光性を有する導電層側(ここでは第2の導電層28とする)から、レーザ照射装置32により、有機化合物層にレーザ光を照射することにより、データの書き込みを行う。より詳しくは、選択された記憶素子30が含む有機化合物層にレーザ光を照射して、有機化合物層を破壊する。破壊された有機化合物層は、絶縁化し、他の記憶素子30と比較すると抵抗値が大幅に大きくなる。このように、レーザ光の照射により、記憶素子30の電気抵抗が変化することを利用してデータの書き込みを行う。例えば、レーザ光を照射していない記憶素子30を「0」のデータとする場合、記憶素子30にレーザ光を照射して破壊することによって電気抵抗を大きくして「1」のデータを書き込むことが可能である。

30

## 【0258】

なお、本発明は、記憶素子30にレーザ光を照射して、有機化合物層を絶縁化することによりデータを書き込む形態に制約されず、記憶素子30の素子構造やレーザ光の強度を調整することにより、記憶素子30にレーザ光を照射して、有機化合物層を絶縁破壊して、記憶素子30の抵抗値を変化させることによりデータを書き込んでもよい。この場合、一対の導電層を短絡させた記憶素子30は、他の記憶素子30と比較すると、抵抗値が大幅に低くなる。このように、光学的作用を加えることにより、記憶素子30の抵抗値が変化することを利用してデータの書き込みを行ってもよい。

40

## 【0259】

また、有機化合物層として、光を吸収することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いた場合、レーザ光を照射すると、照射された部分の電気抵抗値が変化し、未照射の部分は電気抵抗値が変化しない。この場合も、選択された有機化合物層にレーザ光を照射することにより、記憶素子30の抵抗値が変化することを利用してデータの書き込みを行う。例えば、レーザ光を照射していない記憶素子30を「0

50

」のデータとする場合、選択された記憶素子30にレーザ光を照射して電気抵抗値を変化させて「1」のデータを書き込むことが可能である。

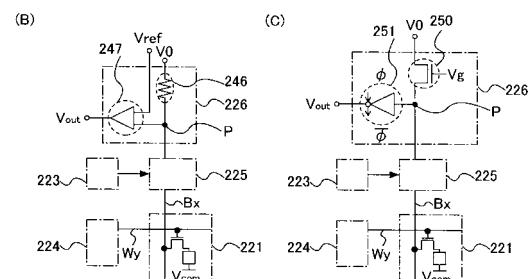

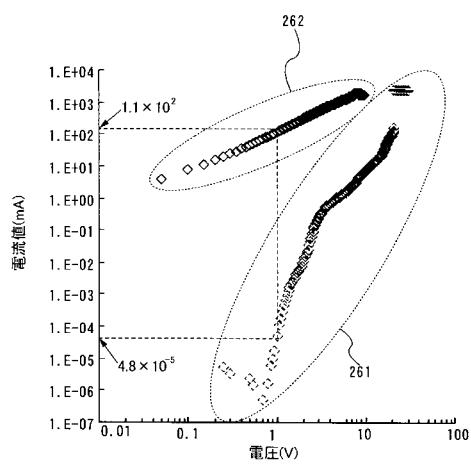

#### 【0260】

続いて、データの読み出しを行う際の動作について説明する(図12参照)。データの読み出しは、メモリセルを構成する第1の導電層と第2の導電層の間の電気特性が、データ「0」を有するメモリセルとデータ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する第1の導電層と第2の導電層の間の実効的な電気抵抗(以下、単にメモリセルの電気抵抗と呼ぶ)が、読み出し電圧において $R_0$ 、データ「1」を有するメモリセルの電気抵抗を、読み出し電圧において $R_1$ とし、電気抵抗の差を利用して読み出す方法を説明する。なお、 $R_1 < < R_0$ とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図12(B)に示す抵抗素子46と差動増幅器47を用いた回路26を考えることができる。抵抗素子46は抵抗値 $R_r$ を有し、 $R_1 < R_r < R_0$ であるとする。抵抗素子46の代わりにトランジスタ48を用いても良いし、差動増幅器の代わりにクロックドインバータ49を用いることも可能である(図12(C))。クロックドインバータ49には、読み出しを行うときに $H_i$ 、行わないときに $L_o$ となる、信号又は反転信号が入力される。勿論、回路構成は図12に限定されない。

10

#### 【0261】

メモリセル21からデータの読み出しを行う場合、まず、デコーダ23、24およびセレクタ25によってメモリセル21を選択する。具体的には、デコーダ24によって、メモリセル21に接続されるワード線 $W_y$ に所定の電圧 $V_y$ を印加する。また、デコーダ23とセレクタ25によって、メモリセル21に接続されるピット線 $B_x$ を読み出し/書き込み回路26の端子Pに接続する。その結果、端子Pの電位 $V_p$ は、抵抗素子46(抵抗値 $R_r$ )とメモリセル21(抵抗値 $R_0$ もしくは $R_1$ )による抵抗分割によって決定される値となる。従って、メモリセル21がデータ「0」を有する場合には、 $V_p0 = V_y + (V_0 - V_y) \times R_0 / (R_0 + R_r)$ となる。また、メモリセル21がデータ「1」を有する場合には、 $V_p1 = V_y + (V_0 - V_y) \times R_1 / (R_1 + R_r)$ となる。その結果、図12(B)では、 $V_{ref}$ を $V_p0$ と $V_p1$ の間となるように選択することで、図12(C)では、クロックドインバータの変化点を $V_p0$ と $V_p1$ の間となるように選択することで、出力電位 $V_{out}$ として、データ「0」/「1」に応じて、 $L_o$ /  $H_i$ (もしくは $H_i$ /  $L_o$ )が出力され、読み出しを行うことができる。

20

#### 【0262】

例えば、差動増幅器を $V_{dd} = 3V$ で動作させ、 $V_y = 0V$ 、 $V_0 = 3V$ 、 $V_{ref} = 1.5V$ とする。仮に、 $R_0 / R_r = R_r / R_1 = 9$ とすると、メモリセルのデータが「0」の場合、 $V_p0 = 2.7V$ となり $V_{out}$ は $H_i$ が出力され、メモリセルのデータが「1」の場合、 $V_p1 = 0.3V$ となり $V_{out}$ は $L_o$ が出力される。こうして、メモリセルの読み出しを行うことができる。

30

#### 【0263】

上記の方法によると、有機化合物層又は相変化層29の電気抵抗の状態は、抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

40

#### 【0264】

また、有機化合物層にレーザ光を照射することによりデータの書き込みを行った場合も同様であり、光学作用を加えていない記憶素子30の抵抗値と、光学的作用を加えた記憶素子30の抵抗値の相違を電気的に読み取ることにより、データの読み出しを行う。

#### 【0265】

また、有機化合物層に、光を吸収することによって酸を発生する化合物(光酸発生剤)

50

をドープした共役高分子を用いた場合も同様であり、光学的作用を加えていない記憶素子30の抵抗値と、光学的作用を加えた記憶素子の抵抗値の相違を電気的に読み取ることにより、データの読み出しを行う。

#### 【0266】

また、有機化合物層又は相変化層29の代表例の一つとして、相変化層を用いてもよい。ここでは、相変化層とは、結晶状態と非晶質状態の間で可逆的に変化する材料、相変化層は第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料、又は、非晶質状態から結晶状態にのみ変化する材料が挙げられる。このような材料で形成される層という。

#### 【0267】

なお、可逆的な材料を用いる場合、データの読み出しとデータの書き込みを行うことができる。一方、不可逆的な材料を用いる場合は、データの読み出しあしか行うことができない。このように、材料の種類によっては、相変化メモリは、読み出し専用メモリ又は読み出し／書き込みメモリになりうるため、半導体装置の用途に従って、相変化層に用いる材料を適宜選択する。

#### 【0268】

相変化層において、結晶状態と非晶質状態の間で可逆的に変化する材料とは、ゲルマニウム(Ge)、テルル(Se)、アンチモン(Sb)、硫黄(S)、酸化テルル(SeO<sub>x</sub>)、Sn(スズ)、金(Au)、ガリウム(Ga)、セレン(Se)、インジウム(In)、タリウム(Tl)、Co(コバルト)及び銀(Ag)から選択された複数を有する材料であり、例えば、Ge-Te-Sb-S、Te-TeO<sub>2</sub>-Ge-Sn、Te-Ge-Sn-Au、Ge-Te-Sn、Sn-Se-Te、Sb-Se-Te、Sb-Se、Ga-Se-Te、Ga-Se-Te-Ge、In-Se、In-Se-Tl-Co、Ge-Sb-Te、In-Se-Te、Ag-In-Sb-Te系材料が挙げられる。

#### 【0269】

相変化層において、第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料とは、銀(Ag)、亜鉛(Zn)、銅(Cu)、アルミニウム(Al)、ニッケル(Ni)、インジウム(In)、アンチモン(Sb)、セレン(Se)及びテルル(Se)から選択された複数を有する材料であり、例えば、Te-TeO<sub>2</sub>、Te-TeO<sub>2</sub>-Pd、Sb<sub>2</sub>Se<sub>3</sub>/Bi<sub>2</sub>Te<sub>3</sub>が挙げられる。この材料の場合、相変化は2つの異なる結晶状態の間で行われる。

#### 【0270】

相変化層において、非晶質状態から結晶状態にのみ変化する材料とは、テルル(Se)、酸化テルル(SeO<sub>x</sub>)、アンチモン(Sb)、セレン(Se)及びビスマス(Bi)から選択された複数を有する材料であり、例えば、Ag-Zn、Cu-Al-Ni、In-Sb、In-Sb-Se、In-Sb-Teが挙げられる。

#### 【0271】

一対の導電層間に相変化材料を有する単純な構成を有する記憶素子は、作製工程が単純であり、安価な半導体装置の提供を可能とする。また、相変化メモリは、不揮発性メモリであるため、データを保持するための電池を内蔵する必要がなく、小型、薄型、軽量の半導体装置の提供を実現する。また、相変化層として不可逆的な材料を用いれば、データの書き換えを行うことはできない。そうすると、偽造を防止し、セキュリティを確保した半導体装置を提供することができる。

#### 【0272】

次に、相変化層を有する記憶素子にデータの書き込みを行う際の動作について説明する。有機化合物層を用いた記憶素子と同様に、第1の導電層27と第2の導電層28の間に電圧を印加して、相変化材料の相を変えることにより、データの書き込みを行う。

#### 【0273】

次に、光によりデータの書き込みを行う場合について説明する(図13(B)参照)。この場合、透光性を有する導電層側(ここでは第2の導電層28とする)から、相変化層にレーザ光を照射することにより行う。相変化層は、レーザ光の照射により、その構造に

10

20

30

40

50

結晶学的な相変化が起こる。このように、レーザ光の照射により、相変化層の相が変わることを活用して、データの書き込みを行う。

【0274】

例えば、「1」のデータを書き込む際は、相変化層にレーザ光を照射して、結晶化温度以上に加熱した後、徐冷することにより、相変化層を結晶状態にする。一方、「0」のデータを書き込む際は、相変化層にレーザ光を照射して、融点以上に加熱昇温して溶融した後に急冷することにより、相変化層を非晶質状態にする。

【0275】

相変化層の相の変化は、メモリセル21の大きさによるが、 $\mu\text{m}$ オーダの径に絞ったレーザ光の照射により実現する。例えば、径が $1\mu\text{m}$ のレーザビームが $10\text{m/s sec}$ の速度で通過するとき、1つのメモリセル21が含む相変化層にレーザ光が照射される時間は $100\text{nsec}$ となる。 $100\text{nsec}$ という短い時間内で相を変化させるためには、レーザパワーは例えば $10\text{mW}$ 、パワー密度は $10\text{kW/mm}^2$ とするとよい。

【0276】

なお、相変化層に対するレーザ光の照射は、全てのメモリセル21に対して行ってもよいし、選択的に行ってもよい。例えば、形成したばかりの相変化層が非晶質状態の場合、非晶質状態のままにするときはレーザ光を照射せず、結晶状態に変化させるとときはレーザ光を照射するとよい。つまり、レーザ光を選択的に照射することで、データの書き込みを行ってもよい。このように、レーザ光を選択的に照射する場合は、パルス発振のレーザ照射装置を用いて行うとよい。

【0277】

上記の通り、レーザ光の照射によりデータの書き込みを行う本発明の構成は、半導体装置を簡単に大量に作成することができる。従って、安価な半導体装置を提供することができる。

【0278】

続いて、相変化層を有する記憶素子にデータの読み出しを行う際の動作は、有機化合物層を有する記憶素子と同様であり、相変化層の相状態に伴う抵抗変化から、電圧または電流の変化を読み取ることができる。

【0279】

また、上記構成とは異なる構成として、第1の導電層27と有機化合物層又は相変化層29aの間、もしくは第2の導電層28と有機化合物又は相変化層29の間に、整流性を有する素子を設けてもよい(図13(C)参照)。整流性を有する素子とは、代表的には、ショットキーダイオード、PN接合を有するダイオード、PIN接合を有するダイオード、あるいはゲート電極とドレイン電極を接続したトランジスタである。もちろん、他の構成のダイオードでも構わない。ここでは、第1の導電層と有機化合物を含む層の間に、半導体層44、45を含むPN接合ダイオードを設けた場合を示す。半導体層44、45のうち、一方は一方はN型半導体であり、他方はP型半導体である。このように整流作用を有する素子を設けることにより、メモリセルの選択性を向上し、読み出しや書き込みの動作マージンを向上させることができる。

【0280】

上記の通り、本発明の半導体装置が含む記憶回路は、一対の導電層間に有機化合物層又は相変化層が挟まれた単純な構造の記憶素子を有することを特徴とし、上記特徴により、作製が簡単であるために安価な半導体装置及びその作製方法を提供することができる。また、高集積化が容易なため、大容量の記憶回路を有する半導体装置及びその作製方法を提供することができる。

【0281】

また、本発明の半導体装置が含む記憶回路は、光学的作用又は電気的作用によりデータの書き込みを行うものであり、不揮発性であって、データの追記が可能であることを特徴とする。上記特徴により、書き換えによる偽造を防止してセキュリティを確保しつつ、新たなデータを追加して書き込むことができる。従って、高機能化と高付加価値化を実現し

10

20

30

40

50

た半導体装置及びその作製方法を提供することができる。

(実施形態 14)

次に、本発明の半導体装置が有する記憶回路の構成とその動作について図面を参照して説明する。メモリセル 21 は、ビット線  $B_x$  ( $1 \times m$ ) を構成する第 1 の導電層と、ワード線  $W_y$  ( $1 \times n$ ) を構成する第 2 の導電層と、トランジスタ 31 と、記憶素子 30 とを有する。記憶素子 30 は、一対の導電層の間に、有機化合物層が挟まれた構造を有する。トランジスタのゲート電極はワード線と接続され、ソース電極もしくはドレイン電極のいずれか一方はビット線と接続され、残る一方は記憶素子が有する 2 端子の一方と接続される。記憶素子の残る 1 端子は共通電極 (電位  $V_{com}$ ) と接続される。

【0282】

次に、メモリセル 21 にデータの書き込みを行うときの動作について説明する (図 14)。

【0283】

まず、電気的作用によりデータの書き込みを行うときの動作について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態 (電気的作用を加えていない状態) をデータ「0」、電気特性を変化させた状態を「1」とする。

【0284】

ここでは、 $x$  列  $y$  行目のメモリセル 21 にデータを書き込む場合について説明する。メモリセル 21 にデータ「1」を書き込む場合、まず、デコーダ 23、24 およびセレクタ 25 によってメモリセル 21 を選択する。具体的には、デコーダ 24 によって、メモリセル 21 に接続されるワード線  $W_y$  に所定の電圧  $V_{22}$  を印加する。また、デコーダ 23 とセレクタ 25 によって、メモリセル 21 に接続されるビット線  $B_x$  を読み出し / 書き込み回路 26 に接続する。そして、読み出し / 書き込み回路 26 からビット線  $B_x$  へ書き込み電圧  $V_{21}$  を出力する。

【0285】

こうして、メモリセルを構成するトランジスタ 31 をオン状態とし、記憶素子 30 に、ビット線を電気的に接続し、おおむね  $V_w = V_{com} - V_{21}$  の電圧を印加する。なお、記憶素子 30 の一方の電極は電位  $V_{com}$  の共通電極に接続されている。電位  $V_w$  を適切に選ぶことで、当該導電層間に設けられた有機化合物層を物理的にもしくは電気的に変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第 1 の導電層と第 2 の導電層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、単に短絡 (ショート) させてもよい。なお、電位は、( $V_{21}$ 、 $V_{22}$ 、 $V_{com}$ ) = (5 ~ 15 V、5 ~ 15 V、0 V)、あるいは (-12 ~ 0 V、-12 ~ 0 V、3 ~ 5 V) の範囲から適宜選べば良い。電圧  $V_w$  は 5 ~ 15 V、あるいは -5 ~ -15 V とすればよい。

【0286】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。具体的には、非選択のワード線には接続されるメモリセルのトランジスタをオフ状態とする電位 (例えば 0 V) を印加し、非選択のビット線は浮遊状態とするか、 $V_{com}$  と同程度の電位を印加するとよい。

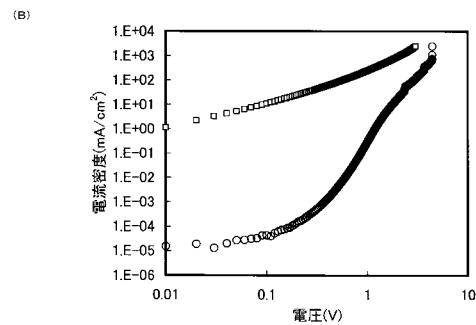

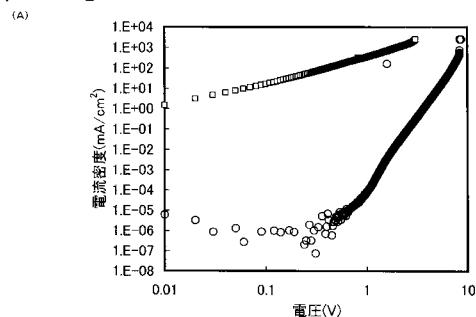

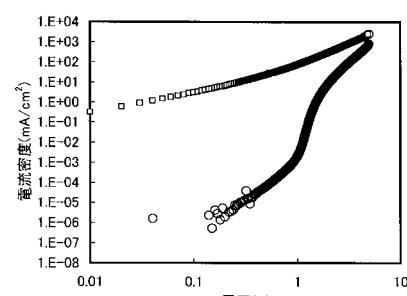

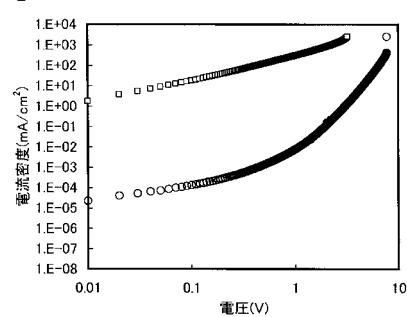

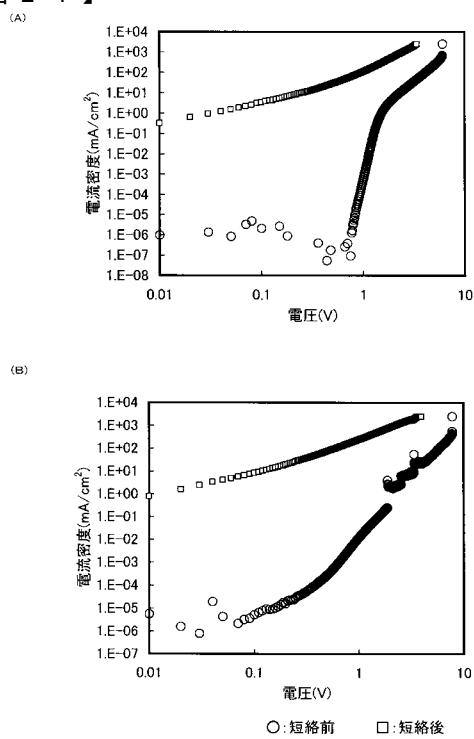

【0287】