(19) (KR)

(12) (B1)

|                              |      |              |

|------------------------------|------|--------------|

| (51) . Int. Cl. <sup>7</sup> | (45) | 2002 08 09   |

| G06F 13/12                   | (11) | 10 - 0347753 |

|                              | (24) | 2002 07 24   |

---

|      |                     |      |                |

|------|---------------------|------|----------------|

| (21) | 10 - 2000 - 0047718 | (65) | 2002 - 0014438 |

| (22) | 2000 08 18          | (43) | 2002 02 25     |

---

(73) 136 - 1

(72) 136 - 1

(74)

:

---

(54)

---

CPU ,

CPU    UART(Universal Asynchronous Receiver Transmitter,

CPU ,

) ,

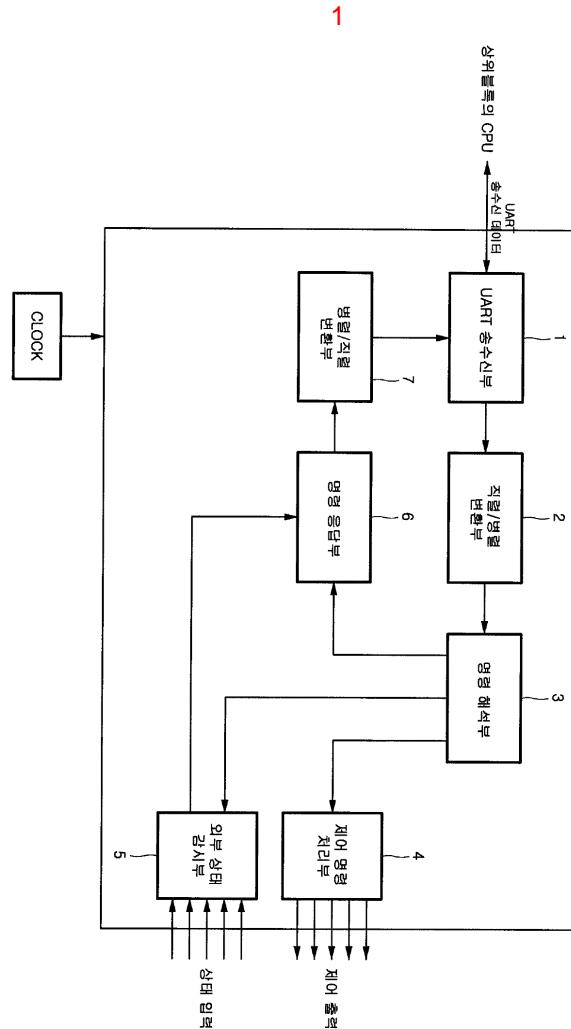

1

UART, , FIFO, - ,

1 (UART)

## 2a                   UART

## 2b                   UART

<

1: UART                  2:        /

3: 4:

5: 6:

7: /

CPU , CPU UART(Universal Asynchronous Receiver Transmitte ) (U

, CPU (ROM, RAM ) . CPU

가

CPU , CPU UART(Universal Asynchronous Receiver Transmitter,

), (UART)

(UART)

UART (1) / (7)

2a 2b (UART)

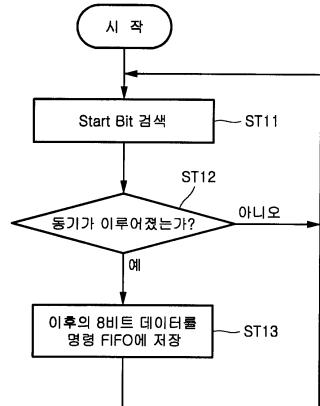

UART (1) (start bit) F

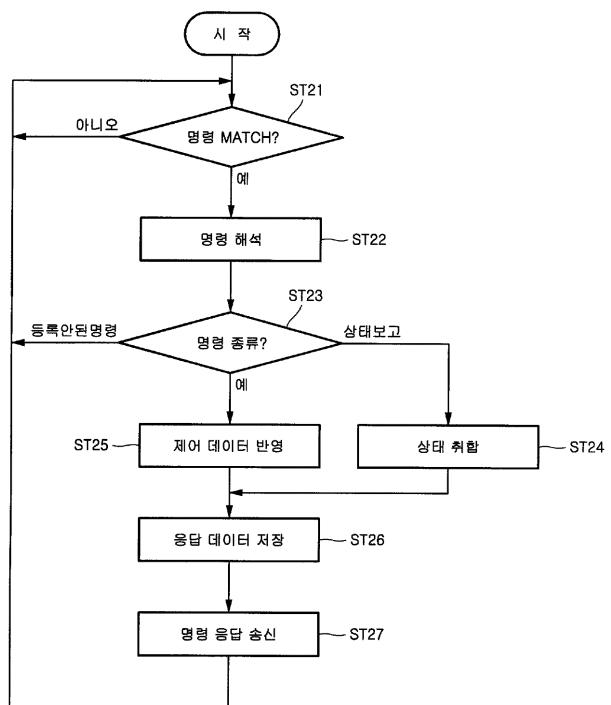

IFO (ST11 - ST13) ; FIFO (ST21,

ST22) ; (6)

(ST23 - ST26) ; UART

UART (ST27) .

가 (ST11 - ST13) , UART FIFO (1)

$$(\text{ST23} - \text{ST26}) \quad , \quad (6) \quad ,$$

(UART)

UART (1) CPU UART 가 , (ST1)

1). 가 8 (3) FIFO (ST12,ST13).

(3)

(ST21,ST22).

(ST23). ,

(3) (5)

(4)

(ST24,ST25,ST26).

UART

(ST27). (6) / (7)

/ (7) UART CPU 가 . UART (1)

(UART)

, CPU      UART

, CPU      ,      (cost)

(57)

1.

2.

The diagram illustrates the connection between a CPU and a USART module. The CPU is connected to the USART module via a bidirectional bus. The USART module is connected to an external FIFO buffer. The FIFO buffer has two outputs: one labeled '(start bit)' and another labeled 'FIFO'.

3.

UART

EIO

4

## UART

2a

2b