(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4046513号

(P4046513)

(45) 発行日 平成20年2月13日(2008.2.13)

(24) 登録日 平成19年11月30日(2007.11.30)

(51) Int.Cl.

G 11 C 11/15 (2006.01)

F 1

G 11 C 11/15 15 O

請求項の数 5 (全 34 頁)

(21) 出願番号 特願2002-21127 (P2002-21127)

(22) 出願日 平成14年1月30日 (2002.1.30)

(65) 公開番号 特開2003-228974 (P2003-228974A)

(43) 公開日 平成15年8月15日 (2003.8.15)

審査請求日 平成17年1月13日 (2005.1.13)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100096781

弁理士 堀井 豊

(73) 特許権者 591036457

三菱電機エンジニアリング株式会社

東京都千代田区九段北一丁目13番5号

(74) 代理人 100064746

弁理士 深見 久郎

最終頁に続く

(54) 【発明の名称】半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が、磁気的に書き込まれた記憶データに応じて第1および第2の電気抵抗の一方を有する磁性体を含む複数のメモリセルと、

前記第1および第2の電気抵抗の中間的な電気抵抗を有し、少なくとも前記データ読出時に、第1および第2の電圧の間に電気的に結合される基準セルと、

データ読出時に、選択されたアドレスに対応する選択メモリセルを介して前記第1および第2の電圧の間に電気的に結合される第1のデータ線と、

前記選択メモリセルおよび前記基準セルの通過電流差に応じたデータ読出を行なうためのデータ読出回路とを備え、

前記データ読出回路は、

前記データ読出時に、前記基準セルの通過電流に基いて、前記第1のデータ線を所定電圧にクランプするためのデータ線電圧クランプ部と、

前記第1の電圧と第1のノードの間に設けられ、一定電流を前記第1のノードへ供給するための第1の電流供給部と、

前記第1の電圧と第2のノードの間に設けられ、前記一定電流を前記第2のノードへ供給するための第2の電流供給部とさらに含み、

前記データ線電圧クランプ部は、

前記基準セルを介して前記第2の電圧と接続される基準ノードと、

前記第1のノードと前記基準ノードとの間に設けられ、前記基準ノードの電圧が前記所

10

20

定電圧に維持されるように、前記基準ノードの通過電流を制御する第1の電流制御部と、前記第2のノードと前記第1のデータ線との間に設けられ、前記基準ノードの電圧が前記所定電圧に維持されるように、前記第1のデータ線の通過電流を制御する第2の電流制御部とを有し、

前記データ読出回路は、前記第1のデータ線および前記基準ノードの通過電流差を電圧差に変換するための電流差検出部をさらに含む、半導体集積回路。

#### 【請求項2】

前記データ線電圧クランプ部は、

前記基準ノードの電圧と前記所定電圧との電圧差に応じた帰還電圧を発生する電圧増幅器をさらに有し、

10

前記第1の電流制御部は、前記第1のノードと前記基準ノードとの間に電気的に結合されて、前記帰還電圧をゲートに受ける第1のトランジスタを有し、

前記第2の電流制御部は、アドレス選択結果に応じて、前記第1のデータ線と前記第2のノードとを電気的に結合するための第2のトランジスタを有し、

前記第2のトランジスタのゲートへは前記帰還電圧が入力される、請求項1に記載の半導体集積回路。

#### 【請求項3】

各々が、磁気的に書き込まれた記憶データに応じて第1および第2の電気抵抗の一方を有する磁性体を含む複数のメモリセルが行列状に配置されたメモリアレイと、

前記複数のメモリセルの列にそれぞれ対応して設けられ、各々が、データ読出時に選択されたメモリセルを介して読出電流経路を形成する複数のビット線と、

20

基準電流と前記選択されたメモリセルの読出電流との差を検知増幅する読出増幅器と、

前記複数のビット線の所定本数毎に設けられ、前記データ読出時に前記読出増幅器と対応する前記所定本数のビット線のうちの選択されたビット線との間に電気的に接続されて前記読出電流経路を形成するデータ線と、

前記メモリアレイとは異なる領域に配置されたレプリカメモリセルと、

第1の電源と前記レプリカメモリセルとの間に接続されたトランジスタと、

前記レプリカメモリセルおよび前記トランジスタの接続ノードの電位と基準電位とを比較して、電位差に基づく帰還電圧を前記トランジスタの制御電極へ与える電圧増幅器と、

前記複数のビット線にそれぞれ対応して設けられ、各々が、対応のビット線および前記データ線の間に接続されて、前記対応のビット線の選択時に前記帰還電圧を制御電極に受ける複数の列選択トランジスタとを備える、半導体集積回路。

30

#### 【請求項4】

前記複数のビット線にそれぞれ対応して設けられ、各々が、対応の前記列選択トランジスタの制御電極と前記帰還電圧の伝送ノードとの間に接続される複数の読出選択ゲートをさらに備え、

各前記読出選択ゲートは、対応の列選択信号の活性化に応答して、前記対応の列選択トランジスタの制御電極を前記伝送ノードと接続する一方で、前記対応の列選択信号の非活性時には、前記対応の列選択トランジスタの制御電極を、前記列選択トランジスタをオフさせるための所定電位を供給する第2の電源と接続する、請求項3記載の半導体集積回路

40

#### 【請求項5】

前記第1の電源は、前記レプリカメモリセルに電流を供給する電流源である、請求項3記載の半導体集積回路。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、薄膜磁性体記憶装置に関し、より特定的には、磁気トンネル接合（M T J：Magnetic Tunneling Junction）を有するメモリセルを備えた薄膜磁性体記憶装置に関する。

50

**【0002】****【従来の技術】**

低消費電力で不揮発的なデータ記憶が可能な記憶装置として、M R A M デバイスが注目されている。M R A M デバイスは、半導体集積回路に形成された複数の薄膜磁性体を用いて、不揮発的なデータ記憶を行ない薄膜磁性体の各々をメモリセルとして、ランダムアクセスが可能な記憶装置である。

**【0003】**

特に、近年では磁気トンネル接合を利用した薄膜磁性体をメモリセルとして用いることによって、M R A M デバイスの性能が飛躍的に進歩することが発表されている。磁気トンネル接合を有するメモリセルを備えたM R A M デバイスについては、“A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell”, ISSCC Digest of Technical Papers, TA7.2, Feb. 2000.、 “Nonvolatile RAM based on Magnetic Tunnel Junction Elements”, ISSCC Digest of Technical Papers, TA7.3, Feb. 2000.、および“ A 256kb 3.0V 1T1MTJ Nonvolatile Magnetoresistive RAM”, ISSCC Digest of Technical Papers, TA7.6, Feb. 2001.等の技術文献に開示されている。等の技術文献に開示されている。

**【0004】**

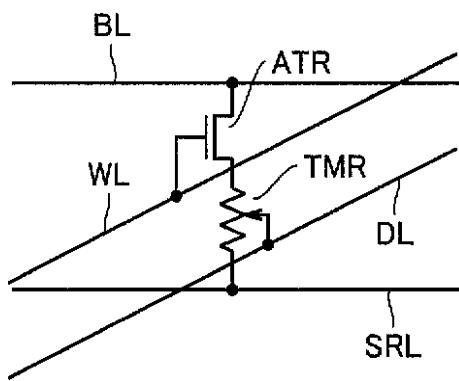

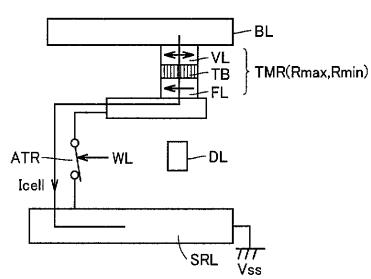

図15は、磁気トンネル接合部を有するメモリセル（以下、単に「M T J メモリセル」とも称する）の構成を示す概略図である。

**【0005】**

図15を参照して、M T J メモリセルは、磁気的に書き込まれた記憶データのデータレベルに応じて電気抵抗が変化するトンネル磁気抵抗素子T M Rと、アクセストランジスタA T Rとを含む。アクセストランジスタA T Rは、ビット線B Lおよびソース線S R Lの間に、トンネル磁気抵抗素子T M Rと直列に接続される。代表的には、アクセストランジスタA T Rとして、半導体基板上に形成された電界効果型トランジスタが適用される。

**【0006】**

M T J メモリセルに対しては、データ書込時に異なった方向のデータ書込電流をそれぞれ流すためのビット線B Lおよびディジット線D Lと、データ読み出を指示するためのワード線W Lと、データ読み出時にトンネル磁気抵抗素子T M Rを接地電圧V s sにプルダウンするためのソース線S R Lとが設けられる。データ読み出時においては、アクセストランジスタA T Rのターンオンに応答して、トンネル磁気抵抗素子T M Rは、ソース線S R L（接地電圧V s s）およびビット線B Lの間に電気的に結合される。

**【0007】**

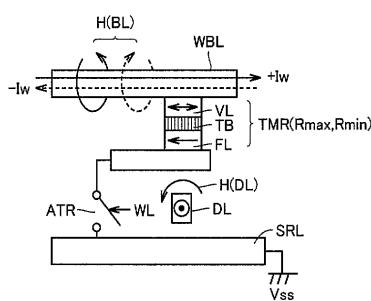

図16は、M T J メモリセルに対するデータ書込動作を説明する概念図である。

**【0008】**

図16を参照して、トンネル磁気抵抗素子T M Rは、固定された一定の磁化方向を有する強磁性体層（以下、単に「固定磁化層」とも称する）F Lと、外部からの印加磁界に応じた方向に磁化される強磁性体層（以下、単に「自由磁化層」とも称する）V Lとを有する。固定磁化層F Lおよび自由磁化層V Lの間には、絶縁体膜で形成されるトンネルバリア（トンネル膜）T Bが設けられる。自由磁化層V Lは、書き込まれる記憶データのレベルに応じて、固定磁化層F Lと同一方向または固定磁化層F Lと反対方向に磁化される。これらの固定磁化層F L、トンネルバリアT Bおよび自由磁化層V Lによって、磁気トンネル接合が形成される。

**【0009】**

トンネル磁気抵抗素子T M Rの電気抵抗は、固定磁化層F Lおよび自由磁化層V Lのそれぞれの磁化方向の相対関係に応じて変化する。具体的には、トンネル磁気抵抗素子T M Rの電気抵抗は、固定磁化層F Lの磁化方向と自由磁化層V Lの磁化方向とが平行である場合に最小値R m i nとなり、両者の磁化方向が反対（反平行）方向である場合に最大値R m a xとなる。

**【0010】**

10

20

30

40

50

データ書込時においては、ワード線 W L が非活性化されて、アクセストランジスタ A T R はターンオフされる。この状態で、自由磁化層 V L を磁化するためのデータ書込電流は、ビット線 B L およびディジット線 D L のそれぞれにおいて、書込データのレベルに応じた方向に流される。

【 0 0 1 1 】

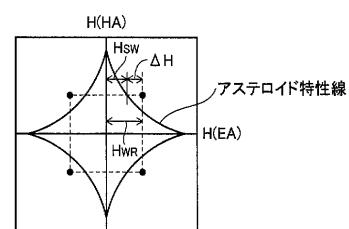

図 17 は、データ書込時におけるデータ書込電流とトンネル磁気抵抗素子の磁化方向との関係を説明する概念図である。

【 0 0 1 2 】

図 17 を参照して、横軸は、トンネル磁気抵抗素子 T M R 内の自由磁化層 V L において磁化容易軸 ( E A : Easy Axis ) 方向に印加される磁界を示す。一方、縦軸 H ( H A ) は、自由磁化層 V L において磁化困難軸 ( H A : Hard Axis ) 方向に作用する磁界を示す。磁界 H ( E A ) および H ( H A ) は、ビット線 B L およびディジット線 D L をそれぞれ流れる電流によって生じる 2 つの磁界の一方ずつにそれぞれ対応する。10

【 0 0 1 3 】

M T J メモリセルにおいては、固定磁化層 F L の固定された磁化方向は、自由磁化層 V L の磁化容易軸に沿っており、自由磁化層 V L は、記憶データのレベル ( “ 1 ” および “ 0 ” ) に応じて、磁化容易軸方向に沿って、固定磁化層 F L と平行あるいは反平行 ( 反対 ) 方向に磁化される。M T J メモリセルは、自由磁化層 V L の 2 通りの磁化方向と対応させて、1 ビットのデータ ( “ 1 ” および “ 0 ” ) を記憶することができる。20

【 0 0 1 4 】

自由磁化層 V L の磁化方向は、印加される磁界 H ( E A ) および H ( H A ) の和が、図中に示されるアステロイド特性線の外側の領域に達する場合においてのみ新たに書換えることができる。すなわち、印加されたデータ書込磁界がアステロイド特性線の内側の領域に相当する強度である場合には、自由磁化層 V L の磁化方向は変化しない。

【 0 0 1 5 】

アステロイド特性線に示されるように、自由磁化層 V L に対して磁化困難軸方向の磁界を印加することによって、磁化容易軸に沿った磁化方向を変化させるのに必要な磁化しきい値を下げることができる。

【 0 0 1 6 】

図 17 に示した例のようにデータ書込時の動作点を設計した場合には、データ書込対象である M T J メモリセルにおいて、磁化容易軸方向のデータ書込磁界は、その強度が H<sub>WR</sub> となるように設計される。すなわち、このデータ書込磁界 H<sub>WR</sub> が得られるように、ビット線 B L またはディジット線 D L を流されるデータ書込電流の値が設計される。一般的に、データ書込磁界 H<sub>WR</sub> は、磁化方向の切換えに必要なスイッチング磁界 H<sub>SW</sub> と、マージン分 H との和で示される。すなわち、 H<sub>WR</sub> = H<sub>SW</sub> + H で示される。30

【 0 0 1 7 】

M T J メモリセルの記憶データ、すなわちトンネル磁気抵抗素子 T M R の磁化方向を書換えるためには、ディジット線 D L とビット線 B L との両方に所定レベル以上のデータ書込電流を流す必要がある。これにより、トンネル磁気抵抗素子 T M R 中の自由磁化層 V L は、磁化容易軸 ( E A ) に沿ったデータ書込磁界の向きに応じて、固定磁化層 F L と平行もしくは、反対 ( 反平行 ) 方向に磁化される。トンネル磁気抵抗素子 T M R に一旦書込まれた磁化方向、すなわち M T J メモリセルの記憶データは、新たなデータ書込が実行されるまでの間不揮発的に保持される。40

【 0 0 1 8 】

図 18 は、M T J メモリセルからのデータ読出を説明する概念図である。

図 18 を参照して、データ読出時においては、アクセストランジスタ A T R は、ワード線 W L の活性化に応答してターンオンする。これにより、トンネル磁気抵抗素子 T M R は、接地電圧 V<sub>SS</sub> でプルダウンされた状態でビット線 B L と電気的に結合される。

【 0 0 1 9 】

この状態で、ビット線 B L を所定電圧でプルアップすれば、ビット線 B L およびトンネル

磁気抵抗素子TMRを含む電流経路を、トンネル磁気抵抗素子TMRの電気抵抗に応じた、すなわちMTJメモリセルの記憶データのレベルに応じたメモリセル電流I<sub>cell</sub>が通過する。たとえば、このメモリセル電流I<sub>cell</sub>を所定の基準電流と比較することにより、MTJメモリセルから記憶データを読出すことができる。

#### 【0020】

このようにトンネル磁気抵抗素子TMRは、印加されるデータ書き込み磁界によって書き換可能な磁化方向に応じてその電気抵抗が変化するので、トンネル磁気抵抗素子TMRの電気抵抗R<sub>max</sub>およびR<sub>min</sub>と、記憶データのレベル（“1”および“0”）とそれに対応付けることによって、不揮発的なデータ記憶を実行することができる。

#### 【0021】

10

#### 【発明が解決しようとする課題】

このように、MRAMデバイスでは、記憶データレベルの違いに対応したトンネル磁気抵抗素子TMRでの接合抵抗差である電気抵抗差 R = (R<sub>max</sub> - R<sub>min</sub>)を利用してデータ記憶が実行される。すなわち、選択メモリセルの通過電流I<sub>cell</sub>の検知に基づいて、データ読み出動作が実行される。

#### 【0022】

たとえば、米国特許公報6,205,073B1号（以下、「従来の技術」と称する）においては、電流伝達回路を用いてメモリセル通過電流を取出す構成が示されている。

#### 【0023】

20

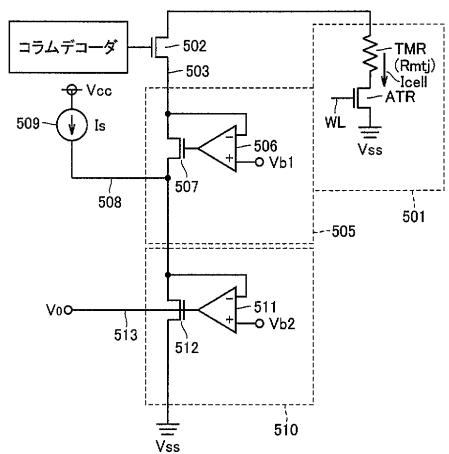

図19は、従来の技術に従うデータ読み出回路の構成を示す回路図である。

図19を参照して、データ読み出時において、選択メモリセル501では、ワード線WLの活性化に伴なってアクセストランジスタATRがターンオンする。さらに、コラムデコーダによってオンされたトランジスタスイッチ502を介して、データ読み出線503と接地電圧Vssとの間に、選択メモリセル501のトンネル磁気抵抗素子TMR（電気抵抗R<sub>mtj</sub>）が接続される。

#### 【0024】

従来の技術に従うデータ読み出回路は、データ読み出線503に対して2段階に設けられた電流伝達回路505および510を含む。

#### 【0025】

30

電流伝達回路505は、データ読み出線503と接点508との間に設けられ、センスアンプ506およびトランジスタ507を有する。トランジスタ507は、データ読み出線503と接点508との間に接続される。センスアンプ506は、所定のバイアス電圧Vb1とデータ読み出線503との電圧差を増幅して、トランジスタ507のゲートに出力する。接点508へは、電流源509によって一定電流Isが供給される。

#### 【0026】

電流伝達回路510は、接点508と接地電圧Vssとの間に設けられ、センスアンプ511およびトランジスタ512を有する。トランジスタ512は、接点508と接地電圧Vssとの間に接続される。センスアンプ511は、所定のバイアス電圧Vb2と接点508との電圧差を増幅して、出力ノード513に出力する。出力ノード513は、トランジスタ512のゲートと接続される。

40

#### 【0027】

電流伝達回路505および510は、負帰還動作によって、データ読み出線503および接点508の電圧を、第1のバイアス電圧Vb1および第2のバイアス電圧Vb2に維持するとともに、選択メモリセル501の通過電流I<sub>cell</sub>に応じた電圧Voを、出力ノード513に生成することができる。すなわち、トンネル磁気抵抗素子TMRへの印加電圧をバイアス電圧Vb1に維持して、トンネル磁気抵抗素子TMRでの電気抵抗特性を安定化した上で、選択メモリセル501の通過電流I<sub>cell</sub>を検知することができる。

#### 【0028】

しかしながら、従来の技術のデータ読み出回路では、センスアンプ506および511が必要とされるなど、比較的多くの回路素子が配置される。実際には、相補的な比較動作に基

50

づいてデータ読出を行なうために、同一のデータ読出回路を2系統配置する必要があるため、その回路素子数はさらに増大する。このため、製造プロセスで生じた回路素子間の特性ばらつきによって、データ読出精度が影響を受けるおそれがある。

#### 【0029】

また、図19に示した回路構成を配慮すれば、出力ノード513に得られる出力電圧 $V_o$ はそれほど高いレベルとならない。したがって、出力電圧 $V_o$ を高精度に検出することが必要となってしまう。

#### 【0030】

さらに、負帰還回路では電源投入直後の動作が不安定化するため、センスアンプ506および511に対して動作電流を常時供給する必要がある。したがって、データ読出回路でのスタンバイ電流が大きくなってしまい、消費電力が増加してしまう。10

#### 【0031】

一方で、ノードNoで得られた出力電圧 $V_o$ は、MTJメモリセルの製造ばらつきに起因する、トンネル磁気抵抗素子TMRの抵抗値( $R_{mtj}$ )の変動を含んでいる。すなわち、データ読出を高精度化するためには、製造プロセス変動に起因するMTJメモリセルの電気抵抗特性のばらつきに追随させて、データ読出精度を補償するための構成を考慮することが必要である

この発明は、このような問題点を解決するためになされたものであって、この発明の目的は、簡易な回路構成で、高精度のデータ読出を実行可能な薄膜磁性体記憶装置の構成を提供することである。20

#### 【0032】

##### 【課題を解決するための手段】

この発明に従う薄膜磁性体記憶装置は、各々が磁気的に書き込まれた記憶データに応じた電気抵抗を有する複数のメモリセルと、相補の第1および第2のデータ線と、第1および第2のデータ線の通過電流差に応じたデータ読出を行なうための差動增幅部とを備える。データ読出時ににおいて、第1および第2のデータ線の一方ずつは、複数のメモリセルのうちの選択メモリセル、および選択メモリセルの比較対象として設けられた比較セルをそれぞれ介して固定電圧と電気的に結合される。差動增幅部は、電源電圧と第1および第2のノード間に設けられ、少なくともデータ読出時に第1および第2のノードへ同一の動作電流を供給するための電流供給回路と、第1および第2のノードと第1および第2のデータ線との間に電気的に結合するとともに、第1および第2のデータ線の各々を基準電圧以下の所定電圧に維持するように、第1および第2のデータ線の間に生じる通過電流差を第1および第2のノードの電圧差に変換する電流增幅回路とを含む。30

#### 【0033】

好ましくは、差動增幅部は、電源電圧と内部ノードとの間に電気的に結合され、データ読出時にオンして動作電流を供給する電流供給トランジスタをさらに含む。電流供給回路は、内部ノードと第1および第2のノードとの間に電気的にそれぞれ結合され、各々が第1のノードと接続されたゲートを有する第1および第2のトランジスタを有する。電流增幅回路は、第1のノードおよび第1のデータ線の間に電気的に結合され、基準電圧をゲートに受ける第3のトランジスタと、第2のノードおよび第2のデータ線の間に電気的に結合され、基準電圧をゲートに受ける第4のトランジスタとを有する。40

#### 【0034】

また好ましくは、電流供給回路は、データ読出前においても、第1および第2のノードに対して動作電流を供給する。

#### 【0035】

さらに好ましくは、電流供給回路は、内部ノードと第1および第2のノードとの間に電気的にそれぞれ結合され、各々が第1のノードと接続されたゲートを有する第1および第2のトランジスタを有する。電流增幅回路は、第1のノードおよび第1のデータ線の間に電気的に結合され、基準電圧をゲートに受ける第3のトランジスタと、第2のノードおよび第2のデータ線の間に電気的に結合され、基準電圧をゲートに受ける第4のトランジスタ50

とを有する。

**【0036】**

特にこのような構成においては、基準電圧は、電源電圧よりも低い。

あるいは好ましくは、固定電圧は接地電圧に相当する。薄膜磁性体記憶装置は、データ読出前に、第1および第2のデータ線の各々を、接地電圧に設定するためのイコライズ回路をさらに備える。

**【0037】**

また好ましくは、複数のメモリセルは、複数のメモリブロックに分割して配置され、差動增幅部と、第1および第2のデータ線とは、メモリブロックごとに設けられる。薄膜磁性体記憶装置は、複数のメモリブロックに共通に設けられる、相補の第1および第2のグローバルデータ線と、第1の電圧と第1および第2のグローバルデータ線との間に設けられ、第1および第2のグローバルデータ線の各々へ同一電流を供給するためのグローバル電流供給部と、メモリブロックごとに設けられ、対応する差動增幅部での第1のノードの電圧に応じた電流で、第1のグローバルデータ線を第2の電圧へ駆動するための第1の電流伝達回路と、メモリブロックごとに設けられ、対応する差動增幅部での第2のノードの電圧に応じた電流で、第2のグローバルデータ線を第2の電圧へ駆動するための第2の電流伝達回路と、第1および第2のグローバルデータ線間の電圧差を増幅して読出データを生成する電圧アンプとをさらに備える。

**【0038】**

さらに好ましくは、各差動增幅部と、各第1および第2の電流伝達回路とは、対応するメモリブロックが選択された場合に動作する。

**【0039】**

また、さらに好ましくは、各メモリブロックにおいて、差動增幅部は並列に動作し、複数のメモリブロックのうちの順に選択された1つにおいて、第1および第2の電流伝達回路は動作する。

**【0040】**

あるいは、さらに好ましくは、第1および第2の電圧は、電源電圧および接地電圧にそれぞれ相当し、第1の電流伝達回路は、第1のグローバルデータ線および接地電圧の間に電気的に結合されて、対応する第1のノードと接続されたゲートを有する第1のNチャネル電界効果型トランジスタを有する。第2の電流伝達回路は、第2のグローバルデータ線および接地電圧の間に電気的に結合されて、対応する第2のノードと接続されたゲートを有する第2のNチャネル電界効果型トランジスタを有する。

**【0041】**

また好ましくは、複数のメモリセルは行列状に配置され、第1および第2のデータ線は、メモリセル列ごとに配置される相補のビット線にそれぞれ対応する。差動增幅部は、メモリセル列ごとにセンスアンプとして設けられる。薄膜磁性体記憶装置は、複数のメモリセルに対して共通に設けられる、相補の第1および第2のグローバルデータ線と、第1の電圧と第1および第2のグローバルデータ線との間に設けられ、第1および第2のグローバルデータ線の各々へ同一電流を供給するためのグローバル電流供給部と、メモリセル列ごとに設けられ、列選択結果に応じて動作して、対応する差動增幅部での第1のノードの電圧に応じた電流で、第1のグローバルデータ線を第2の電圧へ駆動するための第1の電流伝達回路と、メモリセル列ごとに設けられ、列選択結果に応じて動作して、対応する差動增幅部での第2のノードの電圧に応じた電流で、第2のグローバルデータ線を第2の電圧へ駆動するための第2の電流伝達回路と、第1および第2のグローバルデータ線間の電圧差を増幅して読出データを生成する電圧アンプとをさらに備える。

**【0042】**

さらに好ましくは、複数のメモリセルは、行方向に沿って第1および第2の領域に分割して配置され、差動增幅部は、第1および第2の領域の間に配置される。薄膜磁性体記憶装置は、メモリセル列ごとに設けられ、第1および第2の領域の一方において、第1および第2のデータ線と対応する第1および第2のノードとの間を電気的に切離すための接続ス

10

20

30

40

50

イッチをさらに備える。

【0043】

また、さらに好ましくは、薄膜磁性体記憶装置は、メモリセル列ごとに設けられ、列選択結果を対応する第1および第2の電流伝達回路へ伝達するための列選択線をさらに備える。第1および第2のデータ線と、第1および第2のグローバルデータ線とは、列方向に沿って配置され、列選択線は、行方向に沿って配置される。

【0044】

あるいは好ましくは、電流供給回路は、第1のノードおよび第3のノードの各々へ同一電流を供給するための第1のカレントミラー回路と、第2のノードおよび第4のノードの各々へ同一電流を供給するための第2のカレントミラー回路とを有する。電流増幅回路は、第2のデータ線を基準とする通過電流差に応じた電圧を第1のノードに生成するための第1の変換回路と、第1のデータ線を基準とする通過電流差に応じた電圧を第2のノードに生成するための第2の変換回路とを有する。

10

【0045】

さらに好ましくは、第1のカレントミラー回路は、電源電圧と第1および第3のノードとの間に電気的にそれぞれ結合され、各々のゲートが第3のゲートと接続される第1および第2のトランジスタを有する。第2のカレントミラー回路は、電源電圧と第2および第4のノードとの間に電気的にそれぞれ結合され、各々のゲートが第4のゲートと接続される第3および第4のトランジスタを有する。第1の変換回路は、第1および第4のノードと第1のデータ線との間に電気的にそれぞれ結合され、各々のゲートへ基準電圧を受ける第5および第6のトランジスタを有する。第2の変換回路は、第2および第3のノードと第2のデータ線との間に電気的にそれぞれ結合され、各々のゲートへ基準電圧を受ける第7および第8のトランジスタを有する。

20

【0046】

この発明の他の構成に従う薄膜磁性体記憶装置は、各々が磁気的に書込まれた記憶データに応じて第1および第2の電気抵抗の一方を有する複数のメモリセルと、第1および第2の電気抵抗の中間的な電気抵抗を有し、少なくともデータ読出時に、第1および第2の電圧の間に電気的に結合される基準セルと、データ読出時に、選択されたアドレスに対応する選択メモリセルを介して第1および第2の電圧の間に電気的に結合される第1のデータ線と、選択メモリセルおよび基準セルの通過電流差に応じたデータ読出を行なうためのデータ読出回路とを備える。データ読出回路は、データ読出時に、基準セルの通過電流に基いて、第1のデータ線を所定電圧にクランプするためのデータ線電圧クランプ部を含む。

30

【0047】

好ましくは、データ線電圧クランプ部は、データ読出に先立って、第1のデータ線を所定電圧にクランプする。

【0048】

また好ましくは、薄膜磁性体記憶装置は、第1のデータ線と相補のデータを伝達するための第2のデータ線をさらに備える。第2のデータ線は、データ読出時に、基準セルを介して第1および第2の電圧の間に電気的に結合される。データ読出回路は、第1の電圧と第1のノードの間に設けられ、一定電流を第1のノードへ供給するための第1の電流供給部と、第1の電圧と第2のノードの間に設けられ、一定電流を第2のノードへ供給するための第2の電流供給部とを含む。データ線電圧クランプ部は、第1および第2のデータ線の所定の一方と第1のノードとの間に設けられ、一方のデータ線の電圧が所定電圧に維持されるように、一方のデータ線の通過電流を制御する第1の電流制御部と、第1および第2のデータ線の所定の他方と第2のノードとの間に設けられ、一方のデータ線の電圧が所定電圧に維持されるように、他方のデータ線の通過電流を制御する第2の電流制御部とを含む。データ読出回路は、第1および第2のデータ線の通過電流差を電圧差に変換するための電圧変換部をさらに含む。

40

【0049】

あるいは好ましくは、データ読出回路は、第1の電圧と第1のノードの間に設けられ、一

50

定電流を第1のノードへ供給するための第1の電流供給部と、第1の電圧と第2のノードの間に設けられ、一定電流を第2のノードへ供給するための第2の電流供給部とをさらに含む。データ線電圧クランプ部は、基準セルを介して第2の電圧と接続される基準ノードと、第1のノードと基準ノードとの間に設けられ、基準ノードの電圧が所定電圧に維持されるように、基準ノードの通過電流を制御する第1の電流制御部と、第2のノードと第1のデータ線との間に設けられ、基準ノードの電圧が所定電圧に維持されるように、第1のデータ線の通過電流を制御する第2の電流制御部とを有する。データ読出回路は、第1のデータ線および基準ノードの通過電流差を電圧差に変換するための電流差検出部をさらに含む。

## 【0050】

10

さらに好ましくは、データ線電圧クランプ部は、基準ノードの電圧と所定電圧との電圧差に応じた帰還電圧を発生する電圧増幅器をさらに有する。第1の電流制御部は、第1のノードと基準ノードとの間に電気的に結合されて、帰還電圧をゲートに受ける第1のトランジスタを有する。第2の電流制御部は、アドレス選択結果に応じて、第1のデータ線と第2のノードとを電気的に結合するための第2のトランジスタを有し、第2のトランジスタのゲートへは帰還電圧が入力される。

## 【0051】

## 【発明の実施の形態】

以下において、本発明の実施の形態について図面を参照して詳細に説明する。なお、図中における同一符号は、同一または相当部分を示すものとする。

20

## 【0052】

## [実施の形態1]

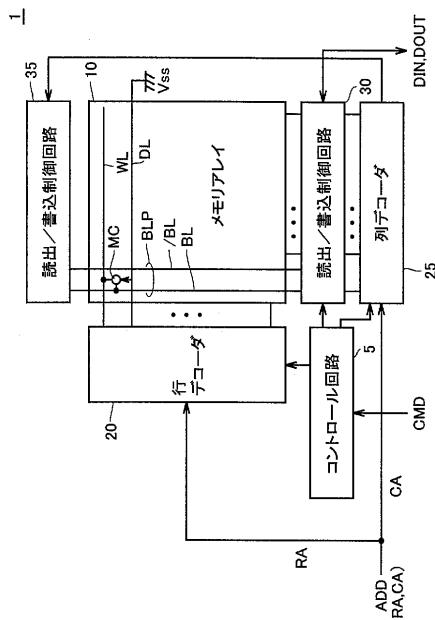

図1は、本発明の実施の形態に従うMRAMデバイス1の全体構成を示す概略ブロック図である。

## 【0053】

図1を参照して、本発明の実施の形態に従うMRAMデバイス1は、外部からの制御信号CMDおよびアドレス信号ADDに応答してランダムアクセスを行ない、書き込みデータDINの入力および読み出データDOUTの出力を実行する。

## 【0054】

MRAMデバイス1は、制御信号CMDに応答してMRAMデバイス1の全体動作を制御するコントロール回路5と、行列状に配されたMTJメモリセルMCを含むメモリアレイ10とを備える。

30

## 【0055】

メモリアレイ10においては、MTJメモリセルの行にそれぞれ対応して、ワード線WLおよびディジット線DLが配置され、MTJメモリセルの列にそれぞれ対応して、相補のビット線BLおよび/BLから構成されるビット線対BLPが配置される。図1においては、代表的に示される1個のMTJメモリセルMCと、これに対応するワード線WL、ディジット線DL、およびビット線対BLPの配置が示される。

## 【0056】

MRAMデバイス1は、アドレス信号によって示されるロウアドレスRAをデコードして、メモリアレイ10における行選択を実行するための行デコーダ20と、アドレス信号ADDによって示されるコラムアドレスCAをデコードして、メモリアレイ10における列選択を実行するための列デコーダ25と、読み出/書き込み制御回路30および35とをさらに備える。

40

## 【0057】

読み出/書き込み制御回路30および35は、メモリアレイ10に対してデータ書込動作を行なうための回路群、およびメモリアレイ10からデータ読み出を行なうための回路群（以下、「データ読み出回路系」とも称する）を総称したものである。

## 【0058】

ディジット線DLは、メモリアレイ10を挟んで行デコーダ20と反対側の領域において

50

、接地電圧 V<sub>SS</sub> と結合される。

【0059】

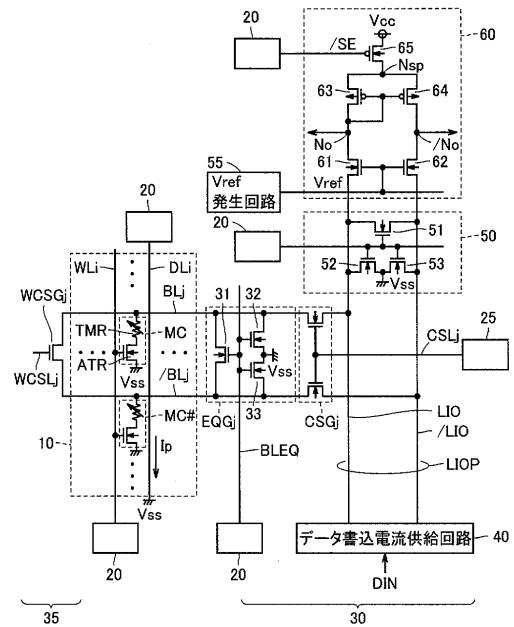

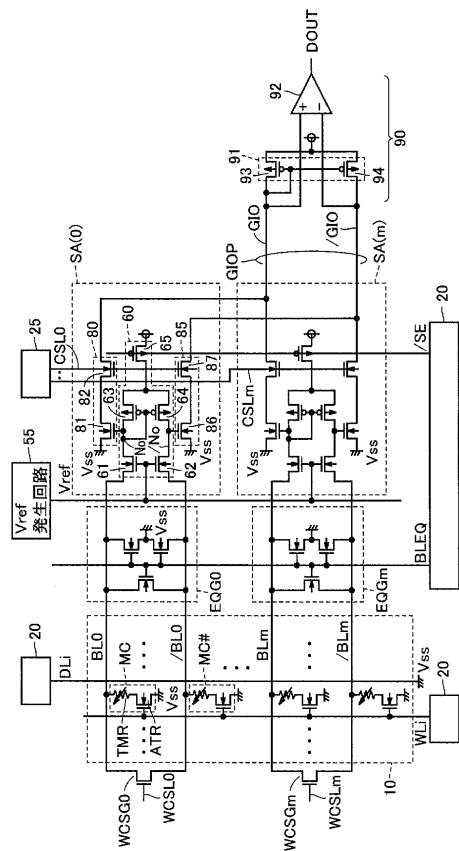

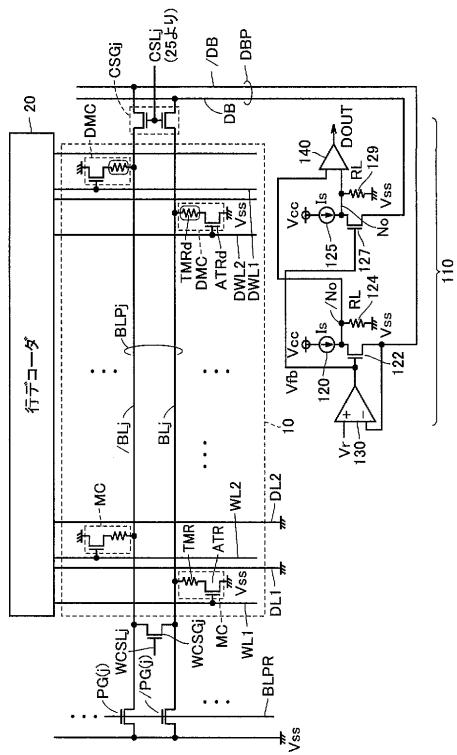

図2は、メモリアレイおよびデータ読出およびデータ書込を実行するための周辺回路についての実施の形態1に従う構成を示す回路図である。

【0060】

図2を参照して、メモリアレイ10は、ビット線BLおよび/BLの各々との交点に対応して、それぞれ配置されるMTJメモリセルを有する。すなわち、行アドレスおよび列アドレスの組合せで示される1つのアドレスに対応して、2個のMTJメモリセルが配置される。MTJメモリセルの各々は、図15に示したのと同様の構成を有し、対応するビット線BLまたは/BLと接地電圧V<sub>SS</sub>との間に直列に接続された、トンネル磁気抵抗素子TMRおよびアクセス素子（アクセストランジスタ）ATRとを有する。アクセストランジスタATRのゲートは、対応するワード線WLと接続される。10

【0061】

以下においては、同一アドレスに対応する2個のMTJメモリセルのうちのビット線BLと接続される一方を、単にメモリセルMCとも称し、ビット線/BLと接続される他方を比較セルMC#とも称する。同一アドレスに対応するメモリセルMCおよび比較セルMC#によって、1ビットのデータ記憶が実行される。具体的には、メモリセルMCには、当該アドレスでの記憶データが書込まれ、比較セルMC#へは、メモリセルMCと相補のデータが書込まれる。20

【0062】

図2においては、第i番目（i：自然数）のメモリセル行および第j番目（j：自然数）に対応する、ワード線WL<sub>i</sub>、ディジット線DL<sub>i</sub>、ビット線BL<sub>j</sub>、/BL<sub>j</sub>、ならびに、対応するメモリセルMCおよび比較セルMC#が代表的に示される。

【0063】

なお、以下においては、信号、信号線およびデータ等の2値的な高電圧状態（たとえば、電源電圧V<sub>CC</sub>）および低電圧状態（たとえば、接地電圧V<sub>SS</sub>）を、それぞれ「Hレベル」および「Lレベル」とも称する。

【0064】

読出/書込制御回路35は、各メモリセル列において、ビット線BLおよび/BLの一端同士に配置されたライトコラム選択ゲートWCSGを有する。ライトコラム選択ゲートWCSGは、対応するライトコラム選択線WC<sub>S</sub>Lの活性化（Hレベル）に応答してオンする。ライトコラム選択線WC<sub>S</sub>Lは、データ書込時に選択列において活性化（Hレベル）される。図2には、ビット線BL<sub>j</sub>および/BL<sub>j</sub>に対応して設けられる、ライトコラム選択線WC<sub>S</sub>L<sub>j</sub>およびライトコラム選択ゲートWCSG<sub>j</sub>が代表的に示される。30

【0065】

さらに、メモリアレイ10に隣接して、読出データおよび書込データを伝達するための相補のデータ線LI0および/LI0が配置される。データ線LI0および/LI0は、データ線対LIOPを構成する。

【0066】

各メモリセル列において、ビット線BLおよび/BLの他端と、データ線LI0および/LI0との間にコラム選択ゲートCSGが設けられる。コラム選択ゲートCSGは、対応するコラム選択線CSLの活性化（Hレベル）に応答してオンする。コラム選択線CSLは、データ書込時およびデータ読出時の双方において、選択列で活性化（Hレベル）される。図2には、ビット線BL<sub>j</sub>および/BL<sub>j</sub>に対応して設けられる、コラム選択線CS<sub>L</sub><sub>j</sub>およびコラム選択ゲートCSG<sub>j</sub>が代表的に示される。40

【0067】

まず、MTJメモリセルへのデータ書込動作について簡単に説明する。ここでは、一例として、第i行・第j列がデータ書込対象に選択された場合について説明する。

【0068】

行デコーダ20は、データ書込時において、選択行のディジット線DL<sub>i</sub>を活性化するた50

めに電源電圧 V<sub>CC</sub> と結合する。これにより、活性化されたディジット線 D<sub>Li</sub> は、その両端を電源電圧 V<sub>CC</sub> および接地電圧 V<sub>SS</sub> とそれぞれ接続される。したがって、活性化されたディジット線 D<sub>Li</sub> に対して、行方向のデータ書き込み電流 I<sub>p</sub> を流すことができる。行方向のデータ書き込み電流 I<sub>p</sub> は書き込みデータのレベルにかかわらず一定である。

#### 【0069】

一方、行デコーダ 20 は、非選択行のディジット線 D<sub>L</sub> については、接地電圧 V<sub>SS</sub> に固定する。これにより、非選択のディジット線 D<sub>L</sub> に行方向のデータ書き込み電流 I<sub>p</sub> が流れることはない。

#### 【0070】

読み出し / 書込み制御回路 30 は、データ書き込み電流供給回路 40 をさらに含む。データ書き込み電流供給回路 40 は、書き込みデータ D<sub>IN</sub> に応じて、データ線 L<sub>IO</sub> および / L<sub>IO</sub> を、電源電圧 V<sub>CC</sub> (H レベル) および接地電圧 V<sub>SS</sub> (L レベル) の一方ずつに設定する。たとえば、書き込みデータ D<sub>IN</sub> = “1” である場合には、データ書き込み電流供給回路 40 は、データ線 L<sub>IO</sub> を H レベル、/ L<sub>IO</sub> を L レベルに設定する。反対に、書き込みデータ D<sub>IN</sub> = “0” である場合には、データ書き込み電流供給回路 40 は、データ線 L<sub>IO</sub> を L レベル、/ L<sub>IO</sub> を H レベルに設定する。

10

#### 【0071】

これにより、ライトコラム選択ゲート W<sub>CSGj</sub> によって一端側同士を接続された選択列のビット線 B<sub>Lj</sub> および / B<sub>Lj</sub> に対して、書き込みデータ D<sub>IN</sub> のレベルに応じて、互いに逆方向の電流が流すことができる。この結果、選択アドレスに対応するメモリセル M<sub>C</sub> および比較セル M<sub>C#</sub> に対して、書き込みデータ D<sub>IN</sub> およびその相補データを並列に書き込むことができる。

20

#### 【0072】

次に、MTJ メモリセルからのデータ読み出動作について説明する。

読み出し / 書込み制御回路 30 は、メモリセル列ごとに配置されたイコライズ回路 E<sub>QG</sub> を有する。図 2 においては、第 j 番目のメモリセル列に対応するイコライズ回路 E<sub>QGj</sub> が代表的に示される。

#### 【0073】

イコライズ回路 E<sub>QGj</sub> は、対応するビット線 B<sub>Lj</sub>, / B<sub>Lj</sub> の間に接続されるトランジスタスイッチ 31 と、ビット線 B<sub>Lj</sub> および接地電圧 V<sub>SS</sub> の間に接続されるトランジスタスイッチ 32 と、ビット線 / B<sub>Lj</sub> および接地電圧 V<sub>SS</sub> の間に接続されるトランジスタスイッチ 33 とを有する。トランジスタスイッチ 31, 32 および 33 の各々は、たとえば N チャネル MOS トランジスタで構成される。

30

#### 【0074】

トランジスタスイッチ 31 ~ 33 の各々のゲートには、行デコーダ 20 によって生成される、メモリアレイ 10 内のメモリセル列に共通のビット線イコライズ信号 B<sub>LEQ</sub> が入力される。ビット線イコライズ信号 B<sub>LEQ</sub> は、少なくともデータ読み出動作前の所定期間ににおいて、H レベルへ活性化される。

#### 【0075】

図示しないが、他のメモリセル列に対応して設けられるイコライズ回路も同様の構成を有し、ビット線イコライズ信号 B<sub>LEQ</sub> に応答して動作する。ビット線イコライズ信号 B<sub>LEQ</sub> の活性化に応答したプリチャージ・イコライズ動作によって、各メモリセル列においてビット線 B<sub>L</sub> および / B<sub>L</sub> の各々は、接地電圧 V<sub>SS</sub> へ設定される。

40

#### 【0076】

読み出し / 書込み制御回路 30 は、さらに、データ線対 L<sub>TOP</sub> をイコライズするためのデータ線イコライズ回路 50 と、差動増幅器 60 とを有する。

#### 【0077】

データ線イコライズ回路 50 は、データ線 L<sub>IO</sub> および / L<sub>IO</sub> の間に接続されるトランジスタスイッチ 51 と、データ線 L<sub>IO</sub> および接地電圧 V<sub>SS</sub> の間に接続されるトランジスタスイッチ 52 と、データ線 / L<sub>IO</sub> および接地電圧 V<sub>SS</sub> の間に接続されるトランジ

50

スタスイッチ 5 3とを有する。トランジスタスイッチ 5 1、5 2および5 3の各々は、たとえばNチャネルMOSトランジスタで構成される。

#### 【0078】

トランジスタスイッチ 5 1～5 3の各々のゲートには、行デコーダ 2 0によって生成されるデータ線イコライズ信号 L I O E Q が入力される。データ線イコライズ信号 L I O E Q は、少なくともデータ読出動作前の所定期間において、H レベルへ活性化される。これに応答したプリチャージ・イコライズ動作によって、データ線 L I O および / L I O の各々は、接地電圧 V s s へ設定される。

#### 【0079】

差動増幅器 6 0は、ノード N o およびデータ線 L I O の間に接続されたNチャネルMOSトランジスタ 6 1と、ノード / N o とデータ線 / L I Oとの間に接続されたNチャネルMOSトランジスタ 6 2と、ノード N s p およびノード N o の間に接続されるPチャネルMOSトランジスタ 6 3と、ノード N s p およびノード / N o の間に接続されるPチャネルMOSトランジスタ 6 4と、電源電圧 V c c およびノード N s p の間に接続されるPチャネルMOSトランジスタ 6 5とを有する。

10

#### 【0080】

トランジスタ 6 3および 6 4の各々のゲートは、ノード N o と接続される。トランジスタ 6 3および 6 4は、カレントミラー回路を構成し、ノード N o および / N o の各々に対して、同一電流を供給しようとする。

#### 【0081】

トランジスタ 6 1および 6 2の各々のゲートには、V r e f 発生回路 5 5によって生成される固定された基準電圧 V r e f が入力される。トランジスタ 6 1および 6 2は、データ線 L I O および / L I O を基準電圧以下に維持するとともに、データ線 L I O および / L I O の通過電流差を増幅して、ノード N o および / N o 間の電圧差に変換する。

20

#### 【0082】

トランジスタ 6 5のゲートへは、行デコーダ 2 0によってデータ読出動作時に L レベルに活性化されるセンスイネーブル信号 / S E が入力される。トランジスタ 6 5は、センスイネーブル信号 / S E の活性化 (L レベル) に応答して動作電流を供給して、差動増幅器 6 0を動作させる。

#### 【0083】

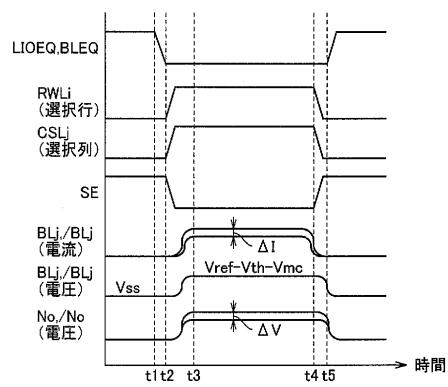

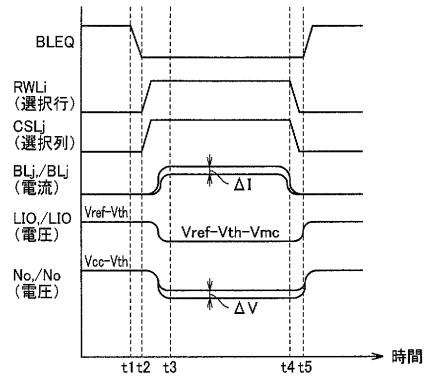

次に、図 3を用いて、実施の形態 1に従うM R A M デバイスにおけるデータ読出動作を説明する。図 3においても、第 i 行・第 j 列がデータ読出対象に選択された場合の動作について代表的に説明する。

30

#### 【0084】

図 3を参照して、データ読出実行前の、時刻 t 1以前において、データ線イコライズ信号 L I O E Q およびビット線イコライズ信号 B L E Q は、H レベルに活性化されている。これにより、各メモリセル列においてビット線 B L および / B L は接地電圧 V s s にプリチャージされ、データ線 L I O , / L I O も接地電圧 V s s にプリチャージされる。

#### 【0085】

時刻 t 1においてデータ読出動作が開始されると、まず、データ線イコライズ信号 L I O E Q およびビット線イコライズ信号 B L E Q が L レベルへ非活性化されて、各ビット線 B L , / B L およびデータ線 L I O , / L I O は、接地電圧 V s s から切離される。これにより、データ読出を開始する準備が整う。

40

#### 【0086】

さらに、時刻 t 2において、センスイネーブル信号 / S E が L レベルに活性化されて、差動増幅器 6 0の動作が開始される。これにより、データ線 L I O および / L I O の各々に対する電流供給が開始される。また、同様のタイミングで、選択行のワード線 W L i および選択列のコラム選択線 C S L j が各々 H レベルに活性化される。

#### 【0087】

選択行のワード線 W L i および選択列のコラム選択線 C S L j の活性化に応答して、データ線 L I O および / L I O の各々は、接地電圧 V s s へ設定される。

50

タ線 L I O は、ビット線 B L j およびメモリセル M C を介して接地電圧 V s s へプルダウンされ、データ線 / L I O は、ビット線 / B L j および比較セル M C # を介して接地電圧 V s s へプルダウンされる。既に説明したように、メモリセル M C および比較セル M C # へは互いに相補のデータが書き込まれているので、それぞれの電気抵抗は R m a x および R m i n の一方ずつである。

#### 【 0 0 8 8 】

センスイネーブル信号 / S E の活性化に応答して、トランジスタ 6 5 によって供給される動作電流は、データ線 L I O , / L I O と、ビット線 B L j , / B L j と、メモリセル M C および比較セル M C # のトンネル磁気抵抗素子 T M R を通過して接地電圧 V s s へ至る経路を流れる。

10

#### 【 0 0 8 9 】

差動増幅器 6 0 において、トランジスタ 6 3 および 6 4 で構成されたカレントミラー回路は、データ線 L I O および / L I O の各々に同一電流を供給しようとする。しかし、選択アドレスに対応するメモリセル M C および比較セル M C # 間には電気抵抗差 R が存在するので、両者の通過電流には電流差が生じようとする。この電流差によって生じようとする、ビット線 B L j および / B L j の間、すなわちデータ線 L I O および / L I O 間の電圧差は、差動増幅器 6 0 中のトランジスタ 6 1 および 6 2 におけるソース・ドレイン電圧の差に相当するので、上記の電気抵抗差 R は、トランジスタ 6 1 および 6 2 の通過電流（ソース・ドレイン電流）差 I に変換される。すなわち、この電流差 I が、ビット線 B L j および / B L j 間、ならびにデータ線 L I O および / L I O 間の電流差として現われる。トランジスタ 6 1 および 6 2 は、電流差 I を増幅した電圧差 V を、ノード N o および / N o 間に生じさせる。電圧差 V の極性、すなわちノード N o および / N o の電圧の高低は、選択されたメモリセル M C の記憶データに応じて異なる。

20

#### 【 0 0 9 0 】

一方、ビット線 B L j および / B L j 間、ならびにデータ線 L I O および / L I O 間には電圧差は生じず、データ線 L I O , / L I O およびビット線 B L j , / B L j の各々の電圧は、“ V r e f - V t h - V m c ” に落ち着く。ここで、 V t h はトランジスタ 6 1 , 6 2 のしきい値電圧に相当し、 V m c は、メモリセル M C および比較セル M C # で生じる電圧降下に相当する。

30

#### 【 0 0 9 1 】

基準電圧 V r e f はトンネル磁気抵抗素子中のトンネルバリアである絶縁膜の信頼性等を考慮して、上記の電圧 “ V r e f - V t h - V m c ” がたとえば約 4 0 0 m V 程度となるように設定される。これにより、過電圧印加によるメモリセル破壊を回避して、動作信頼性を向上できる。

#### 【 0 0 9 2 】

このようなノード N o および / N o 間における電圧差 V の極性に応じて、選択アドレスの記憶データを読出することができる。たとえば、ノード N o および / N o の電圧差を増幅するアンプを後段にさらに配置することによって、メモリアレイ 1 0 からの読出データ D O U T を生成することが可能である。

40

#### 【 0 0 9 3 】

データ読出終了時には、時刻 t 4 において、センスイネーブル信号 / S E 、選択行のワード線 W L i および選択列のコラム選択線 C S L j が非活性化される。さらに、時刻 t 5 において、データ線イコライズ信号 L I O E Q およびビット線イコライズ信号 B L E Q が H レベルへ活性化されて、各ビット線 B L , / B L およびデータ線 L I O , / L I O がプリシャージされて、データ読出前の回路状態が再現される。

#### 【 0 0 9 4 】

以上説明したように、実施の形態 1 に従う構成においては、差動増幅器 6 0 の動作電流をメモリセルの通過電流として用いるので、データ読出回路系の回路素子数を削減できる。また、電気抵抗差 R に起因する電流差 I を、トランジスタの増幅作用によって電圧差 V に変換するので、高精度のデータ読出を行なえる。

50

**【 0 0 9 5 】**

さらに、データ読出時における、トンネル磁気抵抗素子TMRへの印加電圧が一定に維持されるので、トンネル磁気抵抗素子の電気抵抗特性の変動を抑制してデータ読出を高精度化できる。

**【 0 0 9 6 】****[ 実施の形態 2 ]**

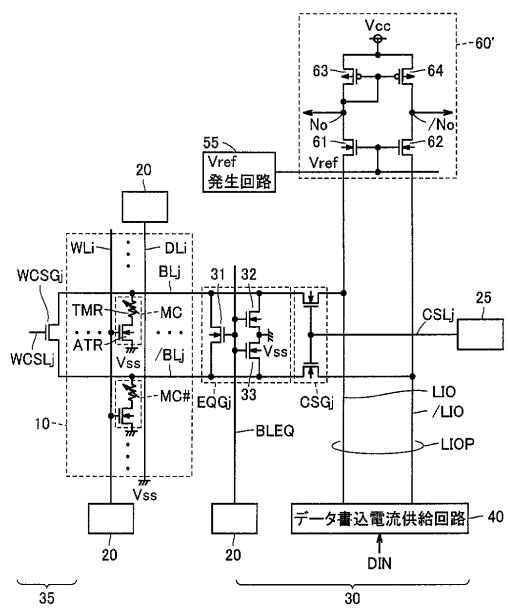

図4は、メモリアレイおよびその周辺回路の実施の形態2に従う構成を示す回路図である。

**【 0 0 9 7 】**

図4を参照して、実施の形態2に従う構成においては、図2に示した構成と比較して、差動増幅器60に代えて差動増幅器60'が配置される点と、データ線イコライズ回路50の配置が省略される点とが異なる。 10

**【 0 0 9 8 】**

差動増幅器60'は、図2に示される差動増幅器60と比較して、電流源として動作するPチャネルMOSトランジスタ65の配置が省略される点で異なる。すなわち、差動増幅器60'においては、PチャネルMOSトランジスタ63および64のソースは、電源電圧Vccと常時電気的に結合される。

**【 0 0 9 9 】**

実施の形態2に従うMRAMデバイスのその他の部分の構成は、実施の形態1と同様であるので詳細な説明は繰返さない。 20

**【 0 1 0 0 】**

次に、図5を用いて、実施の形態2に従うMRAMデバイスにおけるデータ読出動作を説明する。図5においても、第i行・第j列がデータ読出対象に選択された場合の動作について代表的に説明する。

**【 0 1 0 1 】**

図5を参照して、データ読出動作が開始される時刻t1以前においては、ビット線イコライズ信号BLEQがHレベルに活性化されるので、各メモリセル列においてビット線BLおよび/BLは接地電圧Vssにプリチャージされる。

**【 0 1 0 2 】**

差動増幅器60'の動作電流がデータ読出動作前においても常時供給されるので、データ線LI0および/LI0の各々は、基準電圧Vrefに応じて“Vref-Vth”にクランプされる。同様に、ノードNoおよび/N0の各々の電圧も、“Vcc-Vth”に固定されている。 30

**【 0 1 0 3 】**

時刻t2において、選択行のワード線WLiおよび選択列のコラム選択線CSLjが各々Hレベルに活性化されると、選択アドレスにおけるメモリセルMCおよび比較セルMC#の電気抵抗差Rに応じた、実施の形態1と同様の電流差Iが、ビット線BLjおよび/BLj間に、ならびにデータ線LI0および/LI0間に生じる。この電流差Iは、トランジスタ61および62によって、実施の形態1と同様にノードNoおよび/N0間の電圧差Vに変換される。 40

**【 0 1 0 4 】**

一方で、ビット線BLjおよび/BLj間に、データ線LI0および/LI0間に生じる電圧差は発生せず、各々の電圧は、図3に示したのと同様に、“Vref-Vth-Vmc”に落ち着く。

**【 0 1 0 5 】**

このように、実施の形態2に従う構成においては、データ読出回路系を構成する差動増幅器の回路構成をさらに簡易化して、実施の形態1と同様の高精度のデータ読出動作を実行できる。さらに、寄生容量の比較的大きいデータ線LI0および/LI0について、データ読出動作前とデータ読出時との間での電圧変化を小さくできるので、データ読出動作を高速化することができる。 50

**【0106】****[実施の形態3]**

実施の形態3においては、メモリアレイ10が複数の所定単位に分割され、所定単位ごとに実施の形態1または2に従うデータ読出回路系が配置される構成について説明する。

**【0107】**

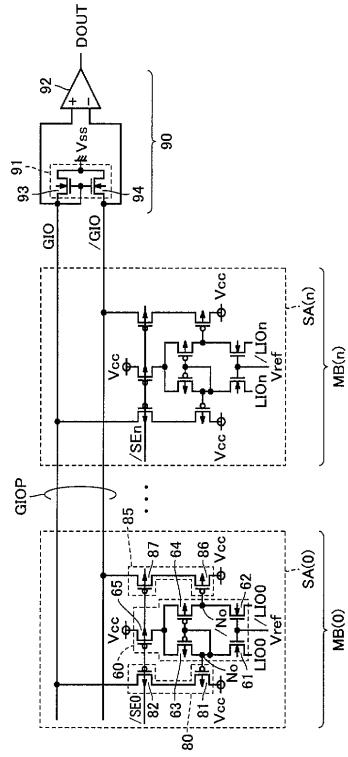

図6は、実施の形態3に従うデータ読出回路系の構成を示す回路図である。

図6を参照して、メモリアレイ10は、(n+1)個(n:自然数)のメモリブロックMB(0)～MB(n)に分割される。メモリブロックMB(0)～MB(n)には、データ線LIO0, /LIO0～LION, /LIONがそれぞれ配置される。メモリブロックMB(0)～MB(n)からのデータ読出は、センスアンプSA(0)～SA(n)によってそれぞれ実行される。10

**【0108】**

なお、以下においては、メモリブロックMB(0)～MB(n)を総称する場合には、単にメモリブロックMBとも称し、センスアンプSA(0)～SA(n)を総称する場合には、単にセンスアンプSAとも称する。同様に、データ線LIO0～LIONを総称する場合には、単にデータ線LIOとも称し、データ線/LIO0～/LIONを総称する場合には、単にデータ線/LIOとも称する。

**【0109】**

実施の形態3に従う構成においては、メモリブロックMB(0)～MB(n)に共通に、相補のグローバルデータ線GIOおよび/GIOと、メインアンプ90とがさらに配置される。グローバルデータ線GIOおよび/GIOは、グローバルデータ線対GIPを構成する。20

**【0110】**

メインアンプ90は、グローバルデータ線GIOおよび/GIOの各々へ同一電流を供給するためのカレントミラー回路91と、グローバルデータ線GIOおよび/GIO間の電圧差を増幅して読出データDOUTを生成する差動増幅器92とを含む。

**【0111】**

カレントミラー回路91は、グローバルデータ線GIOおよび/GIOと接地電圧Vssとの間にそれぞれ接続されたトランジスタ93および94を有する。トランジスタ93および94は、NチャネルMOSトランジスタで構成される。トランジスタ93および94の各々のゲートはグローバルデータ線GIOと接続される。30

**【0112】**

各センスアンプSAは、対応するメモリブロックMBからの1ビットのデータ読出を実行する。以下においては、センスアンプSA(0)の構成について代表的に説明する。

**【0113】**

センスアンプSA(0)は、図2に示した差動増幅器60に加えて、データ伝達回路80および85とを含む。

**【0114】**

データ伝達回路80は、電源電圧Vccおよびグローバルデータ線GIOの間に直列に接続されたトランジスタ81および82を有する。同様に、データ伝達回路85は、電源電圧Vccおよびグローバルデータ線/GIOの間に直列に接続されたトランジスタ86および87を有する。トランジスタ81および86のゲートは、差動増幅器60のノードNoおよび/N0とそれぞれ接続される。トランジスタ82および87のゲートには、差動増幅器60内のトランジスタ65と同様にセンシネーブル信号/SE0が入力される。40

**【0115】**

センシネーブル信号/SE0～/SENは、メモリブロックMB(0)～MB(n)にそれぞれ対応して設けられる。センシネーブル信号/SE0～/SENの各々は、対応するメモリブロックがデータ読出対象に選択された場合にLレベルに活性化される。たとえば、メモリブロックMB(0)がデータ読出対象として選択された場合には、センシネーブル信号/SE0のみがLレベルに活性化され、その他のセンシネーブル信号/S50

E 1 ~ / S E n は H レベルに非活性化される。

**【 0 1 1 6 】**

データ伝達回路 8 0 は、センスイネーブル信号 / S E 0 の活性化に応答して動作して、ノード N o の電圧に応じた電流（トランジスタ 8 6 のソース・ドレイン間電流）でグローバルデータ線 G I O を駆動する。同様に、データ伝達回路 8 5 は、センスイネーブル信号 / S E 0 の活性化に応答して動作して、ノード / N o の電圧に応じた電流（トランジスタ 8 1 のソース・ドレイン間電流）でグローバルデータ線 / G I O を駆動する。

**【 0 1 1 7 】**

このように、データ伝達回路 8 0 , 8 5 は、グローバルデータ線 G I O , / G I O を電源電圧 V c c へ駆動するので、トランジスタ 8 1 , 8 2 , 8 6 , 8 7 の各々は、P チャネル MOS トランジスタで構成される。

10

**【 0 1 1 8 】**

既に説明したように、センスアンプ S A ( 0 )において、差動増幅器 6 0 は、対応するメモリブロック M B ( 0 )における選択アドレスからの読み出データに応じて、ノード N o および / N o の間に電圧差 V を生じさせる。データ伝達回路 8 0 および 8 5 は、この電圧差 V をグローバルデータ線 G I O および / G I O の通過電流差へ変換して、グローバルデータ線 G I O および / G I O へ伝達する。

**【 0 1 1 9 】**

このように、データ伝達回路 8 0 および 8 5 と、カレントミラー回路 9 1 とによって構成される差動増幅器によって、メモリブロック M B ( 0 )でのノード N o および / N o 間の電圧差 V は、グローバルデータ線 G I O および / G I O 間の電圧差に増幅され、差動増幅器 9 2 によってさらに増幅されて、読み出データ D O U T が生成される。他のメモリブロックに対応してそれぞれ設けられるセンスアンプ S A も、センスアンプ S A ( 0 )と同様の構成を有する。

20

**【 0 1 2 0 】**

このような構成とすることにより、選択されたメモリブロック M B からの読み出データに応じた電圧差を、グローバルデータ線 G I O および / G I O に生じさせることができる。この結果、メモリブロック M B ( 0 ) ~ M B ( n ) によって共有される、グローバルデータ線対 G I O P およびメインアンプ 9 0 によって、データ読み出対象に選択されたメモリブロック M B からのデータ読み出を実行できる。

30

**【 0 1 2 1 】**

このように、実施の形態 3 に従う構成によれば、選択メモリセルへの通過電流供給を行なう差動増幅器 6 0 と、グローバルデータ線対 G I O P での電圧増幅を行なうデータ伝達回路 8 0 , 8 5 およびメインアンプ 9 0 との 2 段階の差動増幅動作によって、M R A M デバイスからのデータ読み出を実行する。このように、グローバルデータ線 G I O , / G I O は、選択されたメモリセル M C および比較セル M C # の通過電流経路からは切離されるので、アレイの大容量化に伴って寄生容量が増大するグローバルデータ線 G I O , / G I O を用いても、高速にデータ読み出を実行できる。

**【 0 1 2 2 】**

また、センスイネーブル信号 / S E 0 ~ / S E n は、データ読み出動作タイミングの指示（実施の形態 1 および 2 におけるセンスイネーブル信号 / S E に相当）と、メモリブロック M B ( 0 ) ~ M B ( n ) の選択情報を含んでいるので、両者にそれぞれ対応して独立した信号を設ける場合と比較して、信号配線数を削減できる。

40

**【 0 1 2 3 】**

[ 実施の形態 3 の変形例 1 ]

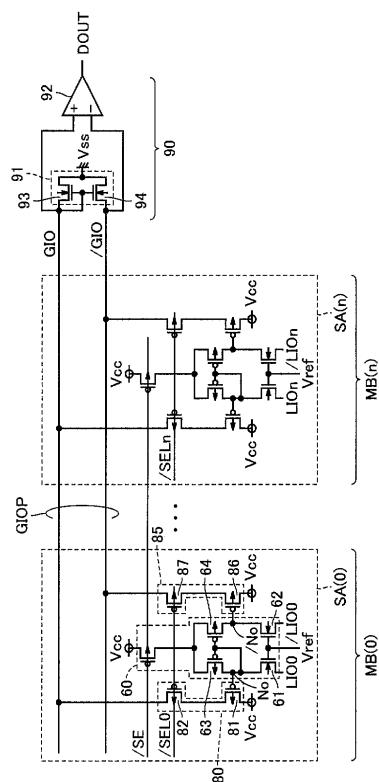

図 7 は、実施の形態 3 の変形例 1 に従うデータ読み出回路系の構成を示す回路図である。

**【 0 1 2 4 】**

図 7 を参照して、実施の形態 3 の変形例 1 に従う構成においては、実施の形態 3 に従う構成と比較して、センスイネーブル信号 / S E と、ブロック選択信号 / S E L 0 ~ / S E L n とが独立して配置される点が異なる。

50

**【 0 1 2 5 】**

センスイネーブル信号 / S E は、実施の形態 1 および 2 と同様に、データ読出時（図 3 における時刻  $t_2 \sim t_5$  間）に L レベルへ活性化され、メモリブロック MB ( 0 ) ~ MB ( n ) に共通の信号として、センスアンプ S A ( 0 ) ~ S A ( n ) の各々に供給される。

**【 0 1 2 6 】**

これに対して、ブロック選択信号 / S E L 0 ~ / S E L n は、メモリブロック MB ( 0 ) ~ MB ( n ) にそれぞれ対応して設けられ、アドレス情報に応じて、対応するメモリブロック MB が活性化された場合に、L レベルへ活性化される。

**【 0 1 2 7 】**

各センスアンプ S A において、差動増幅器 6 0 内のトランジスタ 6 5 のゲートには、センスイネーブル信号 / S E が入力される。一方、データ伝達回路 8 0 および 8 5 内のトランジスタ 8 2 および 8 7 のゲートには、ブロック選択信号 / S E L 0 ~ / S E L n の対応する 1 つが入力される。たとえば、センスアンプ S A ( 0 ) においては、トランジスタ 8 2 および 8 7 の各ゲートへは、ブロック選択信号 / S E L 0 が入力される。その他の部分の構成および動作は、実施の形態 3 と同様であるので、詳細な説明は繰り返さない。10

**【 0 1 2 8 】**

したがって、データ読出動作においては、まず、センスイネーブル信号 / S E の活性化に応じて、メモリブロック MB ( 0 ) ~ MB ( n ) の各々において並列にデータ読出が実行される。これにより、センスアンプ S A ( 0 ) ~ S A ( n ) の各々において、差動増幅器 6 0 のノード N o および / N o に十分な電圧差が生じたタイミングで、ブロック選択信号 / S E L 0 ~ / S E L n のそれを順に活性化して、メモリブロック MB ( 0 ) ~ MB ( n ) の 1 つを順に選択する。これにより、実施の形態 3 に従うデータ読出と同様に、選択されたメモリブロックからの読出データに応じた電圧差をグローバルデータ線 G I O および / G I O 間に生じさせて、読出データ D O U T を生成することができる。20

**【 0 1 2 9 】**

この結果、メモリブロック MB ( 0 ) ~ MB ( n ) のそれぞれからの ( n + 1 ) ビットの読出データを連続的に高速読出できる。すなわち、バースト動作に適した構成の M R A M デバイスを提供できる。

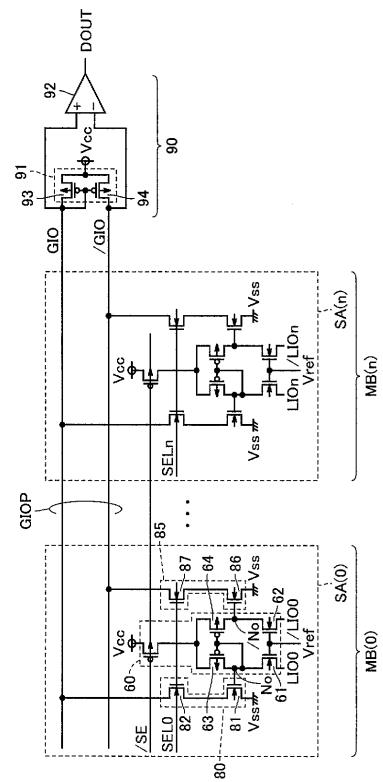

**【 0 1 3 0 】****[ 実施の形態 3 の変形例 2 ]**

30

図 8 は、実施の形態 3 の変形例 2 に従うデータ読出回路系の構成を示す回路図である。

**【 0 1 3 1 】**

図 8 を参照して、実施の形態 3 の変形例 2 に従う構成においては、図 7 に示した実施の形態 3 の変形例 1 に従う構成と比較して、データ伝達回路 8 0 , 8 5 が接地電圧 V s s とグローバルデータ線 G I O および / G I O の間に設けられる点が異なる。これに対応して、カレントミラー回路 9 1 は、電源電圧 V c c とグローバルデータ線 G I O および / G I O との間に設けられる。

**【 0 1 3 2 】**

実施の形態 3 の変形例 2 に従う構成においては、データ伝達回路 8 0 , 8 5 は、グローバルデータ線 G I O , / G I O を接地電圧 V s s へ駆動するので、トランジスタ 8 1 , 8 2 , 8 6 , 8 7 の各々は、N チャネル M O S トランジスタで構成される。また、カレントミラー回路 9 1 を構成するトランジスタ 9 3 および 9 4 は、P チャネル M O S トランジスタで構成される。さらに、ブロック選択信号 / S E L 0 ~ / S E L n に代えて、対応するメモリブロック MB が活性化された場合に H レベルへ活性化されるブロック選択信号 S E L 0 ~ S E L n が設けられ、対応するセンスアンプ S A において、トランジスタ 8 2 および 8 7 の各ゲートへ入力される。その他の部分の構成および動作は、実施の形態 3 の変形例 1 と同様であるので、詳細な説明は繰り返さない。40

**【 0 1 3 3 】**

このような構成としても、電圧増幅における極性は反転するものの、実施の形態 3 の変形例 1 と同様のデータ読出を実行することができる。特に、データ伝達回路 8 0 および 8 5

50

を、より大きなソース・ドレイン電流を確保し易いNチャネルMOSトランジスタで構成することにより、これらのトランジスタのサイズを小型化することが可能となる。

#### 【0134】

なお、図6に示した実施の形態3に従うセンスアンプに対しても同様の構成を適用して、データ伝達回路80, 85を構成するトランジスタ群の小型化を図ることが可能である。

#### 【0135】

#### [実施の形態4]

実施の形態4においては、実施の形態3およびその変形例に示したセンスアンプをメモリセル列ごとに配置したメモリアレイ10からのデータ読出回路系の構成について説明する。

10

#### 【0136】

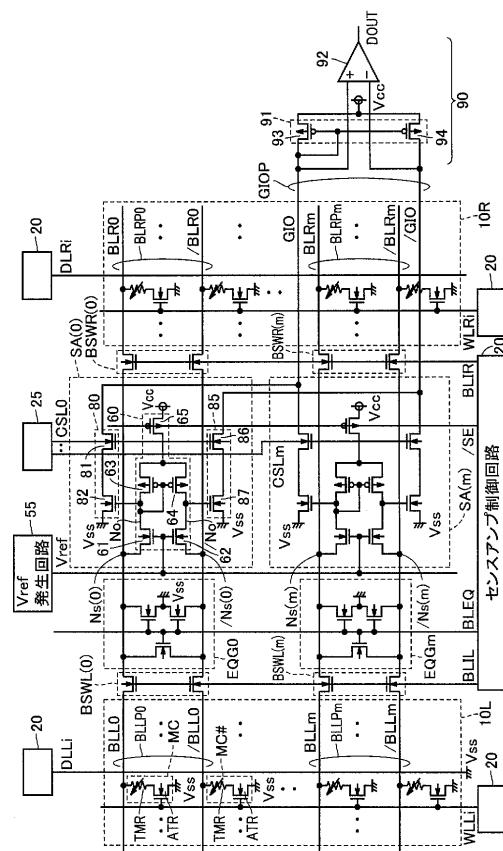

図9は、メモリアレイおよびその周辺回路の実施の形態4に従う構成を示す回路図である。

#### 【0137】

図9を参照して、メモリアレイ10の構成および、メモリセル列にそれぞれ対応して設けられたイコライズ回路EQGおよびライトコラム選択ゲートWCGの構成は、実施の形態1と同様である。グローバルデータ線対GIOPを構成する相補のグローバルデータ線GIOおよび/GIOは、メモリアレイ10からの1ビットのデータ読出およびデータ書き込みのために設けられる。また、メインアンプ90の構成は、実施の形態3と同様であるので詳細な説明は繰返さない。

20

#### 【0138】

実施の形態4に従う構成においては、メモリセル列にそれぞれ対応して、センスアンプSA(0)～SA(n)が設けられる。センスアンプSA(0)～SA(n)の各々の構成は、図8に示した実施の形態3の変形例2に従う構成と同様であるので詳細な説明は繰返さない。

#### 【0139】

各メモリセル列において、センスアンプSAに含まれる差動増幅器60は、センスイネーブル信号/SEの活性化に応答して、対応するビット線BLおよび/BLを介して、選択行のメモリセルMCおよび比較セルMC#の通過電流を供給する。さらに、差動増幅器60は、ビット線BLおよび/BL間に生じた、選択されたメモリセルMCの記憶データに応じた極性を有する電流差Iを、ノードNoおよび/Nの間の電圧差Vに増幅する。このようにして、各メモリセル列において、データ読出動作は、並列に開始される。

30

#### 【0140】

各センスアンプSAにおいて、データ伝達回路80および85は、対応するコラム選択線CSLの活性化(Hレベル)に応答して動作して、対応するノードNoおよび/Nの間の電圧差Vに応じた電流差を、グローバルデータ線GIOおよび/GIOの間に生じさせる。すなわち、対応するコラム選択線CSLがHレベルに活性化された選択列において、差動増幅器60のノードNoおよび/N間に生じた電圧差Vが、カレントミラー回路91およびデータ伝達回路80, 85による差動増幅動作によってグローバルデータ線GIOおよび/GIOの間に電圧差に増幅される。差動増幅器92は、グローバルデータ線GIOおよび/GIOの間に電圧差をさらに増幅して、メモリアレイ10からの読出データDOUTを生成する。

40

#### 【0141】

このような構成とすることにより、各メモリセル列において、並列にデータ読出を開始した後に、列選択を順次切換えて、複数ビットの読出データを連続的に高速出力することができる。特に、各差動増幅器60によって、ビット線対BLPを直接駆動する構成としているので、データ読出動作をさらに高速化することができる。

#### 【0142】

さらに、グローバルデータ線GIOおよび/GIOを、ビット線BLおよび/BLと同一方向に設けることによって、多数ビットの並列出力に適した構成のRAMデバイスとす

50

ることができる。

**【0143】**

[実施の形態4の変形例]

図10は、メモリアレイおよびその周辺回路の実施の形態4の変形例に従う構成を示す回路図である。

**【0144】**

図10を参照して、実施の形態4の変形例に従う構成においては、実施の形態4に従う構成に加えて、さらに、いわゆる「シェアードセンス構成」が適用される。

**【0145】**

すなわち、メモリアレイ10は、センスアンプSA(0)～SA(m)が配置される領域を挟んで、左側領域10Lおよび右側領域10Rに分割される。左側領域10Lおよび右側領域10Rの各々の構成は、これまで説明したメモリアレイ10と実質的に同一である。以下においては、左側領域10Lおよび右側領域10Rを、メモリアレイ10Lおよび10Rともそれぞれ称する。

**【0146】**

なお、図10においては、メモリアレイ10Lおよび10Rにそれぞれ配置される信号線を区別するために、メモリアレイ10Lに配置されるワード線、ディジット線およびビット線について、WLL、DLL、BLL, / BLLと表記し、メモリアレイ10Rに配置される、ワード線、ディジット線およびビット線について、WLR、DLR、BLR, / BLRと表記する。また、図示しないが、メモリアレイ10Lおよび10Rの各々において、図2に示したライトコラム選択ゲートWCSGが各メモリセル列に対応して配置される。

**【0147】**

センスアンプSA(0)～SA(m)の各々は、メモリアレイ10Lおよび10Rによって共有されて、センスノードNs(0)～Ns(m)のうちの対応する1つと、センスノード/Ns(0)～/Ns(m)のうちの対応する1つとの通過電流差を、対応するノードNoおよび/No間の電圧差に増幅する。以下においては、センスノードNs(0)～Ns(m)を総称してセンスノードNsとも称し、センスノード/Ns(0)～/Ns(m)を総称してセンスノード/Nsとも称する。

**【0148】**

メモリセル列にそれぞれ対応して、センスノードNsおよび/Nsと、メモリアレイ10Rおよび10Lとの間の接続を制御するための、ビット線接続スイッチBSWL(0), BSWR(0)～BSWL(m), BSWR(m)がそれぞれ配置される。以下においては、ビット線接続スイッチBSWL(0)～BSWL(m)を総称する場合には、ビット線接続スイッチBSWLとも称し、ビット線接続スイッチBSWR(0)～BSWR(m)を総称する場合には、ビット線接続スイッチBSWRとも称する。

**【0149】**

たとえば、ビット線接続スイッチBSWL(0)は、制御信号BLILの活性化に応答して、ビット線BLL0および/BLL0を、センスノードNs(0)および/Ns(0)とそれぞれ接続する。同様に、ビット線接続スイッチBSWR(0)は、制御信号BLIRの活性化に応答して、ビット線BLR0および/BLR0を、センスノードNs(0)および/Ns(0)とそれぞれ接続する。

**【0150】**

その他のメモリセル列に対応して設けられたビット線接続スイッチBSWLおよびBSWRも同様に動作する。したがって、制御信号BLILが活性化されている期間においては、センスノードNs(0), /Ns(0)～Ns(m), /Ns(m)は、メモリアレイ10Lのビット線BLL0, /BLL0～BLLm, /BLLmとそれぞれ接続される。反対に、制御信号BLIRが活性化された期間においては、センスノードNs(0), /Ns(0)～Ns(m), /Ns(m)は、メモリアレイ10Lのビット線BLR0, /BLR0～BLRm, /BLRmとそれぞれ接続される。

10

20

30

40

50

**【0151】**

メモリセル列にそれぞれ対応して設けられるイコライズ回路EQG0～EQGmは、ビット線イコライズ信号BLEQの活性化に応答して、イコライズ・プリチャージ動作を実行する。たとえば、イコライズ回路EQG0は、ビット線イコライズ信号BLEQに応答して、センスノードNs(0)および/Ns(0)の各々を、接地電圧Vssに設定する。このように、ビット線イコライズ信号BLEQの活性化に応答して、センスノードNs(0), /Ns(0)～Ns(m), /Ns(m)の各々は接地電圧Vssに設定される。

**【0152】**

データ読出時においては、ビット線イコライズ信号BLEQが、HレベルからLレベルに変化して、センスノードNs(0), /Ns(0)～Ns(m), /Ns(m)の各々が接地電圧Vssから切離される。さらに、制御信号BLILおよびBLIRのいずれか一方のみがHレベルに活性化される。これにより、メモリアレイ10Lおよび10Rの非選択である一方に配置されたビット線BL, /BLは、対応するセンスノードNsおよび/Nsから電気的に切離される。

**【0153】**

この結果、センスアンプSA(0)～SA(m)の各々は、対応するセンスノードNs, /Nsと接続された、選択されたメモリアレイのビット線間に生じた電流差に基づいて、実施の形態4と同様のデータ読出動作を実行する。

**【0154】**

実施の形態4の変形例に従う構成によれば、シェアードセンス構成に基づいて、センスアンプSAを配置するので、データ読出時におけるビット線の実質的な配線長を抑制して、データ読出をさらに高速化することができる。

**【0155】****[実施の形態5]**

実施の形態5においては、実施の形態1から4およびそれらの変形例に用いられる差動増幅器60, 60'に代えて適用可能な、より安定的に動作する差動増幅器の構成について説明する。

**【0156】**

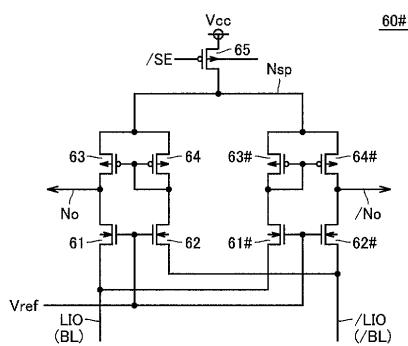

図11は、実施の形態5に従う差動増幅器60#の構成を示す回路図である。

図11を参照して、実施の形態5に従う差動増幅器60#は、データ線LIO(またはビット線BL)およびノードNspの間に直列に接続される、NチャネルMOSトランジスタ61および63と、トランジスタ61および63と並列に接続されるNチャネルMOSトランジスタ61#および63#とを有する。差動増幅器60#は、さらに、データ線/LIO(またはビット線/BL)およびノードNspの間に直列に接続される、PチャネルMOSトランジスタ62および64と、トランジスタ62および64と並列に接続されるPチャネルMOSトランジスタ62#および64#とを有する。

**【0157】**

トランジスタ63および64の各ゲートは、トランジスタ62および64の接続ノードと接続され、トランジスタ63#および64#の各ゲートは、トランジスタ61#および63#の接続ノードと接続される。トランジスタ61, 62, 61#, 62#の各ゲートへは、基準電圧Vrefが入力される。

**【0158】**

差動増幅器60#は、電源電圧VccおよびノードNspの間に電気的に結合されるPチャネルMOSトランジスタ65をさらに有する。トランジスタ65のゲートへは、センシネーブル信号/SEが入力される。なお、図4に示した差動増幅器60'と同様に、トランジスタ65の配置を省略することもできる。

**【0159】**

このような構成とすることにより、差動増幅器60#では、ノードNoおよび/Noの負荷容量を均衡させることができる。差動増幅器60, 60'のように、ノードNoおよび/No間で負荷容量が不均衡である構成では、ノードNoおよび/No間に十分な電圧差

10

20

30

40

50

$V$ が生じるまでに要する時間(センス時間)が読出データのレベルによって変化するのに対して、相補型で構成された差動増幅器60#では、読出データのレベルによらずセンス時間を一定にできる。さらに、差動増幅動作における直流ゲインも大きくなるので、安定したデータ読出動作が実現できる。

#### 【0160】

なお、実施の形態1から4およびそれらの変形例に従う、図2、4、6、7、8、9および10にそれぞれ示したデータ読出回路系において、差動増幅器60、60'および60#のいずれを適用することも可能である。

#### 【0161】

また、実施の形態1から4およびそれらの変形例においては、相補のデータ線を用いたデータ読出動作を前提としているが、メモリアレイ10の構成については、これまで説明したように、2個のMTJメモリセルによって1ビットを記憶するメモリセル配置に限定されるものではない。10

#### 【0162】

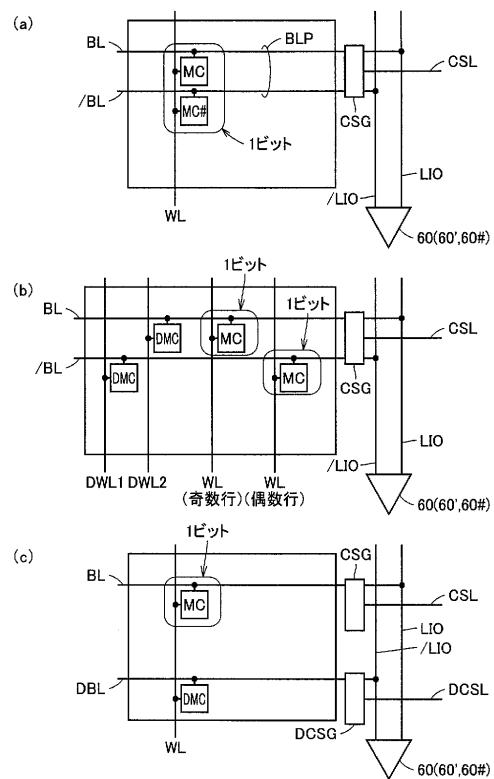

図12は、相補のデータ線によってデータ読出動作を行なうためのアレイ構成のバリエーションを説明する概念図である。

#### 【0163】

図12(a)には、実施の形態1から4およびそれらの変形例で示した、2個のMTJメモリセルによって1ビットを記憶するメモリセル配置が示される。この配置では、同一アドレスに対応する2個のメモリセルMCおよびMC#が相補のデータ線LIO(BL)および/LIO(/BL)とそれぞれ接続されて、相補データ線間の通過電流差に基づいたデータ読出が実行される。20

#### 【0164】

図12(a)に示したメモリセル配置は、記憶ビット数の2倍のMTJメモリセルが必要となるものの、実際に相補データを記憶しているMTJメモリセル間の通過電流差に応じてデータ読出を実行するため、トンネル磁気抵抗素子の製造特性のばらつきに追随して、高精度のデータ読出を実行することができる。

#### 【0165】

図12(b)および(c)には、中間的な電気抵抗を有するダミーメモリセルを用いたメモリセル配置が示される。ダミーメモリセルDMCは、メモリセルMCの2種類の記憶データレベル("1","0")にそれぞれ対応した電気抵抗RmaxおよびRminの中間値である電気抵抗Rmを有する。好ましくは、 $Rm = Rmin + R / 2$ ( $R = Rmax - Rmin$ )に設計される。通常、ダミーメモリセルDMCは、正規のMTJメモリセルMCと同様のトンネル磁気抵抗素子TMRを含むように設計される。30

#### 【0166】

ダミーメモリセルDMCを配置する構成では、1個のMTJメモリセルごとに1ビットのデータ記憶を実行するので、メモリセルの配置個数を削減することが可能となる。

#### 【0167】

図12(b)には、ダミーメモリセルDMCがダミー行を形成する配置例が示される。

#### 【0168】

この配置においては、各メモリセル行において、メモリセルMCは、ビット線BLまたは/BLのいずれかと接続される。たとえば、奇数行においてビット線BLと接続され、偶数行においてビット線/BLと接続されるように、メモリセルMCは交互配置される。40

#### 【0169】

詳細は図示しないが、ダミーメモリセルDMCは、2つのダミー行にわたって、正規のメモリセルMCとメモリセル列を共有するように配置される。さらに、ダミー行にそれぞれ対応して、ダミーワード線DWL1およびDWL2が配置される。ダミーメモリセルDMCは、それぞれのダミー行において、ビット線BLまたは/BLの一方と接続される。

#### 【0170】

このような配置とすることにより、ワード線WLおよびダミーワード線DWL1,DWL50

2の選択的な活性化によって、相補のデータ線LIO(BL)および/LIO(/BL)の一方ずつに、選択されたメモリセルMCおよびダミーメモリセルDMCをそれぞれ接続することができるので、相補データ線間の通過電流差に基づいたデータ読出が可能となる。

#### 【0171】

また、図12(c)に示されるように、ダミー列を形成するようにダミーメモリセルDMCを配置することもできる。ダミーメモリセルDMCは、正規のメモリセルMCとメモリセル行を共有するように配置され、さらに、ダミー列に対応してダミービット線DBLが設けられる。データ線LIOおよび/LIOは、選択列のビット線およびダミービット線DBLと接続される。

10

#### 【0172】

このような配置とすることにより、ワード線WLの選択的な活性化によって、相補のデータ線LIO(BL)および/LIO(DBL)に、選択されたメモリセルMCおよびダミーメモリセルDMCをそれぞれ接続することができるので、相補データ線間の通過電流差に基づいたデータ読出が可能となる。

#### 【0173】

すなわち、ダミーメモリセルDMCを配置して、1個のMTJメモリセルごとに1ビットのデータ記憶を実行する構成としても、実施の形態1から5およびそれらの変形例に従うデータ読出回路系の構成において、比較セルMC#に代えてダミーメモリセルDMCを適用することにより、同様のデータ読出動作を実行することが可能である。

20

#### 【0174】

##### [実施の形態6]

実施の形態6においては、中間的な電気抵抗を有する基準セル、すなわち図12(b), (c)に示したダミーメモリセルDMCの配置を前提としたデータ読出回路系の構成について説明する。

#### 【0175】

図13は、実施の形態6に従うデータ読出回路系の構成を示す回路図である。

図13を参照して、メモリアレイ10には、図12(b)と同様に、メモリセルMCおよびダミーメモリセルDMCが配置される。すなわち、ダミーメモリセルDMCは、2行にわたって、正規のメモリセルMCとメモリセル列を共有するように配置される。

30

#### 【0176】

各メモリセル列に対応して、互いに相補のビット線BLおよび/BLによって構成されるビット線対BLPjが配置される。各ビット線BLおよび/BLにそれぞれ対応して、プリチャージゲートPGおよび/PGが設けられる。各プリチャージゲートPGおよび/PGは、ビット線プリチャージ信号BLPRに応答して、対応するビット線BLおよび/BLの一端側を接地電圧Vssと結合する。

#### 【0177】

メモリセルMCは、奇数行においてビット線BLと接続され、偶数行においてビット線/BLと接続されるように、1行おきに交互配置される。メモリセルMCは、対応するビット線BLまたは/BLと接地電圧Vssとの間に接続される、トンネル磁気抵抗素子TMRおよびアクセス素子(アクセストランジスタ)ATRを有する。アクセストランジスタATRは、対応するワード線WLの活性化に応答してオンする。

40

#### 【0178】

ダミーメモリセルの行にそれぞれ対応して、ダミーワード線DWL1およびDWL2が配置される。ダミーワード線DWL1に対応するダミーメモリセル群は、対応するビット線/BLと接地電圧Vssとの間に接続される、ダミー磁気抵抗素子TMRdおよびダミーアクセス素子(アクセストランジスタ)ATRdを有する。ダミーアクセス素子ATRdは、奇数行の選択時に活性化されるダミーワード線DWL1に応じてオンする。

#### 【0179】

これに対して、ダミーワード線DWL2に対応するダミーメモリセル群は、対応するビッ

50

ト線 B L と接地電圧 V s s との間に接続される、ダミー磁気抵抗素子 T M R d および、ダミーアクセス素子（アクセストランジスタ）A T R d を有する。ダミーアクセス素子 A T R d は、偶数行の選択時に活性化されるダミーワード線 D W L 2 に応じてオンする。

#### 【 0 1 8 0 】

各ダミーメモリセル D M C の電気抵抗 R m は、 $R m = R m i n + ( R / 2 )$  に設計される。たとえば、電気抵抗 R m i n に対応するデータを記憶した、メモリセル M C と同様のトンネル磁気抵抗素子 T M R によってダミー磁気抵抗素子 T M R d を構成し、かつ、ダミーアクセス素子 A T R d のオン抵抗をアクセストランジスタ A T R よりも  $R / 2$  大きく設定することによって、ダミーメモリセル D M C が構成される。あるいは、ダミーアクセス素子 A T R d とアクセストランジスタ A T R のオン抵抗を同様に設計し、ダミー磁気抵抗素子 T M R d を、電気抵抗 R m i n に対応するデータを記憶するトンネル磁気抵抗素子 T M R と電気抵抗が  $R / 2$  の固定抵抗との直列接続によって、ダミーメモリセル D M C を構成することもできる。10

#### 【 0 1 8 1 】

図 13においては、第 1 番目および第 2 番目のメモリセル列に対応するワード線 W L 1 , W L 2 およびディジット線 D L 1 , D L 2 と、第 j 番目のメモリセル列に対応するビット線 B L j および / B L j と、これらに対応するメモリセル M C およびダミーメモリセル D M C が代表的に示される。

#### 【 0 1 8 2 】

実施の形態 6 に従う構成においては、各メモリセル列に対応して配置されるコラム選択ゲート C S G と、メモリアレイ 10 に隣接して配置される相補のデータバス D B および / D B がさらに設けられる。データバス D B および / D B は、データバス対 D B P を構成する。20

#### 【 0 1 8 3 】

コラム選択ゲート C S G は、ビット線 B L および / B L の他端側と、データバス D B および / D B との間に接続され、対応するコラム選択線 C S L の活性化に応答してオンする。たとえば、コラム選択ゲート C S G j は、コラム選択線 C S L j の活性化に応答して、対応するビット線 B L j および / B L j の他端側をデータバス D B および / D B とそれぞれ接続する。

#### 【 0 1 8 4 】

実施の形態 6 に従うデータ読出回路 110 は、電源電圧 V c c およびノード / N o の間に設けられ一定電流 I s をノード / N o へ供給する電流源 120 と、ノード / N o およびデータバス / D B の間に電気的に結合されるトランジスタ 122 と、ノード / N o と接地電圧 V s s との間に接続される電流検出抵抗 124 とを含む。30

#### 【 0 1 8 5 】

データ読出回路 110 は、さらに、電源電圧 V c c およびノード N o の間に設けられ一定電流 I s をノード N o へ供給する電流源 125 と、ノード N o およびデータバス D B の間に電気的に結合されるトランジスタ 127 と、ノード N o と接地電圧 V s s との間に接続される電流検出抵抗 129 とをさらに含む。電流検出抵抗 124 および 129 の電気抵抗は、同一値 R L に設定される。40

#### 【 0 1 8 6 】

データ読出回路 110 は、データバス D B および / D B の所定の一方と、所定の基準電圧 V r との電圧差を増幅して帰還電圧 V f b を生成する電圧増幅器 130 と、ノード N o および / N o 間の電圧差を増幅して読出データ D O U T を生成する電圧増幅器 140 とをさらに含む。図 13 では、電圧増幅器 130 の入力側とデータバス / D B とが接続される回路構成例を示したが、他方のデータバス D B を電圧増幅器 130 の入力側とすることもできる。電圧増幅器 130 が出力する帰還電圧 V f b は、トランジスタ 122 および 127 の各ゲートへ入力される。基準電圧 V r は、実施の形態 1 における基準電圧 V r e f と同様に設定される。

#### 【 0 1 8 7 】

10

20

30

40

50

データ読出前においては、各ワード線 W L は非活性化されているので、ビット線 B L および / B L と、メモリセル M C およびダミーメモリセル D M C の間は切離される。また、ビット線プリチャージ信号 B L P R が活性化されているので、ビット線 B L および / B L の各々は、接地電圧 V s s へプリチャージされる。

#### 【 0 1 8 8 】

さらに、各コラム選択線 C S L も非活性化されているので、データバス D B および / D B は、各ビット線 B L および / B L から切離されている。したがって、電圧増幅器 1 3 0 、トランジスタ 1 2 2 , 1 2 7 によって構成されるデータ線電圧クランプ部によって、データバス D B および / D B の各々は、データ読出に先立って所定電圧 V r にクランプされる。

10

#### 【 0 1 8 9 】

データ読出時には、ビット線プリチャージ信号 B L P R は非活性化されて、各ビット線 B L , / B L は、接地電圧 V s s から切離される。さらに、アドレス選択に応じて、選択行のワード線、選択列のコラム選択線およびダミーワード線 D W L 1 および D W L 2 の一方が選択的に活性化される。

#### 【 0 1 9 0 】

これに応じて、データバス D B および選択列のビット線 B L は、選択されたメモリセル M C およびダミーメモリセル D M C の一方を介して、電源電圧 V c c および接地電圧 V s s の間に電気的に結合される。同様に、データバス / D B および選択列のビット線 / B L は、選択されたメモリセル M C およびダミーメモリセル D M C の他方を介して、電源電圧 V c c および接地電圧 V s s の間に電気的に結合される。

20

#### 【 0 1 9 1 】

データ読出時においても、電圧増幅器 1 3 0 、トランジスタ 1 2 2 , 1 2 7 によって構成されるデータ線電圧クランプ部は、データ読出前と同様に、データバス D B および / D B の各々を所定電圧 V r にクランプする。特に、データバス / D B がダミーメモリセル D M C と接続される場合には、ダミーメモリセル D M C の通過電流に基づいて、データバス D B および / D B のクランプ動作を実行できる。

#### 【 0 1 9 2 】

したがって、データ読出回路 1 1 0 は、データバス D B , / D B および選択列のビット線 B L , / B L が上記の所定電圧にクランプされた状態で、選択されたメモリセル M C およびダミーメモリセル D M C の電気抵抗差 ( R / 2 ) に応じた電流差を、データバス D B および / D B の通過電流間に生じさせる。

30

#### 【 0 1 9 3 】

データバス D B および / D B の通過電流差に応じて、同一の電気抵抗 R L を有する電流検出抵抗 1 2 4 および 1 2 9 の間にも通過電流差が発生し、これに応じて、ノード N o および / N o の間に、選択されたメモリセル M C の記憶データに応じた電圧差が発生する。この結果、電圧増幅器 1 3 0 は、選択されたメモリセル M C の記憶データのレベルを反映した読出データ D O U T を生成できる。

#### 【 0 1 9 4 】

なお、データバス D B とダミーメモリセル D M C が接続された場合でも、電圧増幅器 1 3 0 の入力側とデータバス D B および / D B との間の接続を特に切換えなくとも、選択されたメモリセル M C およびダミーメモリセル D M C の通過電流差に基づいた同様のデータ読出動作が実行できる。しかし、データバス D B , / D B の電圧クランプ動作を、ダミーメモリセル D M C の通過電流に基づいて厳密に実行したい場合には、ダミーワード線 D W L 1 , D W L 2 の選択と連動させて、電圧増幅器 1 3 0 の入力側とデータバス D B および / D B との間の接続を切換える構成としてもよい。

40

#### 【 0 1 9 5 】

以上説明したように、このように、実施の形態 6 に従う構成においては、基本的にデータバス D B , / D B および選択列のビット線 B L および / B L の電圧を一定レベルに維持した上でデータ読出動作を実行できる。したがって、比較的大きな寄生容量を有するこれら

50

のデータ線の充放電を伴うことなく、高速にデータ読出を実行できる。

**【0196】**

特に、データ読出前においても、寄生容量の大きいデータバスDBおよび/DBを、データ読出時と同様の所定電圧にクランプしているため、データ読出開始時においてもデータバスDBおよび/DBの充放電が不要である。この結果、データ読出動作をさらに高速化できる。

**【0197】**

また、データバスDB, /DBの電圧クランプ動作を、ダミーメモリセルDMCの通過電流、すなわち実際の電気抵抗に基づいて実行できるので、製造プロセス変動に起因するMTJメモリセルの電気抵抗特性のばらつきに追随させて、データ読出動作点（最大電圧振幅を得られる点）を確保できる。

**【0198】**

[実施の形態6の変形例]

実施の形態6においては、正規のMTJメモリセルと同一アレイ内に基準セル（ダミーメモリセル）を行列状に配置する構成を示したが、実施の形態6の変形例においては、基準セルをメモリアレイ外に配置する場合のデータ読出回路系の構成について説明する。

**【0199】**

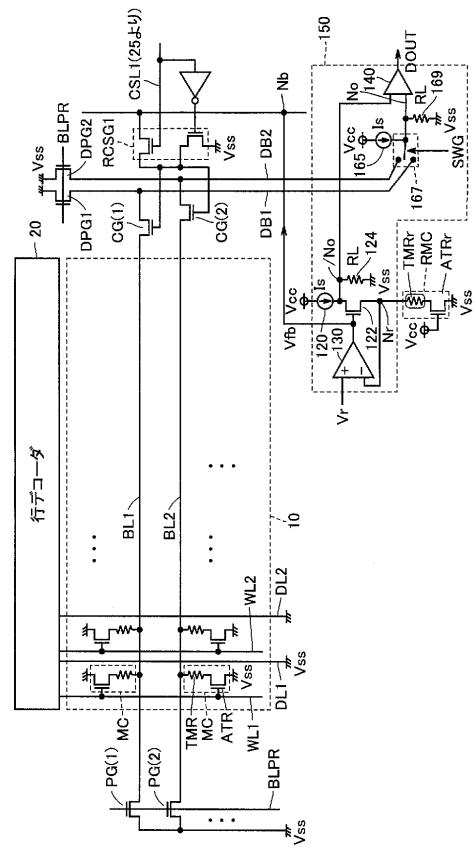

図14は、実施の形態6の変形例に従うデータ読出回路系の構成を示す回路図である。

**【0200】**

図14を参照して、実施の形態6の変形例に従う構成においては、メモリアレイ10内には、データ記憶を実行するための正規のメモリセルMCが、行列状に配置されている。

**【0201】**

各メモリセル列に対応して、ビット線BLが配置される。各ビット線BLに対応して、プリチャージゲートPGが設けられる。各プリチャージゲートPGは、ビット線プリチャージ信号BLPRに応答して、対応するビット線BLの一端側を接地電圧Vssと結合する。メモリセルMCは、ワード線WLとビット線BLとの交点にそれぞれ対応して配置される。図14においては、第1番目および第2番目のメモリセル行と、第1番目および第2番目のメモリセル列に対応する4個のメモリセル列と、これらに対応する信号線群が代表的に示されている。

**【0202】**

実施の形態6の変形例に従う構成においては、2本のデータバスDB1およびDB2が配置される。データバスDB1およびDB2にそれぞれ対応して、DPG1およびDPG2が設けられる。プリチャージゲートDPG1およびDPG2は、ビット線プリチャージ信号BLPRに応答して、データバスDB1およびDB2を接地電圧Vssへプリチャージする。

**【0203】**

コラム選択線CSLは、データバスDBの配置本数に合せて、2個のメモリセル列ごとに配置される。たとえば、図14に示されたコラム選択線CSL1は、第1番目および第2番目のメモリセル列に共通して設けられ、第1番目もしくは第2番目のメモリセル列が選択された場合にHレベルに活性化される。

**【0204】**

メモリセル列にそれぞれ対応して設けられるコラム選択ゲートCG(1), CG(2), ...によって、奇数列のビット線の他端側はデータバスDB1と接続され、偶数列のビット線の他端側は、データバスDB2と電気的に結合される。たとえば、ビット線BL1は、コラム選択ゲートCG(1)を介して、データバスDB1と電気的に結合され、ビット線BL2は、コラム選択ゲートCG(2)を介して、データバスDB2と電気的に結合される。コラム選択ゲートCG(1), CG(2), ...の各々は、たとえばNチャネルMOSトランジスタで構成される。以下においては、コラム選択ゲートCG(1), CG(2), ...を総称する場合には、コラム選択ゲートCGとも称する。

**【0205】**

10

20

30

40

50

さらに、同一のコラム選択線 C S L を共有するメモリセル列ごとに、リード選択ゲート R C S G が配置される。リード選択ゲート R C S G は、対応するコラム選択線が活性化された場合に、コラム選択ゲート C G のゲートをノード N b と接続する。たとえば、コラム選択線 C S L 1 の活性化に応答して、リード選択ゲート R C S G 1 は、コラム選択ゲート C G ( 1 ) および C G ( 2 ) の各ゲートは、ノード N b と接続される。

#### 【 0 2 0 6 】

一方、リード選択ゲート R C S G は、対応するコラム選択線が非活性化される場合には、対応するコラム選択ゲート C G のゲートを接地電圧 V s s と接続する。これにより、非選択のコラム選択線に対応するコラム選択ゲート C G の各々は、オフされる。

#### 【 0 2 0 7 】

メモリアレイ 1 0 外に基準セルとして配置されるレプリカメモリセル R M C は、基準ノード N r と接地電圧 V s s との間に接続される。レプリカメモリセル R M C は、図 1 3 に示したダミーメモリセル D M C と同様の電気抵抗 R m を有し、直列に接続されたレプリカ磁気抵抗素子 T M R r と、レプリカアクセス素子 A T R r とを有する。レプリカ磁気抵抗素子 T M R r およびレプリカアクセス素子 A T R r は、ダミーメモリセル D M C 中のダミー磁気抵抗素子 T M R d およびダミーアクセス素子 A T R d のそれぞれと同様に設計される。レプリカアクセス素子 A T R r のゲートは電源電圧 V c c に固定され、常時オン状態に設定される。

#### 【 0 2 0 8 】

実施の形態 6 の変形例に従うデータ読出回路 1 5 0 は、電流源 1 2 0 と、トランジスタ 1 2 2 と、電流検出抵抗 1 2 4 と、電圧増幅器 1 3 0 , 1 4 0 とを含む。電圧増幅器 1 3 0 は、レプリカメモリセル R M C を介して接地電圧 V s s と結合された基準ノード N r と所定の基準電圧 V r との電圧差を増幅して、帰還電圧 V f b をノード N b へ出力する。トランジスタ 1 2 2 は、基準ノード N r とノード N o との間に電気的に結合されて、ゲートへ帰還電圧 V f b を受ける。

#### 【 0 2 0 9 】

データ読出回路 1 5 0 は、さらに、電源電圧 V c c およびノード N o の間に設けられ一定電流 I s をノード / N o へ供給する電流源 1 6 5 と、データバス D B 1 および D B 2 とノード N o との間の接続を切換えるための選択スイッチ 1 6 7 と、ノード N o と接地電圧 V s s との間に接続される電流検出抵抗 1 6 9 とをさらに含む。電流検出抵抗 1 2 4 および 1 6 9 の電気抵抗は、同一値 R L に設定される。

#### 【 0 2 1 0 】

選択スイッチ 1 6 7 は、制御信号 S W G に応答して、データバス D B 1 および D B 2 のうちの選択メモリセルと結合される一方をノード N o と接続する。たとえば、制御信号 S W G は、選択メモリセルが偶数列および奇数列のいずれに属するかを示す 1 ビット信号で構成することができる。

#### 【 0 2 1 1 】

データ読出前においては、各ワード線 W L および各コラム選択線は非活性化され、かつビット線プリチャージ信号 B L P R が活性化される。したがって、各ビット線 B L は、メモリセル M C と切離されて、接地電圧 V s s へプリチャージされる。さらに、データバス D B および / D B も、接地電圧 V s s へプリチャージされる。

#### 【 0 2 1 2 】

データ読出時には、ビット線プリチャージ信号 B L P R は非活性化されて、各ビット線 B L , / B L およびデータバス D B 1 , D B 2 の各々は、接地電圧 V s s から切離される。さらに、アドレス選択に応じて、選択行のワード線および選択列のコラム選択線が選択的に活性化される。また、選択スイッチ 1 6 7 によって、データバス D B 1 および D B 2 の一方が、ノード N o と接続される。

#### 【 0 2 1 3 】

これに応じて、選択列のコラム選択ゲート C G を構成する M O S トランジスタのゲートには、トランジスタ 1 2 2 のゲートと同様に、基準ノード N r を基準電圧 V r に維持するた

めの帰還電圧  $V_{fb}$  が入力される。したがって、電圧増幅器 130、トランジスタ 122 および選択列のコラム選択ゲート CG によって構成されるデータ線電圧クランプ部によって、選択列のビット線は、レプリカメモリセル RMC の通過電流に基づいて、所定電圧  $V_r$  にクランプされる。

#### 【0214】

これに応じて、データバス DB1 および DB2 の選択された一方および選択列のビット線 BL は、選択されたメモリセル MC を介して、電源電圧  $V_{cc}$  および接地電圧  $V_{ss}$  の間に電気的に結合される。同様に、基準ノードは、レプリカメモリセル RMC を介して、電源電圧  $V_{cc}$  および接地電圧  $V_{ss}$  の間に電気的に結合される。

#### 【0215】

したがって、データ読出回路 110 は、基準ノード  $N_r$  および選択列のビット線 BL が上記の所定電圧にクランプされた状態で、選択されたメモリセル MC およびレプリカメモリセル RMC の電気抵抗差 ( $R/2$ ) に応じた電流差を、選択されたデータバスおよび基準ノード  $N_r$  の通過電流間に生じさせる。

#### 【0216】

これに応じて、同一の電気抵抗 RL を有する電流検出抵抗 124 および 159 によって、ノード  $N_o$  および  $\bar{N}_o$  の間に、選択されたメモリセル MC の記憶データに応じた電圧差が発生される。この結果、電圧増幅器 130 は、実施の形態 6 と同様に読出データ DOUT を生成できる。

#### 【0217】

このような構成とすることにより、実施の形態 6 に従うデータ読出動作と同様に、高速かつ高精度にデータ読出を実行することができる。また、行列状に配置されたダミーメモリセル DMC に代えて、1 個のレプリカメモリセル RMC を配置すればよいため、実施の形態 6 に従う構成と比較して、メモリアレイ 10 の面積を小型化できる。

#### 【0218】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

#### 【0230】

#### 【発明の効果】

請求項 1～5 に記載の半導体集積回路は、選択メモリセルと接続されるデータ線の電圧をクランプした上でデータ読出動作を実行できる。したがって、比較的大きな寄生容量を有するこれらのデータ線の充放電を伴うことなく、高速にデータ読出を実行できる。また、データ線電圧のクランプ動作を、基準セルの通過電流、すなわち実際の電気抵抗に基づいて実行できるので、製造プロセス変動に起因する電気抵抗特性のばらつきに追随させて、データ読出精度を確保できる。

#### 【図面の簡単な説明】

【図 1】 本発明の実施の形態に従う MRAM デバイス 1 の全体構成を示す概略ブロック図である。

【図 2】 メモリアレイおよびその周辺回路の実施の形態 1 に従う構成を示す回路図である。

【図 3】 実施の形態 1 に従う MRAM デバイスにおけるデータ読出動作を説明する動作波形図である。

【図 4】 メモリアレイおよびその周辺回路の実施の形態 2 に従う構成を示す回路図である。

【図 5】 実施の形態 2 に従う MRAM デバイスにおけるデータ読出動作を説明する動作波形図である。

【図 6】 実施の形態 3 に従うデータ読出回路系の構成を示す回路図である。

【図 7】 実施の形態 3 の変形例 1 に従うデータ読出回路系の構成を示す回路図である。

10

20

30

40

50

【図 8】 実施の形態 3 の変形例 2 に従うデータ読出回路系の構成を示す回路図である。

【図 9】 メモリアレイおよびその周辺回路の実施の形態 4 に従う構成を示す回路図である。

【図 10】 メモリアレイおよびその周辺回路の実施の形態 4 の変形例に従う構成を示す回路図である。

【図 11】 実施の形態 5 に従う差動増幅器の構成を示す回路図である。

【図 12】 相補のデータ線によってデータ読出動作を行なうためのアレイ構成のバリエーションを説明する概念図である。

【図 13】 実施の形態 6 に従うデータ読出回路系の構成を示す回路図である。

【図 14】 実施の形態 6 の変形例に従うデータ読出回路系の構成を示す回路図である。 10

【図 15】 MTJ メモリセルの構成を示す概略図である。

【図 16】 MTJ メモリセルに対するデータ書き込み動作を説明する概念図である。

【図 17】 データ書き込みにおけるデータ書き込み電流とトンネル磁気抵抗素子の磁化方向との関係を説明する概念図である。

【図 18】 MTJ メモリセルからのデータ読み出しを説明する概念図である。

【図 19】 従来の技術に従う MRAM デバイスのデータ読み出し回路の構成を示す回路図である。

#### 【符号の説明】

1 MARAM デバイス、 10 , 10L , 10R メモリアレイ、 20 行デコーダ、 2

5 列デコーダ、 50 , EQG イコライズ回路、 60 , 60' , 60# , 92 差動増

幅器、 80 , 85 データ伝達回路、 90 メインアンプ、 110 , 150 データ読み出

回路、 120 , 125 , 155 電流源、 124 , 129 , 159 電流検出抵抗、 13

0 , 140 電圧増幅器、 167 選択スイッチ、 /SEL , /SEL0 ~ /SELn センス

イネーブル信号、 /SEL0 ~ /SELn ブロック選択信号、 ATR アクセストラン

ジスタ、 ATRd ダミーアクセス素子、 ATRr レプリカアクセス素子、 BL , /B

L , BLL , /BLL , BLR , /BLR ビット線、 CG , CSG コラム選択ゲート

、 CSL コラム選択線、 DB , /DB データバス、 LIO , /LIO データ線、 D

L ディジット線、 DMC ダミーメモリセル、 DOUT 読出データ、 DWL1 , DW

L2 ダミーワード線、 GIO , /GIO グローバルデータ線、 LIO , /LIO デ

タ線、 MB メモリブロック、 MC メモリセル、 MC# 比較セル、 Nb , No , /N

o ノード、 Nr 基準ノード、 RMC レプリカメモリセル、 Rmax , Rmin 電

気抵抗、 SA センスアンプ、 TMR トンネル磁気抵抗素子、 TMRe d ダミー磁気抵

抗素子、 TMRe r レプリカ磁気抵抗素子、 Vcc 電源電圧、 Vfb 帰還電圧、 Vr

, Vref 基準電圧、 Vss 接地電圧、 WL ワード線、 I 電流差、 R 電気

抵抗差、 V 電圧差。

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(74)代理人 100085132

弁理士 森田 俊雄

(74)代理人 100091409

弁理士 伊藤 英彦

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100096792

弁理士 森下 八郎

(72)発明者 谷崎 弘晃

東京都千代田区大手町二丁目 6 番 2 号 三菱電機エンジニアリング株式会社内

(72)発明者 日高 秀人

東京都千代田区丸の内二丁目 2 番 3 号 三菱電機株式会社内

(72)発明者 大石 司

東京都千代田区丸の内二丁目 2 番 3 号 三菱電機株式会社内

審査官 滝谷 亮一

(56)参考文献 特許第 6 1 9 1 9 8 9 ( J P , B 2 )

国際公開第 0 1 / 0 7 5 8 9 1 ( WO , A 1 )

特開平 0 8 - 1 4 7 9 9 1 ( J P , A )

特開 2 0 0 1 - 2 5 6 7 8 3 ( J P , A )

特開昭 6 3 - 1 4 2 5 9 8 ( J P , A )

特開 2 0 0 2 - 1 9 7 8 5 3 ( J P , A )

米国特許第 5 8 5 9 7 9 8 ( U S , A )

Roy Scheuerlin, William Gallagher, Stuart Parkin, Alex Lee, Sam Ray, Ray Robertazzi, William Reohr, A 10 ns Read and Write Non-Volatile Memory Array Us, 2000 IEEE International Solid State Circuit Confer, 米国, IEEE, 2000年 2月, p. 128-129

(58)調査した分野( Int.CI. , DB 名)

G11C 11/15

G11C 16/02-16/06