(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 697 37 375 T2 2007.11.29**

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 445 995 B1

(21) Deutsches Aktenzeichen: **697 37 375.4**

(96) Europäisches Aktenzeichen: **04 011 179.1**

(96) Europäischer Anmeldetag: **26.12.1997**

(97) Erstveröffentlichung durch das EPA: **11.08.2004**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **14.02.2007**

(47) Veröffentlichungstag im Patentblatt: **29.11.2007**

(51) Int Cl.<sup>8</sup>: **H05K 3/32 (2006.01)**

**H01L 21/60 (2006.01)**

**H01L 21/56 (2006.01)**

**H01L 23/498 (2006.01)**

**H01L 21/48 (2006.01)**

(30) Unionspriorität:

**35073896 27.12.1996 JP**

(74) Vertreter:

**Eisenführ, Speiser & Partner, 80335 München**

(73) Patentinhaber:

**Matsushita Electric Industrial Co., Ltd., Kadoma,

Osaka, JP**

(84) Benannte Vertragsstaaten:

**DE, FI, FR, GB, NL, SE**

(72) Erfinder:

**Nishida, Kazuto, Osaka 576-0052, JP**

(54) Bezeichnung: **Verfahren zur Befestigung eines elektronischen Bauteils auf einer Leiterplatte und System zum Ausführen des Verfahrens**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Gebiet der Technik**

**[0001]** Die vorliegende Erfindung betrifft ein Verfahren und ein System gemäß Anspruch 1 und 3 zum Bestücken einer Leiterplatte mit einem elektronischen Bauelement. Insbesondere betrifft die vorliegende Erfindung ein Verfahren und ein System zum Bestücken einer Leiterplatte für eine elektronische Schaltung mit einem einzelnen elektronischen Bauelement, beispielsweise einem IC-Chip oder einem Oberflächenwellen-Bauelement (SAW-Bauelement) (im Falle des IC-Chip in Form eines gehäuselosen IC).

**Stand der Technik**

**[0002]** Heutzutage werden Leiterplatten mit elektronischen Schaltungen in einer Vielzahl von Produkten verwendet, und ihre Leistungsfähigkeit wird von Tag zu Tag gesteigert. Auch werden auf den Leiterplatten immer höhere Frequenzen verwendet, und somit ist die Flip-Chip-Montage, die niedrige Impedanz gewährleistet, das geeignete Bestückungsverfahren für elektronische Bauelemente, die mit hohen Frequenzen arbeiten. In Anbetracht von immer mehr tragbaren Geräten wird die Flip-Chip-Montage zum Montieren von IC-Chips ohne Gehäuse auf Leiterplatten benötigt. Aus diesem Grund ergibt sich unter den IC-Chips, die einzeln auf einer Leiterplatte montiert werden, und IC-Chips, die auf elektronischen Bauelementen und Flachbildschirmelementen montiert werden, eine gewisse Anzahl von fehlerhaften Chips. Neben den vorgenannten Flip-Chip-Bauelementen werden auch immer mehr CSP-Bauelemente (Chip-Size-Package-Elemente), BGA-Bauelemente (Ball-Grid-Array-Bauelemente) und dergleichen verwendet.

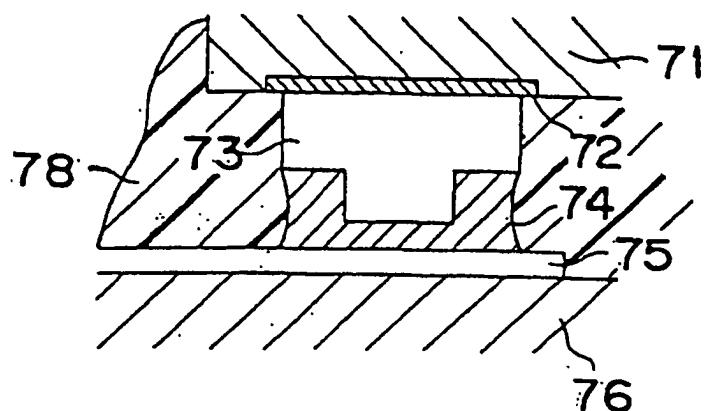

**[0003]** Ein herkömmliches Verfahren (erstes Beispiel nach dem Stand der Technik) zum Bonden eines IC-Chips auf der Leiterplatte eines elektronischen Geräts ist das in der geprüften japanischen Patentveröffentlichung Nr. 06-66355 usw. offenbarte Verfahren. Es ist in [Fig. 1](#) dargestellt. Wie in [Fig. 1](#) gezeigt, wird nach dem allgemein bekannten Verfahren Ag-Paste **74** auf Löthöcker **73** auf einem IC-Chip **71** aufgebracht, die Ag-Paste **74** mit Elektroden **75** auf einer Leiterplatte **76** verbunden, die Ag-Paste **74** dann gehärtet und anschließend Verkapselungsmaterial **78** in den Raum zwischen dem IC-Chip **71** und der Leiterplatte **76** gegossen.

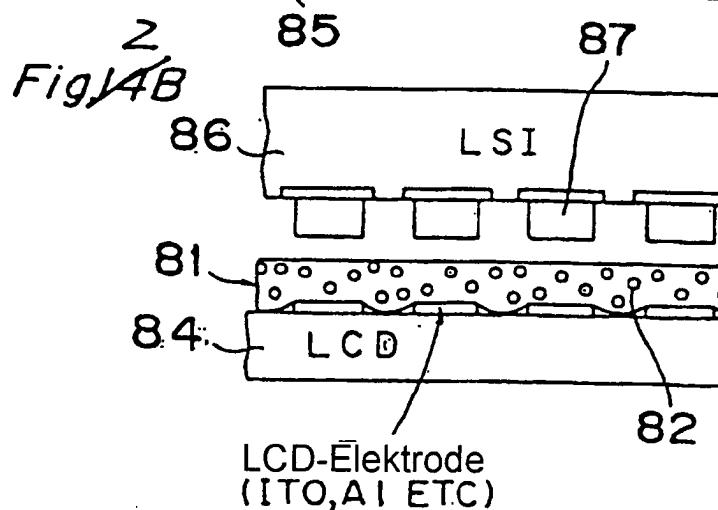

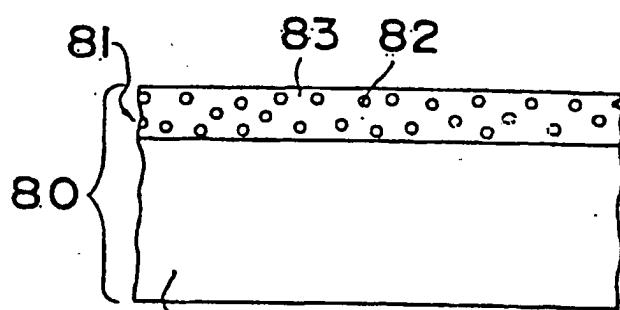

**[0004]** Als Verfahren (zweites Beispiel nach dem Stand der Technik) zum Bonden eines IC-Chips auf einer Flüssigkristallanzeige ist allgemein die Halbleiter-Chip-Verbindungskonstruktion bekannt, die eine anisotrope leitfähige Schicht **80** verwendet, wie sie in der geprüften japanischen Patentveröffentlichung Nr.

62-6652 offenbart und in [Fig. 2](#) gezeigt ist. Bei dieser Konstruktion wird eine anisotrope leitfähige Klebeschicht **81**, die durch Einbringen leitfähiger Teilchen **82** in ein isolierendes Harz **83** gebildet wird, von einer Trennschicht **85** abgezogen und auf das Substrat oder die Glasplatte einer Flüssigkristallanzeige **84** aufgebracht. Durch Befestigen des IC-Chips **86** mittels Thermokompression wird die anisotrope leitfähige Klebeschicht **81** zwischen die Unterseite des IC-Chips **86** und das Substrat **84** eingebracht, wobei die Abschnitte unter den Au-Löthöckern **87** ausgespart werden.

**[0005]** Als drittes Beispiel für den Stand der Technik ist ein Verfahren bekannt, nach dem ein Substrat mit einem unter UV-Licht aushärtenden Harz beschichtet wird, ein IC-Chip auf dem Substrat montiert wird und das Harz unter Druck mit UV-Licht bestrahlt wird, wodurch das Harz zwischen dem IC-Chip und dem Substrat aushärtet und der Kontakt zwischen den beiden durch die Schrumpfungskraft des Harzes erhalten bleibt.

**[0006]** Wie vorstehend beschrieben, wurde die Montage eines IC-Chips ausgeführt, indem ein IC-Chip, beispielsweise mit flachem Gehäuse, durch Druckboden in eine Schaltung eingebaut, die Elektroden des IC-Chips durch Kontaktieren mit der Schaltung verbunden, ein Gehäuse durch Harzguß gebildet, anschließend Lötpaste auf eine Leiterplatte gedrückt, der IC mit dem flachen Gehäuse auf der Leiterplatte montiert und die Paste aufgeschmolzen wurden. Bei dem vorstehenden sogenannten SMT-Verfahren (Surface Mount Technology) konnte die Leiterplatte wegen des langen Verfahrens und der langen Fertigungsdauer nur schwer verkleinert werden. Beispielsweise benötigt ein in einem flachen Gehäuse verkapselfter IC-Chip etwa die vierfache Fläche des IC-Chips, eine Tatsache, die der Verkleinerung entgegenstand.

**[0007]** Demgegenüber wird seit kurzem öfter das Flip-Chip-Verfahren verwendet, nach dem ein IC-Chip ohne Gehäuse direkt montiert wird, um eine Abkürzung des Verfahrens und eine kleine, leichte Konstruktion zu erhalten. Dieses Flip-Chip-Verfahren wurde in vielen Ausgestaltungen entwickelt, beispielsweise als stud bump bonding (SBB) mit Höckerbildung an einem IC-Chip, Höckereinebnung, Aufbringen von AgPd-Paste, Montage, Prüfung, Verkapselung mit Verkapselungsharz und Prüfung und UV-Harzboden zum gleichzeitigen Höckerbilden an einem IC-Chip und UV-Aushärten des Harzes, mit dem die Leiterplatte beschichtet ist, und anschließend Montage, UV-Aushärten des Harzes und Prüfung.

**[0008]** Allerdings hatte jedes der Verfahren den Nachteil, dass für das Aushärten der Paste zum Verbinden der Löthöcker des IC-Chips mit den Elektro-

den der Leiterplatte und für das Beschichten mit dem Verkapselungsharz und seine Aushärtung viel Zeit erforderlich ist, was die Produktivität verringert. Außerdem muss für die Leiterplatte Keramik oder Glas verwendet werden, was den Nachteil hoher Kosten mit sich bringt. Nach dem Verfahren, bei dem wie beim ersten Beispiel für den Stand der Technik leitfähige Paste als Bondiermaterial verwendet wird, müssen die Höcker des IC-Chips eingeebnet und vor Verwendung abgeflacht werden, um die Transfermontage zu stabilisieren.

**[0009]** Für die Verbindungskonstruktion, bei der wie im zweiten Beispiel für den Stand der Technik der anisotrope leitfähige Kleber verwendet wird, wurde eine Konstruktion entwickelt, bei der Glas als Basismaterial der Leiterplatte verwendet wird. Jedoch ist es schwierig, die leitfähigen Partikel gleichmäßig im leitfähigen Kleber zu verteilen, so dass es durch die ungleichmäßige Verteilung der Teilchen zu Kurzschlüssen kommt und der leitfähige Kleber teuer wird.

**[0010]** Bei dem Verbindungsverfahren, bei dem das Harz durch UV-Licht ausgehärtet wird wie beim dritten Beispiel für den Stand der Technik, gibt es das Problem, dass Höhenunterschiede der Höcker nur  $\pm 1 \mu\text{m}$  betragen dürfen und Verbindungen auf einer nicht einwandfrei ebenen Leiterplatte, beispielsweise einer Kunstharzleiterplatte (Glasepoxid-Leiterplatte), nicht hergestellt werden können. Bei dem Verfahren mit Lötmittel musste Verkapselungsharz vergossen und ausgehärtet werden, um Unterschiede in der Wärmeausdehnung und der Kontraktion der Leiterplatte und des IC-Chip nach dem Bonden abzumildern. Diese Harzverkapselung dauert zwei bis vier Stunden, was zu dem Problem einer deutlich geringen Produktivität geführt hat.

**[0011]** Die deutsche Offenlegungsschrift 195 35 282 offenbart ein Verfahren zum Bestücken von Leiterplatten mit elektronischen Bauelementen, bei dem Wärme und Druck zur Montage der Bauelemente eingesetzt werden. Bei dem Bestückungsverfahren wird ein elektrisch nicht leitender Kleber zwischen dem elektronischen Bauelement und der Leiterplatte verwendet. Dieser elektrisch nicht leitende Kleber kann Füllstoffe enthalten, die festgelegte mechanische, elektrische, thermische und/oder chemische Eigenschaften aufweisen, um ein definiertes Aushärten des Klebers zu bewirken.

**[0012]** Außerdem offenbart die europäische Patentanmeldung 0 475 022 ein Verfahren zum direkten Anbringen von Halbleiterchips auf einem Substrat oder Modul mit einer Polymerzwischenschicht.

**[0013]** In Anbetracht der genannten Probleme beim Stand der Technik hat die vorliegende Erfindung die Aufgabe, ein Verfahren und ein System zum Bestücken einer Leiterplatte mit elektronischen Bauele-

menten zur Verfügung zu stellen, wobei das direkte Bonden des elektronischen Bauelements auf der Leiterplatte bei hoher Produktivität vorgesehen ist.

#### Offenbarung der Erfindung

**[0014]** Um die genannten Probleme zu lösen, ist die vorliegende Erfindung wie folgt gestaltet: Gemäß dem ersten Aspekt der Erfindung wird ein Bestückungsverfahren nach Anspruch 1 zur Verfügung gestellt.

**[0015]** Gemäß dem zweiten Aspekt der Erfindung wird ein Bestückungsverfahren gemäß dem ersten Aspekt zur Verfügung gestellt, wobei der warmaus härtende Harzbogen eine Dicke hat, die größer ist als der Abstand zwischen der aktiven Oberfläche des elektronischen Bauelements und der zur Leiterplatte gehörenden Oberfläche, auf der die Elektroden nach dem Bonden gebildet werden.

**[0016]** Gemäß dem dritten Aspekt der Erfindung wird ein Bestückungssystem nach Anspruch 3 zur Verfügung gestellt.

**[0017]** Außerdem wird nach dem vierten Aspekt der Erfindung ein Bestückungssystem nach dem dritten Aspekt zur Verfügung gestellt, bei dem der warmaus härtende Harzbogen dicker ist als der Abstand zwischen der aktiven Oberfläche des elektronischen Bauelements und der zur Leiterplatte gehörenden Oberfläche, auf der die Elektroden nach dem Bonden gebildet werden.

#### Kurzbeschreibung der Zeichnungen

**[0018]** Die genannten und weitere Aspekte und Merkmale der vorliegenden Erfindung werden aus nachstehender Beschreibung anhand der bevorzugten Ausführungsbeispiele und unter Bezugnahme auf die beigefügten Zeichnungen deutlich, die folgendes zeigen:

**[0019]** [Fig. 1](#): ein Schnittbild, das ein Verfahren zum Befestigen eines IC-Chips an einer Leiterplatte nach dem Stand der Technik zeigt;

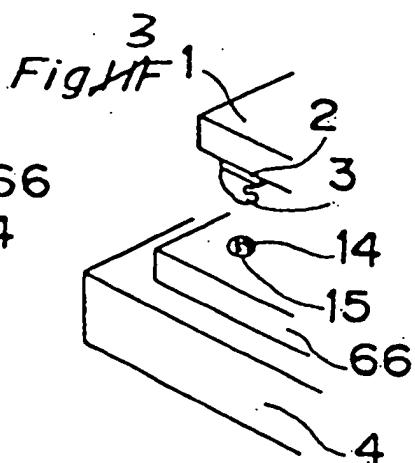

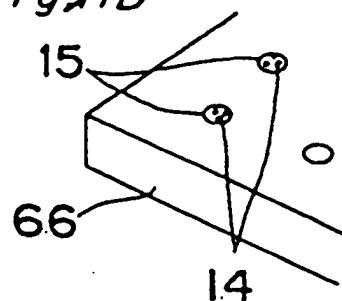

**[0020]** [Fig. 2A](#) und [Fig. 2B](#): Ansichten zur Erläuterung eines bekannten Verfahrens zum Befestigen eines IC-Chips an einer Leiterplatte;

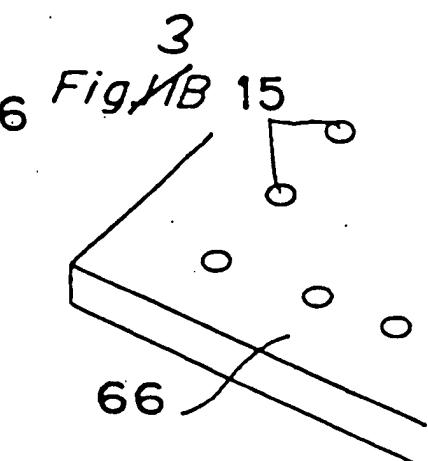

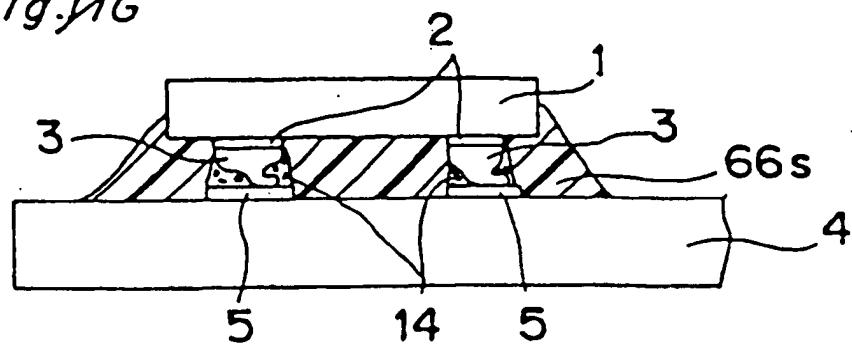

**[0021]** [Fig. 3A](#), [Fig. 3B](#), [Fig. 3C](#), [Fig. 3D](#), [Fig. 3E](#), [Fig. 3F](#) und [Fig. 3G](#): Ansichten zur Erläuterung des Vorgangs der Befestigung eines IC-Chips an einer Leiterplatte nach einem Ausführungsbeispiel des erfindungsgemäßen Bestückungsverfahrens.

#### Beste Art der Ausführung der Erfindung

**[0022]** Vorab sei darauf hingewiesen, dass gleiche

Teile in den Zeichnungen durchweg mit demselben Bezugszeichen bezeichnet sind.

**[0023]** Es werden ein Bestückungsverfahren und eine Bestückungsvorrichtung gemäß einem Ausführungsbeispiel der Erfindung unter Bezugnahme auf [Fig. 3A](#) bis [Fig. 3G](#) beschrieben. Bei dem Ausführungsbeispiel handelt es sich um ein Bestückungsverfahren und eine Bestückungsvorrichtung, bei denen unabhängig von Gleichzeitigkeit keine Nivellierung vorgenommen wird.

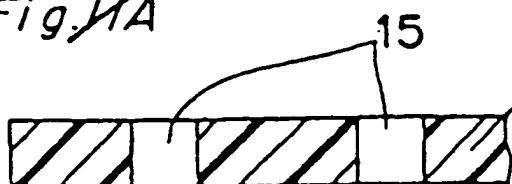

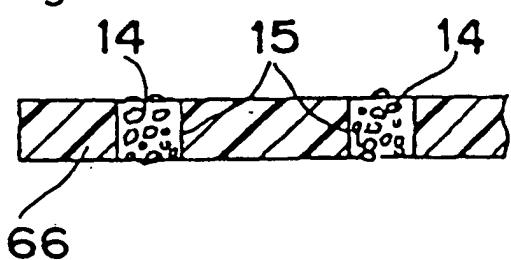

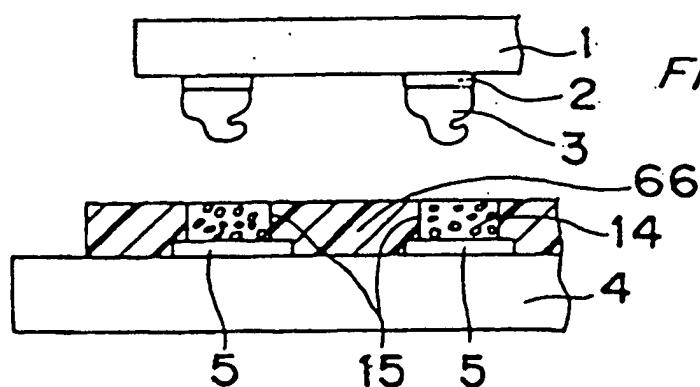

**[0024]** Wie in [Fig. 3E](#) und [Fig. 3F](#) gezeigt, werden an den Elektroden **2** des IC-Chips **1** mittels eines Drahtkontakteiers (nicht abgebildet) vorab überstehende Elektroden (Höcker) **3** gebildet, wenn der IC-Chip **1** auf der Leiterplatte **4** montiert wird. Wie in [Fig. 3A](#) und [Fig. 3B](#) gezeigt, werden durch den warmaushärtenden Harzbogen **6** hindurch in eine Richtung (Dickenrichtung des Harzbogens **6**) Durchgangsbohrungen **15** hergestellt, in denen die Höcker **3** und die Elektroden **5** der Leiterplatte **4** an der Position der Höcker **3** und der Elektroden **5** der Leiterplatte **4** miteinander in Kontakt gebracht werden und eine leitende Verbindung zwischen ihnen hergestellt wird. Dann werden, wie in [Fig. 3C](#) und [Fig. 3D](#) gezeigt, leitfähige Partikel **14**, bestehend beispielsweise aus Harzkügelchen mit goldplattierter Oberfläche, oder Nickelpartikeln, oder leitfähigen Partikeln aus Silber, Silber-Palladium oder Gold, oder einer leitfähigen Paste, oder Partikeln aus Goldkügelchen in Pastenform, durch Drucken, Hineindrücken mittels einer Rake oder dergleichen in die Durchgangsbohrungen **15** eingebracht, wodurch ein elektrisch leitfähiger warmaushärtender Harzbogen **66** geschaffen wird. Der so gebildete Harzbogen **66** wird nach Positions ausrichtung, wie in [Fig. 3E](#) und [Fig. 3F](#) gezeigt, auf die Elektroden **5** der Leiterplatte **4** gesteckt. Wenn leitfähige Partikel **14** in Pastenform verwendet werden und die Viskosität der Paste höher eingestellt wird als die Viskosität beim Bonden des warmaushärtenden Klebers des warmaushärtenden Harzbogens **66**, lässt sich die Paste durch das Harz des warmaushärtenden Harzbogens **66** schlecht schieben und zum Fließen bringen, wenn der IC-Chip **1** angedrückt wird, was ein weiterer Vorteil ist. Anschließend werden die Höcker **3** des IC-Chips **1** nach den Elektroden **5** der Leiterplatte **4** ausgerichtet, wie in [Fig. 11E](#) und [11F](#) gezeigt, und der IC-Chip **1** wird vom aufgeheizten Kontaktierkopf **8** gegen die Leiterplatte **4** gedrückt, um das warmaushärtende Harz im warmaushärtenden Harzbogen **66**, der zwischen den IC-Chip **1** und die Leiterplatte **4** geschoben ist, zu härteten, während gleichzeitig die Nivellierung der Höcker **3** und die Verzugskorrektur an der Leiterplatte **4** vorgenommen werden, so dass der IC-Chip **1** durch das gehärtete Harz **66s** an der Leiterplatte **4** befestigt wird, wie in [Fig. 3G](#) gezeigt. Wenn die Leiterplatten Seite erwärmt wird, kann die Temperatur des Kontaktierkopfs **8** weiter gesenkt werden.

**[0025]** Die durch den warmaushärtenden Harzbogen **66** hindurch gebildeten Löcher **15** werden vorzugsweise entweder an der Position der Elektroden **2** des IC-Chips **1** oder der Höcker **3** oder an der Position der Elektroden **5** der Leiterplatte **4** gebildet. Wenn die Anzahl der Elektroden **5** der Leiterplatte **4** größer ist als die Anzahl der Elektroden **2** des IC-Chips **1**, ist es beispielsweise zweckmäßig, die Löcher **15** entsprechend der zum Kontaktieren der Elektroden **2** des IC-Chips **1** nötigen Anzahl, d.h. der Position und der Anzahl der Elektroden **2** des IC-Chips **1** zu bilden.

## Patentansprüche

1. Bestückungsverfahren, umfassend:

Ausrichten der Position von Elektroden **(5)** einer Leiterplatte **(4)** nach Höckern **(3)**, die durch Drahtkontakteierung von Elektroden **(2)** eines elektronischen Bauelements **(1)** gebildet wurden, mit Einlage eines warmaushärtenden Harzbogens **(6)**,

**dadurch gekennzeichnet**, dass der warmaushärtende Harzbogen **(6)** ein fester warmaushärtender Harzbogen **(6)** ist, bei dem in Durchgangsbohrungen **(15)**, die an Positionen ausgebildet sind, die den Höckern **(3)** der Elektroden **(2)** des elektronischen Bauelements **(1)** an den Elektroden **(5)** der Leiterplatte **(4)** entsprechen, Teilchen **(14)** folgender Art eingebettet sind: Harzkügelchen, die an der Oberfläche mit Gold plattierte sind, oder Nickelpartikel, oder leitfähige Teilchen aus Silber, Silber-Palladium oder Gold, oder eine leitfähige Paste, oder Goldkügelchen, und Härteten des zwischen das elektronische Bauelement **(1)** und die Leiterplatte **(4)** gelegten warmaushärtenden Harzes **(6)** durch Wärme, während eine Wellung der Leiterplatte **(4)** korrigiert wird, indem das elektronische Bauelement **(1)** mit einer Kraft von wenigstens 0,196133 N (20 gf) pro Höcker **(3)** gegen die Leiterplatte **(4)** gedrückt wird, wodurch das elektronische Bauelement **(1)** und die Leiterplatte **(4)** unter Herstellung einer elektrischen Verbindung zwischen ihnen beiden Elektroden **(2, 5)** miteinander verbunden werden,

wobei das Ausrichten der Position der Höcker **(3)** des elektronischen Bauelements **(1)** nach den Elektroden **(5)** der Leiterplatte **(4)** ausgeführt wird, nachdem der warmaushärtende Harzbogen **(6)** an den Elektroden **(5)** der Leiterplatte **(4)** haftet.

2. Bestückungsverfahren nach Anspruch 1, bei dem der warmaushärtende Harzbogen **(6)** eine Dicke hat, die größer ist als der Abstand zwischen der aktiven Oberfläche des elektronischen Bauelements **(1)** und der zur Leiterplatte **(4)** gehörenden Oberfläche, auf der die Elektroden **(5)** nach dem Bonden gebildet werden.

3. Bestückungssystem zum Ausführen des Verfahrens nach Anspruch 1 oder 2, aufweisend:

eine Bestückungsvorrichtung, einen festen, warmaushärtenden Harzbogen **(6)**, eine Leiterplatte

(4) mit darauf ausgebildeten Elektroden (5), ein elektronisches Bauelement (1) mit durch Drahtkontakte rung daran ausgebildeten Höckern, wobei der feste, warmaushärtende Harzbogen (6) Teilchen (14) folgender Art enthält: Harzkügelchen, die an der Oberfläche mit Gold plattierte sind, oder Nickelpartikel, oder leitfähige Partikel aus Silber, Silber-Palladium oder Gold, oder eine leitfähige Paste, oder Goldkügelchen, die in Durchgangsbohrungen (15) eingebettet sind, die an Positionen ausgebildet sind, die den Höckern (3) der Elektroden (2) des elektronischen Bauelements (1) an den Elektroden (5) der Leiterplatte (4) entsprechen, wobei die Bestückungsvorrichtung aufweist:

eine Positionsausrichtungseinrichtung zum Ausrichten der Elektroden (5) der Leiterplatte (4) nach den Höckern (3) des elektronischen Bauelements (1) mit Einlegen des warmaushärtenden Harzes (6), eine Heizeinrichtung (8a) zum Erwärmen des warmaushärtenden Harzes (6) und

eine Bondiereinrichtung zum Härteln des warmaushärtenden Harzes (6), das zwischen das elektronische Bauelement (1) und die Leiterplatte (4) gelegt wurde, durch Wärme, während die Wellung der Leiterplatte (4) korrigiert wird, indem das elektronische Bauelement (1) mit einem Druck von wenigstens 0,196133 N (20 gf) pro Höcker (3) gegen die Leiterplatte (4) gedrückt wird, wobei Wärme von der Heizeinrichtung (8a) auf das warmaushärtende Harz (6) einwirkt, wodurch das elektronische Bauelement (1) und die Leiterplatte (4) unter Herstellung einer elektrischen Verbindung zwischen beider Elektroden (2, 5) miteinander verbunden werden,

wobei die Positionsausrichtungseinrichtung dazu eingerichtet ist, den festen, warmaushärtenden Harzbo gen (6) mit den Elektroden (5) der Leiterplatte (4) zu verkleben, und danach die Ausrichtung der Position der Höcker (3) des elektronischen Bauelements (1) nach den Elektroden (5) der Leiterplatte (4) vorzunehmen.

4. Bestückungssystem nach Anspruch 3, wobei der warmaushärtende Harzbogen (6) eine Dicke hat, die größer ist als der Abstand zwischen der aktiven Oberfläche des elektronischen Bauelements (1) und der zu der Leiterplatte (4) gehörenden Oberfläche, auf der die Elektroden (5) nach dem Bonden gebildet werden.

Es folgen 2 Blatt Zeichnungen

Fig. 13

Fig. 14A

3

Fig. 1A3

Fig. 1C3

Fig. 1E3

Fig. 1G3

Fig. 1D