(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년12월30일

(11) 등록번호 10-1477493

(24) 등록일자 2014년12월23일

(51) 국제특허분류(Int. Cl.)

H04B 1/7183 (2011.01)

(21) 출원번호 10-2012-7025607

(22) 출원일자(국제) 2011년03월01일

심사청구일자 2012년09월28일

(85) 번역문제출일자 2012년09월28일

(65) 공개번호 10-2012-0127735

(43) 공개일자 2012년11월23일

(86) 국제출원번호 PCT/EP2011/053020

(87) 국제공개번호 WO 2011/107471

국제공개일자 2011년09월09일

(30) 우선권주장

10 2010 009 678.4 2010년03월01일 독일(DE)

(56) 선행기술조사문헌

KR100766543 B1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

지멘스 액티엔게젤샤프트

독일 뮌헨 80333 비델스파허프라쓰 2

(72) 발명자

훈드, 요하네스

독일 80804 뮌헨 바를락슈트라쎄 28 / 앱. 244

하인리히, 안드레아스

독일 71032 보블링겐 브룬넨슈트라쎄 18

(뒷면에 계속)

(74) 대리인

이시용, 정현주, 김미희

전체 청구항 수 : 총 25 항

심사관 : 배상진

(54) 발명의 명칭 데이터 패킷들의 와이어-프리 송신을 위한 방법 및 장치

**(57) 요약**

제어 네트워크 내의 네트워크 노드들 사이의 데이터 패킷들의 와이어-프리 송신을 위한 방법으로서, 상기 데이터 패킷들 각각은 동기화를 위한 프리앰블을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들로 이루어지고; 제 1 동작 모드(도 5a)에서, 상기 프리앰블 내의 프리앰블 심볼의 각각의 프리앰블-서브심볼( $C_j$ ,  $C_{j+1}$ )은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고; 제 2 동작 모드(도 5b)에서, 상기 데이터 패킷으로 전송되는 상기 프리앰블에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼( $C_j$ ,  $C_{j+1}$ )을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스가 상기 신호 펄스 시퀀스(SIF) 내에서 반복적으로 전송된다.

**대표도 - 도5**

(72) 발명자

허체홀츠, 스테판

독일 81379 뮌헨 텔처 슈트라쎄 29

슈빈겐슈뢰글, 크리스티안

독일 85640 푸츠부룬 카메터베크 7

## 특허청구의 범위

### 청구항 1

제어 네트워크의 네트워크 노드들(1) 사이의 데이터 패킷들(DP)의 와이어-프리(wire-free) 송신을 위한 방법으로서,

상기 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어지고,

제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각(phase angle)에 의해 코딩되고,

제 2 동작 모드에서, 상기 데이터 패킷(DP)으로 전송되는 상기 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스는 상기 신호 펄스 시퀀스 내에서 반복적으로 전송되며,

상기 네트워크 노드(1)는 2개의 동작 모드들 사이에서 스위칭될 수 있는,

와이어-프리 송신을 위한 방법.

### 청구항 2

제어 네트워크의 네트워크 노드들(1) 사이의 데이터 패킷들(DP)의 와이어-프리 송신을 위한 방법으로서,

상기 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어지고,

제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고,

제 2 동작 모드에서, 상기 데이터 패킷(DP)으로 전송되는 상기 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스는 상기 신호 펄스 시퀀스 내에서 반복적으로 전송되고,

상기 네트워크 노드(1)는 2개의 동작 모드들 중 특정 동작 모드를 위해 미리 구성될 수 있는,

와이어-프리 송신을 위한 방법.

### 청구항 3

제 2 항에 있어서,

상기 특정 동작 모드는 상기 제 2 동작 모드인,

와이어-프리 송신을 위한 방법.

### 청구항 4

제 1 항에 있어서,

상기 단일 신호 펄스 또는 상기 신호 펄스 시퀀스(SIF) 다음에 매번(each time) 신호 일시중지(signal pause; SP)가 뒤따르고, 상기 신호 일시중지(SP)는 상기 프리앰블 서브심볼들(C) 사이의 심볼간 간섭(intersymbol interference)을 회피하기 위해 제공되는,

와이어-프리 송신을 위한 방법.

### 청구항 5

제 2 항에 있어서,

상기 단일 신호 펄스 또는 상기 신호 펄스 시퀀스(SIF) 다음에 매번 신호 일시중지(SP)가 뒤따르고, 상기 신호

일시중지(SP)는 상기 프리앰블 서브심볼들(C) 사이의 심볼간 간섭을 회피하기 위해 제공되는,

와이어-프리 송신을 위한 방법.

#### 청구항 6

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

각각의 프리앰블 심볼(S)은 미리결정된 수의 프리앰블 서브심볼들(C)에 의해 터너리 코딩(ternary coding)되고,

상기 단일 신호 펄스 및 상기 신호 펄스 시퀀스(SIF)의 신호 임펄스들은 각각 포지티브, 네거티브 또는 중립 부호가 선행하는,

와이어-프리 송신을 위한 방법.

#### 청구항 7

제 6 항에 있어서,

수신된 데이터 패킷(DP)의 상기 신호 임펄스들의 선행 부호들이 데이터 패킷 손실율을 감소시키기 위해 검출되는,

와이어-프리 송신을 위한 방법.

#### 청구항 8

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 제 1 동작 모드에서, 각각의 프리앰블 서브심볼(C)은 미리결정된 펄스 지속기간(duration)을 갖는 단일 신호 펄스를 갖고,

상기 단일 신호 펄스 다음에 신호 일시중지(SP)가 뒤따르고, 상기 신호 일시중지(SP)의 지속기간은 상기 단일 신호 펄스의 펄스 지속기간보다 제 1 확산 인자(L1)만큼 더 긴,

와이어-프리 송신을 위한 방법.

#### 청구항 9

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 제 2 동작 모드에서, 각각의 프리앰블 서브심볼(C)은 동일한 위상각을 갖는 미리결정된 수(N)의 연속적인 단일 신호 펄스들로 이루어진 신호 펄스 시퀀스(SIF)를 갖고,

상기 신호 펄스 시퀀스(SIF) 내의 각각의 단일 신호 펄스는 미리결정된 펄스 지속기간을 갖고,

상기 신호 펄스 시퀀스(SIF) 다음에 신호 일시중지(SP)가 뒤따르고, 상기 신호 일시중지(SP)의 지속기간은 상기 신호 펄스 시퀀스(SIF)의 지속기간보다 제 2 확산 인자(L2)만큼 더 길거나, 또는 상기 신호 일시중지(SP)의 지속기간은 상기 제 1 동작 모드에서의 프리앰블 서브심볼(C)의 지속기간에서 상기 신호 펄스 시퀀스(SIF)의 지속기간을 차감한 지속기간에 대응하는,

와이어-프리 송신을 위한 방법.

#### 청구항 10

제 8 항에 있어서,

상기 제 2 동작 모드에서, 각각의 프리앰블 서브심볼(C)은 동일한 위상각을 갖는 미리결정된 수(N)의 연속적인 단일 신호 펄스들로 이루어진 신호 펄스 시퀀스(SIF)를 갖고,

상기 신호 펄스 시퀀스(SIF) 내의 각각의 단일 신호 펄스는 미리결정된 펄스 지속기간을 갖고,

상기 신호 펄스 시퀀스(SIF) 다음에 신호 일시중지(SP)가 뒤따르고, 상기 신호 일시중지(SP)의 지속기간은 상기 신호 펄스 시퀀스(SIF)의 지속기간보다 제 2 확산 인자(L2)만큼 길거나, 또는 상기 신호 일시중지(SP)의 지속기간은 상기 제 1 동작 모드에서의 프리앰블 서브심볼(C)의 지속기간에서 상기 신호 펄스 시퀀스(SIF)의 지속기간을 차감한 지속기간에 대응하는,

와이어-프리 송신을 위한 방법.

#### 청구항 11

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해서 표준 IEEE 802.15.4a에 따라 코딩되는,

와이어-프리 송신을 위한 방법.

#### 청구항 12

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 제 1 동작 모드에서 전송된 상기 단일 신호 펄스 및 상기 제 2 동작 모드에서 전송된 상기 신호 펄스 시퀀스(SIF)의 신호 임펄스들은 펄스 형상을 갖고, 상기 펄스 형상의 위상각은 스펙트럼 펄스 응답의 극성으로부터 명확하게 유도되는,

와이어-프리 송신을 위한 방법.

#### 청구항 13

제 12 항에 있어서,

상기 펄스 형상은 가우스 펄스 형상, 가우스 더블릿(doublet) 펄스 형상 또는 루트 레이즈드 펄스 코사인 펄스 형상(root raised pulse cosine pulse shape)인,

와이어-프리 송신을 위한 방법.

#### 청구항 14

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 데이터 패킷(DP)의 프리앰블(PRE)은  $2^{n_1}$  개의 프리앰블 심볼들을 갖는 동기화 헤더(SYNC) 및  $2^{n_2}$  개의 프리앰블 심볼들을 갖는 시작 프레임 딜리미터(start frame delimiter; SFD)를 가지며, 여기서  $n_1$ ,  $n_2$ 는 자연수들인,

와이어-프리 송신을 위한 방법.

#### 청구항 15

제 14 항에 있어서,

네트워크 노드(1)에 의해 수신된 상기 제어 네트워크의 데이터 패킷(DP)의 상기 프리앰블(PRE)의 상기 동기화 헤더(SYNC)는 SYNC 상관 디바이스(11)에 의해 제 1 상관값(KW1)을 계산하기 위해 이용되고, 상기 제 1 상관값(KW1)에 따라 상기 네트워크 노드(1)의 MF 스테이지(6) 내의 수신 증폭기가 설정되는,

와이어-프리 송신을 위한 방법.

#### 청구항 16

제 14 항에 있어서,

상기 제어 네트워크의 네트워크 노드(1)에 의해 수신된 데이터 패킷(DP)의 상기 프리앰블(PRE)의 상기 시작 프레임 딜리미터(SFD)는, 상기 데이터 패킷(DP) 내의 유용한 데이터의 시작의 검출을 위해 SFD 상관 디바이스에 의해 제 2 상관값(KW2)을 계산하기 위해 이용되는,

와이어-프리 송신을 위한 방법.

#### 청구항 17

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 단일 신호 펄스의 펄스 지속기간은 2 나노초(nsec)인,

와이어-프리 송신을 위한 방법.

### 청구항 18

제 9 항에 있어서,

상기 제 2 동작 모드에서, 상기 신호 펄스 시퀀스(SIF)의 연속적인 단일 신호 펄스들의 수(N)는 N=4인,

와이어-프리 송신을 위한 방법.

### 청구항 19

제 10 항에 있어서,

상기 제 2 동작 모드에서, 상기 신호 펄스 시퀀스(SIF)의 연속적인 단일 신호 펄스들의 수(N)는 N=4인,

와이어-프리 송신을 위한 방법.

### 청구항 20

데이터 패킷들(DP)을 전송하기 위한 네트워크 노드(1)로서,

상기 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어지고,

제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고,

제 2 동작 모드에서, 상기 데이터 패킷(DP)으로 전송되는 상기 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스가 상기 신호 펄스 시퀀스 내에서 반복적으로 전송되며,

상기 네트워크 노드(1)는 2개의 동작 모드들 사이에서 스위칭될 수 있는,

네트워크 노드.

### 청구항 21

데이터 패킷들(DP)을 전송하기 위한 네트워크 노드(1)로서,

상기 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어지고,

제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고,

제 2 동작 모드에서, 상기 데이터 패킷(DP)으로 전송되는 상기 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스가 상기 신호 펄스 시퀀스 내에서 반복적으로 전송되고,

상기 네트워크 노드(1)는 2개의 동작 모드들 중 특정 동작 모드를 위해 미리 구성될 수 있는,

네트워크 노드.

### 청구항 22

제 21 항에 있어서,

상기 특정 동작 모드는 상기 제 2 동작 모드인,

네트워크 노드.

### 청구항 23

데이터 패킷들(DP)을 전송하는 네트워크 노드들(1)을 갖는 와이어-프리 제어 네트워크 시스템으로서, 상기 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어지고, 제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고, 제 2 동작 모드에서, 상기 데이터 패킷(DP)으로 전송되는 상기 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스가 상기 신호 펄스 시퀀스 내에서 반복적으로 전송되고, 상기 네트워크 노드(1)는 2개의 동작 모드들 사이에서 스위칭될 수 있는, 와이어-프리 제어 네트워크 시스템.

#### 청구항 24

데이터 패킷들(DP)을 전송하는 네트워크 노드들(1)을 갖는 와이어-프리 제어 네트워크 시스템으로서, 상기 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어지고, 제 1 동작 모드에서, 상기 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고, 제 2 동작 모드에서, 상기 데이터 패킷(DP)으로 전송되는 상기 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 상기 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송되고, 상기 단일 신호 펄스가 상기 신호 펄스 시퀀스 내에서 반복적으로 전송되고, 상기 네트워크 노드(1)는 2개의 동작 모드들 중 특정 동작 모드를 위해 미리 구성될 수 있는, 와이어-프리 제어 네트워크 시스템.

#### 청구항 25

제 24 항에 있어서, 상기 특정 동작 모드는 상기 제 2 동작 모드인, 와이어-프리 제어 네트워크 시스템.

### 명세서

#### 기술 분야

[0001] 본 발명은, 특히 제어 네트워크 내의 네트워크 노드들 사이의 데이터 패킷들의 와이어-프리(wire-free) 송신을 위한 방법 및 장치에 관한 것이다.

#### 배경 기술

[0002] 예전대 머신들을 제어하기 위한, 제어 네트워크 내의 네트워크 노드들 사이의 와이어-프리 통신 동안, 데이터 패킷들이 무선 인터페이스들을 통해 전송된다. 머신들을 제어하기 위한 와이어-프리 통신은, 한편으로는 매우 낮은 레이턴시들을, 그리고 다른 한편으로는 매우 높은 데이터 송신 신뢰성을 요구한다. 특히, 제어 네트워크가 보다 높은-레벨의 제어 네트워크로서 기능하는 경우, 제어 네트워크는 다른 와이어-프리 네트워크들과 공존(co-exist)할 수 있을 필요가 또한 있다. 이러한 경우에, 높은 데이터 송신 신뢰성의 제공은 기술적 도전을 의미하는데, 그 이유는 데이터 송신 동안 신뢰성을 향상시키기 위해 이용되는 대부분의 종래의 조치들은 레이턴시를 증가시키기 때문이다. 제어 네트워크에 의해 제어되는 머신들을 이용하는 산업 생산 플랜트들은, 무선 인터페이스들을 통한 와이어-프리 통신에 어려운 환경을 이룬다. 머신들을 이용하는 생산 플랜트들 또는 산업 생산 셀들은 데이터 송신 신호들을 반사하거나 또는 방해하는 금속 표면들과 연관되어, 비교적 높은 레벨의 전자기 노이즈가 존재한다. 반사적인 금속 표면들은 이른바 다중경로 신호 전파를 초래한다.

[0003] 상기의 문제점들은, 예컨대 블루투스 또는 IEEE 802.15.4와 같은 종래의 무선 네트워크 기술들이, 특히 산업 생산 환경들 또는 공장 자동화에서 제어 네트워크들에 실제로는 적합하지 않다는 것을 의미한다.

[0004] 그러므로, 데이터 패킷들이 제어 네트워크의 네트워크 노드들 사이에서 와이어-프리 방식으로 전송되는, 표준 IEEE 802.15.4a에 따른 데이터 송신이 제안되었다. 그러나, 표준 IEEE 802.15.4에 따른 데이터 패킷 송신은 높은 데이터 패킷 손실율을 초래한다는 것이 밝혀졌다. 여기서, 높은 패킷 손실율들은 특히, 데이터 패킷들의 헤더들에서 부정확하게 인식되는 프리앰블들로 인한 것이다. 이는 특히, 에너지 검출에 의해 작용하는 네트워크 노드들의 수신기들에서 발생한다.

### 발명의 내용

[0005] 그러므로, 본 발명의 목적은 제어 네트워크 내의 네트워크 노드들 사이의 데이터 패킷들의 와이어-프리 송신을 위한 방법 및 장치를 제공하는 것이며, 상기 방법 및 장치를 이용하여, 산업 환경에서 조작, 데이터 패킷들이 낮은 데이터 패킷 손실율로 제어 네트워크 내의 네트워크 노드들 사이에서 신뢰적으로 송신될 수 있다.

[0006] 이러한 목적은 청구항 제 1 항에 개시된 특징들을 갖는 방법에 의해 본 발명에 따라 달성된다.

[0007] 본 발명은, 제어 네트워크 내의 네트워크 노드들 사이의 데이터 패킷들의 와이어-프리 송신을 위한 방법을 제공하며, 데이터 패킷들 각각은 동기화를 위한 프리앰블을 갖고, 상기 프리앰블은 미리 결정된 수의 프리앰블 심볼들로 이루어지며, 제 1 동작 모드에서, 프리앰블 내의 프리앰블 심볼의 각각의 프리앰블 서브심볼은 전송된 단일 신호 펄스의 위상각(phase angle)에 의해 코딩되며, 제 2 동작 모드에서, 데이터 패킷으로 전송되는 프리앰블에 대한 신호 인식 성능을 향상시키기 위해, 프리앰블 서브심볼을 코딩하기 위한 신호 펄스 시퀀스가 단일 신호 펄스 대신에 전송되고, 단일 신호 펄스가 상기 신호 펄스 시퀀스 내에서 반복적으로 전송된다.

[0008] 그러므로, 본 발명에 따른 방법은 프리앰블의 인식을 단순화하고 그러므로 데이터 패킷 손실율을 상당히 감소시키는 부가적인 동작 모드를 도입한다.

[0009] 본 발명에 따른 방법의 하나의 가능한 실시예에서, 제 1 동작 모드에서, 단일 신호 펄스 다음에 신호 일시중지(signal pause)가 뒤따르고, 상기 신호 일시중지는 프리앰블 서브심볼들 사이의 심볼간 간섭(intersymbol interference; ISI)을 회피하기 위해 제공된다.

[0010] 본 발명에 따른 방법의 하나의 가능한 실시예에서, 제 2 동작 모드에서, 신호 펄스 시퀀스 다음에 신호 일시중지가 또한 뒤따르고, 상기 신호 일시중지는 프리앰블 서브심볼들 사이의 심볼간 간섭(ISI)을 회피하기 위해 제공된다.

[0011] 본 발명에 따른 방법의 하나의 가능한 실시예에서, 프리앰블의 각각의 프리앰블 심볼은 미리 결정된 수의 프리앰블 서브심볼들에 의해 터너리 코딩(ternary coding) 된다.

[0012] 본 발명에 따른 방법의 하나의 가능한 실시예에서, 제 1 동작 모드에서, 단일 신호 펄스는 포지티브, 네거티브 또는 중립 부호가 선행한다.

[0013] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 제 2 동작 모드에서, 신호 펄스 시퀀스의 신호 펄스들은 또한 포지티브, 네거티브 또는 중립 부호가 선행한다.

[0014] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 제 1 동작 모드에서, 각각의 프리앰블 서브심볼은 미리 결정된 펄스 지속기간을 갖는 단일 신호 펄스를 갖고, 단일 신호 펄스 다음에 신호 일시중지가 뒤따르고, 상기 신호 일시중지의 지속기간은 단일 신호 펄스의 펄스 지속기간보다 제 1 확산 인자만큼 길다.

[0015] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 제 2 동작 모드에서, 각각의 프리앰블 서브심볼은 동일한 위상각을 갖는 미리 결정된 수의 연속적인 단일 신호 펄스들로 이루어진 신호 펄스 시퀀스를 가지며, 신호 펄스 시퀀스의 각각의 단일 신호 펄스는 미리 결정된 펄스 지속기간을 갖는다.

[0016] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 신호 펄스 시퀀스 다음에 신호 일시중지가 뒤따르고, 상기 신호 일시중지의 지속기간은 신호 펄스 시퀀스의 지속기간보다 제 2 확산 인자만큼 길다.

[0017] 본 발명에 따른 방법의 추가의 가능한 다른 실시예에서, 신호 펄스 시퀀스 다음에 신호 일시중지가 뒤따르고, 상기 신호 일시중지의 지속기간은 제 1 동작 모드에서의 프리앰블 서브심볼의 지속기간 빼기(minus) 신호 펄스 시퀀스의 지속기간에 대응한다.

[0018] 본 발명에 따른 방법의 하나의 가능한 실시예에서, 제 1 동작 모드에서, 프리앰블 내의 프리앰블 심볼의 각각의

프리앰블 서브심볼은 표준 IEEE 802.15.4a에 따라서, 전송된 단일 신호 펄스의 위상각에 의해 코딩된다.

[0019] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 제 1 동작 모드에서 전송된 단일 신호 펄스 및 제 2 동작 모드에서 전송된 신호 펄스 시퀀스의 신호 펄스들은 펄스 형상을 갖고, 상기 펄스 형상의 위상각은 스펙트럼 펄스 응답의 극성으로부터 명확하게 유도된다.

[0020] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 펄스 형상은 가우스 펄스 형상이다.

[0021] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 펄스 형상은 가우스 더블렛(doublet) 펄스 형상이다.

[0022] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 펄스 형상은 루트 레이즈드 펄스 코사인 펄스 형상(root raised pulse cosine pulse shape)이다.

[0023] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 데이터 패킷의 프리앰블은  $2^{n1}$  개의 프리앰블 심볼들을 갖는 동기화 헤더 및  $2^{n2}$  개의 프리앰블 심볼들을 갖는 시작 프레임 딜리미터(start frame delimiter; SFD)를 가지며, 여기서  $n1$ ,  $n2$ 는 자연수들이다.

[0024] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 프리앰블의 수신된 동기화 헤더는 SYNC 상관 디바이스에 의해 제 1 상관값을 계산하기 위해 이용되고, 이에 따라 제어 네트워크 내의 네트워크 노드의 수신 증폭기 가 설정된다.

[0025] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 프리앰블의 수신된 시작 프레임 딜리미터(SFD)는 수신된 데이터 패킷 내의 유용한 데이터의 시작의 검출을 위해 SFD 상관 디바이스에 의해 제 2 상관값을 계산하기 위해 이용된다.

[0026] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 단일 신호 펄스의 펄스 지속기간은 약 2 nsec이다.

[0027] 본 발명에 따른 방법의 하나의 추가의 가능한 실시예에서, 제 2 동작 모드에서, 신호 펄스 시퀀스의 연속적인 단일 신호 펄스들의 수(N)는 N=4이다.

[0028] 본 발명은 또한 제 14 항에 개시된 특징들을 갖는 네트워크 노드들을 갖는 와이어-프리 제어 네트워크를 제공한다.

[0029] 본 발명은 데이터 패킷들을 전송하는 네트워크 노드들을 갖는 와이어-프리 제어 네트워크를 제공하며, 데이터 패킷들 각각은 동기화를 위한 프리앰블을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들로 이루어지고, 제 1 동작 모드에서, 프리앰블 내의 프리앰블 심볼의 각각의 프리앰블 서브심볼은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고, 제 2 동작 모드에서, 데이터 패킷으로 전송된 프리앰블에 대한 신호 인식 성능을 향상시키기 위해, 프리앰블 서브심볼을 코딩하기 위한 신호 펄스 시퀀스가 단일 신호 펄스 대신에 전송되고, 단일 신호 펄스가 상기 신호 펄스 시퀀스 내에서 반복적으로 전송된다.

[0030] 본 발명에 따른 와이어-프리 제어 네트워크의 하나의 가능한 실시예에서, 제 1 동작 모드에서, 와이어-프리 제어 네트워크는 IEEE 802.15.4a 네트워크를 형성한다.

[0031] 본 발명에 따른 방법 및 본 발명에 따른 와이어-프리 제어 네트워크의 추가의 가능한 실시예들은 첨부된 도면들을 참조하여 아래에서 더욱 상세하게 설명된다.

### 도면의 간단한 설명

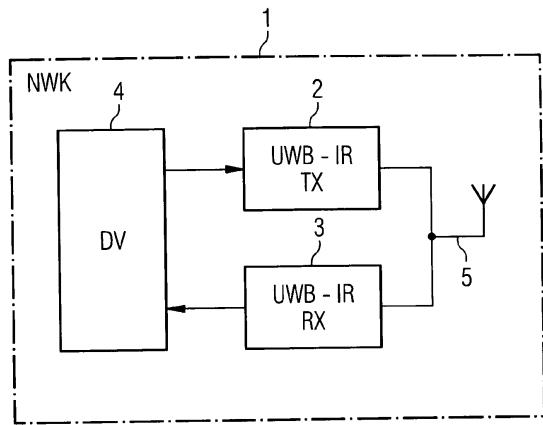

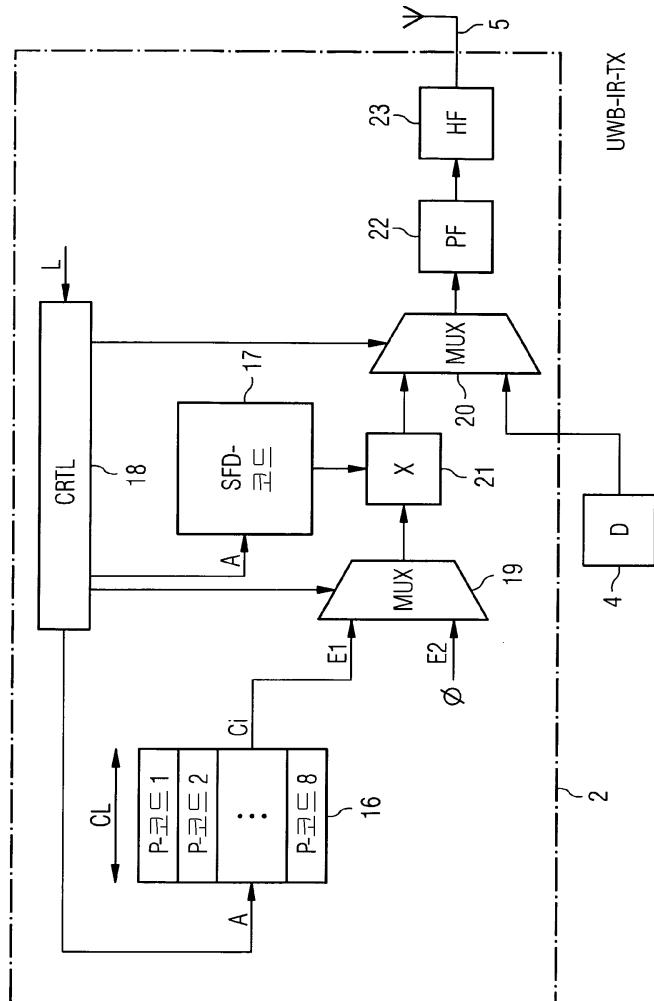

[0032] 도 1은 본 발명에 따른 와이어-프리 제어 네트워크에서 이용되는 네트워크 노드의 예시적 실시예의 블록도.

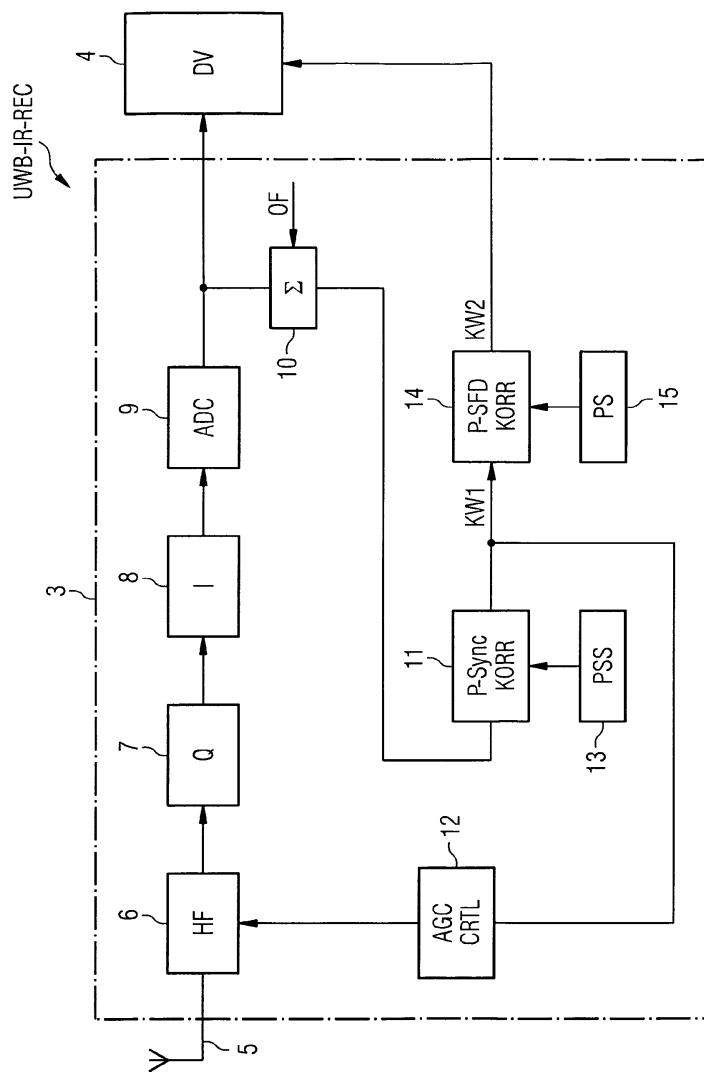

도 2는 도 1에 도시된 네트워크 노드에서 이용되는 수신기에 대한 예시적 실시예의 블록도.

도 3은 도 1에 도시된 네트워크 노드에 포함되는 송신기의 예시적 실시예의 블록도.

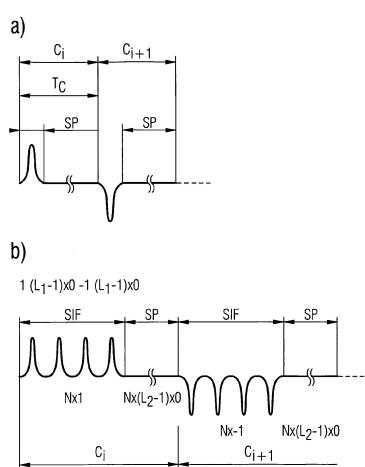

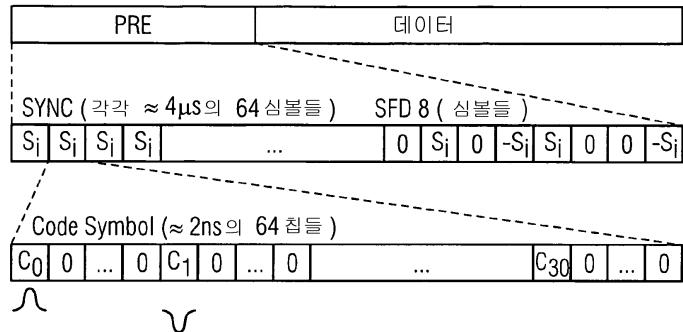

도 4a 및 도 4b는 본 발명에 따른 방법으로 전송되는 데이터 패킷의 데이터 구조를 설명하는 도면들.

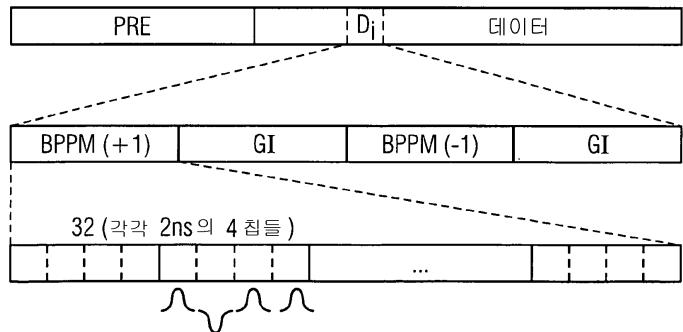

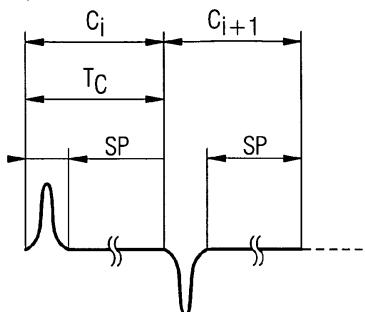

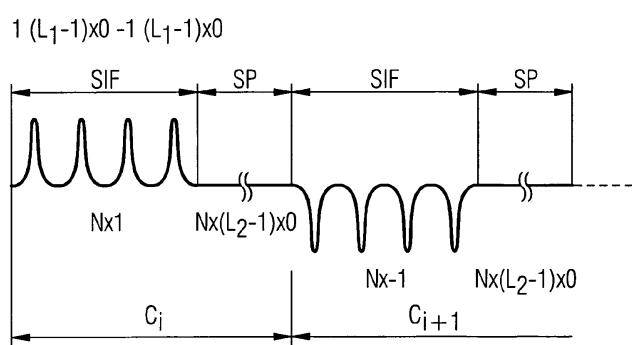

도 5a 및 도 5b는 본 발명에 따른 방법으로 제공되는 동작 모드들을 설명하는 신호도들.

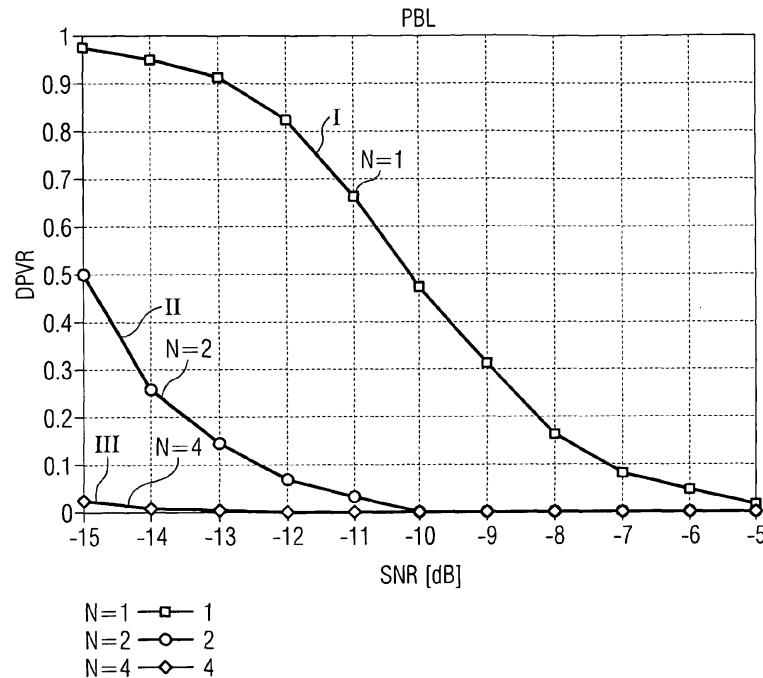

도 6은 본 발명에 따른 방법에 의해 달성되는 데이터 손실율에 대한 개선을 설명하는 도면.

도 7은 선행 부호 복구를 이용한 실시예를 이용하여 추가로 감소된 데이터 패킷 손실율을 도시하는 추가의 신호도.

## 발명을 실시하기 위한 구체적인 내용

[0033] 본 발명에 따른 와이어-프리 제어 네트워크에 있어서, 데이터 패킷들(DP)은 네트워크 노드들(1) 사이에서 전송된다. 도 1에 도시된 바와 같이, 도시된 예시적인 실시예에서, 제어 네트워크의 네트워크 노드(1)는, 데이터 처리 디바이스(4) 예컨대, CPU 또는 마이크로프로세서에 각각 접속되는 전송 디바이스(2) 및 수신 디바이스(3)를 포함한다. 전송 디바이스(2) 및 수신 디바이스(3)는 또한, 전송 및 수신 안테나(5)에 접속된다. 네트워크 노드들(1)은 와이어-프리 인터페이스 또는 무선 인터페이스를 통해 와이어-프리 제어 네트워크 내의 추가의 네트워크 노드들과 통신하기 위해 전송 및 수신 안테나(5)를 이용한다.

[0034] 하나의 가능한 실시예에서, 전송 디바이스(2) 및 수신 디바이스(3) 각각은 개별 안테나들을 가지며, 다시 말해, 전송 디바이스(2)는 전송 안테나에 접속되고 수신 디바이스(3)는 수신 안테나에 접속된다. 네트워크 노드(1)는 추가의 디바이스들 또는 스위칭 부분들, 특히 액츄에이터들, 센서들 및 자기 자신의 전원을 포함할 수 있다. 네트워크 노드(1)는 통신을 위해 다른 네트워크 노드들과 데이터 패킷들(DP)을 교환하기 위해 무선 인터페이스를 이용한다. 이러한 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖고, 상기 프리앰블은 미리결정된 수의 프리앰블 심볼들(S)로 이루어진다.

[0035] 제 1 동작 모드에서, 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩된다. 제 2 동작 모드에서, 데이터 패킷(DP)으로 전송되는 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 각각의 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스가 단일 신호 펄스(SIF) 대신에 전송되고, 신호 펄스 시퀀스(SIF)를 형성하기 위해, 제 1 동작 모드에서 이용된 단일 신호 펄스가 반복적으로 전송된다.

[0036] 제 2 동작 모드에서, 데이터 패킷(DP)으로 전송되는 프리앰블(PRE)에 대한 신호 인식 성능이 제 1 동작 모드에 비해 향상되어, 네트워크 노드(1)의 수신 디바이스(3)가 수신된 데이터 패킷(DP)의 프리앰블(PRE)을 인식하는 것이 보다 용이하다. 이는 데이터 패킷 손실율(DPVR)을 상당히 감소시킨다. 하나의 가능한 실시예에서, 도 1에 도시된 바와 같이, 네트워크 노드(1)는 2개의 동작 모드들 사이에서 스위칭될 수 있다. 대안적으로, 네트워크 노드(1)는 특정 동작 모드를 위해, 특히 제 2 동작 모드를 위해 미리 구성될 수 있다.

[0037] 제 1 및 제 2 동작 모드 양측 모두에서, 각각의 경우에서, 단일 신호 펄스 또는 신호 펄스 시퀀스(SIF) 다음에, 프리앰블 서브심볼들(C) 사이의 심볼간 간섭(ISI)을 회피하기 위해 제공된 신호 일시중지(SP)가 뒤따른다. 여기서, 각각의 프리앰블 심볼(S)은 바람직하게, 미리결정된 수의 프리앰블 서브심볼들(C)에 의해 터너리 코딩된다. 터너리 코딩에 있어서, 단일 신호 펄스 또는 신호 펄스 시퀀스(SIF)의 신호 펄스들은 각각 포지티브, 네거티브 또는 중립 부호가 선행한다. 제 1 동작 모드에서, 프리앰블 서브심볼(C)은 미리결정된 펄스 지속기간을 갖는 단일 신호 펄스를 갖는다. 이러한 펄스 지속기간은, 예컨대 2 nsec이다. 여기서, 제 1 동작 모드에서, 단일 신호 펄스 다음에 신호 일시중지(SP)가 뒤따르고, 하나의 가능한 실시예에서, 상기 신호 일시중지의 지속기간은 단일 신호 펄스의 펄스 지속기간보다 제 1 확산 인자(L1)만큼 길다.

[0038] 제 1 동작 모드에서, 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펄스의 위상각에 의해 코딩되는 반면, 제 2 동작모드에서, 데이터 패킷(DP)으로 전송되는 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 각각의 프리앰블 서브심볼(C)을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송된다. 여기서, 제 2 동작 모드에서, 각각의 프리앰블 서브심볼(C)은 동일한 위상각을 갖는 미리결정된 수(N)의 연속적인 단일 신호 펄스들로 이루어진 신호 펄스 시퀀스(SIF)를 갖는다. 신호 펄스 시퀀스(SIF)의 각각의 단일 신호 펄스는 미리결정된 펄스 지속기간을 갖는다. 신호 펄스 시퀀스 다음에 신호 일시중지(SP)가 뒤따른다. 하나의 가능한 실시예에서, 이러한 신호 일시중지(SP)는 신호 펄스 시퀀스(SIF)의 지속기간보다 제 2 확산 인자(L2)만큼 긴 지속기간을 갖는다.

[0039] 하나의 대안적 실시예에서, 신호 일시중지(SP)는, 제 1 동작 모드에서의 프리앰블 서브심볼(C)의 지속기간 빼기 (minus) 신호 펄스 시퀀스(SIF)의 지속기간에 대응하는 지속기간을 갖는다. 이러한 실시예는, 전체적으로, 프리앰블 서브심볼 길이가 양측 동작 모드들에서 동일하게 유지되어, 제 1 실시예와 비교하여 보다 짧은 레이턴시들이 획득된다는 이점을 갖는다. 이에 반해, 신호 일시중지의 지속기간이 신호 펄스 시퀀스의 지속기간보다 제 2 확산 인자(L2)만큼 긴 제 1 변형 또는 실시예는 신호들의 다중경로 신호 전파에 대해 보다 높은 저항성을 갖는다.

[0040] 하나의 가능한 실시예에서, 도 1에 도시된 네트워크 노드의 제 1 동작 모드에서, 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 표준 IEEE 802.15.4a에 따라서, 전송된 단일 신호 펄스의 위상각에

의해 코딩된다. 그러므로, 도 1에 도시된 네트워크 노드(1)는 표준에 부합하고 제 2 동작 모드에 의해 확장된다. 제 2 동작 모드에서 전송된 신호 펄스 시퀀스(SIF)는 신호 임펄스들로 이루어지고, 하나의 가능한 실시예에서, 펄스 형상은 단일 신호 펄스 또는 제 1 동작 모드에서 전송된 펄스의 펄스 형상에 대응한다. 여기서, 신호 펄스 시퀀스(SIF)의 신호 펄스들 각각은 펄스 형상을 갖고, 상기 펄스 형상의 위상각은 스펙트럼 펄스 응답의 극성으로부터 명확하게 유도된다.

[0041] 하나의 가능한 실시예에서, 펄스 형상은 가우스 펄스 형상이다. 대안적으로, 펄스 형상은 또한 가우스 더블릿 펄스 형상 또는 루트 레이즈드 펄스 코사인 펄스 형상일 수 있다. 도 1에 도시된 바와 같은 네트워크 노드(1)에 의해 교환된 데이터 패킷들(DP) 각각은 동기화를 위한 프리앰블(PRE)을 갖는다. 여기서, 데이터 패킷(DP)의 프리앰블은 바람직하게,  $2^{n1}$  개의 프리앰블 심볼들을 갖는 동기화 헤더(SYNC) 및  $2^{n2}$  프리앰블 심볼들을 갖는 시작 프레임 딜리미터(SFD)를 가지며, 여기서  $n1$ ,  $n2$ 는 자연수들이다.

[0042] 본 발명에 따른 네트워크 노드(1)의 하나의 가능한 실시예에서, 수신 디바이스(3)는 상관 디바이스들을 포함한다.

[0043] 하나의 가능한 실시예에서, 데이터 패킷(DP)의 프리앰블(PRE)의 수신된 동기화 헤더(SYNC)는, 네트워크 노드(1)의 수신 디바이스(3) 내의 SYNC-상관 디바이스에 의해 제 1 상관값을 계산하기 위해 이용되고, 이에 따라 네트워크 노드(1)의 수신 증폭기가 설정된다.

[0044] 하나의 가능한 실시예에서, 네트워크 노드(1)의 수신 디바이스(3)는 추가의 이른바 SFD 상관 디바이스를 갖는다. 프리앰블(PRE)의 시작 프레임 딜리미터(SFD)는 수신 디바이스(3)의 이러한 SFD 상관 디바이스에 의해, 수신된 데이터 패킷(DP) 내의 유용한 데이터의 시작의 검출을 위해 제 2 상관값을 계산하기 위해 이용된다.

[0045] 도 1에 도시된 네트워크 노드(1) 내의 수신 디바이스(3)는, 하나의 가능한 실시예에서 도 2에 도시된 바와 같이 구현되는 초광대역(UWB) 임펄스 응답(IR) 수신기일 수 있다. 도 2에 도시된 바와 같이, 수신 디바이스(3) 또는 수신기(3)는 안테나(5)를 통해 수신된 신호들을 다운믹싱하기 위한 HF 스테이지(6)를 갖는다. HF 스테이지(6)는 하나 또는 그보다 많은 신호 증폭기들 및 대역통과 필터(BPF)를 포함할 수 있고, 신호 제곱(squaring) 스테이지(7)에 인가되는 기저대역 신호를 발생시킨다. 다운믹싱된, 대역통과-필터링된 신호는 제곱되어 신호 적분기(integrator)(8)에 인가된다. 신호 적분기(8)는 심볼 시간( $T_s$ )으로 신호를 적분하고, 적분된 값을 아날로그-디지털 변환기(9)에 인가한다. 형성된 디지털 값은 데이터 처리 디바이스, 예컨대 도 1에 도시된 데이터 처리 디바이스(4)에 공급된다. 부가하여, 도 2에 도시된 바와 같이, 수신 디바이스(3)는 토텔링 또는 어그리게이션(totaling or aggregation) 디바이스(10)를 포함하고, 상기 토텔링 또는 어그리게이션 디바이스(10)는 프리앰블 서브심볼(C)에 대해 디지털화된 값들을 합산(add up)한다. 하나의 가능한 실시예에서, 이러한 토텔링 디바이스(10)는 오버샘플링 인자(OF)에 의해 제어되거나 또는 조절되고, 오버샘플링 인자(OF)는 프리앰블 서브심볼의 지속기간( $T_c$ )과 심볼의 지속기간( $T_s$ ) 사이의 비율로부터 획득된다.

[0046] 토텔링 디바이스(10)는 출력측 상에서, 수신 디바이스(3)의 제 1 상관 디바이스(11)에 접속된다. 수신 디바이스(3)에 의해 수신된 데이터 패킷(DP)은 프리앰블(PRE)을 포함하고, 상기 프리앰블(PRE)은 동기화 헤더(SYNC) 및 시작 프레임 딜리미터(SFD)를 포함할 수 있다. 도 2에 도시된 프리앰블 동기화 헤더-상관 디바이스(11)는 자동화 이득 제어부(12)에 출력되는 제 1 상관값(KW1)을 계산하기 위해 프리앰블(PRE)의 수신된 동기화 헤더(SYNC)를 이용한다. 제 1 상관값(KW1)에 따라, 자동화 이득 제어부(12)는 수신되는 신호들에 대해 수신 디바이스(3)를 튜닝하기 위해 HF 스테이지(6)에 포함된 적어도 하나의 수신 증폭기의 이득을 제어한다. 도 2에 도시된 실시예에서, 상관 디바이스(11)는 프리앰블 서브심볼들(C) 또는 프리앰블 칩들(C), 예컨대 31개의 프리앰블 서브심볼들을 포함하는 레지스터(13)에 접속된다. 레지스터에 저장된 프리앰블 서브심볼들(C)은 저장된 인식 템플릿(recognition template)을 형성한다. 상관 디바이스(11)에 의해 방출된 상관값은 수신된 프리앰블(PRE)이 예상된 프리앰블과 얼마나 유사한지를 나타낸다. 하나의 가능한 실시예에서, 임계값 비교기는 상관값을 임계값(TH)과 비교하기 위해 이용될 수 있다. 계산된 상관값이 임계값을 초과하자마자, 수신된 프리앰블(PRE)은 예상된 프리앰블에 대응하는 것으로 인식된다. 그러므로, 임계값(TH)이 초과될 때, 프리앰블 심볼이 인식된다.

[0047] 도 2에 도시된 실시예에서, SFD 상관 디바이스(14)는, 데이터 패킷(DP) 내의 유용한 데이터의 시작의 선택을 위해 제 2 상관값(KW2)을 계산하기 위해, 수신된 데이터 패킷(DP)의 수신된 시작 프레임 딜리미터(SFD)를 이용한다. SFD 상관기(14)는, 예상된 시작 프레임 딜리미터(SFD)에 대해 예컨대 8개의 미리지정된 프리앰블 심볼들(S)을 포함하는 레지스터(15)에 접속된다. 시작 프레임 딜리미터(SFD)가 인식된다면, 데이터 처리 디바이스(4)는 도 2에 도시된 바와 같이 ADC(9)에 의해 방출되는 유용한 데이터를 처리하기 위해 활성화된다.

[0048]

도 3은 도 1에 도시된 네트워크 노드(1) 내에서 이용되는 전송 디바이스(2)의 예시적 실시예를 도시하는 개략적인 블록도이다. 도 3에 도시된 예시적인 실시예에서, 전송 디바이스(2)는 초광대역(UWB)-임펄스 응답(IR) 송신기이다. 도 3에 도시된 스위칭 부분은 본 발명에 따른 방법에서 이용되는 데이터 패킷(DP)의 프리앰블(PRE)을 발생시킨다. 데이터 메모리(16), 예컨대 RAM 메모리는, 미리결정된 수의 프리앰블 서브심볼들(C), 예컨대 31개의 프리앰블 서브심볼들(C)을 각각 포함하는 예컨대, 8개의 프리앰블 코드들(P-코드 1 내지 P-코드 8)을 포함한다. 도 3에 도시된 바와 같이, 프리앰블 코드 내의 프리앰블 서브심볼들(C)의 수는 코드 길이(CL)를 형성한다. 제 2 데이터 메모리(17)는 표준 SFD(시작 프레임 딜리미터) 코드의 프리앰블 심볼들을 포함한다. 예컨대, RAM 메모리들인 2개의 데이터 메모리들(16, 17)은 제어 로직(18)에 의해 주소지정(address)된다. 도 3에 도시된 바와 같이, 제어 로직(18)은 또한, 제어 라인들을 통해 2개의 멀티플렉서들(19, 20)을 제어한다. 제어 로직(18)은 복수의 카운팅 디바이스들 또는 카운터들을 포함할 수 있다.

[0049]

하나의 가능한 실시예에서, 제어 로직(18)의 하나의 카운터는 값 0부터 확산 인자(L1)까지 카운팅하고, 카운트 값 0에서, 멀티플렉서(19)의 제 1 입력(E1)이 스위칭 스루(switch through)되고, 이러한 카운터의 다른 카운트 값들에서, 멀티플렉서(19)의 제 2 입력(E2)이 스위칭 스루된다. 따라서, 다수의 0들 또는 0 값들은 메모리(16)에서 현재 주소지정되어 있는 프리앰블 코드의 프리앰블 서브심볼(C<sub>i</sub>)에 부착되고, 신호 일시중지(SP)를 형성하는 부착된 0 값들의 수는 확산 인자(L-1)에 대응한다. 제어 로직(18)의 하나의 가능한 실시예에서, 확산 인자(L)는 조절가능하다. 예컨대, 확산 인자(L)가 16이면, 15개의 0 값들이, 다음(next) 프리앰블 서브심볼(C)이 스위칭 스루되기 전에 메모리(16)로부터 판독된 각각의 프리앰블 서브심볼(C)에 부착된다. 도 3에 도시된 바와 같이, 확산 인자(L)에 대응하는 다수의 0 값들을 각각 갖는, 멀티플렉서(19)에 형성된 프리앰블 서브심볼들(C)의 시퀀스는 믹서 또는 곱셈기(mixer or multiplier)(21)에 공급된다. 상기 믹서 또는 곱셈기(21)는 메모리(17)로부터 판독된 표준 SFD 코드의 프리앰블 심볼을 멀티플렉서(19)에 의해 방출된 시퀀스와 곱셈한다. 프리앰블(PRE)이 준비되자마자, 제어 로직(18)은 멀티플렉서(20)를 데이터 입력부로 스위칭하고, 상기 데이터 입력부는 데이터 처리 디바이스, 예컨대 도 1에 도시된 데이터 처리 디바이스(4)에 접속된다. 출력측 상에서, 멀티플렉서(20)는 펠스 세이퍼(shaper)(22)에 접속되고, 차례로 상기 펠스 세이퍼(22)는 출력측 상에서 HF 스테이지(23)에 접속된다.

[0050]

하나의 가능한 실시예에서, 제어 로직(18)은 카운터를 클록킹하기 위한 통합된 클록 발생기를 갖는다. 하나의 가능한 실시예에서, 클록 발생기는 500 MHz의 오디오 주파수를 갖는 클록 신호(CLK)를 발생시키며, 상기 클록 신호는 멀티플렉서(19)를 제어하기 위한 카운터에 인가된다. 대안적으로, 제어 로직(18)의 클록 신호(CLK)는 또한 외부로부터 공급될 수 있다.

[0051]

도 4a는 본 발명에 따른 방법 및 본 발명에 따른 장치와 함께 이용되는 데이터 패킷(DP)의 프리앰블(PRE)의 데이터 구조를 설명하도록 기능한다. 프리앰블(PRE)은 시작 프레임 딜리미터(SFD)를 갖는 동기화 헤더(SYNC)로 이루어진다. 동기화 헤더(SYNC)는 바람직하게  $2^{n1}$  개의 프리앰블 심볼들(S)로 이루어진다. 도 4a에 도시된 예시적 실시예에서, 동기화 헤더(SYNC)는 예컨대, 64개의 프리앰블 심볼들(S)(n1=6)을 갖는다. 프리앰블(PRE)은 또한,  $2^{n2}$  개의 프리앰블 심볼들, 예컨대 도 4a에 도시된 바와 같이, 8개의 프리앰블 심볼들(n2=3)을 갖는 시작 프레임 딜리미터(SFD)를 포함한다. 차례로 각각의 프리앰블 심볼(S)은 프리앰블 서브심볼들(C) 또는 코드 칩들(C<sub>i</sub>)로 이루어진다. 본 발명에 따른 방법의 제 1 동작 모드에서, 프리앰블(PRE) 내의 프리앰블 심볼(S)의 각각의 프리앰블 서브심볼(C)은 전송된 단일 신호 펠스의 위상각에 의해 코딩된다. 이는, 각각의 코드 칩(C<sub>i</sub>)은 단일 신호 펠스를 갖고, 상기 단일 신호 펠스, 다음에, 신호 일시중지(SP)를 형성하는 0 값들의 시퀀스가 뒤따른다는 것을 의미한다. 신호 일시중지(SP)는 프리앰블 서브심볼들 또는 코드 칩들(C<sub>i</sub>) 사이의 심볼간 간섭(ISI)을 방지하도록 기능한다. 신호 펠스는 바람직하게 포지티브, 네거티브 또는 중립 부호가 선행한다. 프리앰블 심볼(S)은 바람직하게, 미리결정된 수의 프리앰블 서브심볼들(C)에 의해 터너리 코딩된다. 바람직하게, 도 4a에 도시된 바와 같이, 각각의 프리앰블 서브심볼은 31개의 프리앰블 심볼들에 의해 터너리 코딩된다. 제 1 동작 모드에서, 예컨대 2 nsec의 특정한 미리지정된 펠스 지속기간을 갖는 단일 신호 펠스가 각각의 프리앰블 서브심볼 또는 코드 칩(C<sub>i</sub>)의 시작에 제공된다. 단일 신호 펠스 다음에 다수의 0 값들이 뒤따르고, 0 값들의 수는 확산 인자(L) 빼기(minus) 1에 의해 결정된다. 그러므로, 확산 인자 L=16의 경우, 단일 신호 펠스 다음에 15개의 0 값들이 뒤따를 것이며, 64의 확산 인자의 경우, 단일 신호 펠스 다음에 63개의 0 값들이 뒤따를 것이다. 0 값들의 수가 보다 많을수록, 그러므로 후속하는 신호 일시중지(SP)가 보다 길수록, 프리앰블(PRE)은 다중경로 신호 전파로부터의 간섭에 대해 보다 저항력이 있다. 그러나, 프리앰블 서브심볼들의 보다 큰 길이로

인해, 레이턴시가 증가된다. 본 발명에 따른 방법의 제 1 동작 모드에서, 각각의 프리앰블 서브심볼 또는 코드 칩( $C_i$ )은 전송된 단일 신호 펄스의 위상각에 의해 코딩되고, 단일 신호 펄스는 특정 펄스 형상 및 미리결정된 펄스 지속기간을 갖는다. 단일 신호 펄스는 가우스 펄스 형상, 가우스 더블릿 펄스 형상 또는 루트 레이즈드 펄스 코사인 펄스 형상을 갖는 펄스일 수 있다. 단일 신호 펄스의 펄스 지속기간이, 예컨대 2 nsec 미만이기 때문에, 단일 신호 펄스는 송신 동안 단지 낮은 양의 에너지만을 가지며, 이는 특히 잡음 환경(noisy environment)의 경우에, 수신 디바이스가 인식하기 어렵다.

[0052] 도 5a는 본 발명에 따른 방법의 제 1 동작 모드에서의 신호 송신을 설명하는 신호도이다. 이러한 동작 모드에서, 초기에 단일 신호 펄스가 전송되고, 상기 단일 신호 펄스 다음에 특정 수의 0 값들이 뒤따른다. 0 값들의 수는 확산 인자( $L$ )에 의해 결정된다. 예컨대,  $L=16$ 의 확산 인자의 경우, 15개의 0 값들이 전송될 것이다. 2 nsec의 펄스 지속기간의 경우, 프리앰블 서브심볼( $C$ )의 지속기간( $T_C$ )은  $16 \times 2 \text{ nsec} = 32 \text{ nsec}$ 이다. 64의 확산 인자의 경우, 프리앰블 서브심볼의 지속기간( $T_C$ )은 예컨대, 128 nsec이다. 예컨대, 프리앰블 심볼( $S$ ) 내의 프리앰블 서브심볼들( $C$ )의 수 또는 코드 길이( $CL$ )가  $CL=31$ 이면, 프리앰블(PRE) 내의 심볼의 지속기간은 약  $4 \mu \text{sec}$ 이다. 도 5a에 도시된 예에서, 초기에 포지티브 부호가 선행하는 단일 신호 펄스가 전송되고 네거티브 부호가 선행하는 단일 신호 펄스가 뒤따른다.

[0053] 본 발명에 따른 방법의 하나의 가능한 실시예에서, 각각의 프리앰블 서브심볼( $C$ )은 터너리 코딩되고, 각각의 단일 신호 펄스는 포지티브, 네거티브 또는 심지어 중립 부호(VZ)가 선행한다. 다른 유형들의 코딩, 예컨대 이진 코딩이 또한 가능하다.

[0054] 도 5b는 본 발명에 따른 방법의 제 2 동작 모드를 설명하는 신호도이다. 제 2 동작 모드에서, 데이터 패킷( $D_P$ )으로 전송되는 프리앰블(PRE)에 대한 신호 인식 성능을 향상시키기 위해, 프리앰블 심볼( $S$ )을 코딩하기 위한 신호 펄스 시퀀스(SIF)가 단일 신호 펄스 대신에 전송된다. 여기서, 제 1 동작 모드에서 전송된 단일 신호 펄스가 반복적으로 전송된다. 제 2 동작 모드에서, 각각의 프리앰블 서브심볼( $C$ )은 동일 위상각을 갖는 미리결정된 수( $N$ )의 연속적인 단일 신호 펄스들을 갖는다. 도 5b에 도시된 예에서, 신호 펄스 시퀀스(SIF)는 4개의 연속적인 단일 신호 펄스들( $N=4$ )을 갖는다. 4개의 펄스들로 이루어진 신호 펄스 시퀀스(SIF) 다음에 신호 일시중지(SP)가 뒤따른다. 하나의 가능한 변형에서, 신호 일시중지(SP)의 지속기간은 신호 펄스 시퀀스의 지속기간보다 제 2 확산 인자( $L_2$ )만큼 길다. 확산 인자( $L_2$ )는 제 1 동작 모드에서 이용된 확산 인자( $L_1$ )와 동일할 수 있다. 제 2 확산 인자( $L_2$ )가, 예컨대, 도 5b에 도시된 예시적 실시예에서와 같이 16이면, 신호 펄스 시퀀스(SIF) 다음에  $4 \times 15 = 60$ 의 0 값들을 갖는 신호 일시중지(SP)가 뒤따를 것이다. 그 다음에, 이는, 도 5b에 도시된 예에서와 같이, 다음(next) 코드 칩( $C_{it1}$ ) 또는 프리앰블 서브심볼의 다음(next) 신호 펄스 시퀀스(SIF)가 뒤따르고, 여기서 신호 펄스 시퀀스(SIF)는 네거티브 부호들이 선행하는 4개의 연속적인 신호 임펄스들로 이루어진다.

[0055] 대안적인 예시적 실시예에서, 신호 일시중지(SP)의 지속기간은 제 1 동작 모드에서의 프리앰블 서브심볼( $C_i$ ) 또는 코드 칩의 지속기간 빼기(minus) 신호 펄스 시퀀스(SIF)의 지속기간에 대응할 수 있다. 이러한 실시예는, 코드 칩( $C_i$ ) 또는 프리앰블 서브심볼의 지속기간이 양측 동작 모드들에서 동일하게 길다는 이점을 갖는다. 이러한 점에 있어서는, 다른 대안들에 비해 보다 짧은 프리앰블 서브심볼 길이로 인해 레이턴시가 보다 양호하다. 그러나, 도 5b에 도시된 실시예에서, 다중경로 신호 전파로 인한 간섭에 대한 저항성은, 프리앰블 서브심볼들( $C$ ) 사이의 연관된 보다 낮은 심볼간 간섭(ISI) 및 신호 일시중지(SP)의 길이로 인해 보다 높다.

[0056] 그러므로, 도 5b에 도시된 제 2 동작 모드에서, 프리앰블(PRE)로 전송되는 것은 단일 신호 펄스들이 아니라 신호 펄스 시퀀스들(SIF)이다. 이를 신호 펄스 시퀀스들(SIF) 다음에, 도 5b에 도시된 예시적 실시예에서 신호 펄스 시퀀스(SIF) 내의 펄스들의 수에 따라 확장되는 보다 긴 신호 일시중지(SP)가 뒤따른다. 도 5b에 도시된 변형에서, 방출되는 평균 에너지는 변화되지 않고 에너지 밸런스는 변화없이 유지된다.

[0057] 본 발명에 따른 방법에서, 제 2 동작 모드에서, 프리앰블(PRE) 내의 프리앰블 심볼( $S$ )은, 도 5b에 도시된 변형으로 확장되며, 데이터 패킷들( $DP$ )의 반복이 회피될 수 있다는 점에서 인식 성능이 개선되거나 또는 향상된다. 바람직하게, 프리앰블 심볼( $S$ )의 변경은 시간 및 에너지에 대해 중립적이지만, 유리하게 데이터 패킷 손실율( $DPVR$ )은 대단히 감소된다.

[0058] 본 발명에 따른 방법에서, 펄스 형상은 바람직하게, 그의 위상각이 스펙트럼 펄스 응답의 극성으로부터 명확하게 유도되도록 선택된다. 예컨대, 선택된 펄스 형상은 가우스 펄스 형상, 가우스 더블릿 펄스 형상 또는 루트

레이즈트 펄스 코사인 펄스 형상이다.

[0059] 하나의 가능한 실시예에서, 수신 디바이스(3)에서, 수신된 심볼에 선행하는 부호(VZ)는 제곱 전에 결정되고, 결정된 선행 부호(VZ)는 프리앰블 인식을 위해 이용된다. 이러한 변형에서, 프리앰블 심볼(S)의 인식에 대한 훨씬 더 양호한 또는 훨씬 더 높은 인식 성능이 제공된다. 본 실시예에서, 이를 위해 도 2의 수신 디바이스(3)에서, 선행 부호 인식 회로가 HF 스테이지(6) 뒤에 제공되고, 상기 선행 부호 인식 회로는 신호 펄스에 선행하는 부호(VZ)를 결정하고, 그 다음에 결정된 선행 부호를 다시(again) 비트 또는 선행 부호 비트로서 ADC 원더(wander) 스테이지(9) 뒤에 삽입한다.

[0060] 도 4b는 본 발명에 따른 방법에서 이용되는 데이터 패킷(DP)의 데이터 부분을 도시한다. 데이터 부분은 버스트 위치 변조(burst position modulation; BPM)를 이용하여 변조될 수 있다. 이러한 동안, 긴 일시중지들이 뒤따르는 매우 짧은, 고-에너지 펄스 시퀀스들이 전송될 수 있다. 전송된 정보는 심볼에 대한, 즉 전측 또는 후측 절반(front or rear half)에 대한 기간 내에서 펄스 버스트의 위치에 의해 코딩된다. 이러한 동안, 단지 절반(half)의 전측 쿼터만이, 즉 각각의 심볼 기간의 쿼터 1 및 쿼터 3 만이 모든 경우들에서 이용된다. 각각의 절반의 제 2 쿼터는 심볼간 간섭을 감소시키기 위해 안전 거리 또는 가드 간격(GI)으로서 제공된다. 결과적으로, 심볼 간격은 도 4b에 도시된 데이터 구조를 갖는다. 심볼 간격은 길이( $T_{BPPM}$ )를 갖는 2개의 절반들로 이루어지고, 그 각각에서, 제 2 절반은 가드 간격(GI)으로서 자유롭게 유지된다. 차례로, 2개의 나머지 쿼터들은 길이( $t_{burst}$ )를 갖는 몇몇의 온-호핑(on-hopping) 위치들로 다시 분할된다. 각각의 데이터 비트에 대해, 시스티매틱 컨벌루션 디코더(systematic convolution decoder)의 체크섬(checksum)을 포함하는 제 2 비트는 펄스 버스트의 개개의 펄스의 위상각으로 코딩된다.

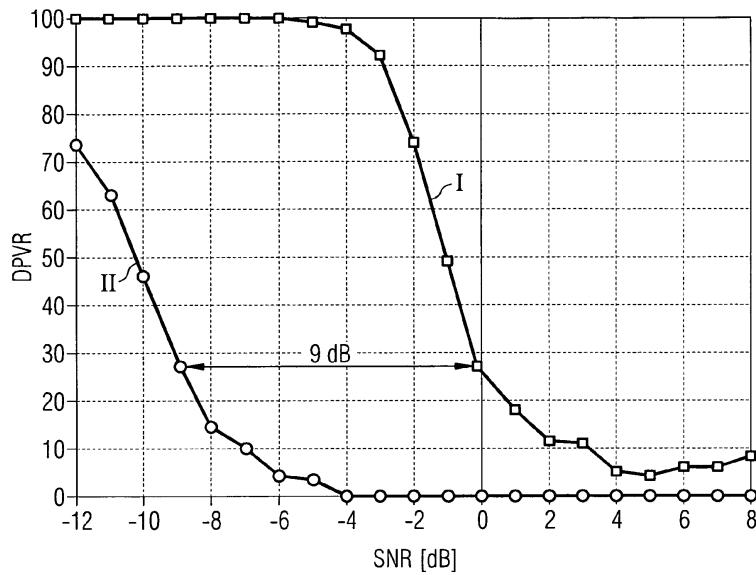

[0061] 도 6은 제어 네트워크의 네트워크 노드들(1) 사이의 데이터 패킷들(DP)의 송신을 위한 본 발명에 따른 방법에서 데이터 패킷 손실율(DPVR)에 있어서의 감소를 설명하는 도면이다. 증가하는 신호-잡음비(SNR)는 도 6에 도시된 바와 같이 데이터 패킷 손실율(DVPR)을 감소시킨다. 데이터 패킷 손실율(DVPR)은 또한, 상승하는 프리앰블 버스트 길이(PBL)를 따라 하강한다.

[0062] 곡선 I은 프리앰블 서브심볼(C)에 대한 데이터 패킷 손실율(DPVR)을 도시하고, 상기 프리앰블 서브심볼(C)은 개별적으로 전송된 단일 신호 펄스( $N=1$ )의 위상각에 의해 코딩된다. 결과적으로, 곡선 I은 제어 네트워크의 네트워크 노드들(1) 사이의 데이터 패킷들(DP)의 와이어-프리 송신을 위한 본 발명에 따른 방법의 제 1 동작 모드에서의 거동을 도시한다.

[0063] 곡선 II는 신호 펄스 시퀀스(SIF)의 다수의( $N=2$ ) 연속적인 신호 펄스들을 이용한 제 2 동작 모드에서의 데이터 패킷 손실율(DPVR)의 거동을 도시한다. 제 2 동작 모드에서 신호 펄스 시퀀스(SIF) 내의 신호 펄스들의 수가  $N=4$ 이면, 거동은 도 6의 곡선 III에 의해 표시된 바와 같다.

[0064] 도 6에 도시된 바와 같이, 심지어 겨우 4개의 연속적인 신호 임펄스들( $N=4$ )을 이용하여, 데이터 패킷 손실율(DPVR)은 거의 0으로 감소될 수 있고, 그러므로 심지어 신호-잡음비(SNR) = -15 decibels를 갖는 거의 100%의 성공적인 동기화가 허용된다.

[0065] 선행 부호 인식의 부가적인 성능은 도 7에 도시된 신호-잡음비(SNR)에 따라 데이터 패킷 손실율(DPVR)의 도시된 코스를 초래한다. 도 7에서 확인할 수 있는 바와 같이, 프리앰블 코드들의 선행 부호 인식은 선행 부호 인식을 갖지 않는 수신기에 비해 심지어 9 decibel의 더 나쁜(worse) 신호-잡음비(SNR)를 갖는 동일한 데이터 패킷 손실율(DPVR)을 달성한다. 도 7에서, 곡선 I은 선행 부호 인식을 갖지 않는 경우를 도시하고, 곡선 II는 선행 부호 인식을 갖는 수신 디바이스의 경우에서의 코스를 도시한다.

도면

도면1

도면2

도면3

## 도면4

a)

DP

b)

DP

## 도면5

a)

b)

도면6

도면7