**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

*H01L 21/76* (2006.01)

(45) 공고일자

2006년12월11일

(11) 등록번호

10-0654871

(24) 등록일자

2006년11월30일

(21) 출원번호 10-2004-0082084

(22) 출원일자 2004년10월14일

심사청구일자 2004년10월14일

(65) 공개번호 10-2005-0043622

(43) 공개일자 2005년05월11일

(30) 우선권주장 JP-P-2003-00376639 2003년11월06일 일본(JP)

(73) 특허권자 가부시끼가이샤 르네사스 테크놀로지

일본 100-6334 도쿄도 지요다구 마루노우찌 2-초메 4-1

(72) 발명자 쯔지우찌미끼오

일본 도쿄도 지요다구 마루노우찌 2초메 4-1 가부시끼가이샤 르네사스

테크놀로지 내

이와마쓰도시아끼

일본 도쿄도 지요다구 마루노우찌 2초메 4-1 가부시끼가이샤 르네사스

테크놀로지 내

(74) 대리인 장수길

이중희

구영창

심사관 : 소재현

전체 청구항 수 : 총 14 항

**(54) 반도체 장치의 제조 방법**

**(57) 요약**

반도체 디바이스가 갖는 성능 및 신뢰성이 금속 오염 물질에 의해 저하되는 것을 방지한다. 산화 실리콘 기판(1)과 실리콘 막(2)으로 SOI 기판이 형성된다. 실리콘막(2)의 표면이 산화되어 실리콘 산화막(3)이 형성된다. 다결정 실리콘(4)과 실리콘 질화막(5)이 실리콘 산화막(3) 상에 순서대로 형성된다. 그리고, 트렌치(7)가 영역 R1에 형성된다. 트렌치(7)에 절연 재료인 실리콘 산화막(13)이 매립된다.

**내용**

도 4

**특허청구의 범위**

## 청구항 1.

- (a) 산화 실리콘 기판 상의 실리콘막 상에, 실리콘 산화막과, 다결정 실리콘파, 실리콘 질화막을 순서대로 적층하는 공정과,

- (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘파, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과,

- (c) 상기 트렌치에 노출되는 상기 실리콘막의 표면에 600°C 이하에서 절연막을 형성하는 공정과,

- (d) 상기 절연막을 제거하는 공정과,

- (e) 상기 트렌치에 절연 재료를 매립하는 공정

- 을 포함하는 반도체 장치의 제조 방법.

## 청구항 2.

제1항에 있어서,

상기 공정 (c)는, 200°C ~ 600°C에서 상기 실리콘막의 표면을 래디컬 산화, 플라즈마 산화 혹은 플라즈마 질화하는 반도체 장치의 제조 방법.

## 청구항 3.

제1항에 있어서,

상기 공정 (c)는, 오존계 용액을 이용하여 20°C ~ 120°C에서 상기 실리콘막의 표면을 산화하는 반도체 장치의 제조 방법.

## 청구항 4.

- (a) 산화 실리콘 기판 상의 실리콘막 상에, 실리콘 산화막과, 다결정 실리콘파, 실리콘 질화막을 순서대로 적층하는 공정과,

- (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘파, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과,

- (c) 800°C ~ 1200°C에서, 30초~4시간의 어닐링을 행하고, 상기 트렌치에 노출되는 상기 실리콘막의 표면에 절연막을 형성하는 공정과,

- (d) 상기 절연막을 제거하는 공정과,

- (e) 상기 트렌치에 절연 재료를 매립하는 공정

- 을 포함하는 반도체 장치의 제조 방법.

## 청구항 5.

제4항에 있어서,

상기 공정 (c)의 상기 어닐링은, 질소 분위기 내 혹은 아르곤/산소 분위기 내에서 행하는 반도체 장치의 제조 방법.

### 청구항 6.

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 공정 (d)와 상기 공정 (e)의 사이에, 상기 트렌치에 노출되는 상기 실리콘막의 표면에 산화막을 형성하는 공정을 더 포함하는 반도체 장치의 제조 방법.

### 청구항 7.

(a) 산화 실리콘 기판 상의 실리콘막 상에 실리콘 산화막과, 다결정 실리콘과, 실리콘 질화막을 순서대로 적층하는 공정과,

(b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘과, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과,

(c) 상기 트렌치에 노출되는 상기 실리콘막의 표면을, 웨트 에칭에 의해 제거하는 공정과,

(d) 상기 트렌치에 절연 재료를 매립하는 공정

을 포함하는 반도체 장치의 제조 방법.

### 청구항 8.

제7항에 있어서,

상기 공정 (c)에서 행하는 상기 웨트 에칭은, 암모니아 과수계 용액, 암모니아 용액, 완충 불산 용액 및 수산화칼륨 용액 중 어느 하나를 이용하여, 20°C~150°C에서 행하는 반도체 장치의 제조 방법.

### 청구항 9.

제7항 또는 제8항에 있어서,

상기 공정 (c)와 상기 공정 (d)의 사이에, 상기 트렌치에 노출되는 상기 실리콘막의 표면에 산화막을 형성하는 공정을 더 포함하는 반도체 장치의 제조 방법.

### 청구항 10.

제1항 내지 제5항, 제7항 및 제8항 중 어느 한 항에 있어서,

상기 트렌치에 절연 재료를 매립하는 공정 후에, 600°C 이하에서 1시간 이상 어닐링하는 공정을 더 포함하는 반도체 장치의 제조 방법.

### 청구항 11.

제1항 내지 제5항, 제7항 및 제8항 중 어느 한 항에 있어서,

상기 트렌치에 절연 재료를 매립하는 공정 후에, 표면에 노출된 상기 절연 재료의 상기 실리콘막측을 곡면 형상으로 하는 공정을 더 포함하는 반도체 장치의 제조 방법.

### 청구항 12.

- (a) 산화 실리콘 기판 상의 실리콘막 상에 실리콘 산화막과, 다결정 실리콘과, 실리콘 질화막을 순서대로 적층하는 공정과,

- (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘과, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과,

- (c) 상기 트렌치에 노출되는 상기 실리콘막의 표면에 산화막을 형성하는 공정과,

- (d) 상기 트렌치에 절연 재료를 매립하는 공정과,

- (e) 600°C 이하에서 1시간 이상 어닐링하는 공정

- 을 포함하는 반도체 장치의 제조 방법.

### 청구항 13.

제12항에 있어서,

상기 공정 (e) 후에, 상기 실리콘막에 웨爾 영역을 형성하는 공정을 더 포함하는 반도체 장치의 제조 방법.

### 청구항 14.

제12항 또는 제13항에 있어서,

상기 트렌치에 상기 절연 재료를 매립하는 공정 후에, 표면에 노출된 상기 절연 재료의 상기 실리콘막측을 곡면 형상으로 하는 공정을 더 포함하는 반도체 장치의 제조 방법.

**명세서**

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 반도체 장치의 제조 방법에 관한 것으로, 예를 들면, 트랜지스터나 집적 회로 메모리에 적용할 수 있다.

종래부터, 반도체 디바이스를 제조하는 기술의 하나로서, MOS(Metal Oxide Semiconductor) 구조 등을 갖는 디바이스를 SOI(Silicon on Insulating substrate) 기판 상에 형성하고 있다. 또한, 소자간의 분리를 행하기 위해서, pn 접합 분리나 산화막 분리(예를 들면, LOCOS(Local Oxidation of Silicon)법 등) 등이 이용되고 있다.

또한, 실리콘 기판 중의 오염 물질의 농도를 저하시키고, 그 후에 형성되는 산화막에 오염 물질이 확산되는 것을 방지하는 기술이, 특히 문헌1에 개시되어 있다. 소자간의 분리를 행하기 위한 트렌치 분리 영역을 형성하는 기술이, 특히 문헌2에 개시되어 있다. 또한, 실리콘 질화막과 다결정 실리콘·실리콘 산화막의 적층 구조를, 후술하는 CMP의 마스크에 채용하는 기술이 비 특허 문헌1에 소개되어 있다. 오염 금속의 확산 계수와 온도의 관계가 비 특허 문헌2에 소개되어 있다.

[특허 문헌1] 일본 특개평10-209446호 공보

[특허 문헌2] 일본 특표평11-513538호 공보

[비 특허 문헌1] 케이. 호리타(K.Horita) 외 7명, 「Advanced Shallow Trench Isolation to Suppress the Inverse Narrow Channel Effects for  $0.24\mu\text{m}$  Pitch Isolation and Beyond」, 2000 Symposium on VLSI Technology Digest of Technical Papers, 2000년, p.178~179

[비 특허 문헌2] 오오미 타다히로 외 감수, 「실리콘의 과학」 리얼라이즈(REALIZE Inc)사, p.1015

### 발명이 이루고자 하는 기술적 과제

그런데, SOI 기판 상에 디바이스를 형성할 때에 금속 오염 물질이 총 사이에 잔류하고, 또한, 소자 분리를 행하기 위한 트렌치를 형성할 때에 트렌치 바닥부에 금속 오염 물질이 부착된다. 금속 오염 물질은, 반도체 디바이스가 갖는 성능 및 신뢰성을 저하시키는 원인이 된다.

지금까지도 금속 오염 물질을 제거하는 방법이 제안되고 있다. 즉, 실리콘 표면 상에 게이트 절연막을 형성하기 전에, 그 게이트 절연막이 형성되는 위치에 희생 산화막을 형성한다. 그리고, 실리콘과 희생 산화막의 계면에 금속 오염 물질을 확산·응집시키고, 희생 산화막을 제거함과 함께 금속 오염 물질을 제거한다.

그러나, 이 방법에는 다음과 같은 가능성을 생각할 수 있다. 즉, 그 응집된 금속 오염 물질이 실리콘 표면 상에 오목부의 흔적을 남기고, 그 실리콘 표면 상에 게이트 절연막을 형성하면, 그 오목부의 흔적에 응력이 발생하고, 절연막에 균열이 발생하여 절연 과괴를 일으킨다.

본 발명은, 상기의 사정을 감안하여 이루어진 것으로, 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지한다.

### 발명의 구성

본 발명에 따른 제1 반도체 장치의 제조 방법은, (a) 산화 실리콘 기판 상의 실리콘막 상에 실리콘 산화막과, 다결정 실리콘과, 실리콘 질화막을 순서대로 적층하는 공정과, (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘과, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과, (c) 상기 트렌치에 노출되는 상기 실리콘막의 표면에  $600^\circ\text{C}$  이하에서 절연막을 형성하는 공정과, (d) 상기 절연막을 제거하는 공정과, (e) 상기 트렌치에 절연 재료를 매립하는 공정을 포함한다.

본 발명에 따른 제2 반도체 장치의 제조 방법은, (a) 산화 실리콘 기판 상의 실리콘막 상에 실리콘 산화막과, 다결정 실리콘과, 실리콘 질화막을 순서대로 적층하는 공정과, (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘과, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과, (c) 상기 트렌치에 노출되는 상기 실리콘막의 표면을, 웨트 에칭에 의해  $1\text{nm} \sim 20\text{nm}$ 의 두께를 제거하는 공정과, (d) 상기 트렌치에 절연 재료를 매립하는 공정을 포함한다.

본 발명에 따른 제3 반도체 장치의 제조 방법은, (a) 산화 실리콘 기판 상의 실리콘막 상에 실리콘 산화막과, 다결정 실리콘과, 실리콘 질화막을 순서대로 적층하는 공정과, (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘과, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과, (c) 상기 트렌치에 노출되는 상기 실리콘막의 표면을, 웨트 에칭에 의해  $1\text{nm} \sim 20\text{nm}$ 의 두께를 제거하는 공정과, (d) 상기 트렌치에 절연 재료를 매립하는 공정을 포함한다.

본 발명에 따른 제4 반도체 장치의 제조 방법은, (a) 산화 실리콘 기판 상의 실리콘막 상에 실리콘 산화막과, 다결정 실리콘과, 실리콘 질화막을 순서대로 적층하는 공정과, (b) 소정 영역에서 상기 실리콘 질화막과, 상기 다결정 실리콘과, 상기 실리콘 산화막과, 상기 실리콘막을 에칭하여, 상기 실리콘막 내에 저면을 갖는 트렌치를 형성하는 공정과, (c) 상기 트렌치에 노출되는 상기 실리콘막의 표면에 산화막을 형성하는 공정과, (d) 상기 트렌치에 절연 재료를 매립하는 공정과, (e)  $600^\circ\text{C}$  이하에서 1시간 이상 어닐링하는 공정을 포함한다.

<실시예1>

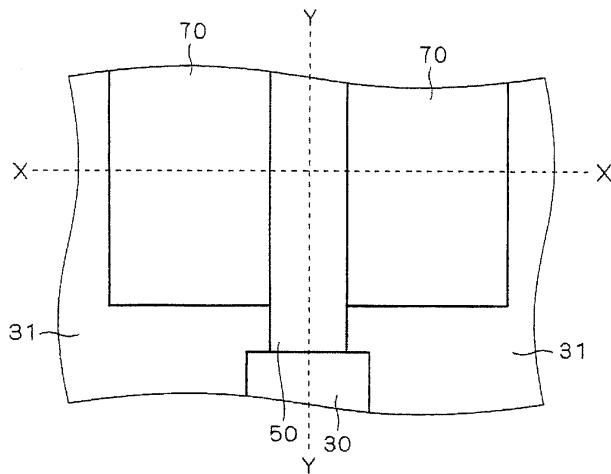

본 실시예에서는, 트렌치 내부를 저온에서 산화한다. 도 1은 본 실시예에서 설명되는 방법에 의해서 제작되는 반도체 장치의 평면도이다. 도 10 및 도 11은, 각각 도 1에서 도시되는 위치 Y-Y 및 위치 X-X에서의 개념적인 단면도이고, 도 2~도 10은, 위치 Y-Y에서 SOI 기판 상에 MOS 디바이스를 형성하는 과정을 순서대로 도시하는 단면도이다. 단, 본 명세서에서 말하는 MOS 디바이스는 게이트 전극의 재료로서 금속(Meta1)에 한정되지 않고, 도전성 반도체를 이용하는 경우를 포함하는 개념이다.

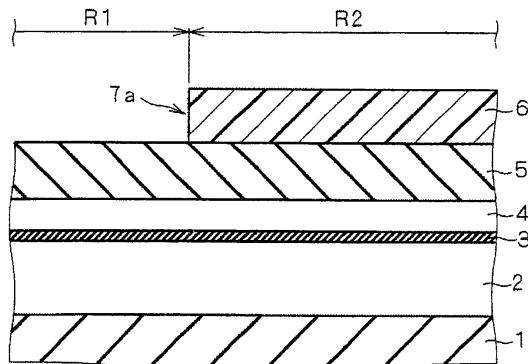

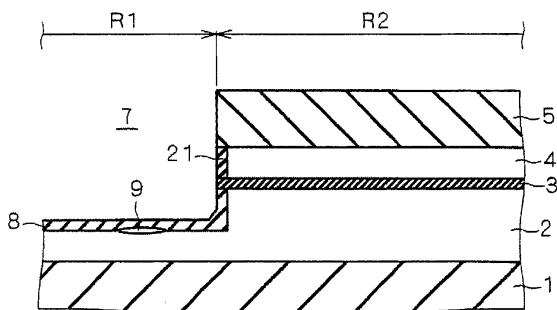

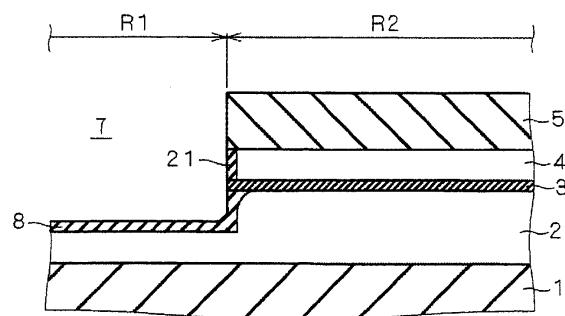

첫번째로, SOI 기판이 산화 실리콘 기판(1)과 실리콘막(2)으로 형성된다. 산화 실리콘 기판(1)과는 반대측에서 실리콘막(2)의 표면 상에, 실리콘 산화막(3)이 산화에 의해서 형성된다. 그리고 실리콘 산화막(3) 상에, 다결정 실리콘(4)과 실리콘 질화막(5)이 순서대로 적층된다. 영역 R1은 소자 분리를 위한 구성을 형성하기 위해서, 영역 R2는 소자를 형성하기 위해서 각각 설정된다. 실리콘 질화막(5) 상에는, 영역 R1에서 개구하여 영역 R2를 덮는 레지스트 수지(6)가 적층된다. 레지스트 수지(6)의 단면(7a)은 영역 R1, R2의 경계에 위치한다(도 2).

실리콘 산화막(3)이나 다결정 실리콘(4)·실리콘 질화막(5)을 형성하는 단계마다 금속 오염 물질이 부착될 가능성이 있다. 금속 오염 물질로서, 철(Fe)이나 니켈(Ni)·코발트(Co)·티탄(Ti)·알루미늄(Al)·크롬(Cr) 등을 생각할 수 있다.

두번째로, 레지스트 수지(6)의 단면(7a)에서 형성되는 패턴에 따라서, 실리콘 질화막(5)과 다결정 실리콘(4)·실리콘 산화막(3)·실리콘막(2)을 에칭함으로써, 영역 R1에 트렌치(7)가 형성된다. 레지스트(6)의 표면 상에 개구하여 내부가 중공인 트렌치(7)에서는, 실리콘막(2) 내에 저면이 위치한다(도 3). 트렌치(7)의 형성시에도 트렌치(7)의 저면에 금속 오염 물질이 부착될 가능성이 있다.

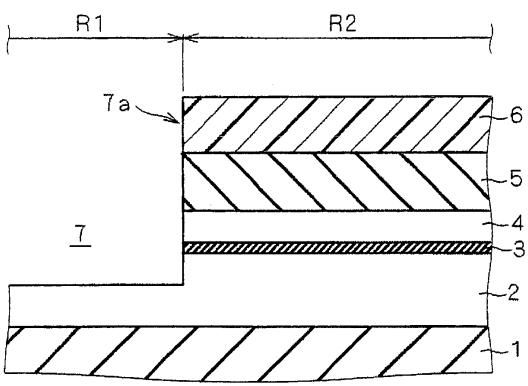

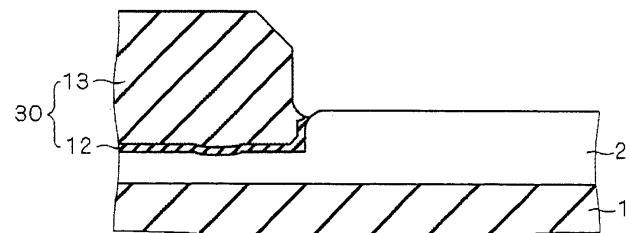

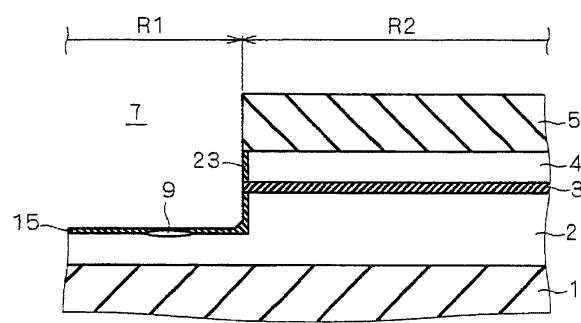

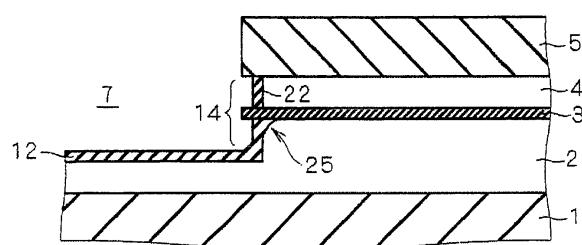

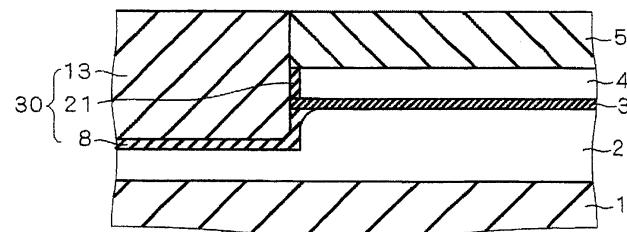

세번째로, 레지스트 수지(6)를 제거하여, 트렌치(7)에 노출되는 실리콘막(2)의 표면에 600°C 이하에서 절연막을 형성한다. 절연막을 형성하는 방법으로서 실리콘막(2)을 래디컬 산화 혹은 고밀도 플라즈마 산화하는 것 등을 채용할 수 있다. 예를 들면, 고밀도 플라즈마 산화를 행할 때에는, 기판 온도를 200°C ~ 600°C로 하고, 여기 에너지를 플라즈마로 공급한다. 이로써, 트렌치(7)에 있어서 노출된 실리콘막(2)의 표면 상에서 산화 반응을 일으켜, 실리콘 산화막(8)이 절연막으로서 형성된다. 이에 수반하여, 트렌치(7)의 측면에 노출된 다결정 실리콘(4)에 대해서도 산화되어, 실리콘 산화막(21)이 형성된다. 트렌치(7)의 저면에 부착된 금속 오염 물질은, 실리콘 산화막(8)과 실리콘막(2)의 계면에서, 혹은 실리콘 산화막(8)의 내부에서 응집하여 금속 실리사이드(9)로 된다(도 4).

형성하는 실리콘 산화막(8)의 두께는, 트렌치(7)의 저면에 부착된 금속 오염물질이 실리콘막(2)에 침입하는 깊이와, 금속 오염 물질을 어디에 응집시킬까에 따라서 정해도 된다. 금속 오염 물질은, 실리콘막(2)과 실리콘 산화막(8)의 계면에 응집시켜도 되고, 실리콘 산화막(8)의 내부에 응집시켜도 된다. 예를 들면, 금속 오염 물질의 침입 깊이가 최대 10nm라 한다면, 실리콘막(2)과 실리콘 산화막(8)의 계면에 오염 금속을 응집시키는 경우에는, 실리콘 산화막(8)의 두께를 1~10nm 정도로 하고, 금속 오염 물질을 실리콘 산화막(8)의 내부에 응집시키는 경우에는, 실리콘 산화막의 두께를 1~30nm 정도로 한다. 이러한 막 두께의 결정 방법은, 실리콘막(2)의 표면에 형성되는 절연막이 후술하는 바와 같은 실리콘 질화막인 경우에 있어서도 적용할 수 있다.

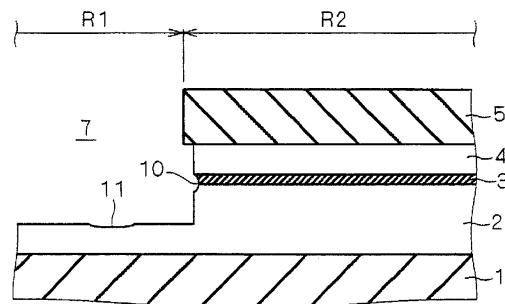

네번째로, 제3 공정에서 형성한 실리콘 산화막(8)을 HF(불화 수소산)계 용액에 의해서 제거한다. 이에 수반하여 금속 실리사이드(9)도 제거되어, 트렌치(7)의 실리콘막(2)에 있어서 오목부(11)가 형성된다. 이 때에는, 트렌치(7)의 측면에 노출되어 있는 부분에 대하여 제1 공정에서 형성된 실리콘 산화막(3)도 HF계 용액에 의해서 침식되고, 그 침식된 부분이 오목부(10)로 된다. 또한 제3 공정에서 형성된 실리콘 산화막(21)도 HF계 용액에 의해서 제거된다(도 5).

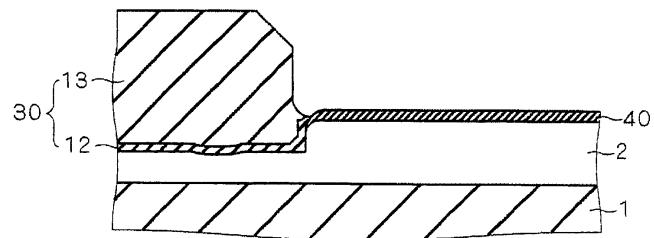

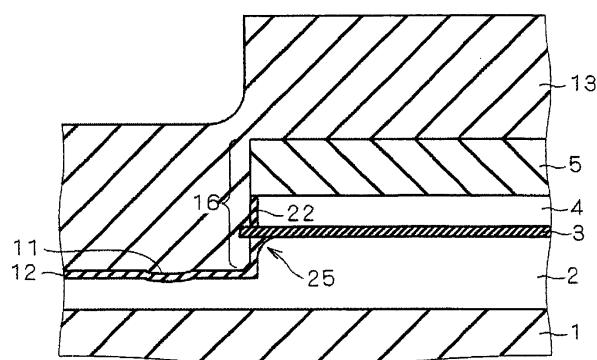

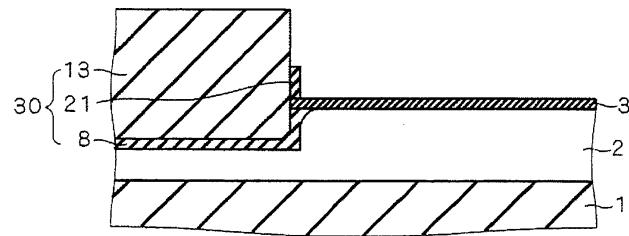

다섯번째로, 다시 산화함으로써, 트렌치(7)에 있어서 노출된 실리콘막(2)의 표면에 실리콘 산화막(12)을 형성한다. 이에 수반하여, 트렌치(7)의 측면에 노출된 부분에 대하여 다결정 실리콘(4)도 산화되어, 실리콘 산화막(22)이 형성된다. 이 때의 산화는, 실리콘 산화막(8)의 형성시와는 달리, 600°C 이하일 것을 필요로 하지 않는다. 그 후, 트렌치(7)를 매립하고, 또한 실리콘 질화막(5)의 표면 상을 덮는 절연 재료, 예를 들면, 실리콘 산화막(13)이 퇴적된다. 전자와 후자에 퇴적되는 실리콘 산화막(13)은 연속되어 있다(도 6).

실리콘 산화막(12)의 형성시에는, 오목부(10)에 응력이 발생하여 균열이 발생할 가능성도 생각할 수 있다. 그러나, 실리콘 산화막(13)이 매립된 트렌치(7)는 소자 분리를 위한 구성을 기능하기 때문에, 균열의 발생은 해당 기능에 대하여 문제로 되지 않는다.

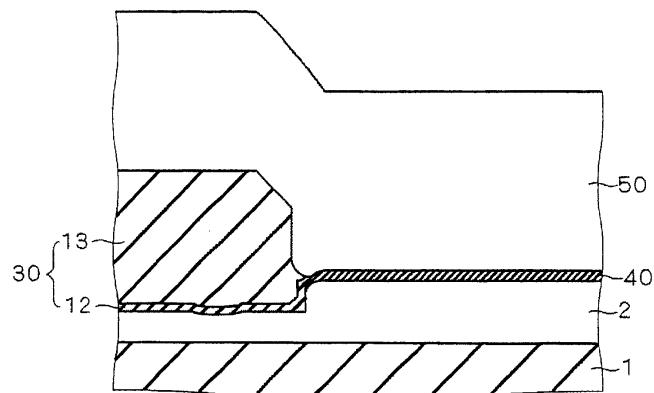

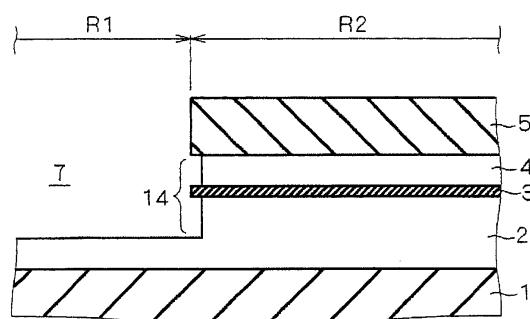

여섯번째로, CMP(Chemical and Mechanical Polishing)에 의해, 제5 공정에서 형성한 실리콘 산화막(13)을 연마하여 평탄화함과 함께, 실리콘 질화막(5)의 표면 전체를 노출시킨다(도 7). 이 때, 트렌치(7)의 내부에 잔존하는 실리콘 산화막(12, 13)이 소자를 분리하기 위한 산화막, 즉 분리 산화막(30)으로 된다.

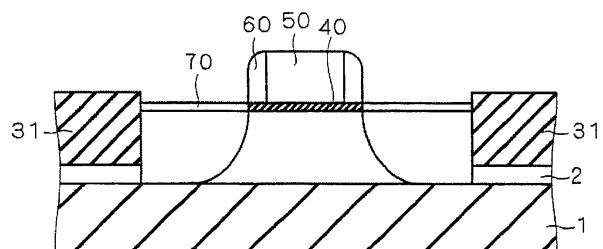

일곱번째로, 실리콘 질화막(5)과 다결정 실리콘(4)·실리콘 산화막(3)·실리콘 산화막(22)이 제거된다(도 8). 이를 제거에 의해 노출된 실리콘막(2)의 표면을 산화함으로써, 실리콘 산화막(40)이 형성된다(도 9). 그리고, 실리콘 산화막(13, 40)의 표면 상에 다결정 실리콘(50)을 퇴적한다(도 10).

여덟번째로, 제7 공정 후, 다결정 실리콘(50)의 패턴 에칭, 절연막의 형성 및 절연막의 패턴 에칭을 거쳐, 다결정 실리콘(50)의 측면에 절연막(60)을 형성한다. 그리고, 불순물 이온의 주입 및 금속 실리사이드막(70)의 형성에 의해 반도체 디바이스를 제작한다(도 11).

금속 오염 물질은, 반도체 디바이스 내에서 상대적으로 응력이 큰 부분에 확산·응집하기 쉽다. 트렌치(7)에 관한 응력은 다른 부분에 비해 커진다고 생각되기 때문에, 트렌치(7)의 저면에 부착된 금속 오염 물질은 산화시 그곳에 잔류하기 쉬워진다.

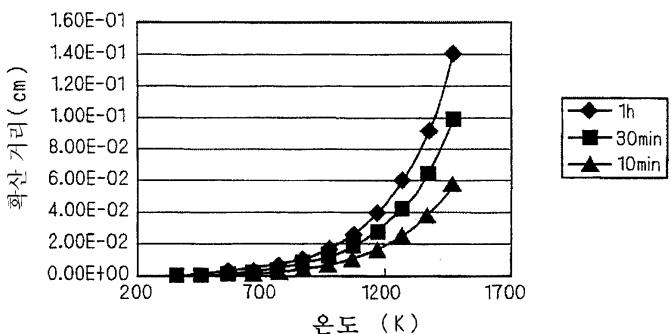

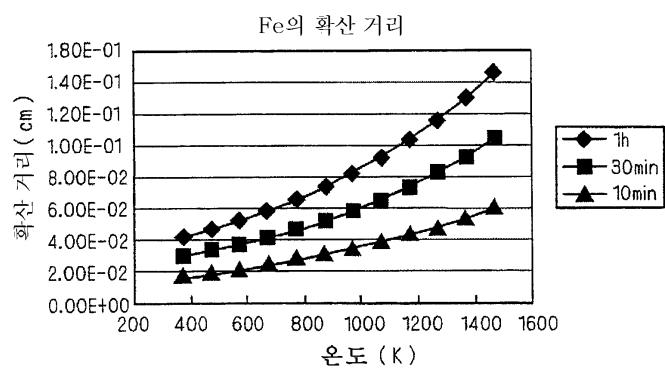

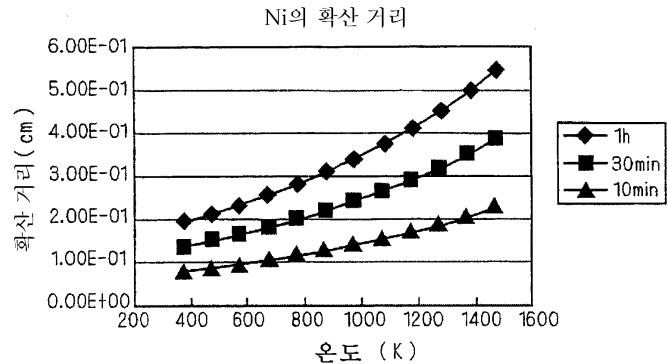

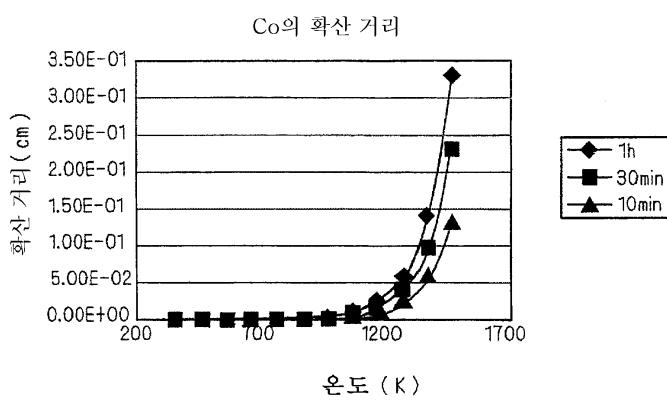

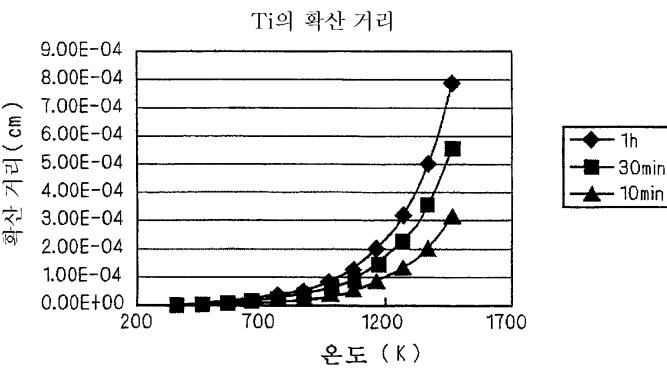

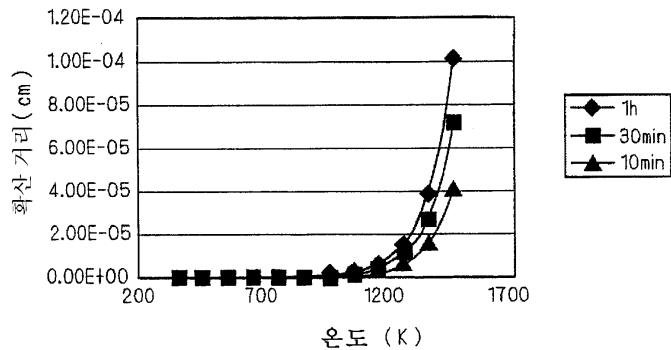

한편, 금속 오염 물질의 확산은 온도에 의존한다. 금속 오염 물질의 온도와 확산 거리의 관계가 금속 오염 물질의 종류마다 도 24~도 29에 되어 있다. 금속 오염 물질의 확산 거리는,  $\sqrt{(DSt)}$ 에 의해 구해진다. 여기서, D는 확산 계수(단위는  $\text{cm}^2/\text{sec}$ 이다), t는 확산 시간(단위는 sec이다)을 각각 나타낸다. 확산 계수 D는, 비 특허문현2 중의 Fig.1에 소개되는 확산 계수 D와 온도의 관계로부터, 금속 오염 물질마다 구해진다.

실리콘막(2)의 표면 상에 실리콘 산화막(8)을 형성하는 온도가 600°C(도면에 도시되는 그래프의 획축을 나타내는 온도의 단위는 켈빈(K)으로, 873K에 대응한다) 이하이기 때문에, 도 24~도 29로부터 금속 오염 물질의 확산 거리가 작아지는 것을 이해할 수 있다. 이 때문에, 트렌치(7)의 저면에 있는 금속 오염 물질은, 영역 R1으로부터 영역 R2에 확산되기 어려워, 실리콘 산화막(8)과 실리콘막(2)의 계면, 혹은 실리콘 산화막(8)의 내부에서 응집하기 쉬워진다. 도 26~도 29에 도시되는 바와 같이, 600°C 이하에서는 Co·Ti·Al·Cr의 확산 거리가 매우 작아, 특히 이들 오염 물질에 대하여 본 실시예가 유효하다. 따라서, 반도체 디바이스의 제작 과정에서 혼입하는 금속 오염 물질을 제거할 수 있어, 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

트렌치(7)의 저면에 부착된 금속 오염 물질을 제거하는 경우 뿐만 아니라, 제1 공정에 기재하는 실리콘막(2)이나 실리콘 산화막(3)·다결정 실리콘(4)·실리콘 질화막(5) 각각의 계면(영역 R2에 있는 계면)에 존재하는 금속 오염 물질을 제거하는 경우에도, 실리콘 산화막(8)의 형성이 유효하다. 즉, 실리콘 산화막(8)의 형성에 의해, 영역 R2에 있는 계면에 존재하는 금속 오염 물질이 실리콘막(2)과 실리콘 산화막(8)의 계면, 혹은 실리콘 산화막(8)의 내부에 확산·응집하여, 금속 오염 물질은 금속 실리사이드(9)로 된다. 따라서, 도 24, 도 25에 도시된 바와 같이 600°C 이하에서도 확산 거리가 큰 Fe·Ni 등에 특히 유효하다.

이 경우에도 상술한 내용과 마찬가지로, 실리콘 산화막(8)과 함께 금속 실리사이드(9)가 HF계 용액에 의해 제거된다. 따라서, 반도체 디바이스의 제작 과정에서 혼입하는 금속 오염 물질을 제거할 수 있어, 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

상기 제3 공정에서, 트렌치(7)에 노출된 실리콘막(2)의 표면 상을 플라즈마 질화해도 된다. 이 경우, 기판 온도를 200°C~600°C로 하고, 여기 에너지를 플라즈마로 공급한다. 이로써, 트렌치(7)에 있어서 노출된 실리콘막(2)과 다결정 실리콘(4)의 표면 상에서 질화 반응이 발생하여, 실리콘 질화막이 절연막으로서 형성된다. 금속 오염 물질은, 실리콘 질화막과 실리콘막(2)의 계면에, 혹은 실리콘 산화막(8)의 내부에 확산·응집하여 금속 실리사이드(9)로 된다. 그 후, 제4 공정에서 HF계 용액 대신에 인산계 용액을 이용함으로써, 실리콘 질화막과 함께 금속 실리사이드(9)가 제거된다.

상기 제3 공정에서, 트렌치(7)에 노출된 실리콘막(2)의 표면 상을 오존계 용액에 의해 산화해도 된다. 이 경우, 기판 온도를 20°C~120°C로 한다. 이로써, 트렌치(7)에 있어서 노출된 실리콘막(2)과 다결정 실리콘(4)의 표면 상에서 산화 반응이 발생하여, 실리콘 산화막(8)이 절연막으로서 형성된다. 금속 오염 물질은, 실리콘 산화막(8)과 실리콘막(2)의 계면에, 혹은 실리콘 산화막(8)의 내부에 확산·응집하여 금속 실리사이드(9)로 된다. 그 후, 제4 공정에서, 실리콘 산화막(8)과 함께 금속 실리사이드(9)가 HF계 용액에 의해 제거된다.

실리콘막(2)의 표면 상을, 플라즈마에 의한 질화 및 오존계 용액에 의한 산화 중 어느 방법에 있어서도, 상술한 예를 들면, 플라즈마에 의해 산화하는 방법과 마찬가지로, 반도체 디바이스의 제작 과정에서 혼입하는 금속 오염 물질을 제거할 수 있다. 따라서, 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

#### <실시예2>

본 실시예에서는, 질소 분위기 내에서 어닐링을 행한다. 도 12~도 14는, 도 1에서 도시되는 위치 Y-Y에서의 개념적인 단면도이고, SOI 기판 상에 MOS 디바이스를 형성하는 과정을 순서대로 도시한다.

첫번째로, 실시예1에서 기재되는 제1 및 제2 공정과 마찬가지로 SOI 기판 상에 각종의 막을 형성하고, 그 후에 트렌치(7)를 형성한다(도 3). 이 때, 실리콘막(2)이나 실리콘 산화막(3)·다결정 실리콘(4)·실리콘 질화막(5)을 형성하는 각각의 단계에서 금속 오염 물질이 부착되는 것, 또한 트렌치(7)의 저면에 금속 오염 물질이 부착되는 것의 각각의 가능성을 생각할 수 있다.

두번째로, 레지스트 수지(6)를 제거하고 질화한다. 이 질화에서는, 800°C ~ 1200°C의 질소 분위기 내에서 30초간~4시간, 실리콘막(2)의 표면을 어닐링한다. 이로써, 트렌치(7)에 있어서 노출된 실리콘막(2)의 표면에, 실리콘 질화막(15)이 절연막으로서 형성된다. 이에 수반하여, 트렌치(7)의 측면에 노출된 부분에 대하여 다결정 실리콘(4)도 질화되어, 실리콘 질화막(23)이 형성된다. 실리콘막(2)이나 실리콘 산화막(3)·다결정 실리콘(4)·실리콘 질화막(5)의 각각의 계면에 있는 금속 오염 물질은, 실리콘막(2)과 실리콘 질화막(15)의 계면에, 혹은 실리콘 질화막(15)의 내부에 확산·응집하여 금속 실리사이드(9)로 된다(도 12).

실시예1과 마찬가지로, 형성하는 실리콘 질화막(15)의 두께는, 트렌치(7)의 저면에 부착된 금속 오염 물질이 실리콘막(2)에 침입하는 깊이와, 금속 오염 물질을 어디에 응집시킬까에 따라서 정해도 된다.

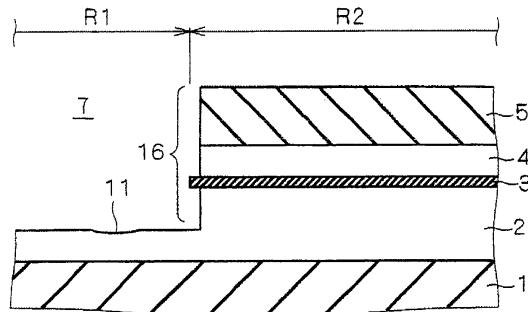

세번째로, 제2 공정에서 형성한 실리콘 질화막(15)을, 20°C ~ 180°C의 인산계 용액에 의해 제거한다. 이에 수반하여 금속 실리사이드(9)도 제거되어, 트렌치(7)의 실리콘막(2)에 있어서 오목부(11)가 형성된다. 이 때는, 트렌치(7)의 측면에 노출되어 있는 부분에 대하여 제1 공정에서 형성된 실리콘 질화막(5)도 인산계 용액에 의해서 침식된다. 또한, 실리콘 질화막(23)도 인산계 용액에 의해서 제거된다. 이 때, 실리콘 산화막(3)은 인산계 용액에 반응하지 않기 때문에, 실리콘 산화막(3)이 돌출된 형상(16)을 트렌치(7)의 측면에 띤다(도 13).

실리콘 질화막(15)의 제거에, 20°C ~ 100°C의 HF 용액을 이용하여도 된다. 이 경우에도 마찬가지로, 금속 실리사이드(9)를 제거할 수 있다.

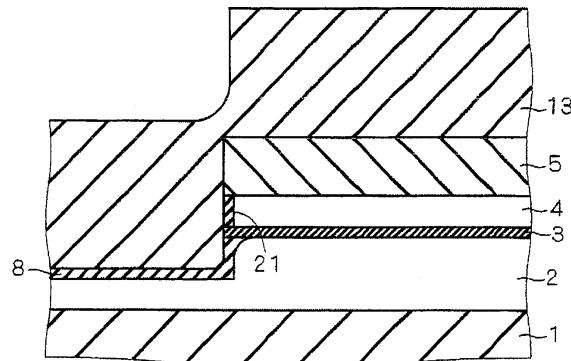

네번째로, 산화함으로써, 트렌치(7)에 노출된 실리콘막(2)의 표면에 실리콘 산화막(12)을 형성한다. 이에 수반하여, 트렌치(7)의 측면에 노출된 부분에 대하여 다결정 실리콘(4)도 산화되어, 실리콘 산화막(22)이 형성된다. 그 후, 트렌치(7)를 매립하고, 또한 실리콘 질화막(5)의 표면 상을 덮는 절연 재료, 예를 들면, 실리콘 산화막(13)이 퇴적된다. 전자와 후자에 퇴적된 실리콘 산화막(13)은 연속되어 있다(도 14).

실리콘 산화막(12)의 형성시에는, 오목부(10)에 응력이 발생하여 균열이 발생할 가능성도 생각할 수 있다. 그러나, 실리콘 산화막(13)이 매립된 트렌치(7)는 소자 분리를 위한 구조으로서 기능하기 때문에, 균열의 발생은 해당 기능에 대하여 문제로 되지 않는다.

다섯번째로, 실시예1에서 기재되는 제6~8의 공정과 마찬가지로, 반도체 디바이스를 제작한다.

반도체 디바이스의 다른 부분에 비해 트렌치(7)에 관한 응력은 커진다고 생각된다. 이 때문에, 실리콘막(2)과 실리콘 질화막(15)의 계면에 어닐링에 의해서 확산된 금속 오염 물질은, 그 계면에 잔류하게 되어 응집하기 쉬워진다. 또한, 30초간 ~ 4시간으로 설정된 어닐링 시간은, 실리콘막(2)과 실리콘 질화막(15)의 계면에 금속 오염 물질이 도달하기에 충분한 시간이라고 생각된다.

예를 들면, Fe나 Ni·Co·Cr에 대하여, 이들 금속 오염 물질이 확산되어야만 하는 거리를 0.1mm로 하는 경우, 1200°C에서 1.22초~18.3초의 확산 시간을, 800°C에서 2.60초~53.6분의 확산 시간을 각각 필요로 한다. 또한, 확산되어야만 하는 거리를 1mm로 할 경우, 1200°C에서 2.03분~30.4분의 확산 시간을, 800°C에서 4.34분~89.4시간의 확산 시간을 각각 필요로 한다. 이와 같이, 어닐링 시간은 금속 오염 물질의 종류나 온도·확산 거리에 따라 설정된다.

상술한 내용으로부터, 800°C ~ 1200°C의 질소 분위기 내에서 30초간~4시간에 걸쳐 실리콘막(2)의 표면을 어닐링함으로써, 영역 R2 내의 금속 오염 물질은 R1에 확산하여, 실리콘막(2)과 실리콘 질화막(15)의 계면에서 응집하기 쉬워진다. 따라서, 반도체 디바이스의 제작 과정에서 혼입하는 금속 오염 물질을 제거할 수 있어, 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

실리콘막(2)이나 실리콘 산화막(3)·다결정 실리콘(4)·실리콘 질화막(5)의 각각의 계면에 존재하는 금속 오염 물질을 제거하는 경우 뿐만 아니라, 트렌치(7)의 저면에 부착되는 금속 오염 물질을 제거하는 경우에도, 본 실시예의 특징 중 800°C ~ 1200°C의 질소 분위기 내에서 어닐링하는 것이 유효하다.

상기 제2 공정에서, 트렌치(7)에 노출된 실리콘막(2)의 표면을, 800°C ~ 1200°C의 아르곤/산소 분위기 내에서 어닐링해도 된다. 이 경우, 실리콘막(2)의 표면 상이 산화되어 실리콘 산화막이 절연막으로서 형성됨과 함께, 실리콘막(2)과 실리콘 산화막의 계면에 미세한 요철이 형성된다. 이로 인해, 그곳에 잔류하기 쉬워진 금속 오염 물질은, 실리콘 산화막과 실리콘 막(2)의 계면에서, 혹은 실리콘 산화막의 내부에서 응집하여 금속 실리사이드(9)로 된다. 그 후, 제3 공정에서, 실리콘 산화막과 함께 금속 실리사이드(9)가 HF계 용액에 의해 제거된다.

### <실시예3>

본 실시예에서는, 트렌치 내부를 에칭한다. 도 15~도 17은, 도 1에서 도시되는 위치 Y-Y에서의 개념적인 단면도로, SOI 기판 상에 MOS 디바이스를 형성하는 과정이 순서대로 도시된다.

첫번째로, 실시예1에서 기재되는 제1 및 제2 공정과 마찬가지로 SOI 기판 상에 각종의 막을 형성하고, 그 후에 트렌치(7)를 형성한다(도 3). 이 때, 트렌치(7)의 저면에 금속 오염 물질이 부착될 가능성이 있다.

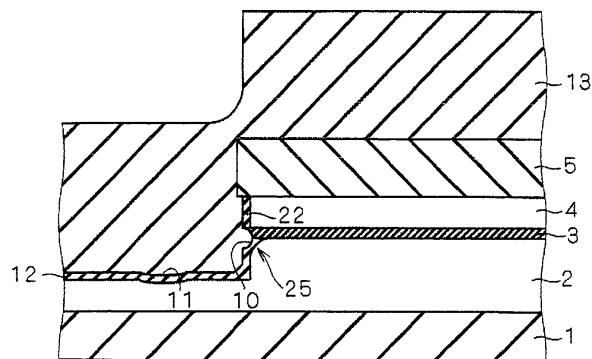

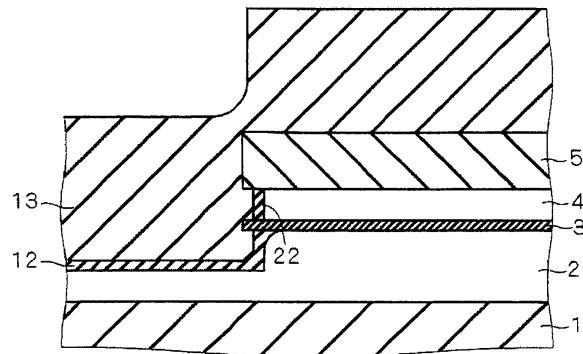

두번째로, 레지스트 수지(6)를 제거하고, 20°C ~ 150°C의 암모니아과수계 용액을 이용하여 트렌치(7)에 노출된 실리콘막(2)의 표면을 웨트 에칭한다. 이로써, 실리콘막(2)에 부착된 금속 오염 물질을 제거할 수 있다. 예를 들면, 금속 오염 물질의 실리콘막(2)에 대한 침입 깊이가 10nm 정도인 경우에는, 웨트 에칭에 의해 제거하는 실리콘막의 두께가 10nm ~ 20nm인 것이 바람직하다. 암모니아과수계 용액은 다결정 실리콘(4)도 에칭하기 때문에, 트렌치(7)의 측면에 있는 다결정 실리콘(4)과 실리콘막(2)의 각각의 단면이 후퇴되어 실리콘 산화막(3)이 돌출된 형상(14)을 트렌치(7)의 측면에 띤다(도 15).

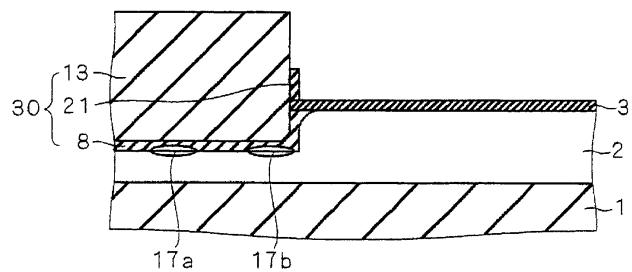

세번째로, 트렌치(7)에 노출된 실리콘막(2)의 표면을 산화하여 실리콘 산화막(12)을 형성한다. 이에 수반하여, 트렌치(7)의 측면에 노출된 부분에 대하여 다결정 실리콘(4)도 산화되어, 실리콘 산화막(22)이 형성된다(도 16). 그 후, 트렌치(7)를 매립하고, 또한 실리콘 질화막(5)의 표면 상을 덮는 절연 재료, 예를 들면, 실리콘 산화막(13)이 퇴적된다. 전자와 후자에 퇴적된 실리콘 산화막(13)은 연속되어 있다(도 17).

네번째로, 실시예1에서 기재되는 제6~제8 공정과 마찬가지로 반도체 디바이스를 제작한다.

암모니아과수계 용액에 의해, 트렌치(7)에 노출된 실리콘막(2)의 표면을 에칭함으로써, 트렌치(7)의 저면에 부착된 금속 오염 물질을 제거한다. 따라서, 반도체 디바이스의 제작 과정에서 혼입하는 금속 오염 물질을 제거할 수 있어, 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

상기 제2 공정에서, 20°C ~ 150°C의 암모니아수용액이나 20°C ~ 150°C의 완충 불산(BHF) 용액, 20°C ~ 150°C의 수산화칼륨(KOH) 용액 등을 이용하여, 트렌치(7)에 노출된 실리콘막(2)의 표면을 웨트 에칭해도 된다. 이 경우에도, 상술한 20°C ~ 150°C의 암모니아과수계 용액을 이용했을 때와 마찬가지의 효과를 얻을 수 있다.

상술한 실시예1의 제5 공정, 실시예2의 제4 공정, 실시예3의 제3 공정에서, 각각 트렌치(7)에 있어서 노출된 실리콘막(2)의 표면에 실리콘 산화막(12)을 형성함으로써, 실리콘막(2)의 트렌치(7)측의 엣지 부분(25)이 곡면 형상으로 된다(도 6, 도 14, 도 16). 이로써, 엣지부(25)가 각자 있을 때에 일어날 가능성이 있는 전계 집중을 저감할 수 있다. 따라서, 반도체 장치가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

상기 어느 실시예에 있어서도 실리콘 산화막(12)을 형성하지 않는 경우를 생각할 수 있는데, 예를 들면, 실리콘 산화막(12)을 형성함으로써 전계 집중을 회피할 수 있다.

### <실시예4>

본 실시예에서는, 저온에서 어닐링을 행한다. 도 18~도 22는, 도 1에서 도시되는 위치 Y-Y에서의 개념적인 단면도로, SOI 기판 상에 MOS 디바이스를 형성하는 과정을 순서대로 도시한다.

첫번째로, 실시예1에서 기재되는 제1 및 제2 공정과 마찬가지로 SOI 기판 상에 각종의 막을 형성하고, 그 후에 트렌치(7)를 형성한다(도 3). 이 때, 실리콘막(2)이나 실리콘 산화막(3)·다결정 실리콘(4)·실리콘 질화막(5)을 형성하는 각각의 단계에서 금속 오염 물질이 부착되는 것, 또한 트렌치(7)의 저면에 금속 오염 물질이 부착되는 것의 각각의 가능성을 생각할 수 있다.

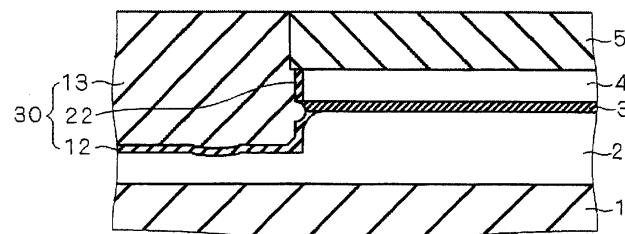

두번째로, 레지스트 수지(6)를 제거하고, 산화함으로써 트렌치(7)에 노출된 실리콘 산화막(8)을 형성한다. 이에 수반하여, 트렌치(7)의 측면에 노출된 부분에 대하여 다결정 실리콘(4)도 산화되어 실리콘 산화막(21)이 형성된다(도 18). 그 후, 트렌치(7)를 매립하고, 또한 실리콘 질화막(5)의 표면 상을 덮는 절연 재료, 예를 들면, 실리콘 산화막(13)이 퇴적된다. 전자와 후자에 퇴적된 실리콘 산화막(13)은 연속되어 있다(도 19).

세번째로, 제2 공정에서 형성한 실리콘 산화막(13)을 CMP에 의해 연마하여 평탄화함과 함께, 실리콘 질화막(5)의 표면 전체를 노출시킨다(도 20). 이 때, 트렌치(7)의 내부에 잔존하는 실리콘 산화막(8, 13, 21)이 분리 산화막(30)으로 된다. 그리고, 실리콘 질화막(5)과 다결정 실리콘(4)이 제거된다(도 21).

네번째로, 제3 공정까지 제작된 반도체 디바이스 전체를 600°C 이하에서 1시간 이상 어닐링한다. 이로써, 제1 공정에서 혼입한 금속 오염 물질은, 실리콘막(2)과 실리콘 산화막(8)의 계면에서 응집하여 금속 실리사이드(17a, 17b)로 된다. 금속 실리사이드(17a)는, 트렌치(7)의 형성시에 부착된 금속 오염 물질이 응집하고, 또한 금속 실리사이드(17b)는, 실리콘막(2)이나 실리콘 산화막(3)·다결정 실리콘(4)·실리콘 질화막(5)의 각각의 계면에 존재하는 금속 오염 물질이 확산·응집하여 실리콘막(2)과 실리콘 산화막(8)의 계면에 형성된다(도 22).

다섯번째로, 실리콘 산화막(3, 13, 21)의 표면 상에 다결정 실리콘(50)을 퇴적한다. 이하, 실시예1의 제8 공정과 마찬가지로 반도체 디바이스를 제작한다.

반도체 디바이스의 다른 부분에 비해 응력이 커지는 트렌치(7)에서 금속 오염 물질이 잔류하기 쉬워진다. 그리고, 그곳에서 응집한 금속 오염 물질은 금속 실리사이드(17a, 17b)로 된다. 따라서, 디바이스로서 기능하는 주요 부분(영역 R2)에는 금속 오염 물질이 거의 존재하지 않아, 반도체 디바이스가 갖는 성능 및 신뢰성이 저하를 방지할 수 있다.

상술한 반도체 디바이스의 제작에 있어서, 실리콘막(2)에 웰 영역을 형성할 필요가 있는 경우에는, 제3 공정과 제4 공정의 사이, 즉, 도 21에 도시되는 상태에서, 실리콘막(2)에 실리콘 산화막(3)측으로부터 불순물의 주입을 행하여 웰 영역을 형성해도 된다. 이 경우, 제4 공정에서 행하는 어닐링에 의해서 웰 영역에 주입된 불순물은 금속 오염 물질과 함께 확산되어, 웰 영역의 불순물 농도가 설정치로부터 어긋날 가능성이 있다. 이 때문에, 어닐링 후에 웰 영역의 불순물 농도를 재조정하는 것이 바람직하다.

실리콘막(2)에 웰 영역을 형성할 필요가 있는 경우에는, 제4 공정 후에 상기 실리콘막(2)에 웰 영역을 형성해도 된다. 이 경우, 웰 영역의 불순물 농도를 재조정할 필요가 없고, 따라서 공정이 단순화된다.

실시예1의 제7 공정(실시예2의 제4 공정 또는 실시예3의 제5 공정에서 채용되는 경우를 포함한다)에서, 실리콘 산화막(3)을 제거하기 전에 본 실시예의 제4 공정에서 설명한 어닐링 방법을 적용함으로써, 보다 효과적으로 반도체 디바이스가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

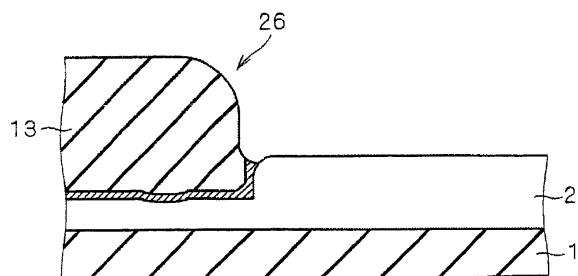

상술한 어느 실시예에서도, 트렌치(7)에 절연 재료(13)를 매립한 후에, 표면에 노출된 절연 재료(13)의 실리콘 산화막(2)측을 곡면 형상으로 해도 된다. 도 23에는, 예를 들면, 도 8에 대응시켜, 표면에 노출된 절연 재료(13)의 실리콘 산화막(2)측의 부분(26)이 곡면 형상을 갖는 경우가 도시되어 있다.

절연 재료(13)의 부분(26)이 곡면 형상을 갖는 경우에는, 절연 재료(13)의 부분(26)의 실리콘막(2)의 표면에 대한 경사가 완만해진다. 따라서, 게이트를 형성하는 프로세스가 용이해진다.

## 발명의 효과

본 발명에 관한 제1 혹은 제2 반도체 장치의 제조 방법에 따르면, 공정 (c)에 의해서 실리콘막과 절연막의 계면에 금속 오염 물질을 확산·응집시킬 수 있고, 절연막의 제거와 함께 그 금속 오염 물질을 제거할 수 있다. 따라서, 반도체 장치가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

본 발명에 관한 제3 반도체 장치의 제조 방법에 따르면, 공정 (c)에 의해서 실리콘막의 표면에 부착되는 금속 오염 물질을 제거할 수 있다. 따라서, 반도체 장치가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

본 발명에 관한 제4 반도체 장치의 제조 방법에 따르면, 공정 (e)에 의해서 실리콘막과 산화막의 계면에 금속 오염 물질을 확산·응집시킬 수 있다. 따라서, 반도체 장치가 갖는 성능 및 신뢰성의 저하를 방지할 수 있다.

### 도면의 간단한 설명

도 1은 반도체 장치를 도시하는 개념적인 평면도.

도 2는 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 3은 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 4는 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 5는 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 6은 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 7은 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 8은 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 9는 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 10은 실시예1에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 11은 실시예1에서 설명하는, 제조되는 반도체 장치를 도시하는 단면도.

도 12는 실시예2에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 13은 실시예2에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 14는 실시예2에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 15는 실시예3에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 16은 실시예3에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 17은 실시예3에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 18은 실시예4에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 19는 실시예4에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 20은 실시예4에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 21은 실시예4에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 22는 실시예4에서 설명하는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 23은 절연 재료 및 실리콘막이 곡면 형상을 갖는, 제조 단계에서의 반도체 장치를 도시하는 단면도.

도 24는 실시예1에서 설명하는, Fe의 온도와 확산 거리의 관계를 도시하는 도면.

도 25는 실시예1에서 설명하는, Ni의 온도와 확산 거리의 관계를 도시하는 도면.

도 26은 실시예1에서 설명하는, Co의 온도와 확산 거리의 관계를 도시하는 도면.

도 27은 실시예1에서 설명하는, Ti의 온도와 확산 거리의 관계를 도시하는 도면.

도 28은 실시예1에서 설명하는, Al의 온도와 확산 거리의 관계를 도시하는 도면.

도 29는 실시예1에서 설명하는, Cr의 온도와 확산 거리의 관계를 도시하는 도면.

<도면의 주요 부분에 대한 부호의 설명>

1 : 산화 실리콘 기판

2 : 실리콘막

3, 8, 12, 13, 15, 21, 22, 23 : 실리콘 산화막

4 : 다결정 실리콘

5 : 실리콘 질화막

7 : 트렌치

R1 : 영역

**도면**

도면1

도면2

1 : 산화 실리콘 기판

2 : 실리콘막

3 : 실리콘 산화막

4 : 다결정 실리콘

5 : 실리콘 질화막

R 1 : 영역

R 2 : 영역

도면3

7 : 트렌치

도면4

8 , 21 : 실리콘 산화막

도면5

도면6

12, 13, 22 : 실리콘 산화막

도면7

도면8

도면9

도면10

도면11

도면12

15, 23 : 실리콘 산화막

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

## 도면28

Al의 화산 거리

## 도면29

Cr의 화산 거리