(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7325552号**

**(P7325552)**

(45)発行日 令和5年8月14日(2023.8.14)

(24)登録日 令和5年8月3日(2023.8.3)

(51)国際特許分類

|         |                  |     |         |       |       |

|---------|------------------|-----|---------|-------|-------|

| H 1 0 B | 43/20 (2023.01)  | F I | H 1 0 B | 43/20 |       |

| H 0 1 L | 21/336 (2006.01) |     | H 0 1 L | 29/78 | 3 7 1 |

| H 0 1 L | 29/788 (2006.01) |     |         |       |       |

| H 0 1 L | 29/792 (2006.01) |     |         |       |       |

請求項の数 16 (全14頁)

|             |                             |

|-------------|-----------------------------|

| (21)出願番号    | 特願2021-576379(P2021-576379) |

| (86)(22)出願日 | 令和1年6月28日(2019.6.28)        |

| (65)公表番号    | 特表2022-538095(P2022-538095) |

|             | A)                          |

| (43)公表日     | 令和4年8月31日(2022.8.31)        |

| (86)国際出願番号  | PCT/CN2019/093678           |

| (87)国際公開番号  | WO2020/258246               |

| (87)国際公開日   | 令和2年12月30日(2020.12.30)      |

| 審査請求日       | 令和3年12月21日(2021.12.21)      |

|          |                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 519237948<br>長江存儲科技有限責任公司<br>Yangtze Memory Technologies Co., Ltd.<br>中華人民共和国湖北省武漢市東湖新技術<br>開發区未来三路88号<br>No. 88 Weilai 3rd Ro<br>ad, East Lake High-t<br>ech Development Zon<br>e, Wuhan, Hubei, Chin<br>a |

| (74)代理人  | 100108453<br>弁理士 村山 靖彦                                                                                                                                                                                      |

| (74)代理人  | 100110364<br>弁理士 実広 信哉                                                                                                                                                                                      |

最終頁に続く

(54)【発明の名称】 高記憶密度化3次元フラッシュメモリデバイス

**(57)【特許請求の範囲】****【請求項1】**

基板と、

前記基板上方に配置された、垂直方向に沿って延在する半導体材料の円柱と、

前記円柱の周りを覆っているワード線スタックと、

前記ワード線スタックと前記円柱との間に配置された電荷蓄積要素と、を含み、前記円柱、前記電荷蓄積要素、および前記ワード線スタックは、少なくとも2つのメモリセルを構成する、3次元フラッシュメモリデバイスであって、

前記少なくとも2つのメモリセルのうちの2つは、前記垂直方向に沿って延在する共通のローカルソース線を含み、

前記少なくとも2つのメモリセルのうちの2つは、前記垂直方向に沿って延在し、前記少なくとも2つのメモリセルのうちの2つを分離する、チャネルブレーカを含み、

前記円柱は、前記垂直方向に沿って延在する、少なくとも2つのローカルビット線および前記共通のローカルソース線を備え、

前記3次元フラッシュメモリデバイスは、

前記少なくとも2つのローカルビット線のうちの第1のローカルビット線と、前記共通のローカルソース線との間の第1のチャネル領域と、

前記少なくとも2つのローカルビット線のうちの第2のローカルビット線と、前記共通のローカルソース線との間の第2のチャネル領域と、を含み、

前記チャネルブレーカは、前記第1のチャネル領域を前記第2のチャネル領域から分離す

る、

3次元フラッシュメモリデバイス。

【請求項2】

前記チャネルブレーカは、絶縁層を含む、請求項1に記載の3次元フラッシュメモリデバイス。

【請求項3】

前記チャネルブレーカは、前記少なくとも2つのローカルビット線を分離することによつて前記少なくとも2つのメモリセルを分離する、請求項1に記載の3次元フラッシュメモリデバイス。

【請求項4】

ワード線を含む前記ワード線スタックが、前記垂直方向と直角をなす第2の方向に沿つて延在する、請求項3に記載の3次元フラッシュメモリデバイス。

【請求項5】

前記少なくとも2つのメモリセルのうちの2つは、前記ワード線および前記少なくとも2つのローカルビット線によって制御されるように構成される、請求項4に記載の3次元フラッシュメモリデバイス。

【請求項6】

前記少なくとも2つのローカルビット線が、2つのグローバルビット線にそれぞれ電気的に結合されている、請求項4に記載の3次元フラッシュメモリデバイス。

【請求項7】

前記2つのグローバルビット線が、前記第2の方向および前記垂直方向と直角をなす第3の方向に沿つて延在する、請求項6に記載の3次元フラッシュメモリデバイス。

【請求項8】

前記2つのグローバルビット線が、選択トランジスタに電気的に結合されており、前記選択トランジスタが、前記2つのグローバルビット線を前記少なくとも2つのローカルビット線に接続する、請求項6に記載の3次元フラッシュメモリデバイス。

【請求項9】

基板と、

前記基板上方に配置された半導体材料の複数の円柱であつて、前記複数の円柱の各々が、垂直方向に沿つて延在する、複数の円柱と、

前記複数の円柱の周りを覆っているワード線スタックと、

前記ワード線スタックと前記複数の円柱の各々との間に配置された電荷蓄積要素と、を含み、前記複数の円柱の各々、前記電荷蓄積要素、および前記ワード線スタックは、複数のメモリセルを構成し、

前記複数のメモリセルは、前記垂直方向に沿つて延在する少なくとも1つの共通のローカルソース線を含み、

前記複数の円柱の各々は、前記垂直方向に沿つて延在する、複数のローカルビット線および複数のローカルソース線を備え、複数のチャネル領域が、前記複数のローカルビット線と複数のローカルソース線との間に配置されており、

前記複数のチャネル領域のうちの2つの間を分離するチャネルブレーカをさらに備える、

3次元フラッシュメモリデバイス。

【請求項10】

前記複数のメモリセルのうちの各々2つは、前記垂直方向に沿つて延在する、少なくとも2つのローカルビット線および前記少なくとも1つの共通のローカルソース線を備える、請求項9に記載の3次元フラッシュメモリデバイス。

【請求項11】

ワード線を含む前記ワード線スタックが、前記垂直方向と直角をなす第2の方向に沿つて延在する、請求項10に記載の3次元フラッシュメモリデバイス。

【請求項12】

前記複数のメモリセルのうちの各々2つは、ワード線および前記少なくとも2つのロ-

10

20

30

40

50

カルピット線によって制御されるように構成される、請求項1\_1に記載の3次元フラッシュメモリデバイス。

**【請求項13】**

前記複数のローカルピット線が、複数のグローバルピット線にそれぞれ電気的に結合されている、請求項1\_1に記載の3次元フラッシュメモリデバイス。

**【請求項14】**

前記複数のグローバルピット線が、前記第2の方向および前記垂直方向と直角をなす第3の方向に沿って延在する、請求項1\_3に記載の3次元フラッシュメモリデバイス。

**【請求項15】**

前記複数のグローバルピット線の各々が、選択トランジスタに電気的に結合されており、前記選択トランジスタが、前記複数のグローバルピット線を前記複数のローカルピット線に接続する、請求項1\_3に記載の3次元フラッシュメモリデバイス。

10

**【請求項16】**

前記チャネルブレーカが、前記複数のローカルピット線のうちの2つの間に配置される、請求項9に記載の3次元フラッシュメモリデバイス。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、メモリデバイスに関し、より詳細には、高記憶密度化3次元(3D)NORフラッシュメモリデバイスに関する。

20

**【背景技術】**

**【0002】**

フラッシュメモリデバイスは、記憶されたデータが電気的に消去または書き込み可能な(すなわち、プログラミング可能な)不揮発性メモリデバイスである。実際に、フラッシュメモリデバイスは、単一の処理で消去でき、電気的にプログラミング可能であるので、コンピュータおよびメモリカードに広く使用されている。

**【0003】**

読み出し動作用のロジックゲートに基づくフラッシュメモリには2つの主要な種類、NANDタイプおよびNORタイプがある。NORフラッシュメモリに関して、あらゆる個々のメモリセルが別々に読み出されまたは変更され得、それにより完全なランダムアクセスを提供し、そのため、揮発性SRAMまたはDRAMを置換する、不揮発性を有する実行可能なコード記憶装置として使用され得る。

30

**【0004】**

当技術分野で知られているように、NORメモリストリングまたはNORストリングは、多くの記憶トランジスタを含み、その各々が共有ソース領域および共有ドレイン領域に接続されている。そのため、NORストリングのトランジスタは、並列に接続されている。NORストリング内の記憶トランジスタを読み出すまたはプログラミングするために、その記憶トランジスタのみが、アクティブ化される(すなわち、「オン」または導通)必要があり、NORストリング内の他のすべての記憶トランジスタは、休止状態(すなわち、「オフ」または非導通)のままである。したがって、NORストリングは、読み出されるアクティブ化された記憶トランジスタの非常に速い検知を可能にする。

40

**【0005】**

従来のNORトランジスタは、電子がソース領域とドレイン領域との間の電圧差によってチャネル領域で加速され、適切な電圧が制御ゲートに印加されているときに制御ゲートとチャネル領域との間の電荷捕捉層内に注入される、チャネルホットエレクトロン(CHE)注入法によってプログラミングされる。

**【0006】**

フラッシュメモリチップの連続する世代とともに、製造コストを最小化する一方で、アレイ密度を増大させチップ面積を最大化することに、重点が置かれ続けている。目下の工程フローの最小限の変更または変更せずに、フラッシュメモリデバイスの記憶密度を増

50

大させることが、さらに所望されている。

【発明の概要】

【発明が解決しようとする課題】

【0007】

改善された高記憶密度化3次元(3D)NORフラッシュメモリデバイスを提供することが、本開示の一目的である。

【課題を解決するための手段】

【0008】

本開示の一態様によれば、3次元フラッシュメモリデバイスは、十分な平坦面を有する基板を含む。半導体材料の複数の活性円柱が、基板上に配置されている。複数の活性円柱の各々は、基板の平坦面に直交する第1の方向に沿って延在する。複数の活性円柱は、2次元のアレイに配設されている。複数の活性円柱の各々は、第1の方向に沿って延在する、少なくとも2つのローカルビット線および少なくとも1つのローカルソース線を備える。第1のチャネル領域が、少なくとも2つのローカルビット線のうちの第1のローカルビット線と、少なくとも1つのローカルソース線との間に配置されている。第2のチャネル領域が、少なくとも2つのローカルビット線のうちの第2のローカルビット線と、少なくとも1つのローカルソース線との間に配置されている。ワード線スタックが、複数の活性円柱の周りを覆っている。電荷蓄積要素が、ワード線スタックと複数の活性円柱の各々との間に配置されている。

10

【0009】

いくつかの実施形態によれば、ワード線スタックは、基板の平坦面に平行な第2の方向に沿って延在する。

20

【0010】

いくつかの実施形態によれば、少なくとも2つのローカルビット線が、2つのグローバルビット線にそれぞれ電気的に結合されている。

【0011】

いくつかの実施形態によれば、2つのグローバルビット線は、第2の方向に平行でなく、基板の平坦面に平行な第3の方向に沿って延在する。

【0012】

いくつかの実施形態によれば、2つのグローバルビット線の各々は、ビットラインアクセス選択トランジスタに電気的に結合されており、ビットラインアクセス選択トランジスタは、2つのグローバルビット線の各々を少なくとも2つのローカルビット線の各々に接続する。

30

【0013】

いくつかの実施形態によれば、電荷蓄積要素は、電荷捕捉層を含む。

【0014】

いくつかの実施形態によれば、電荷捕捉層は、窒化シリコンを含む。

【0015】

いくつかの実施形態によれば、3次元フラッシュメモリデバイスは、第1のチャネル領域を第2のチャネル領域から分離する、チャネルブレーカをさらに備える。

40

【0016】

いくつかの実施形態によれば、複数の活性円柱は、互い違いに配設されている。

【0017】

いくつかの実施形態によれば、基板は、シリコン基板を含む。

【0018】

本開示の別の態様によれば、3次元フラッシュメモリデバイスは、十分な平坦面を有する基板を含む。半導体材料の複数の活性円柱が、基板上に配置される。複数の活性円柱の各々は、基板の平坦面に直交する第1の方向に沿って延在する。複数の活性円柱は、2次元のアレイに配設されている。複数の活性円柱の各々は、第1の方向に沿って延在する、複数のローカルビット線および複数のローカルソース線を備える。複数のチャネル領域が

50

、複数のローカルビット線と複数のローカルソース線との間に配置されている。ワード線スタックが、複数の活性円柱の周りを覆っている。電荷蓄積要素が、ワード線スタックと複数の活性円柱の各々との間に配置されている。

**【0019】**

いくつかの実施形態によれば、ワード線スタックは、基板の平坦面に平行な第2の方向に沿って延在する。

**【0020】**

いくつかの実施形態によれば、複数のローカルビット線は、複数のグローバルビット線にそれぞれ電気的に結合されている。

**【0021】**

いくつかの実施形態によれば、複数のグローバルビット線は、第2の方向に平行でなく、基板の平坦面に平行な第3の方向に沿って延在する。

**【0022】**

いくつかの実施形態によれば、複数のグローバルビット線の各々は、ビットラインアクセス選択トランジスタに電気的に結合されており、ビットラインアクセス選択トランジスタは、複数のグローバルビット線の各々を複数のローカルビット線の各々に接続する。

**【0023】**

いくつかの実施形態によれば、電荷蓄積要素は、電荷捕捉層を含む。

**【0024】**

いくつかの実施形態によれば、電荷捕捉層は、窒化シリコンを含む。

**【0025】**

いくつかの実施形態によれば、3次元フラッシュメモリデバイスは、複数のローカルビット線のうちの2つの間のチャネルブレーカをさらに備える。

**【0026】**

いくつかの実施形態によれば、複数の活性円柱は、互い違いに配設されている。

**【0027】**

いくつかの実施形態によれば、基板は、シリコン基板を含む。

**【0028】**

本発明のこれらの目的および他の目的は、以下の、多様な図形および図画で図示されている好ましい実施形態の詳細な説明を読むことで、当業者にはおそらく明白になるであろう。

**【0029】**

本明細書に組み込まれ、明細書の一部を形成する添付図面は、本開示の実施形態を図解し、記述と共に、本開示の原理を説明し、当業者が本開示を製造し、使用することを可能にすることに、さらに助力する。

**【図面の簡単な説明】**

**【0030】**

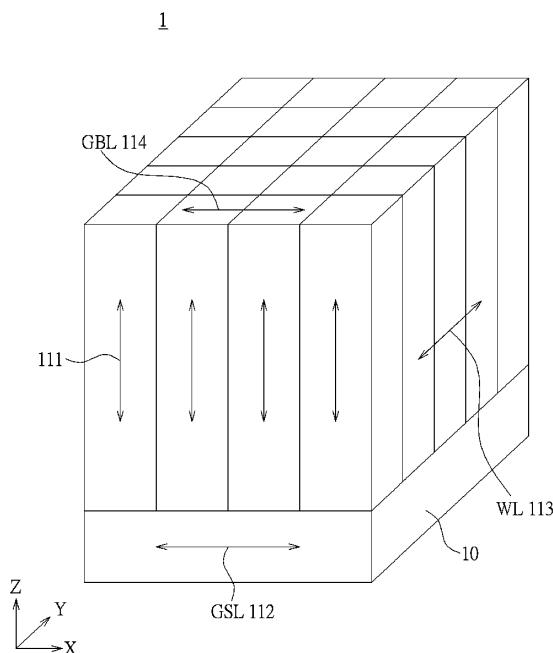

**【図1】**本発明のある実施形態による、概念化されたメモリ構造の図であり、垂直NORストリング内に設けられたメモリセルの3次元構成を図解している。各垂直NORストリングは、いくつかの水平ワード線のうちの1つによって各々が制御されるメモリセルを有する。

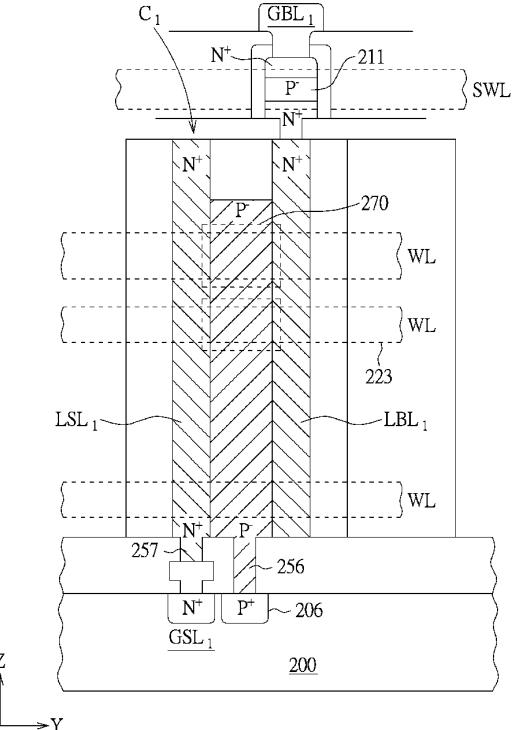

**【図2】**本発明のある実施形態による、活性円柱の垂直NORストリングの、グローバルビット線、グローバルソース線、および共通柱身バイアスソースへの接続を示す、Z-Y平面の断面図である。

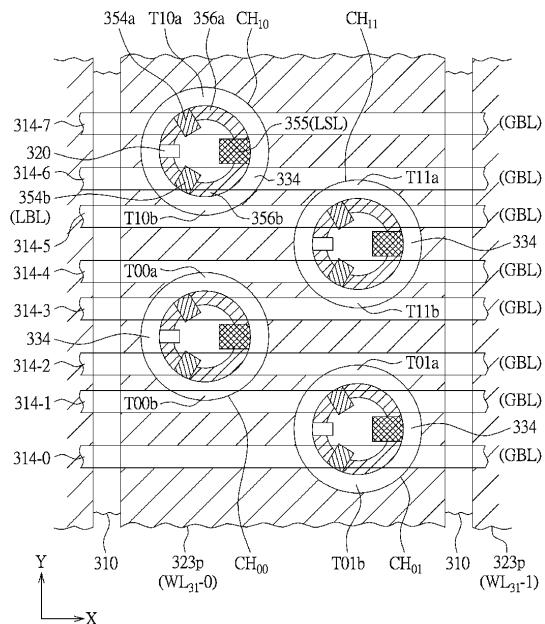

**【図3】**本発明の実施形態による、ワード線スタックを共有する垂直NORストリングの互い違いの近接実装を示す、X-Y平面の断面図である。

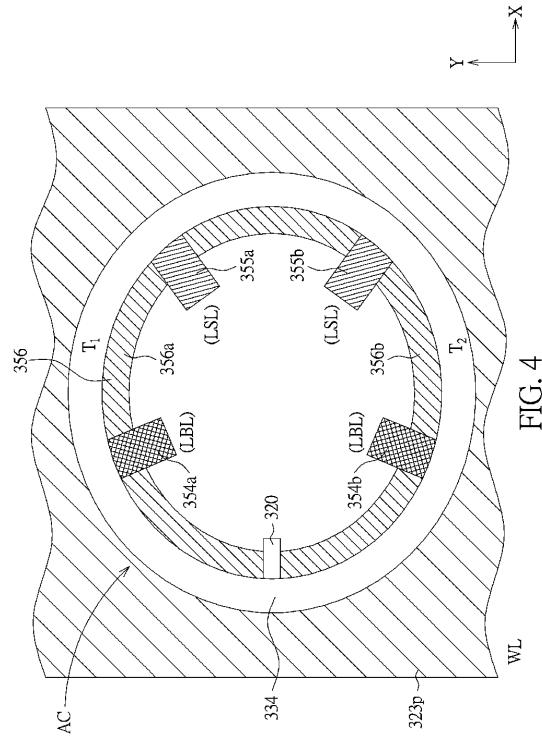

**【図4】**本発明の別の実施形態による、1つの活性円柱の複数のローカルビット線および複数のローカルソース線を示す、X-Y平面の概略断面図である。

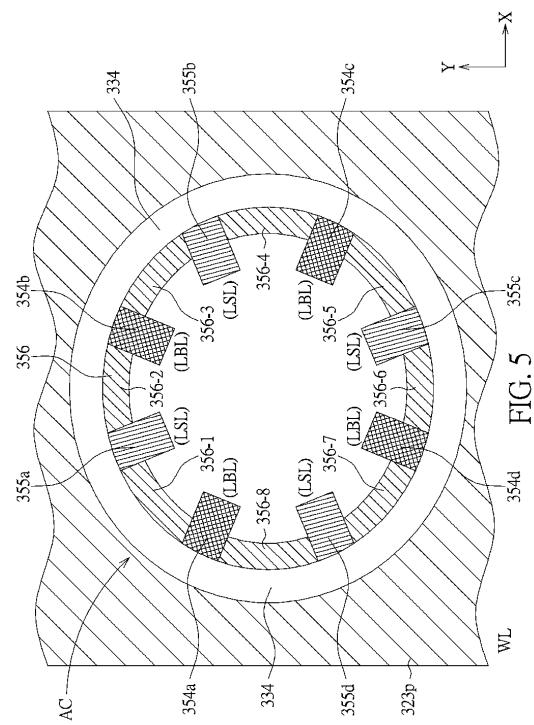

**【図5】**本発明のやはり別の実施形態による、1つの活性円柱の複数のローカルビット線および複数のローカルソース線を示す、X-Y平面の概略断面図である。

10

20

30

40

50

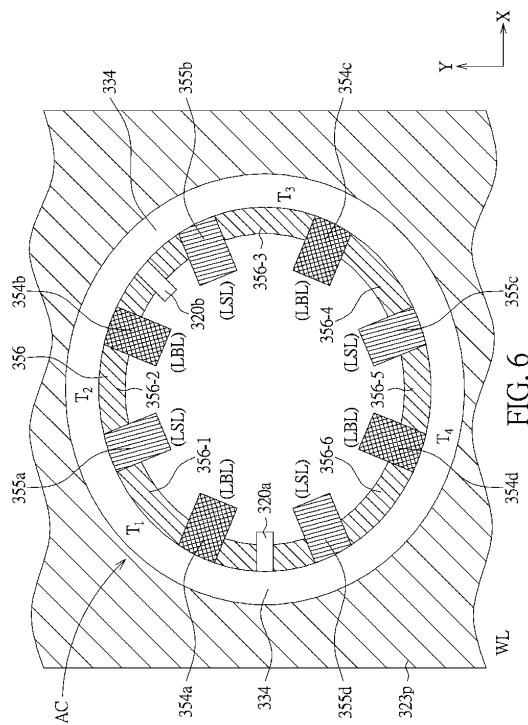

【図6】本発明のさらに別の実施形態による、1つの活性円柱の複数のローカルピット線および複数のローカルソース線を示す、X-Y平面の概略断面図である。

【発明を実施するための形態】

【0031】

本開示の実施形態が、添付図面を参照して説明されることになる。

【0032】

ここで、本開示を理解し、実施し、技術的效果を実感するために、添付図面において図示されている、本発明の例示的な実施形態への参照が、詳細になされることになる。以下の説明が、一例としてのみなされ、しかしながら本開示を限定するためになされていないことが、理解されよう。本開示の多様な実施形態および実施形態内の互いに矛盾しない多様な特徴は、多様な方法で組み合わせられ、再編成され得る。本開示の主旨および範囲から逸脱することなく、本開示への変形例、同等物、または改善は、当業者に理解可能であり、本開示の範囲内に包括的に含まれることが意図されている。

10

【0033】

明細書内での「ある実施形態」、「実施形態」、「例示的な実施形態」、「いくつかの実施形態」などへの参照は、記述された実施形態が特定の機能、構造、または特徴を含み得るが、あらゆる実施形態が必ずしも特定の形体、構造、または特徴を含まなくてよい、ことを示すことに留意されたい。また、そのような語句は、必ずしも同一の実施形態を参照しない。

20

【0034】

さらに、特定の形体、構造、または特徴が、ある実施形態と連絡して記述されている場合、それが他の実施形態と連絡するそのような特定の形体、構造、または特徴に影響を及ぼすことは、明示的に記述されているか否かにかかわらず、当業者には自明のことであろう。

【0035】

一般に、専門用語は、文脈内での使用法から少なくとも部分的に理解され得る。たとえば、本明細書で使用されているような「1つまたは複数の」という用語は、文脈に少なくとも部分的に依存して、任意の形体、構造、または特徴を单一の意味で記述するために使用され得る、あるいは形体、構造、または特徴の組み合わせを複数の意味で使用され得る。同様に、「a」、「an」、または「the」などの用語は、やはり文脈に少なくとも部分的に依存して、単一の語法を伝える、あるいは複数の語法を伝えると理解され得る。

30

【0036】

本開示内の「の上に(on)」、「より上に(above)」、「の上方に(over)」の意味は、最も広範に解釈されるべきであり、「の上に(on)」は、何か「の直接上に(on)」の意味だけでなく、それらの間に中間の形体または層を有して何か「の上に(on)」の意味も含み、「より上に(above)」、「の上方に(over)」は、何か「より上に(above)」、「の上方に(over)」を意味するだけでなく、それらの間に中間の形体または層を有さないで何か「より上に(above)」、「の上方に(over)」の意味(すなわち、何かの直接上)も含み得ることが容易に理解されるであろう。

40

【0037】

また、「の下に(beneath)」、「より下に(below)」、「下のほうの(lower)」、「より上に(above)」、「上のほうの(upper)」などの空間的に相対的な用語が、ある構成要素、もしくは形体の別の構成要素との関係、または図中で説明されているような形体の記述を記述しやすくするために、本明細書では使用されている場合がある。空間的に相対的な用語は、図中で表現されている向きに加えて、使用または動作中のデバイスの異なる向きを、包括的に含むことが意図されている。装置は、別の方向に向けられ(90度回転されまたは他の向きで)、本明細書で使用されている空間的に相対的な記述語が、それに応じて同様に解釈され得る。「垂直の」という用語は、半導体基板の表面に垂直な方向を指し、「水平の」という用語は、その半導体基板の表面

50

に平行な任意の方向を指す。

**【 0 0 3 8 】**

図1は、概念化されたメモリ構造1を示し、垂直NORストリング内に設けられたメモリセル（または記憶素子）の3次元構成を図解している。概念化されたメモリ構造1では、各垂直NORストリングは、本発明のある実施形態による、対応する水平ワード線によって各々が制御されるメモリセルを含む。概念化されたメモリ構造1では、各メモリセルは、「垂直に」配設されている、すなわち、基板10の表面に垂直な方向に沿って、堆積された薄膜内に形成されている。基板10は、たとえば、それらに限定されないが、集積回路製造に使用される、従来のシリコンウェハまたはシリコン基板であり得る。図1に示されているように、デカルト座標系が、単に説明を容易にするために採用されている。この座標系では、基板10表面は、X-Y平面に平行な平面としてみなされる。そのため、本明細書で使用されるように、「水平の」という用語は、X-Y平面に平行な任意の方向を指し、一方、「垂直の」は、Z方向を指す。

**【 0 0 3 9 】**

図1では、Z方向にある各々の垂直柱が、垂直NORストリング（たとえば、垂直NORストリング111）内の記憶素子またはTFTに相当する。垂直NORストリングは、X方向に沿って各々延在する列では、規則的に配設されている。同様の配置が、代わりに、Y方向に沿って各々延在する列の配置として見られ得る。垂直NORストリングの記憶素子は、垂直ローカルビット線を備え得、垂直ローカルソース線を共有し得る（図示せず）。水平ワード線（たとえば、WL113）のスタックがY方向に沿って通っており、各ワード線は、Y方向に沿ったワード線に隣接して配置された垂直NORストリングの対応するTFT用の制御ゲートとして機能する。グローバルソース線（たとえば、GSL112）およびグローバルビット線（GBL114）は、通常、概念化されたメモリ構造1の底部下方または上部上方のどちらかを通るX方向に沿って配設され得る。代わりに、信号ラインGSL112およびGBL114は、両方、概念化されたメモリ構造1の下方に、または上方に経路が定められ得、それらの各々は、アクセストランジスタ（図1に図示せず）によって個々の垂直NORストリングのローカルソース線およびローカルビット線に選択的に接続され得る。

**【 0 0 4 0 】**

図解目的だけのために、概念化されたメモリ構造1は、垂直NORストリングの4×5配列から構成されるマルチゲート垂直NORストリングアレイであり、各NORストリングは、通常、32以上の記憶素子およびアクセス選択トランジスタを有する。図1内で、いくつかの記憶素子を有する各垂直NORストリングを備える、垂直NORストリングの4×5配列として示されているが、本発明のメモリ構造は、XおよびY方向のいずれかに沿った各列内に任意の数の垂直NORストリングを、および各垂直NORストリング内に任意の数の記憶素子を、有し得る。たとえば、XおよびY方向の両方に沿った列内に配列された、たとえば2、4、8、16、32、64、128またはより多くの記憶素子を有するNORストリングを各々備える、数千の垂直NORストリングが、存在し得る。

**【 0 0 4 1 】**

図1の各垂直NORストリング（たとえば、垂直NORストリング）内の記憶素子の数は、垂直NORストリングに制御ゲートを提供するワード線（たとえば、WL113）の数に相当する。ワード線は、Y方向に沿って各々延在する、細く長い金属帯状体として形成されていてもよい。ワード線は、互いにスタックされており、それらの間の誘電体絶縁層によって互いから電気的に絶縁されている。各スタック内のワード線の数は、任意の数であり得るが、2の整数倍（すなわち、 $2^n$ 、ここでnは整数）であることが好ましい。

**【 0 0 4 2 】**

図2は、本発明のある実施形態による、活性円柱C1の垂直NORストリングの、グローバルビット線GBL1、グローバルソース線GSL1、および共通柱身バイアスソース206への接続を示す、Z-Y平面の断面図である。図2に示されているように、ビットライナーアクセス選択トランジスタ211は、グローバルビット線GBL1とローカルビッ

ト線 LBL<sub>1</sub>を接続し、コンタクト 256 は、任意選択で、活性帯状体上の P - 柱身（または無ドープの柱身）領域を基板 200 内の柱身バイアスソース 206 に接続する。ビットライナーアクセス選択トランジスタ 211 が活性円柱 C<sub>1</sub> の上方に形成されている。しかしながら、代わりに、ビットライナーアクセス選択トランジスタ 211 は、活性円柱 C<sub>1</sub> の底部で、または他の実施形態の基板 200 内で形成され得る。

#### 【0043】

たとえば、ビットライナーアクセス選択トランジスタ 211 は、N<sup>+</sup> / P<sup>-</sup> / N<sup>+</sup> ドープされた多結晶シリコンスタックの絶縁された島内に、アクセス選択ワード線 SWL と共に、形成され得る。十分に高い電圧が選択ワード線 SWL に印加された場合、P - チャネルが反転されて、それによりローカルビット線 LBL<sub>1</sub> をグローバルビット線 GBL<sub>1</sub> に接続する。アクセス選択ワード線 SWL は、垂直 NOR ストリングの TFT270 への制御ゲートとして機能する、ワード線 223 と異なる方向（すなわち、Y 方向）に沿って通り得る。アクセス選択ワード線 SWL は、ワード線 223 から別に形成され得る。ある実施形態では、グローバルビット線 GBL<sub>1</sub> は、水平に X 方向（すなわち、ワード線の方向と垂直に）に沿って通り、ビットライナーアクセス選択トランジスタ 211 は、グローバルビット線 GBL<sub>1</sub> によってサービングされる多くの垂直 NOR ストリングのうちの単に 1 つのローカルビット線である、ローカルビット線 LBL<sub>1</sub> へのアクセスを提供する。読み出しおよびプログラム動作の効率を向上させるために、マルチゲート NOR ストリングアレイでは、数千のグローバルビット線は、アクセス選択ワード線 SWL によってアクセスされる、数千の垂直 NOR ストリングのローカルビット線に、並列にアクセスするために使用され得る。図 2 では、ローカルソース線 LSL<sub>1</sub> が、コンタクト 257 を介してグローバルソース線 GSL<sub>1</sub> に接続され得る。図 2 の活性円柱 C<sub>1</sub> の垂直 NOR ストリングは、図解目的だけのためのものであることが分かる。いくつかの他の実施形態では、ビットライナーアクセス選択トランジスタ 211 は、省略され得ることが理解されよう。

#### 【0044】

グローバルソース線 GSL<sub>1</sub> は、基板 200 内のデコーディング回路によってデコードされ得る。支援回路は、とりわけ、アドレスエンコーダ、アドレスデコーダ、センス増幅器、入力 / 出力ドライバ、シフトレジスタ、ラッチ、基準セル、電力供給ライン、バイアスおよび基準電圧発生器、インバータ、NAND、NOR、排他的論理和および他のロジックゲート、他の記憶素子、シーケンサ、ならびに状態機械を備え得る。マルチゲート NOR ストリングアレイは、回路の複数のブロックとして組織され得、各ブロックは、複数のマルチゲート NOR ストリングアレイを有する。

#### 【0045】

図 3 は、本発明の実施形態による、ワード線スタックリーを共有する垂直 NOR ストリングの互い違いの近接実装を示す、X - Y 平面の断面図である。本発明のある実施形態によれば、図 3 で示されているように、複数の垂直 NOR ストリングまたは周りを覆うワード線を備える活性円柱が、図示されている。垂直 NOR ストリングまたは活性円柱は、共により近接するように互い違いにされ、その結果、ワード線スタックリー 323 p (WL31 - 0) は、より多くの垂直 NOR ストリングによって共有され得る。

#### 【0046】

図 3 では、半導体材料の複数の活性円柱（チャネルホール CH<sub>00</sub>、CH<sub>01</sub>、CH<sub>10</sub>、CH<sub>11</sub> によって表される）が、基板（図 3 に図示せず）上方に配置されており、複数の活性円柱の各々は、基板の平坦面に直交する方向に沿って延在する。活性円柱は、2 次元のアレイに互い違いに配設されている。垂直 NOR ストリングは、チャネルホール CH<sub>00</sub>、CH<sub>01</sub>、CH<sub>10</sub>、CH<sub>11</sub>、それぞれの内側に形成されている。チャネルホール CH<sub>00</sub>、CH<sub>01</sub>、CH<sub>10</sub>、CH<sub>11</sub> は、ワード線間の金属ワード線のスタックリーと誘電体絶縁層をエッティングで貫通することによって形成される。製造工程フローは、従来技術の垂直 NAND ストリングのものと同様であるが、垂直 NAND ウイング内のトランジスタが直列に配設されているのに対して、垂直 NOR ストリング内のトランジスタが互いに平行に配設されていることを除く。4 つの例示のチャネルホール CH<sub>00</sub>、CH<sub>01</sub>、CH<sub>10</sub>

10

20

30

40

50

10、C H<sub>11</sub>の各々の内部で、垂直N O Rストリングのトランジスタ形成は、垂直N O Rストリングに沿ったすべてのT F Tの1つの共有ローカルソース線(L S L)355ならびに2つのローカルビット線(L B L)354aおよび354bを備える、チャネルホールの深さ全体に延在するN<sup>+</sup>ドープ垂直柱によって支援される。

#### 【0047】

本発明のある実施形態によれば、4つの例示のチャネルホールC H<sub>00</sub>、C H<sub>01</sub>、C H<sub>10</sub>、C H<sub>11</sub>の各々において、無ドープのまたは低濃度ドープのチャネル領域356aおよび356bは、ローカルビット線(L B L)354aおよび354bにそれぞれ隣接して配置されている。チャネル領域356aおよび356bは、絶縁層などのチャネルブレーカ320によって、互いから分離されている。電荷捕捉層を含む電荷蓄積素子334は、チャネル領域356aおよび356bとワード線スタック323pとの間に位置しており、そのため、垂直活性帯状体に沿った2、4、8、16、32、64、128またはより多くのT F Tのスタックを形成する。本発明のある実施形態によれば、電荷蓄積素子334の電荷捕捉層は、それに限定されないが、窒化シリコンを含み得る。電荷トラッピング層は、たとえば、トンネル誘電体(例えば、シリコン二酸化物)の薄膜と、その後に続く窒化シリコンまたは非導電性誘電体材料に埋め込まれた導電性ナノドットなどの電荷トラッピング材料の薄層と、または絶縁フローディングゲート、から構成されるトランジスタゲート誘電体材料であり得、ONO(酸化物-窒化物-酸化物)などの阻止誘電体層またはアルミニウム酸化物もしくはハフニウム酸化物などの高誘電率膜、あるいはそのような誘電体のいくつかの組み合わせによって覆われている。電荷は、チャネルホットエレクトロン注入プログラミング手法を使用して、電荷捕捉層内に蓄積される。

#### 【0048】

図3の実施形態では、ワード線スタックは、エアギャップまたは絶縁分離310によって互いから分離されている個々の水平帯状体323p(W L 31-0)、323p(W L 31-1)と共に、Y方向に通っている。8つの例示のグローバルビット線(G B L)314-0~314-7は、ワード線と垂直に、X方向に沿った列で水平に通っている。8つの例示のグローバルビット線(G B L)314-0~314-7の各々は、垂直帯状体の列に沿ったローカルビット線(L B L)に、メモリアレイ上方に位置し得るアクセス選択トランジスタ(図2の211、図3で図示せず)を介してアクセスする。同様に、各グローバルソース線(図3で図示せず)は、列にそったローカルソース線柱にアクセスする。たとえば、グローバルソース線は、メモリアレイの下方に配置され得る。

#### 【0049】

図3では、2つのT F T(または2つのメモリセル)が4つの例示のチャネルホールC H<sub>00</sub>、C H<sub>01</sub>、C H<sub>10</sub>、C H<sub>11</sub>の各々に配置されている。たとえば、2つのメモリセルT<sub>10a</sub>およびT<sub>10b</sub>は、チャネルホールC H<sub>10</sub>内に配置され、2つのメモリセルT<sub>00a</sub>およびT<sub>00b</sub>は、チャネルホールC H<sub>00</sub>内に配置され、2つのメモリセルT<sub>11a</sub>およびT<sub>11b</sub>は、チャネルホールC H<sub>11</sub>内に配置され、2つのメモリセルT<sub>01a</sub>およびT<sub>01b</sub>は、チャネルホールC H<sub>01</sub>内に配置されている。図3に示されている、各垂直N O Rストリングは、2つのチャネル領域356aおよび356b、2つのローカルビット線(L B L)354aおよび354b、ならびに1つの共有ローカルソース線(L S L)355を有する。たとえば、チャネル領域356a、ローカルビット線354a、共有ローカルソース線355、電荷蓄積要素334、およびワード線323pが、チャネルホールC H<sub>10</sub>内のメモリセルT<sub>10a</sub>を構成する。たとえば、チャネル領域356b、ローカルビット線354b、共有ローカルソース線355、電荷蓄積要素334、およびワード線323pが、チャネルホールC H<sub>10</sub>内のメモリセルT<sub>10b</sub>を構成する。したがって、開示されているメモリ構造は、垂直N O Rストリングの記憶密度を2倍にする。

#### 【0050】

図4は、本発明の別の実施形態による、1つの活性円柱の複数のローカルビット線および複数のローカルソース線を示す、X-Y平面の概略断面図であり、同様の数字が、同様の要素、領域、または層を指定している。図4で示しているように、活性円柱A Cが、ワード線323pによって支持される。

10

20

30

40

50

ード線WLによって、周りを覆われている。活性円柱ACは、基板(図4で図示せず)の平坦面に直交するZ方向に沿って延在する垂直NORストリングを備える。図3に示されているように、基板上で2次元アレイ内に互い違いに配置された複数の活性円柱が存在し得る。

#### 【0051】

活性円柱AC内の垂直NORストリングの1つの特定の平面のみが、図4に示されていることが分かる。環状シリコンチャネル356が、示されている。電荷捕捉層を含む電荷蓄積要素334が、シリコンチャネル356とワード線WLとの間に位置している。シリコンチャネル356および活性円柱ACの形状は、図解目的のためだけのものであることが理解されよう。卵形の形状、長方形の形状、または不規則な形状などの他の形状が、本発明の多様な実施形態に従って、適用可能であり得る。信号ラインLBLおよびLSLならびにチャネルブレーカの位置の形状は、図解目的のためだけのものであることが理解されよう。信号ラインLBLおよびLSLならびにチャネルブレーカの位置は、処理/製造要件に従って、調整され得る。

10

#### 【0052】

別の実施形態によれば、活性円柱ACは、2つのローカルビット線354aおよび354b、ならびに2つのローカルソース線355aおよび355bを含み得る。チャネル領域356aは、ローカルビット線354aとローカルソース線355aとの間に位置する。チャネル領域356bは、ローカルビット線354bとローカルソース線355bとの間に位置する。同様に、絶縁層などのチャネルブレーカ320は、チャネル領域356aをチャネル領域356bから分離するように、2つのローカルビット線354aと354bとの間に位置する。いくつかの実施形態では、チャネルブレーカ320が省略され得ることが分かる。たとえば、チャネル領域356a、ローカルビット線354a、ローカルソース線355a、電荷蓄積要素334、およびワード線323pが、メモリセルT<sub>1</sub>を構成する。たとえば、チャネル領域356b、ローカルビット線354b、ローカルソース線355b、電荷蓄積要素334、およびワード線323pが、メモリセルT<sub>2</sub>を構成する。

20

#### 【0053】

各活性円柱内の信号ラインLBLおよびLSLの数は、設計要件に依存し得る。いくつかの実施形態では、3つ以上の信号ラインLBLおよび3つ以上の信号ラインLSSLが、フラッシュメモリデバイスの記憶密度をさらに増大させるために、存在し得る。図5は、本発明のやはり別の実施形態による、1つの活性円柱の複数のローカルビット線および複数のローカルソース線を示す、X-Y平面の概略断面図であり、同様の数字が、同様の要素、領域、または層を指定している。図5で示しているように、同様に、活性円柱ACが、ワード線WLによって、周りを覆われている。活性円柱ACは、基板(図5で図示せず)の平坦面に直交するZ方向に沿って延在する垂直NORストリングを備える。

30

#### 【0054】

活性円柱AC内の垂直NORストリングの1つの特定の平面のみが、図5に示されていることが分かる。環状シリコンチャネル356が、示されている。電荷捕捉層を含む電荷蓄積要素334が、シリコンチャネル356とワード線WLとの間に位置している。シリコンチャネル356および活性円柱ACの形状は、図解目的のためだけのものであることが理解されよう。卵形の形状、長方形の形状、または不規則な形状などの他の形状が、本発明の多様な実施形態に従って、適用可能であり得る。信号ラインLBLおよびLSSLの位置の形状は、図解目的のためだけのものであることが理解されよう。信号ラインLBLおよびLSSLの位置は、処理/製造要件に従って、調整され得る。

40

#### 【0055】

別の実施形態によれば、活性円柱ACは、4つのローカルビット線354a～354d、ならびに4つのローカルソース線355a～355dを含み得る。シリコンチャネル356は、4つのローカルビット線354a～354d、ならびに4つのローカルソース線355a～355dによって、複数のチャネル領域356-1～356-8に分断されて

50

いる。図5では、チャネルブレーカは、ローカルビット線間に配置されていない。複数のメモリセルが、フラッシュメモリデバイスの記憶密度を増大させるように、形成され得る。たとえば、チャネル領域356-1および356-8、ローカルビット線354a、ローカルビット線354aに隣接する2つのローカルソース線355aおよび355d、電荷蓄積要素334、ならびにワード線323pが、1つのメモリセルを構成する。

#### 【0056】

図6は、本発明のさらに別の実施形態による、1つの活性円柱の複数のローカルビット線および複数のローカルソース線を示す、X-Y平面の概略断面図であり、同様の数字が、同様の要素、領域、または層を指定している。図6で示しているように、同様に、活性円柱ACが、ワード線WLによって、周りを覆われている。活性円柱ACは、基板(図6で図示せず)の平坦面に直交するZ方向に沿って延在する垂直NORストリングを備える。

10

#### 【0057】

活性円柱AC内の垂直NORストリングの1つの特定の平面のみが、図6に示されていることが分かる。環状シリコンチャネル356が、示されている。電荷捕捉層を含む電荷蓄積要素334が、シリコンチャネル356とワード線WLとの間に位置している。シリコンチャネル356および活性円柱ACの形状は、図解目的のためだけのものであることが理解されよう。卵形の形状、長方形の形状、または不規則な形状などの他の形状が、本発明の多様な実施形態に従って、適用可能であり得る。信号ラインLBLおよびLSLならびにチャネルブレーカの位置の形状は、図解目的のためだけのものであることが理解されよう。信号ラインLBLおよびLSLならびにチャネルブレーカの位置は、処理/製造要件に従って、調整され得る。

20

#### 【0058】

別の実施形態によれば、活性円柱ACは、4つのローカルビット線354a～354d、ならびに4つのローカルソース線355a～355dを含み得る。シリコンチャネル356は、4つのローカルビット線354a～354d、ならびに4つのローカルソース線355a～355dによって、複数のチャネル領域356-1～356-6に分断されている。複数のメモリセルが、フラッシュメモリデバイスの記憶密度を増大させるように、形成され得る。たとえば、チャネル領域356-1、ローカルビット線354a、ローカルビット線354aに隣接する共有ローカルソース線355a、電荷蓄積要素334、ならびにワード線323pが、メモリセルT<sub>1</sub>を構成する。たとえば、チャネル領域356-2、ローカルビット線354b、ローカルビット線354bに隣接する共有ローカルソース線355a、電荷蓄積要素334、ならびにワード線323pが、メモリセルT<sub>2</sub>を構成する。たとえば、チャネル領域356-3および356-4、ローカルビット線354c、ローカルビット線354cに隣接する2つのローカルソース線355bおよび355c、電荷蓄積要素334、ならびにワード線323pが、メモリセルT<sub>3</sub>を構成する。たとえば、チャネル領域356-5および356-6、ローカルビット線354d、ローカルビット線354dに隣接する2つのローカルソース線355cおよび355d、電荷蓄積要素334、ならびにワード線323pが、メモリセルT<sub>4</sub>を構成する。

30

#### 【0059】

図6では、2つの例示のチャネルブレーカ320aおよび320bが、チャネルを分断するために追加されているが、必ずしも有する必要はない。2つのチャネルブレーカ320aおよび320bは、図解目的のためだけのものであることが分かる。チャネルブレーカの数は、各LBLがそれに加えて少なくとも1つのLSL有することができ、LBLとLSLとの間に連続するチャネルが存在する、という事実に影響を及ぼさない限り、増減され得る。この図内のチャネルブレーカの位置および数は、図解のためだけのものである。本発明の教示を保持しながらも、デバイスおよび方法の多数の変形および変更がなされ得ることに、当業者は、容易に気づくであろう。したがって、上の開示は、添付の請求項の境界によってのみ、限定されると解釈されるべきである。

40

#### 【符号の説明】

#### 【0060】

50

## 1 メモリ構造

## 1 0 基板

## 1 1 1 垂直NORストリング

## 1 1 2 グローバルソース線 (GSL)、信号ライン

## 1 1 3 ワード線 (WL)

## 1 1 4 グローバルビット線 (GBL)、信号ライン

## 2 0 0 基板

## 2 0 6 柱身バイアスソース

## 2 1 1 ビットラインアクセス選択トランジスタ

## 2 2 3 ワード線

## 2 5 6 コンタクト

## 2 5 7 コンタクト

## 2 7 0 垂直NORストリングのTFT

## 3 1 0 絶縁分離

## 3 1 4 - 0 ~ 3 1 4 - 7 グローバルビット線 (GBL)

## 3 2 0、3 2 0 a、3 2 0 b チャネルブレーカ

## 3 2 3 p ワード線スタック

## 3 3 4 電荷蓄積素子

## 3 5 4 a ~ 3 5 4 d ローカルビット線 (LBL)

## 3 5 5、3 5 5 a ~ 3 5 5 d ローカルソース線 (LSL)

## 3 5 6 チャネル領域、環状シリコンチャネル

## 3 5 6 a、3 5 6 b、3 5 6 - 1 ~ 3 5 6 - 8 チャネル領域

【図面】

【図1】

FIG. 1

【図2】

FIG. 2

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

---

フロントページの続き

(74)代理人 100133400

弁理士 阿部 達彦

(72)発明者 ミン・シェ

中華人民共和国・フーペイ・430074・ウーハン・イースト・レイク・ハイ・テック・デヴェロップメント・ゾーン・グアンドン・サイエンス・アンド・テクノロジー・インダストリアル・パーク・ファグエン・ロード・ナンバー・18・ルーム・7018

(72)発明者 チアン・タン

中華人民共和国・フーペイ・430074・ウーハン・イースト・レイク・ハイ・テック・デヴェロップメント・ゾーン・グアンドン・サイエンス・アンド・テクノロジー・インダストリアル・パーク・ファグエン・ロード・ナンバー・18・ルーム・7018

審査官 小山 満

(56)参考文献 特表2019-504479(JP,A)

米国特許出願公開第2017/0148517(US,A1)

国際公開第2017/091338(WO,A1)

米国特許出願公開第2016/0099254(US,A1)

米国特許出願公開第2018/0182776(US,A1)

(58)調査した分野 (Int.Cl., DB名)

H10B 43/20

H01L 21/336

H01L 29/788

H01L 29/792