(12)

## Patentschrift

(21) Aktenzeichen: 10 2018 125 128-9

(22) Anmeldetag: 11.10.2018

(43) Offenlegungstag: 27.06.2019

(45) Schließungstag. **27**

(45) Veröffentlichungstag

der Patenterteilung: **15.12.2022**

(51) Int Cl.: **G11C 16/34 (2006.01)**

G06E 3/06 (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                  |    |    |                  |    |    |                  |    |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------|----|----|------------------|----|----|------------------|----|

| (30) Unionspriorität:<br><b>10-2017-0177848</b> 22.12.2017 KR                                             | (72) Erfinder:<br><b>Kim, Seung-Bum, Hwasung-City, Gyeonggi-do, KR</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                  |    |    |                  |    |    |                  |    |

| (73) Patentinhaber:<br><b>Samsung Electronics Co., Ltd., Suwon-si, Gyeonggi-do, KR</b>                    | (56) Ermittelter Stand der Technik:<br><table> <tr> <td data-bbox="898 875 975 887">US</td> <td data-bbox="1143 875 1321 887">2013 / 0 028 022</td> <td data-bbox="1327 875 1378 887">A1</td> </tr> <tr> <td data-bbox="898 889 975 902">US</td> <td data-bbox="1143 889 1321 902">2014 / 0 372 678</td> <td data-bbox="1327 889 1378 902">A1</td> </tr> <tr> <td data-bbox="898 905 975 916">US</td> <td data-bbox="1143 905 1321 916">2015 / 0 135 025</td> <td data-bbox="1327 905 1378 916">A1</td> </tr> </table> | US | 2013 / 0 028 022 | A1 | US | 2014 / 0 372 678 | A1 | US | 2015 / 0 135 025 | A1 |

| US                                                                                                        | 2013 / 0 028 022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A1 |                  |    |    |                  |    |    |                  |    |

| US                                                                                                        | 2014 / 0 372 678                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A1 |                  |    |    |                  |    |    |                  |    |

| US                                                                                                        | 2015 / 0 135 025                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A1 |                  |    |    |                  |    |    |                  |    |

| (74) Vertreter:<br><b>KUHNEN &amp; WACKER Patent- und Rechtsanwaltsbüro PartG mbB, 85354 Freising, DE</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                  |    |    |                  |    |    |                  |    |

(54) Bezeichnung: **Nichtflüchtige Speichervorrichtung, Verfahren zum Betreiben einer nichtflüchtigen Speichervorrichtung und Speichervorrichtung mit derselben**

(57) Hauptanspruch: Nichtflüchtige Speichervorrichtung, die Folgendes aufweist:

eine Speicherzellanordnung (100), welche eine Mehrzahl von Speicherblöcken (BLK1 - BLKz) aufweist, wobei jeder der Mehrzahl von Speicherblöcken (BLK1 - BLKz) eine Mehrzahl von Speicherzellen aufweist, welche jeweils mit Wortleitungen (WL1 - WL<sub>n</sub>) gekoppelt sind, wobei die Wortleitungen (WL1 - WL<sub>n</sub>) vertikal auf einem Substrat (111) gestapelt sind, wobei einige Speicherzellen der Mehrzahl von Speicherzellen durch eine Unterblockeinheit kleiner als ein Speicherblock der Mehrzahl von Speicherblöcke (BLK1 - BLKz) auswählbar sind; und

eine Steuerschaltung (500, 500a, 500b), welche konfiguriert ist, um Unterblöcke eines ersten Speicherblocks (BLK1) der Mehrzahl von Speicherblöcken (BLK1 - BLKz) in wenigstens einen schlechten Unterblock (SB1) und wenigstens einen normalen Unterblock (SB2, SB3) basierend auf einer Fehlerauftretshäufigkeit jedes der Unterblöcke des ersten Speicherblocks (BLK1) zu unterteilen, und konfiguriert ist, um unterschiedliche Programmier-/Lösch-Zyklen auf den wenigstens einen schlechten Unterblock (SB1) als auf den wenigstens einen normalen Unterblock (SB2, SB3) anzuwenden basierend auf einem Befehl und einer Adresse, welche von außerhalb für die nichtflüchtige Speichervorrichtung vorgesehen sind, wobei der wenigstens eine schlechte Unterblock (SB1) benachbart zu dem wenigstens einen normalen Unterblock (SB2, SB3) ist,

wobei die Steuerschaltung (500, 500a, 500b) ferner konfi-

guriert ist, um einen ersten Programmier-/Löschenzyklus (821) auf den wenigstens einen normalen Unterblock (SB2, SB3) anzuwenden, wenn die Adresse den wenigstens einen normalen Unterblock (SB2, SB3) bezeichnet, und um einen zweiten Programmier-/Löschenzyklus (822) auf den wenigstens einen schlechten Unterblock (SB1) bis zu einem ersten Referenzzykluswert anzuwenden und um einen dritten Programmier-/Löschenzyklus (823) auf den wenigstens einen schlechten Unterblock (SB1) nach dem ersten Referenzzykluswert anzuwenden, wenn die Adresse den wenigstens einen schlechten Unterblock (SB1) bezeichnet; und wobei ...

**Beschreibung****HINTERGRUND**

**[0001]** Einige Ausführungsformen beziehen sich allgemein auf Speichervorrichtungen und genauer auf nichtflüchtige Speichervorrichtungen, Verfahren zum Betreiben nichtflüchtiger Speichervorrichtungen und Speichervorrichtungen mit denselben.

**[0002]** Halbleiterspeichervorrichtungen können flüchtig oder nichtflüchtig sein. Flashspeichervorrichtungen sind typischerweise nichtflüchtige Halbleiterspeichervorrichtungen. Flashspeichervorrichtungen können als ein Stimm- und Bild-Datenspeichermedium für Informationsvorrichtungen wie beispielsweise den Computer, ein Mobiltelefon, einen PDA, eine digitale Kamera, einen handgeführten PC und dergleichen verwendet werden.

**[0003]** Nichtflüchtige Speichervorrichtungen, welche Speicherzellen haben, welche in drei Dimensionen gestapelt sind, wurden erforscht, um die Integrität der nichtflüchtigen Speichervorrichtungen zu verbessern. Zunahmen jedoch in der Speicherkapazität können verschiedene Probleme verursachen, welche nicht mit existierenden Speicherverwaltungsregeln übereinstimmen.

**[0004]** US 2015/0135025 A1 offenbart: Ein Verfahren zum Ansteuern einer Speichersteuerung, die zum Steuern einer nichtflüchtigen Speichervorrichtung konfiguriert ist. Das Verfahren enthält das Zählen einer Anzahl von Fehlerbits von Lesedaten, die von der nichtflüchtigen Speichervorrichtung bereitgestellt werden, das Bestimmen eines laufenden Durchschnittswertes unter Verwendung der Anzahl von Fehlerbits und das Ausführen eines Abnutzungsausgleichs an der nichtflüchtigen Speichervorrichtung unter Verwendung des laufenden Durchschnittswertes als Abnutzungsausgleichsindex.

**[0005]** US 2013/0028022 A1 offenbart: Verfahren zum Bestimmen eines Programmfensters und Speichervorrichtungen. Ein solches Verfahren zur Bestimmung des Programmfensters misst die Menge an Programmstörungen, die durch einen bestimmten Zustand auftreten, und bestimmt das Programmfenster in Abhängigkeit von der Menge an Programmstörungen.

**[0006]** US 2014/0372678 A1 offenbart: Ein Zugriffsverfahren auf eine nichtflüchtige Speichervorrichtung, die in einer Benutzervorrichtung enthalten ist, umfasst das Empfangen einer Schreibanforderung, um Daten in die nichtflüchtige Speichervorrichtung zu schreiben; das Erfassen einer Anwendung, die die Schreibanforderung ausgibt, eines Benutzerkontextes, einer Warteschlangengröße eines Schreibpuffers, eines Attributs der zum Schreiben angefor-

derten Daten oder eines Operationsmodus der Benutzervorrichtung; und das Entscheiden eines aus einer Mehrzahl von Schreibmodi, die zum Schreiben der zum Schreiben angeforderten Daten in die nichtflüchtige Speichervorrichtung gemäß der erfassten Information zu verwenden sind. Die Schreibmodi haben unterschiedliche Programmspannungen und Verifizierungsspannungssätze.

**KURZFASSUNG**

**[0007]** Die vorliegende Erfindung ist definiert in den unabhängigen Ansprüchen und bezieht sich auf eine nichtflüchtige Speichervorrichtung, ein Verfahren zum Betreiben derselben und eine Speichervorrichtung mit einer solchen. Spezifische Ausführungsformen sind definiert in den abhängigen Ansprüchen.

**[0008]** Demzufolge kann die nichtflüchtige Speichervorrichtung Unterblöcke eines ersten Speicherblocks in wenigstens einen schlechten Unterblock und wenigstens einen normalen Unterblock basierend auf einer Fehlerauftrittshäufigkeit jedes der Unterblöcke oder basierend auf einer Ausdauercharakteristik aufgrund von Positionen der Unterblöcke unterteilen, kann unterschiedliche Programmier-/Löschenzyklen auf den wenigstens einen schlechten Unterblock und den wenigstens einen normalen Unterblock ausüben und kann einen Anpassungsvorspannungszustand auf den ersten Speicherblock während eines Speicherbetriebs beziehungsweise einer Speicheroperation des ersten Speicherblocks ausüben. Demnach kann die nichtflüchtige Speichervorrichtung die Leistungsfähigkeit erhöhen und eine Verringerung einer Lebensdauer der nichtflüchtigen Speichervorrichtung verhindern.

**Figurenliste**

**[0009]** Veranschaulichende, nicht beschränkende beispielhafte Ausführungsformen werden deutlicher aus der folgenden detaillierten Beschreibung in Verbindung mit den beigefügten Zeichnungen verstanden werden.

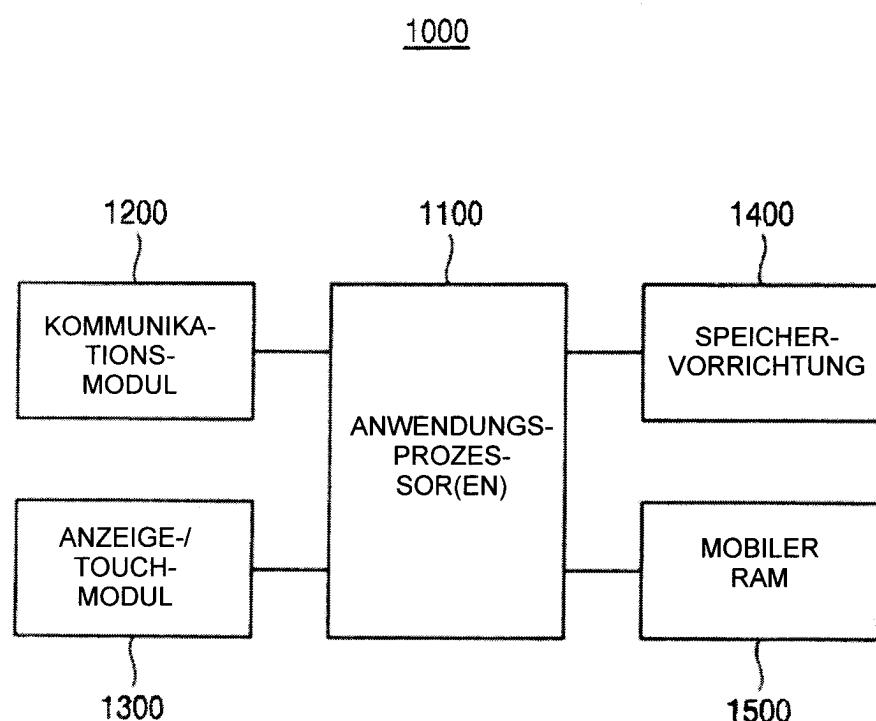

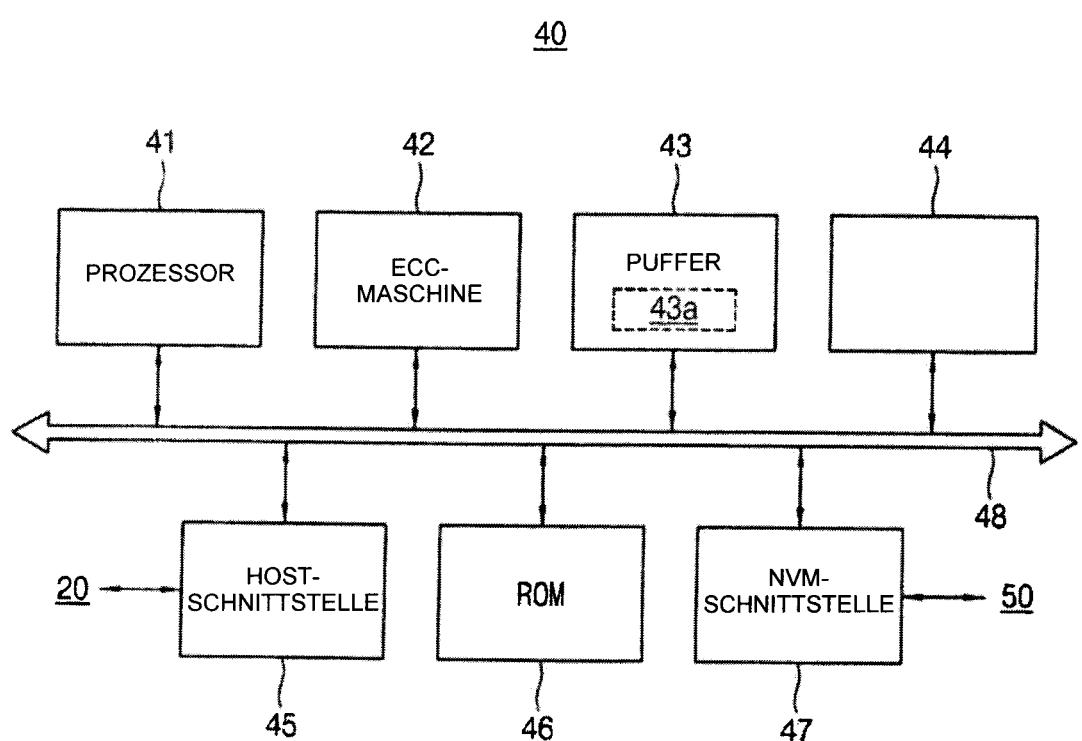

**Fig. 1** ist ein Blockschaltbild, welches eine elektronische Vorrichtung gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

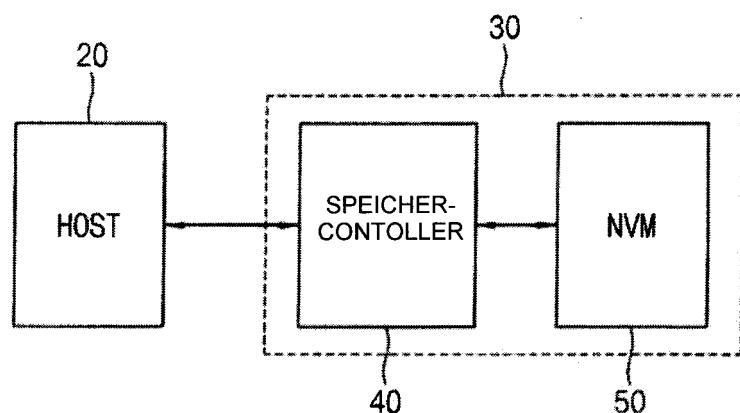

**Fig. 2** ist ein Blockschaltbild, welches die Speichervorrichtung in **Fig. 1** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

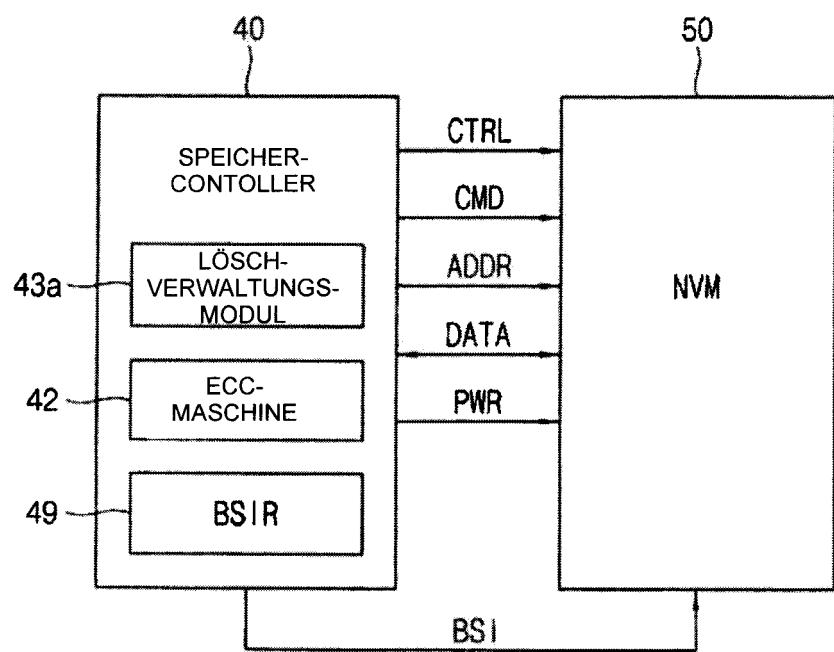

**Fig. 3** ist ein Blockschaltbild, welches den Speichercontroller in der Speichervorrichtung der **Fig. 2** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

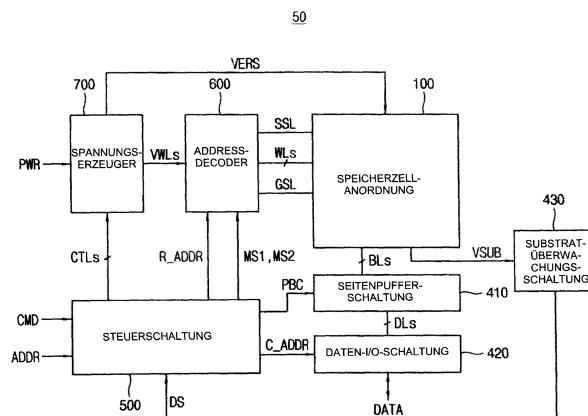

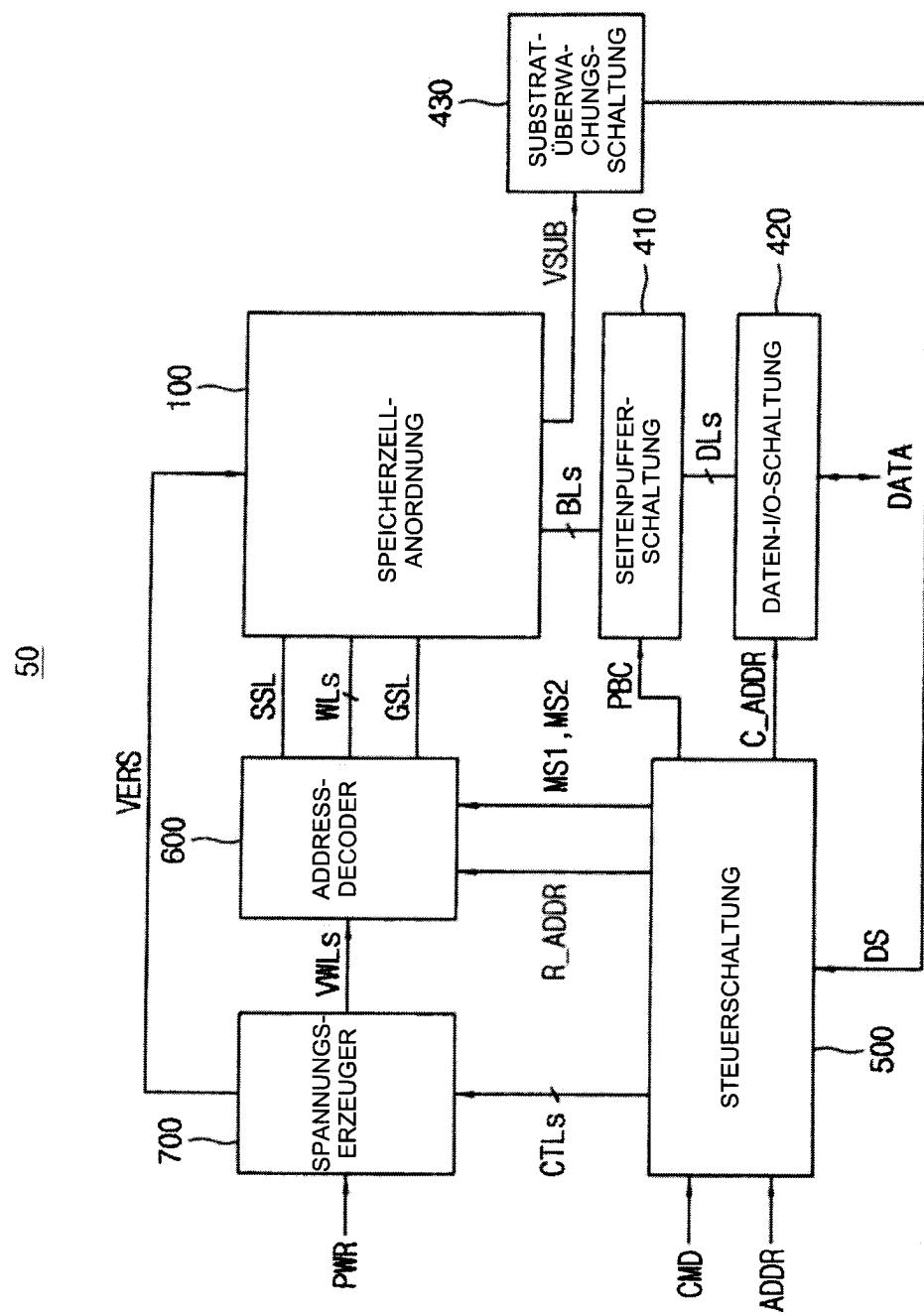

**Fig. 4** ist ein Blockschaltbild, welches die nicht-flüchtige Speichervorrichtung (nonvolatile memory device) in der Speichervorrichtung (storage device) der **Fig. 2** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

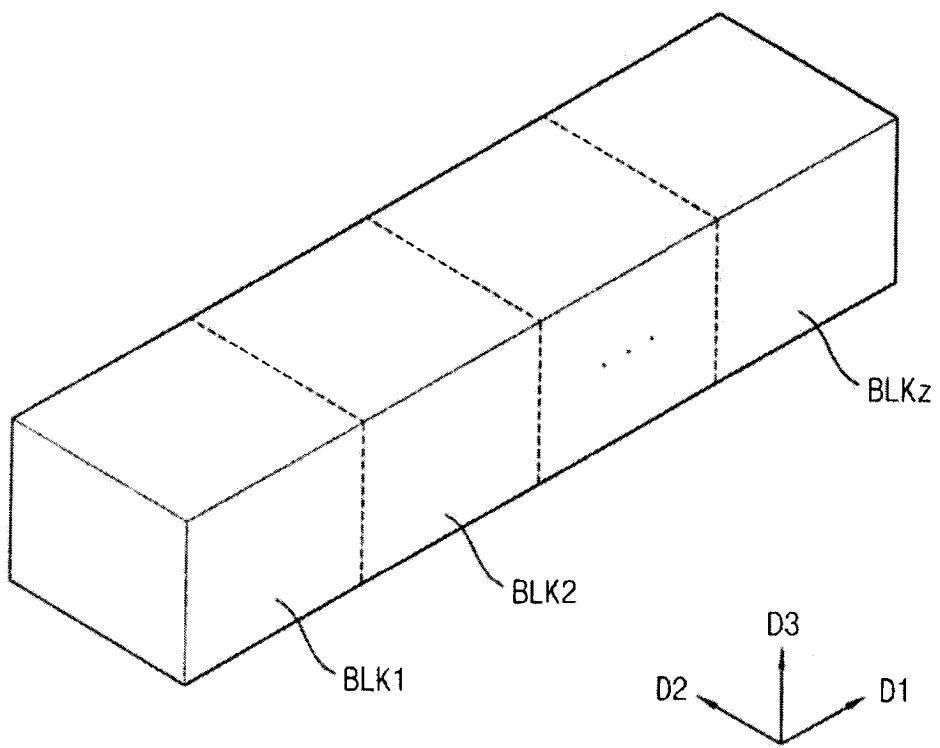

**Fig. 5** ist ein Blockschaltbild, welches die Speicherzellanordnung in **Fig. 4** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

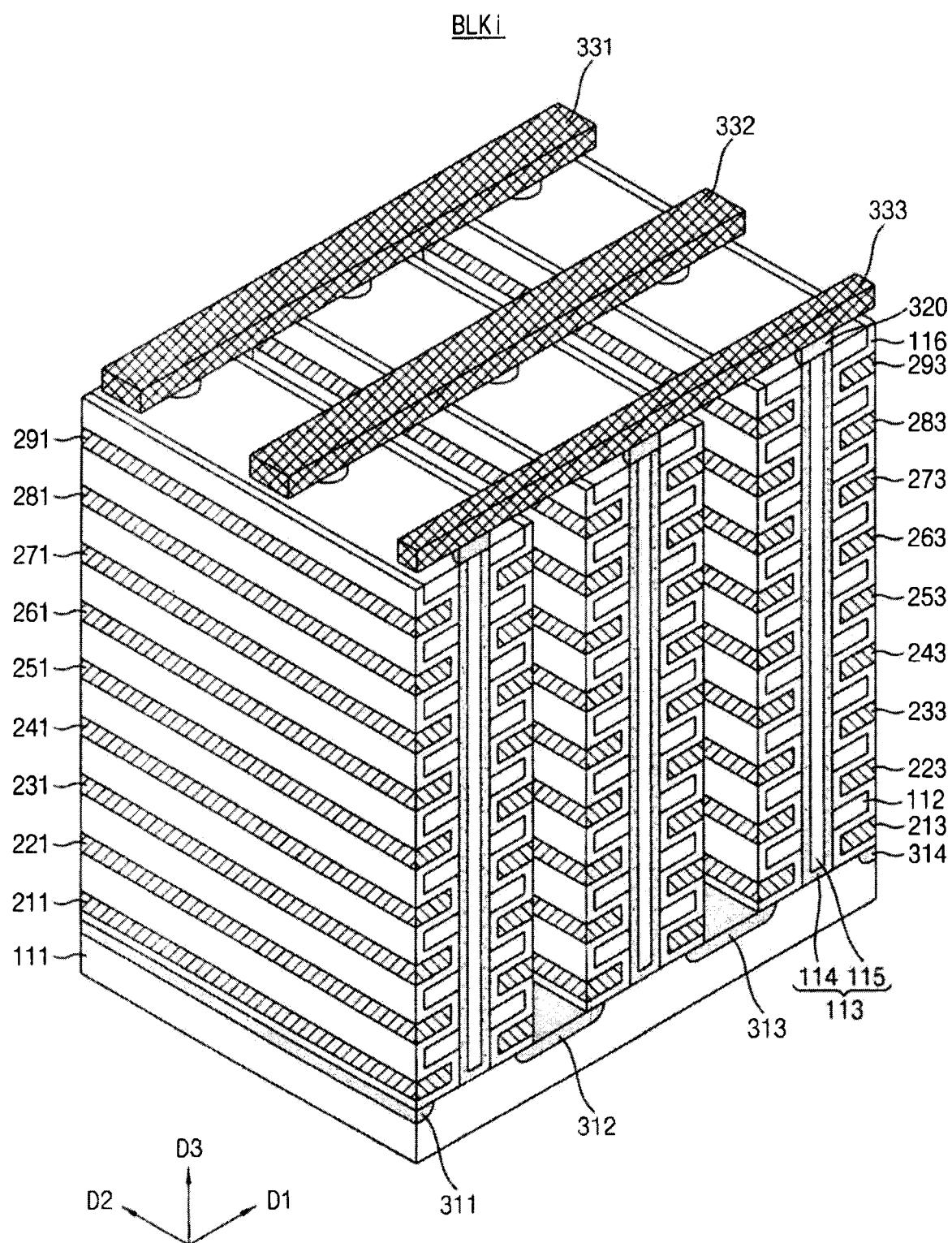

**Fig. 6** ist eine perspektivische Ansicht, welche einen der Speicherblöcke der **Fig. 5** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 7** ist ein Ersatzschaltbild, welches den Speicherblock der **Fig. 6** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 8** veranschaulicht einen Zellbereich, in welchem die Speicherzellanordnung der **Fig. 4** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts gebildet ist.

**Fig. 9A** und **Fig. 9B** veranschaulichen Querschnitte von Strängen der Speicherblöcke der **Fig. 8** jeweils gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts.

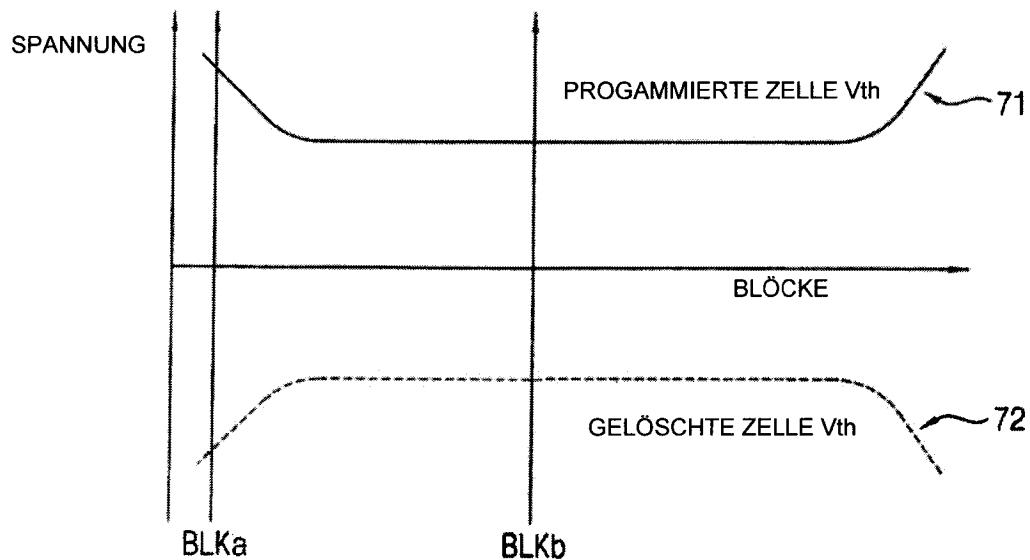

**Fig. 10** ist ein Graph, welcher ein Ergebnis eines Durchföhrens einer Programmieroperation und einer Löschoperation auf die Speicherblöcke in **Fig. 8** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts zeigt.

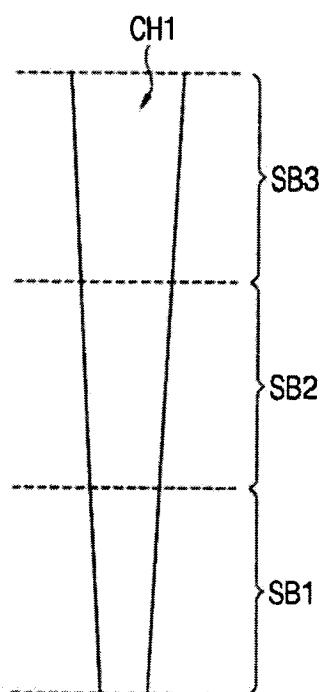

**Fig. 11** veranschaulicht ein Beispiel einer vertikalen Struktur in **Fig. 8** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts.

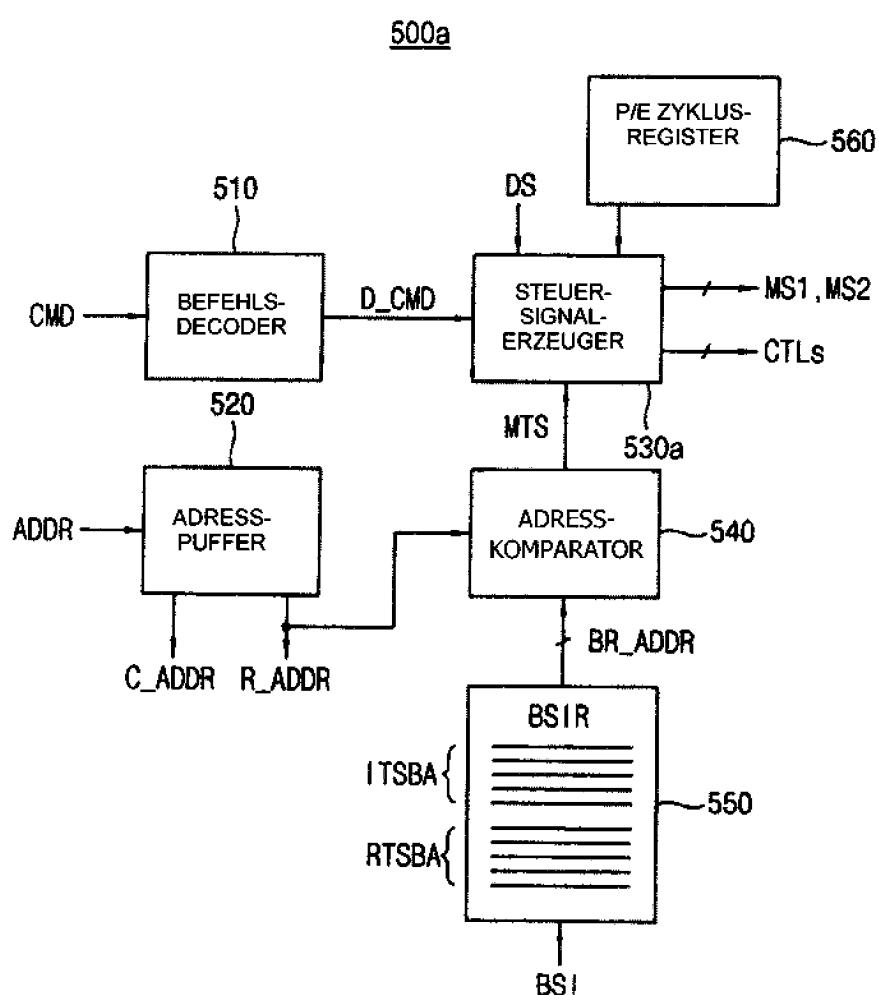

**Fig. 12** ist ein Blockschaltbild, welches ein Beispiel der Steuerschaltung in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

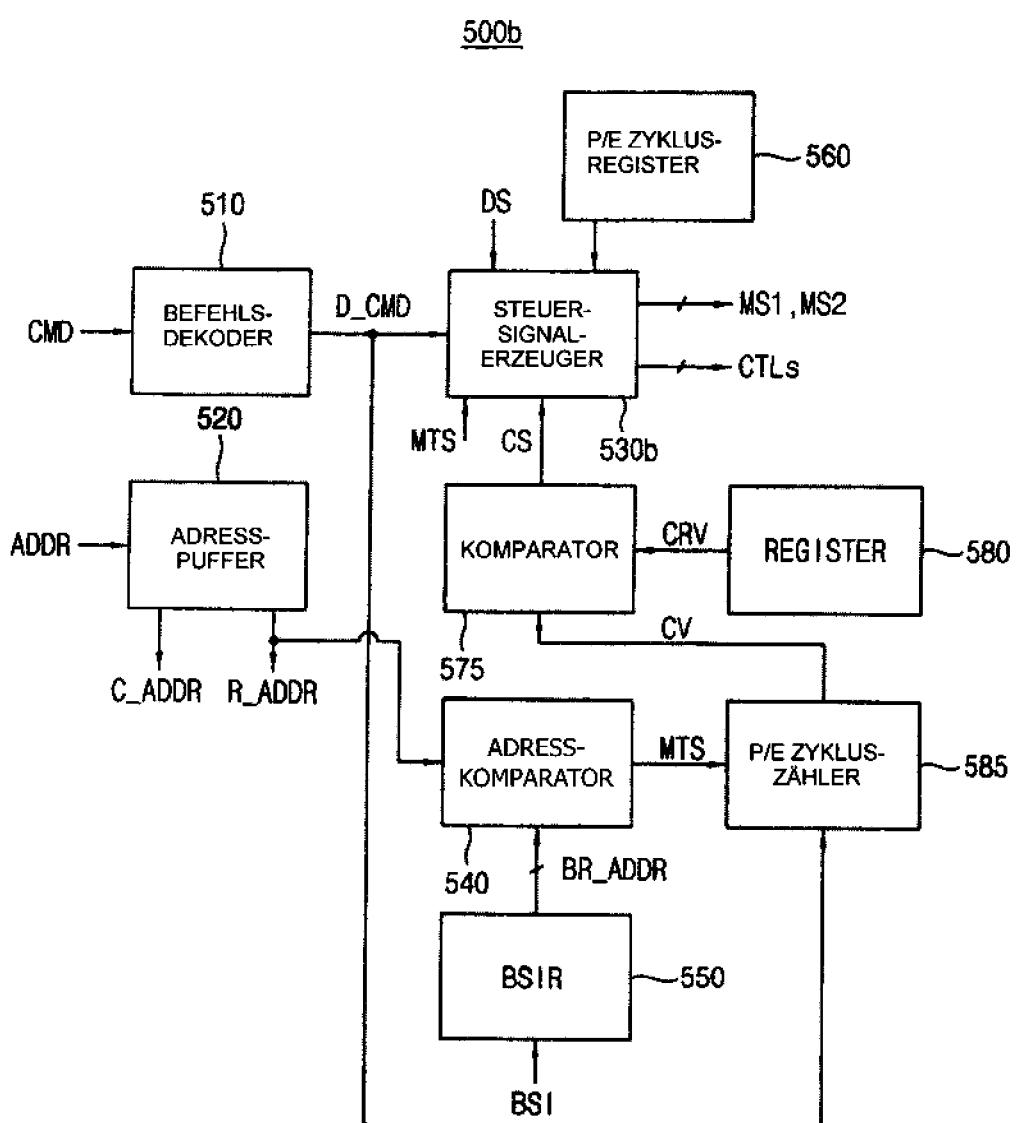

**Fig. 13** ist ein Blockschaltbild, welches ein anderes Beispiel der Steuerschaltung in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 14** ist ein Blockschaltbild, welches den Spannungserzeuger in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 15** ist ein Blockschaltbild, welches den Adressdecoder in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 16** ist ein Flussdiagramm, welches ein Verfahren zum Betreiben einer nichtflüchtigen Speichervorrichtung gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

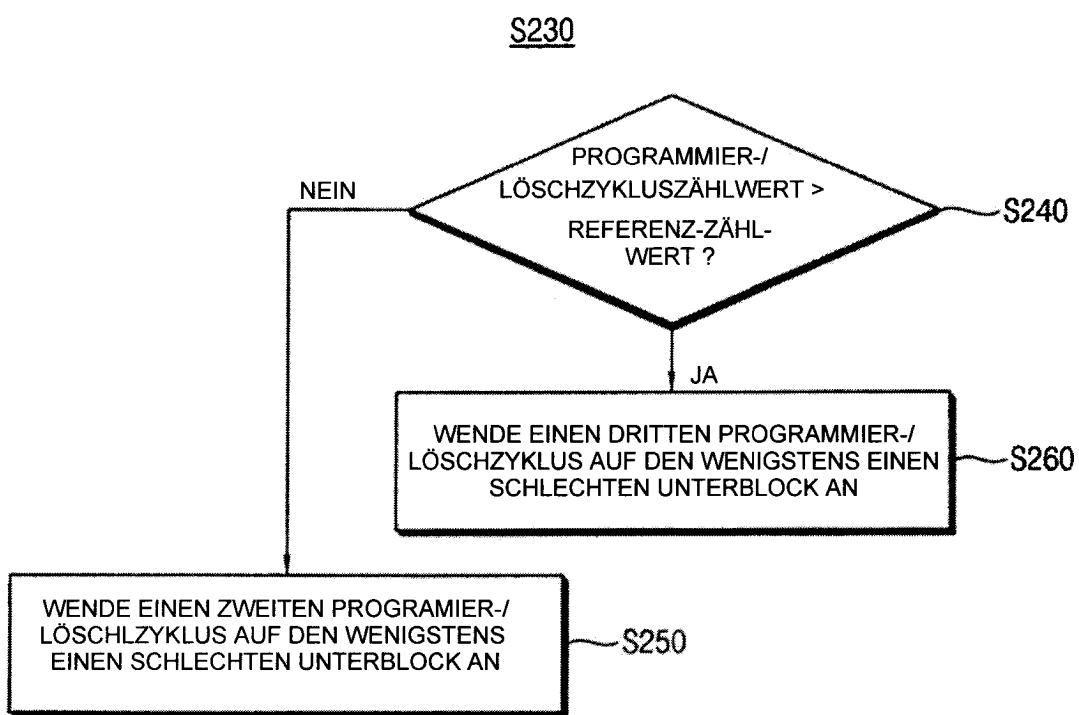

**Fig. 17** ist ein Flussdiagramm, welches eine Operation zum Ausüben der unterschiedlichen Programmier-/Löschenzyklen in **Fig. 16** im Detail gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 18** ist ein Flussdiagramm, welches eine Operation veranschaulicht, dass wenigstens ein zweiter Programmier-/Löschenzyklus im Detail in **Fig. 17** gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts ausgeübt wird.

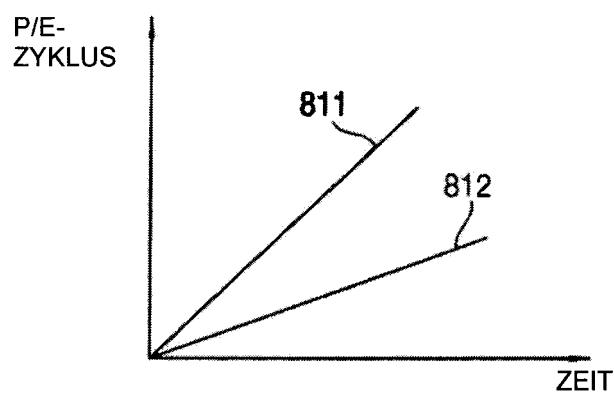

**Fig. 19A** und **Fig. 19B** veranschaulichen Programmier-/Löschenzyklen, welche auf den normalen Unterblock und den schlechten Unterblock jeweils gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts ausgeübt werden.

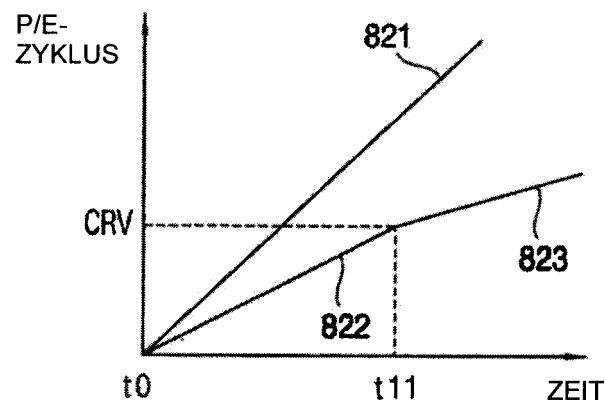

**Fig. 20** ist ein Flussdiagramm, welches ein Verfahren zum Betreiben einer nichtflüchtigen Speichervorrichtung gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

**Fig. 21A** bis **Fig. 26B** veranschaulichen Vorspannungszustände, welche auf Unterblöcke in dem ersten Speicherblock jeweils gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts ausgeübt werden.

**Fig. 27** ist ein Blockschaltbild, welches eine mobile Vorrichtung gemäß beispielhaften Ausführungsformen des vorliegenden erfinderischen Konzepts veranschaulicht.

## DETAILLIERTE BESCHREIBUNG

**[0010]** Es wird angemerkt, dass Aspekte des erfinderischen Konzepts, welche hinsichtlich einer Ausführungsform beschrieben sind, in einer unterschiedlichen Ausführungsform inkorporiert sein können, obwohl nicht spezifisch in Bezug darauf beschrieben. Das heißt, dass alle Ausführungsformen und/oder Merkmale einer beliebigen Ausführungsform auf einem beliebigen Wege und/oder Kombination kombiniert werden können. Diese und anderer Aufgaben und/oder Aspekte des erfinderischen Konzepts werden im Detail in der Beschreibung, welche untenstehend erläutert ist, erklärt.

**[0011]** Einige verschiedene Ausführungsformen werden vollständiger hierin nachstehend unter Bezugnahme auf die beigefügten Zeichnungen beschrieben werden, in welchen einige Ausführungsformen gezeigt sind.

**[0012]** Die Ausführungsformen werden beschrieben und in den Zeichnungen veranschaulicht in Einheiten von funktionalen Blöcken, Einheiten und/oder Modulen. Diese Blöcke, Einheiten und/oder Module können physikalisch implementiert sein durch elektronische (oder optische) Schaltungen wie beispielsweise Logikschaltungen, diskrete Komponenten, Mikroprozessoren, festverdrahtete Schaltungen, Speicherelemente, Verdrahtungsverbindungen und dergleichen, welche zusammen in einer einzelnen integrierten Schaltung (beispielsweise als ein einzelner Halbleiterchip) oder als getrennte integrierte Schaltungen und/oder diskrete Komponenten (beispielsweise verschiedene Halbleiterchips, welche auf einer Leiterplatte miteinander verdrahtet sind) unter Verwendung von Halbleiterherstellungstechniken und/oder anderen Herstellungstechnologien gebildet werden können. Diese Blöcke, Einheiten und/oder Module können durch einen Prozessor (beispielsweise einen Mikroprozessor, einen Controller, eine CPU, eine GPU) oder Prozessoren implementiert sein, welche unter Verwendung von Software (beispielsweise Microcode) programmiert werden, um verschiedene Funktionen, welche hierin diskutiert sind, durchzuführen. Jeder Block, jede Einheit und/oder Modul können durch dedizierte Hardware oder als eine Kombination von dedizierter Hardware, um einige Funktionen durchzuführen und ein Prozessor zum Durchführen anderer Funktionen implementiert sein. Ebenso kann jeder Block, Einheit und/oder Modul der Ausführungsformen durch physikalisch getrennte Schaltungen ausgeführt sein und muss nicht als eine einzelne integrierte gebildet sein. Wenn hierin verwendet, weist der Begriff „und/oder“ eine beliebige und alle Kombinationen von einem oder mehreren der zugeordneten aufgelisteten Gegenstände auf. Ausdrücke wie beispielsweise „wenigstens einer von“ modifizieren, wenn sie einer Liste von Elementen voranstehen, die gesamte Liste der Elemente und modifizieren nicht die individuellen Elemente der Liste.

**[0013]** **Fig. 1** ist ein Blockschaltbild, welches eine elektronische Vorrichtung gemäß einigen Ausführungsformen veranschaulicht.

**[0014]** Bezug nehmend auf **Fig. 1** kann eine elektronische Vorrichtung 10 einen Host 20 und eine Speichervorrichtung (Storage Device) oder ein Speicher-System (memory system) 30 aufweisen. Die Speichervorrichtung (storage device) 30 kann einen Speichercontroller (memory controller) 14 und wenigstens eine nichtflüchtige Speichervorrichtung (nonvolatile memory device) 50 aufweisen. Der

Host 20 kann den Gesamtbetrieb der Speichervorrichtung 30 steuern.

**[0015]** Der Speichercontroller 40 kann die Signale wie beispielsweise einen Befehl, eine Adresse, Daten etc. mit dem Host 20 austauschen. Der Speichercontroller 40 kann Daten in die nichtflüchtige Speichervorrichtung 50 schreiben und liest Daten aus der nichtflüchtigen Speichervorrichtung 50 gemäß einem Befehl von dem Host 20.

**[0016]** **Fig. 2** ist ein Blockschaltbild, welches die Speichervorrichtung (Storage Device) in **Fig. 1** gemäß einigen Ausführungsformen veranschaulicht.

**[0017]** Bezug nehmend auf **Fig. 2** kann die Speichervorrichtung 30 den Speichercontroller 40 und wenigstens eine nichtflüchtige Speichervorrichtung 50 aufweisen.

**[0018]** In einigen Ausführungsformen können jeder des Speichercontrollers 40 und der nichtflüchtigen Speichervorrichtung 50 in der Form eines Chip, eines Package oder eines Modul vorgesehen sein. In einigen Ausführungsformen können der Speichercontroller 40 und die nichtflüchtige Speichervorrichtung 50 auf verschiedenen Packages montiert sein, um als eine Speichervorrichtung wie beispielsweise eine Speicherplatte vorgesehen zu sein.

**[0019]** Die nichtflüchtige Speichervorrichtung 50 kann eine Leseoperation, eine Löschoperation, eine Programmieroperation oder eine Schreiboperation unter der Steuerung des Speichercontrollers 40 durchführen. Die nichtflüchtige Speichervorrichtung 50 empfängt einen Befehl CMD, eine Adresse ADDR und Daten DATA über Eingangs-/Ausgangsleitungen von dem Speichercontroller 40 zum Durchführen solcher Operationen. Zusätzlich empfängt die nichtflüchtige Speichervorrichtung 50 ein Steuersignal CTRL über eine Steuerleitung von dem Speichercontroller 40. Zusätzlich empfängt die nichtflüchtige Speichervorrichtung 50 eine Leistung PWR über eine Stromleitung beziehungsweise Leistungsleitung von dem Speichercontroller 40.

**[0020]** Speicherzellen der nichtflüchtigen Speichervorrichtung 50 können die physikalische Charakteristik haben, dass eine Schwellenspannungsverteilung aufgrund von Gründen wie beispielsweise einer verstrichenen Programmierzeit, einer Temperaturänderung oder einem Lesen, einer Programmierstörung, einer Lesestörung etc. variiert. Beispielsweise können Daten, welche in der nichtflüchtigen Speichervorrichtung 50 gespeichert sind, aufgrund der obigen Gründe fehlerhaft werden. Der Speichercontroller 40 kann eine Vielzahl von Fehlerkorrekturtechniken verwenden, um solche Fehler zu korrigieren. Beispielsweise kann der Speichercontroller 40 eine Fehlerkor-

rekturcode (ECC = Error Correction Code = Fehlerkorrekturcode)-Maschine 42 aufweisen.

**[0021]** Der Speichercontroller 40 kann eine Löschoperation auf der nichtflüchtigen Speichervorrichtung 50 durch eine Unterblockeinheit durchführen und der Unterblock ist kleiner als ein Speicherblock der nichtflüchtigen Speichervorrichtung 50. Als ein Beispiel kann ein Speicherblock eine Mehrzahl von Unterblöcken aufweisen. Der Speichercontroller 40 kann ein Löschoberwaltungsmodul 43a aufweisen, um die Löschoperation durch die Unterblockeinheit zu verwalten.

**[0022]** Nach einer Unterblocklöschoperation kann das Löschoberwaltungsmodul 43a einen Löschstatus eines gelöschten Unterblocks und/oder eines Unterblocks benachbart zu dem gelöschten Unterblock überprüfen. Beispielsweise kann das Löschoberwaltungsmodul 43a Speicherzellen des gelöschten Unterblocks abtasten, um zu bestimmen, ob spezifische Parameter einen Referenzzykluswert überschreiten. Das Löschoberwaltungsmodul 43a kann Daten eines Unterblocks (von Unterblöcken) benachbart zu dem gelöschten Unterblock lesen, um eine Lösch-Inhibitionseffizienz zu erfassen. Beispielsweise kann das Löschoberwaltungsmodul 43a eine Bitfehlerrate (BER = Bit Error Rate = Bitfehlerrate) basierend auf Daten, welche aus einem gelöschten Unterblock gelesen werden, erfassen. Das Löschoberwaltungsmodul 43a kann Wear-Leveling-Information (beispielsweise Löschzählung) auf dem gelöschten Unterblock erlangen und überwachen. Zusätzlich kann das Löschoberwaltungsmodul 43a Daten des gelöschten Unterblocks lesen, um eine Variation in Schwellenspannungen von ausgewählten Speicherzellen und/oder eine Variation in der Bitfehlerrate (BER) zu überwachen. Das Löschoberwaltungsmodul 43a kann ebenso Daten eines unausgewählten Unterblocks lesen, um eine Variation in einer Schwellenspannung zu erfassen. Der Speichercontroller 40 kann verschiedene Prozeduren zum Kompensieren einer unausreichenden Löschung eines ausgewählten Unterblocks basierend auf Löschstatusinformation, welche durch das Löschoberwaltungsmodul 43a erfasst wird, durchführen.

**[0023]** Allgemein kann ein Speicherblock eine maximale Größe einer Speichereinheit sein, welche zu derselben Zeit gelöscht werden kann. In einer dreidimensionalen nichtflüchtigen Speichervorrichtung, in der Wortleitungen in einer Richtung gestapelt sind, welche ein Substrat schneidet (beispielsweise rechtwinklig zu einem Substrat), kann ein Speicherblock als eine Gruppe von Zellsträngen definiert sein, welche gestapelte Wortleitungen gemeinsam verwenden. Ein Unterblock kann einer Unterspeicherseinheit entsprechen, welche durch ein Unterteilen des Speicherblocks (oder physikalischen Blocks)

durch eine Wortleitungseinheit oder Auswahlleitungseinheit definiert beziehungsweise begrenzt ist. Beispielsweise kann jeder Unterblock aus Speicherzellen gebildet sein, welche einen Abschnitt der Wortleitungen des Speicherblocks gemeinsam verwenden.

**[0024]** Während einer Leseoperation auf der nichtflüchtigen Speichervorrichtung 50 kann der Speichercontroller 40 Daten, welche auf einer ersten Seite der nichtflüchtigen Speichervorrichtung 50 gespeichert sind, unter Verwendung eines Default-Lesespannungssatzes lesen. Der Default-Lesespannungssatz kann vorbestimmte Lesespannungen aufweisen. Die ECC-Maschine 42 kann Fehler, welche in Daten enthalten sind, welche aus der nichtflüchtigen Speichervorrichtung 50 gelesen werden, erfassen und korrigieren. Die ECC-Maschine 42 kann eine ECC-Operation durch ein Erfassen und Korrigieren von Fehlern durchführen. In einigen Ausführungsformen kann die ECC-Maschine 42 in der Form von Hardware implementiert sein. Die ECC-Maschine 42 kann eine Fehlerauftrittshäufigkeit in den gelesenen Daten von der nichtflüchtigen Speichervorrichtung 50 mittels einer Einheit eines Unterblocks bestimmen und kann einen Unterblock als einen schlechten Unterblock bezeichnen beziehungsweise designieren, dessen Fehlerauftrittshäufigkeit größer ist als ein Referenzzykluswert während einer vorbestimmten Zeit.

**[0025]** Der Speichercontroller 40 kann ein Schlechtunterblockinformationsregister 49 aufweisen, welches Information über wenigstens einen schlechten Unterblock der Unterblöcke speichert und kann die nichtflüchtige Speichervorrichtung 50 mit einer Information über einen schlechten Unterblock, welche Schlechtunterblockadressen des schlechten Unterblocks aufweist.

**[0026]** **Fig. 3** ist ein Blockschaltbild, welches den Speichercontroller in der Speichervorrichtung der **Fig. 2** gemäß einigen Ausführungsformen veranschaulicht.

**[0027]** Bezugnehmend auf die **Fig. 2** und **Fig. 3** kann der Speichercontroller einen Prozessor 41, die ECC-Maschine 42, den Puffer 43, das Löschoberwaltungsmodul 43a, welches mit dem Puffer 43 verbunden sein kann, einen Randomisierer 44, eine Hostschnittstelle 45, einen Nur-Lese-Speicher(ROM = Read Only Memory = Nur-Lese-Speicher) 46 und eine nichtflüchtige Speicherschnittstelle 47 aufweisen, welche über einen Bus 48 verbunden sind. Die ECC-Maschine 42 und das Löschoberwaltungsmodul 43a werden unter Bezugnahme auf **Fig. 2** beschrieben und eine Beschreibung davon wird demnach ausgelassen.

**[0028]** Der Prozessor 41 steuert einen Gesamtbetrieb des Speichercontrollers 40. In einigen Ausführungsformen kann das Löschverwaltungsmodul 43a in Software implementiert sein und in dem Puffer 43 gespeichert sein. Das Löschverwaltungsmodul 43a, welches in dem Puffer 43 gespeichert ist, kann durch den Prozessor 41 betrieben werden. Der ROM 46 kann eine Vielzahl von Information, welche für den Speichercontroller 40 zum Arbeiten benötigt wird, in Firmware speichern. Der Puffer 43 kann Daten, welche von der nichtflüchtigen Speichervorrichtung 50 vorgesehen sind, speichern, und kann das Löschverwaltungsmodul 43a aufweisen.

**[0029]** Der Randomisierer 44 kann Daten, welche in der nichtflüchtigen Speichervorrichtung 50 zu speichern sind, randomisieren. Beispielsweise kann der Randomisierer 44 Daten, welche in der nichtflüchtigen Speichervorrichtung 50 zu speichern sind, in einer Einheit einer Wortleitung randomisieren.

**[0030]** Ein Datenrandomisieren kann durchgeführt werden, um Daten wie beispielsweise Programmierzustände von Speicherzellen, welche mit einer Wortleitung verbunden sind, zu verarbeiten, um dasselbe Verhältnis zu haben. Beispielsweise hat, wenn Speicherzellen, welche mit einer Wortleitung verbunden sind, Multilevelzellen (MLC) sind, von welchen jede 2-Bit-Daten speichert, jede der Speicherzellen einen eines Löschezustands und eines ersten bis dritten Programmierzustandes. In diesem Fall randomisiert der Randomisierer 44 Daten derart, dass in Speicherzellen, welche mit einer Wortleitung verbunden sind, die Anzahl von Speicherzellen, welche den Löschezustand haben, die Anzahl von Speicherzellen, welche den ersten Programmierzustand haben, die Anzahl von Speicherzellen, welche den zweiten Programmierzustand haben, und die Anzahl von Speicherzellen, welche den dritten Programmierzustand haben, im Wesentlichen gleich zueinander sind. Beispielsweise haben Speicherzellen, in welchen randomisierte Daten gespeichert werden, Programmierzustände, deren Anzahl gleich zueinander ist. Der Randomisierer 44 de-randomisiert Daten, welche aus der nichtflüchtigen Speichervorrichtung 50 gelesen werden. Es wird verstanden werden, dass, obwohl die Begriffe „erster/erste/erstes, zweiter/zweite/zweites, dritter/dritte/drittes“ etc. verwendet werden können hierin, um verschiedene Elemente zu beschreiben, Elemente nicht durch diese Begriffe beschränkt sein sollten. Vielmehr werden diese Begriffe nur verwendet, um ein Element von einem anderen Element zu unterscheiden. Demnach könnte ein erstes Element, welches untenstehend diskutiert ist, als ein zweites Element benannt werden, ohne vom Umfang des vorliegenden erforderlichen Konzepts abzuweichen.

**[0031]** Der Randomisierer 44 kann Seitendaten randomisieren. Zum Zweck des leichten Verständ-

nisses wird ein idealer Betrieb des Randomisierers 44 beschrieben. Das erforderliche Konzept ist jedoch nicht darauf beschränkt. Beispielsweise randomisiert der Randomisierer 44 Daten derart, dass in Speicherzellen, welche mit einer Wortleitung verbunden sind, die Anzahl von Speicherzellen, welche den Löschezustand haben, die Anzahl von Speicherzellen, welche den ersten Programmierzustand haben, die Anzahl von Speicherzellen, welche den zweiten Programmierzustand haben und die Anzahl von Speicherzellen, welche den dritten Programmierzustand haben ungefähr derselbe Wert sind. Beispielsweise haben Speicherzellen, in welchen randomisierte Daten gespeichert werden, Programmierzustände, deren Anzahl ähnlich zueinander ist.

**[0032]** Der Speichercontroller 40 kommuniziert mit dem Host 20 über die Hostschnittstelle 45. Beispielsweise kann die Hostschnittstelle 45 einen Universal Serial Bus (USB), eine Multimedia Card (MMC), eine eingebettete MMC, eine Peripheral Component Interconnection (PCI), PCI-express, Advanced Technology Attachment (ATA), Serial-ATA, Parallel-ATA, eine Small Computer Small Interface (SCSI), eine Enhanced Small Disk Interface (ESDI), Integrated Drive Electronics (IDE), eine Mobile Industry Processor Interface (MIPI), Nonvolatile Memory Express (NVMe), Universal Flash Storage (UFS) und etc. aufweisen. Der Speichercontroller 40 kommuniziert mit der nichtflüchtigen Speichervorrichtung 50 über die nichtflüchtige Speicherschnittstelle 47.

**[0033]** **Fig. 4** ist ein Blockschaltbild, welches die nichtflüchtige Speichervorrichtung in der Speichervorrichtung der **Fig. 2** gemäß einigen Ausführungsformen veranschaulicht.

**[0034]** Bezug nehmend auf **Fig. 4** weist die nichtflüchtige Speichervorrichtung (Memory Device) 50 eine Speicherzellanordnung 100, einen Adressdecoder 600, eine Seitenpufferschaltung 410, eine Dateneingangs-/Ausgangsschaltung 420, eine Substratüberwachungsschaltung 430, eine Steuerschaltung 500 und einen Spannungserzeuger 700 auf.

**[0035]** Die Speicherzellanordnung 100 kann mit dem Adressdecoder 600 über eine Strangauswahlleitung SSL, eine Mehrzahl von Wortleitungen WLs und/oder eine Masseauswahlleitung GSL gekoppelt sein. Zusätzlich kann die Speicherzellanordnung 100 mit der Seitenpufferschaltung 410 über eine Mehrzahl von Bitleitungen BLs gekoppelt sein. Die Speicherzellanordnung 100 kann eine Mehrzahl von Speicherzellen aufweisen, welche mit der Mehrzahl von Wortleitungen WLs und der Mehrzahl von Bitleitungen BLs gekoppelt sind.

**[0036]** Der Adressdecoder 600 kann Spannungen zu der Strangauswahlleitung SSL, der Mehrzahl von Wortleitungen WLs und/oder der Masseauswahllei-

tung GSL zum Betreiben von Speicherzellen der Speicherzellanordnung 100 in Antwort auf eine Adresse ADDR und einen Befehl CMD übertragen, welche von dem Speichercontroller 40 empfangen werden, durch ein Empfangen verschiedener Wortleitungsspannungen VWLs von dem Spannungserzeuger 700. Der Spannungserzeuger 700 kann die Wortleitungsspannung VWLs für den Adressdecoder 600 und eine Löschspannung VERS für die Speicherzellanordnung 100 in Antwort auf Steuersignale CTLs, welche von der Steuerschaltung 500 empfangen werden, vorsehen.

**[0037]** **Fig. 5** ist ein Blockschaltbild, welches die Speicherzellanordnung in **Fig. 4** gemäß einigen Ausführungsformen veranschaulicht.

**[0038]** Bezug nehmend auf **Fig. 5** kann die Speicherzellanordnung 100 eine Mehrzahl von Speicherblöcken BLK1 bis BLKz aufweisen, welche sich in einer ersten bis dritten Richtung D1, D2 und D3 erstrecken. In einer Ausführungsform werden die Speicherblöcke BLK1 bis BLKz durch den Adressdecoder 600 in **Fig. 4** ausgewählt. Beispielsweise kann der Adressdecoder 600 einen Speicherblock BLK, welcher einer Blockadresse aus den Speicherblöcken BLK1 bis BLKz entspricht, auswählen. Der Adressdecoder 600 kann wenigstens einen Unterblock in einem Speicherblock in Antwort auf eine Zeilenadresse R\_ADDR auswählen.

**[0039]** **Fig. 6** ist eine perspektivische Ansicht, welche einen der Speicherblöcke der **Fig. 5** gemäß einigen Ausführungsformen veranschaulicht.

**[0040]** Bezug nehmend auf **Fig. 6** weist ein Speicherblock BLKa Strukturen auf, welche sich entlang der ersten bis dritten Richtung D1-D3 erstrecken.

**[0041]** Ein Substrat 111 ist vorgesehen. Beispielsweise kann das Substrat 111 einen p-Trog beziehungsweise eine p-Mulde aufweisen, welche durch ein Implantieren eines Gruppe-3-Elements wie beispielsweise Bor (B) gebildet wird. Beispielsweise kann das Substrat 111 eine Taschen-p-Mulde haben, welche in einer n-Mulde vorgesehen ist. In einer Ausführungsform hat das Substrat 111 eine p-Typ-Mulde (oder eine p-Typ-Taschenmulde). Der leitfähige Typ des Substrats 111 ist jedoch nicht auf den p-Typ beschränkt.

**[0042]** Eine Mehrzahl von Dotierungsbereichen 311 bis 314, welche sich entlang der ersten Richtung D1 erstreckt, ist in/auf dem Substrat 111 vorgesehen. Beispielsweise kann die Mehrzahl von Dotierungsbereichen 311 bis 314 einen zweiten Typ (beispielsweise einen zweiten leitfähigen Typ) unterschiedlich von dem ersten Typ des Substrats 111 haben. In einigen Ausführungsformen haben der erste bis vierte Dotierungsbereich 311 bis 314 einen n-Typ. Der leit-

fähige Typ des ersten bis vierten Dotierungsbereichs 311 bis 314 ist jedoch nicht auf den n-Typ beschränkt.

**[0043]** Eine Mehrzahl von Isoliermaterialien 112, welche sich entlang der zweiten Richtung D2 erstreckt, ist nacheinander folgend entlang der dritten Richtung D3 auf einen Bereich des Substrats 111 zwischen dem ersten und zweiten Dotierungsbereich 311 und 312 vorgesehen. Beispielsweise ist die Mehrzahl von Isoliermaterialien 112 entlang der dritten Richtung D3 durch einen spezifischen Abstand beabstandet vorgesehen. Beispielsweise können die Isoliermaterialien 112 ein Isoliermaterial wie beispielsweise eine Oxidschicht aufweisen.

**[0044]** Eine Mehrzahl von Säulen 113, welche die Isoliermaterialien entlang der dritten Richtung D3 durchdringen, sind nacheinander folgend entlang der zweiten Richtung D2 auf einem Bereich des Substrats 111 zwischen dem ersten und zweiten Dotierungsbereich 311 und 312 angeordnet. Beispielsweise durchdringt die Mehrzahl von Säulen 113 die Isoliermaterialien 112, um das Substrat 111 zu kontaktieren.

**[0045]** Beispielsweise kann jede Säule 113 eine Mehrzahl von Materialien aufweisen. Beispielsweise kann eine Kanalschicht 114 jeder Säule 113 ein Siliziummaterial aufweisen, welches einen ersten Typ hat. Beispielsweise kann die Kanalschicht 114 jeder Säule 113 ein Siliziummaterial aufweisen, welches denselben Typ wie das Substrat 111 hat. In einigen Ausführungsformen kann die Kanalschicht 114 jeder Säule 113 ein p-Typ-Silizium aufweisen. Die Kanalschicht 114 jeder Säule 113 ist jedoch nicht auf das p-Typ-Silizium beschränkt.

**[0046]** Ein Innenmaterial 115 jeder Säule 113 weist ein Isoliermaterial auf. Beispielsweise kann das Innenmaterial 115 jeder Säule 113 ein Isoliermaterial wie beispielsweise ein Siliziumoxid aufweisen. Beispielsweise kann das Innenmaterial 115 jeder Säule 113 einen Luftspalt aufweisen.

**[0047]** Eine Isolierschicht 116 ist entlang der freiliegenden Oberflächen der Isoliermaterialien 112, der Säulen 113 und des Substrats 111 auf einem Bereich zwischen dem ersten und dem zweiten Dotierungsbereich 311 und 312 vorgesehen. Beispielsweise kann die Isolierschicht 116, welche auf der freiliegenden Oberfläche in der dritten Richtung D3 des letzten Isoliermaterials 112 vorgesehen ist, entfernt sein.

**[0048]** Eine Mehrzahl von ersten leitfähigen Materialien 211 bis 291 ist zwischen zweiten Dotierungsbereichen 311 und 312 auf den freiliegenden Oberflächen der Isolierschicht 116 vorgesehen. Beispielsweise ist das erste leitfähige Material 211, welches sich entlang der zweiten Richtung D2

erstreckt, zwischen dem Substrat 111 und dem Isoliermaterial 112 benachbart zu dem Substrat 111 vorgesehen.

**[0049]** Ein erstes leitfähiges Material, welches sich entlang der ersten Richtung D1 erstreckt, ist zwischen der Isolierschicht 116 an der Oberseite eines spezifischen Isoliermaterials aus den Isoliermaterialien 112 und der Isolierschicht 116 an dem Boden eines spezifischen Isoliermaterials unter den Isoliermaterialien 112 vorgesehen. Beispielsweise ist eine Mehrzahl von ersten leitfähigen Materialien 221 bis 281, welche sich entlang der ersten Richtung D1 erstreckt, zwischen den Isoliermaterialien 112 vorgesehen und es kann verstanden werden, dass die Isolierschicht 116 zwischen den Isoliermaterialien 112 und den ersten leitfähigen Materialien 221 bis 281 vorgesehen ist. Die Mehrzahl von ersten leitfähigen Materialien 211 bis 291 kann ein metallisches Material aufweisen. Die Mehrzahl von ersten leitfähigen Materialien 211 bis 291 können ein leitfähiges Material wie beispielsweise Polysilizium aufweisen.

**[0050]** Ähnliche Strukturen wie diejenigen auf dem ersten und zweiten Dotierungsbereich 311 und 312 können in einem Bereich zwischen dem zweiten und dritten Dotierungsbereich 312 und 313 vorgesehen sein. In dem Bereich zwischen dem zweiten und dritten Dotierungsbereich 312 und 313 ist eine Mehrzahl von Isoliermaterialien 112 vorgesehen, welche sich entlang der ersten Richtung D1 erstreckt, eine Mehrzahl von Säulen 113, welche nacheinander folgend entlang der ersten Richtung D1 angeordnet ist, und die Mehrzahl von Isoliermaterialien 112 entlang der dritten Richtung D3 durchdringt, eine Isolierschicht 116, welche auf den freiliegenden Oberflächen der Mehrzahl von Isoliermaterialien 112 und der Mehrzahl von Säulen 113 vorgesehen ist, und eine Mehrzahl von dritten leitfähigen Materialien 213 bis 293, welche sich entlang der ersten Richtung D1 erstreckt.

**[0051]** In einem Bereich zwischen dem dritten und vierten Dotierungsbereich 313 und 314 können ähnliche Strukturen wie diejenigen auf dem ersten und zweiten Dotierungsbereich 311 und 312 vorgesehen sein. In dem Bereich zwischen dem dritten und vierten Dotierungsbereich 313 und 314 ist eine Mehrzahl von Isoliermaterialien 112 vorgesehen, welche sich entlang der ersten Richtung D1 erstreckt, eine Mehrzahl von Säulen 113, welche nacheinander folgend entlang der ersten Richtung D1 angeordnet ist, und die Mehrzahl von Isoliermaterialien 112 entlang der dritten Richtung D3 durchdringt, eine Isolierschicht 116, welche auf den freiliegenden Oberflächen der Mehrzahl von Isoliermaterialien 112 und der Mehrzahl von Säulen 113 vorgesehen ist, und eine Mehrzahl von dritten leitfähigen Materialien 213 bis 293, welche sich entlang der ersten Richtung D1 erstreckt.

**[0052]** Drains 320 sind auf der Mehrzahl von Säulen 113 jeweils vorgesehen. Auf den Drains sind die zweiten leitfähigen Materialien 331 bis 333, welche sich entlang der ersten Richtung D1 erstrecken, vorgesehen. Die zweiten leitfähigen Materialien 331 bis 333 sind entlang der zweiten Richtung D2 durch einen spezifischen Abstand beabstandet angeordnet. Die zweiten leitfähigen Materialien 331 bis 333 sind jeweils mit den Drains 320 in einem entsprechenden Bereich verbunden. Die Drains 320 und das zweite leitfähige Material 333, welches sich entlang der ersten Richtung D1 erstreckt, können über jeweilige Kontaktstecker verbunden sein.

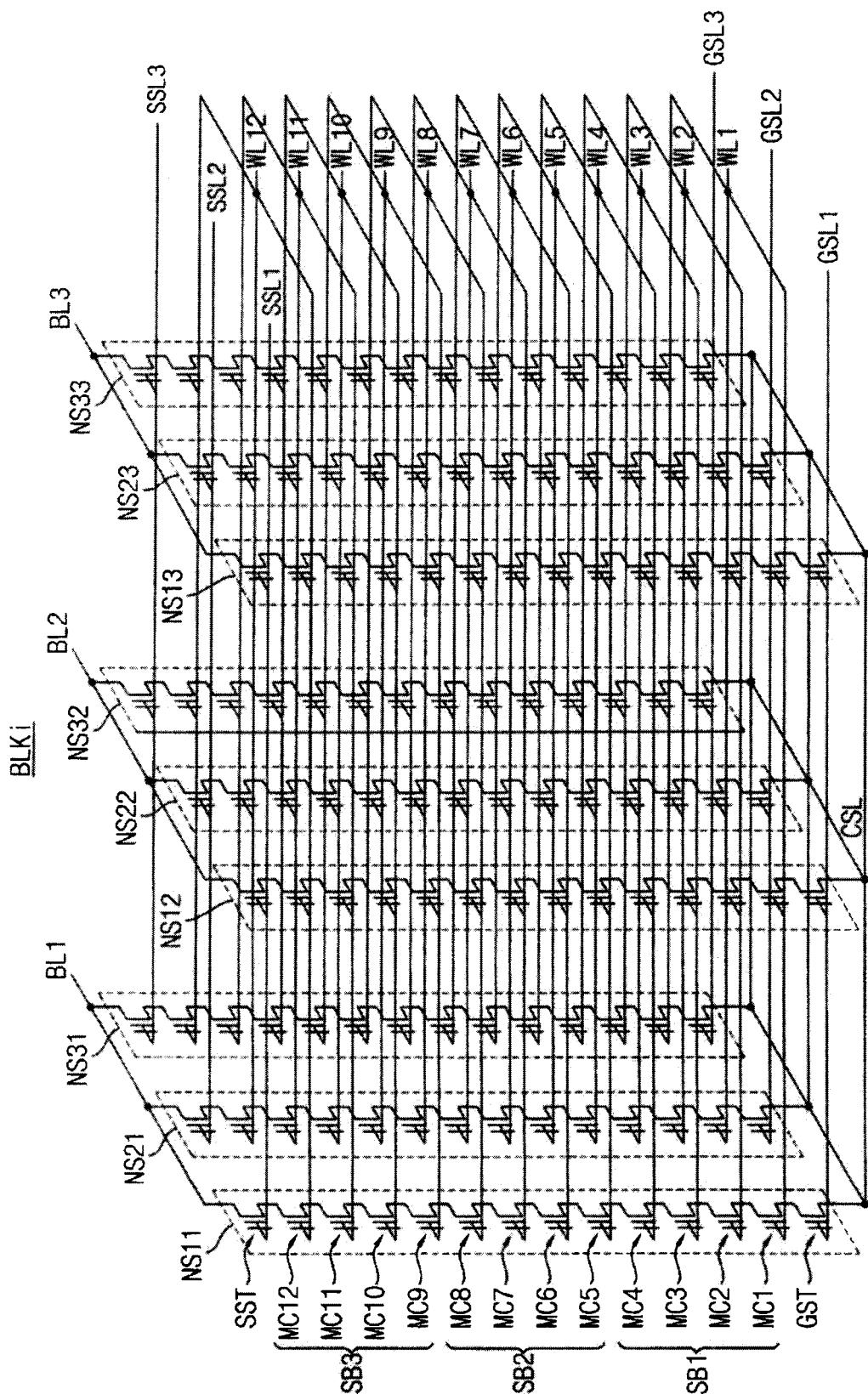

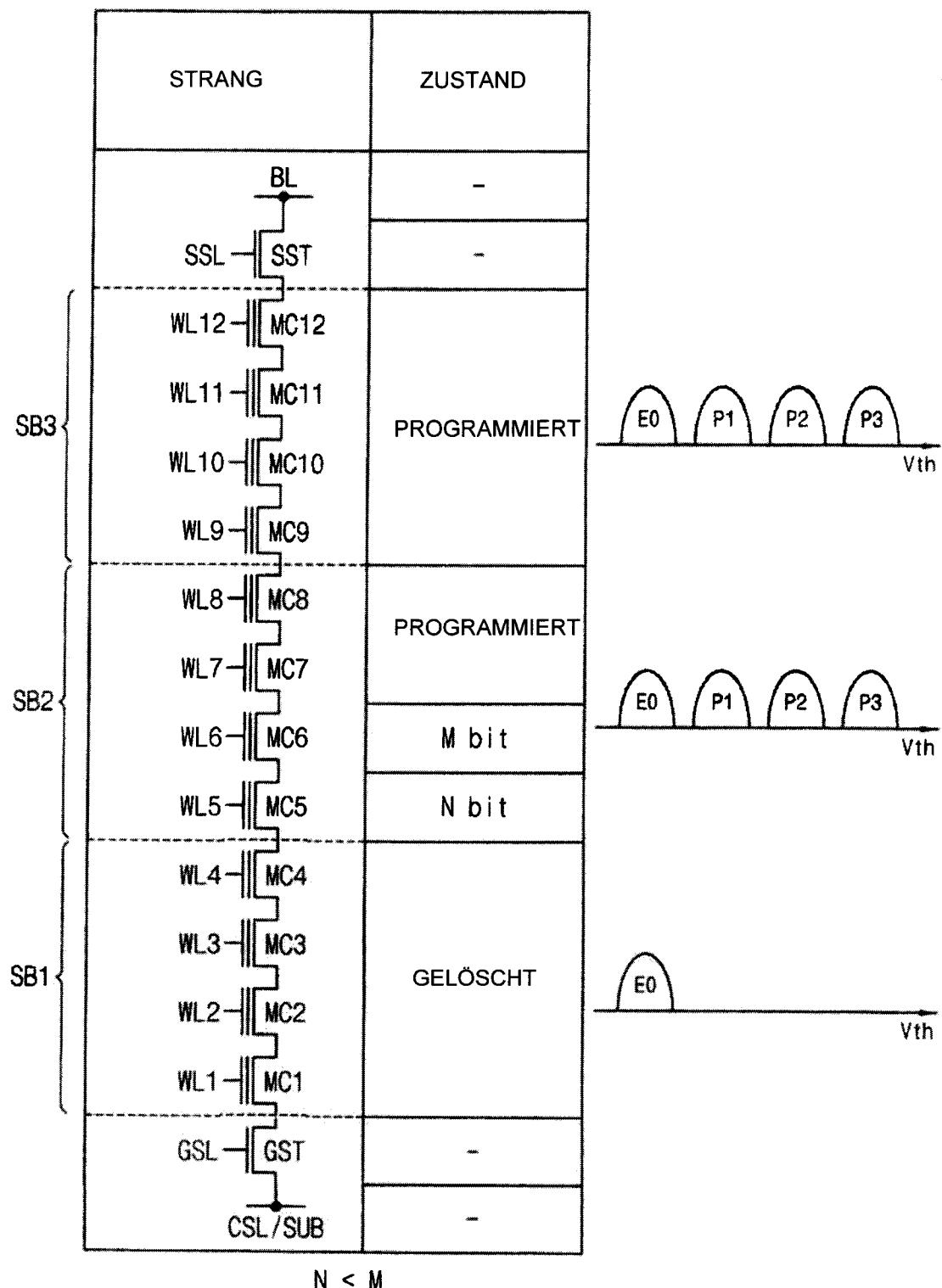

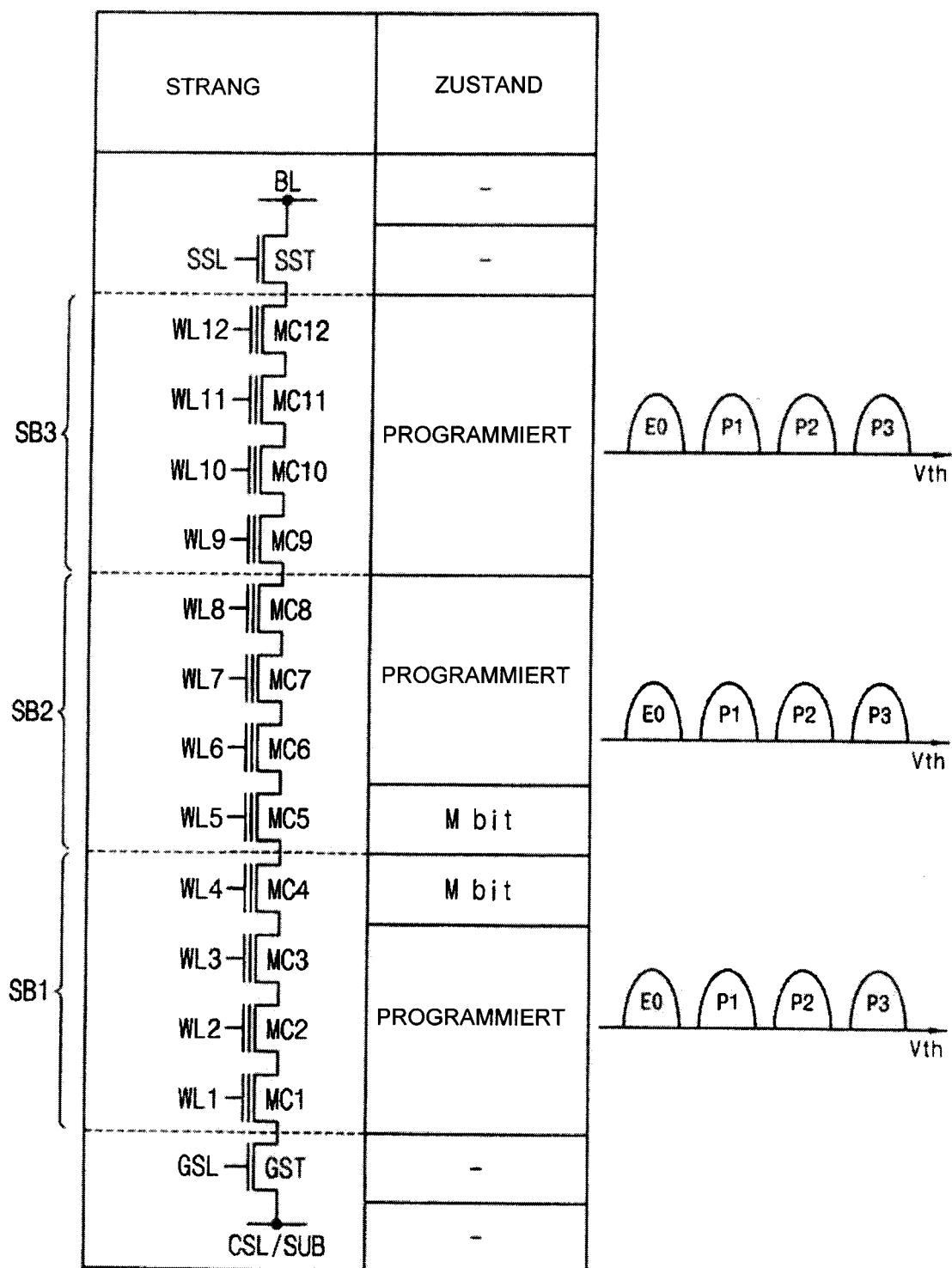

**[0053]** **Fig. 7** ist ein Ersatzschaltbild, welches den Speicherblock der **Fig. 6** gemäß einigen Ausführungsformen veranschaulicht.

**[0054]** Der Speicherblock BLKi der **Fig. 7** kann auf einem Substrat in einer dreidimensionalen Struktur (oder einer vertikalen Struktur) gebildet sein. Beispielsweise kann eine Mehrzahl von Speicherzellsträngen, welche in dem Speicherblock BLKi enthalten ist, in einer Richtung rechtwinklig zu dem Substrat gebildet sein.

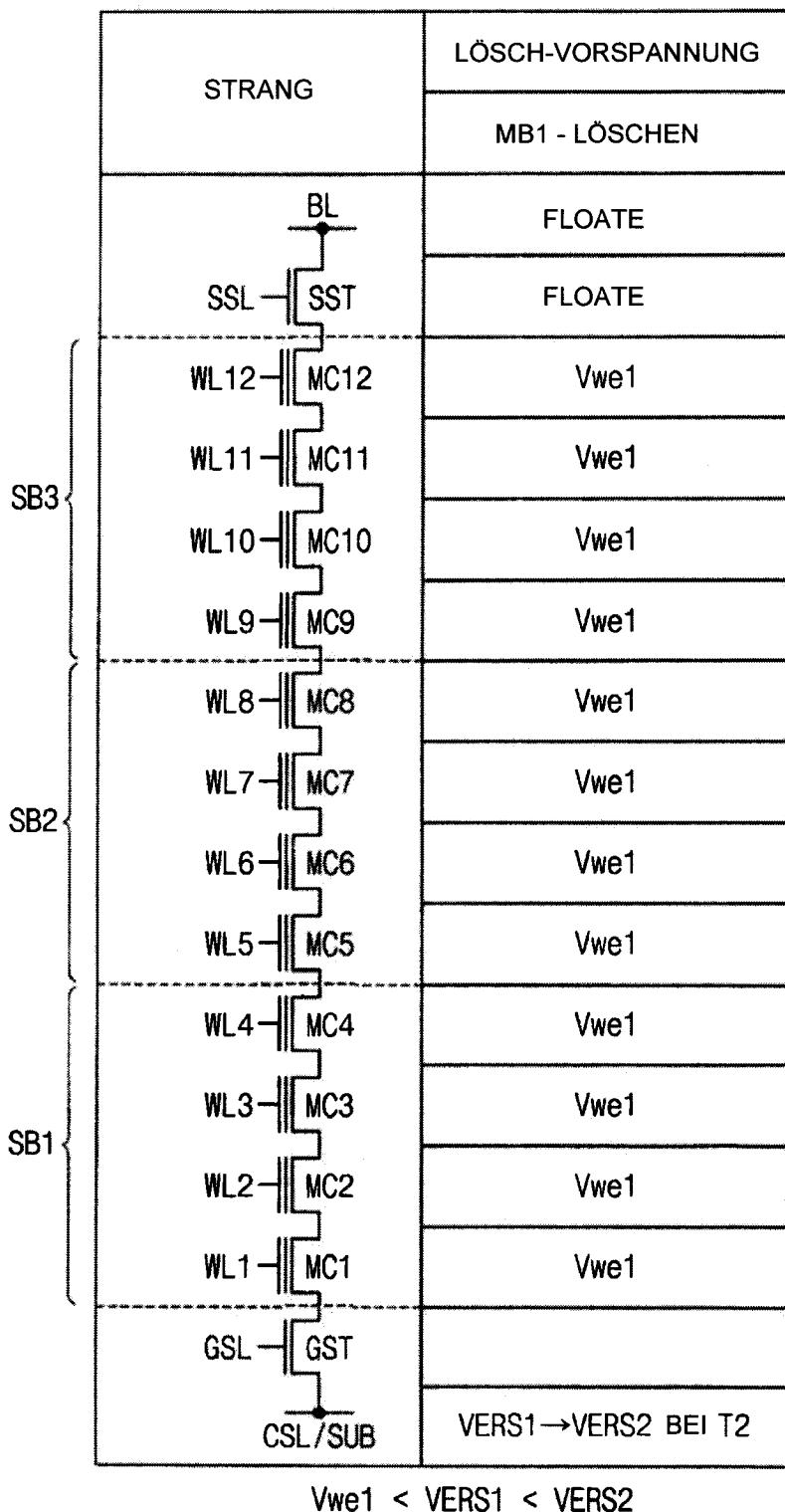

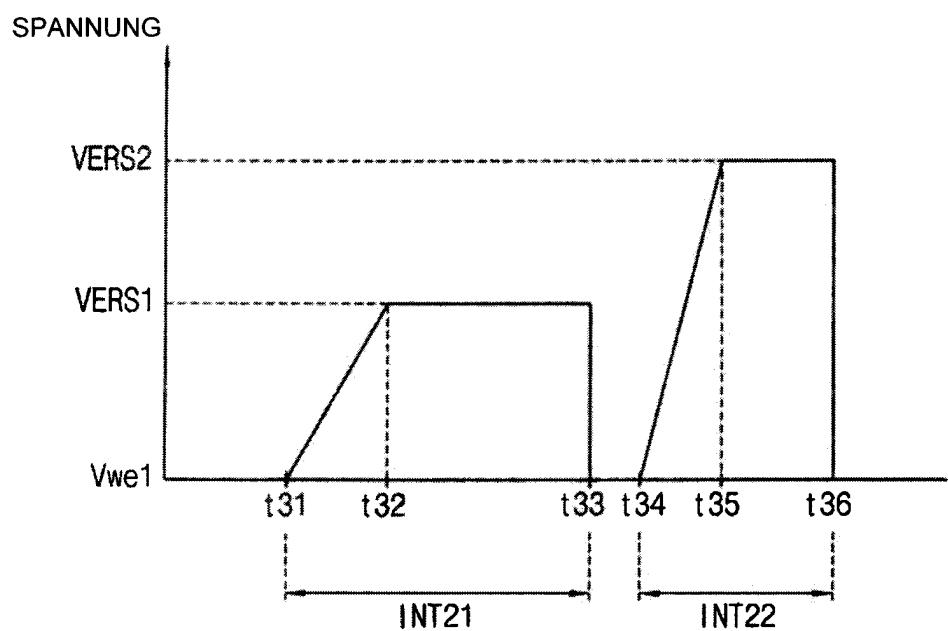

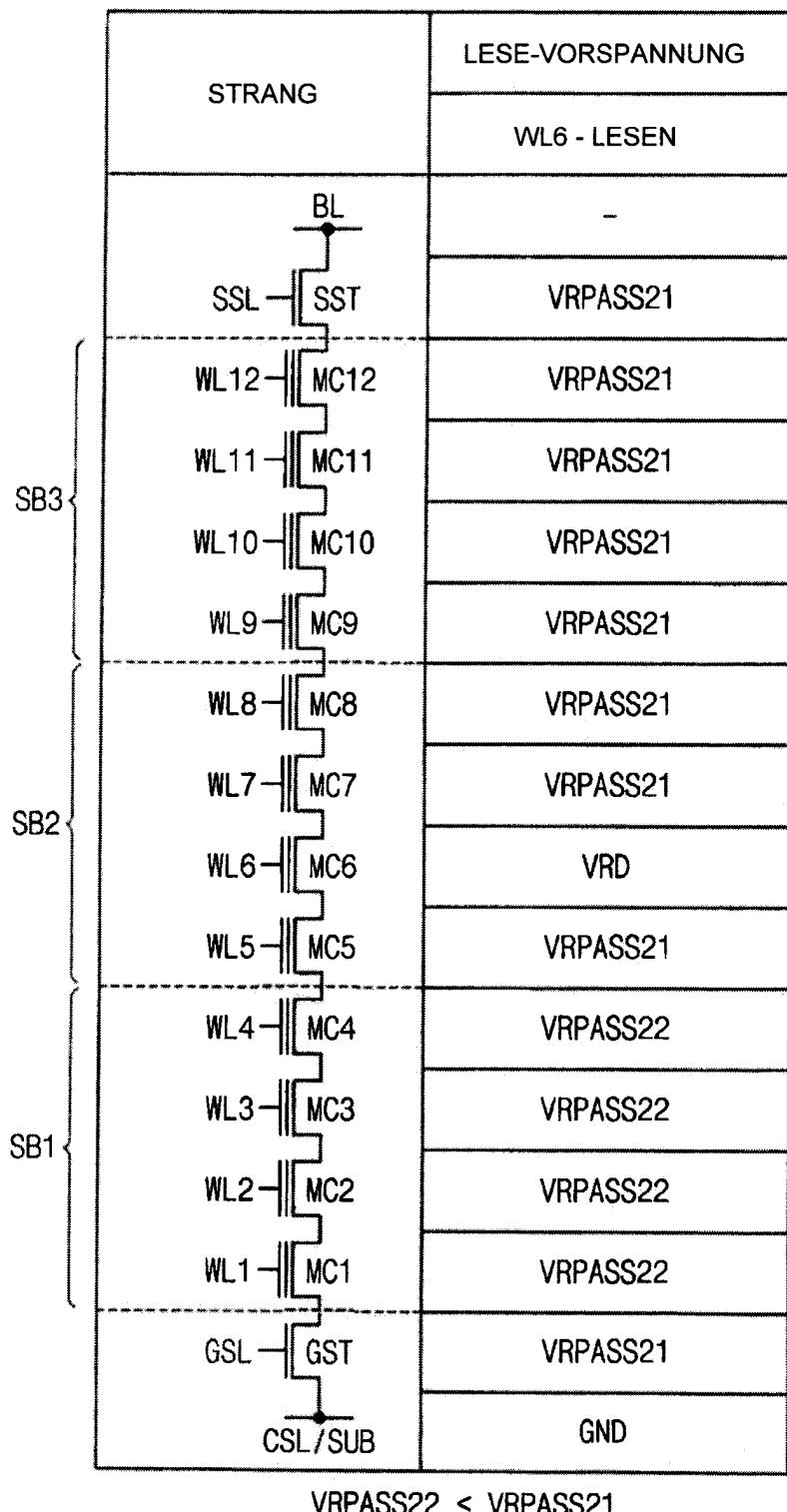

**[0055]** Bezug nehmend auf **Fig. 7** kann der Speicherblock BLKi Speicherzellstränge NS11 bis NS33, welche zwischen Bitleitungen BL1, BL2 und BL3 und einer gemeinsamen Sourceleitung CSL gekoppelt sind, aufweisen. Jeder der Speicherzellstränge NS11 bis NS33 kann einen Strangauswahltransistor SST, eine Mehrzahl von Speicherzellen MC1 bis MC12 und einen Masseauswahltransistor GST aufweisen. In **Fig. 7** ist jeder der Speicherzellstränge NS11 bis NS33 veranschaulicht, um zwölf Speicherzellen MC1 bis MC12 aufzuweisen. Einige Ausführungsformen jedoch sind nicht darauf beschränkt. In einigen Ausführungsformen kann jeder der Speicherzellstränge NS11 bis NS33 eine beliebige Anzahl von Speicherzellen aufweisen.

**[0056]** Der Strangauswahltransistor SST kann mit entsprechenden Strangauswahlleitungen SSL1 bis SSL3 verbunden sein. Die Mehrzahl von Speicherzellen MC1 bis MC12 kann jeweils mit entsprechenden Wortleitungen WL1 bis WL12 verbunden sein. Der Masseauswahltransistor GST kann mit entsprechenden Masseauswahlleitungen GSL1 bis GSL3 verbunden sein. Der Strangauswahltransistor SST kann mit entsprechenden Bitleitungen BL1, BL2 und BL3 verbunden sein, und der Masseauswahltransistor GST kann mit der gemeinsamen Sourceleitung CSL verbunden sein.

**[0057]** In beispielhaften Ausführungsformen können Dummy-Speicherzellen, welche mit einer Dummy-Wortleitung (nicht gezeigt) verbunden sind, zwischen dem Strangauswahltransistor SST und der Speicherzelle MC12 gekoppelt sein und/oder zwischen dem

Masseauswahltransistor GST und der Speicherzelle MC1 gekoppelt sein. Beispielsweise können Dummy-Speicherzellen simultan mit normalen Speicherzellen mit demselben Prozess gebildet werden. Eine Dummy-Speicherzelle kann durch eine Dummy-Wortleitung aktiviert werden, aber kann keine „Daten“ gespeichert haben, um von einer externen Vorrichtung zu lesen. Beispielsweise können Daten, welche in einer Dummy-Speicherzelle gespeichert sind, welche elektrisch mit einer Dummy-Wortleitung verbunden ist, nicht nach außerhalb der Speicherzellanordnung über Auswahlsignale übertragen werden, welche durch den Spaltendecoder vorgesehen sind, wie es manchmal der Fall für normale Speicherzellen ist. Beispielsweise kann eine Dummy-Speicherzelle, welche elektrisch mit einer Dummy-Wortleitung verbunden ist, keine Verbindung zu einer Bitleitung haben, um Daten dazwischen zu übertragen wie bei normalen Speicherzellen.

**[0058]** Wortleitungen (beispielsweise WL1), welche dieselbe Höhe haben, können gemeinsam verbunden sein, und die Masseauswahlleitungen GSL1 bis GSL3 und die Strangauswahlleitungen SSL1 bis SSL3 können getrennt sein. In **Fig. 7** ist der Speicherblock BLKa veranschaulicht, um mit zwölf Wortleitungen WL1 bis WL12 und drei Bitleitungen BL1 bis BL3 gekoppelt zu sein. Einige Ausführungsformen sind jedoch nicht darauf beschränkt. In einigen Ausführungsformen kann die Speicherzellanordnung 100 mit einer beliebigen Anzahl von Wortleitungen und Bitleitungen gekoppelt sein.

**[0059]** Gemäß einigen Ausführungsformen ist der Speicherblock BLKi in eine Mehrzahl von Unterblöcken unterteilt, welche durch repräsentative Unterblöcke SB1, SB2 und SB3 angezeigt werden, wobei jeder Unterblock kleiner in der Größe ist als der Speicherblock BLKi. Die Unterblöcke SB1, SB2 und SB3 können in einer Wortleitungsrichtung unterteilt sein, wie in **Fig. 7** gezeigt ist. In einigen Ausführungsformen können die Unterblöcke SB1, SB2 und SB3 auf der Basis von Bitleitungen oder Strangauswahlleitungen unterteilt sein. Die Unterblöcke SB1, SB2 und SB3 in dem Speicherblock BLKa können unabhängig von der Referenz, welche verwendet wird, um die Speicherblöcke BLKa in Unterblöcke zu unterteilen, gelöscht werden.

**[0060]** Beispielsweise weist der Unterblock SB1 Speicherzellen auf, welche mit den Wortleitungen WL1, WL2, WL3 und WL4 gekoppelt sind, der Unterblock SB2 weist Speicherzellen auf, welche mit den Wortleitungen WL5, WL6, WL7 und WL8 gekoppelt sind, und der Unterblock SB3 weist Speicherzellen auf, welche mit den Wortleitungen WL9, WL10, WL11 und WL12 aus inmitten der Speicherzellen gekoppelt sind, welche in dem Speicherblock BLKa enthalten sind. Die Speicherzellen, welche in dem

Unterblock SB1 enthalten sind, können unabhängig von den verbleibenden Unterblöcken SB2 und SB3 ausgewählt und gelöscht werden und umgekehrt. Einer oder mehrere der Unterblöcke SB1, SB2 und SB3 können zu derselben Zeit oder zu unterschiedlichen Zeiten ausgewählt werden und gelöscht werden. Der Adressdecoder 600 der nichtflüchtigen Speichervorrichtung 50 (es sei Bezug genommen auf **Fig. 4**) kann eine Vorspannung zum Löschen von Speicherzellen durch Unterblockeinheiten vorsehen.

**[0061]** Zurückverweisend auf **Fig. 4** kann die Steuerschaltung 500 den Befehl (Signal) CMD und die Adresse (Signal) ADDR von dem Speichercontroller 40 empfangen und eine Löschungsoperation, eine Programmieroperation und eine Leseoperation der nichtflüchtigen Speichervorrichtung 50 basierend auf dem Befehlssignal CMD und dem Adresssignal ADDR steuern.

**[0062]** In beispielhaften Ausführungsformen kann die Steuerschaltung 500 der **Fig. 4** die Steuersignale CTLs erzeugen, welche zum Steuern des Spannungserzeugers 700 verwendet werden und kann das Seitenpuffersteuersignal PBC zum Steuern der Seitenpufferschaltung 410 basierend auf dem Befehlssignal CMD und eine Zeilenadresse R\_ADDR und eine Spaltenadresse C\_ADDR basierend auf dem Adresssignal ADDR erzeugen. Die Steuerschaltung 500 der **Fig. 4** kann die Zeilenadresse R\_ADDR für den Adressdecoder 600 vorsehen und die Spaltenadresse C\_ADDR für die Dateneingangs-/Ausgangsschaltung 420 vorsehen. Zusätzlich kann die Steuerschaltung 500 den Adressdecoder 600 mit einem ersten Modussignal MS 1 in Antwort auf ein Erfassungssignal DS, welches von der Substratüberwachungsschaltung 430 vorgesehen ist, vorsehen. Das erste Modussignal MS 1 zeigt an, dass ein Spannungspegel des Substrats 111 einen Referenzpegel erreicht oder zeigt an, dass der Spannungspegel des Substrats 111 auf einem konstanten Pegel während eines Referenzzeitintervalls aufrechterhalten wird. Zusätzlich kann die Steuerschaltung 500 den Adressdecoder 600 mit einem zweiten Modussignal MS2 vorsehen, welches eine Operation, welche durch den Befehl SMD bezeichnet wird, anzeigt.

**[0063]** Der Adressdecoder 600 der **Fig. 4** kann mit der Speicherzellanordnung 100 über die Strangauswahlleitung SSL, die Mehrzahl von Wortleitungen WLs und die Masseauswahlleitung GSL gekoppelt sein. Der Spannungserzeuger 700 kann die Wortleitungsspannungen VBLs, welche für den Betrieb der nichtflüchtigen Speichervorrichtung 50 benötigt werden, basierend auf den Steuersignalen CTLs erzeugen. Der Spannungserzeuger 700 kann die Leistung PWR von dem Speichercontroller 40 empfangen. Die Wortleitungsspannungen VWLs können an die Mehr-

zahl von Wortleitungen WLs über den Adressdecoder 600 angelegt werden.

**[0064]** Beispielsweise kann während der Unterblocklöschoperation der Spannungserzeuger 700 die Löschspannung VERS an eine Mulde beziehungsweise einen Topf des Speicherblocks oder des Substrats 111 anlegen und kann eine Wortleitungslöschspannung (beispielsweise eine Massespannung) an Wortleitungen von einem ausgewählten Unterblock anlegen. Während der Löschverifikationsoperation kann der Spannungserzeuger 700 eine Löschverifikationsspannung an die gesamten Wortleitungen des ausgewählten Unterblocks anlegen oder die Löschverifikationsspannung nacheinander folgend an Wortleitungen des ausgewählten Unterblocks auf einer Wortleitungsbasis anlegen.

**[0065]** Beispielsweise kann während der Programmieroperation der Spannungserzeuger 700 eine Programmierspannung an die ausgewählte Wortleitung anlegen und kann eine Programmierpassierspannung an die unausgewählten Wortleitungen anlegen. Zusätzlich kann während der Programmierverifikationsoperationen der Spannungserzeuger 700 eine Programmierverifikationsspannung an die ausgewählte Wortleitung anlegen und kann eine Verifikationspassierspannung an die unausgewählten Wortleitungen anlegen. Zusätzlich kann während der Leseoperation der Spannungserzeuger 700 eine Lesespannung an die ausgewählte Wortleitung anlegen und kann eine Lesepassierspannung an die nicht ausgewählten Wortleitungen anlegen.

**[0066]** Die Seitenpufferschaltung 410 kann mit der Speicherzellanordnung 100 über die Mehrzahl von Bitleitungen BLs gekoppelt sein. Die Seitenpufferschaltung 410 kann eine Mehrzahl von Seitenpuffern aufweisen. In einigen Ausführungsformen kann ein Seitenpuffer mit einer Bitleitung verbunden sein. In einigen Ausführungsformen kann ein Seitenpuffer mit zwei oder mehreren Bitleitungen verbunden sein.

**[0067]** Die Seitenpufferschaltung 410 kann vorübergehend Daten speichern, welche in eine ausgewählte Seite zu programmieren sind, oder Daten, welche von der ausgewählten Seite der Speicherzellanordnung 100 ausgelesen werden. Die Seitenpufferschaltung 410 kann eine Mehrzahl von Seitenpuffern aufweisen. Die Seitenpufferschaltung 410 kann vorübergehend Daten speichern, welche in eine ausgewählte Seite zu programmieren sind, und kann vorübergehend Daten, welche aus der ausgewählten Seite gelesen sind, speichern.

**[0068]** Die Dateneingangs-/Ausgangsschaltung 420 kann mit der Seitenpufferschaltung 410 über Datenleitungen DLs gekoppelt sein. Während der Programmieroperation kann die Dateneingangs-/Aus-

gangsschaltung 420 Programmierdaten DATA von dem Speichercontroller 40 empfangen und die Programmierdaten DATA für die Seitenpufferschaltung 410 basierend auf der Spaltenadresse C\_ADDR, welche von der Steuerschaltung 500 empfangen wird, vorsehen. Während der Leseoperation kann die Dateneingangs-/Ausgangsschaltung 420 Lese daten DATA, welche in der Seitenpufferschaltung 410 gespeichert sind, für den Speichercontroller 40 basierend auf der Spaltenadresse C\_ADDR, welche von der Steuerschaltung 500 empfangen wird, vorsehen.

**[0069]** Während der Löschoperation kann die Substratüberwachungsschaltung 430 einen Spannungspegel einer Substratspannung (oder einen Spannungspegel des Substrats 111) VSUB in Antwort auf die Löschspannung VERS, welche an das Substrat angelegt wird, überwachen und kann die Steuerschaltung 500 mit dem Erfassungssignal DS vorsehen, welches anzeigt, dass ein Pegel der Substratspannung VSUB einen Referenzpegel erreicht und/oder anzeigt, dass der Pegel der Substratspannung VSUB auf einem Pegel der Löschspannung VERS während eines Referenzzeitintervalls aufrechterhalten wird.

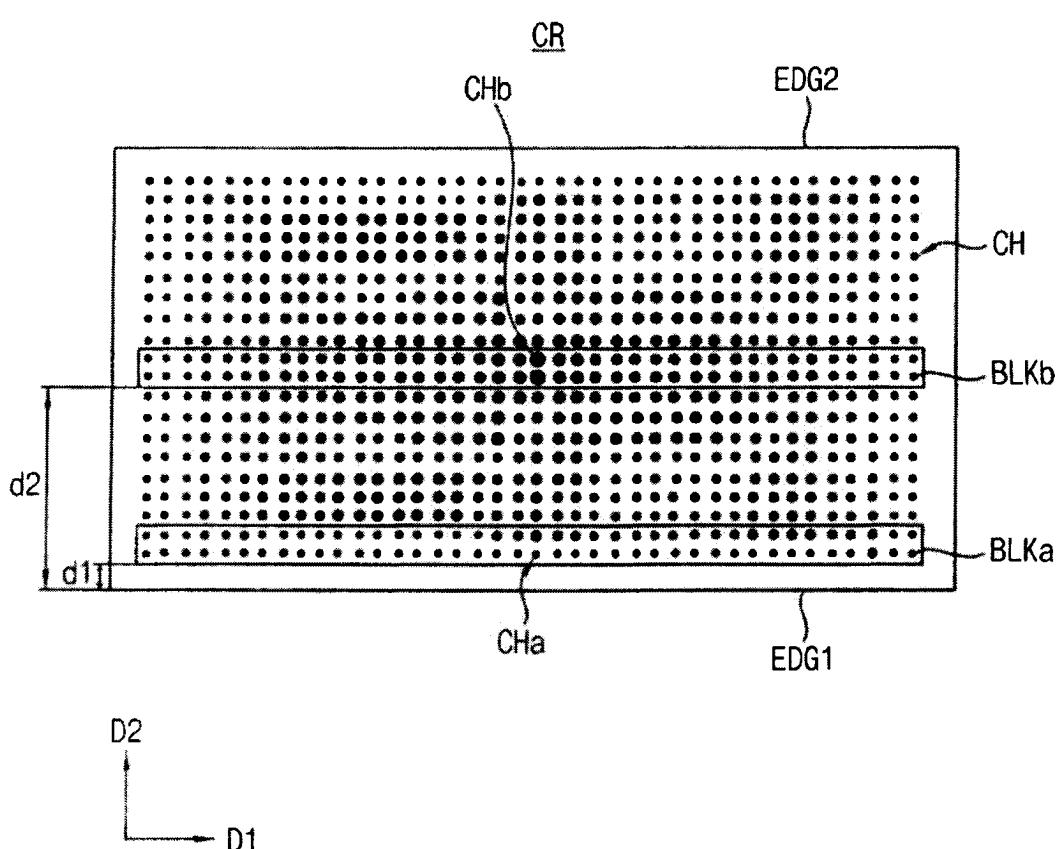

**[0070]** **Fig. 8** veranschaulicht einen Zellbereich, in welchem die Speicherzellanordnung der **Fig. 4** gemäß einigen Ausführungsformen gebildet ist.

**[0071]** Bezug nehmend auf **Fig. 8** weist ein Zellbereich CR eine Mehrzahl von Kanallöchern CH auf.

**[0072]** Eine Kanallochgröße, beispielsweise ein Kanallochdurchmesser, kann gemäß Positionen innerhalb des Zellbereichs CR variiert werden. Beispielsweise haben Kanallöcher CH benachbart zu dem ersten und zweiten Rand EDG1 und EDG2 eine niedrige Umfangsdichte und können demnach einen unterschiedlichen Durchmesser von demjenigen von anderen Kanallöchern CH haben. Ein Speicherblock BLKa kann benachbart zu dem zweiten Rand EDG2 sein und kann von dem zweiten Rand EDG2 durch einen ersten Abstand d1 beabstandet sein. Ein Speicherblock BLKb kann nicht benachbart zu dem ersten und dem zweiten Rand EDG1 und EDG2 sein und in einer Mitte des Zellbereichs CR sein und kann von dem zweiten Rand EDG2 durch einen zweiten Abstand d2 beabstandet sein. Der zweite Abstand d2 kann größer sein als der erste Abstand d1. Ein erster Durchmesser D1 eines ersten Kanallochs CHa, welches in dem Speicherblock BLKa enthalten ist, kann kleiner sein als ein zweiter Durchmesser D2 eines zweiten Kanallochs CHb, welches in dem Speicherblock BLKb enthalten ist.

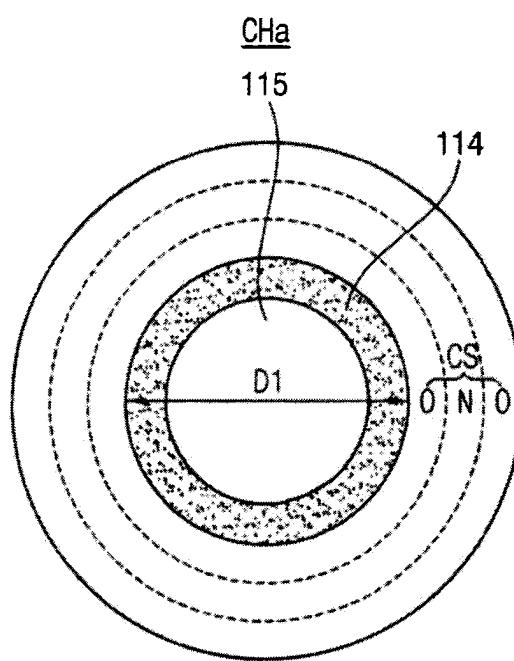

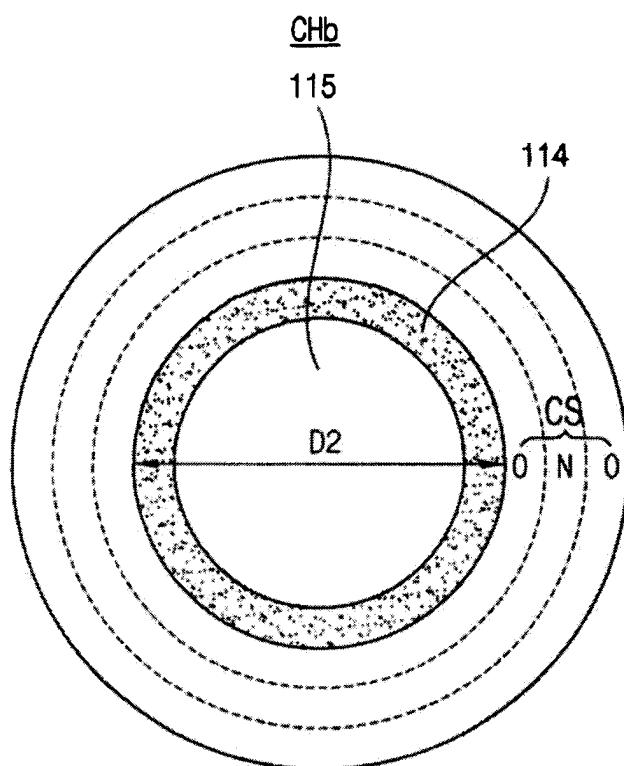

**[0073]** Die **Fig. 9A** und **Fig. 9B** veranschaulichen jeweils Querschnitte von Strängen der Speicherblöcke BLKa und BLKb der **Fig. 8**.

**[0074]** Bezug nehmend auf **Fig. 9A** können eine Säule, welche eine Kanalschicht 114 und eine interne Schicht 115 aufweist, in dem ersten Kanaloch CHa, welches in dem Speicherblock BLKa enthalten ist, gebildet werden, und eine Ladungsspeicherschicht CS kann um das erste Kanaloch CHa herum gebildet werden und die Ladungsspeicherschicht CS kann eine (Oxid-Nitrid-Oxid)ONO-Struktur haben.

**[0075]** Bezug nehmend auf **Fig. 9B** kann eine Säule, welche eine Kanalschicht 114 und eine interne Schicht 115 aufweist, in dem zweiten Kanaloch CHb, welches in dem Speicherblock BLKb enthalten ist, gebildet werden, und eine Ladungsspeicherschicht CS kann um das zweite Kanaloch CHb herum gebildet werden, und die Ladungsspeicherschicht CS kann eine ONO-Struktur haben.

**[0076]** In einer beispielhaften Ausführungsform kann eine Dicke der Ladungsspeicherschicht CS, welche in dem Speicherblock BLKb enthalten ist, unterschiedlich von einer Dicke der Ladungsspeicherschicht CS sein, welche in dem Speicherblock BLKa enthalten ist. Charakteristiken von Speicherzellen können aufgrund des Unterschieds in den Kanalochdurchmessern variieren. Beispielsweise wird in einer 3D-Speichervorrichtung, welche eine Gate-All-Around-Struktur hat, in welcher eine Gateelektrode um einen Umfang eines Kanallochs herum angeordnet ist, wenn ein Kanalochdurchmesser verringert wird, die Größe eines elektrischen Feldes, welches zwischen einer Gateelektrode (beispielsweise der Gateelektrode 211 der **Fig. 6**) und einem Kanalbereich 114 gebildet wird, erhöht. Demnach können Programmier- und Löschgeschwindigkeiten einer Speicherzelle, welche einen relativ kleinen Kanalochdurchmesser hat wie das erste Kanaloch CHa höher sein als diejenige in einer Speicherzelle, welche einen relativ großen Kanalochdurchmesser hat wie das zweite Kanaloch CHb.

**[0077]** Zurückverweisend auf **Fig. 8** ist der Speicherblock in dem Zellbereich CR gebildet, um alle Speicherzellen, welche einer Seite entsprechen, in der ersten Richtung D1 aufzuweisen, das heißt in einer Wortleitungsrichtung, und um einige Stränge in der zweiten Richtung D2 aufzuweisen, das heißt in einer Bitleitungsrichtung. Demnach erstreckt sich jeder Speicherblock in der ersten Richtung D1 und Kanalochgrößen, das heißt Kanalochdurchmesser können sich in Einheiten von Speicherblöcken unterscheiden. Demnach können Programmier- und Löschgeschwindigkeiten von Speicherzellen, welche in dem Speicherblock BLKa enthalten sind, höher sein als Programmier- und Löschgeschwindigkeiten von Speicherzellen, welche in dem Speicherblock BLKb enthalten sind.

**[0078]** **Fig. 10** ist ein Graph, welcher ein Ergebnis des Durchführen einer Programmieroperation und einer Löschoperation auf den Speicherblöcken in **Fig. 8** zeigt.

**[0079]** Bezug nehmend auf **Fig. 10** bezeichnet eine horizontale Achse Positionen von Speicherblöcken in der zweiten Richtung D2, das heißt einer Bitleitungsrichtung, und eine vertikale Achse bezeichnet eine Schwellenspannung. Beispielsweise bezeichnet eine durchgezogene Linie 71 einen zentralen Wert von Schwellenspannungen gemäß Speicherblockpositionen einer programmierten Speicherzelle und eine gepunktete Linie 72 bezeichnet einen zentralen Wert der Schwellenspannungen gemäß Speicherblockpositionen einer gelöschten Speicherzelle.

**[0080]** Wie obenstehend beschrieben ist, kann die Schwellenspannungsverteilung, wie durch die durchgezogene Linie 71 angezeigt ist, von programmierten Speicherzeilen eine U-Form haben. Wie durch den U-förmigen Graphen angezeigt ist, kann eine Programmierung von Speicherzellen bei Speicherblockpositionen näher zu einem oberen und/oder unteren Rand der Speichervorrichtung eine höhere Schwellenspannung benötigen. Zusätzlich kann die Schwellenspannungsverteilung, wie durch die gepunktete Linie 72 angezeigt ist, von gelöschten Speicherzellen ein invertiertes U- haben. Wie durch den invertierten U-förmigen Graphen angezeigt, kann ein Löschen von Speicherzellen an Speicherblockpositionen näher einem oberen und/oder unteren Rand der Speichervorrichtung eine niedrigere Schwellenspannung benötigen.

**[0081]** **Fig. 11** veranschaulicht ein Beispiel einer vertikalen Struktur in **Fig. 8**.

**[0082]** Bezug nehmend auf **Fig. 11** ist ein Kanaloch CH1, welches einem Strang entspricht, welcher in einer 3D-Speichervorrichtung enthalten ist, veranschaulicht. Wie obenstehend beschrieben ist, ist das Kanaloch CH1 durch ein Ätzen von Abschnitten von Gateelektroden und Isolierschichten, welche auf einem Substrat gestapelt sind, gebildet, und demnach kann das Kanaloch CH1 ein konisches Ätzprofil sein, in dem ein Durchmesser des Kanallochs CH1 nach unten kleiner wird. Demnach kann ein Durchmesser des Kanallochs CH1 in Richtung des Substrats kleiner sein.

**[0083]** In einigen Ausführungsformen kann das Kanaloch CH1 in drei Zonen gemäß Kanalochdurchmessern unterteilt sein. Beispielsweise kann auf eine Zone, in welcher ein Kanalochdurchmesser kleiner ist als ein erster Wert Bezug genommen werden als eine erste Zone, und auf eine Zone, in welcher ein Kanalochdurchmesser gleich oder größer als der erste Wert ist und kleiner als ein zweiter Wert kann Bezug genommen werden als eine zweite

Zone, und auf eine Zone, in welcher ein Kanalochdurchmesser gleich oder größer als der zweite Wert ist und kleiner als ein dritter Wert kann Bezug genommen werden als eine dritte Zone. Die erste Zone entspricht dem Unterblock SB1, die zweite Zone entspricht dem Unterblock SB2 und die dritte Zone entspricht dem Unterblock SB3. Demnach können Speicherzellen in einem Kanaloch unterschiedliche Charakteristiken aufgrund des Unterschieds von Durchmessern des Kanalochs gemäß Positionen von Unterblöcken haben. Demnach können Programmier- und Löschgeschwindigkeiten von Speicherzellen, welche in einem Kanaloch enthalten sind, gemäß Positionen von Unterblöcken unterschiedlich sein, wie in dem Graphen der **Fig. 10** angezeigt ist.

**[0084]** **Fig. 12** ist ein Blockschaltbild, welches ein Beispiel der Steuerschaltung in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß beispielhaften Ausführungsformen veranschaulicht.

**[0085]** Bezug nehmend auf **Fig. 12** kann eine Steuerschaltung 500a einen Befehlsdecoder 510, einen Adresspuffer 520, einen Steuersignalerzeuger 530a, einen Adresskomparator 540, ein Schlechtunterblockinformationsregister (BSIR) 550 und ein Programmier-/Lösch(P/E)-Zyklusinformationsregister 560 aufweisen.

**[0086]** Der Befehlsdecoder 510 decodiert den Befehl CMD und sieht einen decodierten Befehl D\_CMD für den Steuersignalerzeuger 530 vor. Der Adresspuffer 520 empfängt das Adresssignal ADDR, sieht die Zeilenadresse R\_ADDR für den Adressdecoder 600 und den Adresskomparator 540 vor und sieht die Spaltenadresse C\_ADDR für die Dateneingangs-/Ausgangsschaltung 420 vor.

**[0087]** Das Schlechtunterblockinformationsregister 550 kann die Schlechte-Unterblock-Information BSI speichern und die Schlechte-Unterblock-Information BSI kann anfängliche schlechte Unterblockadressen ITSBA und schlechte Laufzeit- Unterblockadressen RTSBA aufweisen. Die anfänglichen schlechten Unterblockadressen ITSBA sind Adressen von schlechten Unterblöcken, welche bezeichnet werden, wenn die nichtflüchtige Speichervorrichtung 50 versendet wird. Die schlechten Laufzeit-Unterblockadressen RTSBA sind Adressen von schlechten Unterblöcken, welche bezeichnet werden, wenn die nichtflüchtige Speichervorrichtung 50 arbeitet.

**[0088]** Der Adresskomparator 540 vergleicht die Zeilenadresse R\_ADDR mit wenigstens einer schlechten Unterblockzeilenadresse BR\_ADDR, welche in dem Schlechtunterblockinformationsregister 550 gespeichert ist, und sieht den Steuersignalerzeuger 530a mit einem Übereinstimmungssignal MTS vor, welches ein Ergebnis des Vergleichs der

Zeilenadresse R\_ADDR mit der wenigstens einen schlechten Unterblockzeilenadresse BR\_ADDR anzeigt.

**[0089]** Der Steuersignalerzeuger 530a empfängt den decodierten Befehl D\_CMD und das Übereinstimmungssignal MTS, erzeugt die Steuersignale CTLs basierend darauf ob eine Operation, welche durch den decodierten Befehl D\_CMD geleitet wird, mit dem schlechten Unterblock verbunden ist, und sieht die Steuersignale CTLs für den Spannungserzeuger 700 vor. Zusätzlich empfängt der Steuersignalerzeuger 530a das Erfassungssignal DS und sieht den Adressdecoder 600 mit dem ersten Modussignal MS 1 vor, welches anzeigt, dass der Pegel der Substratspannung VSUB den Referenzpegel erreicht oder dass der Pegel der Substratspannung VSUB auf einem bestimmten Pegel aufrechterhalten wird, basierend auf dem Erfassungssignal DS. Zusätzlich sieht der Steuersignalerzeuger 530a den Adressdecoder 600 mit dem zweiten Modussignal MS vor, welches die Operation anzeigt, welche durch den zweiten decodierten Befehl D\_CMD bezeichnet ist.

**[0090]** Wenn das Übereinstimmungssignal MTS anzeigt, dass die Zeilenadresse R\_ADDR auf den normalen Unterblock zugreift, erzeugt der Steuersignalerzeuger 530a die Steuersignale CTLs durch eine Bezugnahme auf das Programmier-/Lösch-Zyklus-Informationsregister 560 derart, dass ein erster Programmier-/Lösch-Zyklus auf den normalen Unterblock angewandt wird. Wenn das Übereinstimmungssignal MTS anzeigt, dass die Zeilenadresse R\_ADDR auf den schlechten Unterblock zugreift, erzeugt der Steuersignalerzeuger 530a die Steuersignale CTLs durch eine Bezugnahme auf das Programmier-/Lösch-Zyklus-Informationsregister 560 derart, dass ein zweiter Programmier-/Lösch-Zyklus auf den schlechten Unterblock angewandt wird. Der erste Programmier-/Lösch-Zyklus ist größer als der zweite Programmier-/Lösch-Zyklus. Demnach wird der Programmier-/Lösch-Zyklus auf dem schlechten Unterblock gelockert und demnach kann die Beständigkeit der nichtflüchtigen Speichervorrichtung 50 erhöht werden.

**[0091]** **Fig. 13** ist ein Blockschaltbild, welches ein anderes Beispiel der Steuerschaltung in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß beispielhaften Ausführungsformen veranschaulicht.

**[0092]** Bezug nehmend auf **Fig. 13** kann eine Steuerschaltung 500b einen Befehlsdecoder 510, einen Adresspuffer 520, einen Steuersignalerzeuger 530b, einen Adresskomparator 540, ein Schlechtunterblockinformationsregister 550, ein Programmier-/Lösch-Zyklus-Informationsregister 560, einen Komparator 575, ein Register 580 und ein Programmier-/Lösch-Zyklus-Register 585 aufweisen.

**[0093]** Die Steuerschaltung 500b der **Fig. 13** unterscheidet sich von der Steuerschaltung 500a der **Fig. 12** darin, dass die Steuerschaltung 500b ferner den Komparator 575, das Register 580 und das Programmier-/Löschen-Zyklus-Register 585 aufweist und darin, dass der Adresskomparator 540 ferner das Übereinstimmungssignal MTS für das Programmier-/Löschen-Zyklus-Register 585 vorsieht.

**[0094]** Das Programmier-/Löschen-Zyklus-Register 585 erhöht einen Zählwert CV, wenn die Zeilenadresse R\_ADDR auf den schlechten Unterblock zugreift und der decodierte Befehl D\_CMD einem Programmierbefehl oder einem Löschenbefehl entspricht, basierend auf dem Übereinstimmungssignal MTS und dem decodierten Befehl D\_CMD. Der Komparator 575 vergleicht den Zählwert CV und einen Referenzzählwert CRV, welche in dem Register 580 gespeichert sind, und sieht den Steuerspannungserzeuger 560b mit einem Vergleichssignal CV vor, welches ein Ergebnis des Vergleichs anzeigt. Der Steuerspannungserzeuger 530b empfängt den decodierten Befehl D\_CMD, das Übereinstimmungssignal MTS, das Vergleichssignal CS und das Getan-Signal DS und erzeugt die Steuersignale CTLs, das erste Modussignal MS1 und das zweite Modussignal MS2 derart, dass ein zweiter Programmier-/Löschen-Zyklus auf den schlechten Unterblock angewandt wird, wenn der Zählwert CV kleiner und gleich zu dem Referenzzählwert ist, und ein dritter Programmier-/Löschen kleiner als der Referenzzählwert CRV und der zweite Programmier-/Löschen-Zyklus wird auf den schlechten Unterblock angewandt, wenn der Zählwert CV den Referenzzählwert CRV überschreitet.

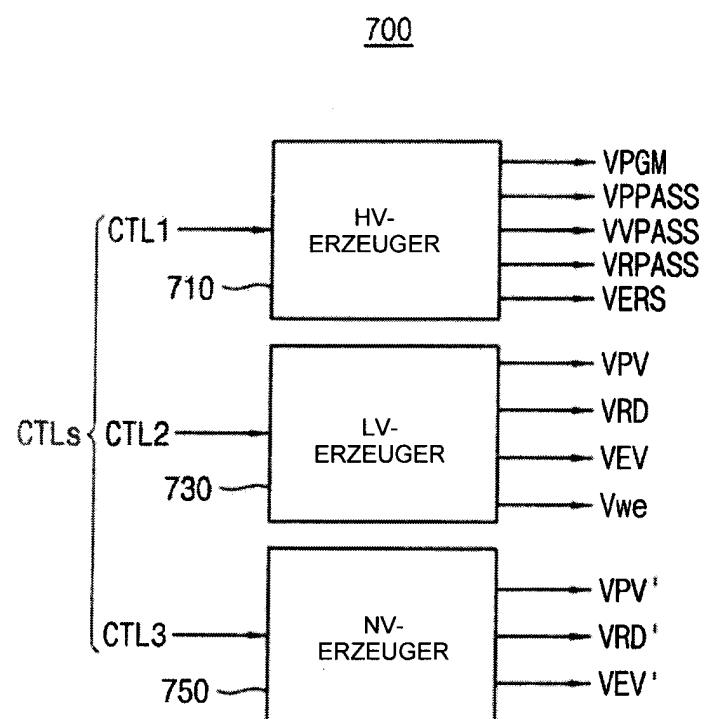

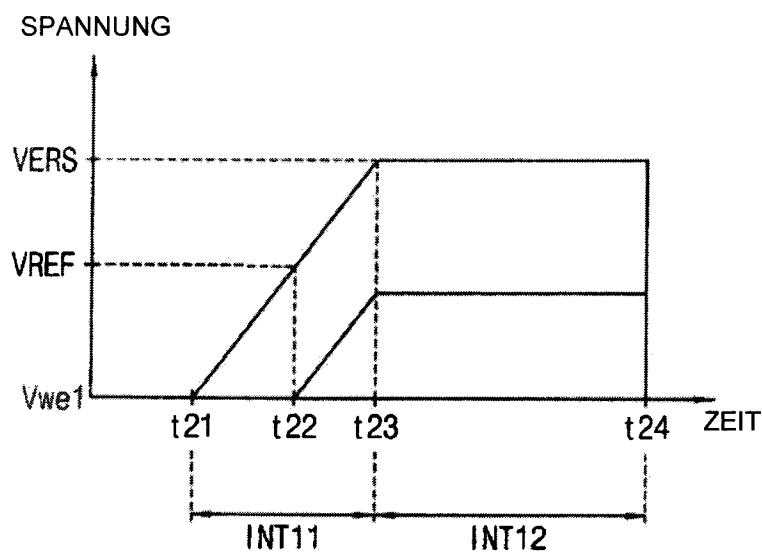

**[0095]** **Fig. 14** ist ein Blockschaltbild, welches den Spannungserzeuger in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß einigen Ausführungsformen veranschaulicht.

**[0096]** Bezugnehmend auf **Fig. 14** kann der Spannungserzeuger 700 einen Hochspannungserzeuger 710 und einen Niederspannungserzeuger 730 aufweisen. Der Spannungserzeuger 700 kann ferner einen Negativspannungserzeuger 750 aufweisen.

**[0097]** Der Hochspannungserzeuger 710 kann eine Programmierspannung VPGM, eine Programmierpassierspannung VPPASS, eine Verifikationspassierspannung VVPASS, eine Lesepassierspannung VRPASS und eine Löschspannung VERS gemäß Operationen, welche durch den Befehl CMD (oder einen decodierten Befehl D\_CMD) geleitet werden, in Antwort auf ein erstes Steuersignal CTL1 der Steuersignale CTLs erzeugen. Die Programmierspannung VPGM wird an die ausgewählte Wortleitung angelegt, die Programmierpassierspannung VPPASS, die Verifikationspassierspannung VVPASS, die Lesepassierspannung VRPASS können an die nicht ausgewählten Wortleitungen ange-

legt werden, und die Löschspannung VERS kann an die Mulde oder das Substrat des Speicherblocks angelegt werden. Das erste Steuersignal CTL1 kann eine Mehrzahl von Bits aufweisen, welche die Operationen anzeigen, welche durch den Befehl CMD geleitet werden.

**[0098]** Der Niederspannungserzeuger 730 kann eine Programmierverifikationsspannung VPV, eine Lesespannung VRD, eine Löscherkennungsspannung VER und eine Wortleitungslöscherkennung Vwe gemäß Operationen, welche durch den Befehl CMD geleitet werden, in Antwort auf ein zweites Steuersignal CTL2 der Steuersignale CTLs erzeugen. Die Programmierverifikationsspannung VPV, die Lesespannung VRD und die Löscherkennungsspannung VEV können an die ausgewählte Wortleitung gemäß einer Operation der nichtflüchtigen Speichervorrichtung 200 angelegt werden. Die Wortleitungslöscherkennung Vwe kann an Wortleitungen des ausgewählten Unterblocks angelegt werden. Das zweite Steuersignal CTL2 kann eine Mehrzahl von Bits aufweisen, welche die Operationen anzeigen, welche durch den Befehl CMD geleitet werden.

**[0099]** Der Negativspannungserzeuger 750 kann eine Programmierverifikationsspannung VPV', eine Lesespannung VRD' und eine Löscherkennungsspannung VEV', welche negative Pegel haben, gemäß Operationen, welche durch den Befehl CMD geleitet werden, in Antwort auf ein drittes Steuersignal CTL3 der Steuersignale CTLs erzeugen. Das dritte Steuersignal CTL3 kann eine Mehrzahl von Bits aufweisen, welche die Operationen anzeigen, welche durch den Befehl CMD geleitet werden.

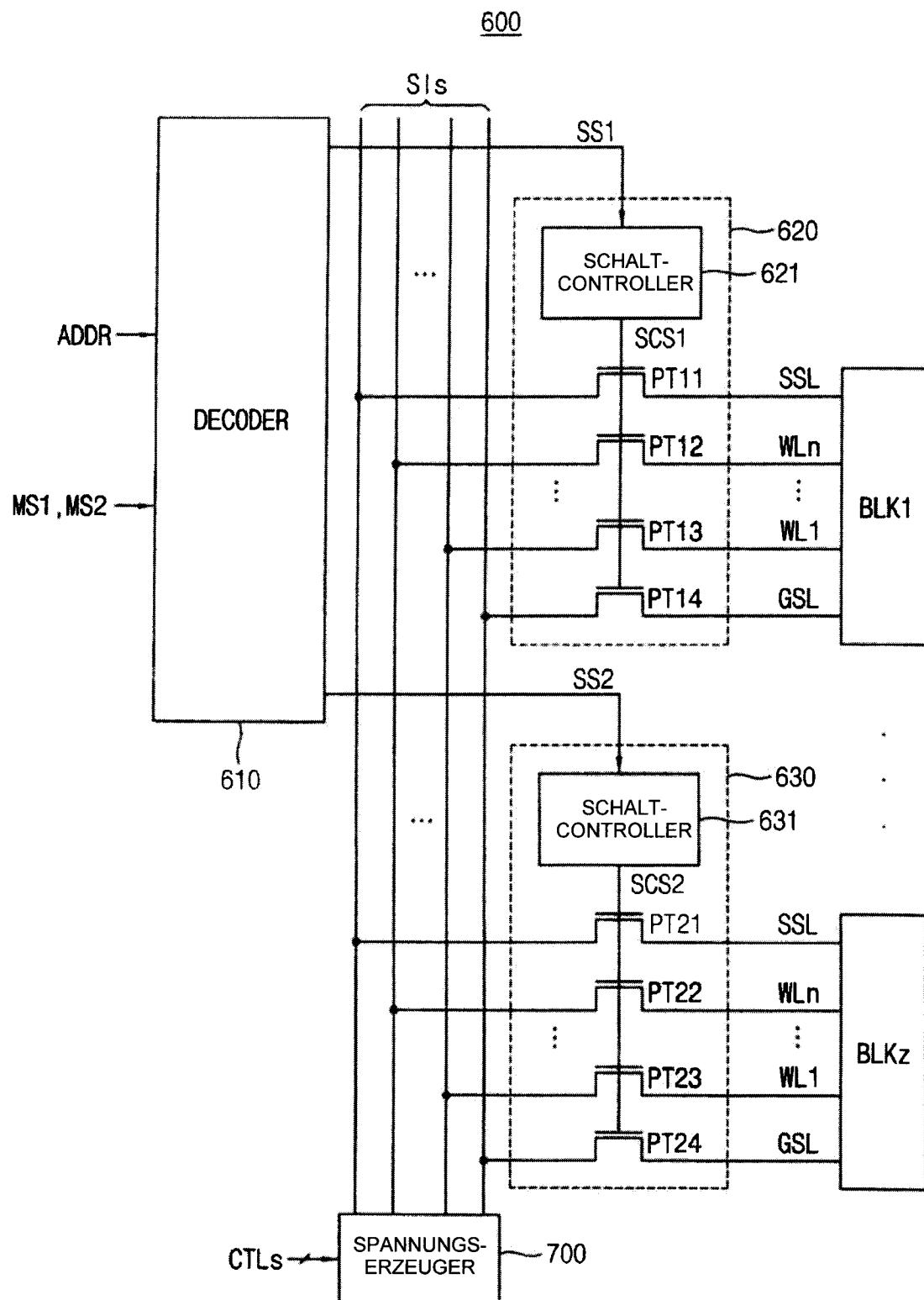

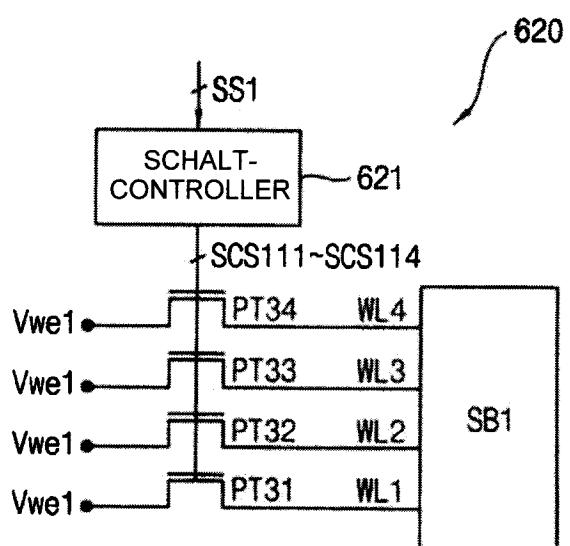

**[0100]** **Fig. 15** ist ein Blockschaltbild, welches den Adressdecoder 600 in der nichtflüchtigen Speichervorrichtung der **Fig. 4** gemäß einigen Ausführungsformen veranschaulicht.

**[0101]** Bezug nehmend auf **Fig. 15** weist der Adressdecoder 600 einen Decoder 610, eine erste Schaltschaltung 620 und eine zweite Schaltschaltung 630 auf.

**[0102]** Der Decoder 610 empfängt die Adresse ADDR (beispielsweise die Zeilenadresse R\_ADDR) und das Modussignal MS, erzeugt ein erstes Auswahlsignal SS1 und ein zweites Auswahlsignal SS2 gemäß einem Unterblock, welcher durch die Adresse ADDR und den Pegel der Substratspannung VSUB oder ein Aufrechterhaltungszeitintervall der Substratspannung VSUB adressiert ist, welches durch das Modussignal angezeigt wird, und sieht das erste Auswahlsignal SS1 und das zweite Auswahlsignal SS2 für die erste Schaltschaltung 620 und die zweite Schaltschaltung 630 jeweils vor. Als ein Beispiel kann jedes des ersten Auswahlsignals SS1 und des

zweiten Auswahlsignals SS2 eine Mehrzahl von Auswahlsignalen zum Auswählen eines Blocks aus der Mehrzahl von Blöcken in der Speicherzellanordnung 100 haben.

**[0103]** Die erste Schaltschaltung 620 und die zweite Schaltschaltung 630 können mit einer Mehrzahl von Auswahlleitungen SIs gekoppelt sein, welche mit dem Spannungserzeuger 700 gekoppelt sind. Der Spannungserzeuger 700 kann die verschiedenen Wortleitungsspannungen VWLs für die Mehrzahl von Auswahlleitungen SIs vorsehen. Die erste Schaltschaltung 620 ist mit dem Speicherblock BLK1 über wenigstens eine Strangauswahlleitung SSL, eine Mehrzahl von Wortleitungen WL1~WL<sub>n</sub> und wenigstens eine Masseauswahlleitung GSL gekoppelt. Die zweite Schaltschaltung 630 ist mit dem Speicherblock BLKz über wenigstens eine Strangauswahlleitung SSL, eine Mehrzahl von Wortleitungen WL1~WL<sub>n</sub> und wenigstens eine Masseauswahlleitung GSL gekoppelt. Die Masseauswahlleitung GSL für BLK1 ... BLKz kann für jede der ersten Schaltschaltung 620 und der zweiten Schaltschaltung 630 unterschiedlich (das heißt unabhängig) sein.

**[0104]** Die erste Schaltschaltung 620 weist einen Schaltcontroller 621 und eine Mehrzahl von Pass-Transistoren PT11~PT14 auf, welche mit der Strangauswahlleitung SSL, den Wortleitungen WL1~WL<sub>n</sub> und der Masseauswahlleitung GSL des Speicherblocks BLK1 gekoppelt sind. Der Schaltcontroller 621 kann ein Anschalten und Abschalten der Pass-Transistoren PT11~PT14 durch ein Vorsehen eines ersten Schaltsteuersignals SCS1 für die Pass-Transistoren PT11~PT14 in Antwort auf das erste Auswahlsignal SS1 steuern. Als ein Beispiel kann das erste Schaltsteuersignal SCS1 eine Mehrzahl von ersten Schaltsteuersignalen zum Auswählen eines Unterblocks aus der Mehrzahl von Unterblöcken in dem Speicherblock BLK1 in Antwort auf das erste Auswahlsignal SS1 haben. Als ein Beispiel kann der Schaltcontroller 621 eine Anschaltzeitwahl (beispielsweise ein Zeitintervall) der Pass-Transistoren PT11~PT14 durch ein Auswählen eines bestimmten Zeitintervalls aus einer Mehrzahl von unterschiedlichen Zeitintervallen in Antwort auf die ersten Schaltsteuersignale des ersten Schaltsteuersignals SCS1 steuern.

**[0105]** Die zweite Schaltschaltung 630 weist einen Schaltcontroller 631 und eine Mehrzahl von Pass-Transistoren PT21~PT24 auf, welche mit der Strangauswahlleitung SSL, den Wortleitungen WL1~WL<sub>n</sub> und der Masseauswahlleitung GSL des Speicherblocks BLKz gekoppelt sind. Der Schaltcontroller 631 kann ein Anschalten und Abschalten der Pass-Transistoren PT21~PT24 durch ein Vorsehen eines zweiten Schaltsteuersignals SCS2 für die Pass-Transistoren PT21~PT24 in Antwort auf das zweite Aus-

wahlsignal SS2 steuern. Als ein Beispiel kann das zweite Schaltsteuersignal SCS2 eine Mehrzahl von zweiten Schaltsteuersignalen zum Auswählen eines Unterblocks aus der Mehrzahl von Unterblöcken in dem Speicherblock BLKz in Antwort auf das zweite Auswahlsignal SS2 haben.

**[0106]** Der Schaltcontroller 631 kann eine Anschaltzeitwahl (beispielsweise ein Zeitintervall) der Pass-Transistoren PT21~PT24 durch ein Auswählen eines bestimmten Zeitintervalls aus einer Mehrzahl von unterschiedlichen Zeitintervallen in Antwort auf die zweiten Schaltsteuersignale des zweiten Schaltsteuersignals SCS2 steuern.

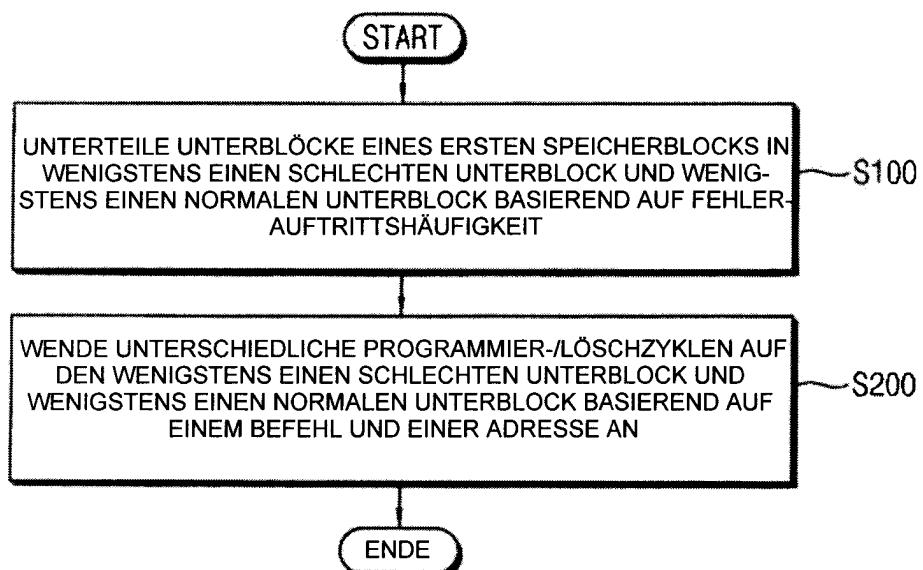

**[0107]** **Fig. 16** ist ein Flussdiagramm, welches ein Verfahren zum Betreiben einer nichtflüchtigen Speichervorrichtung gemäß einigen Ausführungsformen veranschaulicht.

**[0108]** Hierin nachstehend wird angenommen, dass der erste Unterblock SB 1 der Unterblöcke SB1, SB2 und SB3 in dem Speicherblock BLKi der **Fig. 7**, welcher benachbart zu dem Substrat ist, wenigstens einem schlechten Unterblock entspricht, und der zweite und der dritte Unterblock SB2 und SB3 wenigstens einem normalen Unterblock entsprechen.

**[0109]** Ein Block in einem NAND-Flashspeicher kann an einer Fehlfunktion leiden, welche durch einen Programmierfehler oder einen Löschfehler verursacht wird. In diesem Fall wird der Block als ein schlechter Laufzeit-Block betrachtet und durch einen anderen Block, welcher vorangehend reserviert wird, ersetzt. Neben einem schlechten Laufzeit-Block kann es einen anfänglichen schlechten Block geben, welcher bereits als schlechter Block bekannt ist, wenn ein NAND-Flashspeicher von einem Werk versendet wird. Allgemein wird eine geringe Anzahl von schlechten Laufzeit-Blöcken über eine lange Zeitperiode erzeugt, wenn ein NAND-Flashspeicher verwendet wird. Zusätzlich existiert eine kleine Anzahl von anfänglichen schlechten Blöcken normalerweise, wenn der NAND-Flashspeicher von einem Werk versendet wird. Wenn jedoch eine große Anzahl von schlechten Laufzeit-Blöcken in einer kurzen Zeitperiode erzeugt wird oder eine große Anzahl von anfänglichen schlechten Blöcken in der frühen Stufe existiert, können alle reservierten Blöcke erschöpft sein. Demnach kann eine nichtflüchtige Speichervorrichtung nicht länger verwendet werden. Aus diesem Grunde ebenso ist die Lebensdauer der Halbleiterspeichervorrichtung beschränkt.

**[0110]** Da der erste Unterblock SB1 benachbart zu dem Substrat gebildet ist und eine schmale Kanalbreite hat, werden Speicherzellen in dem ersten Unterblock SB1 in großem Maße durch Belastung

aufgrund der Programmierspannung oder der Löschspannung beeinflusst. Demnach ist eine Wahrscheinlichkeit eines Auftretens eines Fehlers in dem ersten Unterblock SB1 höher, der erste Unterblock SB1 kann als ein schlechter Unterblock festgesetzt werden.

**[0111]** Bezug nehmend auf die **Fig. 2** bis **Fig. 16** unterteilt zum Überkommen der Begrenzung der Lebensdauer gemäß einigen Ausführungsformen die Steuerschaltung 500 Unterblöcke eines ersten Speicherblocks der Mehrzahl von Speicherblöcken in wenigstens einen schlechten Unterblock (schlechter Unterblock) und wenigstens einen normalen Unterblock (normaler Unterblock) basierend auf einer Fehlerauftritthäufigkeit von jedem der Unterblöcke in dem ersten Speicherblock (S100). Information über den schlechten Unterblock kann in dem Schlechtunterblockinformationsregister 49 der **Fig. 2** und/oder 550 der **Fig. 12** gespeichert werden. Die Steuerschaltung 500 kann unterschiedliche Programmier-/Löschen-Zyklen auf den schlechten Unterblock und den normalen Unterblock basierend auf dem Befehl CND und der Adresse ADDR (S200) ausüben. Die Steuerschaltung 500 kann einen schwachen (slacked) Programmier-/Löschen-Zyklus auf den schlechten Unterblock anwenden, um die Lebensdauer der nichtflüchtigen Speichervorrichtung 50 zu erhöhen.

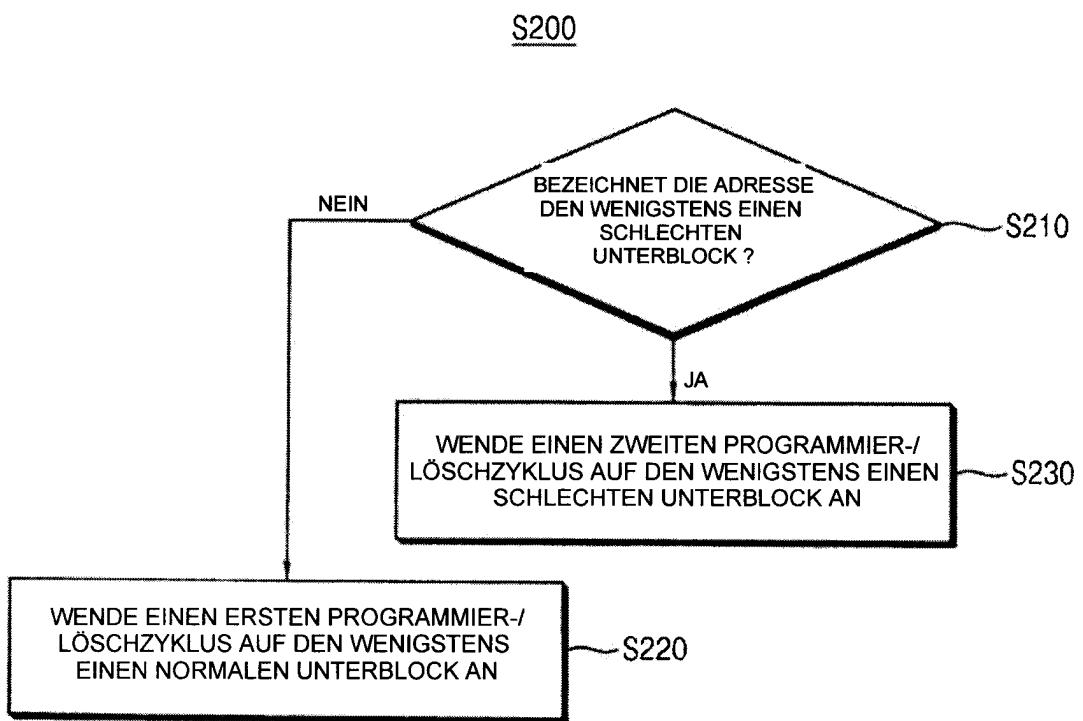

**[0112]** **Fig. 17** ist ein Flussdiagramm, welches eine Operation zum Ausüben der unterschiedlichen Programmier-/Löschen-Zyklen in **Fig. 16** im Detail veranschaulicht.

**[0113]** **Fig. 18** ist ein Flussdiagramm, welches eine Operation wenigstens eines zweiten Programmier-/Löschen-Zyklus veranschaulicht, welcher angewandt wird, und zwar im Detail in **Fig. 17**.

**[0114]** Die **Fig. 19A** und **Fig. 19B** veranschaulichen Programmier-/Löschen-Zyklen, welche jeweils auf den normalen Unterblock und den schlechten Unterblock angewandt werden.

**[0115]** Bezug nehmend auf die **Fig. 17** bis **Fig. 19B** bestimmt zum Ausüben unterschiedlicher Programmier-/Löschen-Zyklen auf den normalen Unterblock und den schlechten Unterblock (S200) die Steuerschaltung 500 der **Fig. 4**, ob die Zeilenadresse R\_ADDR den schlechten Unterblock bezeichnet (S210). Wenn die Zeilenadresse R\_ADDR den normalen Unterblock bezeichnet (NEIN in S210), steuert die Steuerschaltung den Spannungserzeuger 700 der **Fig. 14** und den Adressdecoder 600 der **Fig. 15** durch eine Bezugnahme auf das Programmier-/Löschen-Zyklus-Informationsregister 560 derart, dass ein erster Programmier-/Löschen-Zyklus 811 oder 812 auf den normalen Unterblock angewandt wird (S220). Wenn die Zeilenadresse R\_ADDR den

schlechten Unterblock bezeichnet (JA in S210), steuert die Steuerschaltung 500 den Spannungserzeuger 700 und den Adressdecoder 600 durch ein Bezugnehmen auf das Programmier-/Löschen-Zyklus-Informationsregister 560 derart, dass wenigstens ein zweiter Programmier-/Löschen-Zyklus 812 oder 822 auf den schlechten Unterblock angewandt wird (S230).