(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-141903

(P2007-141903A)

(43) 公開日 平成19年6月7日(2007.6.7)

| (51) Int.CI.                  | F 1             | テーマコード (参考) |

|-------------------------------|-----------------|-------------|

| <b>H01L 21/8238 (2006.01)</b> | H01L 27/08 321A | 5FO48       |

| <b>H01L 27/092 (2006.01)</b>  | H01L 27/08 321D | 5F140       |

| <b>H01L 29/78 (2006.01)</b>   | H01L 29/78 301N |             |

審査請求 未請求 請求項の数 5 O L (全 13 頁)

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2005-329593 (P2005-329593) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |

| (22) 出願日  | 平成17年11月15日 (2005.11.15)     | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                          |

|           |                              | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                          |

|           |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                          |

|           |                              | (72) 発明者 | 山下 朋弘<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

|           |                              | (72) 発明者 | 西田 征男<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

|           |                              |          | 最終頁に続く                                          |

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】フルシリサイド化ゲート電極を含むMISFETに、ライナー膜によるチャネル部分へのストレス印加技術を適用可能な半導体装置およびその製造方法を実現する。

【解決手段】MISFET形成済みの半導体基板上に第1のライナーシリコン窒化膜11aを形成し、ゲート電極6の側方を十分に充填するよう、第1のライナーシリコン窒化膜11a上にシリコン酸化膜等の絶縁膜を形成する。次に、絶縁膜および第1のライナーシリコン窒化膜11aに平坦化処理を施して、ポリシリコンゲート電極6aを露出させ、第1のライナーシリコン窒化膜11aを残置しつつ絶縁膜を除去する。露出したゲート電極6をフルシリサイド化し、第1のライナーシリコン窒化膜11aおよび露出したフルシリサイド化ゲート電極6を覆う第2のライナーシリコン窒化膜11bを形成する。

。

【選択図】

図7

**【特許請求の範囲】****【請求項 1】**

(a) 半導体基板に、シリコンゲート電極、ソース領域およびドレイン領域を有する少なくとも一つのMISFET (Metal Insulator Semiconductor Field Effect Transistor) を形成する工程と、

(b) 前記シリコンゲート電極、ソース領域およびドレイン領域を少なくとも覆う第1シリコン窒化膜を、前記半導体基板上に形成する工程と、

(c) 前記シリコンゲート電極の側方を充填するよう、前記第1シリコン窒化膜上に絶縁膜を形成する工程と、

(d) 前記絶縁膜および前記第1シリコン窒化膜に平坦化処理を施して、前記シリコンゲート電極を露出させる工程と、10

(e) 前記第1シリコン窒化膜を残置しつつ前記絶縁膜を除去する工程と、

(f) 露出した前記シリコンゲート電極をシリサイド化する工程と、

(g) 前記第1シリコン窒化膜、および、露出したシリサイド化済みの前記シリコンゲート電極を少なくとも覆う第2シリコン窒化膜を、前記第1シリコン窒化膜および前記シリコンゲート電極上に形成する工程と

を備える半導体装置の製造方法。

**【請求項 2】**

請求項1に記載の半導体装置の製造方法であって、

前記少なくとも一つのMISFETには、第1導電形の第1MISFETと、前記第1導電形とは異なる第2導電形の第2MISFETと、が含まれ、20

前記第1および第2MISFETの双方に対して、前記工程(a)乃至(g)が行われ、

(h) 前記工程(g)の後、前記第1MISFET近傍の前記第2シリコン窒化膜は残置しつつ、前記第2MISFET近傍の前記第2シリコン窒化膜を除去する工程と、

(i) 前記第2MISFET上の前記第1シリコン窒化膜および前記第2MISFETの前記シリコンゲート電極を少なくとも覆う第3シリコン窒化膜を、前記第2MISFET上の前記第1シリコン窒化膜および前記第2MISFETの前記シリコンゲート電極上に形成する工程と

を更に備える半導体装置の製造方法。30

**【請求項 3】**

半導体基板と、

前記半導体基板に形成された、シリサイド化シリコンゲート電極、ソース領域およびドレイン領域を有する第1MISFET (Metal Insulator Semiconductor Field Effect Transistor) と、

前記ソース領域、前記ドレイン領域および前記シリコンゲート電極の頂部を少なくとも覆うシリコン窒化膜と

を備え、

前記シリコンゲート電極の前記頂部上の前記シリコン窒化膜の膜厚よりも、前記ソース領域およびドレイン領域上の前記シリコン窒化膜の膜厚の方が大きい半導体装置。40

**【請求項 4】**

請求項3に記載の半導体装置であって、

前記シリコン窒化膜は、

前記ソース領域およびドレイン領域を少なくとも覆い、前記シリコンゲート電極の頂部は覆わない第1シリコン窒化膜と、

前記第1シリコン窒化膜および前記シリコンゲート電極の前記頂部を少なくとも覆う第2シリコン窒化膜と

を含む

半導体装置。50

**【請求項 5】**

請求項 4 に記載の半導体装置であって、

前記半導体基板に形成された、シリサイド化シリコンゲート電極、ソース領域およびドレイン領域を有する、前記第 1 M I S F E T とは異なる導電形の第 2 M I S F E T と、

前記第 2 M I S F E T の前記ソース領域およびドレイン領域を少なくとも覆い、前記第 2 M I S F E T の前記シリコンゲート電極の頂部は覆わない第 3 シリコン窒化膜と、

前記第 3 シリコン窒化膜および前記第 2 M I S F E T の前記シリコンゲート電極の前記頂部を少なくとも覆う第 4 シリコン窒化膜と

を更に備え、

前記第 2 および第 4 シリコン窒化膜の一方は圧縮性のライナー膜であり、他方は引っ張り性のライナー膜である

半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、シリサイド化されたゲート電極を含む M I S F E T (Metal Insulator Semiconductor Field Effect Transistor) を備える半導体装置およびその製造方法に関する。

**【背景技術】****【0002】**

M I S F E T のチャネル部分に歪みを発生させると、反転層内のキャリアの移動度が変化する。そこで、M I S F E T のチャネル部分に物理的ストレスを印加して歪みを発生させ、M I S F E T の駆動能力を向上させる技術が研究されている。

**【0003】**

その一つとして、下記非特許文献 1 に記載の技術がある。非特許文献 1 に記載のように、この技術によれば、基板表面、並びに、P チャネル形および N チャネル形の各 M I S F E T を覆うシリコン窒化膜を、ストレス印加のためのライナー膜として用いる。そして、P チャネル形 M I S F E T には圧縮性 (compressive) のストレスを、N チャネル形 M I S F E T には引っ張り性 (tensile) のストレスを、それぞれ印加することにより、P チャネル形および N チャネル形の各 M I S F E T の駆動能力を向上させている。

**【0004】**

なお、非特許文献 1 以外にも、この出願の発明に関連する先行技術文献情報としては次のものがある。

**【0005】**

【特許文献 1】特開 2003 - 86708 号公報

【特許文献 2】特開 2005 - 175121 号公報

【特許文献 3】特開 2003 - 273240 号公報

【非特許文献 1】C.D.Sheraw et al., 「Dual Stress Liner Enhancement in Hybrid Orientation Technology」, 2005 Symposium on VLSI Technology Digest of Technical Paper s, pp.12-13

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

従来、M I S F E T のゲート電極の材料には、N 形もしくは P 形の不純物がドープされたポリシリコンが採用されてきた。しかし、ポリシリコンをゲート電極に採用する場合、ゲート電極の空乏化による実効ゲート絶縁膜厚增加の問題や、高誘電率ゲート絶縁膜を導入する際のしきい値制御の困難性の問題がある。そのため、近年ではメタルゲート電極の採用が活発に研究されている。

**【0007】**

メタルゲート電極の一例として、フルシリサイド化 (F U S I ) ゲート電極が提案され

10

20

30

40

50

ている。フルシリサイド化ゲート電極とは、M I S F E T のポリシリコンゲート電極上にC o やN i 等の金属膜を形成し、ポリシリコンと金属膜とを反応させてゲート電極の全体をシリサイド化することにより形成されたゲート電極である。

#### 【 0 0 0 8 】

このフルシリサイド化ゲート電極を含むM I S F E T に、上記非特許文献1に記載のライナー膜によるチャネル部分へのストレス印加技術を適用する場合、以下の問題が発生する。

#### 【 0 0 0 9 】

一般的なフルシリサイド化ゲート電極形成プロセスは、1. ポリシリコンゲート電極を有する複数のM I S F E T の構造を半導体基板上に形成し、2. シリコン酸化膜等の絶縁膜で、各M I S F E T のポリシリコンゲート電極間の部分を埋め込み、かつ、ポリシリコンゲート電極を覆い、3. 埋め込んだシリコン酸化膜等の絶縁膜に対し、C M P (Chemical Mechanical Polishing) 法等による平坦化処理を行って、ポリシリコンゲート電極の表面を露出させた後、4. ポリシリコンゲート電極上に金属膜を堆積して、シリサイド化反応を行う、との工程を有する。10

#### 【 0 0 1 0 】

一方、上記非特許文献1に記載の技術では、ゲート電極を取り囲むようにライナー膜を設けることでチャネル部分へのストレス印加を行う。上記のフルシリサイドゲート電極形成プロセスにこのストレス印加技術を組み入れるためには、上記2. シリコン酸化膜等の埋め込みプロセスの前にライナー膜を設けることが考えられる。20

#### 【 0 0 1 1 】

しかし、そのような方策を探ると、上記3. 平坦化処理の際にポリシリコンゲート電極上のライナー膜まで除去されてしまう。ポリシリコンゲート電極上のライナー膜が除去されると、ライナー膜によるストレス印加効果が薄れてしまう。

#### 【 0 0 1 2 】

この発明は上記の事情に鑑みてなされたもので、フルシリサイド化ゲート電極を含むM I S F E T に、ライナー膜によるチャネル部分へのストレス印加技術を適用可能な半導体装置およびその製造方法を提供することにある。

#### 【 課題を解決するための手段】

#### 【 0 0 1 3 】

請求項1に記載の発明は、(a) 半導体基板に、シリコンゲート電極、ソース領域およびドレイン領域を有する少なくとも一つのM I S F E T (Metal Insulator Semiconductor Field Effect Transistor) を形成する工程と、(b) 前記シリコンゲート電極、ソース領域およびドレイン領域を少なくとも覆う第1シリコン窒化膜を、前記半導体基板上に形成する工程と、(c) 前記シリコンゲート電極の側方を充填するよう、前記第1シリコン窒化膜上に絶縁膜を形成する工程と、(d) 前記絶縁膜および前記第1シリコン窒化膜に平坦化処理を施して、前記シリコンゲート電極を露出させる工程と、(e) 前記第1シリコン窒化膜を残置しつつ前記絶縁膜を除去する工程と、(f) 露出した前記シリコンゲート電極をシリサイド化する工程と、(g) 前記第1シリコン窒化膜、および、露出したシリサイド化済みの前記シリコンゲート電極を少なくとも覆う第2シリコン窒化膜を、前記第1シリコン窒化膜および前記シリコンゲート電極上に形成する工程とを備える半導体装置の製造方法である。3040

#### 【 0 0 1 4 】

請求項3に記載の発明は、半導体基板と、前記半導体基板に形成された、シリサイド化シリコンゲート電極、ソース領域およびドレイン領域を有する第1M I S F E T (Metal Insulator Semiconductor Field Effect Transistor) と、前記ソース領域、前記ドレイン領域および前記シリコンゲート電極の頂部を少なくとも覆うシリコン窒化膜とを備え、前記シリコンゲート電極の前記頂部上の前記シリコン窒化膜の膜厚よりも、前記ソース領域およびドレイン領域上の前記シリコン窒化膜の膜厚の方が大きい半導体装置である。

#### 【 発明の効果】

## 【0015】

請求項1に記載の発明によれば、平坦化処理によりシリコンゲート電極上の第1シリコン窒化膜が除去されるが、シリコンゲート電極のシリサイド化後に第2シリコン窒化膜がシリコンゲート電極を再び覆う。よって、シリサイド化されたシリコンゲート電極付近の第1および第2シリコン窒化膜が、チャネル部分へのストレス印加用ライナー膜として機能するので、フルシリサイド化ゲート電極を含むMISFETに、ライナー膜によるチャネル部分へのストレス印加技術を適用可能な半導体装置の製造方法が実現できる。また、絶縁膜形成時に、ソース領域およびドレイン領域上に第1シリコン窒化膜が形成済みであるので、ソース領域およびドレイン領域が既にシリサイド化されている場合に、絶縁膜とソース領域およびドレイン領域とが反応することがない。

10

## 【0016】

請求項3に記載の発明によれば、ソース領域、ドレイン領域およびシリコンゲート電極の頂部を覆うシリコン窒化膜とを備え、シリコンゲート電極の頂部上のシリコン窒化膜の膜厚よりも、ソース領域およびドレイン領域上のシリコン窒化膜の膜厚の方が大きい。よりチャネル部分に近い、ソース領域およびドレイン領域上のシリコン窒化膜の膜厚が大きいため、チャネル部分へのストレス印加能力の高いMISFETが得られる。また、シリコンゲート電極の頂部のシリコン窒化膜の膜厚は小さいので、誘電率の高いシリコン窒化膜の膜厚を少なくすることができる。よって、MISFET上層に金属配線を設けた場合であっても、シリコンゲート電極 - 金属配線間の寄生容量を少なくすることができる。

20

## 【発明を実施するための最良の形態】

## 【0017】

## &lt;実施の形態1&gt;

本実施の形態は、平坦化処理によりシリコンゲート電極上の第1シリコン窒化膜が除去されても、シリコンゲート電極のフルシリサイド化後に第2シリコン窒化膜をシリコンゲート電極上に再び形成する、半導体装置およびその製造方法である。

## 【0018】

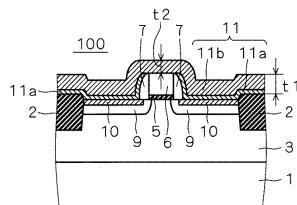

図1は、本実施の形態に係る製造方法により製造された半導体装置を示す断面図である。この半導体装置は、シリコン基板等の半導体基板1と、半導体基板1に形成されたNチャネル形MISFET100およびPチャネル形MISFET200と、ライナーシリコン窒化膜11と、シリコン酸化膜等の層間絶縁膜12と、複数の配線13と、を備える。

30

## 【0019】

半導体基板1内には、P形不純物が注入されたP形ウェル3と、N形不純物が注入されたN形ウェル4とが形成されている。また、半導体基板1の表面の一部には選択的に、シリコン酸化膜等の素子分離膜2が形成されている。

## 【0020】

Nチャネル形MISFET100はP形ウェル3上に形成されている。Nチャネル形MISFET100は、半導体基板1表面に形成された、シリコン酸化膜やシリコン酸窒化膜、高誘電率絶縁膜(ハフニウム酸化膜(HfO<sub>2</sub>)やハフニウム酸窒化膜(HfSiON)等)等のゲート絶縁膜5と、ゲート絶縁膜5上に形成されたフルシリサイド化シリコンゲート電極6と、ゲート絶縁膜5およびフルシリサイド化シリコンゲート電極6の側面に形成された、シリコン窒化膜等のサイドウォール7と、P形ウェル3内に形成されたN形ソース領域・ドレイン領域9と、N形ソース領域・ドレイン領域9の表面に形成されたシリサイド化領域10と、を有する。

40

## 【0021】

Pチャネル形MISFET200はN形ウェル4上に形成されている。Pチャネル形MISFET200は、半導体基板1表面に形成された、シリコン酸化膜や高誘電率絶縁膜(ハフニウム酸化膜等)等のゲート絶縁膜5と、ゲート絶縁膜5上に形成されたフルシリサイド化シリコンゲート電極6と、ゲート絶縁膜5およびフルシリサイド化シリコンゲート電極6の側面に形成された、シリコン窒化膜等のサイドウォール7と、N形ウェル4内に形成されたP形ソース領域・ドレイン領域8と、P形ソース領域・ドレイン領域8の表

50

面に形成されたシリサイド化領域 10 と、を有する。

【0022】

Nチャネル形MISFET100とPチャネル形MISFET200とは、素子分離膜2で電気的に絶縁されている。また、複数の配線13は、それぞれコントラクトプラグを介して、Nチャネル形MISFET100およびPチャネル形MISFET200の各シリサイド化領域10に接続される。

【0023】

ライナーシリコン窒化膜11は、後述するように、その一部が二層、他の一部が単層のシリコン窒化膜である。このライナーシリコン窒化膜11が、後述するようにチャネル部分へのストレス印加機能を担う。

10

【0024】

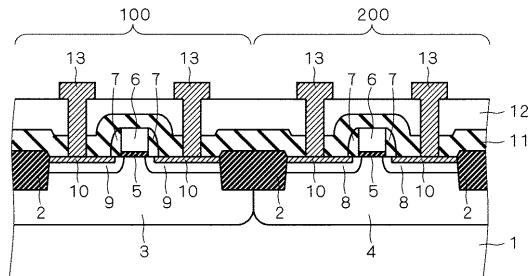

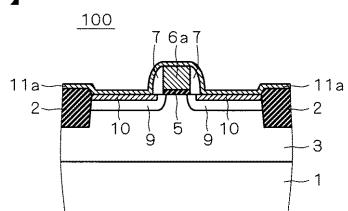

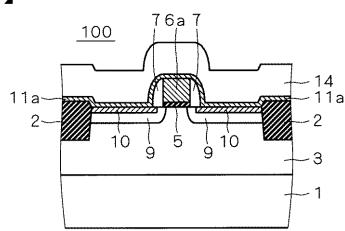

図2～図7は、本実施の形態に係る半導体装置の製造方法の各工程を示す図である。なお、図2～図7においては、表示を簡略化するために、Pチャネル形MISFET200の領域を示さず、Nチャネル形MISFET100の領域のみを示している。Pチャネル形MISFET200の領域においても、Nチャネル形MISFET100の領域における同様に、後述する各成膜処理や平坦化処理等が行われる。

【0025】

まず、熱酸化法やトレンチ形成技術、CVD (Chemical Vapor Deposition) 技術等を用いて、半導体基板1の表面の一部に、選択的にシリコン酸化膜等の素子分離膜2を形成する。次に、選択的に不純物イオン注入を行い、半導体基板1内のNチャネル形MISFET100の形成領域にP形ウェル3を形成する。また、選択的に不純物イオン注入を行い、Pチャネル形MISFET200の形成領域にN形ウェル4を形成する。

20

【0026】

次に、半導体基板1に、Nチャネル形MISFET100およびPチャネル形MISFET200を形成する。具体的には、CVD技術やフォトリソグラフィ技術、エッチング技術を用いて、シリコン酸化膜やシリコン酸窒化膜、高誘電率絶縁膜(ハフニウム酸化膜等)等のゲート絶縁膜5とポリシリコンゲート電極6aとの積層構造を半導体基板1の表面に選択的に形成する。その後、選択的に不純物イオン注入を行い、P形ソース領域・ドレイン領域8及びN形ソース領域・ドレイン領域9のエクステンション領域(図示せず)を形成する。そして、シリコン窒化膜等の成膜及び当該シリコン窒化膜等への等方性エッチングを行って、サイドウォール7を形成する。その後、選択的に不純物イオン注入を行い、P形ソース領域・ドレイン領域8及びN形ソース領域・ドレイン領域9を形成する。そして、P形ソース領域・ドレイン領域8及びN形ソース領域・ドレイン領域9の各表面上に、シリサイド化領域10を形成する。

30

【0027】

なお、Nチャネル形MISFET100およびPチャネル形MISFET200は、この段階ではフルシリサイド化シリコンゲート電極6を有しておらず、図2に示すように、シリサイド化されていないポリシリコンゲート電極6aを有しているに過ぎない。また、ポリシリコンゲート電極6aには、B、P、As、In、Sb、F、N等の不純物イオンを注入しても良い。

40

【0028】

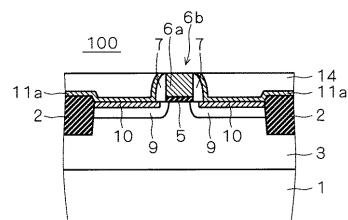

次に、図2に示すように、Nチャネル形MISFET100およびPチャネル形MISFET200のポリシリコンゲート電極6a、P形ソース領域・ドレイン領域8及びN形ソース領域・ドレイン領域9を少なくとも覆う第1のライナーシリコン窒化膜11aを、CVD技術により半導体基板1上に形成する。続いて、図3に示すように、ポリシリコンゲート電極6aの側方を十分に充填するよう、第1のライナーシリコン窒化膜11a上に、シリコン酸化膜等の絶縁膜14を形成する。この絶縁膜14は、次工程の平坦化処理におけるゲート倒れ防止用膜として機能する。

【0029】

次に、図4に示すように、絶縁膜14および第1のライナーシリコン窒化膜11aに平

50

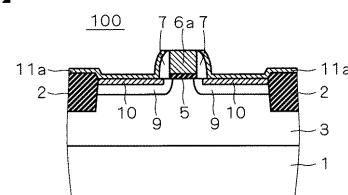

平坦化処理を施して、ポリシリコンゲート電極 6 a の頂部 6 b を露出させる。この平坦化処理には、C M P 法や、C M P 法とドライ又はウェットエッチング法との組み合わせを採用すればよい。続いて、図 5 に示すように、第 1 のライナーシリコン窒化膜 1 1 a を残置しつつ絶縁膜 1 4 を除去する。この除去処理においては、第 1 のライナーシリコン窒化膜 1 1 a とシリコン酸化膜等の絶縁膜 1 4 とのエッティング選択性を利用したウェットエッティングを行えばよい。

#### 【 0 0 3 0 】

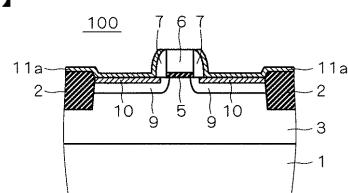

次に、図 6 に示すように、露出したポリシリコンゲート電極 6 a をフルシリサイド化し、フルシリサイド化シリコンゲート電極 6 へと変質させる。フルシリサイド化に当たっては、Co、Ni、Pt、Er、Pd 等の金属膜（図示せず）を少なくともポリシリコンゲート電極 6 a 上に堆積した後、熱処理を行って当該金属膜とポリシリコンゲート電極 6 a とを反応させ、未反応の当該金属膜を除去すればよい。

#### 【 0 0 3 1 】

なお、本実施の形態においては、ポリシリコンゲート電極 6 a をフルシリサイド化させているが、本願発明は、ポリシリコンゲート電極 6 a の全体ではなくその一部をシリサイド化させる場合を排除するものではない。よって、フルシリサイド化シリコンゲート電極 6 に代わって、一部がシリサイド化したシリコンゲート電極が採用されていても良い。

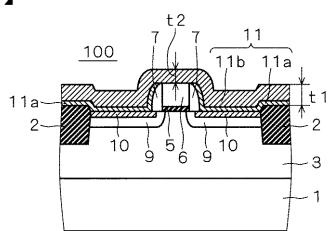

#### 【 0 0 3 2 】

次に、図 7 に示すように、第 1 のライナーシリコン窒化膜 1 1 a および露出したフルシリサイド化シリコンゲート電極 6 を少なくとも覆う第 2 のライナーシリコン窒化膜 1 1 b を、第 1 のライナーシリコン窒化膜 1 1 a およびフルシリサイド化シリコンゲート電極 6 上に、プラズマ C V D 技術等により形成する。第 1 のライナーシリコン窒化膜 1 1 a および第 2 のライナーシリコン窒化膜 1 1 b の積層構造が、図 1 のライナーシリコン窒化膜 1 1 を構成する。すなわち、ライナーシリコン窒化膜 1 1 は、P 形ソース領域・ドレイン領域 8 及び N 形ソース領域・ドレイン領域 9 上においては第 1 及び第 2 のライナーシリコン窒化膜 1 1 a, 1 1 b と二層の、フルシリサイド化シリコンゲート電極 6 上においては第 2 のライナーシリコン窒化膜 1 1 b のみの単層の、シリコン窒化膜である。

#### 【 0 0 3 3 】

この後、層間絶縁膜 1 2 をライナーシリコン窒化膜 1 1 上に形成し、フォトリソグラフィ技術及びエッティング技術により層間絶縁膜 1 2 及びライナーシリコン窒化膜 1 1 内にコンタクトホールを形成する。そして、コンタクトホール内および層間絶縁膜 1 2 表面に金属膜（図示せず）を形成し、ダマシン法等により配線 1 3 を形成すれば、図 1 の構造が得られる。

#### 【 0 0 3 4 】

本実施の形態に係る半導体装置の製造方法によれば、平坦化処理によりポリシリコンゲート電極 6 a 上の第 1 のライナーシリコン窒化膜 1 1 a が除去されるが、ポリシリコンゲート電極 6 a のシリサイド化後に第 2 のライナーシリコン窒化膜 1 1 b がフルシリサイド化シリコンゲート電極 6 を再び覆う。よって、フルシリサイド化シリコンゲート電極 6 付近の第 1 および第 2 のライナーシリコン窒化膜 1 1 a, 1 1 b が、チャネル部分へのストレス印加用ライナー膜として機能するので、フルシリサイド化シリコンゲート電極 6 を含む M I S F E T に、ライナー膜によるチャネル部分へのストレス印加技術を適用可能な半導体装置の製造方法が実現できる。また、絶縁膜 1 4 の形成時に、P 形および N 形ソース領域・ドレイン領域 8, 9 上に第 1 のライナーシリコン窒化膜 1 1 a が形成済みであるので、P 形および N 形ソース領域・ドレイン領域 8, 9 が既にシリサイド化されている（シリサイド化領域 1 0 を含む）場合に、絶縁膜 1 4 と P 形および N 形ソース領域・ドレイン領域 8, 9 とが反応することがない。

#### 【 0 0 3 5 】

また、本実施の形態に係る半導体装置の構造においては、ライナーシリコン窒化膜 1 1 が P 形および N 形ソース領域・ドレイン領域 8, 9 およびフルシリサイド化シリコンゲート電極 6 の頂部を少なくとも覆う。そして、図 7 に示すように、フルシリサイド化ゲート

10

20

30

40

50

電極 6 の頂部上の第 2 のライナーシリコン窒化膜 11 b の膜厚  $t_2$  よりも、P 形および N 形ソース領域・ドレイン領域 8, 9 上の第 1 および第 2 のライナーシリコン窒化膜 11 a, 11 b の積層膜の膜厚  $t_1$  の方が大きい。

#### 【0036】

すなわち、本実施の形態に係る半導体装置によれば、フルシリサイド化シリコンゲート電極 6 の頂部上のライナーシリコン窒化膜 11 の膜厚  $t_2$  よりも、P 形および N 形ソース領域・ドレイン領域 8, 9 上のライナーシリコン窒化膜 11 の膜厚  $t_1$  の方が大きい。よりチャネル部分に近い、P 形および N 形ソース領域・ドレイン領域 8, 9 上のライナーシリコン窒化膜 11 の膜厚が大きいため、チャネル部分へのストレス印加能力の高い MISFET が得られる。また、フルシリサイド化シリコンゲート電極 6 の頂部のライナーシリコン窒化膜 11 の膜厚は小さいので、誘電率の高いライナーシリコン窒化膜 11 の膜厚を少なくすることができる。よって、MISFET 上層に金属配線 13 を設けた場合であっても、フルシリサイド化シリコンゲート電極 6 - 金属配線 13 間の寄生容量を少なくすることができる。10

#### 【0037】

また、ライナーシリコン窒化膜 11 は、P 形および N 形ソース領域・ドレイン領域 8, 9 を少なくとも覆い、フルシリサイド化シリコンゲート電極 6 の頂部は覆わない第 1 のライナーシリコン窒化膜 11 a と、第 1 のライナーシリコン窒化膜 11 a およびフルシリサイド化シリコンゲート電極 6 の頂部を少なくとも覆う第 2 のライナーシリコン窒化膜 11 b とを含む。よって、P 形および N 形ソース領域・ドレイン領域 8, 9 上は第 1 および第 2 のライナーシリコン窒化膜 11 a, 11 b の積層膜となっており、また、フルシリサイド化シリコンゲート電極 6 の頂部では第 1 のライナーシリコン窒化膜 11 a が存在せず、第 2 のライナーシリコン窒化膜 11 b の単層膜となっているので、膜厚  $t_2$  よりも膜厚  $t_1$  の方が大きいライナーシリコン窒化膜 11 の構造を容易に得ることができる。20

#### 【0038】

##### < 実施の形態 2 >

本実施の形態は、実施の形態 1 に係る半導体装置およびその製造方法の変形例であって、図 7までの工程を行った後に、N チャネル形 MISFET 100 近傍の第 2 のライナーシリコン窒化膜 11 b は残置しつつ、P チャネル形 MISFET 200 近傍の第 2 のライナーシリコン窒化膜 11 b を除去し、P チャネル形 MISFET 200 側に第 3 のライナーシリコン窒化膜 11 c を形成するものである。30

#### 【0039】

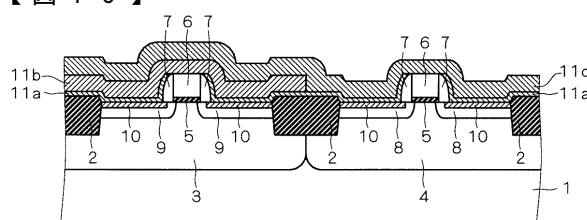

図 8 ~ 図 11 は、本実施の形態に係る半導体装置の製造方法の各工程を示す図である。まず、N チャネル形 MISFET 100 および P チャネル形 MISFET 200 の双方に対して、実施の形態 1 に記載の図 2 ~ 図 7 の工程を行う。これにより、図 8 に示される、N チャネル形 MISFET 100 および P チャネル形 MISFET 200 の両領域にて、第 1 のライナーシリコン窒化膜 11 a 及び第 2 のライナーシリコン窒化膜 11 b が形成された半導体装置の構造が得られる。

#### 【0040】

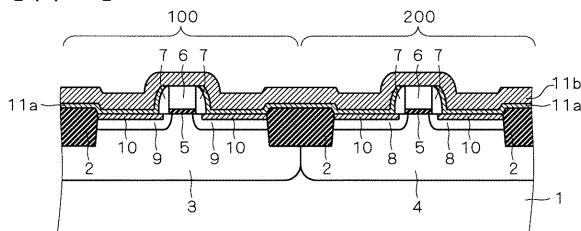

次に、図 9 に示すように、N チャネル形 MISFET 100 近傍の第 2 のライナーシリコン窒化膜 11 b は残置しつつ、P チャネル形 MISFET 200 近傍の第 2 のライナーシリコン窒化膜 11 b を除去する。この除去処理においては、フォトリソグラフィ技術及びエッチング技術により第 2 のライナーシリコン窒化膜 11 b をパターニングすればよい。40

#### 【0041】

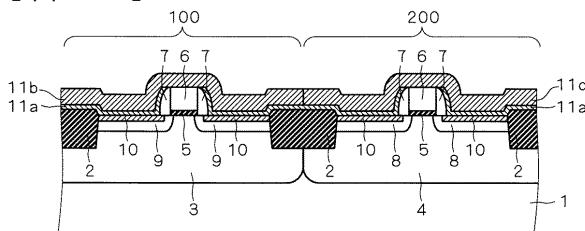

次に、図 10 に示すように、P チャネル形 MISFET 200 上の第 1 のライナーシリコン窒化膜 11 a および P チャネル形 MISFET 200 のフルシリサイド化シリコンゲート電極 6 を少なくとも覆う第 3 のライナーシリコン窒化膜 11 c を、P チャネル形 MISFET 200 の第 1 のライナーシリコン窒化膜 11 a およびフルシリサイド化シリコンゲート電極 6 上、並びに、N チャネル形 MISFET 100 の第 2 のライナーシリコン窒化膜 11 b を除いて、P チャネル形 MISFET 200 上に形成する。50

化膜 11b 上に、プラズマ CVD 技術等により形成する。

【0042】

この第3のライナーシリコン窒化膜 11c の形成に当たっては、第2のライナーシリコン窒化膜 11b 形成時におけるプラズマ CVD 装置のプラズマパワー ガス流量比とは異なる、プラズマ CVD 装置のプラズマパワー ガス流量比の値を採用すればよい。このように、第2及び第3のライナーシリコン窒化膜 11b, 11c の成膜時の各種プロセス条件を制御することで、第3のライナーシリコン窒化膜 11c を圧縮性のライナー膜とし、第2のライナーシリコン窒化膜 11b を引っ張り性のライナー膜とすることができます。N チャネル形 MISFET 100 上のライナー膜を引っ張り性ストレス印加可能とし、P チャネル形 MISFET 200 上のライナー膜を圧縮性ストレス印加可能とすれば、N 及び P チャネル形 MISFET 100, 200 の双方において、駆動能力が向上する。10

【0043】

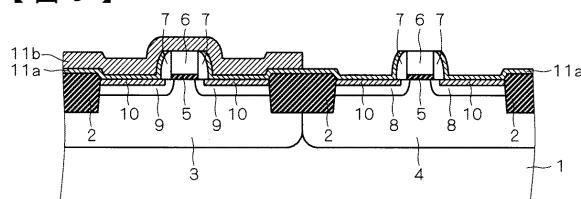

そして、図 11 に示すように、P チャネル形 MISFET 200 近傍の第3のライナーシリコン窒化膜 11c は残置しつつ、N チャネル形 MISFET 100 近傍の第3のライナーシリコン窒化膜 11c を除去する。この除去処理においては、フォトリソグラフィ技術及びエッチング技術により第3のライナーシリコン窒化膜 11c をパターニングすればよい。

【0044】

このように本実施の形態に係る半導体装置の製造方法によれば、P チャネル形 MISFET 200 上の第1のライナーシリコン窒化膜 11a および P チャネル形 MISFET 200 のフルシリサイド化シリコンゲート電極 6 上には、第2のライナーシリコン窒化膜 11b に代わって第3のライナーシリコン窒化膜 11c を形成する。よって、第2および第3のライナーシリコン窒化膜 11b, 11c を、異なるプロセス条件で形成することにより、第2および第3のライナーシリコン窒化膜 11b, 11c の一方を圧縮性のライナー膜とし、他方を引っ張り性のライナー膜とすることができます。20

【0045】

また、本実施の形態に係る半導体装置の構造においては、P チャネル形 MISFET 200 上の第1のライナーシリコン窒化膜 11a を、P 形ソース領域・ドレイン領域 8 を少なくとも覆い、P チャネル形 MISFET 200 のフルシリサイド化シリコンゲート電極 6 の頂部は覆わない第3のライナーシリコン窒化膜と捉え、P チャネル形 MISFET 200 上のライナーシリコン窒化膜 11c を、第3のライナーシリコン窒化膜 11a および P チャネル形 MISFET 200 のフルシリサイド化ゲート電極 6 の頂部を少なくとも覆う第4のライナーシリコン窒化膜と捉えることもできる。そしてこの場合、P チャネル形 MISFET 200 上の第4のライナーシリコン窒化膜 11c は圧縮性のライナー膜であり、N チャネル形 MISFET 100 上の第2のライナーシリコン窒化膜 11b は引っ張り性のライナー膜である、と言える。30

【0046】

よって、本実施の形態に係る半導体装置によれば、第2および第4のライナーシリコン窒化膜 11b, 11c の一方が圧縮性のライナー膜であり、他方は引っ張り性のライナー膜であるので、N チャネル形および P チャネル形 MISFET 100, 200 の一方には圧縮性のストレスを、他方には引っ張り性のストレスを、それぞれ印加して、P チャネル形および N チャネル形の各 MISFET 100, 200 の駆動能力を向上させることができる。40

【0047】

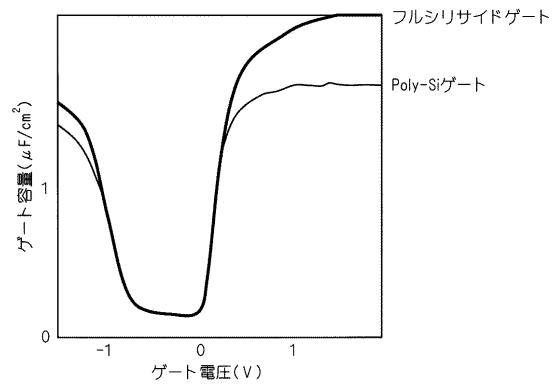

なお、図 12 は、フルシリサイド化ゲート電極を有する MISFET と、シリサイド化を行わないポリシリコンゲート電極を有する MISFET との、ゲート電圧 - ゲート容量の関係を示すグラフである。図 12 から分かるとおり、フルシリサイド化ゲート電極の方がゲート容量が増大し、実効的ゲート絶縁膜厚が薄膜化して、MISFET の駆動能力が向上することとなる。これは、ポリシリコンゲート電極で見られるゲート空乏化がフルシリサイド化ゲート電極では抑制されることに起因すると考えられる。なお、N チャネル形50

、Pチャネル形いずれの場合も、図12のグラフ特性となる。

#### 【0048】

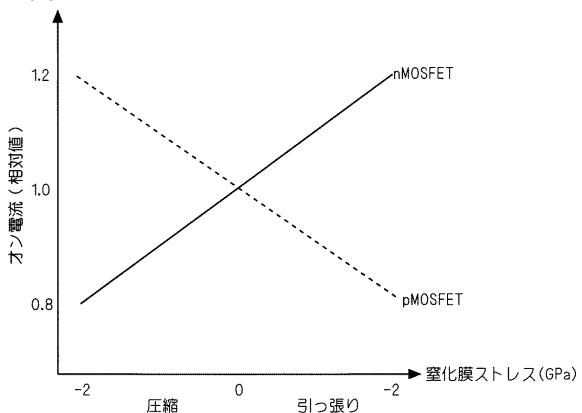

また、図13は、ライナーシリコン窒化膜のストレス方向・ストレス量と、Nチャネル形MISFET及びPチャネル形MISFETのオン電流との関係を示すグラフである。図13に示すとおり、引っ張り性のライナーシリコン窒化膜を採用すれば、Nチャネル形MISFETのオン電流が増大してその駆動能力が向上し、圧縮性のライナーシリコン窒化膜を採用すれば、Pチャネル形MISFETのオン電流が増大してその駆動能力が向上する。

#### 【0049】

よって、Pチャネル形MISFET200側のライナーシリコン窒化膜11cを圧縮性のライナー膜とし、Nチャネル形MISFET100側のライナーシリコン窒化膜11bを引っ張り性のライナー膜として、両MISFETの駆動能力を向上させることができる。

#### 【0050】

なお、両MISFET上に存在するライナーシリコン窒化膜11aについては、ストレス量の少ないシリコン窒化膜を採用すればよい。そうすれば、Nチャネル形MISFET100及びPチャネル形MISFET200の一方の駆動能力を過剰に高め、他方の駆動能力を減じることがない。

#### 【図面の簡単な説明】

#### 【0051】

【図1】実施の形態1に係る製造方法により製造された半導体装置を示す断面図である。

【図2】実施の形態1に係る半導体装置の製造方法の一工程を示す図である。

【図3】実施の形態1に係る半導体装置の製造方法の一工程を示す図である。

【図4】実施の形態1に係る半導体装置の製造方法の一工程を示す図である。

【図5】実施の形態1に係る半導体装置の製造方法の一工程を示す図である。

【図6】実施の形態1に係る半導体装置の製造方法の一工程を示す図である。

【図7】実施の形態1に係る半導体装置の製造方法の一工程を示す図である。

【図8】実施の形態2に係る半導体装置の製造方法の一工程を示す図である。

【図9】実施の形態2に係る半導体装置の製造方法の一工程を示す図である。

【図10】実施の形態2に係る半導体装置の製造方法の一工程を示す図である。

【図11】実施の形態2に係る半導体装置の製造方法の一工程を示す図である。

【図12】フルシリサイド化ゲート電極を有するMISFETと、シリサイド化を行わないゲート電極を有するMISFETとの、ゲート電圧・ゲート容量の関係を示すグラフである。

【図13】ライナーシリコン窒化膜のストレス方向・ストレス量と、Nチャネル形MISFET及びPチャネル形MISFETのオン電流との関係を示すグラフである。

#### 【符号の説明】

#### 【0052】

1 半導体基板、2 素子分離膜、3 P形ウェル、4 N形ウェル、5 ゲート絶縁膜、6 フルシリサイド化ゲート電極、6a ポリシリコンゲート電極、7 サイドウォール、8 P形ソース領域・ドレイン領域、9 N形ソース領域・ドレイン領域、10 シリサイド化領域、11, 11a ~ 11c ライナーシリコン窒化膜、12 層間絶縁膜、13 配線、14 絶縁膜。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図10】

【図8】

【図11】

【図9】

【図 1 2】

【図 1 3】

---

フロントページの続き

(72)発明者 尾田 秀一

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5F048 AA07 AC03 BB05 BB08 BB11 BC06 BE03 BF06 BF11 BF16

BG13 DA25 DA27 DA30

5F140 AA00 AB03 AC28 BA01 BC06 BD04 BD11 BF01 BF08 BG08

BG14 BG34 BG43 BG51 BG53 BH14 CB01 CB04 CC01 CC08

CC12 CE06 CE07