US 20080054963A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2008/0054963 A1

# (10) Pub. No.: US 2008/0054963 A1 (43) Pub. Date: Mar. 6, 2008

# Masenas

## (54) DELAY LOCKED LOOP HAVING CHARGE PUMP GAIN INDEPENDENT OF OPERATING FREQUENCY

(76) Inventor: Charles J. Masenas, Essex Junction, VT (US)

> Correspondence Address: HOFFMAN, WARNICK & D'ALESSANDRO LLC 75 STATE ST 14TH FLOOR ALBANY, NY 12207 (US)

- (21) Appl. No.: 11/854,046

- (22) Filed: Sep. 12, 2007

## **Related U.S. Application Data**

(63) Continuation of application No. 11/279,446, filed on Apr. 12, 2006, now Pat. No. 7,301,380.

### **Publication Classification**

- (51) Int. Cl. *H03L* 7/06 (2006.01)

# (57) ABSTRACT

A delay looked loop (DLL) having a charge pump gain independent of the operating frequency of the DLL. A charge pump is disclosed for providing a charge to a capacitive element on a voltage controlled delay line, wherein the charge is independent of a control voltage step cycle time of the DLL, the charge pump includes: a charge/ dump signal generation stage that generates a charge signal and a dump signal during each period of a reference clock signal; a first switched capacitor stage that charges a first capacitor in response to the charge signal and dumps a positive charge from the first capacitor in response to the dump signal; a second switched capacitor stage that charges a second capacitor in response to the charge signal and dumps a negative charge from the second capacitor in response to the dump signal; and an output stage that selectively loads either the positive charge or the negative charge to the capacitive element on the voltage controlled delay line in response to an input signal from a phase detector.

22

FIG. 2

[0001] This continuation application claims priority to co-pending patent application "DELAY LOCKED LOOP HAVING CHARGE PUMP GAIN INDEPENDENT OF OPERATING FREQUENCY," Ser. No. 11/279,446, filed on Apr. 12, 2006, the contents of which are hereby incorporated by reference.

#### FIELD OF THE INVENTION

**[0002]** The invention relates generally to delay locked loops (DLLs), and more particularly relates to a DLL that utilizes a switched capacitor circuit as a charge pump to eliminate the dependence of the magnitude of the control voltage steps on cycle time.

#### BACKGROUND OF THE INVENTION

**[0003]** A delay locked loop (DLL) is a commonly used circuit for synchronizing clocks. A DLL works by inserting delay between an input clock and a feedback clock until the two rising edges align, putting the two clocks 360° out of phase (meaning they are in phase but delayed by exactly one clock cycle time). After the edges from the input clock line up with the edges from the feedback clock, the DLL "locks." As long as the circuit is not evaluated until after the DLL locks, the two clocks have no discernible difference in phase.

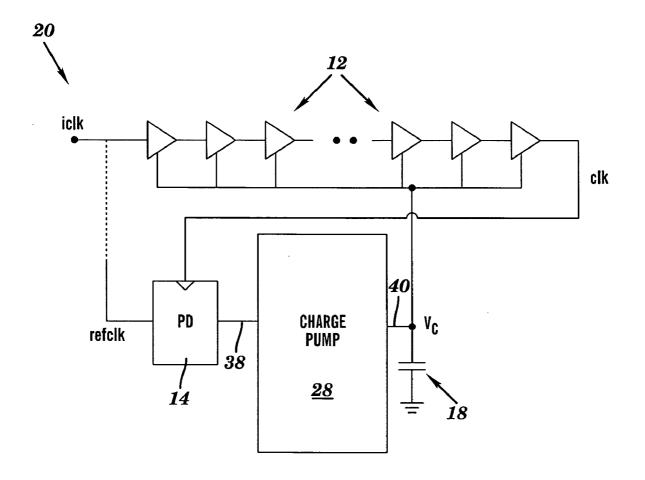

[0004] DLLs typically comprise a phase detector (e.g., XOR, latch, etc.), a charge pump, a capacitor, and voltage controlled delay line. Typically, the types of phase detectors employed are current sources that are "on" for all or part of the duration of the cycle time. FIG. 1 depicts a prior art example of a DLL 10 having a delay chain 12 that receives an input clock (clk) and generates an output clock (clk). The output clock (clk) and a reference clock signal (refclk) are inputs to a phase detector (PD) 14, which in turn controls a charge pump 16 that charges or discharges a capacitive load 18, depending upon whether the output clock (clk) is lagging or leading the reference clock (refclk).

[0005] Note that phase detector 14 is a clocked latch whose output is a digital signal valid for a full clock cycle. This type of signal created by this circuit, referred to as a "bang-bang" control signal type, has constant amplitude and a direction dependent on the polarity of the phase error (in contrast to a linear control signal where the phase detector produces a signal proportional to the phase error). Charge pump 16 is a push-pull current source that injects a current into a capacitive load 18 for the duration of a clock cycle. The charge pump current polarity is either positive (charging) or negative (discharging) into the load. As the period of the clock signal becomes longer (lower frequency), the magnitude of the voltage swings on the control node of the voltage controlled delay line Vc becomes larger, and consequently, more jitter is produced on the output of delay chain 12. In other words, the charge being loaded onto the control voltage Vc is proportional to the cycle time of the DLL.

**[0006]** Since DLLs typically are required to operate over a wide frequency range (typically a ratio of 2 to 1), it is important to minimize jitter over the entire frequency range. Accordingly, a need exists for an enhanced DLL circuit that can minimize jitter, particularly for processing low frequency clock periods. **[0007]** The present invention addresses the above-mentioned problems, as well as others, by providing a DLL that utilizes a switched capacitor circuit as a charge pump to completely eliminate the dependence of control voltage steps on cycle time. Separate clock phases are developed to control the capacitor switching.

**[0008]** In a first aspect, the invention provides a delay locked loop (DLL) circuit having a charge pump gain independent of frequency, comprising: a switched capacitor charge pump configured with an "H" driver output stage; a phase detector; a capacitor; and a voltage controlled delay line.

**[0009]** In a second aspect, the invention provides a method of controlling a charge pump gain from a charge pump to a voltage controlled delay line in a delay locked loop (DLL) circuit, comprising: generating a charge signal and a dump signal during each period of a reference clock signal; charging a first capacitor and a second capacitor in response to the charge signal; dumping a positive charge from the first capacitor and a negative charge from the second capacitor to an output stage of the charge pump in response to the dump signal; and selectively loading either the positive charge or the negative charge to a capacitive element on the voltage controlled delay line in response to an input signal from a phase detector.

[0010] In a third aspect, the invention provides an integrated circuit having a delay locked loop (DLL) that includes a charge pump for providing a charge to a capacitive element on a voltage controlled delay line of the DLL, wherein the charge is independent of a cycle time of the DLL, and wherein the charge pump comprises: a charge/ dump signal generation stage that generates a charge signal and a dump signal during each period of a reference clock signal; a first switched capacitor stage that charges a first capacitor in response to the charge signal and dumps a positive charge from the first capacitor in response to the dump signal; a second switched capacitor stage that charges a second capacitor in response to the charge signal and dumps a negative charge from the second capacitor in response to the dump signal; and an output stage that selectively loads either the positive charge or the negative charge to the capacitive element on the voltage controlled delay line in response to an input signal from a phase detector.

**[0011]** In a fourth aspect, the invention provides a method for providing a constant gain for a charge pump component of a delay locked loop (DLL), the method comprising: providing a switched capacitor stage responsive to a charge phase for charging a capacitor and a dump phase for dumping the capacitor; and aligning the charge phase and the dump phase such that a control voltage provided by the charge pump is independent of a frequency of a DLL charge and discharge phase.

**[0012]** In a fifth aspect, the invention provides delay locked loop (DLL) having a charge pump that comprises: an "H" driver output stage; a first switched capacitor stage for dumping a predetermined positive charge into the "H" driver output stage from a first capacitor during each period of a reference clock; and a second switched capacitor stage for dumping a predetermined negative charge into the "H" driver output stage from a second capacitor during each period of the reference clock.

**[0013]** Advantages of this circuit include: less jitter compared to a current source charge pump; no need for a separate current reference circuit (e.g., band gap) and associated wiring between the current reference and the charge pumps in applications having several DLLs; and a constant charge pump gain with manufacturing process variations due to excellent integrated circuit process tracking between switched capacitor source and capacitor load.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0014]** These and other features of this invention will be more readily understood from the following detailed description of the various aspects of the invention taken in conjunction with the accompanying drawings in which:

[0015] FIG. 1 depicts a prior art DLL circuit.

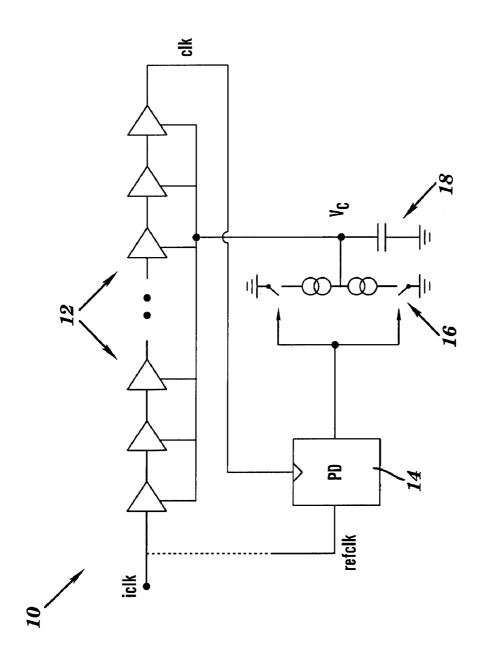

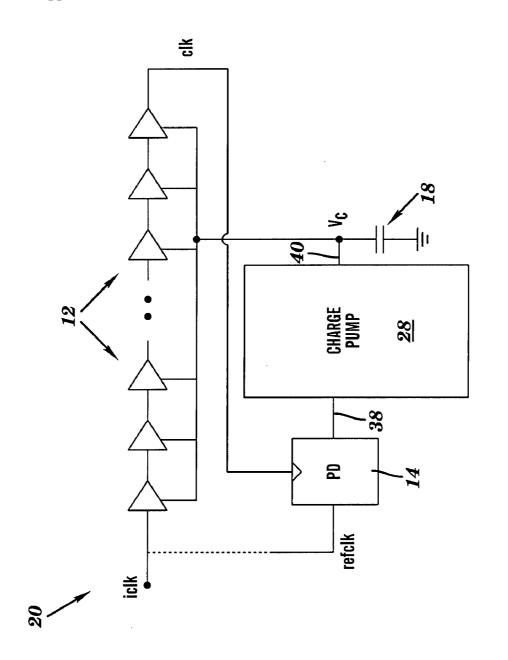

**[0016]** FIG. **2** depicts a DLL circuit having a switched capacitor charge pump circuit in accordance with an embodiment of the present invention.

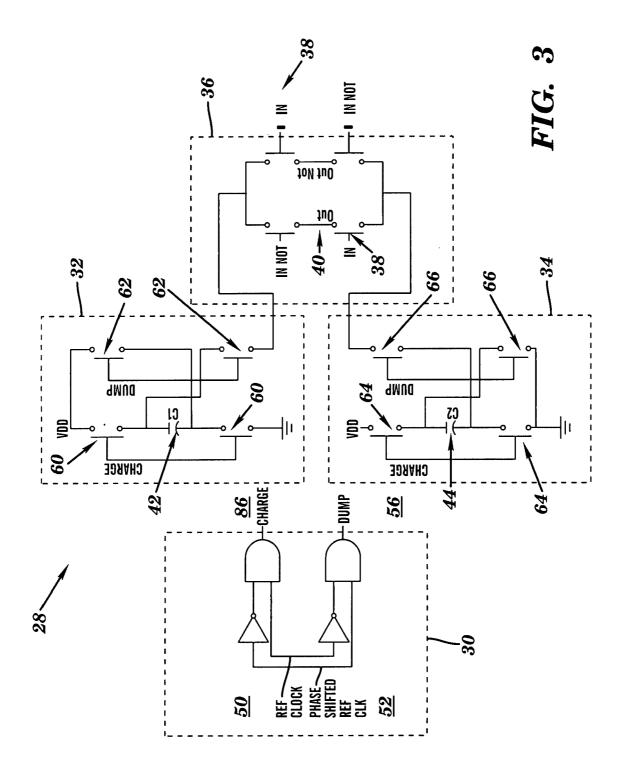

**[0017]** FIG. **3** depicts a switched capacitor charge pump circuit in accordance with an embodiment of the present invention.

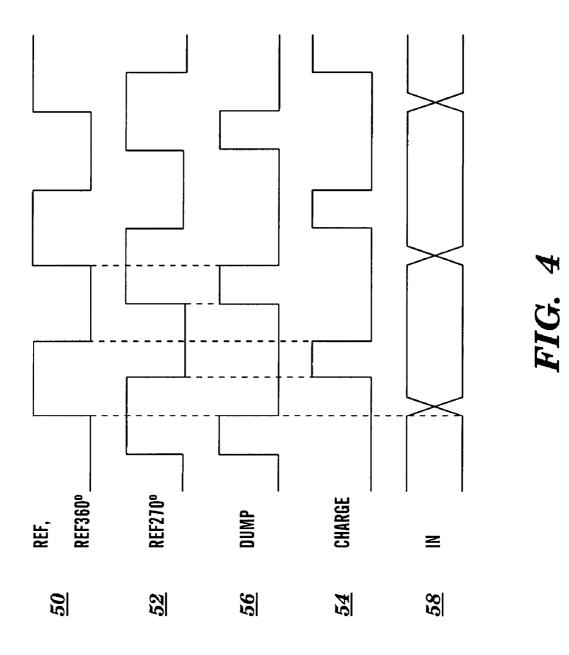

**[0018]** FIG. **4** depicts wave form diagram showing the charge and dump signals in accordance with an embodiment of the present invention.

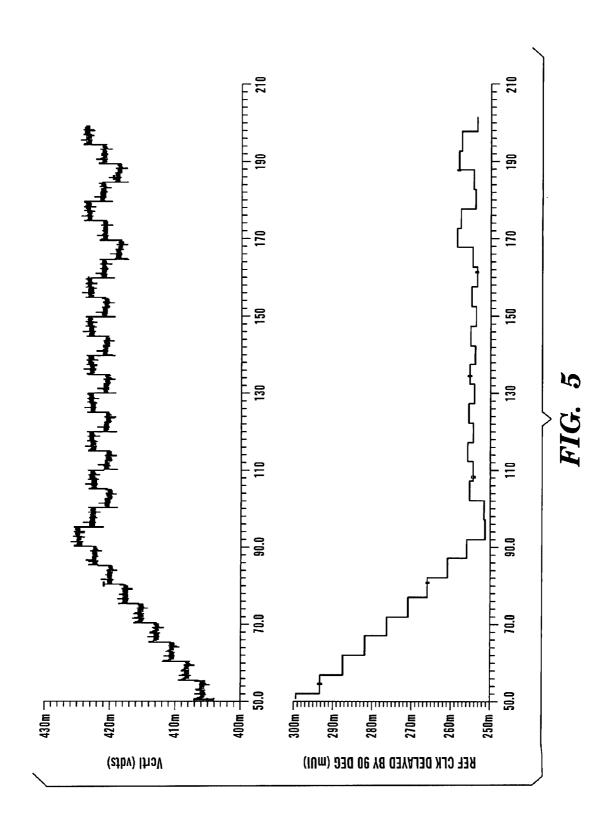

**[0019]** FIG. **5** depicts resulting experimental graphs for a DLL having a switched capacitor charge pump circuit in accordance with an embodiment of the present invention.

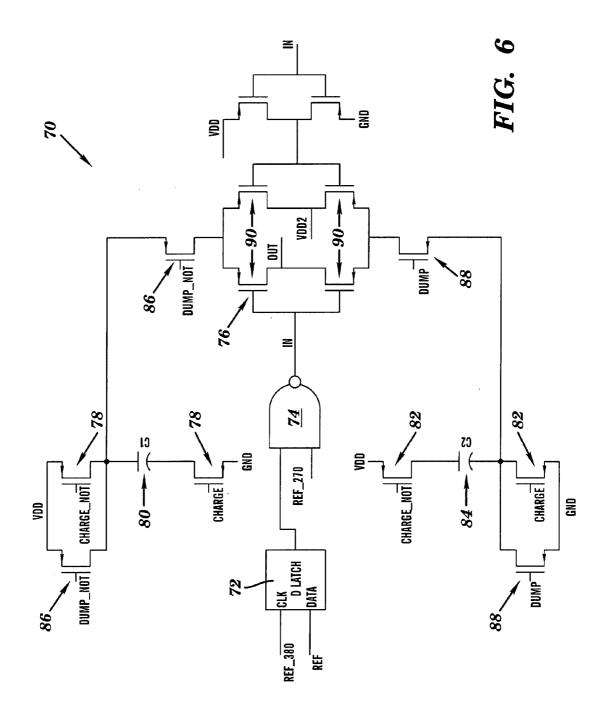

**[0020]** FIG. **6** depicts an integrated circuit implementation of a switched capacitor charge pump circuit using FETs in accordance with an embodiment the present invention.

# DETAILED DESCRIPTION OF THE INVENTION

[0021] FIG. 2 depicts a delay locked loop (DLL) circuit 20 that is similar in implementation to the prior art circuit shown in FIG. 1, with the exception that DLL circuit 20 includes a switched capacitor charge pump 28 that provides a charge that is independent of the cycle time of the DLL. Switched capacitor charge pump 28 includes an input 38 coupled to an output of phase detector (PD) 14, and an output 40 coupled to a capacitive load 18 that resides on a voltage control delay line Vc.

[0022] FIG. 3 depicts a schematic diagram of an illustrative switched capacitor charge pump 28 that includes: a charge/dump signal generation stage 30; a pair of switched capacitor stages 32, 24; and output stage 36.

[0023] Charge/dump signal generation stage 30 takes as input a reference clock 50 and a phase shifted reference clock 52 and outputs a charge signal 54 and dump signal 56 during each period of reference clock 50. FIG. 4 illustrates a wave form diagram for creating charge signal 54 and dump signal 56. The diagram of FIG. 4 includes reference clock 50, a 270 degree phase shifted reference clock 52, dump signal 56 and charge signal 54. The width and timing of the dump signal 56 is defined by the leading edge of the 270 degree phase shifted reference clock 52 and the leading edge of reference clock 50. The width and timing of charge signal 54 is defined by the trailing edge of the 270 degree phase shifted reference clock 52 and the leading edge of reference clock 50. The width and timing of charge signal 54 is defined by the trailing edge of the 270 degree phase shifted reference clock 52 and the trailing edge of reference clock 53 and the trailing edge of the 250 degree phase shifted reference clock 54 and the trailing edge of the 250 degree phase shifted reference clock 54 and the trailing edge of the 250 d

clock 50. Dump and charge signals 56, 54 are timed so as not to interfere with any transient input signals received in the charge pump output stage 36 (FIG. 3), which is shown as IN signal 58 in the waveform diagram. The charge and dump phases are aligned so that the latch outputs of the phase detector latch are resolved well before the dump phase is initiated. This timing resolves the charge direction before the switched capacitors are dumped. This timing occurs because signal IN 58 is the output of a latch having signal Ref360 as the clock input. Since Ref360 nominally has the same phase as reference clock 50 (Ref), signal IN 58 will change state when clock 50 (Ref) changes state. It is evident from FIG. 4 that this timing ensures that IN 58 is resolved (does not change state) during the dump cycle. Alternatively, IN 58 can also be resolved at the time of the falling edge of clock 50 (Ref) by changing the polarities of the latch and latch input.

[0024] Returning to FIG. 3, the charge pump output stage 36, which is referred to as an "H" driver configuration, includes both input node 38 (IN) and output node 40 (OUT) of the charge pump 28. The particular "H" driver configuration includes a pair of opposed In/In Not nodes, an Out node and an Out Not node. The Out Not node may be used to control one side of a capacitor in a differential voltage controlled system, but in the present embodiment it will be tied to a constant voltage source. This arrangement minimizes glitching of output node 40 during switching transients. In a single ended implementation, Out Not node can be tied to a constant voltage approximately equal to the voltage of Out, i.e., output node 40. Output stage 36 is coupled to a first switched capacitor stage 32 having a first switched capacitor 42 (C1) and a second switched capacitor stage 34 having a second switched capacitor 44 (C2).

[0025] Switched capacitors 42, 44 are each charged and dumped once per cycle in response to charge 54 and dump 56 signals generated by charge/dump signal generation stage 30. Switched capacitor stage 32 is configured to dump a positive charge, and switched capacitor stage 34 is configured to dump a negative charge. The respective charges stored on switched capacitors 42, 44 are injected into either the Out or the Out Not node depending on the state of input node IN 38. The state of input node IN 38 is a digital signal that is the output of phase detector 28 (FIG. 2). Thus, for instance, if the state of input node IN 38 is high, then the negative charge from switched capacitor 44 will be dumped to output node Out 40 and the positive charge from switched capacitor 42 will be dumped to Out Not. Conversely, if the state of input node IN 38 is low, then the positive charge from switched capacitor 42 will be dumped to output node Out 40 and the negative charge from switched capacitor 44 will be dumped to Out Not.

[0026] Switched capacitor stage 32 includes: a first pair of switches 60 that connect switched capacitor 42 (C1) to VDD and ground, which causes switched capacitor 42 (C1) to be charged when a charge signal 54 is received from the charge/dump signal generation stage 30; and a second pair of switches 62 that cause the charge stored on switched capacitor 42 (C1) to be dumped into output stage 36. Similarly, switched capacitor stage 34 includes: a first pair of switches 64 that connect switched capacitor 44 (C2) to VDD and ground, and causes switched capacitor 44 (C2) to be charged when a charge signal 54 is received from the charge/dump signal generation stage 30; and a second pair of switches 64 that connect switched capacitor 44 (C2) to VDD and ground, and causes switched capacitor 44 (C2) to be charged when a charge signal 54 is received from the charge/dump signal generation stage 30; and a second pair

of switches **66** that cause a negative charge stored on switched capacitor **44** (C**2**) to be dumped into output stage **36**. Accordingly, output stage **36** will always receive a predetermined constant charge. During the charge phase, switched capacitors **42** (C**1**) and **44** (C**2**) are each charged to a voltage of +VDD. During the dump phase, the voltage on switched capacitor **42** (C**1**) will be  $V_{OUT}$  -VDD (where  $V_{OUT}$  is the voltage of node Out **40**) and the voltage on switched capacitor **44** (C**2**) will be  $-V_{OUT}$ . Assuming that the voltage  $V_{OUT}$  is VDD/2, the net change in voltage for each capacitor that is dumped into Out **40** is thus 1.5\*VDD during each clock cycle, regardless of the clock period.

**[0027]** FIG. **5** depicts experimental results generated using a switched capacitor charge pump **28** such as that described above. The top trace depicts the voltage on the storage capacitor Vc as a function of time, while the bottom trace depicts the phase in milli-unit intervals (mUI) of the output of delay line that is 90 degrees out of phase with the input clock **50**. As can be seen in the bottom trace, the signal stabilizes at about 250 mUI, which indicates good performance (250 mUI=90 degrees).

[0028] FIG. 6 depicts an integrated circuit implementation 70 of a switched capacitor charge pump 28 that utilizes FETs to control the switching operations. As shown, NAND gate 74 resides between phase latch detector 72 and an H-driver 76. NAND gate 74 ensures locking of the DLL, and is also necessary to initialize the DLL by charging capacitive load 18 (see FIG. 2) to VDD before the circuit is turned on.

[0029] In addition, integrated circuit implementation 70 includes: a first set of charge FETs 78, which when activated cause capacitor 80 to charge; a second set of charge FETs 82, which when activated cause capacitor 84 to charge; a first set of dump FETs 86, which when activated cause a positive charge to be dumped from capacitor 80; a second set of dump FETs 88, which when activated cause a positive charge to be dumped from capacitor 84; and the H-driver 76 configuration that includes opposed pairs of FETs 90.

**[0030]** The foregoing description of the invention has been presented for purposes of illustration and description. It is not intended to be exhaustive or to limit the invention to the precise form disclosed, and obviously, many modifications and variations are possible. Such modifications and variations that may be apparent to a person skilled in the art are intended to be included within the scope of this invention as defined by the accompanying claims.

#### What is claimed is:

**1**. A delay locked loop (DLL) circuit having a charge pump gain independent of frequency, comprising:

- a switched capacitor charge pump configured with an "H" driver output stage;

- a phase detector;

- a capacitor; and

- a voltage controlled delay line.

**2**. A delay locked loop (DLL) circuit having a charge pump gain independent of frequency, comprising:

a switched capacitor charge pump configured with an "H" driver output stage that feeds a signal into a first switched capacitor stage configured for dumping a charge into an output stage from a first capacitor;

a phase detector;

- a capacitor; and

- a voltage controlled delay line.

**3**. The delay lock loop (DLL) of claim 2, wherein the switched capacitor charge pump generates a charge signal and a dump signal during each period of a reference clock that is fed into the first switched capacitor stage.

**4**. The delay lock loop (DLL) of claim 3, wherein the charge comprises a positive charge.

\* \* \* \* \*