(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4524652号

(P4524652)

(45) 発行日 平成22年8月18日(2010.8.18)

(24) 登録日 平成22年6月11日(2010.6.11)

(51) Int.Cl.

F 1

H03M 1/56 (2006.01)

H03M 1/56

H03M 1/08 (2006.01)

H03M 1/08

H04N 5/335 (2006.01)

H04N 5/335

H04N 5/335

A

E

Z

請求項の数 9 (全 34 頁)

(21) 出願番号

特願2005-197044 (P2005-197044)

(22) 出願日

平成17年7月6日(2005.7.6)

(65) 公開番号

特開2007-19682 (P2007-19682A)

(43) 公開日

平成19年1月25日(2007.1.25)

審査請求日

平成20年6月26日(2008.6.26)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 遠山 隆之

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 鈴木 敦史

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 福島 範之

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】 A D変換装置並びに半導体装置

(57) 【特許請求の範囲】

【請求項 1】

アナログ信号生成部から出力されたアナログ信号をデジタル信号に変換するための参照信号を生成する参照信号生成部と、

前記アナログ信号が比較部の第1の入力端子に入力され、前記参照信号生成部から出力された前記参照信号が前記比較部の第2の入力端子に入力され、プリセットスイッチで前記第1と第2の入力端子と出力端子間を短絡した後該プリセットスイッチを開放して前記アナログ信号と前記参照信号を比較し、当該比較結果を前記出力端子から出力する比較部と、該比較部における比較処理と並行して、所定のカウントクロックでカウント処理を行ない、前記比較部から比較結果が出力されて、比較処理が完了した時点のカウント値を保持するカウンタ部と、

前記比較部と前記アナログ信号生成部がそれぞれ複数設けられ、該複数の比較部は複数のブロックに分離され、該分離されたブロック内で前記参照信号生成部の出力端子が各信号配線を介して該信号配線に対応するそれぞれの前記比較部の入力端子に接続され、前記参照信号が、前記信号配線を介して前記比較部に供給される参照信号供給インターフェース部

を備えた A D 変換装置であって、

前記参照信号供給インターフェース部は、前記参照信号生成部と前記信号配線間に接続され、前記参照信号生成部で生成された参照信号を受け取り、前記各信号配線を介して該信号配線に対応するそれぞれの比較部に供給する緩衝増幅器を有する

ことを特徴とする A/D 変換装置。

**【請求項 2】**

前記参照信号供給インターフェース部は、複数の前記比較部に対して 1 つの前記緩衝増幅器を有している

ことを特徴とする請求項 1 に記載の A/D 変換装置。

**【請求項 3】**

前記参照信号供給インターフェース部は、前記緩衝増幅器を、前記複数の比較部のそれぞれに 1 つずつ有している

ことを特徴とする請求項 2 に記載の A/D 変換装置。

**【請求項 4】**

前記緩衝増幅器の周波数帯域は、前記比較部の周波数帯域と同等もしくはより広い

ことを特徴とする請求項 2 に記載の A/D 変換装置。

**【請求項 5】**

入射された電磁波に対応する電荷を生成する電荷生成部および前記電荷生成部により生成された電荷に応じたアナログの単位信号を生成する単位信号生成部を単位構成要素内に含む有効領域を備え、かつ前記単位信号をデジタルデータに変換する機能要素として、前記単位信号をデジタルデータに変換するための参照信号を生成する参照信号生成部と、前記単位信号生成部の出力端子が前記比較部の第 1 の入力端子に接続され、前記参照信号生成部の出力端子が前記比較部の第 2 の入力端子に接続され、前記単位信号と前記参照信号を比較し、当該比較結果を出力する出力端子を有する比較部と、該比較部における比較処理と並行して、所定のカウントクロックでカウント処理を行ない、前記比較部の出力端子から比較結果が出力されて、比較処理が完了した時点のカウント値を保持するカウンタ部と

前記比較部と前記アナログ信号生成部がそれぞれ複数設けられ、該複数の比較部は複数のブロックに分離され、該分離されたブロック内で前記参照信号生成部の出力端子が各信号配線を介して該信号配線に対応するそれぞれの前記比較部の入力端子に接続され、前記参照信号が、前記信号配線を介して前記比較部に供給される参照信号供給インターフェース部

を、備えた物理量分布検知のための半導体装置であって、

前記参照信号供給インターフェース部は、前記参照信号生成部と前記信号配線間に接続され、前記参照信号生成部で生成された参照信号を受け取り、前記信号配線を介して前記比較部に供給する緩衝増幅器を有し、該緩衝増幅器は、前記単位信号生成部の出力段の回路構成と同じ回路構成である

ことを特徴とする半導体装置。

**【請求項 6】**

前記緩衝増幅器は、トランジスタで構成されたソースフォロワ回路を有する

ことを特徴とする請求項 5 に記載の半導体装置。

**【請求項 7】**

前記ソースフォロワ回路を構成するトランジスタは、前記単位信号生成部の出力段のソースフォロワ回路を構成するトランジスタと同じ特性のものである

ことを特徴とする請求項 6 に記載の半導体装置。

**【請求項 8】**

前記ソースフォロワ回路を構成するトランジスタは、前記単位信号生成部の出力段のソースフォロワ回路を構成するトランジスタと、酸化膜厚および閾値電圧が等しい

ことを特徴とする請求項 6 に記載の半導体装置。

**【請求項 9】**

前記ソースフォロワ回路を構成するトランジスタは、前記単位信号生成部の出力段のソースフォロワ回路を構成するトランジスタと、サイズ比が等しい

ことを特徴とする請求項 6 に記載の半導体装置。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、アナログ信号をデジタル信号に変換する A D (Digital to Digital) 変換装置と、この A D 変換装置を備えた、撮像装置などの半導体装置に関する。より詳細には、所定の傾きで変化する参照信号と処理対象のアナログ信号とを比較し、その比較時間をカウントする、いわゆるシングルスロープ積分型あるいはランプ信号比較型といわれる A D 変換の仕組みに関する。

**【背景技術】****【0002】**

電子機器においては、アナログ信号をデジタル信号に変換する A D 変換装置が種々使用されている。10

**【0003】**

たとえば、光や放射線などの外部から入力される電磁波に対して感応性をする単位構成要素（たとえば画素）をライン状もしくはマトリクス状に複数個配列してなる物理量分布検知半導体装置が様々な分野で使われている。

**【0004】**

たとえば、映像機器の分野では、物理量のうちの光（電磁波の一例）を検知する C C D (Charge Coupled Device) 型あるいは M O S (Metal Oxide Semiconductor) や C M O S (Complementary Metal-oxide Semiconductor) 型の固体撮像装置が使われている。これらは、単位構成要素（固体撮像装置にあっては画素）によって電気信号に変換された物理量分布を電気信号として読み出す。ここで“固体”とは半導体製であることを意味している。20

**【0005】**

また、固体撮像装置の中には、電荷生成部で生成された信号電荷に応じた画素信号を生成する画素信号生成部に增幅用の駆動トランジスタを有する增幅型固体撮像素子（A P S ; Active Pixel Sensor / ゲインセルともいわれる）構成の画素を備えた増幅型固体撮像装置がある。たとえば、C M O S 型固体撮像装置の多くはそのような構成をなしている。

**【0006】**

このような増幅型固体撮像装置において画素信号を外部に読み出すには、複数の単位画素が配列されている画素部に対してアドレス制御をし、個々の単位画素からの信号を任意に選択して読み出すようにしている。つまり、増幅型固体撮像装置は、アドレス制御型の固体撮像装置の一例である。30

**【0007】**

たとえば、単位画素がマトリクス状に配された X - Y アドレス型固体撮像素子の一種である増幅型固体撮像素子は、画素そのものに増幅機能を持たせるために、M O S 構造などの能動素子（M O S トランジスタ）を用いて画素を構成している。すなわち、光電変換素子であるフォトダイオードに蓄積された信号電荷（光電子）を前記能動素子で増幅し、画像情報として読み出す。

**【0008】**

この種の X - Y アドレス型固体撮像素子では、たとえば、画素トランジスタが 2 次元行列状に多数配列されて画素部が構成され、ライン（行）ごとあるいは画素ごとに入射光に対応する信号電荷の蓄積が開始され、その蓄積された信号電荷に基づく電流または電圧の信号がアドレス指定によって各画素から順に読み出される。40

**【0009】**

ここで、M O S (C M O S を含む) 型においては、アドレス制御の一例として、1 行分を同時にアクセスして行単位で画素信号を画素部から読み出して外部に出力する方式が多く用いられている。また、画素部から読み出されたアナログの画素信号を、アナログ - デジタル変換装置（A D 変換装置；Analog Digital Converter）にてデジタル信号に変換してから外部に出力する方式が採られることがある（たとえば特許文献 1 ~ 5 を参照）。

**【0010】**

10

20

30

40

50

【特許文献1】特開2000-152082号公報

【特許文献2】特開2002-232291号公報

【特許文献3】米国特許第5,877,715号公報

【特許文献4】米国特許第5,920,274号公報

【特許文献5】米国特許第6,344,877号公報

【0011】

上記特許文献1～5に記載のように、A/D変換の方式には回路規模や処理速度や分解能などの観点から様々なものがあり、その中には、アナログの単位信号とデジタル信号に変換するための単調に変化する参照信号とを比較するとともに、この比較処理と並行してカウント処理を行ない、比較処理が完了した時点のカウント値に基づいて単位信号のデジタル信号を取得する、いわゆるシングルスロープ積分型あるいはランプ信号比較型といわれるA/D変換方式がある。10

【発明の開示】

【発明が解決しようとする課題】

【0012】

しかしながら、従来のシングルスロープ積分型のA/D変換方式では、複数ある電圧比較部を駆動するための各種信号線が共通配線となっており、ある電圧比較部で発生した雑音が、これらの共通配線を通じて他の電圧比較部に伝達され、その他の電圧比較部における動作に影響を及ぼしてしまい、その結果として、A/D変換処理に悪影響を与えててしまう。

【0013】

本発明は、上記事情に鑑みてなされたものであり、ある電圧比較部で発生した雑音が他の電圧比較部における処理に悪影響を及ぼさないようにする仕組みを提案することを目的とする。

【課題を解決するための手段】

【0014】

本発明に係る仕組みにおいては、参照信号生成部で生成された参照信号を複数の比較部に供給するに当たって、複数の比較部を複数のブロックに分離し、該分離したブロック内の各比較部に单一の信号配線で供給するのではなく、それぞれ異なる信号配線すなわち複数の信号配線を介して供給する参照信号供給インターフェース部を備えるものとした。

【0015】

この際の考え方としては、1つの参照信号生成部で生成され1つの信号経路で伝達された参照信号を複数の信号経路に分けることで複数の比較部に伝達する第1の手法を探ることが考えられる。あるいは、参照信号生成部そのものを複数用意し、それらの出力をそのまま伝達する第2の手法を探ることも考えられる。

【0016】

第1の手法を探る際には、複数の比較部の全体を、さらに複数の比較部を有するサブブロックに分け、このサブブロックごとに1つの信号経路で参照信号を伝達してもよいし、1つの比較部に対して1つの信号経路で参照信号を伝達する完全な個別対応を探ってもよい。

【0017】

ここで、1つの信号経路を複数の信号経路に分けて伝達する手法を探るに当たっては、参照信号生成部側の信号配線を入力側とし、比較部側の信号配線を出力側とする緩衝増幅器を利用するのが都合がよい。それぞれ異なる信号配線を介して参照信号を各比較部に伝達するので、結果的に、緩衝増幅器を複数使用し、1つの参照信号生成部で生成された参照信号を、これらの緩衝増幅器で分配することになる。緩衝増幅器を介することで、参照信号線をツリー構造にするのである。こういった点では、緩衝増幅器を多段構成にして分配することもできる。

【発明の効果】

【0018】

本発明によれば、参照信号を複数の比較部に供給するに当たって、それぞれ異なる信号

10

20

30

40

50

配線を介して供給するようにした。これにより、比較部の参照信号の入力段を複数ブロックに分離する構造を探ることができ、あるブロックに属する比較部の参照信号入力段に雑音成分が発生しても、分離された方のブロックに属する比較部の参照信号入力段には、その雑音成分が伝達されないようにすることができる。これにより、ある電圧比較部で発生した雑音が他の電圧比較部における処理に悪影響を及ぼさないようにすることができる。

#### 【発明を実施するための最良の形態】

##### 【0019】

以下、図面を参照して本発明の実施形態について詳細に説明する。なお、以下においては、X-Yアドレス型の固体撮像装置の一例である、CMOS撮像素子をデバイスとして使用した場合を例に説明する。また、CMOS撮像素子は、全ての画素がNMOSあるいはPMOSよりなるものであるとして説明する。10

##### 【0020】

ただしこれは一例であって、対象となるデバイスはMOS型の撮像デバイスに限らない。光や放射線などの外部から入力される電磁波に対して感応性をする単位構成要素をライン状もしくはマトリクス状に複数個配列してなる物理量分布検知用の半導体装置の全てに、後述する全ての実施形態が同様に適用できる。

##### 【0021】

なお、本願発明において、撮像装置とは、物理量の変化を検知する複数の検知部と、それぞれの検知部で検知した物理量の変化に基づいて単位信号を出力する単位信号生成部とを単位構成要素内に含み、この単位構成要素が所定の順に配された物理量分布検知のための装置を使用し、物理量についての所定の検知条件の元で取得された単位信号に基づいて、所定目的用の物理情報を取得する物理情報取得装置の総称である。20

##### 【0022】

###### <固体撮像装置の構成>

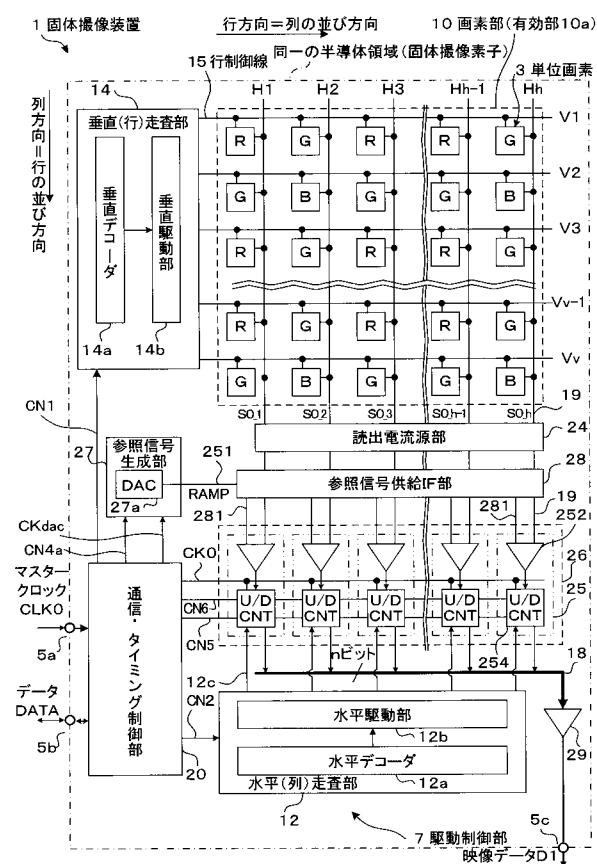

図1は、本発明に係る半導体装置の一実施形態であるCMOS固体撮像装置(CMOSイメージセンサ)の概略構成図である。なお、このCMOS固体撮像装置は、電子機器の一態様でもある。

##### 【0023】

固体撮像装置1は、入射光量に応じた信号を出力する受光素子(電荷生成部の一例)を含む複数個の画素が行および列に配列された(すなわち2次元マトリクス状の)画素部を有し、各画素からの信号出力が電圧信号であって、CDS(Correlated Double Sampling; 相関2重サンプリング)処理機能部やデジタル変換部(ADC; Analog Digital Converter)などが列並列に設けられているものである。30

##### 【0024】

“列並列にCDS処理機能部やデジタル変換部が設けられている”とは、垂直列の垂直信号線19に対して実質的に並列に複数のCDS処理機能部やデジタル変換部が設けられていることを意味する。複数の各機能部は、デバイスを平面視したときに、ともに画素部(撮像部)10に対して列方向の一方の端縁側(図の下側に配されている出力側)にのみ配されている形態のものであってもよいし、画素部10に対して列方向の一方の端縁側(図の下側に配されている出力側)とその反対側である他方の端縁側(図の上側)に分けて配されている形態のものであってもよい。後者の場合、行方向の読み出走査(水平走査)を行なう水平走査部も、各端縁側に分けて配して、それぞれが独立に動作可能に構成するのがよい。40

##### 【0025】

たとえば、列並列にCDS処理機能部やデジタル変換部が設けられている典型例としては、撮像部の出力側に設けたカラム領域と呼ばれる部分に、CDS処理機能部やデジタル変換部を垂直列ごとに設け、順次出力側に読み出すカラム型のものである。また、カラム型に限らず、隣接する複数(たとえば2つ分)の垂直信号線19(垂直列)に対して1つのCDS処理機能部やデジタル変換部を割り当てる形態や、N本おき(Nは正の整数;間にN-1本を配する)のN本分の垂直信号線19(垂直列)に対して1つのCDS処理機50

能部やデジタル変換部を割り当てる形態などを採ることもできる。

**【0026】**

カラム型を除くものは、何れの形態も、複数の垂直信号線 19（垂直列）が 1 つの CDS 处理機能部やデジタル変換部を共通に使用する構成となるので、画素部 10 側から供給される複数列分の画素信号を 1 つの CDS 处理機能部やデジタル変換部に供給する切替回路（スイッチ）を設ける。なお、後段の処理によっては、出力信号を保持するメモリを設けるなどの対処が必要になる。

**【0027】**

何れにしても、複数の垂直信号線 19（垂直列）に対して 1 つの CDS 处理機能部やデジタル変換部を割り当てる形態などを採ることで、各画素信号の信号処理を画素列単位で読み出した後に行なうことと、同様の信号処理を各単位画素内で行なうものに比べて、各単位画素内の構成を簡素化し、イメージセンサの多画素化、小型化、低コスト化などに対応できる。10

**【0028】**

また、列並列に配された複数の信号処理部にて 1 行分の画素信号を同時並行処理することができる所以、出力回路側やデバイスの外部で 1 つの CDS 处理機能部やデジタル変換部にて処理を行なう場合に比べて、信号処理部を低速で動作させることができ、消費電力や帯域性能やノイズなどの面で有利である。逆に言えば、消費電力や帯域性能などを同じにする場合、センサ全体の高速動作が可能となる。

**【0029】**

なお、カラム型の構成の場合、低速で動作させることができ消費電力や帯域性能やノイズなどの面で有利であるとともに切替回路（スイッチ）が不要である利点もある。以下の実施形態では、特に断りのない限り、このカラム型で説明する。20

**【0030】**

図 1 に示すように、固体撮像装置 1 は、画素形状が概ね正方状の複数の単位画素（単位構成要素の一例）3 が行および列（つまり正方格子状）に配列された画素部（撮像部）10 と、画素部 10 の外側に設けられた駆動制御部 7 と、画素部 10 の単位画素 3 に画素信号読出用の動作電流（読出電流）を供給する読出電流源部 24 と、垂直列ごとに配されたカラム A/D 回路 25 を有するカラム処理部 26 と、カラム処理部 26 に A/D 変換用の参照電圧を供給する参照信号生成部 27 と、参照信号生成部 27 で生成された参照信号をカラム処理部 26 の各カラム A/D 回路 25 に供給する参照信号供給インターフェース（IF）部 28 と、出力部 29 とを備えている。これらの各機能部は、同一の半導体基板上に設けられている。30

**【0031】**

なお、カラム処理部 26 の前段または後段には、必要に応じて信号増幅機能を持つ AGC (Auto Gain Control) 回路などをカラム処理部 26 と同一の半導体領域に設けることも可能である。カラム処理部 26 の前段で AGC を行なう場合にはアナログ増幅、カラム処理部 26 の後段で AGC を行なう場合にはデジタル増幅となる。n ビットのデジタル信号を単純に増幅してしまうと、階調が損なわれてしまう可能性があるため、どちらかというとアナログにて増幅した後にデジタル変換するのが好ましいと考えられる。40

**【0032】**

駆動制御部 7 は、画素部 10 の信号を順次読み出すための制御回路機能を備えている。たとえば、駆動制御部 7 としては、列アドレスや列走査を制御する水平走査部（列走査回路）12 と、行アドレスや行走査を制御する垂直走査部（行走査回路）14 と、内部クロックを生成するなどの機能を持つ通信・タイミング制御部 20 とを備えている。

**【0033】**

図 1 では、簡単のため行および列の一部を省略して示しているが、現実には、各行や各列には、数十から数千の単位画素 3 が配置されて画素部 10 が構成される。このうち、上下左右に設けられる黒画素などの基準画素領域を除く部分が実際の画像形成に関わる有効部 10a となる。単位画素 3 は、典型的には、受光素子（電荷生成部）としてのフォトダ

イオードと、増幅用の半導体素子（たとえばトランジスタ）を有する画素内アンプとから構成される。

**【0034】**

画素内アンプとしては、たとえばフローティングディフュージョンアンプ構成のものが用いられる。一例としては、電荷生成部に対して、電荷読出部（転送ゲート部／読出ゲート部）の一例である読出選択用トランジスタ、リセットゲート部の一例であるリセットトランジスタ、垂直選択用トランジスタ、およびフローティングディフュージョンの電位変化を検知する検知素子の一例であるソースフォロア構成の増幅用トランジスタを有する、CMOSセンサとして汎用的な4つのトランジスタからなる構成のものを使用することができる。

10

**【0035】**

あるいは、特許第2708455号公報に記載のように、電荷生成部により生成された信号電荷に対応する信号電圧を増幅するための、ドレイン線（D R N）に接続された増幅用トランジスタと、電荷生成部をリセットするためのリセットトランジスタと、垂直シフトレジスタより転送配線（T R F）を介して走査される読出選択用トランジスタ（転送ゲート部）を有する、3つのトランジスタからなる構成のものを使用することもできる。

**【0036】**

なお、固体撮像装置1は、色分解（色分離）フィルタを使用することで、画素部10をカラー撮像対応にすることができます。すなわち、画素部10における各電荷生成部（フォトダイオードなど）の電磁波（本例では光）が入射される受光面に、カラー画像を撮像するための複数色の色フィルタの組合せからなる色分解フィルタの何れかの色フィルタを、たとえばいわゆるベイヤ（B a y e r）配列などにして設けることで、カラー画像撮像対応とする。

20

**【0037】**

単位画素3は、行選択のための行制御線15を介して垂直走査部14と、また垂直信号線19を介してカラムA D回路25が垂直列ごとに設けられているカラム処理部26と、それぞれ接続されている。ここで、行制御線15は垂直走査部14から画素に入る配線全般を示す。

**【0038】**

水平走査回路12は、カラム処理部26からカウント値を読み出す読出走査部の機能を持つ。水平走査部12や垂直走査回路14などの駆動制御部7の各要素は、画素部10とともに、半導体集積回路製造技術と同様の技術を用いて単結晶シリコンなどの半導体領域に一体的に形成され、半導体システムの一例である固体撮像素子（撮像デバイス）として構成される。

30

**【0039】**

水平走査部12や垂直走査部14は、後述のようにデコーダを含んで構成され、通信・タイミング制御部20から与えられる制御信号C N 1, C N 2に応答してシフト動作（走査）を開始するようになっている。このため、行制御線15には、単位画素3を駆動するための種々のパルス信号（たとえば、リセットパルスR S T、転送パルスT R F、D R N制御パルスD R Nなど）が含まれる。

40

**【0040】**

通信・タイミング制御部20は、図示しないが、各部の動作に必要なクロックや所定タイミングのパルス信号を供給するタイミングジェネレータT G（読出アドレス制御装置の一例）の機能ブロックと、端子5aを介してマスタークロックCLK0を受け取り、また端子5bを介して動作モードなどを指令するデータD A T Aを受け取り、さらに固体撮像装置1の情報を含むデータを出力する通信インターフェースの機能ブロックとを備える。

**【0041】**

たとえば、水平アドレス信号を水平デコード12aへ、また垂直アドレス信号を垂直デコード14aへ出力し、各デコード12a, 14aは、それを受け対応する行もしくは列を選択する。

50

**【 0 0 4 2 】**

この際、単位画素3を2次元マトリックス状に配置してあるので、画素信号生成部5により生成され垂直信号線19を介して列方向に出力されるアナログの画素信号を行単位で(列並列で)アクセスし取り込む(垂直)スキャン読みを行ない、この後に、垂直列の並び方向である行方向にアクセスし画素信号(本例ではデジタル化された画素データ)を出力側へ読み出す(水平)スキャン読みを行なうようにすることで、画素信号や画素データの読み出しの高速化を図るのがよい。もちろん、スキャン読みに限らず、読み出したい単位画素3を直接にアドレス指定することで、必要な単位画素3の情報を読み出すランダムアクセスも可能である。

**【 0 0 4 3 】**

また、通信・タイミング制御部20では、端子5aを介して入力されるマスタークロック(マスタークロック)CLK0と同じ周波数のクロックCLK1や、それを2分周したクロックやより分周した低速のクロックをデバイス内の各部、たとえば水平走査部12、垂直走査部14、カラム処理部26などに供給する。以下、2分周したクロックやそれ以下の周波数のクロック全般を纏めて、低速クロックCLK2という。

**【 0 0 4 4 】**

垂直走査部14は、画素部10の行を選択し、その行に必要なパルスを供給するものである。たとえば、垂直方向の読み出行を規定する(画素部10の行を選択する)垂直デコード14aと、垂直デコード14aにて規定された読み出アドレス上(行方向)の単位画素3に対する行制御線15にパルスを供給して駆動する垂直駆動部14bとを有する。なお、垂直デコード14aは、信号を読み出す行の他に、電子シャッタ用の行なども選択する。

**【 0 0 4 5 】**

水平走査部12は、低速クロックCLK2に同期してカラム処理部26のカラムA/D回路25を順番に選択し、その信号を水平信号線(水平出力線)18に導くものである。たとえば、水平方向の読み出列を規定する(カラム処理部26内の個々のカラムA/D回路25を選択する)水平デコード12aと、水平デコード12aにて規定された読み出アドレスに従って、カラム処理部26の各信号を水平信号線18に導く水平駆動部12bとを有する。なお、水平信号線18は、たとえばカラムA/D回路25が取り扱うビット数n(nは正の整数)分、たとえば10(=n)ビットならば、そのビット数分に対応して10本配置される。

**【 0 0 4 6 】**

このような構成の固体撮像装置1において、単位画素3から出力された画素信号は、垂直列ごとに、垂直信号線19を介して、カラム処理部26のカラムA/D回路25に供給される。

**【 0 0 4 7 】**

カラム処理部26の各カラムA/D回路25は、1列分の画素のアナログ信号Soを受け、そのアナログ信号Soを処理する。たとえば、各カラムA/D回路25は、アナログ信号を、たとえば低速クロックCLK2を用いて、たとえば10ビットのデジタル信号に変換するA/D C(Analog Digital Converter)回路を持つ。

**【 0 0 4 8 】**

カラム処理部26におけるA/D変換処理としては、行単位で並列に保持されたアナログ信号を、列ごとに設けられたカラムA/D回路25を使用して、行ごとに並列にA/D変換する方法を探る。この際には、たとえば、特許公報第2532374号や学術文献“コラム間FPNのないコラム型A/D変換器を搭載したCMOSイメージセンサ”(映情学技法, IPU2000-57, pp. 79-84)などに示されているシングルスロープ積分型(あるいはランプ信号比較型)のA/D変換の手法を使用する。この手法は、簡単な構成でA/D変換器が実現できるため、並列に設けても回路規模が大きくならないという特徴を有している。

**【 0 0 4 9 】**

A/D C回路の構成については、詳細は後述するが、変換開始から参照電圧RAMPと処理対

10

20

30

40

50

象信号電圧とが一致するまでの時間に基づいて、アナログの処理対象信号をデジタル信号に変換する。このための仕組みとしては、原理的には、コンパレータ（電圧比較器）にランプ状の参照電圧RAMPを供給すると同時にクロック信号でのカウント（計数）を開始し、垂直信号線19を介して入力されたアナログの画素信号を参照電圧RAMPと比較することによってパルス信号が得られるまでカウントすることでA/D変換を行なう。

#### 【0050】

また、この際、回路構成を工夫することで、A/D変換とともに、垂直信号線19を介して入力された電圧モードの画素信号に対して、画素リセット直後の信号レベル（ノイズレベル）と真の（受光光量に応じた）信号レベルVsigtとの差分をとる処理を行なうことができる。これにより、固定パターンノイズ（FPN；Fixed Pattern Noise）やリセットノイズといわれるノイズ信号成分を取り除くことができる。10

#### 【0051】

このカラムA/D回路25でデジタル化された画素データは、水平走査部12からの水平選択信号により駆動される図示しない水平選択スイッチを介して水平信号線18に伝達され、さらに出力部29に入力される。なお、10ビットは一例であって、10ビット未満（たとえば8ビット）や10ビットを超えるビット数（たとえば14ビット）など、その他のビット数としてもよい。

#### 【0052】

このような構成によって、電荷生成部としての受光素子が行列状に配された画素部10からは、行ごとに各垂直列について画素信号が順次出力される。そして、受光素子が行列状に配された画素部10に対応する1枚分の画像すなわちフレーム画像が、画素部10全体の画素信号の集合で示されることとなる。20

#### 【0053】

<参照信号生成部とカラムA/D回路との詳細>

参照信号生成部27は、A/D変換用の参照信号を発生する機能要素であるD/A変換回路（DAC；Digital Analog Converter）27aを備える。なお、カラー画像撮像対応とする場合には、参照信号生成部27としては、色対応の変化特性（傾き）や初期値を持つ個別の参照信号を比較回路に供給することができるよう、画素部10における色分解フィルタを構成する色フィルタの色の種類や配列に応じて、A/D変換用の参照信号を発生する機能要素であるD/A変換回路を個別に備えるとともに処理対象行の切替えにより処理対象色が切り替ることに対処する切替機構を設けるのがよい。30

#### 【0054】

こうすることで、参照電圧発生器（本例ではD/A変換回路に相当）やこの参照電圧発生器からの配線を色分解フィルタを構成する色フィルタの数よりも少なくすることができる。また、色フィルタごとに参照電圧発生器を用意した場合に必要とされる各参照電圧発生器からのアナログ基準電圧（本例の参照信号に相当）を選択的に出力する垂直列ごとの選択手段（マルチプレクサ）も不要となるので、回路規模を縮小できる。カラー画素に応じた参照信号を比較器の入力側に伝達する信号線の数を、カラー画像を撮像するための色フィルタの色成分の数よりも少なくすることができる。

#### 【0055】

通信・タイミング制御部20から参照信号生成部27のD/A変換回路27aに供給する制御データCN4は、比較処理ごとのランプ電圧の傾き（変化の度合い；時間変化量）や初期値を指示する情報も含んでいる。40

#### 【0056】

D/A変換回路27aは、通信・タイミング制御部20からDAC用のカウントクロックCKdacの供給を受け、カウントクロックCKdacに同期して、たとえば線形的に減少する階段状の鋸歯状波（ランプ波形）を生成し、参照信号RAMPを介してカラムA/D回路25に、この生成した鋸歯状波をA/D変換用の参照電圧（ADC基準信号）として供給する。また、たとえばカウントクロックCKdacの周期を調整することで参照信号RAMPの傾きを変え、これにより後述する差分処理時の係数を調整し、A/D変換時にアナログゲインを制50

御する。

**【0057】**

カラム A D 回路 25 は、参照信号生成部 27 の D A 変換回路 27a で生成される参照信号 RAMP と、行制御線 15 ( V1, V2, ... ) ごとに単位画素 3 から垂直信号線 19 ( H1, H2, ... ) を経由し得られるアナログの画素信号とを比較する電圧比較部 ( コンパレータ ) 252 と、電圧比較部 252 が比較処理を完了するまでの時間をカウントし、その結果を保持するカウンタ部 254 とを備えて構成され n ビット A D 変換機能を有している。

**【0058】**

通信・タイミング制御部 20 は、電圧比較部 252 が画素信号のリセット成分 V と信号成分 Vsig の何れについて比較処理を行なっているのかに応じてカウンタ部 254 におけるカウント処理のモードを切り替える制御部の機能を持つ。この通信・タイミング制御部 20 から各カラム A D 回路 25 のカウンタ部 254 には、カウンタ部 254 がダウンカウントモードで動作するのかアップカウントモードで動作するのかを指示するための制御信号 C N5 が入力されている。

**【0059】**

参照信号供給 I F 部 28 は、参照信号生成部 27 で生成された参照信号を参照信号線 251 を介して受け取り、参照信号出力線 281 に出力する。電圧比較部 252 の一方の入力端子 RAMP は、本実施形態の特徴部分である参照信号供給 I F 部 28 を介して、参照信号生成部 27 で生成される階段状の参照信号 RAMP が参照信号出力線 281 から入力され、他方の入力端子には、それぞれ対応する垂直列の垂直信号線 19 が接続され、画素部 10 からの画素信号電圧が個々に入力される。

**【0060】**

また、電圧比較部 252 には、通信・タイミング制御部 20 から、2 種類のリセット信号 PSET, NSET やその他の制御信号 ( 繼めて比較制御信号 C N7 ともいう ) が供給され、また電圧比較部 252 の出力信号はカウンタ部 254 に供給される。

**【0061】**

カウンタ部 254 のクロック端子 CK には、他のカウンタ部 254 のクロック端子 CK と共に、通信・タイミング制御部 20 からカウントクロック CK0 が入力されている。

**【0062】**

このカウンタ部 254 は、その構成については図示を割愛するが、一般的にラッチで構成されるデータ記憶部の配線形態を同期カウンタ形式に変更することで実現でき、1 本のカウントクロック CK0 の入力で、内部カウントを行なうようになっている。n 個のラッチの組合せで n ビットのカウンタ部 254 を実現でき、2 系統の n 個のラッチで構成されたデータ記憶部の回路規模に対して半分になる。加えて、列ごとのカウンタ部が不要になるから、全体としては、大幅にコンパクトになる。

**【0063】**

ここで、カウンタ部 254 は、詳細は後述するが、カウントモードに拘わらず共通のアップダウンカウンタ ( U / D CNT ) を用いて、ダウンカウント動作とアップカウント動作とを切り替えて ( 具体的には交互に ) カウント処理を行なうことが可能に構成されている。また、カウンタ部 254 は、カウント出力値がカウントクロック CK0 に同期して出力される同期カウンタを使用する。

**【0064】**

なお、同期カウンタの場合、すべてのフリップフロップ ( カウンタ基本要素 ) の動作がカウントクロック CK0 で制限される。よって、より高周波数動作が要求される場合には、カウンタ部 254 としては、その動作制限周波数が最初のフリップフロップ ( カウンタ基本要素 ) の制限周波数でのみ決められるため高速動作に適する非同期カウンタの使用がより好ましい。

**【0065】**

カウンタ部 254 には、水平走査部 12 から制御線 12c を介して制御パルスが入力される。カウンタ部 254 は、カウント結果を保持するラッチ機能を有しており、制御線 1

10

20

30

40

50

$2^c$  を介しての制御パルスによる指示があるまでは、カウンタ出力値を保持する。

#### 【0066】

このような構成のカラム A D 回路 25 は、先にも述べたように、垂直信号線 19 ( H1 , H2 , ... ) ごとに配置され、列並列構成の A D C ブロックであるカラム処理部 26 が構成される。

#### 【0067】

個々のカラム A D 回路 25 の出力側は、水平信号線 18 に接続されている。先にも述べたように、水平信号線 18 は、カラム A D 回路 25 のビット幅である n ビット幅分の信号線を有し、図示しないそれぞれの出力線に対応した n 個のセンス回路を経由して出力部 29 に接続される。

10

#### 【0068】

このような構成において、カラム A D 回路 25 は、画素信号読出期間において、カウント動作を行ない、所定のタイミングでカウント結果を出力する。すなわち、先ず、電圧比較部 252 では、参照信号生成部 27 からのランプ波形電圧と、垂直信号線 19 を介して入力される画素信号電圧とを比較し、双方の電圧が同じになると、電圧比較部 252 のコンパレータ出力が反転（本例では H レベルから L レベルへ遷移）する。

#### 【0069】

カウンタ部 254 は、参照信号生成部 27 から発せられるランプ波形電圧に同期してダウンカウントモードもしくはアップカウントモードでカウント動作を開始しており、コンパレータ出力の反転した情報がカウンタ部 254 に通知されると、カウント動作を停止し、その時点のカウント値を画素データとしてラッチ（保持・記憶）することで A D 変換を完了する。

20

#### 【0070】

この後、カウンタ部 254 は、所定のタイミングで水平走査部 12 から制御線 12c を介して入力される水平選択信号 CH ( i ) によるシフト動作に基づいて、記憶・保持した画素データを、順次、カラム処理部 26 外や画素部 10 を有するチップ外へ出力端子 5c から出力する。

#### 【0071】

なお、本実施形態の説明としては直接関連しないため特に図示しないが、その他の各種信号処理回路なども、固体撮像装置 1 の構成要素に含まれる場合がある。

30

#### 【0072】

##### <画素部>

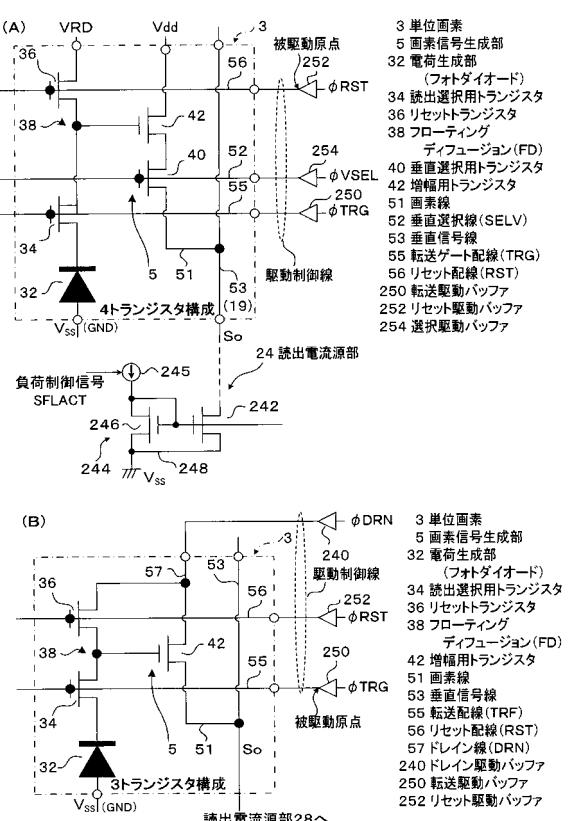

図 2 は、図 1 に示した固体撮像装置 1 に使用される単位画素 3 の構成例と、駆動部と駆動制御線と画素トランジスタの接続様式を示す図である。画素部 10 内の単位画素（画素セル）3 の構成は、通常の C M O S イメージセンサと同様であり、本実施形態では、C M O S センサとして汎用的な 4 T R 構成のものや、たとえば、特許第 2708455 号公報に記載のように、3 つのトランジスタからなる 3 T R 構成のものを使用することができる。もちろん、これらの画素構成は一例であり、通常の C M O S イメージセンサのアレイ構成であれば、何のものでも使用できる。

#### 【0073】

40

画素内アンプとしては、たとえばフローティングディフュージョンアンプ構成のものが用いられる。一例としては、電荷生成部に対して、電荷読出部（転送ゲート部 / 読出ゲート部）の一例である読出選択用トランジスタ、リセットゲート部の一例であるリセットトランジスタ、垂直選択用トランジスタ、およびフローティングディフュージョンの電位変化を検知する検知素子の一例であるソースフォロア構成の増幅用トランジスタを有する、C M O S センサとして汎用的な 4 つのトランジスタからなる構成（以下 4 T R 構成ともいう）のものを使用することができる。

#### 【0074】

たとえば、図 2 ( A ) に示す 4 T R 構成の単位画素 3 は、光を受光して電荷に変換する光電変換機能とともに、その電荷を蓄積する電荷蓄積機能の各機能を兼ね備えた電荷生成

50

部32と、電荷生成部32に対して、電荷読出部（転送ゲート部／読出ゲート部）の一例である読出選択用トランジスタ（転送トランジスタ）34、リセットゲート部の一例であるリセットトランジスタ36、垂直選択用トランジスタ40、およびフローティングディフュージョン38の電位変化を検知する検知素子の一例であるソースフォロア構成の増幅用トランジスタ42を有する。

#### 【0075】

この単位画素3は、電荷蓄積部の機能を備えた電荷注入部の一例であるフローティングディフュージョン38とからなるF D A (Floating Diffusion Amp)構成の画素信号生成部5を有するものとなっている。フローティングディフュージョン38は寄生容量を持った拡散層である。

10

#### 【0076】

読出選択用トランジスタ（第2の転送部）34は、転送信号TRGが供給される転送駆動バッファ250により転送配線（読出選択線TX）55を介して駆動されるようになっている。リセットトランジスタ36は、リセット信号RSTが供給されるリセット駆動バッファ252によりリセット配線（RST）56を介して駆動されるようになっている。垂直選択用トランジスタ40は、垂直選択信号VSELが供給される選択駆動バッファ254により垂直選択線（SEL）52を介して駆動されるようになっている。各駆動バッファは、垂直走査部14の垂直駆動部14bによって駆動可能になっている。

#### 【0077】

画素信号生成部5におけるリセットトランジスタ36は、ソースがフローティングディフュージョン38に、ドレインが電源Vddにそれぞれ接続され、ゲート（リセットゲートRG）にはリセットパルスRSTがリセット駆動バッファから入力される。

20

#### 【0078】

垂直選択用トランジスタ40は、一例として、ドレインが増幅用トランジスタ42のソースに、ソースが画素線51にそれぞれ接続され、ゲート（特に垂直選択ゲートSELVという）が垂直選択線52に接続されている。なおこのような接続構成に限らず、ドレインが電源Vddに、ソースが増幅用トランジスタ42のドレインにそれぞれ接続され、垂直選択ゲートSELVが垂直選択線52に接続されるようにしてもよい。

#### 【0079】

垂直選択線52には、垂直選択信号SELが印加される。増幅用トランジスタ42は、ゲートがフローティングディフュージョン38に接続され、ドレインが垂直選択用トランジスタ40を介して電源Vddに、ソースは画素線51に接続され、さらに垂直信号線53（19）に接続されるようになっている。

30

#### 【0080】

さらに垂直信号線53は、その一端がカラム処理部26側に延在するとともに、その経路において、読出電流源部24が接続され、増幅用トランジスタ42との間で、略一定の動作電流（読出電流）が供給されるソースフォロワ構成が採られるようになっている。

#### 【0081】

具体的には、読出電流源部24は、各垂直列に設けられたN M O S型のトランジスタ（特に負荷M O Sトランジスタという）242と、全垂直列に対して共用される電流生成部245およびゲートおよびドレインが共通に接続されソースがソース線248に接続されたN M O S型のトランジスタ246を有する基準電流源部244とを備えている。

40

#### 【0082】

各負荷M O Sトランジスタ242は、ドレインが対応する列の垂直信号線53に接続され、ソースが接地線であるソース線248に共通に接続されている。これにより、各垂直列の負荷M O Sトランジスタ242は基準電流源部244のトランジスタ246との間でゲート同士が接続されカレントミラー回路を構成するように接続されている。

#### 【0083】

ソース線248は、水平方向の端部（図1の左右の垂直列）で基板バイアスである接地（G N D）に接続され、負荷M O Sトランジスタ242の接地に対する動作電流（読出電

50

流)が、チップの左右両端から供給されるような構成となっている。

#### 【0084】

電流生成部245には、必要時にのみ所定電流を出力するようにするための負荷制御信号SFLACTが、図示しない負荷制御部から供給されるようになっている。電流生成部245は、信号読出し時には、負荷制御信号SFLACTのアクティブ状態が入力されることで、各増幅用トランジスタ42に接続された負荷MOSトランジスタ242によって、予め決められた定電流を流し続けるようになっている。つまり、負荷MOSトランジスタ242は、選択行の増幅用トランジスタ42とソースフォロアを組んで読出電流を増幅用トランジスタ42に供給することで垂直信号線53への信号出力をさせる。

#### 【0085】

このような4TR構成では、フローティングディフュージョン38は増幅用トランジスタ42のゲートに接続されているので、増幅用トランジスタ42はフローティングディフュージョン38の電位(以下FD電位という)に対応した信号を電圧モードで、画素線51を介して垂直信号線19(53)に出力する。

#### 【0086】

リセットトランジスタ36は、フローティングディフュージョン38をリセットする。読出選択用トランジスタ(転送トランジスタ)34は、電荷生成部32にて生成された信号電荷をフローティングディフュージョン38に転送する。垂直信号線19には多数の画素が接続されているが、画素を選択するのには、選択画素のみ垂直選択用トランジスタ40をオンする。すると選択画素のみが垂直信号線19と接続され、垂直信号線19には選択画素の信号が出力される。

#### 【0087】

これに対して、電荷生成部と3つのトランジスタからなる構成(以下3TR構成ともいう)とすることで、単位画素3におけるトランジスタが占める面積を少なくし、画素サイズを小さくすることができる(たとえば特許第2708455号公報参照)。

#### 【0088】

たとえば、図2(B)に示す3TR構成の単位画素3は、光電変換を行なうことで受光した光に対応する信号電荷を生成する電荷生成部32(たとえばフォトダイオード)と、電荷生成部32により生成された信号電荷に対応する信号電圧を増幅するための、ドレン線(DRN)に接続された増幅用トランジスタ42と、電荷生成部32をリセットするためのリセットトランジスタ36とを、それぞれ有している。また、図示しない垂直走査回路14より転送配線(TRF)55を介して走査される読出選択用トランジスタ(転送ゲート部)34が、電荷生成部32と増幅用トランジスタ42のゲートとの間に設けられている。

#### 【0089】

増幅用トランジスタ42のゲートおよびリセットトランジスタ36のソースは読出選択用トランジスタ34を介して電荷生成部32に、リセットトランジスタ36のドレンおよび増幅用トランジスタ42のドレンはドレン線に、それぞれ接続されている。また、増幅用トランジスタ42のソースは垂直信号線53に接続されている。

#### 【0090】

読出選択用トランジスタ34は、転送配線55を介して転送駆動バッファ250により駆動されるようになっている。リセットトランジスタ36は、リセット配線56を介してリセット駆動バッファ252により駆動されるようになっている。

#### 【0091】

転送駆動バッファ250、リセット駆動バッファ252とも基準電圧である0Vと、電源電圧の2倍で動作する。特に、この画素における読出選択用トランジスタ34のゲートに供給されるローレベル電圧は0Vである。

#### 【0092】

この3TR構成の単位画素3においては、4TR構成と同様に、フローティングディフュージョン38は増幅用トランジスタ42のゲートに接続されているので、増幅用トラン

10

20

30

40

50

ジスタ42はフローティングディフュージョン38の電位に対応した信号を垂直信号線53に出力する。

#### 【0093】

リセットトランジスタ36は、リセット配線(RST)56が行方向に延びており、ドレイン線(DRN)57は殆どの画素に共通になっている。このドレイン線57は、ドレン駆動信号DRNが供給されるドレン駆動バッファ(以下DRN駆動バッファという)240により駆動される。リセットトランジスタ36はリセット駆動バッファ252により駆動され、フローティングディフュージョン38の電位を制御する。

#### 【0094】

ドレイン線57が行方向に分離されているが、このドレイン線57は1行分の画素の信号電流を流さなければならないので、実際には列方向に電流を流せるように、全行共通の配線となる。電荷生成部32(光電変換素子)にて生成された信号電荷は読出選択用トランジスタ34によりフローティングディフュージョン38に転送される。

10

#### 【0095】

ここで、3TR構成の単位画素3には、4TR構成とは異なり、増幅用トランジスタ42と直列に接続される垂直選択用トランジスタ40が設けられていない。垂直信号線53には多数の画素が接続されているが、画素の選択は、選択トランジスタではなく、FD電位の制御により行なう。通常は、FD電位をロー(Low)にしている。画素を選択するときは、選択画素のFD電位をハイ(High)にすることで、選択画素の信号を垂直信号線53に出す。その後、選択画素のFD電位をローに戻す。この操作は1行分の画素に20

対して同時に行なわれる。

20

#### 【0096】

このようにFD電位を制御するためには、1)選択行FD電位をハイにするときに、ドレイン線57をハイにし、選択行のリセットトランジスタ36を通して、そのFD電位をハイにする、2)選択行FD電位をローに戻すときに、ドレイン線57をローにし、選択行のリセットトランジスタ36を通して、そのFD電位をローにする、という動作を行なう。

#### 【0097】

このような4TRもしくは3TRの構成を持つ単位画素3を具備した画素部10を駆動するには、各駆動バッファ240, 250, 252, 254(纏めて駆動部ともいう)から駆動用の各配線52, 55, 56, 57(纏めて駆動制御線ともいう)を介して、単位画素3を構成する各トランジスタ34, 36, 40(纏めて画素トランジスタともいう)を駆動する。

30

#### 【0098】

##### <固体撮像装置の動作>

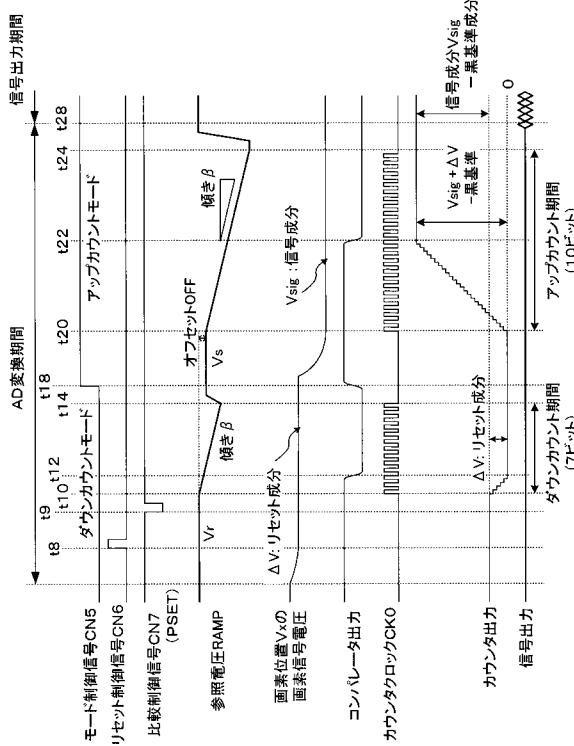

図3および図4は、図1に示した固体撮像装置1のカラムAD回路25における基本動作である信号取得差分処理を説明するためのタイミングチャートである。

#### 【0099】

画素部10の各単位画素3で感知されたアナログの画素信号をデジタル信号に変換する仕組みとしては、たとえば、所定の傾きで下降するランプ波形状の参照信号RAMPと単位画素3からの画素信号における基準成分や信号成分の各電圧とが一致する点を探し、この比較処理で用いる参照信号RAMPの生成時点から、画素信号における基準成分や信号成分に応じた電気信号と参照信号とが一致した時点までをカウントクロックでカウント(計数)することで、基準成分や信号成分の各大きさに対応したカウント値を得る手法を探る。

40

#### 【0100】

ここで、垂直信号線19から出力される画素信号は、時間系列として、基準成分としての画素信号の雑音を含むリセット成分Vの後に信号成分Vsigが現れるものである。1回目の処理を基準成分(リセット成分V)について行なう場合、2回目の処理は基準成分(リセット成分V)に信号成分Vsigを加えた信号についての処理となる。以下具体的に説明する。

50

**【0101】**

1回目の読み出しのため、先ず通信・タイミング制御部20は、モード制御信号CN5をローレベルにしてカウンタ部254をダウンカウントモードに設定するとともに、リセット制御信号CN6を所定期間アクティブ（本例ではハイレベル）にしてカウンタ部254のカウント値を初期値“0”にリセットさせる（t8）。

**【0102】**

そして、垂直走査部14による走査によってある行が選択され、その選択行Vの単位画素3から垂直信号線19（H1, H2, ...）への1回目の読み出しが安定した後、通信・タイミング制御部20は、参照信号生成部27に向けて、参照信号RAMP生成用の制御データCN4（ここではオフセットOFFと傾きを含む）を供給する。 10

**【0103】**

このとき同時に、通信・タイミング制御部20は、アクティブPLのリセット信号PSETがある短い期間だけ電圧比較部252に与える（t9）。これにより、電圧比較部252の各入力端の電位が所定電位にセットされ、電圧比較部252の動作点が行の選択動作ごとに適正レベルに決定される。

**【0104】**

制御データCN4が供給された参照信号生成部27においては、先ず、V行上に存在する色のカラー画素特性に合わせた傾きを持ち全体として鋸歯状（RAMP状）に時間変化させた階段状の波形（RAMP波形）を持った参照信号RAMPをDA変換回路27aにて生成し、対応するカラムAD回路25の電圧比較部252の一方の入力端子RAMPに、比較電圧として供給する。 20

**【0105】**

各列の電圧比較部252は、このRAMP波形の比較電圧と画素部10から供給される対応列の垂直信号線19（H）の画素信号電圧とを比較する。

**【0106】**

また、電圧比較部252の入力端子RAMPへの参照信号RAMPの入力と同時に、電圧比較部252における比較時間を、行ごとに配置されたカウンタ部254で計測するために、参照信号生成部27から発せられるランプ波形電圧に同期して（t10）、カウンタ部254のクロック端子に通信・タイミング制御部20からカウントクロックCK0を入力し、1回目のカウント動作として、初期値“0”からダウンカウントを開始する。すなわち、負の方向にカウント処理を開始する。 30

**【0107】**

電圧比較部252は、参照信号生成部27からのランプ状の参照信号RAMPと垂直信号線19を介して入力される画素信号電圧Vxとを比較し、双方の電圧が同じになったときに、コンパレータ出力をHレベルからLレベルへ反転させる（t12）。つまり、リセット成分Vrstに応じた電圧信号と参照信号RAMPとを比較して、リセット成分Vrstの大きさに対応した時間経過後にアクティブロー（L）のパルス信号を生成して、カウンタ部254に供給する。

**【0108】**

この結果を受けて、カウンタ部254は、コンパレータ出力の反転とほぼ同時にカウント動作を停止し、その時点のカウント値を画素データとしてラッチ（保持・記憶）することでAD変換を完了する（t12）。つまり、電圧比較部252に供給するランプ状の参照信号RAMPの生成とともにダウンカウントを開始し、比較処理によってアクティブロー（L）のパルス信号が得られるまでクロックCK0でカウント（計数）することで、リセット成分Vrstの大きさに対応したカウント値を得る。 40

**【0109】**

通信・タイミング制御部20は、所定のダウンカウント期間を経過すると（t14）、電圧比較部252への制御データの供給と、カウンタ部254へのカウントクロックCK0の供給とを停止する。これにより、電圧比較部252は、ランプ状の参照信号RAMPの生成を停止する。 50

**【 0 1 1 0 】**

この1回目の読み出し時は、画素信号電圧 $V_x$ におけるリセットレベル $V_{rst}$ を電圧比較部252で検知してカウント動作を行なっているので、単位画素3のリセット成分 $V$ を読み出していることになる。

**【 0 1 1 1 】**

このリセット成分 $V$ 内には、単位画素3ごとにバラ付く雑音がオフセットとして含まれている。しかし、このリセット成分 $V$ のバラ付きは一般に小さく、またリセットレベル $V_{rst}$ は概ね全画素共通であるので、任意の垂直信号線19の画素信号電圧 $V_x$ におけるリセット成分 $V$ の出力値はおおよそ既知である。

**【 0 1 1 2 】**

したがって、1回目のリセット成分 $V$ の読み出し時には、RAMP電圧の変化特性を調整することにより、ダウンカウント期間( $t_{10} \sim t_{14}$ ; 比較期間)を短くすることで、1回目の比較期間を短くすることが可能である。本実施形態では、リセット成分 $V$ についての比較処理の最長期間を、7ビット分のカウント期間(128クロック)にして、リセット成分 $V$ の比較を行なっている。

10

**【 0 1 1 3 】**

続いての2回目の読み出し時には、リセット成分 $V$ に加えて、単位画素3ごとの入射光量に応じた電気信号成分 $V_{sig}$ を読み出し、1回目の読み出しと同様の動作を行なう。すなわち、先ず通信・タイミング制御部20は、モード制御信号CN5をハイレベルにしてカウンタ部254をアップカウントモードに設定する( $t_{18}$ )。そして、選択行 $V$ の単位画素3から垂直信号線19(H1, H2, ...)への2回目の読み出しが安定した後、通信・タイミング制御部20は、信号成分 $V_{sig}$ についてのA/D変換処理のため、参照信号RAMP生成用の制御データCN4をD/A変換回路27aに供給する。このときには、通信・タイミング制御部20は、1回目の処理とは異なり、リセット信号PSETをアクティブLにすることはしない。

20

**【 0 1 1 4 】**

これを受け、参照信号生成部27においては、先ず、 $V$ 行上に存在するある色のカラー画素特性に合わせた傾き $\gamma$ を持ち全体として鋸歯状(RAMP状)に時間変化させた階段状の波形(RAMP波形)を持つとともに、リセット成分 $V$ 用の初期値 $V_{ar}$ に対してオフセットOFFだけ下がった参照信号RAMPをD/A変換回路27aにて生成し、対応するカラムAD回路25の電圧比較部252の一方の入力端子RAMPに、比較電圧として供給する。

30

**【 0 1 1 5 】**

各列の電圧比較部252は、このRAMP波形の比較電圧と画素部10から供給される対応列の垂直信号線19(H)の画素信号電圧とを比較する。

**【 0 1 1 6 】**

電圧比較部252の入力端子RAMPへの参照信号RAMPの入力と同時に、電圧比較部252における比較時間を、行ごとに配置されたカウンタ部254で計測するために、参照信号生成部27から発せられるランプ波形電圧に同期して( $t_{20}$ )、カウンタ部254のクロック端子に通信・タイミング制御部20からカウントクロックCK0を入力し、2回目のカウント動作として、1回目の読み出し時に取得された単位画素3のリセット成分 $V$ に対応するカウント値から、1回目とは逆にアップカウントを開始する。すなわち、正の方向にカウント処理を開始する。

40

**【 0 1 1 7 】**

電圧比較部252は、参照信号生成部27からのランプ状の参照信号RAMPと垂直信号線19を介して入力される画素信号電圧 $V_x$ とを比較し、双方の電圧が同じになったときに、コンパレータ出力をHレベルからLレベルへ反転させる( $t_{22}$ )。つまり、信号成分 $V_{sig}$ に応じた電圧信号と参照信号RAMPとを比較して、信号成分 $V_{sig}$ の大きさに対応した時間経過後にアクティブロー(L)のパルス信号を生成して、カウンタ部254に供給する。

**【 0 1 1 8 】**

50

この結果を受けて、カウンタ部 254 は、コンパレータ出力の反転とほぼ同時にカウント動作を停止し、その時点のカウント値を画素データとしてラッチ（保持・記憶）することで A/D 変換を完了する（t22）。つまり、電圧比較部 252 に供給するランプ状の参照信号RAMPの生成とともにダウンカウントを開始し、比較処理によってアクティブロー（L）のパルス信号が得られるまでクロック CK0 でカウント（計数）することで、信号成分 Vsig の大きさに対応したカウント値を得る。

## 【0119】

通信・タイミング制御部 20 は、所定のダウンカウント期間を経過すると（t24）、電圧比較部 252 への制御データの供給と、カウンタ部 254 へのカウントクロック CK0 の供給とを停止する。これにより、電圧比較部 252 は、ランプ状の参照信号RAMPの生成を停止する。10

## 【0120】

この2回目の読み出し時は、画素信号電圧 Vx における信号成分 Vsig を電圧比較部 252 で検知してカウント動作を行なっているので、単位画素 3 の信号成分 Vsig を読み出していることになる。

## 【0121】

ここで、本実施形態においては、カウンタ部 254 におけるカウント動作を、1回目の読み出し時にはダウンカウント、2回目の読み出し時にはアップカウントとし、カウント結果を同じ格納場所に保持するので、カウンタ部 254 内で自動的に、式（1）で示す減算が行なわれ、この減算結果に応じたカウント値がカウンタ部 254 に保持される。20

## 【0122】

## 【数1】

$$(2\text{回目の比較期間におけるカウント値}) - (1\text{回目の比較期間におけるカウント値}) \cdots (1)$$

## 【0123】

ここで、式（1）は、式（2）のように変形でき、結果としては、カウンタ部 254 に保持されるカウント値は信号成分 Vsig に応じたものとなる。なお、ここでは、高精度なカラー画像撮像を行なうべく、初期値とゲインを色対応別に制御する観点から黒基準についても考慮しているが、一般的には（モノクロ撮像を含む）、最後の項の黒基準の項を無視することもできる。30

## 【0124】

## 【数2】

$$\begin{aligned} & (2\text{回目の比較期間}) - (1\text{回目の比較期間}) \\ & = (\text{信号成分 } V_{sig} + \text{リセット成分 } \Delta V + \text{カラムAD回路25のオフセット成分} - (\text{黒基準成分})) \\ & \quad - (\text{リセット成分 } \Delta V + \text{カラムAD回路25のオフセット成分}) \\ & = (\text{信号成分 } V_{sig}) - (\text{黒基準成分}) \end{aligned} \quad \left. \right\} (2)$$

## 【0125】

つまり、上述のような一連の動作において、1回目の読み出し時におけるダウンカウントと2回目の読み出し時におけるアップカウントといった、2回の読み出しとカウント処理によるカウンタ部 254 内での減算処理によって、単位画素 3 ごとのバラつきを含んだリセット成分 V とカラム AD 回路 25 ごとのオフセット成分とを除去することができる。また、単位画素 3 ごとの入射光量に応じた信号成分 Vsig に黒基準成分の補正を加えた信号についてのデジタル信号のみを簡易な構成で取り出すことができる。40

## 【0126】

この際、回路バラつきやリセット雑音も除去できる利点がある。つまり、2回目のカウント後の出力値が、雑音成分を除去した純粋なデジタル信号量を表すこととなる。よって、本実施形態のカラム AD 回路 25 は、アナログの画素信号をデジタルの画素データに変50

換するデジタル変換部としてだけでなく、CDS(Correlated Double Sampling ; 相関2重サンプリング)処理機能部としても動作することとなる。

#### 【0127】

また、式(2)で得られるカウント値が示す画素データは正の信号電圧を示すので、補数演算などが不要となり、既存のシステムとの親和性が高い。

#### 【0128】

ここで、2回目の読み出し時は、入射光量に応じた信号成分Vsigtを読み出すので、光量の大小を広い範囲で判定するために、アップカウント期間(t20 ~ t24; 比較期間)を広く取り、電圧比較部252に供給するランプ電圧を大きく変化させる必要がある。

#### 【0129】

そこで本実施形態では、信号成分Vsigtについての比較処理の最長期間を、10ビット分のカウント期間(1024クロック)にして、信号成分Vsigtの比較を行なっている。つまり、リセット成分V(基準成分)についての比較処理の最長期間を、信号成分Vsigtについての比較処理の最長期間よりも短くする。リセット成分V(基準成分)と信号成分Vsigtの双方の比較処理の最長期間すなわちAD変換期間の最大値を同じにするではなく、リセット成分V(基準成分)についての比較処理の最長期間を信号成分Vsigtについての比較処理の最長期間よりも短くすることで、2回に亘るトータルのAD変換時間が短くなるように工夫する。

#### 【0130】

この場合、1回目と2回目との比較ビット数が異なるが、通信・タイミング制御部20から制御データを参照信号生成部27に供給して、この制御データに基づいて参照信号生成部27にてランプ電圧を生成するようにすることで、ランプ電圧の傾きすなわち参照信号RAMPの変化率を1回目と2回目とで同じにする。デジタル制御でランプ電圧を生成するので、ランプ電圧の傾きを1回目と2回目とで同じにすることが容易である。これにより、AD変換の精度を等しくできるため、アップダウンカウンタによる式(1)で示した減算結果が正しく得られる。

#### 【0131】

2回目のカウント処理が完了した後の所定のタイミングで(t28)、通信・タイミング制御部20は水平走査部12に対して画素データの読み出しを指示する。これを受け、水平走査部12は、制御線12cを介してカウンタ部254に供給する水平選択信号CH(i)を順次シフトさせる。

#### 【0132】

こうすることで、カウンタ部254に記憶・保持した式(2)で示されるカウント値、すなわちnビットのデジタル信号で表された画素データが、n本の水平信号線18を介して、順次、カラム処理部26外や画素部10を有するチップ外へ出力端子5cから出力され、その後、順次行ごとに同様の動作が繰り返されることで、2次元画像を表す映像データD1が得られる。

#### 【0133】

以上説明したように、固体撮像装置によれば、アップダウンカウンタを用いつつ、その処理モードを切り替えて2回に亘ってカウント処理を行なうようにした。また、行列状に単位画素3が配列された構成において、カラムAD回路25を垂直列ごとに設けた列並列カラムAD回路で構成した。

#### 【0134】

ここで、比較回路とカウンタとでAD変換回路を構成するに当たり、比較回路に供給するAD変換用の参照信号を発生する機能要素であるDA変換回路を、カラー画像撮像に使用する色分解フィルタにおける色フィルタの全色分を用意するのではなく、色の種類や配列で決まる色の繰返しサイクルに応じた所定色の組合せに応じた分だけ設けるようにした。また、処理対象行が切り替わることで、その処理対象行に存在する所定色の組合せが切り替わることに応じて、DA変換回路が発する参照信号(アナログ基準電圧)の変化特性(具体的には傾き)や初期値を、色フィルタすなわちアナログの画素信号の特性に応じて

10

20

30

40

50

切り替えるようにした。

**【 0 1 3 5 】**

これにより、参照電圧発生器として機能する D A 変換回路や参照電圧発生器からの配線を色分解フィルタを構成する色フィルタの数よりも少なくすることができ、また、色フィルタごとに参照電圧発生器を用意した場合に必要となるアナログ基準電圧（参照信号）を選択的に出力するマルチプレクサも不要となるので、大幅に回路規模が縮小できる。

**【 0 1 3 6 】**

また、処理対象行に存在する所定色の組合せが切り替わることに応じて、D A 変換回路が発する参照信号の変化特性（具体的には傾き）を切替設定するようにしたので、画素部 10 を構成する各カラー画素の特性に応じて互いに異なる基準電圧を各々生成して比較処理を行なうことによって、単位画素から出力されるアナログの画素信号をデジタル信号に変換する際、各々のカラーに応じて参照信号の傾きを調節することで、各カラーの特性を緻密に制御することができる。

**【 0 1 3 7 】**

加えて、D A 変換回路が発する参照信号の初期値を D A 変換回路で生ずる固有のバラ付き成分や黒基準成分に応じて切替設定するようにしたので、回路バラ付きを補正できるとともに、黒基準成分の補正を加えた信号のみについて簡易な構成で A D 変換することができる。

**【 0 1 3 8 】**

さらに、基準成分（リセット成分）と信号成分との減算処理が 2 回目のカウント結果として垂直列ごとに直接に取得することができ、基準成分と信号成分のそれぞれのカウント結果を保持するメモリ装置をカウンタ部が備えるラッチ機能で実現でき、A D 変換されたデータを保持する専用のメモリ装置をカウンタとは別に用意する必要がない。

**【 0 1 3 9 】**

加えて、基準成分と信号成分との差を取るための特別な減算器が不要になる。よって、従来構成よりも、回路規模や回路面積を少なくすることができ、加えて、雑音の増加や電流あるいは消費電力の増大を解消することができる。

**【 0 1 4 0 】**

また、比較部とカウンタ部でカラム A D 回路（A D 変換部）を構成したので、ビット数によらずカウンタ部を動作させるカウントクロック 1 本とカウントモードを切り替える制御線とでカウント処理を制御でき、従来構成で必要としていたカウンタ部のカウント値をメモリ装置まで導く信号線が不要になり、雑音の増加や消費電力の増大を解消することができる。

**【 0 1 4 1 】**

つまり、A D 変換装置を同一チップ上に搭載した固体撮像装置 1 において、電圧比較部 252 とカウンタ部 254 とを対にして A D 変換部としてのカラム A D 回路 25 を構成するとともに、カウンタ部 254 の動作としてダウンカウントとアップカウントとを組み合わせて使用しつつ、処理対象信号の基本成分（本実施形態ではリセット成分）と信号成分との差をデジタル信号にすることで、回路規模や回路面積や消費電力、あるいは他の機能部と間のインターフェース用配線の数や、この配線によるノイズや消費電流などの問題を解消することができる。

**【 0 1 4 2 】**

なお、図示を割愛するが、カウンタ部 254 の後段に、このカウンタ部 254 の保持したカウント結果を保持する n ビットのメモリ装置としてのデータ記憶部を設けてよい。データ記憶部には、水平走査部 12 から制御線 12c を介して制御パルスが入力される。データ記憶部は、制御線 12c を介しての制御パルスによる指示があるまでは、カウンタ部 254 から取り込んだカウント値を保持する。水平走査部 12 は、カラム処理部 26 の各電圧比較部 252 とカウンタ部 254 とが、それぞれが担当する処理を行なうのと並行して、各データ記憶部が保持していたカウント値を読み出す読出走査部の機能を持つ。このような構成にすると、パイプライン処理が実現できる。

10

20

30

40

50

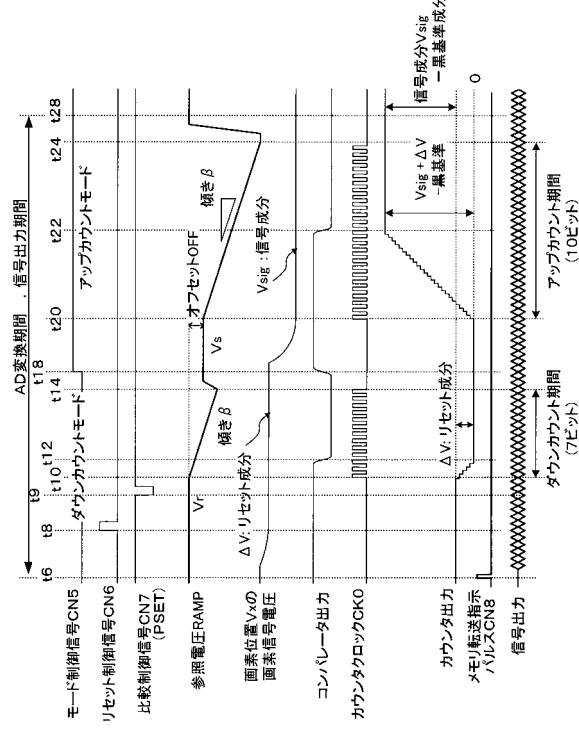

**【0143】**

すなわち、カウンタ部254の動作前( $t_6$ )に、通信・タイミング制御部20からのメモリ転送指示パルスCN8に基づき、前行 $H \times -1$ の処理時におけるカウント結果をデータ記憶部に転送する。

**【0144】**

図3に示した動作では、処理対象の画素信号における2回目の読み出し処理、すなわちAD変換処理が完了した後でなければ画素データをカラム処理部26の外部に出力することができないので、読み出し処理には制限がある。これに対して、カウンタ部254の後段にデータ記憶部を設けると、図4に示す動作のように、処理対象の画素信号における1回目の読み出し処理(AD変換処理)に先立って前回の減算処理結果を示すカウント値をデータ記憶部に転送することができ、読み出し処理には制限がない。10

**【0145】**

よって、このような構成を探ることで、カウンタ部254のカウント動作すなわちAD変換処理と、カウント結果の水平信号線18への読み出動作とを独立して制御可能であり、AD変換処理と外部(先ずは水平信号線18)への信号の読み出動作とを独立・並行して行なうパイプライン動作が実現できる。

**【0146】**

## &lt;電圧比較部の詳細構成例&gt;

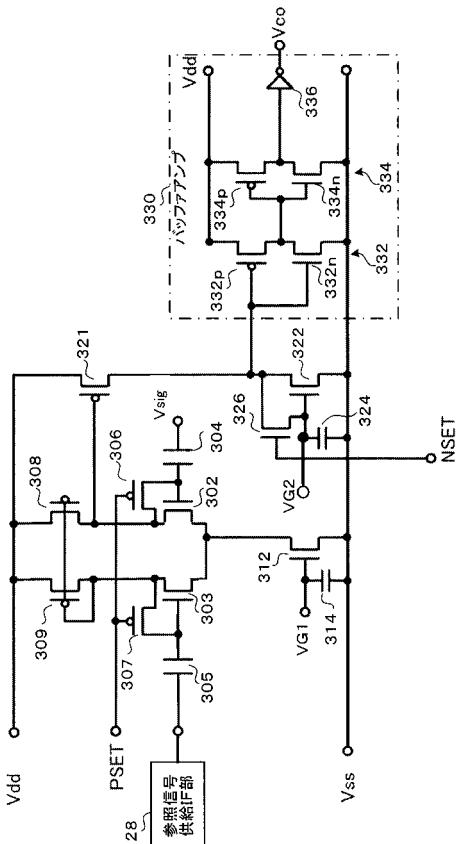

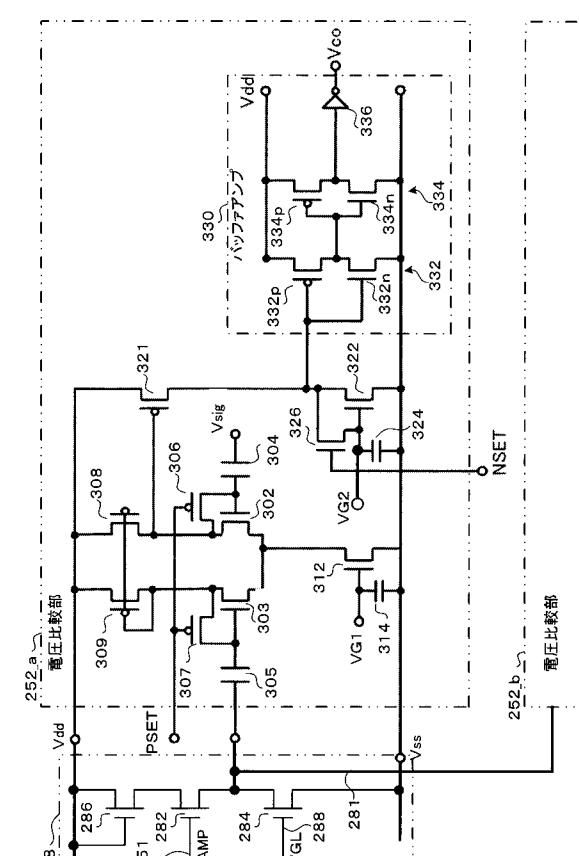

図5は、電圧比較部252の詳細な構成例を示す図である。電圧比較部252は先ず、20

入力段に、差動接続されたN MOS型のトランジスタ302, 303と結合コンデンサ304, 305と、リセットスイッチ用のPMOS型のトランジスタ306, 307とを備えている。トランジスタ302のゲートは結合コンデンサ304を介して垂直信号線19に接続され、トランジスタ303のゲートは結合コンデンサ305を介して参照信号供給IF部28の出力に接続される。差動対を構成するトランジスタ302, 303のゲートを特に差動入力ゲートと称する。

**【0147】**

トランジスタ302のゲートとドレインの間には、トランジスタ306のソース-ドレインが接続されている。トランジスタ303のゲートとドレインの間には、トランジスタ307のソース-ドレインが接続されている。各トランジスタ306, 307のゲートには、アクティブPLのリセット信号PSETが通信・タイミング制御部20から印加される。30

**【0148】**

また、電圧比較部252は、トランジスタ302, 303の各ドレイン側に、負荷回路として、各ソースが電源Vddに接続されるとともにゲート同士が接続されてカレントミラーハイブを構成するPMOS型のトランジスタ308, 309を備えている。トランジスタ309のドレインは自身のゲートと接続されるとともにトランジスタ303のドレインと接続され、またトランジスタ308のドレインはトランジスタ302のドレインと接続されている。

**【0149】**

また、電圧比較部252は、トランジスタ302, 303の各ソース側に、トランジスタ302, 303の動作電流を規定するN MOS型のトランジスタ(特に負荷MOSトランジスタという)312を備えている。負荷MOSトランジスタ312のドレインは、トランジスタ302, 303の各ソースに共通接続されるとともに、ソースが接地され、ゲート-接地間にはコンデンサ314が接続され、かつそのゲートには動作電流を規定するためのDCゲート電圧VG1が通信・タイミング制御部20から供給される。負荷MOSトランジスタ312は、ゲートにDCゲート電圧VG1が与えられることで定電流源として動作する。40

**【0150】**

トランジスタ302, 303, 308, 309, 312で、全体として、差動アンプが構成されるようになっている。

**【0151】**

10

20

30

40

50

また、電圧比較部 252 は、差動アンプの出力端、すなわちトランジスタ 308 のドレイン側に、PMOS 型のトランジスタ 321 のゲートが接続されている。このトランジスタ 321 は、ソースが電源 Vdd に接続され、ドレインがNMOS 型のトランジスタ（特に負荷 MOS トランジスタという）322 を介して接地されている。この負荷 MOS トランジスタ 322 は、ドレインがトランジスタ 321 のドレインに接続されるとともに、ソースが接地され、ゲート - 接地間にコンデンサ 324 が接続され、かつそのゲートには動作電流を規定するための DC ゲート電圧 VG2 が通信・タイミング制御部 20 から供給される。負荷 MOS トランジスタ 322 は、ゲートに DC ゲート電圧 VG2 が与えられることで定電流源として動作する。

## 【0152】

10

また、電圧比較部 252 は、トランジスタ 322 のゲートとドレインとの間に、リセットスイッチ用の NMOS 型のトランジスタ 326 のソース - ドレインが接続されている。トランジスタ 326 のゲートには、アクティブ H のリセット信号 NSET が通信・タイミング制御部 20 から印加される。

## 【0153】

トランジスタ 321, 322 のドレインから導出される差動アンプ出力は、反転出力型のバッファアンプ 330 を介して比較器出力 Vco となり、次段のカウンタ部 254 に与えられる。ここで、バッファアンプ 330 は、電源 Vdd と接地との間に直列に接続され、ゲート同士およびドレイン同士がそれぞれ共通に接続された PMOS 型のトランジスタ 332p および NMOS 型のトランジスタ 332n からなる前段の CMOS インバータ 332 と、同様に電源 Vdd と接地との間に直列に接続され、ゲート同士およびドレイン同士がそれぞれ共通に接続された PMOS 型のトランジスタ 334p および NMOS 型のトランジスタ 334n からなる後段の CMOS インバータ 334 と、一般的な CMOS 構成のインバータ 336 とを備えている。なお、ここで示したバッファアンプ 330 の構成は一例に過ぎず、たとえば、前段の CMOS インバータ 332 のみで構成することもできる。

20

## 【0154】

< 参照信号供給 IF 部 ; 第 1 実施形態 >

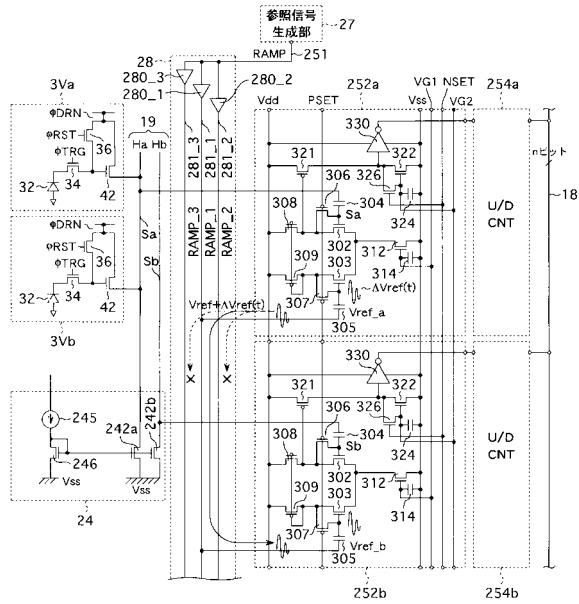

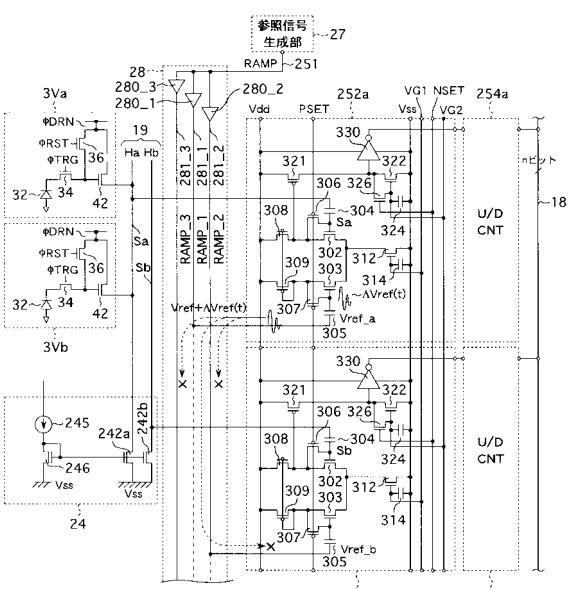

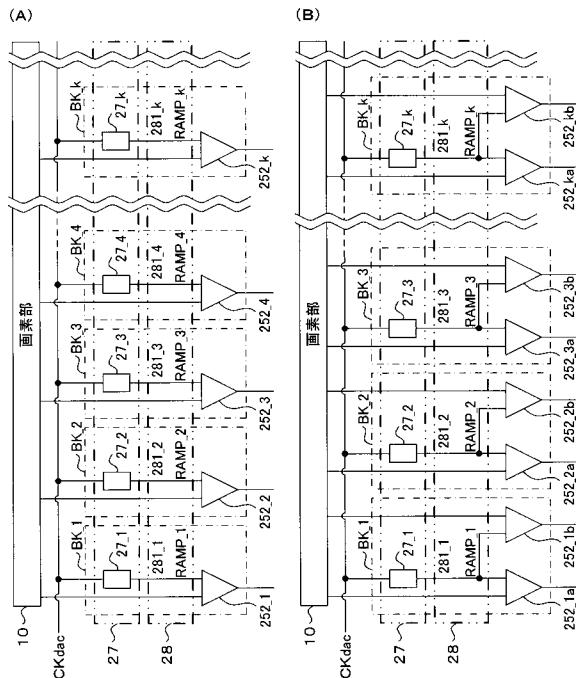

図 6 ~ 図 8 は、参照信号供給 IF 部 28 の第 1 実施形態を示す図である。ここでは特に単位画素 3 および参照信号生成部 27 とカラム AD 回路 25 の電圧比較部 252 との間の信号の伝達（インターフェース）手法に着目して示している。

30

## 【0155】

ここで、図 6 は第 1 実施形態で採用するインターフェース手法の基本構成を示し、図 7 はその全体概要を示し、図 8 は比較例としての、従来のインターフェース手法の基本構成を示す。なお、何れも、ある列 Ha の 2 行分の単位画素 3Va, 3Vb と、2 列分の電圧比較部 252a, 252b については、上述した詳細な回路構成を示しており、単位画素 3 として図 2 (B) に示す 3TR 構成のものを使用している。

## 【0156】

先ず、単位画素 3Va, 3Vb の各画素信号が Ha 列の垂直信号線 19 に伝達され、この画素信号 Sa が電圧比較部 252a の画素信号入力段（コンデンサ 304 側のゲート）に入力される。また、Hb 列の垂直信号線 19 に伝達された画素信号 Sb が電圧比較部 252b の画素信号入力段（コンデンサ 304 側のゲート）に入力される。

40

## 【0157】

本実施形態の参照信号供給 IF 部 28 は、図 6 および図 7 に示すように、参照信号生成部 27 から出力された参照信号を各電圧比較部 252 に供給するバッファ回路（緩衝増幅器）280 を参照信号線 251 上に備えている。

## 【0158】

特に、本実施形態では、参照信号供給 IF 部 28 は、複数のバッファ回路 280 を備えるとともに、1 つのブロック BK 内に属する複数の電圧比較部 252 に対して 1 つのバッファ回路 280 が配されるようになっている。全列の（複数の）電圧比較部 252 を、それぞれ複数（当然に全列数よりも少ない）の電圧比較部 252 を有する複数のブロック BK\_k

50

( $k$  は任意の整数) に分け、各ブロックに対して 1 つのバッファ回路 280 を設けるということである。

#### 【0159】

図 6 に示した例では、2 つの電圧比較部 252a, 252b に対して 1 つのバッファ回路 280\_k が用意されている。バッファ回路 280\_1 から出力された参照信号 RAMP\_1 は、参照信号出力線 281\_1 を介して、電圧比較部 252a, 252b の各参照信号入力段 (コンデンサ 305 側のゲート) に共通に伝達され、電圧比較部 252a では参照信号 Vref\_a として、また電圧比較部 252b では参照信号 Vref\_b として入力される。なお、各参照信号出力線 281\_k は、必要箇所までの配線で留めることもできるが、各列で信号遅延量を等しくするため、図に点線で示すように、同長にしてもよい。

10

#### 【0160】

なお、図 6 では図示を割愛しているが、図 7 に全体概要を示すように、他のバッファ回路 280\_k から出力された参照信号 RAMP\_k は、参照信号出力線 281\_k を介して、他の複数列の電圧比較部 252 (本例ではそれぞれ a, b の 2 列分) の各参照信号入力段 (コンデンサ 305 側のゲート) に共通に入力される。

#### 【0161】

もちろんこれは一例であって、参照信号供給 IF 部 28 は、全列の電圧比較部 252 の参照信号入力段を複数ブロックに分離する構成を備えていればよく、少なくとも 2 つのバッファ回路 280 を備えるとともに、たとえば 1 つのバッファ回路 280 に複数の電圧比較部 252 が接続されるものであればよい。もちろん、後述する第 3 実施形態のように、列ごとにバッファ回路 280 を備えることで、各列の電圧比較部 252 に対して 1 つのバッファ回路 280 を割り当てるようにしてもよい。一方、1 つのバッファ回路 280 だけを設け、この 1 つのバッファ回路 280 に全列の電圧比較部 252 が接続される構成は、事実上、図 8 に示す構成と同じようになり、電圧比較部 252 の参照信号入力段を複数ブロックに分離することにならないので、本願発明の構成には含まない。

20

#### 【0162】

バッファ回路 280 は、参照信号生成部 27 (さらに詳しくは DA 変換回路 27a) の出力インピーダンスを低出力インピーダンスに変換するとともに入出力を分離する緩衝增幅回路の機能を備えている。バッファ回路 280 は、電圧比較部 252 の差動対を構成するトランジスタ 302, 303 の一方の入力部 (トランジスタ 303 のゲート) に設けられる結合コンデンサ 305 に参照信号を供給する。なお、バッファ回路 280 の詳細については後述する。

30

#### 【0163】

一方、従来の参照信号供給 IF 部 28 は、図 7 に示すように、参照信号生成部 27 を構成する DA 変換回路 27a から出力される参照信号 RAMP を参照信号線 251 で電圧比較部 252 まで伝達するようになっている。参照信号線 251 には、全列の電圧比較部 252 が接続される。すなわち、ある列の電圧比較部 252 の参照信号入力段は、他の電圧比較部 252 の参照信号入力段と共に、参照信号 RAMP が供給される構成となっているのである。

#### 【0164】

40

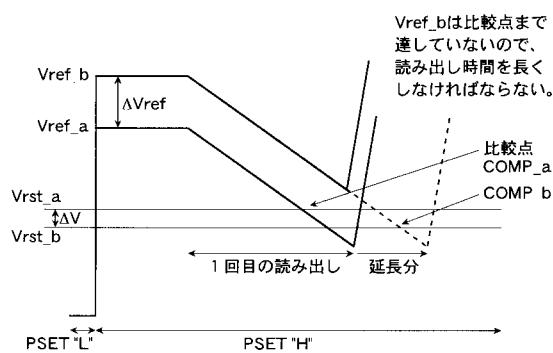

< 従来構成の問題点の詳細 >

図 9 は、従来の参照信号供給 IF 部 28 の問題点を詳細に説明する図である。図 1 に示したカラム処理部 26 (特にカラム A/D 回路 25) においては、2 回に及ぶ、リセット電位および信号電位のカウント時間を如何に短くするかが高速撮像のポイントとなる。

#### 【0165】

ここで、図 7 に示す従来の参照信号供給 IF 部 28 を備えた構成の場合、カウンタ読出しに時間が掛かってしまう。これは、以下のような理由によると考えられる。すなわち、複数ある電圧比較部 252 を駆動するための各種の信号線が共通配線となっており、ある電圧比較部で発生した雑音がこれらの共通配線を通じて他の電圧比較部に伝達され、他の電圧比較部における動作に影響を及ぼすことが考えられる。

50

## 【0166】

たとえば、図7に示す構成から分かるように、各垂直列に電圧比較部252が存在し、各電圧比較部252は電源電圧(Vdd)、接地電位(グランド;Vss)、参照信号RAMP用の参照信号線251、PSET信号用のリセット制御線331(特にPSET制御線331ともいう)およびNSET信号用のリセット制御線332(特にNSET制御線332ともいう)が、それぞれ共通配線となっている。そのため、ある列の電圧比較部252で発生した雑音が、上記の各共通配線を通じて他列の電圧比較部252の動作に影響を及ぼすことが考えられる。

## 【0167】

特に、処理対象のアナログ信号や参照信号が入力される各入力段には、比較処理における動作点を設定するスイッチ手段としてのトランジスタ306,307が設けられており、このスイッチ手段が共通のリセット信号で制御されることにより、リセット信号PSETを通じた雑音伝播が参照信号RAMPに対する電圧バラ付きに大きく影響を及ぼす。10

## 【0168】

ここで、リセット信号PSETを通じた雑音には、リセット信号PSETをインアクティブ(オフ)にしたときに発生する、PSET用のトランジスタ307,308のフィードスルーやチャージインジェクション、あるいはkTCノイズで決まる固定点バラ付きが存在する。

## 【0169】

たとえば、図7には、異常動作時におけるリセット信号PSETのオフ直後の参照信号RAMPと差動入力ゲートの電位を表している。図7に示すように、PSET制御線331を通じた雑音により、参照信号RAMPの電位がVrefではなく、時間方向に雑音成分Vref(t)を持ち、Vref + Vref(t)となる。20

## 【0170】

ここで、リセット信号PSETは場所依存性やスイッチの性能により遅延を持つので、各垂直列のPSET用のトランジスタ306,307がオフになる時間が異なる。そのため、電圧比較部252aのリセット信号PSETのオフで発生した雑音成分Vref(t)が、参照信号線251を経由して、未だリセット信号PSETがオフされていない電圧比較部252bの参照信号入力段(トランジスタ303のゲート)に達し、このトランジスタ303のリセット電位Vref\_bを変えてしまう可能性がある

## 【0171】

この現象は、図9に示すように、リセット時の列ごとの差動入力ゲート端電位バラ付きVrefという形で表れることになり、全列のこのバラ付きの影響がA/D変換処理に悪影響を与えないようにするには、1回目の読み出し時間を長くしなければならない。30

## 【0172】

すなわち、図3を用いた1回目(画素信号におけるリセット成分)の読み出動作の説明では、リセット成分Vのバラ付きは一般に小さく、またリセットレベルVrstは概ね全画素共通であるので、任意の垂直信号線19の画素信号電圧Vxにおけるリセット成分Vの出力値はおおよそ既知であるとし、1回目のリセット成分Vの読み出し時には、RAMP電圧を調整することにより、ダウンカウント期間(t10 ~ t14; 比較期間)を短くすることが可能であると説明していた。40

## 【0173】

しかしながら、参照信号RAMPに電位バラ付き(雑音成分Vref)が存在すると、何れの列の電圧比較部252においても比較処理が完了できるだけの十分な余裕を持つ必要が生じ、その分だけ、1回目の比較処理時間が掛かってしまう。

## 【0174】

たとえば、図9に示すように、画素信号におけるリセットレベルのバラ付きがV(Vrst\_a > Vrst\_b)であって、列Haでは参照信号Vref\_aにてリセットレベルVrst\_aの比較点COMP\_aまで達していても、列Hbでは参照信号Vref\_bにてリセットレベルVrst\_bの比較点COMP\_bまで達することができず、これを避けるには、比較点COMP\_bまで達するよう、比較処理時間を延長しなければならない。たとえば、7ビット分のカウント期間(150

28クロック)では1回目のA/D変換処理を完了させることができず、さらに、たとえば1ビット分の追加が必要になり、1回目の読出処理時間が長く掛かってしまうことになる。

#### 【0175】

このように、参照信号生成部27と電圧比較部252とを直接に参照信号線251でインターフェースする従来の参照信号供給IF部28では、特に1回目のカウンタ値の読出しに時間が掛かってしまうが、その原因是、上記説明から明らかなように、参照信号生成部27で生成された参照信号RAMPを、単一の参照信号線251を介して全ての垂直列の電圧比較部252の参照信号入力段まで供給していることがそもそもの要因であると考えてよい。

10

#### 【0176】

したがって、この問題を解消するには、一例として、ある列の垂直列の電圧比較部252の参照信号入力段を他の列の電圧比較部252の参照信号入力段と分離する構成(以下参照信号入力段分離構造ともいう)を探る手法が有効であると考えられる。こうすることで、仮に、ある垂直列の電圧比較部252の参照信号入力段に雑音成分Vrefが発生しても、分離された方の電圧比較部252の参照信号入力段には、その雑音成分Vrefが伝達されない。以下、このような参照信号入力段分離構造を持つ参照信号供給IF部28について詳細に説明する。

#### 【0177】

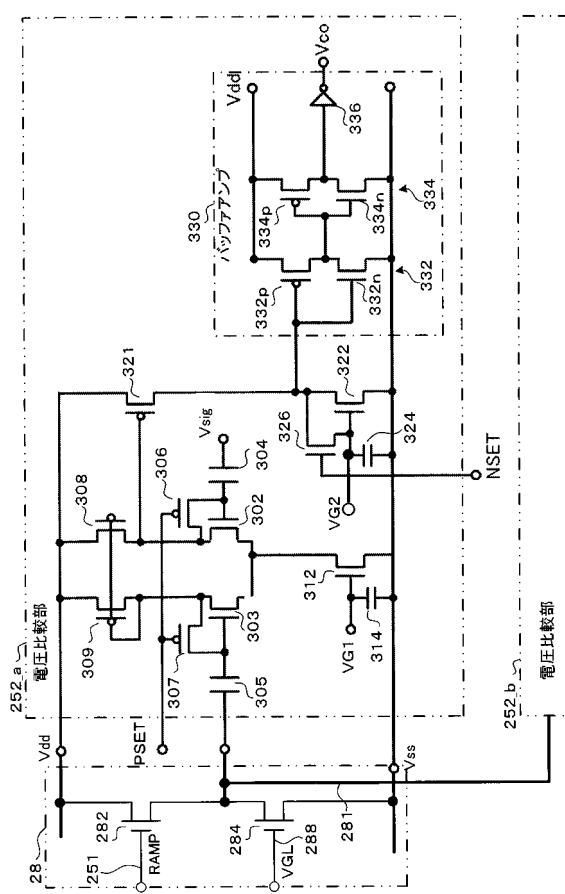

##### <バッファ回路；第1実施形態>

20

図10は、バッファ回路280の詳細構成例の第1実施形態を、電圧比較部252の詳細構成例とともに示した図である。また、図11は、比較例としての従来の参照信号供給IF部28を電圧比較部252の詳細構成例とともに示した図である。

#### 【0178】

バッファ回路280は、ソースフォロア回路構成となっている。具体的には、バッファ回路280は、ドレインが電源Vddに接続されるとともに参照信号線251を介して供給される参照信号RAMPをゲートに受けるN MOS型のトランジスタ(アンプトランジスタという)282と、このアンプトランジスタ282のソースと接地との間に配され、アンプトランジスタ282に動作電流を供給するN MOS型のトランジスタ(負荷MOSトランジスタという)284とを備えている。

30

#### 【0179】

アンプトランジスタ282のソースは、電圧比較部252の差動対を構成する一方のトランジスタ303のゲートに設けられる結合コンデンサ313の入力側に接続される。負荷MOSトランジスタ284のゲートには動作電流を規定するDCゲート電圧VGLが通信・タイミング制御部20からバイアス制御線288を介して供給される。

#### 【0180】

このように、バッファ回路280を利用して参照信号入力段を複数ブロックに分離する参照信号入力段分離構造を探ると、参照信号線251と各ブロックの参照信号出力線281とがバッファ回路280によって分離され、参照信号出力線281に生じ得るバッファ回路280の出力電位の変動は入力電位(つまり参照信号線251)に殆ど影響を及ぼさないので、あるブロックに属する電圧比較部252の参照信号入力段に雑音成分Vrefが発生しても、分離された方のブロックに属する電圧比較部252の参照信号入力段には、その雑音成分Vrefが伝達されない。

40

#### 【0181】

これにより、図6に点線とその点線の矢指部に×印で示すように、従来の参照信号供給IF部28で問題としてきた、PSETオフ時のある列の電圧比較部252の雑音が参照信号線251を通じて他のブロック内の電圧比較部252における1回目(本例ではリセット電位のA/D変換用)の比較処理における比較点(特にリセット点ともいう)を変動させてしまう可能性を少なくすることができる。このリセット点の変動を抑えることは、画素信号におけるリセット電位をカウントする時間、つまりリセット電位のA/D変換処理時間を

50

短くすることに寄与し、高速撮像が可能となるのである。

#### 【0182】

ここで「可能性を少なくすることができる」といったのは、図6に実線で示すように、同一ブロック内では、参照信号出力線281を介して、PSETオフ時のある列の電圧比較部252の雑音が他列の電圧比較部252の比較点を変動させてしまうことは避けることができないからである。この点においては、ブロック内の電圧比較部252の数、つまり1つのバッファ回路280が担当する電圧比較部252の数を少なくすればするほどこの問題が軽減されることになり、後述する参照信号供給IF部28の第2実施形態では、この点に着目している。

#### 【0183】

なお、バッファ回路280を構成するトランジスタ282, 284は、電圧比較部252の差動入力端のリニアリティを保証するため、画素部10における画素信号生成部5の出力段の構成、具体的には、増幅用トランジスタ42および負荷MOSトランジスタ242でなる画素信号生成部5側のソースフォロワ回路と、アンプトランジスタ282および負荷MOSトランジスタ284でなる電圧比較部252側のソースフォロワ回路の構成を同じにすることや、ほぼ同じトランジスタ特性を持つものとすることが望ましい。この点においては、電圧比較部252を含むカラム処理部26および参照信号供給IF部28を画素部10と同一チップ上に集積すると都合がよい。

#### 【0184】

具体的には、アンプトランジスタ282および負荷MOSトランジスタ284の酸化膜厚および閾値電圧が、増幅用トランジスタ42および負荷MOSトランジスタ242のものと等しいことにより、同じトランジスタ特性となるものが挙げられる。また、サイズに関しては、アンプトランジスタ282は画素信号生成部5で使用しているソースフォロワ回路の増幅用トランジスタ42と同等で、負荷MOSトランジスタ284は同様に負荷MOSトランジスタ242と同等の大きさであるのが望ましい。これは、電圧比較部252の両入力ゲートのリニアリティを等しくする上で効果的であるために依る。

#### 【0185】

なお、バッファ回路280をなすソースフォロワ回路を構成するトランジスタのサイズは、厳密に画素信号生成部5のトランジスタのサイズと同等にする必要は無く、対応する各トランジスタのゲート幅/ゲート長比（いわゆるサイズ比）が等しくなるようにすることで、事実上、同じトランジスタ特性と言えるものであればよい。ただし、CMOSイメージセンサで複数の閾値電圧を持つトランジスタを使用する場合には、上記の各対応するトランジスタは閾値が等しくなる組み合わせで用いることが望ましい。

#### 【0186】

また、参照信号生成部27で生成された参照信号RAMPが、ソースフォロワ構成のバッファ回路280を正確に通過することを目的に、ソースフォロワ構成のバッファ回路280の周波数帯域が電圧比較部252の周波数帯域と同等かもしくはより広い方が望ましい。

#### 【0187】

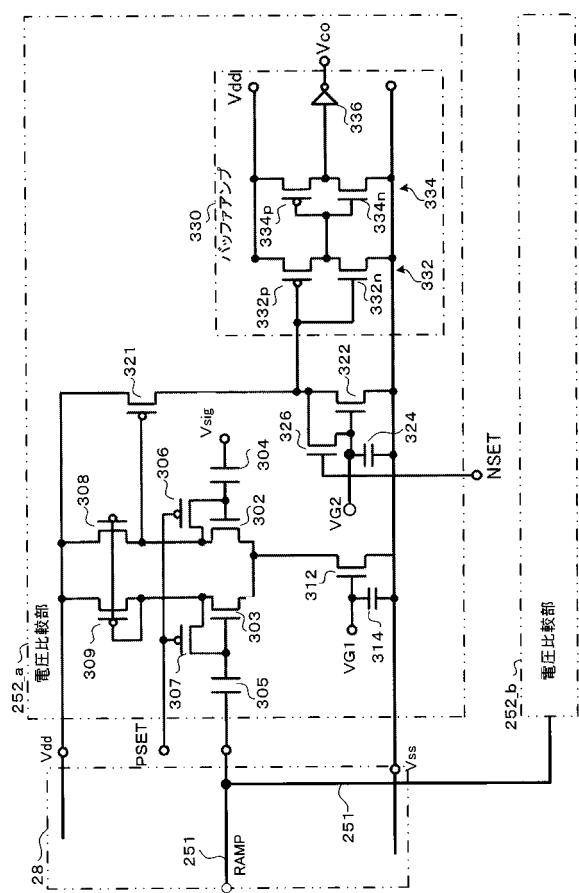

##### <バッファ回路；第2実施形態>

図12および図13は、バッファ回路280の詳細構成例の第2実施形態を電圧比較部252の詳細構成例とともに示した図である。この第2実施形態のバッファ回路280は、単位画素3として図2(A)に示す4TR構成のものを使用した場合への対処構成である。

#### 【0188】

第1実施形態でも説明したが、バッファ回路280を構成するソースフォロワは、電圧比較部252の差動入力端のリニアリティを保証するため、画素部10側のソースフォロワ回路と同じ構成にすることや、トランジスタのサイズを同じにすることが望ましい。

#### 【0189】

単位画素3が図2(A)に示す4TR構成の場合に、これに対処するには、図12に示すように、アンプトランジスタ282のソースと負荷MOSトランジスタ284のドレイ

10

20

30

40

50

ンとの間に、垂直選択用トランジスタ40と同一のサイズで同一特性のN M O S型のトランジスタ286を追加するとよい。このトランジスタ286は、ドレインをアンプトランジスタ282のソースに、ソースを負荷M O Sトランジスタ284のドレインに、ゲートを電源Vddに接続する。

#### 【0190】

また、画素信号生成部5において、垂直選択用トランジスタ40のドレインが電源Vddに、ソースが増幅用トランジスタ42のドレインにそれぞれ接続され、垂直選択ゲートS E L Vが垂直選択線52に接続されるものである場合には、ソースフォロワ構成と同じにするべく、図13に示すように、アンプトランジスタ282のドレインと電源Vddとの間に、垂直選択用トランジスタ40と同一のサイズで同一特性のN M O S型のトランジスタ286を追加するとよい。このトランジスタ286は、ドレインを電源Vddに、ソースをアンプトランジスタ282のドレインに、ゲートを電源Vddに接続する。

10

#### 【0191】

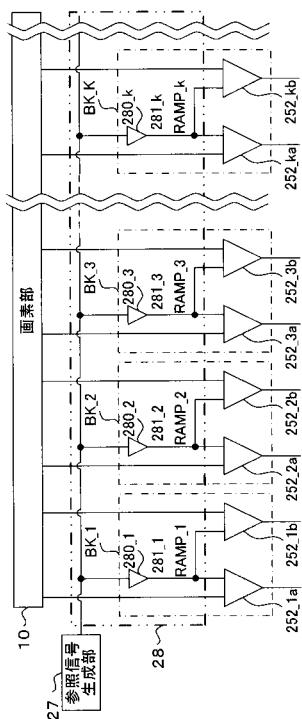

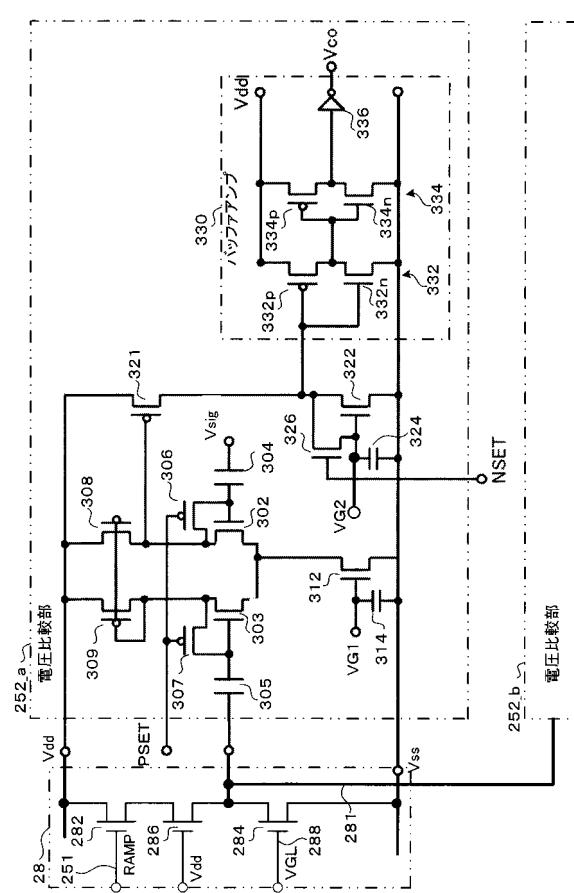

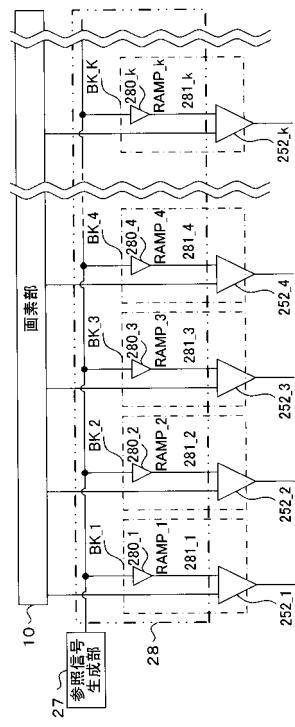

<参照信号供給IF部；第2実施形態>

図14および図15は、参照信号供給IF部28の第2実施形態を示す図である。ここでは特に単位画素3および参照信号生成部27とカラムA D回路25の電圧比較部252との間の信号の伝達（インターフェース）手法に着目して示している。ここで、図14は第2実施形態で採用するインターフェース手法の基本構成を示し、図15は、その全体概要を示している。

#### 【0192】

第1実施形態の参照信号供給IF部28では、電圧比較部252の参照信号入力段を分離する参照信号入力段分離構造を探るに当たって、1つのバッファ回路280を含んで構成される1つのブロック内に複数の電圧比較部252を備える、つまり1つのバッファ回路280が担当する電圧比較部252の数を複数としていた。これに対して、この第2実施形態では、1つのバッファ回路280が1つの電圧比較部252を担当する、つまり、垂直列ごとにバッファ回路280と電圧比較部252とを1つずつ備えることで、1つの比較部に対して1つの信号経路で参照信号を伝達する完全な個別対応を探る点に特徴を有している。

20

#### 【0193】

たとえば、バッファ回路280\_1から出力された参照信号RAMP\_1は、参照信号出力線281\_1を介して、電圧比較部252\_aの参照信号入力段（コンデンサ305側のゲート）に伝達され、電圧比較部252\_aでは参照信号Vref\_aとして入力される。同様に、バッファ回路280\_2から出力された参照信号RAMP\_2は、参照信号出力線281\_2を介して、電圧比較部252\_bの参照信号入力段（コンデンサ305側のゲート）に伝達され、電圧比較部252\_bでは参照信号Vref\_bとして入力される。なお、各参照信号出力線281\_kは、必要箇所までの配線で留めることもできるが、各列で信号遅延量を等しくするため、図に点線で示すように、同長にしてもよい。

30

#### 【0194】

なお、図14では図示を割愛しているが、図15に全体概要を示すように、他のバッファ回路280\_kから出力された参照信号RAMP\_kは、参照信号出力線281\_kを介して、他の単一列の電圧比較部252の参照信号入力段（コンデンサ305側のゲート）に入力される。

40

#### 【0195】

このように、垂直列ごとにバッファ回路280と電圧比較部252とを1つずつ設けた参照信号入力段分離構造を探ると、バッファ回路280の数が第1実施形態よりも大幅に増えることになるが、参照信号線251と各ブロックの参照信号出力線281とがバッファ回路280によって完全に（つまり全ての垂直列が）分離されることになる。

#### 【0196】

これにより、図14に点線とその点線の矢指部に×印で示すように、あるブロックに属する（本例では任意の1列そのものである）電圧比較部252の参照信号入力段に雑音成

50

分  $V_{ref}$  が発生しても、分離された方のブロックに属する（本例ではその他の全ての列である）電圧比較部 252 の参照信号入力段には、その雑音成分  $V_{ref}$  が伝達されない。これにより、従来の参照信号供給 IF 部 28 で問題としてきた、PSET オフ時のある列の電圧比較部 252 の雑音が参照信号線 251 を通じて他列の電圧比較部 252 におけるリセット点を変動させてしまうことをほぼ完全に抑えることができ、画素信号におけるリセット電位をカウントする時間を短くすることが、第 1 実施形態よりも確実に実現できるようになるのである。

#### 【0197】

なお、回路規模の側面では、第 2 実施形態の方がバッファ回路 280 の数が多く回路規模が大幅に増えるので、リセット点変動抑制性能が劣ることにはなるものの、回路規模の側面では、1つのバッファ回路 280 が担当する電圧比較部 252 の数が多いほど好ましいことになる。したがって、1つのバッファ回路 280 が担当する電圧比較部 252 の数に関しては、回路規模と他の列におけるリセット点変動抑制性能の側面の双方を勘案して、決定するのがよい。

#### 【0198】

以上、本発明を実施形態を用いて説明したが、本発明の技術的範囲は上記実施形態に記載の範囲には限定されない。発明の要旨を逸脱しない範囲で上記実施形態に多様な変更または改良を加えることができ、そのような変更または改良を加えた形態も本発明の技術的範囲に含まれる。

#### 【0199】

また、上記の実施形態は、クレーム（請求項）にかかる発明を限定するものではなく、また実施形態の中で説明されている特徴の組合せの全てが発明の解決手段に必須であるとは限らない。前述した実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜の組合せにより種々の発明を抽出できる。実施形態に示される全構成要件から幾つかの構成要件が削除されても、効果が得られる限りにおいて、この幾つかの構成要件が削除された構成が発明として抽出され得る。

#### 【0200】

たとえば、上記実施形態では、電圧比較部 252 の参照信号入力段を分離する参照信号入力段分離構造を探るに当たって、バッファ回路 280 を利用して参照信号線 251 と参照信号入力段と接続される参照信号出力線 281 とを分離するようにしていったが、各垂直列の電圧比較部 252 の参照信号入力段を複数ブロックに分離することができればよく、その限りにおいて、様々な変形構成を探ることができる。

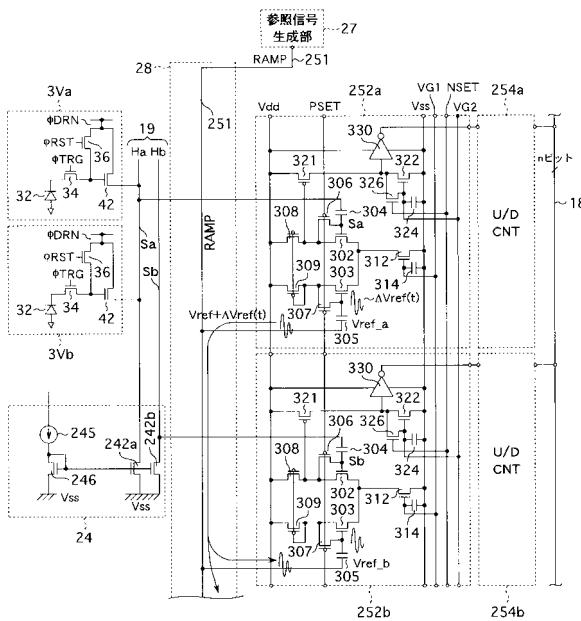

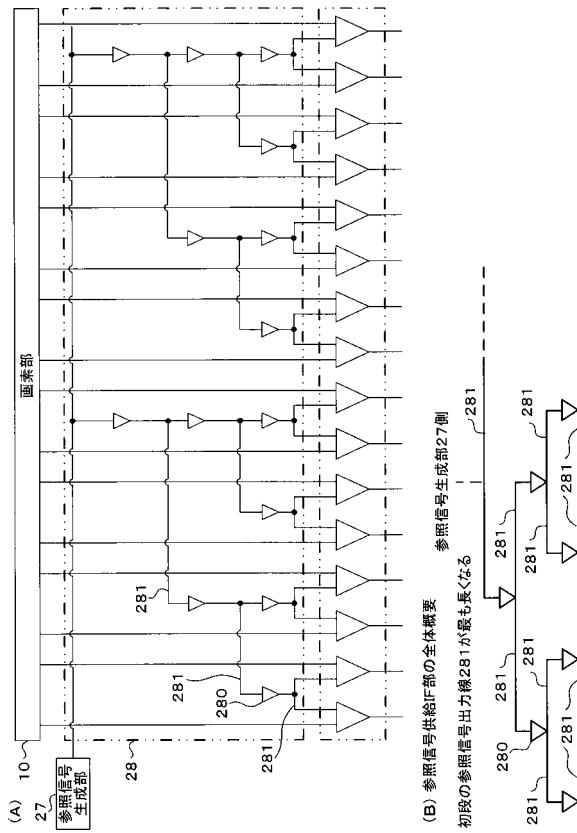

#### 【0201】

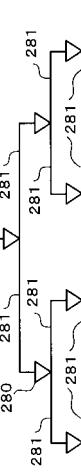

たとえば、図 16 に示す変形実施形態 1 のように、バッファ回路 280 を多段接続構成にすることで参照信号線をツリー構造にして分配することもできる。このようなツリー構造を探れば、電圧比較部 252 に近い下段側ではできるだけ隣接した電圧比較部 252 を担当するようにして電圧比較部 252 の出力側の参照信号出力線 281 の引回しを必要箇所までの配線で留めることで短くしつつ、参照信号生成部 27 に近い上段側では、各列で信号遅延量を等しくするため同長にするのがよい。

#### 【0202】

上述した第 1 および第 2 実施形態のように各バッファ回路 280 を 1 段で並列配置すると、信号遅延量を等しくするための同長配線が全てのバッファ回路 280 について必要になるのに対して、変形実施形態 1 では、バッファ回路 280 の使用数が増えるものの、信号遅延量を等しくするための同長配線は参照信号生成部 27 側の上段側のバッファ回路 280 についてのみの対処でよく、全体としての参照信号用配線の引回しが容易になる。

#### 【0203】

すなわち、図 16 (B) に全体概要を示しているが、デバイス内で参照信号を均等に分配する際に図 16 のようなツリー構造のレイアウトを探る場合、回路全体としての信号遅延誤差（一般的にスキューと呼ばれる）は、最も配線長が長くならざるを得ない初段のスキューによって制約されることとなるが、ここでのスキューを最小化する上では、参照信

10

20

30

40

50

号出力線 281 を同長にするのがよいのである。

**【0204】**

またたとえば、図17に示す変形実施形態2のように、参照信号生成部27自身を、複数ブロックに分離する構成を探ることが考えられる。この場合、参照信号生成部27そのものを複数用意することになり、参照信号供給IF部28としては、各参照信号生成部27の出力をそのまま伝達する手法を探ることになる。

**【0205】**

なおこの変形実施形態2の場合にも、回路規模の側面では、図17(A)に示すように、1つの参照信号生成部27が1つの電圧比較部252を担当する構成を探ると、参照信号生成部27の数が多く回路規模が大幅に増えるので、リセット点変動抑制性能が劣ることにはなるものの、回路規模の側面では、図17(B)に示すように、1つの参照信号生成部27が担当する電圧比較部252の数が多いほど好ましいことになる。したがって、1つの参照信号生成部27が担当する電圧比較部252の数に関しては、回路規模と他の列におけるリセット点変動抑制性能の側面の双方を勘案して決定するのがよい。

10

**【0206】**

参照信号供給IF部28を複数設けるか、バッファ回路280を複数設けるかの比較においては、参照信号生成部27の構成の方が遙かに回路規模が大きく、上述した第1あるいは第2実施形態の参照信号供給IF部28の構成の方が好ましいことになる。

**【0207】**

また、上記実施形態では、参照信号線251に生じるノイズの発生要因として、電圧比較部252の参照信号入力段に設けられるPSET用のトランジスタ306, 307によるリセット信号PSETを通じた雑音伝播を特に問題としていたが、上記実施形態の仕組みは、このような雑音に限らず、たとえば浮遊容量を介した飛込みノイズなど参照信号線251に生じるあらゆる種類のノイズ(雑音)に対して効果を奏するものである。

20

**【0208】**

また、上記実施形態では、光や放射線などの外部から入力される電磁波に対して感應性をするCMOS型の固体撮像装置について例示したが、物理量の変化を検知するあらゆるものに、上記実施形態で説明した仕組みを適用でき、光などに限らず、たとえば、指紋に関する情報を圧力に基づく電気的特性の変化や光学的特性の変化に基づき指紋の像を検知する指紋認証装置(特開2002-7984や特開2001-125734などを参照)など、その他の物理的な変化を検知する仕組みにおいて、アナログ信号をデジタル信号に変換する際の参照信号線上のノイズ対策として、上記実施形態を同様に適用することができる。

30

**【図面の簡単な説明】**

**【0209】**

【図1】本発明に係る半導体装置の一実施形態であるCMOS固体撮像装置の概略構成図である。

【図2】単位画素の構成例と、駆動部と駆動制御線と画素トランジスタの接続態様を示す図である。

【図3】カラムAD回路における基本動作である信号取得差分処理を説明するためのタイミングチャート(その1)である。

40

【図4】カラムAD回路における基本動作である信号取得差分処理を説明するためのタイミングチャート(その2；パイプライン処理)である。

**【図5】**電圧比較部の詳細な構成例を示す図である。

**【図6】**参照信号供給IF部の第1実施形態を示す図(その1)である。

**【図7】**参照信号供給IF部の第1実施形態を示す図(その2)である。

**【図8】**従来の参照信号供給IF部を示す図である。

**【図9】**従来の参照信号供給IF部28の問題点を詳細に説明する図である。

【図10】バッファ回路の詳細構成例の第1実施形態を、電圧比較部の詳細構成例とともに示した図である。

50

【図11】比較例としての従来の参照信号供給IF部を電圧比較部の詳細構成例とともに示した図である。

【図12】バッファ回路の詳細構成例の第2実施形態を電圧比較部の詳細構成例とともに示した図(その1)である。

【図13】バッファ回路の詳細構成例の第2実施形態を電圧比較部の詳細構成例とともに示した図(その2)である。

【図14】参照信号供給IF部の第2実施形態を示す図(その1)である。

【図15】参照信号供給IF部の第2実施形態を示す図(その2)である。

【図16】参照信号供給IF部の変形実施形態1を示す図である。

【図17】参照信号供給IF部の変形実施形態2を示す図である。

10

### 【符号の説明】

#### 【0210】

1...固体撮像装置、3...単位画素、5...画素信号生成部、7...駆動制御部、10...画素部、12...水平走査部、14...垂直走査部、18...水平信号線、19...垂直信号線、20...通信・タイミング制御部、24...読み出電流源部、25...カラムAD回路、26...カラム処理部、27...参照信号生成部、28...参照信号供給IF部、29...出力部、251...参照信号線、252...電圧比較部、254...カウンタ部、280...バッファ回路、281...参照信号出力線

【図1】

【図2】

【 义 3 】

【 四 4 】

【 四 5 】

【 四 6 】

### ＜第1実施形態のインターフェース手法＞

【 図 7 】

【 四 8 】

#### ＜従来のインターフェース手法＞

【 図 9 】

【図10】

【 図 1 1 】

【図12】

【図13】

【図14】

## ＜第2実施形態のインターフェース手法＞

【図 1 5】

【図 1 6】

【図 1 7】

(B) 参照信号供給部の全体概要

初段の参照信号出力線 281 が最も長くなる

参照信号生成部 27 個

---

フロントページの続き

(72)発明者 安井 幸弘

神奈川県横浜市保土ヶ谷区神戸町134番地 ソニー・エルエスアイ・デザイン株式会社内

(72)発明者 新田 嘉一

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 栗栖 正和

(56)参考文献 特開2000-286706(JP,A)

米国特許第06344877(US,B1)

特開平01-286625(JP,A)

特開2001-244446(JP,A)

特開平09-238286(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88

H04N 5/335