(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3833064号

(P3833064)

(45) 発行日 平成18年10月11日(2006.10.11)

(24) 登録日 平成18年7月28日(2006.7.28)

(51) Int.C1.

F 1

HO3K 19/0175 (2006.01)

HO3K 19/00 101N

請求項の数 6 (全 12 頁)

(21) 出願番号 特願2000-372580 (P2000-372580)

(22) 出願日 平成12年12月7日 (2000.12.7)

(65) 公開番号 特開2002-176350 (P2002-176350A)

(43) 公開日 平成14年6月21日 (2002.6.21)

審査請求日 平成16年10月27日 (2004.10.27)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100085811

弁理士 大日方 富雄

(72) 発明者 金城 新

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体グループ内

(72) 発明者 大門 一夫

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体グループ内

(72) 発明者 遠藤 祐弘

千葉県茂原市早野3681番地 日立デバイスエンジニアリング株式会社内

最終頁に続く

(54) 【発明の名称】半導体集積回路および液晶駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

正相入力端子に正相クロックを受け、負相入力端子に負相クロックを受け第1クロックを出力する第1差動アンプと、

負相入力端子に上記正相クロックを受け、正相入力端子に上記負相クロックを受け第2クロックを出力する第2差動アンプと、

正相データを受ける第1外部端子と、

負相データを受ける第2外部端子と、

上記正相データ及び負相データを上記第1外部端子及び上記第2外部端子とを介して差動で受けてデータを出力する第3差動アンプと、

上記第1差動アンプから出力される上記第1クロックにより、上記第3差動アンプからの上記データをラッチする第1ラッチと、

上記第2差動アンプから出力される上記第2クロックにより、上記第3差動アンプからの上記データをラッチする第2ラッチと、を具備し、

上記第3差動アンプは、

そのゲートが上記第1外部端子と上記第2外部端子とに各々接続された一対の差動MOSFETと、

電源と上記一対の差動MOSFETの共通ソースとの間に接続された電流源MOSFETと、

グランドと上記一対の差動MOSFETのそれぞれのドレインとの間に接続された負

荷MOSFETとを含み、

上記電流源MOSFETのゲートには、電流制御用電圧が供給されることを特徴とする半導体集積回路。

【請求項2】

上記第1差動アンプ及び第2アンプのそれぞれは、

そのゲートが上記第1外部端子と上記第2外部端子とに各々接続された一対の差動MOSFETと、

電源と上記一対の差動MOSFETの共通ソースとの間に接続された電流源MOSFETと、

グランドと上記一対の差動MOSFETのそれぞれのドレインとの間に接続された負荷MOSFETとを含み、

上記電流源MOSFETのゲートには、電流制御用電圧が供給されることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

上記第1ラッチ及び上記第2ラッチの出力データに基づいて液晶表示装置を駆動する液晶駆動回路を備えることを特徴とする請求項1または2に記載の半導体集積回路。

【請求項4】

液晶パネルに表示すべき画素データが差動形態で供給され差動インターフェース回路と、

上記差動インターフェース回路に結合され、上記差動インターフェース回路からの出力データを格納するデータレジスタと、

上記データレジスタの出力に結合され、上記液晶パネルの1ライン分の画素データが格納されるデータラッチ回路と、

上記データラッチ回路に結合され、1ライン分の画素データから各画素ごとの階調度を示すアナログ信号に変換するD/Aコンバータと、

上記D/Aコンバータからのアナログ信号に基づいて上記液晶パネルのデータ線を駆動する駆動電圧を発生する出力バッファと、

その正相入力端子に正相クロックを受け、その負相入力端子に負相クロックを受け第1クロックを出力する第1差動アンプと、

その負相入力端子に上記正相クロックを受け、その正相入力端子に上記負相クロックを受け第2クロックを出力する第2差動アンプと、

と、を具備し、

上記差動インターフェース回路は、正相データを受ける第1外部端子と負相データを受ける第2外部端子とに結合され、上記正相データ及び負相データを上記第1外部端子及び上記第2外部端子とを介して差動データを受けて上記出力データを出力する第3差動アンプを含み、

上記データレジスタは、上記第1差動アンプから出力される上記第1クロックにより、上記第3差動アンプからの上記データをラッチする第1ラッチと、上記第2差動アンプから出力される上記第2クロックにより、上記第3差動アンプからの上記データをラッチする第2ラッチとを含み、

上記第3差動アンプは、そのゲートが上記第1外部端子と上記第2外部端子とに各々接続された一対の差動MOSFETと、電源と上記一対の差動MOSFETの共通ソースとの間に接続された電流源MOSFETと、グランドと上記一対の差動MOSFETのそれぞれのドレインとの間に接続された負荷MOSFETとを含み、

上記電流源MOSFETのゲートには、電流制御用電圧が供給されることを特徴とする液晶駆動装置。

【請求項5】

上記第1差動アンプ及び第2アンプのそれぞれは、

そのゲートが上記第1外部端子と上記第2外部端子とに各々接続された一対の差動MOSFETと、

10

20

30

40

50

電源と上記一対の差動MOSFETの共通ソースとの間に接続された電流源MOSFETと、

グランドと上記一対の差動MOSFETのそれぞれのドレインとの間に接続された負荷MOSFETとを含み、

上記電流源MOSFETのゲートには、電流制御用電圧が供給されることを特徴とする請求項4に記載の液晶駆動装置。

【請求項6】

上記差動インターフェース回路は、LVDS等の小振幅差動信号インターフェース回路であることを特徴とする請求項4に記載の液晶駆動装置。

【発明の詳細な説明】

10

【0001】

【発明の属する技術分野】

この発明は、例えばLVDS (Low Voltage Differential Signals) その他の小振幅差動信号インターフェースを備えた入力回路に適用して有用な技術に関し、例えばTFT (thin film transistors) 液晶パネルを駆動する液晶ドライバなどに利用して特に有用な技術に関する。

【0002】

【従来の技術】

例えばノート型コンピュータや液晶ディスプレイに備わるTFT液晶パネルのデータ線を駆動する液晶ドライバとして、1画素あたり6ビットのデジタルデータを高速に入力するとともに、これらのデジタルデータに基づいて64階調で384本の出力電圧を発生するものがある。近年、このような液晶ドライバにおいて高速にデジタルデータを送受信するインターフェースとして、LVDSやその派生規格の小振幅差動信号インターフェースが用いられている。このような小振幅差動信号インターフェースを用いることで、CMOSインターフェースなどを適用した場合に比べて、消費電力の削減や入出力信号の電磁波干渉(EMI)の低減を図ることが出来る。

20

【0003】

従来、小振幅差動信号インターフェースを備えた入力回路においてクロック信号の立上りと立下りの両エッジでデジタルデータを取り込む場合、例えば、図5や図6に示すような方式でデータ信号の入力を行っていた。

30

【0004】

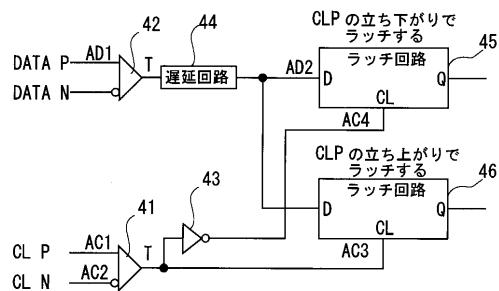

図5に示す方式は、外部から入力されるクロック信号CLの立上りと立下りに基づきデータ信号AD2を取り込む第1のラッチ回路45と第2のラッチ回路46とを備えるとともに、差動信号の形態で送られてくるクロック信号CLP, CLNを1個の差動アンプ(小振幅差動信号インターフェース回路)41で受信して、クロック信号CLP又はCLNと同相の出力AC3と該出力ACをインバータ43で反転した出力AC4とを2個のラッチ回路45, 46のクロック端子にそれぞれ入力してラッチタイミングを与えるようにしたものである。

【0005】

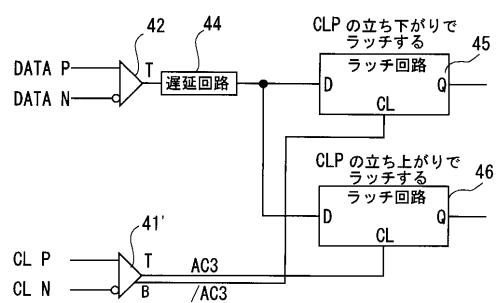

図6に示す方式は、図5の方式と同様にクロック信号CLの立上りと立下りに同期してデータを取り込む第1および第2のラッチ回路45, 46を備えるとともに、差動信号の形態で送られてくるクロック信号CLP, CLNを差動入力差動出力型のアンプ(小振幅差動信号インターフェース回路)41'で受信するとともに、その差動出力AC3, /AC3を2個のラッチ回路45, 46にそれぞれ入力してラッチタイミングを与えるようにしたものである。

40

【0006】

【発明が解決しようとする課題】

本発明者らは上記従来の小振幅差動インターフェースについて検討した結果、データ信号を正しく取り込めないおそれがあることを見出した。

【0007】

50

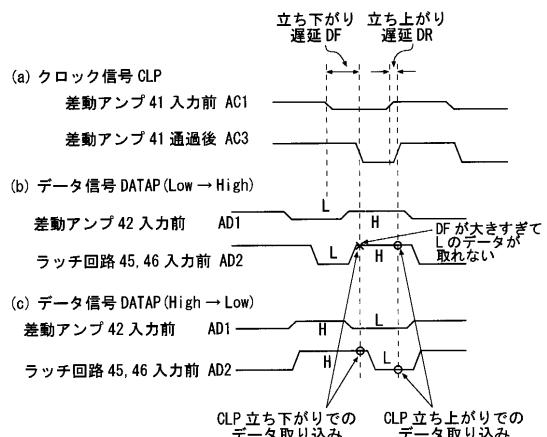

図7には、従来の小振幅差動信号インターフェースを備えた入力回路において信号の取り込みが正常に行えない場合のタイムチャートを示す。同図(a)は、外部から入力されたクロック信号C Lの差動アンプ41入力直前のクロック信号A C 1と、差動アンプ41を通過した後のクロック信号A C 3、(b)および(c)は外部から入力されたデータ信号D A T A Pの差動アンプ42入力直前のデータ信号A D 1と、差動アンプ42を通過しラッチ回路45, 46に入力されるデータ信号A D 2を、それぞれ示している。(b)と(c)とでは、データ信号A D 1は互いに約180°ずれている。

#### 【0008】

ところで、差動アンプ(小振幅差動信号インターフェース回路)は、一般に一対の差動信号の電位差を増幅する差動増幅段を入力側に備えるが、この差動増幅段の特徴から、出力の立上り時間と立下り時間とを同じにすることが難しい。例えば、PチャネルMOSFETとNチャネルMOSFETの駆動力比を変えて立上り時間と立下り時間と同じにしようとしても、入力信号の中心電圧や振幅、差動増幅段に供給される電源電圧、並びに、温度等のちょっとした変化により、その出力の立上り時間と立下り時間に差異が生じてしまう。

10

#### 【0009】

そして、立上り時間や立下り時間に差異が生じると、その信号は後段の駆動段やバッファ段で波形整形されるので、図7(a)に示されているように、立上り信号の遅延D Rと立下り信号の遅延D Fの差異となって現れる。また、図7(a)から分るように、周期的に変化するクロック信号の場合には、差動アンプから出力されるクロック信号A C 3のデューティ比が変化してしまうことになる。

20

#### 【0010】

その結果、図5に示すような従来の入力回路では、差動アンプ41から出力されるクロック信号A C 3の立上りタイミングと立下りタイミングでそれぞれラッチ回路45, 46にデータを取り込むため、クロックタイミングにばらつきが生じたような影響を与え、ラッチ回路のセットアップ時間・ホールド時間に合わせてデータ信号の入力タイミングを調整するのが困難になる。例えば、図7(c)に示すようにクロックの立下りのときにハイレベルからロウレベルに変化するデータ信号D A T A Pが入力された場合には、クロック信号A C 1, A C 3の遅延に差があってもデータを正しく取り込むことが出来るが、図7(b)のようにクロックの立下りのときに応じてロウレベルからハイレベルへ変化するデータ信号D A T A Pが入力された場合には、クロックの立下りタイミングにおいてデータが正しく取り込まれないといった事態が生じかねない。

30

#### 【0011】

その結果、入力回路の高速化が阻害されたり、或いは、差動アンプから出力されるクロック信号のデューティ比を一定に保つために差動アンプの入力中心電圧や電源電圧の許容変動範囲を狭めなければならないという課題が生じる。

#### 【0012】

また、図6に示すように、クロック信号を入力する差動アンプ41'において該差動アンプ41'から差動出力を取り出すようにした場合でも、一般に差動増幅段は正相側と負相側とで非対称の回路構成となっているため、同じ立上りの増幅出力を見ても正相側の出力と負相側の出力とでは同一の遅延にはならず、図5の入力回路と同様の問題が生じる。

40

#### 【0013】

この発明の目的は、クロック信号の立上りと立下りの両方でデータを取り込む小振幅差動インターフェースを用いた入力回路において、クロック信号の立上り部分の遅延と立下り部分の遅延のズレをなくし、データラッチタイミングの調整を容易にすることで、入力信号の中心電圧や電源電圧の許容変動範囲をある程度広くしたまま高速化を阻害することのない入力回路を提供することにある。

#### 【0014】

この発明の他の目的は、上記の入力回路をデータ信号入力部に設けることで、入力信号の中心電圧や電源電圧の許容変動範囲を狭めることなく、EMIを低減し且つ低消費電力に

50

画素毎のデジタルデータを入力することのできる液晶駆動装置を提供することにある。

【0015】

この発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添附図面から明らかになるであろう。

【0016】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を説明すれば、下記のとおりである。

【0017】

すなわち、クロック信号およびデータ信号がそれぞれ差動信号で入力される差動アンプを備え、上記クロック信号の立上りと立下りのそれぞれに同期して上記データ信号を内部に取り込む入力回路において、上記クロック信号が入力される差動アンプが2個設けられ、これらの差動アンプの各正相入力端子と負相入力端子には前記差動クロック信号の正相信号と負相信号がそれぞれ逆の関係で入力されるとともに、両差動アンプからはともに正相側入力と同相或いは負相側入力と同相の信号がデータ取込み用のタイミング信号として出力されるように構成するものである。

10

【0018】

このような手段によれば、クロック信号が入力される2個の差動アンプの一方から出力されるクロック信号と他方から出力されるクロック信号との両方を用いることで、外部入力されるクロック信号の立上りと立下りの両エッジで信号を取り込むように出来るとともに、個々の差動アンプでは、その差動増幅段で増幅信号の立上り時間と立下り時間にずれが生じても、増幅信号の立上り又は立下りの何れかのみを用いて信号取り込み用のクロック信号を出力すれば良いので、それらのズレが信号取り込み用のクロック信号のばらつきとして影響しない。従って、2個の差動アンプから出力されるクロック信号のタイミングを適宜に設定することが可能となり、データ取り込みのタイミング調整を容易にすることが出来る。従って、半導体の製造ばらつき、入力クロックの中心電圧、電源電圧、並びに、温度などの条件がある程度変化しても、動作に支障をきたさない高速な入力回路を実現できる。

20

【0019】

望ましくは、上記クロック信号が入力される2個の差動アンプの差動増幅段は同一の回路構成であると良い。それにより、これらのうち一方の差動アンプの差動増幅段の動作と、他方の差動アンプの差動増幅段の動作とが、正相側と負相側とで完全に対称なものとなり、クロック信号が入力される2個の差動アンプで生じる外部入力されたクロック信号の立上り部分の遅延と立下り部分の遅延をほぼ同一にすることが出来る。

30

【0020】

具体的には、タイミング信号の立上り又は立上りに基づいて上記データ信号をラッチする第1のラッチ回路と第2のラッチ回路が設けられ、これらのうち第1のラッチ回路には上記クロック信号が入力される2個の差動アンプのうちの一方の差動アンプより出力されたタイミング信号が入力され、第2のラッチ回路には他方の差動アンプより出力されたタイミング信号が入力されるように構成すると良い。

40

【0021】

また望ましくは、上記第1のラッチ回路および第2のラッチ回路はともに各々に入力されるタイミング信号の立上り、或いは立下りでデータ信号をそれぞれラッチするように構成すると良い。

【0022】

このように構成することで、外部入力されたクロック信号の立上り部分の遅延と立下り部分の遅延をほぼ同一にして、これらクロック信号の両エッジに基づき容易なタイミング調整でデータラッチすることが出来る。

【0023】

また、本発明に係る液晶駆動装置は、デジタル表示データが入力され、該表示データに基

50

づき液晶駆動用信号を生成して出力する液晶駆動装置において、上述の入力回路が上記表示データを取り込む入力手段として設けた構成である。

【0024】

このような液晶駆動装置によれば、上記の入力回路により、入力信号の中心電圧や電源電圧の許容変動範囲を狭めることなく、高速なデジタルデータの入力を実現することが出来る。

【0025】

【発明の実施の形態】

以下、本発明の好適な実施例を図1～図4の図面に基づいて説明する。

【0026】

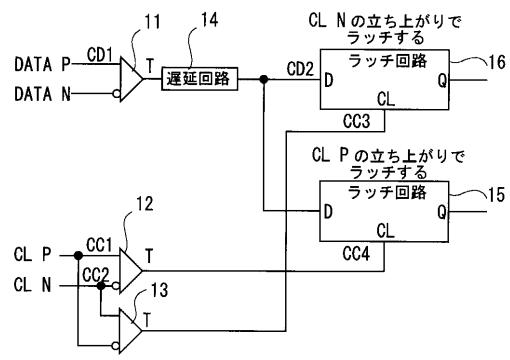

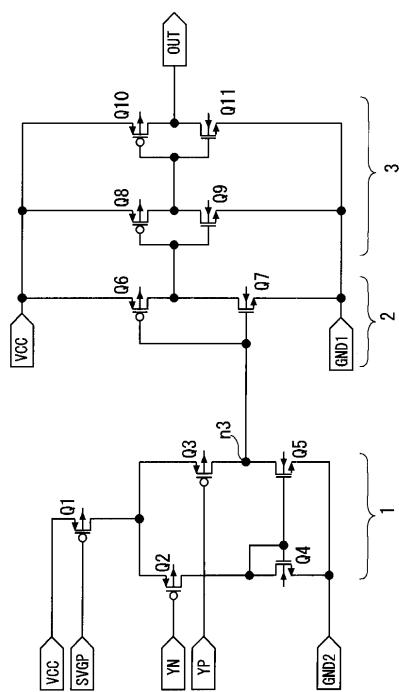

図1は、本発明を適用して好適な入力回路の実施例を示す論理ブロック図、図2は、図1の差動アンプの詳細例を示す回路図である。

【0027】

この実施例の入力回路は、例えばIEEE (Institute of Electrical and Electronics Engineers)に規定されているLDV5インターフェースや、その派生技術の小振幅差動信号インターフェースを用いた入力回路であり、小振幅差動信号(例えば振幅200mV～500mV)の外部クロックCLP, CLNやデータ信号DATAP, DATANを入力して、外部クロック(例えば正相側の外部クロックCLP)の立上りと立下りの両エッジで入力データを内部に取り込むように構成されている。

【0028】

図1において、11～13は小振幅差動信号インターフェース回路を構成する差動アンプ、14はクロックとのレーシングを避けるためにデータ信号に適宜遅延をかける遅延回路、16と15はクロック(クロック端子CLに入力されるタイミング信号)に同期してデータを一時的にラッチするクロック同期式のラッチ回路である。

【0029】

差動アンプ11～13は、特に制限されるものでないが、図2に示すように、一対の差動入力MOSFET Q2, Q3とその共通ソースに接続された定電流用MOSFET Q1と差動入力MOSFET Q2, Q3のドレインに接続されたカレントミラー接続のアクティブ負荷MOSFET Q4, Q5とからなる差動増幅段1、差動増幅段1からの増幅出力を受けてこの出力電圧に応じてハイレベルとロウレベルの信号を出力する駆動段2、駆動段2からの出力を後段の回路のインピーダンスに整合させるバッファ段3などから構成される。

【0030】

差動増幅段1においては、電源VCC側からグランド側に直流電流が生じるが、消費電力を低減するために、MOSFET Q1のゲートに印加される電流制御用電圧SVPにより定電流用MOSFET Q1の電流を制御することによってこの差動増幅段1の直流電流はある程度小さくなるように設定されている。また、差動増幅段1は、差動入力MOSFET Q2, Q3のドレインに接続されるカレントミラー型のアクティブ負荷MOSFET Q4, Q5の共通ゲート端子がMOSFET Q4のドレイン端子に結合されているため、回路は正相側と負相側とで非対称になっている。

【0031】

このような差動増幅段1によれば、電源電圧VCCや制御電圧SVPの変化、正相と負相の入力端子YP, YNから入力される信号の中心電圧や振幅の変化、PチャネルMOSFET Q2, Q3とNチャネルMOSFET Q4, Q5の製造ばらつき等により、出力ノードn3から出力される信号の立上り時間と立下り時間に差異が生じてしまう。そして、この信号は後段の駆動段2やバッファ段3で波形整形されるので、出力端子から出力される信号は立上りと立下りとで遅延の異なる信号となって現れる。すなわち、一対の入力差動信号のうち正相信号の電位が負相信号の電位よりも高くなったタイミングから出力信号OUTが立ち上がるまでの遅延と、正相信号の電位が負相信号の電位よりも低くなったタイミングから出力信号OUTが立ち下がるまでの遅延とが同一時間とならず、図2の

10

20

30

40

50

差動アンプでは電圧などの条件により立上りの際の遅延時間よりも立下りの際の遅延時間の方が長くなってしまう。

【0032】

図1の実施例の入力回路では、差動データ信号DATA, DATA-Nは1個の差動アンプ11により取り込むのに対し、差動クロック信号CLP, CLNは2個の差動アンプ12, 13により取り込むように構成されている。そして、第1の差動アンプ12では正相側クロック信号が正相入力端子に入力され負相クロック信号が負相入力端子に入力される一方、第2の差動アンプ13ではその逆に正相クロック信号が負相入力端子に入力され負相側クロック信号が正相入力端子に入力されるように構成されている。また、これら第1および第2の差動アンプ12, 13は同一の回路構成になっている。これによって、正相側入力クロック信号CLPが立ち上がってから第1の差動アンプ12側の出力が立ち上がるまでの遅延時間と、正相側のクロック信号CLPが立ち下がってから第2の差動アンプ13側の出力が立ち上がるまでの遅延時間とが同一にされる。同様に、正相側入力クロック信号CLPが立ち下がってから第1の差動アンプ12側の出力が立ち下がるまでの遅延時間と、正相側入力クロック信号CLPが立ち上がってから第2の差動アンプ13側の出力が立ち下がるまでの遅延時間とが同一にされる。

10

【0033】

また、図1の実施例の入力回路では、第1の差動アンプ12の出力(タイミング信号)が第1のラッチ回路15のクロック端子に、第2の差動アンプ13の出力(タイミング信号)が第2のラッチ回路16のクロック端子に入力され、第1および第2のラッチ回路15, 16では、それぞれ入力クロックの立上りでデータのラッチ動作を行うように構成されている。その結果、第1のラッチ回路15は外部クロックCLPの立上りに同期してデータをラッチし、第2のラッチ回路16は外部クロックCLPの立下りに同期してデータをラッチするように動作する。

20

【0034】

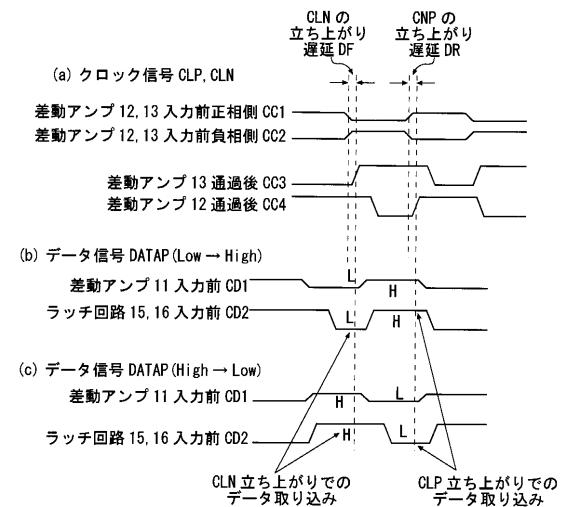

図3には、上記入力回路の動作を説明するためのタイムチャートを示す。

【0035】

同図において、(a)は外部から入力されるクロック信号CLP, CLNの第1および第2の差動アンプ12, 13入力直前のクロック信号CC1, CC2と第1と第2の差動アンプ12, 13を通過した後のクロック信号CC3, CC4、(b)および(c)は外部から入力される正相側のデータ信号DATAの差動アンプ11入力直前のデータ信号CD1と、差動アンプ11を通過してラッチ回路15, 16に入力されるデータ信号CD2とを、それぞれ示している。(b)と(c)とでは、データ信号CD1は互いに約180°ずれている。

30

【0036】

この実施例の入力回路によれば、図3(a)に示すように、差動クロック信号CLP, CLNが2個の差動アンプ12, 13に対して互いに正相側と負相側とが逆にされた状態で入力されるので、第1差動アンプ12から出力されるクロック信号CC4の立上り遅延DRと、第2差動アンプ13から出力されるクロック信号CC3の立上り遅延DFは同一のものとなる。

40

【0037】

図3(b)や(c)に示すように、データ信号DATAは差動アンプ11を通過することでその立上りと立下りとで異なる遅延が及ぼされるが、この実施例の入力回路においては、第1ラッチ回路15は第1差動アンプ12からの出力クロック信号CC4により、また第2ラッチ回路16は第2差動アンプ13からの出力クロック信号CC3により、それぞれデータ信号をラッチする。

【0038】

そして、第1のラッチ回路15に入力されるクロック信号CC4の立上り遅延DRと、第2のラッチ回路16に入力されるクロック信号CC3の立上り遅延DFとが同じ長さであるので、図3(b), (c)に示すように、データ信号DATAがハイレベルからロウ

50

レベルへ変化する場合でもロウレベルからハイレベルへ変化する場合でも上記のクロック信号 C C 3 , C C 4 の立上りエッジでそれぞれラッチ回路 1 5 , 1 6 に正しくデータが取り込まれる。その結果、実施例の入力回路では予め設定されたセットアップ時間とホールド時間に合わせてデータ信号 C D 2 が確定された状態になり、データラッチが正常に行われる。

【 0 0 3 9 】

次に、上記入力回路を半導体集積回路に適用した例について説明する。

【 0 0 4 0 】

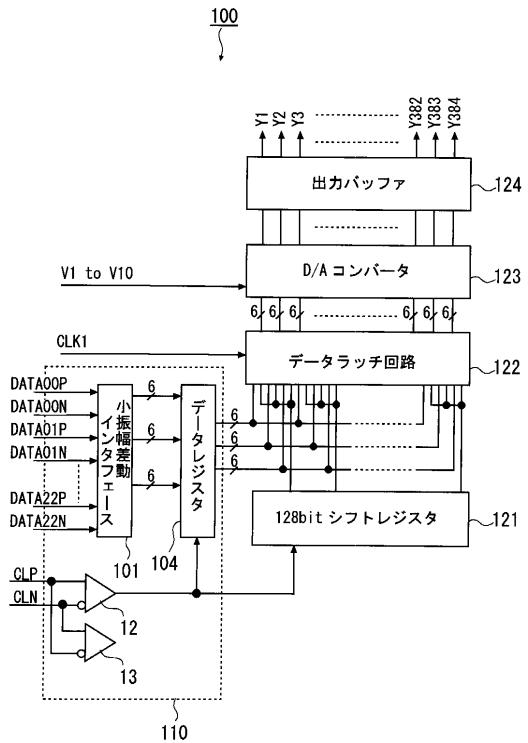

図 4 は、上記の入力回路をデータ入力部に備えた液晶駆動装置である液晶ドライバの全体構成を示すブロック図である。 10

【 0 0 4 1 】

この実施例の液晶ドライバ 1 0 0 は、例えばノート型コンピュータに備わる TFT 液晶パネルやディスプレイとして用いられる TFT 液晶パネルのデータ線を駆動するもので、特に制限されるものでないが、単結晶シリコンのような 1 個の半導体チップ上に形成されて構成される。

【 0 0 4 2 】

この実施例の液晶ドライバ 1 0 0 は、小振幅差動信号の形態で外部から入力される例えば 1 画素あたり 6 ビットのデジタルデータ DATA 0 0 P , DATA 0 0 N ~ DATA 2 2 P , DATA 2 2 N を高速に入力する小振幅差動インターフェース 1 0 1 、同様に小振幅差動信号の形態で入力される外部クロック CL P , CL N を入力する小振幅差動インターフェースである差動アンプ 1 2 , 1 3 、入力したデジタルデータを一時的に保持するデータレジスタ 1 0 4 、データレジスタ 1 0 4 に保持されたデータが順次所定ビットに移されて 1 ライン分のデータを保持するデータラッチ回路 1 2 2 、データレジスタ 1 0 4 のデータをデータラッチ回路 1 2 2 の所定ビットに転送するためのシフトレジスタ 1 2 1 、データラッチ回路 1 2 1 に保持された 1 ライン分のデジタルデータから各画素毎の階調度を示すアナログ信号に変換する D / A コンバータ 1 2 3 、 D / A コンバータ 1 2 3 からのアナログ信号に基づき TFT 液晶パネルのデータ線の駆動電圧を発生させて出力する出力バッファ 1 2 4 等を備えている。 20

【 0 0 4 3 】

この液晶ドライバ 1 0 0 において図 1 の入力回路に相当する部分は、小振幅差動インターフェース 1 0 1 、差動アンプ（小振幅差動インターフェース） 1 2 , 1 3 、データレジスタ 1 0 4 からなる入力回路 1 1 0 の部分である。小振幅差動インターフェース 1 0 1 には、図 1 の差動アンプ 1 1 が所定ビット分設けられ、データレジスタ 1 0 4 にも図 1 のラッチ回路 1 5 , 1 6 が所定ビット分設けられている。 30

【 0 0 4 4 】

以上のように、この実施例の入力回路によれば、クロック入力用に 2 個の差動アンプ 1 2 , 1 3 を設け、それぞれ正相側と負相側が逆にされるように信号を入力させることで、外部クロックの立上りの部分の遅延と立下りの部分の遅延とを同一にしたクロック信号を内部で生成することが出来る。そして、このように生成したクロック信号を用いて外部クロックの立上りと立下りの両エッジに同期させて信号を取り込むようにしたので、データラッチのタイミング調整を容易にすることが出来る。従って、半導体の製造ばらつき、入力クロックの中心電圧、電源電圧、並びに、温度などの条件がある程度変化しても、動作に支障をきたさない高速な入力回路を実現できる。 40

【 0 0 4 5 】

また、このような入力回路をデータ入力部に備えた液晶ドライバ 1 0 0 によれば、入力信号の中心電圧や電源電圧の許容変動範囲を狭めることなく、高速なデジタルデータの入力を実現することが出来る。

【 0 0 4 6 】

また、入力回路 1 1 0 における入力信号の立上り遅延と立下り遅延のばらつきは、クロック信号については解消されデータ信号のみ考慮すればよいことから、液晶ドライバ 1 0 0 50

の入力回路 110 におけるセットアップ・ホールド時間に係るスペック向上を図ることが出来る。また、それにより更に高速な動作も実現できる。

#### 【0047】

また、外部クロック C L P , C L N を 2 個の差動アンプ 12 , 13 に入力することで、クロック入力端子の入力容量は多少変化するが、入力端子と差動アンプ 12 , 13 の間には、規定外の入力信号から内部の回路を保護する保護ダイオード或いは入力電圧をクランプする大きな保護MOSFETが接続されており、それらに対して差動アンプ 12 , 13 のゲート容量は小さなものなので（具体的には 5 pF に対して 0.1 pF 程度かそれ以下）、入力インピーダンスの変化は無視できるレベルである。また、差動アンプが 1 個増えることでその分消費電流も増加するが、半導体チップ全体の消費電流でみれば僅かなものである。 10

#### 【0048】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0049】

例えば、実施例において差動アンプ（小振幅差動信号インターフェース）の具体的な回路構成を例示したが、差動増幅段などは公知となっている種々の変形例があるし、差動増幅段より後段の回路構成も種々の変形が可能である。また、MOSFET に限らずバイポーラトランジスタにより構成することも出来る。また、クロック入力用の 2 個の差動アンプは全く同じ回路構成にする必要もなく、立上り遅延が同等であれば異なる回路構成でも同様の効果が得られる。 20

#### 【0050】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野である液晶ドライバについて説明したがこの発明はそれに限定されるものでなく、小振幅差動信号インターフェースを用いて信号入力を行う半導体集積回路に広く利用することができる。

#### 【0051】

##### 【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。 30

#### 【0052】

すなわち、本発明に従うと、小振幅差動信号インターフェースを用いた入力回路において、クロック信号の立上り遅延と立下り遅延のばらつきが解消され、入力信号の立上り遅延と立下り遅延のばらつきはデータ信号についてのみ考慮すれば良くなるので、クロック信号についてもばらつきが生じていた従来回路に比べて、セットアップ・ホールドに係るスペックが向上され、それにより更に高速な動作が実現できるという効果がある。

#### 【0053】

また、入力信号の中心電圧や電源電圧の許容変動範囲を狭めることなく、高速なデジタルデータの入力を実現できるという効果がある。 40

##### 【図面の簡単な説明】

【図 1】本発明を適用して好適な入力回路の実施例を示す論理ブロック図である。

【図 2】図 1 の差動アンプの部分を詳細に示すMOS回路図である。

【図 3】図 1 の入力回路の動作を説明するタイムチャートである。

【図 4】本発明に係る入力回路を備えた液晶ドライバの全体構成を示すブロック図である。

【図 5】従来の小振幅差動信号インターフェースを用いた入力回路の第 1 例を示す論理ブロック図である。

【図 6】同、従来の入力回路の第 2 例を示す論理ブロック図である。

【図 7】従来の入力回路でデータラッチが正常に行われない場合の動作を説明するタイム 50

チャートである。

【符号の説明】

|           |                           |

|-----------|---------------------------|

| 1         | 差動増幅段                     |

| 2         | 駆動段                       |

| 3         | バッファ段                     |

| 1 1       | 差動アンプ ( 小振幅差動信号インターフェース ) |

| 1 2 , 1 3 | クロック入力用の差動アンプ             |

| 1 4       | 遅延回路                      |

| 1 5 , 1 6 | ラッチ回路                     |

| 1 0 0     | 液晶ドライバ ( 液晶駆動装置 )         |

| 1 1 0     | 入力回路                      |

| 1 0 1     | 小振幅差動インターフェース             |

| 1 0 4     | データレジスタ                   |

| C L P     | 正相側の外部クロック信号              |

| C L N     | 負相側の外部クロック信号              |

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

審査官 宮島 郁美

(56)参考文献 特開2000-114958(JP, A)

特開平11-298459(JP, A)

国際公開第02/047063(WO, A1)

特開2001-034356(JP, A)

特開2001-267892(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096

H03K5/00-5/02, 5/08-5/12, 5/15-5/26