(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

**特許第4717168号

(P4717168)**

(45) 発行日 平成23年7月6日(2011.7.6)

(24) 登録日 平成23年4月8日(2011.4.8)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| G09G 5/39    | (2006.01) |

| G09G 5/00    | (2006.01) |

| H04N 5/907   | (2006.01) |

| H04N 5/765   | (2006.01) |

| GO9G         | 5/36      |

| GO9G         | 5/00      |

| HO4N         | 5/907     |

| HO4N         | 5/91      |

|              | 530D      |

|              | 550R      |

|              | B         |

|              | L         |

請求項の数 3 (全 14 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願平11-167485                 |

| (22) 出願日  | 平成11年6月14日(1999.6.14)        |

| (65) 公開番号 | 特開2000-356984(P2000-356984A) |

| (43) 公開日  | 平成12年12月26日(2000.12.26)      |

| 審査請求日     | 平成18年6月14日(2006.6.14)        |

前置審査

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 復代理人 | 100115624<br>弁理士 濱中 淳宏                     |

| (74) 復代理人 | 100128015<br>弁理士 堀田 誠                      |

| (74) 代理人  | 110001243<br>特許業務法人 谷・阿部特許事務所              |

| (72) 発明者  | 本間 義浩<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

審査官 居島 一仁

最終頁に続く

(54) 【発明の名称】信号処理装置および信号処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

輝度データ及び色差データから構成される画像データを記憶する第1記憶手段と、

第1周期で前記第1記憶手段の前記画像データを読み出す読出手段と、

前記第1周期とは非同期でテレビ信号処理を行う信号処理部と、

前記読出手段に対する読み出しリクエストの発行を制御することにより、前記第1周期に同期して前記読み出された画像データを一時的な記憶領域に書き込み、前記テレビ信号処理に同期して前記一時的な記憶領域の画像データを前記信号処理部に向けて読み出す第2記憶手段と、

を備え、

前記第2記憶手段は、

前記テレビ信号処理の垂直プランギング期間では前記一時的な記憶領域からの画像データの読み出しを行わず、前記テレビ信号処理の映像期間では前記一時的な記憶領域からの画像データの読み出しを行うようにし、前記垂直プランギング期間及び前記映像期間において、前記一時的な記憶領域に画像データが第1の記憶量以下記憶された場合は第1の読み出しリクエストを発行し、前記一時的な記憶領域に画像データが第1の記憶量よりも大きい第2の記憶量以下記憶された場合は前記第1の読み出しリクエストよりも優先度の低い第2の読み出しリクエストを発行することを特徴とする画像処理装置。

## 【請求項 2】

10

20

前記テレビ信号処理は、NTSC規格及びPAL規格のうち少なくとも1つのための信号処理であることを特徴とする請求項1に記載の画像処理装置。

**【請求項3】**

被写体を撮影するための撮像手段と、

前記撮像手段により撮影されたデータを輝度データと色差データとに分けて処理する処理手段と、

をさらに備え、

前記第1記憶手段は、

前記処理手段により処理されたデータを記憶することを特徴とする請求項1または2に記載の画像処理装置。

10

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、信号処理装置および信号処理方法に関し、特に、TVモニタや液晶モニタへの表示を目的とする映像出力装置等の映像信号処理装置に関する。

**【0002】**

**【従来の技術】**

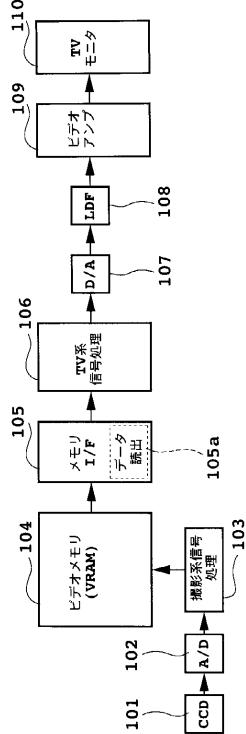

図4は、TVモニタへの表示を目的とする従来の映像出力装置の構成例を示す。

**【0003】**

101は、CCDセンサである。このCCDセンサ101で受光された映像は、電気信号に変換される。

20

**【0004】**

102は、A/D変換器であり、CCDセンサ出力のアナログ映像信号をデジタルの映像信号に変換する。

**【0005】**

103は、撮影系の信号処理回路である。この信号処理回路103は、CCD出力信号から色キャリア除去、アパチャーチャー補正、ガンマ処理等を施して輝度信号を作り、また同時に、色補間、マトリクス変換、ガンマ処理、ゲイン調整等を施して色差信号を作り、YUV等の映像信号を出力する。

**【0006】**

30

104は、VRAMである。このVRAM104は、例えば、ダイナミックRAM(DRAM)に書き込み用と読み出し用のポートを設け、水平ライン毎にアドレッシングを行う構成をしたビデオ用のメモリからなる。

**【0007】**

105は、VRAM104からデータの読み出しを行うためのメモリインターフェイス(I/F)回路である。このデータI/F回路105のデータ読み出し回路105aでVRAM104に格納された映像データを読み出し、後段の回路へ出力する(例えば、水平ライン毎に連続したメモリアドレス上にYUYV...とデータを格納し、水平ライン毎にH1,H2,...のアドレスポインタとデータサイズに従ってデータを読み出す処理)。

**【0008】**

40

106は、TV系の信号処理回路106である。この信号処理回路106は、データI/F105のVRAMデータ出力を、クロマエンコード処理、帯域補正、コンポジット化等の信号処理をし、TV用のデジタル信号にして出力する。

**【0009】**

107は、D/A変換器(DAC)であり、デジタル映像信号出力をアナログ映像信号に変換している。

**【0010】**

108は、映像帯域のローパスフィルタ(LPF)であり、D/A変換後に含まれている高周波ノイズ成分をカットし、コンポジットビデオ信号としてビデオアンプ109へ出力している。

50

**【0011】**

109は、ビデオアンプであり、TV用の信号レベルやTV用の出力インピーダンスにする回路である。

**【0012】**

110は、一般的なビデオ入力を有するTVモニタであり、NTSC方式やPAL方式等とそれぞれのTV方式に従って映像を表示する。

**【0013】**

そして、CCD101で受光された映像信号は、A/D変換器102でデジタル映像信号に変換され、撮像系の信号処理回路103でYUV形式の映像信号に処理される。

**【0014】**

信号処理回路103の出力Yは、輝度信号を示し、色キャリア除去、アパチャード正、ガンマ変換等の処理をして生成している。

**【0015】**

Uは(B-Y)の色差信号で、Vは(R-Y)の色差信号を示し、色補間、マトリクス変換、ガンマ変換等の処理を施して生成している。

**【0016】**

信号処理回路103の撮像系信号処理によるY, U, Vの出力は、例えば下記に示すYUVデータ配列に示すように、画面左上から順に

(上位データ) Y<sub>0</sub> Y<sub>1</sub> Y<sub>2</sub> Y<sub>3</sub> Y<sub>4</sub> Y<sub>5</sub>...

(下位データ) U<sub>0</sub> V<sub>0</sub> U<sub>2</sub> V<sub>2</sub> U<sub>4</sub> V<sub>4</sub>...

とVRAM104へ格納されていく。

**【0017】**

このVRAM104のデータは、メモリIF105のデータ読出し回路105aにより読み出され、TV系の信号処理回路106で、輝度や変調クロマ信号に処理され加算されてコンポジット信号を生成し、D/A変換器107へ出力する。

**【0018】**

そして、TV系の信号処理回路106の映像出力は、D/A変換器107でアナログ信号に変換され、LPF108で帯域制限される。さらに、ビデオアンプ109を通してTVモニタ110に出力する。

**【0019】****【発明が解決しようとする課題】**

従来の回路構成の場合、ビデオメモリ(VRAM)を、システムで使用するDRAM上に構成すると、DRAMのリード/ライトに使用するシステムクロックと、TV系信号処理に使用するクロックを同期させなければならない。

**【0020】**

このため、システムクロックが、TV系信号処理クロックの整数倍にする等の制約を受けることになる(TVモニタへの映像信号処理クロックは、クロマエンコード処理や同期信号発生の都合上、HTSCではサブキャリアの4倍=4fscが、PAL方式では、水平周波数の908倍が適している)。

**【0021】**

また、システムクロックとTV系再生処理クロックを非同期にするためには、VRAMに独立した2ポートメモリ等を使用するなど、DRAMとは独立したVRAMを持つことになり、回路規模の増大を招くという問題がある。

**【0022】**

そこで、本発明の目的は、システムクロックに制約されず、回路規模を増大させることなく、システム全体のデータ転送効率を向上させることが可能な信号処理装置および信号処理方法を提供することにある。

**【0023】**

本発明の画像処理装置は、輝度データ及び色差データから構成される画像データを記憶する第1記憶手段と、第1周期で前記第1記憶手段の前記画像データを読み出す読出手段

10

20

30

40

50

と、前記第1周期とは非同期でテレビ信号処理を行う信号処理部と、前記読み出手段に対する読み出リクエストの発行を制御することにより、前記第1周期に同期して前記読み出された画像データを一時的な記憶領域に書き込み、前記テレビ信号処理に同期して前記一時的な記憶領域の画像データを前記信号処理部に向けて読み出す第2記憶手段と、を備え、前記第2記憶手段は、前記テレビ信号処理の垂直プランキング期間では前記一時的な記憶領域からの画像データの読み出しを行わず、前記テレビ信号処理の映像期間では前記一時的な記憶領域からの画像データの読み出しを行うようにし、前記垂直プランキング期間及び前記映像期間において、前記一時的な記憶領域に画像データが第1の記憶量以下記憶された場合は第1の読み出リクエストを発行し、前記一時的な記憶領域に画像データが第1の記憶量よりも大きい第2の記憶量以下記憶された場合は前記第1の読み出リクエストよりも優先度の低い第2の読み出リクエストを発行することを特徴とする。

10

## 【0038】

## 【発明の実施の形態】

以下、図面を参照して、本発明の実施の形態を詳細に説明する。

## 【0039】

## [概要]

まず、本発明の概要について説明する。

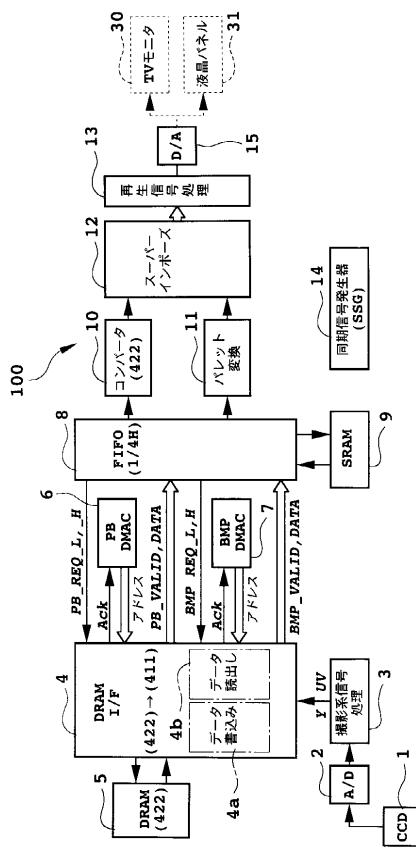

## 【0040】

本発明は、図1に示すように、VRAMを構成するためのDRAM5と、DRAM5に画像データを読み書きするためのインターフェイス(I/F)回路4と、インターフェイス回路4から読み出した画像データを一時的に記憶するためのFIFOメモリ8と、インターフェイス回路4へ読み出すデータのアドレスを指示するDMAC回路6,7とを備え、FIFOメモリ8のデータ書き込みレートと読み出しレートとを異なる構成にする。

20

## 【0041】

また、インターフェイス回路4とFIFOメモリ8のデータハンドシェイクにおいて、 FIFOメモリ8からのリクエスト信号に、互いに異なる少なくとも2種類の要求レベルを含ませるように構成にする。

## 【0042】

## [具体例]

次に、具体的な例を挙げて説明する。

30

## 【0043】

図1は、本発明に係る信号処理装置のシステム全体の構成を示すものである。

ここでは、TVモニタや液晶モニタへの表示を目的とする映像出力装置を例に挙げて説明する。

## 【0044】

本発明の実施例の構成図を示す。

## 【0045】

1は、CCDセンサである。このCCDセンサ1で受光した映像が、電気信号に変換して出力される。

## 【0046】

2は、A/D変換器である。このA/D変換器2は、CCDセンサ1の出力であるアナログ映像信号をデジタルの映像信号に変換する。

40

## 【0047】

3は、撮影系の信号処理回路である。この信号処理装置3は、CCD出力信号から色キャリア除去やアパチャー補正やガンマ処理等を施して輝度信号を作り、また同時に、色補間やマトリクス変換やガンマ処理やゲイン調整等を施して色差信号を作り、YUV等の映像信号を出力する(ここで、Yは輝度信号を示し、Uは色差信号B-Yを示し、Vは色差信号R-Yを示す)。

## 【0048】

4は、DRAM(ダイナミックランダムアクセスメモリ)5へデータの書き込みや読み出しが

50

行うためのDRAMインターフェイス(I/F)回路である。このDRAMI/F4は、データ書込み回路4aと、データ読出し回路4bとを備えている。

**【0049】**

データ書込み回路4aにより信号処理回路3の信号処理後の映像信号をDRAM5へ書込み、データ読出し回路4bによりDRAM5に格納された映像データを読出し、後段の回路へ出力する。

**【0050】**

5は、DRAMである。特に、ここでは、TVモニタ30や液晶パネル31に表示するためのビデオ用のメモリ空間をVRAMと称し、このDRAM5上に割り当てている。

**【0051】**

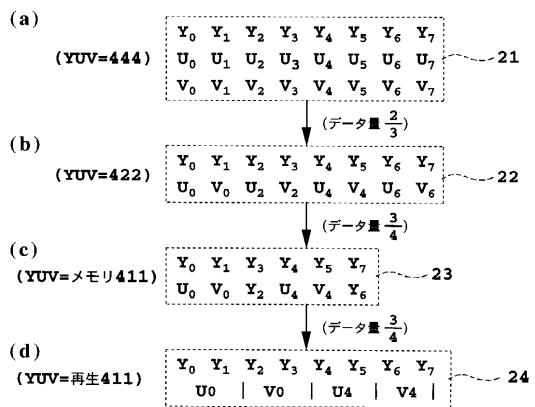

図2(a)～(d)は、DRAM5に格納するデータ構造を示す。

**【0052】**

図2(a)の21は、YUV=444形式のデータ構造を示しており、YUVの画素情報が1:1:1の情報比率で構成されている。

**【0053】**

図2(b)の22は、YUV=422形式のデータ構造を示しており、YUVの画面情報が4:2:2の比率で構成され、Y(輝度)に対してUV(色差)の情報量が半減している。

**【0054】**

図2(c)の23は、YUV=メモリ411形式のデータ構造を示しており、YUVの画素情報が4:1:1の比率で構成され、Yに対してUVの情報量が1/4に減っている。

**【0055】**

上記それぞれの形式のデータ量を比較すると、YUV=444に対して、YUV=422は2/3のデータ量になり、YUV=444に対して、YUV=メモリ411は1/2のデータ量になる。

**【0056】**

従って、用途により必要十分なデータ量が確保できるようにデータ形式を選択することによって、メモリ容量やDRAM5との転送効率の最適化を図ることができる。このことは、システム構成上、大変に有効である。

**【0057】**

そこで、DRAM5上のVRAMでは、この最適化を図るため、ビデオの輝度と色の帯域から考慮して、YUV=411形式のデータ構造で構成する。これにより、少ないメモリ容量と、適した転送効率とによって、ビデオ出力に必要な画素情報が得られる。

**【0058】**

さらに、VRAM構成条件としては、VRAMサイズをNTSC方式では水平752画素×垂直494ライン分とし、PAL方式では水平736画素×垂直580ライン分とする。

**【0059】**

また、1フィールド分は、前述のライン数の半分になり、NTSC方式では247ライン分、PAL方式では290ライン分になる。

**【0060】**

6は、DRAM5から自然画用のVRAMデータをダイレクトメモリアクセスで読出すためのアドレス発生回路(PB\_DMAC)である。

**【0061】**

TVモニタ30へ自然画のみを表示する場合には、PB\_DMAC6から、DRAM5中のVRAMデータを読出すためのアドレスが発生される。そして、そのアドレスに従ってDRAM5中のVRAMデータが読出され、DRAMI/F4からVALIDフラグと一緒に自然画データが FIFO8に送られる。

**【0062】**

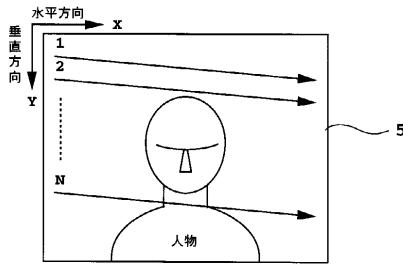

図3は、PB\_DMAC6のアドレスに従って、DRAM5中のVRAMからデータ読出

10

20

30

40

50

しを行うイメージを示す。

**【0063】**

X方向が水平の読み出し方向を示し、Y方向が垂直の読み出し方向を示す。図中の1, 2, ..., Nは、VRAM上のライン方向を示す。

**【0064】**

通常、TVモニタ30は、インターレース表示をしているので、これに合わせVRAMからの読み出しラインは、1, 3, 5, ... N-1, 2, 4, ..., Nというライン順に読み出される（ライン数Nは、NTSC方式とPAL方式とで異なる）。

NTSC = 494 ; PAL = 590）。

**【0065】**

そして、PB\_DMAC6への設定変更によって、フレーム／フィールド、NTSC方式／PAL方式に対応したDMAC動作の切り替えが可能である。フィールド時には、偶数ライン時に1ライン前の奇数ラインデータと同じデータを読み出すことになる。

**【0066】**

7は、TVモニタ30や液晶パネル31上に、文字やキャラクタ等を自然画にスーパーインポーズして表示するためのビットマップ（BMP）データをDRAM5からダイレクトメモリアクセスで読み出すためのアドレス発生回路（BMP\_DMAC）である。

**【0067】**

このBMP\_DMAC7も、PB\_DMAC6と同様に、設定変更によって、フレーム／フィールド、NTSC方式／PAL方式に対応したDMAC動作の切り替えが可能である。

**【0068】**

8は、DRAM1/F4からのデータを約1/4ライン分一時的に蓄える FIFO（ファーストイン・ファーストアウト）メモリである。

**【0069】**

このFIFOメモリ8から読み出される際には、再生信号処理しやすいように図2(d)の24に示すようなYUV=再生411形式に変換している。

**【0070】**

9は、FIFOメモリ8で使用するSRAMであり、1ライン分の1/4の容量を持っている。

**【0071】**

10は、コンバータ(422)であり、図2(d)のYUV=再生411形式からYUV=422形式へ変換するための回路である。

**【0072】**

前述したように、ビデオ出力の帯域としては、YUV=411の情報量で十分だが、文字やキャラクタ等のBMP画は帯域が広く、これとスーパーインポーズするのに自然画データをYUV=422形式にする必要があり、この回路において変換している。

**【0073】**

11は、パレット変換回路であり、文字等のBMPデータをパレットデータに変換する。

**【0074】**

BMPデータでそのままパレットの表示色を表現する場合、パレットの表示色の階調を多くすると、1画素当たりのビット数が増え過ぎてメモリ容量やデータ転送効率を悪くする。一方、1画素当たりのビット数を減らすと、パレットの表示色の階調が失われてしまうという問題がある。

**【0075】**

そこで、BMPデータのビット幅をパレットの同時発色の数に割り当て、パレット色の階調はある程度確保する方法がある。例えば、1画素当たりのBMPデータを4ビットとし、同時発色は16色にして、表示色の階調は16ビットで256階調にする。

**【0076】**

10

20

30

40

50

例えば、16ビット幅のパレットレジスタを16個分用意して、BMPデータの値により前記16個のパレットレジスタから1つを選択する回路にする。

#### 【0077】

すなわち、1画面上の同時発色数はBMPデータのビット幅によって決まり、パレット色の階調はパレットレジスタのビット幅によって決まる。言い替えると、パレット色の階調を維持したまま、同時発色数を制限するだけで、BMP領域のデータ容量を小さくできるようになる。

#### 【0078】

12は、自然画用のPBデータと文字やキャラクタ等のBMPデータをスーパーインポーズするスーパーインポーズ回路である。

10

#### 【0079】

回路構成としては、例えば、パレット色の階調の1つに透明色を用意して、透明色部は自然画をそのまま出力する。これにより、BMP画と自然画を画素毎に切り替えて表示することが可能になる。

#### 【0080】

なお、スーパーインポーズ回路12の出力段にスーパーインポーズをするか否かのセレクタを設け、スーパーインポーズしない方にセレクタを切り替えることにより、BMPデータ無しでもスーパーインポーズせずに自然画だけを表示することができる。

20

#### 【0081】

13は、再生信号処理回路であり、クロマエンコード処理や帯域補正やコンポジット化等の信号処理してTV用のデジタル信号にして出力する。

#### 【0082】

14は、FIFOメモリ8から再生信号処理回路13までのタイミング信号を発生させるための同期信号発生器(SSG)である。

#### 【0083】

15は、再生信号処理回路13のデジタル信号出力をアナログ信号に変換するためのD/Aコンバータである。

#### 【0084】

##### (本システムの特徴)

ここで、本システムの特徴であるFIFOメモリ8の処理について説明する。

30

#### 【0085】

FIFOメモリ8は、データの書込みと読み出しによって独立したポートを備え、書き込み周期に対して非同期にデータを読み出す。

例えば、FIFOメモリ8の書き込みクロック周期は、DRAM5のアクセスクロック周期、言い換えると、システムクロックと同じ(例えば、50MHz)にする。

#### 【0086】

これに対して、FIFOメモリ8の読み出しクロック周期は、TV信号処理に適した約14MHzにする。HTSC方式では、サブキャリアの4倍クロック( $4fsc = 14 \cdot 31818\text{MHz}$ )にして、PAL方式では、水平周波数の908倍( $908fH = 908 \times 15.625\text{kHz} = 14.1875\text{MHz}$ )にする。

40

#### 【0087】

これにより、TV信号処理のクロックに依存せずに、システムクロック(DRAMクロック)を決定することができ、システムのパフォーマンスを比較的自由に高速化することが可能である。

#### 【0088】

以下、FIFOメモリ8へのデータの書き込みは、信号の垂直プランギング期間にあり、また、FIFOメモリ8からのデータの読み出しは、映像期間内にある場合を例に挙げて説明する。

#### 【0089】

##### (システム動作)

50

次に、本システムの動作について説明する。

**【0090】**

C C D センサ 1 によって受光された映像信号は、A / D 変換器 2 でデジタル映像信号に変換され、撮像系の信号処理回路 3 で YUV 形式、ここでは YUV = 422 形式の映像信号に処理される。

**【0091】**

この処理された映像信号は、DRAM I / F 回路 4 内の 411 変換回路によって YUV = 411 形式に変換され、DRAM 5 上の自然画用の VRAM へ書き込まれる。

**【0092】**

撮像系の信号処理回路 3 の輝度信号 Y 出力は、色キャリア除去やアパチャーボード補正やガンマ変換等の処理をして生成される。色差信号 U (B - Y) と色差信号 V (R - Y) は、色補間やマトリクス変換やガンマ変換等の処理を施して生成される。10

**【0093】**

撮像系信号処理 3 の Y, U, V の出力は、図 2 (b) の 22 に示す YUV = 422 形式に示したように画面左上から順に

(上位データ) Y<sub>0</sub>Y<sub>1</sub>Y<sub>2</sub>Y<sub>3</sub>Y<sub>4</sub>Y<sub>5</sub>Y<sub>6</sub>Y<sub>7</sub>...

(下位データ) U<sub>0</sub>V<sub>0</sub>U<sub>1</sub>V<sub>1</sub>U<sub>2</sub>V<sub>2</sub>U<sub>3</sub>V<sub>3</sub>U<sub>4</sub>V<sub>4</sub>U<sub>5</sub>V<sub>5</sub>U<sub>6</sub>V<sub>6</sub>...

と、DRAM I / F 回路 4 へ送られる。

**【0094】**

そして、DRAM I / F 回路 4 内の 411 変換回路にて

図 2 (c) の 23 に示す YUV = 411 形式に変換されて20

(上位データ) Y<sub>0</sub>Y<sub>1</sub>Y<sub>3</sub>Y<sub>4</sub>Y<sub>5</sub>Y<sub>7</sub>...

(下位データ) U<sub>0</sub>V<sub>0</sub>Y<sub>2</sub>V<sub>4</sub>U<sub>4</sub>Y<sub>6</sub>...

となり、DRAM 5 上の自然画用の VRAM 領域に書き込まれる。

**【0095】**

**(自然画の表示)**

ここで、TV モニタ 30 へ自然画のみを表示する場合の PB\_DMAC6 と DRAM I / F 4 のハンドシェイクについて説明する。

**【0096】**

(垂直プランギング期間での FIFO メモリへのデータ書き込み)

まず、SSG 14 で発生する同期タイミングが垂直プランギング中には、垂直同期 (VSYNC) 時に FIFO メモリ 8 が空になり、DRAM I / F 4 へのリクエスト信号である PB\_REQ\_L と、PB\_REQ\_H との両方をアクティブにする。30

**【0097】**

そして、この要求により DRAM I / F 4 では、PB\_DMAC6 で指示されたアドレス (自然画 VRAM 領域) のデータを読み出し VALID フラグと一緒に FIFO メモリ 8 へ送る。

**【0098】**

そして同時に、PB\_DMAC6 へは、アドレスを認識した合図として ACK 信号をアクティブにする。PB\_DMAC6 では、ACK 信号がアクティブになったのを検知して、次に読み出すべきデータのアドレスを計算し、DRAM I / F 4 へ与える。40

**【0099】**

そして、この垂直プランギング中には、FIFO メモリ 8 からデータが読み出されないので、次第に FIFO メモリ 8 にデータが充満し、前述のリクエスト信号の PB\_REQ\_L と、PB\_REQ\_H とは、インアクティブ状態になる。

**【0100】**

ここで、PB\_REQ\_L と、PB\_REQ\_H との 2 つのフラグ信号動作について説明する。

**【0101】**

FIFO メモリ 8 が空になると、PB\_REQ\_L と、PB\_REQ\_H との両方がアク

50

ティプになり、FIFOメモリ8に約1～2割ほどデータが溜まると、PB REQ Hのみインアクティブで、PB REQ Lはアクティブのままになり、FIFOメモリ8に約8割以上データが溜まると、PB REQ LとPB REQ Hとの両方がインアクティブになる。

#### 【0102】

(映像期間でのFIFOメモリからのデータ読出し)

続いて、SSG14で発生する同期タイミングが垂直プランギングを抜けて映像期間に入ると、FIFOメモリ8からデータが読み出されていく。

#### 【0103】

そして、FIFOメモリ8のデータ量がFIFOメモリ容量の約8割を下回ると、前述したように、PB REQ Lがアクティブになる。 10

#### 【0104】

このリクエストPB REQ Lに対して、DRAMI/F4がすぐに応答してVRAMデータをFIFOメモリ8へ送る場合は、PB REQ Hはインアクティブのままで、次第にFIFOメモリ8にデータが満たされて、PB REQ Lがインアクティブになる。

#### 【0105】

もし、PB REQ Lのリクエストに対して、DRAMI/F4がすぐに応答できない場合には、FIFOメモリ8のデータ残量が少なくなつてき、残り約2割を下回った時点でPB REQ Hがアクティブになる。DRAMI/F4内では、PB REQ Hは、プライオリティの高い要求として処理され、即時にVRAMデータをFIFOメモリ8へ送ることになる。 20

#### 【0106】

そして、次第にFIFOメモリ8にデータが溜まり、約2割以上になると、PB REQ Hはインアクティブになり、さらに、FIFOメモリ8へのデータ書き込みが続くなら、約8割を超えた時点でPB REQ Lもインアクティブになる。

#### 【0107】

前述したPB REQ HがインアクティブになったところでFIFOメモリ8へのデータ書き込みが途絶えてしまうと、やがて約2割を下回った時点で、再びPB REQ Hがアクティブになる。 30

#### 【0108】

最悪にも、PB REQ Hがアクティブになっても、VRAMデータが送られてこない場合には、やがてFIFOメモリ8が空になり、FIFOメモリ8から読出すデータが無くなり、TVモニタ30上の表示も異常になる。

#### 【0109】

従って、PB REQ Hのプライオリティを十分に高く設定し、このようなことが絶対に起きないようにしておく必要がある。

#### 【0110】

また、本例を同期回路設計する場合は、前述のACK信号の検出は回路に供給されたクロックエッジで行うようにする。すなわち、データの送受を連続的(バースト的)に行う場合、フラグ信号はアクティブになり続けて(アクティブハイなら "H" のまま)クロックエッジのタイミングで連続的にデータを取り込む。 40

従って、ACK信号がアクティブ状態のときには1クロック毎にアドレス計算をして、DRAMI/F4へ与えることになる。

#### 【0111】

ACK信号と同様に、VALID信号やPB REQ L信号やPB REQ H信号等のフラグ信号も、連続的にアクティブになり、クロックエッジのタイミングで連続的にデータを取り込む場合がある。当然のことながら、単発時には、1クロック幅のフラグ信号になる。

#### 【0112】

上述したように、SSG14で発生する同期タイミングが映像期間中には、 FIFOメモリ8からYUV=再生411形式でデータが読み出され、後段のコンバータ10(422)に送られる。

#### 【0113】

このコンバータ10では、前述したようにYUV=再生411形式の信号をYUV=422形式に変換し、後段のスーパーインポーズ回路12に送られる。

#### 【0114】

自然画のみを表示する場合、スーパーインポーズ回路12は、前述したようにスーパーインポーズしない方にセレクタを切り替えることになる。

#### 【0115】

そして後段の再生信号処理13へ送られる。再生信号処理13では、前述のようにクロマエンコード処理や帯域補正やコンポジット化等のTV表示用のデジタル信号に処理して、後段のD/A変換器15へ出力し、ここでアナログTV信号に変換する。

#### 【0116】

(自然画/BMP画の表示)

次に、TVモニタ30へ自然画とBMP画をスーパーインポーズして表示する場合について説明する。

#### 【0117】

基本的構成は、自然画VRAM時のデータのハンドシェイクと同様であり、垂直同期(VSYNC)時にBMP用のFIFOメモリ8が空になり、DRAMI/F4へのリクエスト信号であるBMP\_REQ\_Lと、BMP\_REQ\_Hとの両方をアクティブにする。

#### 【0118】

そして、DRAMI/F4では、BMP\_DMAC7が示すDRAM5上のBMPのアドレスからデータを読み出し、BMPデータ用のVALIDフラグと一緒にFIFOメモリ8へ送る。

#### 【0119】

そして同時に、BMP\_DMAC回路7へは、アドレスを認識した合図としてBMP\_ACK信号をアクティブにする。BMP\_DMAC7では、ACK信号がアクティブになつたのを検知して、次に読み出すべきデータのアドレスを計算して出力する。

#### 【0120】

さらに、BMP\_REQ\_Lと、BMP\_REQ\_Hとの2つのフラグ信号動作についても、PB\_REQ信号と同様になる。すなわち、FIFOメモリ8が空になると、BMP\_REQ\_Lと、BMP\_REQ\_Hとの両方がアクティブになり、FIFOメモリ8に1~2割ほどデータが溜まると、BMP\_REQ\_Hのみインアクティブで、BMP\_REQ\_Lはアクティブのままになり、FIFOメモリ8に8割以上データが溜まると、BMP\_REQ\_Lと、BMP\_REQ\_Hとの両方がインアクティブになる。

#### 【0121】

自然画PBとBMP画とでは、TVや液晶上での表示領域が異なり、本例でのBMP画の表示領域は、水平640×垂直480で、自然画のVRAMより一回り小さい。そのため、BMP画のデータの読み出しタイミングも自然画のVRAMデータの読み出しタイミングの内側に位置し、転送に必要なFIFOメモリ容量も自然画より少ない。

#### 【0122】

しかし、回路動作は、自然画のデータ時と同じであり、そのBMP画の読み出しタイミングになると、FIFOメモリ8からBMP画のデータが読み出されていき、FIFOメモリ8内のBMP画の残データ量がBMP FIFOメモリ容量の8割を下回ると、前述したように、BMP\_REQ\_Lがアクティブになる。

#### 【0123】

このリクエストに対して、DRAMI/F4がすぐに応答してBMPデータをFIFOメモリ8へ送る場合は、BMP\_REQ\_Hはインアクティブのままでも、次第にFIFOメモリ8にデータが満たされて、BMP\_REQ\_Lがインアクティブになっていく。

10

20

30

40

50

**【 0 1 2 4 】**

もし、B M P \_ R E Q \_ L のリクエストに対して、D R A M I / F 4 がすぐに応答できない場合には、F I F O メモリ 8 のデータ残量が少なくなつていき、2 割を下回った時点で B M P \_ R E Q \_ H がアクティブになる。D R A M I / F 4 内では、B M P \_ R E Q \_ H は、プライオリティの高い要求として処理され、即時に B M P データを F I F O メモリ 8 へ送ることになる。

**【 0 1 2 5 】**

そして、次第に F I F O メモリ 8 にデータが溜まり、2 割以上になると、B M P \_ R E Q \_ H は、インアクティブになり、さらに、F I F O メモリ 8 へのデータ書き込みが続くなら、約 8 割を超えた時点で、B M P \_ R E Q \_ L もインアクティブになる。前述した B M P \_ R E Q \_ H がインアクティブになったところで、F I F O メモリ 8 へのデータ書き込みが途絶えてしまうと、やがて約 2 割を下回った時点で再び、B M P \_ R E Q \_ H がアクティブになる。

10

**【 0 1 2 6 】**

F I F O メモリ 8 から読出された B M P データは、前述したパレット変換回路 1 1 に送られ、パレットデータに変換される。

**【 0 1 2 7 】**

パレット変換回路 1 1 のパレットデータ出力は、スーパーインポーズ回路 1 2 に送られ、自然画用の P B データとスーパーインポーズされる。そのスーパーインポーズ回路 1 2 の出力は、前述のように、後段の再生信号処理回路 1 3 へ送られる。

20

**【 0 1 2 8 】**

再生信号処理回路 1 3 で、クロマエンコード処理や帯域補正やコンポジット化等の T V 表示用のデジタル信号に処理がなされ、後段の D / A 変換器 1 5 へ出力し、アナログ T V 信号に変換される。

**【 0 1 2 9 】**

なお、前述した例は、デジタルカメラ等の撮像装置に適用できるが、この他に、複数の機器（例えば、ホストコンピュータ、インターフェース機器、リーダ、プリンタなど）から構成されるシステムに適用しても、1 つの機器（例えば、P D A（個人情報管理）機器のような小型の画像処理機器、複写機、ファクシミリ装置）からなる装置に適用してもよい。

30

**【 0 1 3 0 】**

また、本発明は、システム或いは装置にプログラムを供給することによって達成される場合にも適用できることはいうまでもない。そして、本発明を達成するためのソフトウェアによって表されるプログラムを格納した記憶媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ（又は C P U や M P U ）が記憶媒体に格納されたプログラムコードを読み出し実行することによっても、本発明の効果を享受することが可能となる。

**【 0 1 3 1 】**

この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。

40

**【 0 1 3 2 】**

プログラムコードを供給するための記憶媒体としては、例えば、フロッピディスク、ハードディスク、光ディスク、光磁気ディスク、C D - R O M 、C D - R 、磁気テープ、不揮発性のメモリカード（I C メモリカード）、R O M （マスク R O M 、フラッシュ E E P R O M など）などを用いることができる。

**【 0 1 3 3 】**

また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼動している O S （オペレーティングシステム）などが実際の処理の一部または全部

50

を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

#### 【0134】

さらに、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

#### 【0135】

##### 【発明の効果】

10

以上述べたように、本発明によれば、FIFOメモリのデータ書込みレートとデータ読出しレートとを異なる構成し、FIFOメモリへの書込み周期に対して非同期に読み出すようにしたので、従来のように、DRAMをアクセスするためのシステムクロックが表示系の信号処理クロックの整数倍に制約されることはなくなり、システムのパフォーマンスを柔軟に向上させることができる。

#### 【0136】

また、本発明によれば、TVや液晶表示のためのビデオメモリ(VRAM)をDRAM上に構成できるので、ASIC化においてIC内のバッファが少なくて済み、従来に比べて大幅な回路規模の削減を図ることができる。

#### 【0137】

20

さらに、本発明によれば、インターフェイス回路とFIFOメモリとのデータハンドシェイクにおいて、FIFOメモリからのリクエスト信号に互いに異なる複数種類の要求レベルを含ませるようにしたので、TVや液晶への画像表示に支障をきたさない限界まで、画像表示以外のDRAMアクセス要求に対する応答を高めることができ、これにより、システム全体のDRAMのデータ転送効率を一段と向上することができる。

##### 【図面の簡単な説明】

【図1】本発明の実施の形態である映像信号処理装置におけるシステム全体の構成を示すブロック図である。

【図2】処理される画像データ形式を比較して示す説明図である。

【図3】メモリ領域からのデータ読出しをイメージ化して示す説明図である。

30

【図4】従来の映像信号処理装置の構成を示すブロック図である。

##### 【符号の説明】

- 1 C C D センサ

- 2 A / D 変換器

- 3 撮像系の信号処理回路

- 4 D R A M I / F

- 5 D R A M

- 6 P B \_ D M A C

- 7 B M P \_ D M A C

- 8 F I F O メモリ

- 9 S R A M

- 10 コンバータ

- 11 パレット変換回路

- 12 スーパーインポーズ回路

- 13 再生信号処理回路

- 14 同期信号発生器

- 15 D / A 変換器

40

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 特開平08-314418(JP,A)

特開平11-008827(JP,A)

国際公開第96/041256(WO,A1)

特開平10-063469(JP,A)

特開2000-105587(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G5/00-5/42