(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4832807号

(P4832807)

(45) 発行日 平成23年12月7日(2011.12.7)

(24) 登録日 平成23年9月30日(2011.9.30)

(51) Int.Cl.

H01L 21/768 (2006.01)

F 1

H01L 21/90

A

請求項の数 10 (全 20 頁)

(21) 出願番号 特願2005-165252 (P2005-165252)

(22) 出願日 平成17年6月6日 (2005.6.6)

(65) 公開番号 特開2006-24905 (P2006-24905A)

(43) 公開日 平成18年1月26日 (2006.1.26)

審査請求日 平成20年5月12日 (2008.5.12)

(31) 優先権主張番号 特願2004-172500 (P2004-172500)

(32) 優先日 平成16年6月10日 (2004.6.10)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に形成され、第一層間絶縁膜と上記第一層間絶縁膜内に第一銅配線とを有する第一層と、

上記第一層上に形成され、上記第一銅配線の上面に接するように形成される第一絶縁膜と、

上記第一絶縁膜上に形成された第二層間絶縁膜と、

上記第一銅配線の上方において上記第一絶縁膜を貫通するように上記第二層間絶縁膜及び上記第一絶縁膜に設けられた第一ホールと、

上記第一ホールの側壁に沿って上記第二層間絶縁膜上及び上記第一絶縁膜上に形成された第一バリアメタルと、

上記第一ホールの下側に上記第一ホールと連通するように上記第一銅配線に設けられ、

上記第一ホールの口径よりも大きな口径を有する第二ホールと、

上記第二ホールの下側に上記第二ホールと連通するように上記第一銅配線に設けられた、円錐形状又は半球形状の第三ホールと、

上記第二ホールの内壁面に形成された所定の導電膜と、

上記第一バリアメタル上、上記第二ホール内の上記所定の導電膜上及び上記第三ホールの内壁面に形成された第二バリアメタルと、

上記第一、第二及び第三ホール内に埋め込まれた第一銅金属とを有することを特徴とする半導体装置。

10

20

**【請求項 2】**

半導体基板上に形成され、第一層間絶縁膜と上記第一層間絶縁膜内に第一銅配線とを有する第一層と、

上記第一層上に形成され、上記第一銅配線の上面に接するように形成される第一絶縁膜と、

上記第一絶縁膜上に形成された第二層間絶縁膜と、

上記第一銅配線の上方において上記第一絶縁膜を貫通するように上記第二層間絶縁膜及び上記第一絶縁膜に設けられた第一ホールと、

上記第一ホールの側壁に沿って上記第二層間絶縁膜上及び上記第一絶縁膜上に形成された第一バリアメタルと、

上記第一ホールの下側に上記第一ホールと連通するように上記第一銅配線に設けられ、上記第一ホールの口径よりも大きな口径を有する第二ホールと、

上記第二ホールの下側に上記第二ホールと連通するように上記第一銅配線に設けられ、上記第一銅配線を 30 nm 以上掘り込むことで形成された第三ホールと、

上記第二ホールの内壁面に形成された所定の導電膜と、

上記第一バリアメタル上、上記第二ホール内の上記所定の導電膜上及び上記第三ホールの内壁面に形成された第二バリアメタルと、

上記第一、第二及び第三ホール内に埋め込まれた第一銅金属とを有することを特徴とする半導体装置。

**【請求項 3】**

半導体基板上に形成され、第一層間絶縁膜と上記第一層間絶縁膜内に第一銅配線とを有する第一層と、

上記第一層上に形成され、上記第一銅配線の上面に接するように形成される第一絶縁膜と、

上記第一絶縁膜上に形成された第二層間絶縁膜と、

上記第一銅配線の上方において上記第一絶縁膜を貫通するように上記第二層間絶縁膜及び上記第一絶縁膜に設けられた第一ホールと、

上記第一ホールの側壁に沿って上記第二層間絶縁膜上及び上記第一絶縁膜上に形成された第一バリアメタルと、

上記第一ホールの下側に上記第一ホールと連通するように上記第一銅配線に設けられ、上記第一ホールの口径よりも大きな口径を有する第二ホールと、

上記第二ホールの下側に上記第二ホールと連通するように上記第一銅配線に設けられ、上記第一ホールの口径よりも小さな口径を有する第三ホールと、

上記第二ホールの内壁面に形成された所定の導電膜と、

上記第一バリアメタル上、上記第二ホール内の上記所定の導電膜上及び上記第三ホールの内壁面に形成された第二バリアメタルと、

上記第一、第二及び第三ホール内に埋め込まれた第一銅金属とを有することを特徴とする半導体装置。

**【請求項 4】**

上記第二層間絶縁膜内に設けられた第一溝内に形成された第二銅配線を更に有し、

上記第一溝の底面及び側面の上記第二層間絶縁膜上に形成された第三バリアメタルと、上記第一溝内の第二銅金属により上記第二銅配線が形成され、

上記第一バリアメタル、上記第二バリアメタル及び上記第一銅金属により第一ビアが形成され、

上記第三バリアメタルと上記第二バリアメタルは同一工程で形成され、

上記第一銅金属及び上記第二銅金属は同一工程で形成されることを特徴とする請求項 1 ~ 3 のいずれか一項に記載の半導体装置。

**【請求項 5】**

上記第一バリアメタルと上記第二バリアメタルとの間に、上記第一バリアメタルの材料と上記第一銅配線の材料との合金で構成された上記所定の導電膜を更に有することを特徴

10

20

30

40

50

とする請求項 4 に記載の半導体装置。

**【請求項 6】**

上記第一層間絶縁膜及び上記第二層間絶縁膜はそれぞれ、TEOS、SiO<sub>2</sub>、SiOCから選択された一つの材料を含有し、

上記第一バリアメタル、上記第二バリアメタルおよび上記第三バリアメタルはそれぞれ、タンタル、タンタル窒化物、タンタル珪化物、タンタル炭化物、チタン窒化物、チタン珪化物、チタン炭化物、タングステン窒化物、タングステン珪化物、タングステン炭化物、ルテニウム、およびルテニウム酸化物よりなる群から選ばれる 1 種以上の膜より形成されていることを特徴とする請求項 4 に記載の半導体装置。

**【請求項 7】**

上記第一銅金属と上記第二銅金属はそれぞれ、シード層と上記シード層上に形成された銅層により構成されていることを特徴とする請求項 4 に記載の半導体装置。

**【請求項 8】**

上記第二銅配線上及び上記第二層間絶縁膜上に第二層がさらに形成されており、上記第二層は、

上記第二銅配線上及び上記第二層間絶縁膜上に形成された第二絶縁膜と、

上記第二絶縁膜上に形成された第三層間絶縁膜と、

上記第二絶縁膜と上記第三層間絶縁膜を貫通するように設けられ、上記第二銅配線を露出するように設けられた第四ホールと、

上記第三層間絶縁膜内に形成され、上記第四ホールと連通する第二溝と、

上記第二溝の側面、上記第二溝の底面、上記第四ホールの側面及び上記第四ホールの底面に形成された第四バリアメタルと、

上記第四バリアメタル上に形成された第三銅金属とを有し、

上記第四ホール内の上記第四バリアメタルと上記第三銅金属により第二ビアが形成され、上記第二溝内の上記第四バリアメタルと上記第三銅金属により第三銅配線が形成され、上記第四ホールの底面の上記第四バリアメタルは露出した上記第二銅配線と接触しており、

上記第四ホールの底面の上記第四バリアメタルは、上記第二絶縁膜と第二銅配線との接觸面よりも高い位置に存在することを特徴とする請求項 4 に記載の半導体装置。

**【請求項 9】**

上記第四ホールの径よりも上記第一ホールの径の方が小さいことを特徴とする請求項 8 記載の半導体装置。

**【請求項 10】**

上記第一絶縁膜は SiCN、SiC 又は SiCO のうちのいずれかを材料とすることを特徴とする請求項 4 記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置に関し、より特定的には、信頼性の高い半導体装置に関する。

**【背景技術】**

**【0002】**

LSI (Large Scale Integrated circuit) の微細化、高速化に伴ない、LSI の配線材料として従来用いられていたアルミニウムに代わり、電気抵抗の低い Cu (銅) が用いられようとしている。LSI の配線材料として Cu を用いることにより、電気抵抗を低く抑えながら配線を微細化することができ、また、LSI の動作速度を向上することができる。しかしながら、Cu は絶縁膜中に拡散しやすい性質を有している。Cu が絶縁膜中に拡散すれば配線の信頼性が低くなってしまう。また、Cu はプラズマイオンとの反応速度が非常に遅いという性質を有している。このため、エッティングにより配線を形成しようとすると十分な生産性が得られない。

**【0003】**

10

20

30

40

50

そこで、これらの問題を解決することができるCu配線の形成方法として、近年、ダマシン法が採用されている。通常のダマシン法を用いた場合、Cu配線は以下のように形成される。

#### 【0004】

まず、Cuよりなる下部配線を覆うように、ライナー膜と、層間絶縁層と、反射防止膜とを積層して形成する。次に、ビアホールを形成するためのレジストを反射防止膜上に形成し、通常の写真製版技術およびエッチング技術により、層間絶縁膜にビアホールを形成する。これにより、ビアホールの底面にはライナー膜が露出する。次に、ビアホールを形成するためのレジストを除去した後、トレンチを形成するためのレジストを反射防止膜上およびビアホール内に形成し、通常の写真製版技術およびエッチング技術により、層間絶縁膜にトレンチを形成する。次に、トレンチを形成するためのレジストおよび反射防止膜を除去した後、ビアホールの底面に露出したライナー膜をエッチングする。これにより、下部配線を露出させる。次に、ビアホールの底面に露出した下部配線表面のCu酸化膜や、ライナー膜のエッティングの際に発生した残渣(ポリマー)などを除去するために、Ar(アルゴン)スパッタエッティングや、H<sub>2</sub>(水素)雰囲気中でのアニールや、プラズマ処理や、ウエットエッティングなどを行なう。次に、ビアホールおよびトレンチの側壁および底面と、層間絶縁層上とにバリアメタルを形成する。次に、メッキのシールド膜となるCu薄膜をバリアメタル上に形成し、ビアホールおよびトレンチの側壁および底面と、層間絶縁層上とに、メッキ法によりCu膜を形成する。その後、層間絶縁層の上部の余分なCu膜およびバリアメタルをCMP(Chemical Mechanical Polish)により除去し、Cu配線が完成する。10

#### 【0005】

上記製造方法によって得られたCu配線には、ボイドの発生により断線が起こりやすいという問題があった。すなわち、熱処理や実際の使用環境の中で高温にされた場合に、層間絶縁層とCu配線との間には熱応力が発生する。従来のCu配線において、下部配線の表面とビアホールの側壁とは直角に接しているため、下部配線の表面とCu配線の底部との接触部分にこの熱応力が集中しやすい。20

#### 【0006】

また、ビアホール内のCu配線を流れる電流は、下部配線の表面とCu配線の底部との接触部分を通過して、ビアホールよりも断面積の大きな下部配線へ流れるので、下部配線の表面とCu配線の底部との接触部分には電流が集中しやすい。30

#### 【0007】

このように、下部配線の表面とCu配線の底部との接触部分には熱応力および電流が集中しやすいので、ボイドの発生起点となっていた。従来のCu配線において、下部配線とCu配線とは平面的に接觸しているため、Cu配線と下部配線との接觸部分の面積が十分ではなく、ボイドの発生により断線が起こりやすいという問題があった。また、Cu配線と下部配線との間の電気抵抗が大きいという問題があった。

#### 【0008】

そこで、Cu配線と下部配線との接觸部分の面積を増加することのできる配線の製造方法が、たとえば特開2002-64138号公報(特許文献1)に開示されている。特許文献1においては、配線は以下のように製造される。40

#### 【0009】

Cuよりなる第1層配線上に銅拡散防止用絶縁膜を形成した後、層間絶縁膜を形成する。次に、層間絶縁膜上にレジスト膜を形成し、これをマスクとして第1層配線の表面が露出するまで層間絶縁膜および銅拡散防止用絶縁膜を異方的にエッチングする。さらに、このエッチングにより露出した第1層配線の表面をエッチングすることにより、その底部が第1層配線の表面より深い位置に達するコンタクトホールを形成する。次に、コンタクトホール内を含む層間絶縁膜上にバリア層を形成する。次に、バリア層の上にTa(タンタル)膜が形成される。続いて、コンタクトホール外のTa膜およびバリア層をCMPにより除去し、プラグが第1層配線上形成される。50

## 【0010】

特許文献1に開示された配線の製造方法では、層間絶縁膜および第1層配線をエッチングして孔を形成し、その孔内にプラグを形成している。このため、プラグの底面およびプラグの側面の一部が第1層配線と接触している。すなわち、プラグと第1層配線とが立体的に接触しているため、プラグと第1層配線との接触部分の面積を増大することができる。

## 【0011】

なお、層間絶縁層および下層配線をエッチングして孔を形成し、その孔内に導電層を形成する技術は、特許文献1の他、たとえば特開2001-77195号公報（特許文献2）、特開2000-114261号公報（特許文献3）、特開平7-14836号公報（特許文献4）、特開2000-133711号公報（特許文献5）に開示されている。

10

【特許文献1】特開2002-64138号公報

【特許文献2】特開2001-77195号公報

【特許文献3】特開2000-114261号公報

【特許文献4】特開平7-14836号公報

【特許文献5】特開2000-133711号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0012】

上記特許文献1に開示された技術では、孔内に残留しているレジストおよび銅拡散防止用絶縁膜の残渣（ポリマー）を除去するために、層間絶縁膜および第1層配線をエッチングした後に孔内を洗浄する必要がある。しかしながら、孔内を洗浄する際に用いられる溶液はCuを溶解する性質を有しているので、洗浄の際に第1層配線がウェットエッチングされる。その結果、層間絶縁膜における孔の口径に比べて第1層配線における孔の口径が大きくなる。言い換えれば、第1層配線における孔の内壁に凹部が形成される。この凹部にはバリア層およびTa膜が形成されにくい（途切れやすい）。このため、凹部がボイド発生の起点となり、電気抵抗の増加や断線などが起こりやすくなる。その結果、半導体装置の信頼性が低下するという問題があった。

20

## 【0013】

したがって、本発明の目的は、信頼性の高い半導体装置を提供することである。

30

## 【課題を解決するための手段】

## 【0014】

本発明の一実施例の半導体装置は、第一層と、第一絶縁膜と、第二層間絶縁膜と、第一ホールと、第一バリアメタルと、第二ホールと、第三ホールと、所定の導電膜と、第二バリアメタルと、第一銅金属とを有している。第一層は、半導体基板上に形成され、第一層間絶縁膜と第一層間絶縁膜内に第一銅配線とを有している。第一絶縁膜は、第一層上に形成され、第一銅配線の上面に接するように形成されている。第二層間絶縁膜は、第一絶縁膜上に形成されている。第一ホールは、第一銅配線の上方において第一絶縁膜を貫通するように上記第二層間絶縁膜及び上記第一絶縁膜に設けられている。第一バリアメタルは、第一ホールの側壁に沿って第二層間絶縁膜上及び第一絶縁膜上に形成されている。第二ホールは、第一ホールの下側に第一ホールと連通するように第一銅配線に設けられ、第一ホールの口径よりも大きな口径を有する。第三ホールは、第二ホールの下側に第二ホールと連通するように第一銅配線に設けられた、円錐形状又は半球形状のものである。所定の導電膜は、上記第二ホールの内壁面に形成されている。第二バリアメタルは、第一バリアメタル上、第二ホール内の所定の導電膜上及び第三ホールの内壁面に形成されている。第一銅金属は、第一、第二及び第三ホール内に埋め込まれている。

40

## 【発明の効果】

## 【0015】

本発明の半導体装置によれば、第二ホールの口径が第一ホールの口径よりも大きい場合にも第二ホールの内壁面全面に所定の導電膜を形成することができるので、第二ホール内

50

にボイドが形成しにくくなり、半導体装置の信頼性が高くなる。

**【発明を実施するための最良の形態】**

**【0016】**

以下、本発明の実施の形態について、図に基づいて説明する。

**(実施の形態1)**

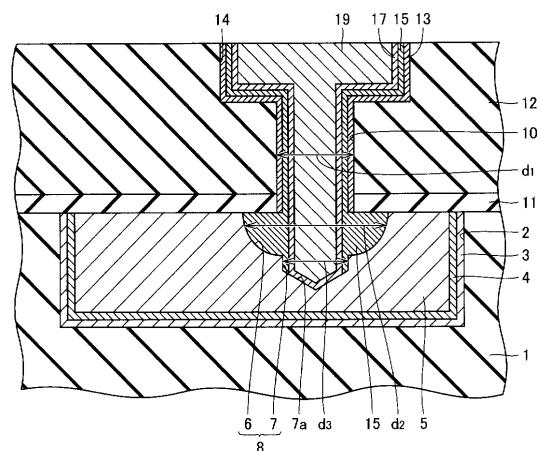

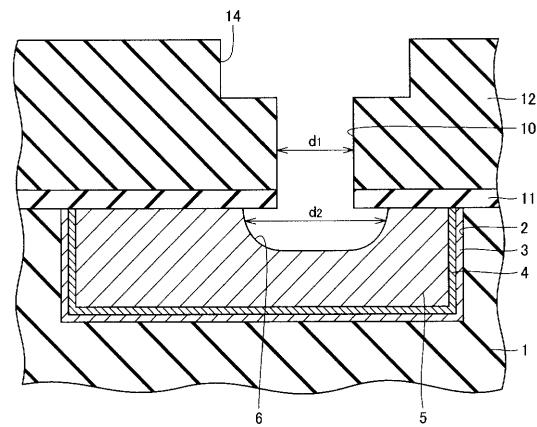

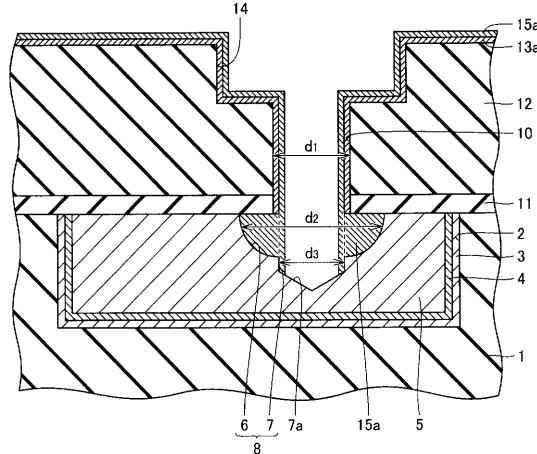

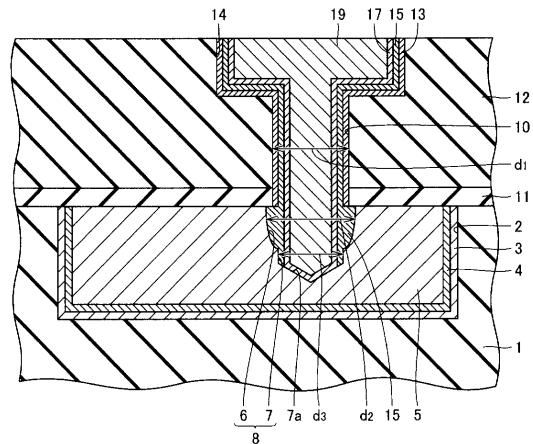

図1は、本発明の実施の形態1における半導体装置の構造を示す断面図である。

**【0017】**

図1に示すように、本実施の形態の半導体装置は、第1絶縁膜としての層間絶縁膜1と、配線としての下部配線5と、第2絶縁膜としてのライナー膜11と、第3絶縁膜としての層間絶縁膜12とを主に備えている。層間絶縁膜1には溝2が形成されており、溝2の内壁面および底面に沿うようにバリアメタル3および4が積層して形成されている。そして、溝2内を埋めるようにバリアメタル4上に下部配線5が形成されている。下部配線5を覆うように層間絶縁膜1上にライナー膜11および層間絶縁膜12が積層して形成されている。ライナー膜11は、下部配線5に含まれているCuが層間絶縁膜12内に拡散するのを防止する役割を果たしている。また、後述する上部孔10形成の際のエッティングストップとしての役割を果たしている。10

**【0018】**

層間絶縁膜12にはトレンチ14が形成されている。また、層間絶縁膜12のトレンチ14内およびライナー膜11には、上部孔10が開口している。また、下部配線5には下部孔8が開口している。上部孔10と下部孔8とは互いに繋がっている。下部孔8は孔6と堀込み部分7とを有している。孔6は半円の断面形状を有している。上部孔10と下部孔8との境界部分付近の孔6の口径d<sub>2</sub>、言い換えれば、ライナー膜11と下部配線5との境界部分付近の孔6の口径d<sub>2</sub>は、上部孔10の口径d<sub>1</sub>よりも大きくなっている。孔6の底部には掘込み部分7が形成されている。堀込み部分7は下部孔8の一部である。掘込み部分7の口径d<sub>3</sub>は、孔6の口径d<sub>2</sub>および上部孔10の口径d<sub>1</sub>よりも小さい。堀込み部分7の底部7aは、たとえば円錐や半球の形状となっている。20

**【0019】**

また、本実施の形態の半導体装置は、下部孔8の内壁面全面に形成された下部導電膜としての導電膜15と、上部孔10の内壁面に沿って形成された上部導電膜としてのバリアメタル13と、上部孔10内および下部孔8内を埋めるように形成されたCu膜19と、バリアメタル17とをさらに備えている。30

**【0020】**

トレンチ14の内壁面および上部孔10の内壁面に沿って、バリアメタル13が形成されている。バリアメタル13は、上部孔10と下部孔8との境界部分において途切れている。下部孔8内には、下部孔8の内壁面全面を覆うように導電膜15が形成されている。導電膜15は堀込み部分7の底部7aには形成されていない。導電膜15は、バリアメタル13および下部配線5と同じ物質を含んでいる。なお、図1においては、導電膜15はトレンチ14および上部孔10内のバリアメタル13上にまで形成されているが、導電膜15は、少なくとも下部孔8の内壁面全面に形成されなければよい。トレンチ14、上部孔10、および下部孔8内の導電膜15上には、バリアメタル17が形成されており、トレンチ14、上部孔10、および下部孔8内を埋めるようにバリアメタル17上にCu膜19が形成されている。なお、本発明の半導体装置では、上部孔10の内壁面に形成された層A(図1におけるバリアメタル13、導電膜15、およびバリアメタル17)と、掘込み部分7の内壁面に形成された層B(図1における導電膜15およびバリアメタル17)と、掘込み部分7の底部7aに形成された層(図1におけるバリアメタル17)との各々の膜厚あるいは層数にA B Cの関係がある。40

**【0021】**

なお、ライナー膜11は、たとえばSiCN、SiCO、またはSiCなどよりなっている。層間絶縁膜12は、たとえばTEOS(Tetra Ethyl Ortho Silicate)、SiO<sub>2</sub>、またはSiOCなどよりなっている。バリアメタル3はたとえばTaNよりなっており50

、バリアメタル4および17はたとえばTaよりなっている。下部配線5はたとえばCuよりなっている。さらに、バリアメタル13は、たとえばTa(タンタル)窒化物、Ta珪化物、Ta炭化物、Ti(チタン)窒化物、Ti珪化物、Ti炭化物、W(タングステン)窒化物、W珪化物、W炭化物、Ru(ルテニウム)、およびRu酸化物よりなる群から選ばれる1種以上の膜よりなっている。

#### 【0022】

本実施の形態の半導体装置では、下部配線5をエッティングして下部孔8を形成し、Cu膜19、バリアメタル17、および導電膜15等の導電膜を下部孔8内に形成している。このため、下部孔8内に形成された導電膜の底面および側面の一部が下部配線5と接觸している。すなわち、下部孔8内に形成された導電膜と下部配線5とが立体的に接觸しているため、下部孔8内に形成された導電膜と下部配線5との接觸部分の面積を増大することができる。これにより、下部配線5の表面と下部孔8内に形成された導電膜の底部との接觸部分へ熱応力および電流が集中するのを緩和することができる。その結果、ボイドが発生しにくくなり、断線が起こりにくくなる。また、Cu膜19と下部配線5と間の電気抵抗を低減することができる。

#### 【0023】

次に、本実施の形態における半導体装置の製造方法について説明する。

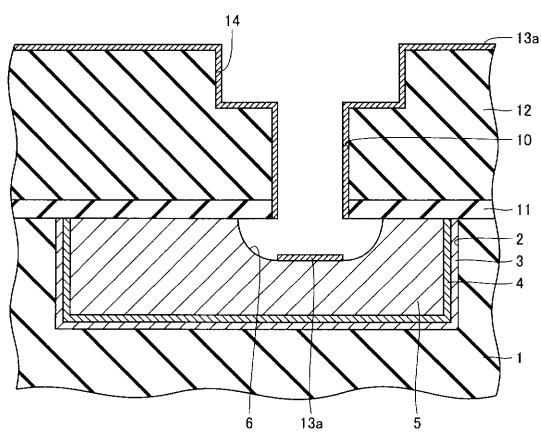

図2～図10は、本発明の実施の形態1における半導体装置の製造方法を工程順に示す断面図である。

#### 【0024】

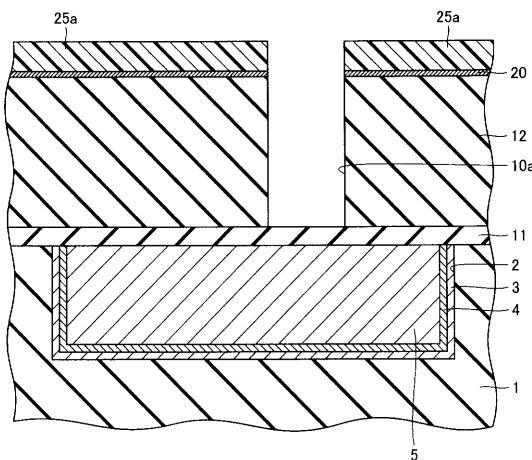

図2を参照して、層間絶縁膜1内に溝2を形成する。次に、層間絶縁膜1上と、溝2の内壁面および底面とに、たとえばCVD(Chemical Vapor Deposition)法やスパッタ法などによりバリアメタル3および4を積層して形成する。次に、溝2内を埋め、層間絶縁膜1を覆うように、たとえばCVD法やメッキ法などにより下部配線5となる導電膜を形成する。次に、CMP(Chemical Mechanical Polish)法により、層間絶縁膜1上の余分なバリアメタル3および4と、余分な導電膜とを除去する。これにより、下部配線5が層間絶縁膜1の内部に形成される。次に、下部配線5を覆うように層間絶縁膜1上にライナー膜11を形成する。

#### 【0025】

図3を参照して、ライナー膜11上に層間絶縁膜12および反射防止膜(ARL:Anti-reflective layer)20を積層して形成する。次に、パターニングされたレジスト25aを反射防止膜20上に形成し、レジスト25aをマスクとして反射防止膜20および層間絶縁膜12をエッティングすることにより、孔10aを形成する。孔10aは上部孔10の一部である。孔10aの底部にはライナー膜11が露出する。

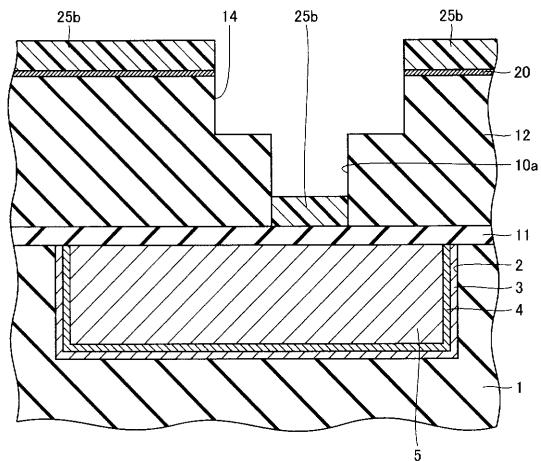

#### 【0026】

図4を参照して、レジスト25aを除去した後、層間絶縁膜12上および孔10a内にパターニングされたレジスト25bを形成する。次に、レジスト25bをマスクとして反射防止膜20および層間絶縁膜12をエッティングすることにより、トレンチ14を形成する。

#### 【0027】

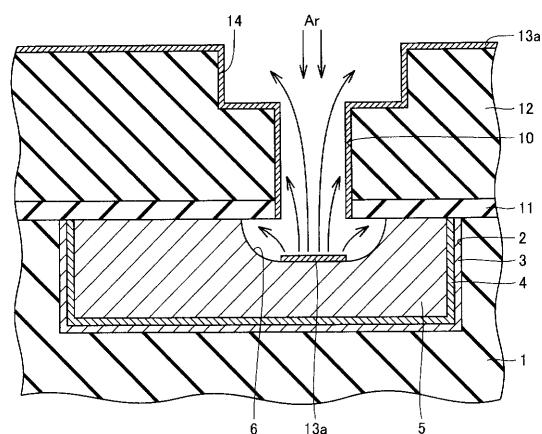

図5を参照して、レジスト25bおよび反射防止膜20を除去した後、孔10aの底部に露出したライナー膜11をエッティングすることにより除去する。これにより、層間絶縁膜12およびライナー膜11に上部孔10が開口する。なお、上部孔10の開口の際、ライナー膜11は完全に除去されなくてもよい。また、ライナー膜11のエッティングの際にには、上部孔10の底部に露出した下部配線5までエッティングしないようにする。上部孔10の開口後、上部孔10内にはレジスト25bの残渣や、ライナー膜11の残渣(ポリマー)が残留している。これらの残渣を除去するために、次に、上部孔10内をウエットエッティングする。また、必要に応じてウエットエッティングの他に、Ar(アルゴン)ガスや、He(ヘリウム)とArとの混合ガスなどを用いたスパッタエッティングや、H<sub>2</sub>(水素)を数%から100%含有した雰囲気でのアニール(たとえば温度100～350、

10

20

30

40

50

10秒～180秒)や、(リモート)プラズマ処理などを行なってもよい。

#### 【0028】

ここで、ウェットエッティングは物質を等方的にエッティングする性質を有している。このため、上部孔10内をウェットエッティングすると、残渣と共に下部配線5もエッティングされ、半円の断面形状の孔6が形成される。ライナー膜11と下部配線5との境界部分付近の孔6の口径 $d_2$ は、上部孔10の口径 $d_1$ よりも大きくなる。すなわち、孔6の内壁面が上部孔10の内壁面よりも外周側(図5中横方向)に削られる。

#### 【0029】

図6を参照して、たとえばスパッタ法やCVD法により、上部孔10の内壁面と、孔6の底部のみとを覆うように、バリアメタル13となる導電膜13aを形成する。ここで、上述のように、孔6の内壁面は、上部孔10の内壁面よりも外周側に削られているので、孔6の内壁面には導電膜13aが形成されない。導電膜13aは、たとえば以下の方法により形成される。

10

#### 【0030】

まず、CVD装置あるいはスパッタ装置などの成膜装置内のロードロックチャンバにウエハを設置し、チャンバ内を真空にする。次に、真空中においてウエハを100以上400以下の温度に加熱し、ウエハ表面に付着している水分などを除去する。次に、-50～300の温度で、0.5nm～50nm程度の厚さの導電膜13aを形成する。

#### 【0031】

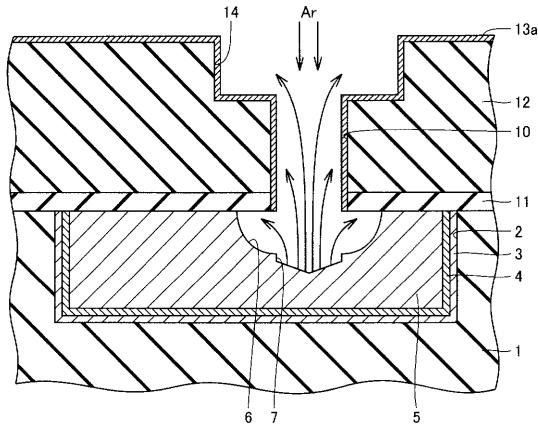

図7を参照して、孔6の底部に存在する導電膜13aを物理的にエッティングすることにより、導電膜13aを孔6の内壁面へ飛散させ、孔6の内壁面全面に導電膜15a(図9)を形成する。導電膜15aは導電膜13aと同じ物質を含んでいる。なお、このとき、導電膜13aをトレンチ14の内壁面および層間絶縁膜12上にまで飛散させ、トレンチ14の内壁面および層間絶縁膜12上にまで導電膜15aを形成してもよい。

20

#### 【0032】

物理的にエッティングする方法としては、たとえばArを用いてスパッタエッティングする方法や、バイアススパッタによるスパッタ粒子を用いたリスペッタをする方法などがある。物理的にエッティングする際には、トレンチ14や孔6の内壁面におけるエッティング速度よりも孔6の底部におけるエッティング速度の方が速くなるような条件にすることが好ましい。また、垂直成分(指向性)の小さなスパッタリング法と上記スパッタエッティングとを同時に行なってもよい。

30

#### 【0033】

図8を参照して、孔6の底部に存在する導電膜13aを完全にエッティングした後で、さらに孔6の底部に存在する下部配線5を物理的にエッティングすることにより、下部配線5の一部を孔6の内壁面へ飛散させる。これにより、孔6の底部に堀込み部分7が形成される。この場合、孔6の内壁面全面に形成された導電膜15aは、下部配線5と同じ物質をさらに含んでいる。なお、下部配線5の一部をトレンチ14の内壁面および層間絶縁膜12上にまで飛散させ、トレンチ14の内壁面および層間絶縁膜12上にまで導電膜15aを形成してもよい。トレンチ14の内壁面および層間絶縁膜12上に導電膜15aを形成した場合、導電膜13aがバリアメタルとしての役割を果たすので、導電膜15a中に含まれるCuはライナー膜11および層間絶縁膜12内に拡散しない。孔6の底部に存在する下部配線5をエッティングする際には、下部配線5の膜厚の4分の1以上あるいは30nm以上エッティングすることが好ましい。

40

#### 【0034】

図9を参照して、エッティング後には、上部孔10の内壁面よりも外周側に削られた孔6の内壁面全面が導電膜15aによって埋められている。また、堀込み部分7は上部孔10を介してのエッティングにより形成されるので、その口径 $d_3$ は、上部孔10の口径 $d_1$ よりも小さくなり、導電膜13aが形成された状態の上部孔10の口径とほぼ等しくなる。また、孔6と堀込み部分7との間には段差が生じる。なお、堀込み部分7の内壁面に近いほどイオンが照射されにくくなるので、エッティングされにくくなる。このため、堀込み部分

50

7の底部7aは、たとえば円錐や半球の形状となる。

#### 【0035】

図10を参照して、たとえばスパッタ法やCVD法などを用いて、バリアメタル17となる導電膜17aが0.5nm~50nmの膜厚で導電膜15a上に形成される。なお、導電膜17aは導電膜15aと同じ材料であってもよい。次に、導電膜17a上にCuのシード膜(図示なし)を形成した後、レンチ14内、上部孔10内、および下部孔8内を埋めるようにCu膜19aを形成する。Cu膜19aは、たとえばCVD法やメッキ法などを用いて形成される。

#### 【0036】

図1を参照して、その後、層間絶縁膜12上の余分な導電膜13a, 15a, 17a, およびCu膜19aをCMP法により除去する。これにより、バリアメタル13、導電膜15、バリアメタル17、およびCu膜19の各々が形成される。以上の工程により、本実施の形態の半導体装置が完成する。

10

#### 【0037】

本実施の形態における半導体装置は、層間絶縁膜1と、層間絶縁膜1内に形成された下部配線5と、層間絶縁膜1上に形成されたライナー膜11と、ライナー膜11上に形成された層間絶縁膜12とを備えている。下部配線5に下部孔8が開口しており、ライナー膜11および層間絶縁膜12には下部孔8に繋がる上部孔10が開口しており、下部孔8の口径d<sub>2</sub>は上部孔の口径d<sub>1</sub>よりも大きくなっている。さらに、下部孔8の内壁面に形成された導電膜15と、上部孔10の内壁面に沿って形成されたバリアメタル13と、上部孔10内および下部孔8内を埋めるように形成されたCu膜19とを備えている。導電膜15はバリアメタル13と同じ物質を含んでいる。

20

#### 【0038】

本実施の形態における半導体装置の製造方法は、以下の工程を備えている。内部に下部配線5が形成された層間絶縁膜1上に、ライナー膜11および層間絶縁膜12を積層して形成する。下部配線5に達する上部孔10をライナー膜11および12に開口する。上部孔10内をウエットエッチングすることにより、上部孔10の口径d<sub>1</sub>よりも大きな口径d<sub>2</sub>を有する孔6を下部配線5内に形成する。上部孔10の内壁面と、孔6の底部のみとを覆うように、導電膜13aを形成する。孔6の底部に存在する導電膜13aを物理的にエッチングすることにより、下部孔8の内壁面に導電膜15を形成する。上部孔10内および下部孔8内を埋めるようにCu膜19を形成する。

30

#### 【0039】

本実施の形態の半導体装置およびその製造方法によれば、孔6の底部に存在する導電膜13aを物理的にエッチングすることにより、導電膜13aを下部孔8の内壁面に導電膜15として形成することができる。したがって、下部孔8の口径d<sub>2</sub>が上部孔10の口径d<sub>1</sub>よりも大きい場合にも下部孔8内にボイドが形成しにくくなるので、半導体装置の信頼性が高くなる。

#### 【0040】

本実施の形態の半導体装置において、導電膜15は下部配線5と同じ物質をさらに含んでいる。

40

#### 【0041】

本実施の形態の半導体装置の製造方法では、導電膜15を形成する際に、孔6の底部に存在する導電膜13aおよび下部配線5を物理的にエッチングする。

#### 【0042】

これにより、導電膜13aおよび下部配線5を飛散させることにより下部孔8の内壁面に導電膜15を厚く形成することができる。これにより、下部配線5が大きくウエットエッチングされた場合にも、導電膜15を下部孔8の内壁面に確実に形成することができる。

#### 【0043】

本実施の形態の半導体装置において、導電膜15は下部孔8の底部7aには形成されて

50

いない。これにより、下部孔 8 の底部 7aにおいて、Cu 膜 19 と下部配線 5 とがバリアメタル 17 のみを介して形成されるので、Cu 膜 19 と下部配線 5との間の電気抵抗を小さくすることができる。

#### 【0044】

本実施の形態の半導体装置において、バリアメタル 13 は、Ta 窒化物、Ta 硅化物、Ta 炭化物、Ti 窒化物、Ti 硅化物、Ti 炭化物、W 窒化物、W 硅化物、W 炭化物、Ru、および Ru 酸化物よりなる群から選ばれる 1 種以上の膜である。

#### 【0045】

これにより、導電膜 15 に含まれる Cu や、Cu 膜 19 がライナー膜 11 および層間絶縁膜 12 中へ拡散することをバリアメタル 13 によって効果的に抑止することができる。

10

#### 【0046】

なお、本実施の形態では、導電膜 13a を物理的にエッチングする際に下部配線 5 までエッチングする場合について示したが、本発明はこのような場合に限定されるものではなく、少なくとも導電膜 13a を物理的にエッチングすればよい。

#### 【0047】

##### (実施の形態 2)

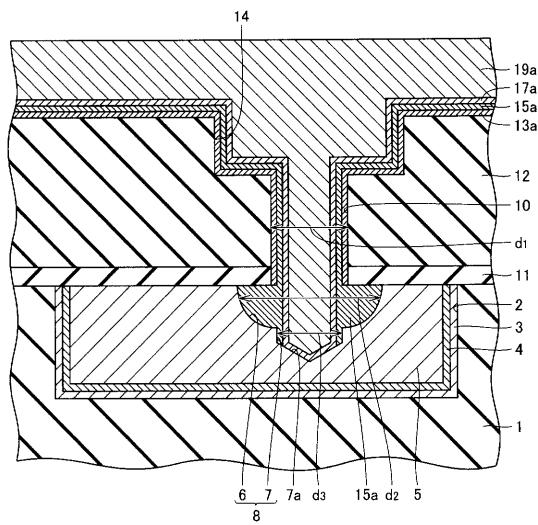

図 11 は、本発明の実施の形態 2 における半導体装置の構造を示す断面図である。

#### 【0048】

図 11 に示すように、本実施の形態の半導体装置では、下部孔 8 の堀込み部分 7 が下部配線 5 を貫通している点において、図 1 に示す本発明の実施の形態 1 における半導体装置と異なっている。このような構造は、図 8 に示す導電膜 15a の形成の際に、下部配線 5 を貫通するまで物理的にエッチングすることによって得られる。

20

#### 【0049】

なお、これ以外の半導体装置の構造およびその製造方法は、図 1 ~ 図 10 に示す本発明の実施の形態 1 の半導体装置およびその製造方法とほぼ同様であるので、同一の部材には同一の符号を付し、その説明を省略する。

#### 【0050】

本実施の形態の半導体装置において、下部孔 8 は下部配線 5 を貫通している。

本実施の形態の半導体装置の製造方法において、導電膜 15a を形成する際に、下部配線 5 を貫通するまで物理的にエッチングする。

30

#### 【0051】

下部孔 8 の底部と下部配線 5 との接触部分は、他の部分に比べてボイドが生成しやすい部分である。本実施の形態の半導体装置およびその製造方法によれば、下部孔 8 の内壁と下部配線 5 との接触部分において Cu 膜 19 と下部配線 5 との電気的な接続を確保している。このため、下部孔 8 の底部と下部配線 5 との接触部分にボイドが生成しても、Cu 膜 19 と下部配線 5 との電気的な接続には影響を与えるないので、半導体装置の信頼性が高くなる。

#### 【0052】

##### (実施の形態 3)

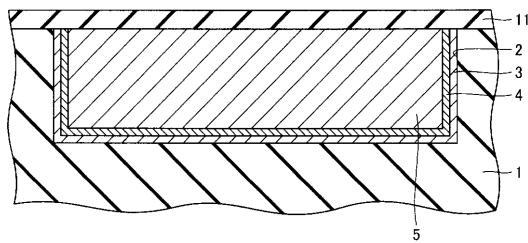

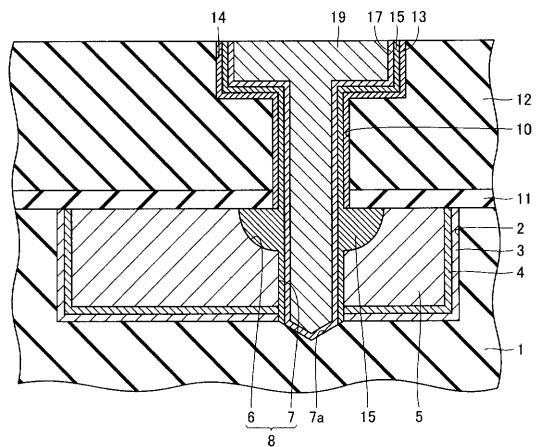

図 12 は、本発明の実施の形態 3 における半導体装置の構造を示す断面図である。

40

#### 【0053】

図 12 に示すように、本実施の形態の半導体装置では、下部孔 8 が層間絶縁膜 1 および下部配線 5 内に開口している点において、図 1 に示す本発明の実施の形態 1 における半導体装置と異なっている。このような構造は、図 5 に示す上部孔 10 の形成の際に、層間絶縁膜 1 および下部配線 5 に達する上部孔 10 を開口することによって得られる。

#### 【0054】

なお、これ以外の半導体装置の構造およびその製造方法は、図 1 ~ 図 10 に示す本発明の実施の形態 1 の半導体装置およびその製造方法とほぼ同様であるので、同一の部材には同一の符号を付し、その説明を省略する。

#### 【0055】

50

本実施の形態の半導体装置において、下部孔 8 は層間絶縁膜 1 および下部配線 5 に開口している。

**【 0 0 5 6 】**

本実施の形態の半導体装置の製造方法において、上部孔 10 を開口する際に、下部配線 5 および層間絶縁膜 1 に達する上部孔 10 を開口する。

**【 0 0 5 7 】**

半導体装置の製造工程においては、上部孔 10 を開口する際に、レジストのずれなどにより、図 12 に示すように上部孔 10 が下部配線 5 の真上からずれた位置に開口する場合がある。本実施の形態の半導体装置およびその製造方法によれば、上部孔 10 の位置がずれた場合でも、下部孔 8 内に形成された導電膜と下部配線 5 との接触部分を確保することができる。その結果、半導体装置の信頼性が高くなり、Cu 膜 19 と下部配線 5 と間の電気抵抗を低減することができる。10

**【 0 0 5 8 】**

なお、実施の形態 1～3 においては、孔 6 の口径  $d_2$  が上部孔 10 の口径  $d_1$  よりもはるかに大きい場合について示した。しかし、本発明の半導体装置は、図 13 に示すように、孔 6 の口径  $d_2$  が上部孔 10 の口径  $d_1$  よりもわずかに大きくてよい。

**【 0 0 5 9 】**

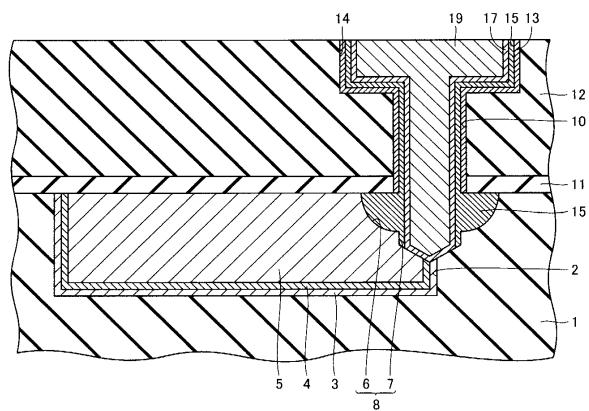

(実施の形態 4)

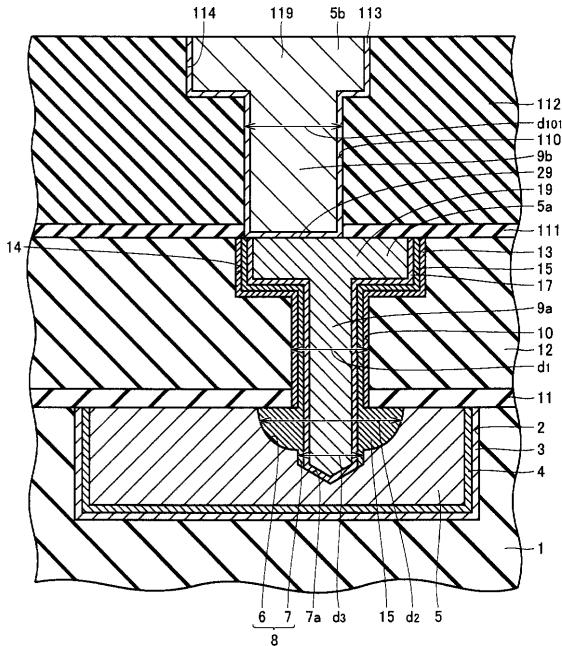

図 14 は、本発明の実施の形態 4 における半導体装置の構造を示す断面図である。図 14 を参照して、本実施の形態の半導体装置は、以下の点において実施の形態 1 の半導体装置と異なっている。すなわち、Cu 膜 19 を覆うように層間絶縁膜 12 上にライナー膜 111 が形成されており、ライナー膜 111 上に層間絶縁膜 112 が形成されている。層間絶縁膜 112 の上部にはトレンチ 114 が形成されており、トレンチ 114 内およびライナー膜 111 には、配線 5a の上面 29 に達する孔 110 が開口されている。トレンチ 114 の内壁面および底部と、孔 110 の内壁面および底部とに沿って、バリアメタル 113 が形成されている。トレンチ 114 および孔 110 内を埋めるように Cu 膜 119 が形成されている。20

**【 0 0 6 0 】**

上部孔 10 および下部孔 8 を埋める Cu 膜 19、バリアメタル 17、および導電膜 15 によってコンタクト 9a が構成されており、トレンチ 114 を埋める Cu 膜 19 によって配線 5a (第 2 配線) が構成されている。また、孔 110 (第 2 配線用孔) を埋める Cu 膜 119 (接続層) によってコンタクト 9b が構成されており、トレンチ 114 を埋める Cu 膜 119 によって配線 5b が構成されている。言い換えれば、本実施の形態においては、下部配線 5、配線 5a、および配線 5b の各々が絶縁膜を介してこの順序で積層して形成されており、下部配線 5 と配線 5a とがコンタクト 9a によって電気的に接続されており、配線 5a と配線 5b とがコンタクト 9b によって電気的に接続されている。30

**【 0 0 6 1 】**

ここで、コンタクト 9a の構造とコンタクト 9b の構造とは互いに異なっている。コンタクト 9a が形成されている上部孔 10 および下部孔 8 のうち、下部孔 8 は下部配線 5 内部に開口されている。一方、コンタクト 9b が形成されている孔 110 は配線 5a 内部に達しておらず、配線 5a の上面 29 で止まっている。また、コンタクト 9b が形成されている孔 110 の口径  $d_{101}$  の大きさは、コンタクト 9a が形成されている孔 10 の口径  $d_1$  よりも大きい。40

**【 0 0 6 2 】**

本実施の形態の半導体装置は、配線 5a と、配線 5a 上から配線 5a に達する孔 110 と、孔 110 内を埋める Cu 膜 119 とを備えている。孔 110 は配線 5a 内部にまで達していない。

**【 0 0 6 3 】**

本実施の形態における半導体装置によれば、以下の効果を得ることができる。口径の大きいコンタクトは、下部の配線との接触面積が大きいので、電流密度が低く、他のコンタ50

クトに比べてボイドの発生起点となり難い。このため、口径の大きいコンタクトの構造をコンタクト9bのような簡易な構造にしても半導体装置の信頼性は確保される。これにより、コンタクト9bについては配線5aをエッティングしたり、孔110に繋がる下部孔を形成したりする必要がないので、半導体装置の製造工程を簡略化することができ、半導体装置の製造コストを削減することができる。

#### 【0064】

また、本実施の形態の半導体装置によれば、孔110の口径 $d_{101}$ は、上部孔10の口径 $d_1$ よりも大きいので、コンタクト9aおよび9bに同じ大きさの電流が流れる場合に、電流密度の低いコンタクト9bを簡易な構造にすることができる。

#### 【0065】

また、本実施の形態の半導体装置によれば、孔110は上部孔10よりも上部に形成されている。これにより、上部に存在するコンタクトの電流密度は下部に存在するコンタクトの電流密度よりも通常低いので、上部に存在する孔110に形成されるコンタクト9bを簡易な構造にすることができる。

#### 【0066】

なお、孔内を埋める層としてCu層19および119を用いる代わりに、Ag(銀)による層や、CuまたはAgを主成分とする合金による層などを用いてもよい。

#### 【0067】

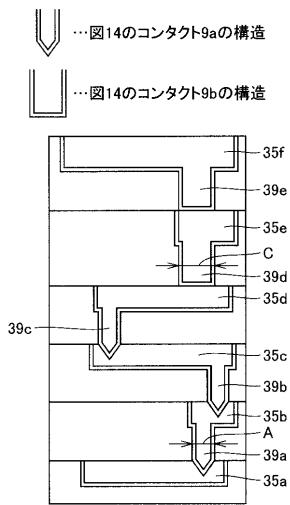

##### (実施の形態5)

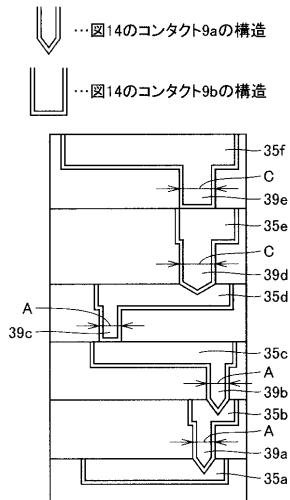

図15は、本発明の実施の形態5における半導体装置の断面を簡略化して示す図である。図15を参照して、本実施の形態の半導体装置は、多数の配線35a～35fの各々と、配線35a～35fの各々の間を電気的に接続するためのコンタクト39a～39eの各々とを備えている。配線35a～35fの各々は、絶縁層を介してこの順序で積層して形成されている。また、配線35aおよび配線35bはコンタクト39aによって電気的に接続されており、配線35bおよび配線35cはコンタクト39bによって電気的に接続されている。また、配線35cおよび配線35dはコンタクト39cによって電気的に接続されており、配線35dおよび配線35eはコンタクト39dによって電気的に接続されている。さらに、配線35eおよび配線35fはコンタクト39eによって電気的に接続されている。

#### 【0068】

コンタクト39a～39eの各々は口径Aまたは口径Cを有している。コンタクト39a～39cの各々は口径Aを有しており、コンタクト39dおよび39eの各々は口径Cを有している。口径Cは口径Aよりも大きい。

#### 【0069】

本実施の形態においては、図14におけるコンタクト9aとほぼ同様の形状のコンタクトと、図14におけるコンタクト9bとほぼ同様の形状のコンタクトとが混在している。具体的には、コンタクト39a～39eのうち、口径Aを有するコンタクト39a～39cの各々はコンタクト9aとほぼ同様の形状を有している。また、口径Cを有するコンタクト39dおよび39eの各々はコンタクト9bとほぼ同様形状を有している。

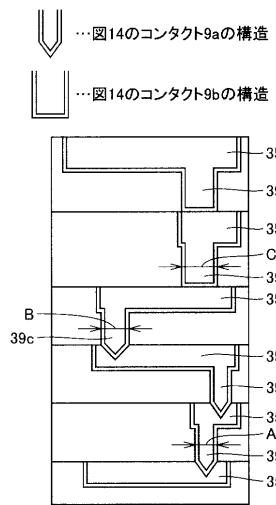

#### 【0070】

また、図16は、本発明の実施の形態5における他の半導体装置の断面を簡略化して示す図である。図16を参照して、コンタクト39a～39eの各々は口径A、口径B、または口径Cを有している。コンタクト39aおよび39bの各々は口径Aを有しており、コンタクト39cは口径Bを有しており、コンタクト39dおよび39eの各々は口径Cを有している。口径Cは口径Bよりも大きく、口径Bは口径Aよりも大きい。

#### 【0071】

図16の構造においては、コンタクト39a～39eのうち、口径Aおよび口径Bを有するコンタクト39a～39cの各々はコンタクト9aとほぼ同様の形状を有している。また、口径Cを有するコンタクト39dおよび39eの各々はコンタクト9bとほぼ同様形状を有している。

10

20

30

40

50

**【0072】**

また、コンタクト39a～39eのうち、口径Aを有するコンタクト39aおよび39bの各々がコンタクト9aとほぼ同様の形状を有しており、口径Bおよび口径Cを有するコンタクト39c～39eの各々がコンタクト9bとほぼ同様形状を有していてもよい。

**【0073】**

なお、これ以外の構成は、図15に示す半導体装置の構成とほぼ同様であるので、同一の部材には同一の符号を付し、その説明を省略する。

**【0074】**

本実施の形態における半導体装置のように、多数のコンタクト39a～39eが形成されている場合であっても、相対的に口径の小さいコンタクトの各々についてはコンタクト9aとほぼ同様の形状とし、相対的に口径の大きいコンタクトの各々についてはコンタクト9bとほぼ同様の形状とすることで、実施の形態5の場合と同様に、半導体装置の信頼性を確保しつつ、半導体装置の製造コストを削減することができる。10

**【0075】**

なお、図15では、口径Aを有するコンタクト39a～39cの各々についてコンタクト9aとほぼ同様の形状とする場合について示したが、口径Aを有するコンタクトのうち最下層のコンタクト39aのみをコンタクト9bとほぼ同様の形状としてもよい。

**【0076】**

また、本実施の形態では、相対的に口径の小さいコンタクトが下層に形成され、相対的に口径の大きいコンタクトが上層に形成される場合について示したが、相対的に口径の小さいコンタクトと、相対的に口径の大きいコンタクトとの各々の形成位置については任意である。20

**【0077】****(実施の形態6)**

図17は、本発明の実施の形態6における半導体装置の断面を簡略化して示す図である。図17を参照して、コンタクト39a～39eは口径Aまたは口径Cを有している。コンタクト39a～39cの各々は口径Aを有しており、コンタクト39dおよび39eの各々は口径Cを有している。口径Cは口径Aよりも大きい。

**【0078】**

本実施の形態では、コンタクト39aおよび39bの各々を流れる電流の量はコンタクト39cを流れる電流の量よりも大きいため、コンタクト39a～39cの各々は同一の口径Aを有しているにも関わらず、コンタクト39aおよび39bの各々の電流密度はコンタクト39cの電流密度よりも大きい。同様に、コンタクト39dを流れる電流の量はコンタクト39eを流れる電流の量よりも大きいため、コンタクト39dおよび39eは同一の口径Cを有しているにも関わらず、コンタクト39dの電流密度はコンタクト39eの電流密度よりも大きい。30

**【0079】**

そこで、コンタクト39a～39eのうち、相対的に電流密度の大きいコンタクト39a、39b、および39dの各々がコンタクト9aとほぼ同様の形状とされている。一方、相対的に電流密度の小さいコンタクト39cおよび39eの各々がコンタクト9bとほぼ同様形状とされている。40

**【0080】**

なお、これ以外の構成は、図15に示す半導体装置の構成とほぼ同様であるので、同一の部材には同一の符号を付し、その説明を省略する。

**【0081】**

多数の配線を備える半導体装置において、電流密度はコンタクト毎に異なっており、電流密度の大きいコンタクトには電流密度の小さいコンタクトに比べてボイドが発生しやすく、断線などが起こりやすい。そこで、相対的に電流密度の小さいコンタクトの構造をコンタクト9bのような簡易な構造にしても半導体装置の信頼性は確保される。これにより、相対的に電流密度の小さいコンタクトについては製造工程を簡略化することができ、半50

導体装置の製造コストを削減することができる。

【実施例 1】

【0082】

以下、本発明の一実施例について説明する。

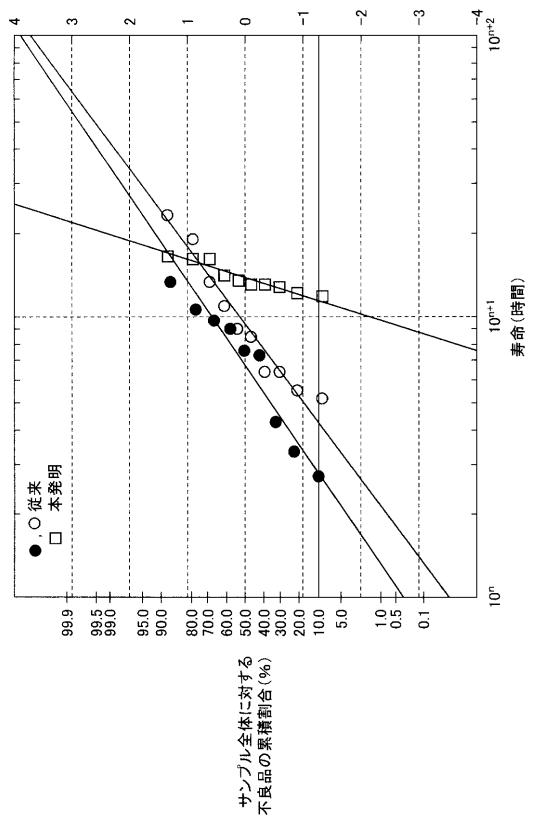

本実施例では、従来の半導体装置と本発明の半導体装置との信頼性を比較した。具体的には、下部配線をエッティングせずにビアホールを形成した従来の半導体装置と、図1に示す本発明の半導体装置との寿命を調べた。図18にその結果を示す。なお、従来の半導体装置については、図18中の黒丸と白丸との2つの集団についての寿命を調べた。四角は本発明の半導体装置を示している。

【0083】

10

図18に示すように、従来の半導体装置では、 $10^{n+1}$ 時間以内にサンプル全体の約50~60%の半導体装置にEM(エレクトロマイグレーション)やSM(ストレスマイグレーション)などの欠陥が生じ、不良品となっていることが分かる。一方、本発明の半導体装置では、 $10^{n+1}$ 時間を超えてもほとんど不良品が発生していないことが分かる。このことから、本発明の半導体装置では、下部配線5の表面と下部孔8内に形成された導電膜の底部との接触部分へ熱応力および電流が集中するのを緩和することができるので、半導体装置の信頼性を高めることができるのが分かる。

【0084】

20

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0085】

【図1】本発明の実施の形態1における半導体装置の構造を示す断面図である。

【図2】本発明の実施の形態1における半導体装置の製造方法の第1工程を示す断面図である。

【図3】本発明の実施の形態1における半導体装置の製造方法の第2工程を示す断面図である。

【図4】本発明の実施の形態1における半導体装置の製造方法の第3工程を示す断面図である。

30

【図5】本発明の実施の形態1における半導体装置の製造方法の第4工程を示す断面図である。

【図6】本発明の実施の形態1における半導体装置の製造方法の第5工程を示す断面図である。

【図7】本発明の実施の形態1における半導体装置の製造方法の第6工程を示す断面図である。

【図8】本発明の実施の形態1における半導体装置の製造方法の第7工程を示す断面図である。

【図9】本発明の実施の形態1における半導体装置の製造方法の第8工程を示す断面図である。

40

【図10】本発明の実施の形態1における半導体装置の製造方法の第9工程を示す断面図である。

【図11】本発明の実施の形態2における半導体装置の構造を示す断面図である。

【図12】本発明の実施の形態3における半導体装置の構造を示す断面図である。

【図13】本発明の実施の形態1~3における半導体装置の変形例の構造を示す断面図である。

【図14】本発明の実施の形態4における半導体装置の構造を示す断面図である。

【図15】本発明の実施の形態5における半導体装置の断面を簡略化して示す図である。

【図16】本発明の実施の形態5における他の半導体装置の断面を簡略化して示す図であ

50

る。

【図17】本発明の実施の形態6における半導体装置の断面を簡略化して示す図である。

【図18】寿命と不良品の累積割合との関係を示す図である。

【符号の説明】

【0086】

1, 12, 112 層間絶縁膜、2 溝、3, 4 バリアメタル、5 下部配線、5a, 5b, 35a ~ 35f 配線、6, 10a, 110 孔、7 堀込み部分、7a 底部、8 下部孔、9a, 9b, 39a ~ 39e コンタクト、10 上部孔、11, 111 ライナー膜、13, 17, 113 バリアメタル、14, 114 トレンチ、13a, 15, 15a, 17a 導電膜、19, 19a, 119 Cu膜、20 反射防止膜、25a, 25b レジスト、29 上面。

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(74)代理人 100098316

弁理士 野田 久登

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 前川 和義

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 森 健壹

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 早川 朋一

(56)参考文献 特開2002-299436 (JP, A)

特開2002-064139 (JP, A)

特表2002-521842 (JP, A)

米国特許第06607977 (US, B1)

特開2000-012684 (JP, A)

特開2005-129677 (JP, A)

国際公開第2004/053926 (WO, A2)

特開2003-249547 (JP, A)

特開2002-246467 (JP, A)

米国特許第06613664 (US, B1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205 - 21/3215

H01L 21/768

H01L 23/52

H01L 23/522 - 23/532