(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3942264号

(P3942264)

(45) 発行日 平成19年7月11日(2007.7.11)

(24) 登録日 平成19年4月13日(2007.4.13)

(51) Int.C1.

F 1

|              |           |            |   |

|--------------|-----------|------------|---|

| HO1L 21/822  | (2006.01) | HO1L 27/04 | L |

| HO1L 27/04   | (2006.01) | HO1L 21/88 | M |

| HO1L 23/52   | (2006.01) |            |   |

| HO1L 21/3205 | (2006.01) |            |   |

請求項の数 2 (全 9 頁)

(21) 出願番号

特願平10-59620

(22) 出願日

平成10年3月11日(1998.3.11)

(65) 公開番号

特開平11-261008

(43) 公開日

平成11年9月24日(1999.9.24)

審査請求日

平成17年3月9日(2005.3.9)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100094525

弁理士 土井 健二

(74) 代理人 100094514

弁理士 林 恒徳

(72) 発明者 小林 修

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 棚田 一也

(56) 参考文献 特開平07-183468 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体基板上に形成されるインダクタンス素子

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上に形成されるインダクタンス素子であって、

前記半導体基板の表面に形成された複数のPN接合と、

前記複数のPN接合が形成された領域上の絶縁膜上に形成され、前記インダクタンス素子を構成する巻き線状の帯状導電膜と、

前記複数のPN接合間に逆バイアス電圧が印加されて、少なくとも前記半導体基板表面領域が完全に空乏化しているインダクタンス素子において、

前記半導体基板が一導電型であり、該基板の表面側から基板内部に向かって不純物濃度が増加する反対導電型の第1の不純物領域が前記基板の表面に形成されて前記PN接合が形成され、前記第1の不純物領域への逆バイアス電圧の印加は、当該第1の不純物領域の基板内部側から行われることを特徴とするインダクタンス素子。

## 【請求項2】

請求項1において、更に、前記反対導電型であって前記第1の不純物領域に接続し該基板内部に埋め込み形成される第2の不純物領域を更に有し、前記逆バイアス電圧の印加は、前記第2の不純物領域を介して行われることを特徴とするインダクタンス素子。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、集積回路を構成する半導体基板上に形成されるインダクタンス素子に関し、特

に損失が少なくインダクタンスの低下が少ない構造のインダクタンス素子に関する。

【0002】

【従来の技術】

近年において携帯電話等の携帯通信機器の小型化が鋭意進められている。かかる小型携帯通信機器に使用される高周波回路を、シリコン半導体を利用した集積回路で構成する要求が高まっている。高周波回路は、トランジスタ、抵抗、容量に加えて、コイルやトランジスタといったインダクタンス素子が必要になる。従って、シリコン半導体基板にトランジスタや抵抗等を利用した集積回路と共に、インダクタンス素子も形成することが必要になる。

【0003】

かかるインダクタンス素子は、一般的には、半導体基板表面に形成した絶縁膜上に、アルミニウム等の帯状導電膜を渦巻き状にあるいは巻き線状の形成することで実現される。しかしながら、かかる構成では、インダクタンス素子のごく近傍に半導体基板が存在し、インダクタンス素子に電流を流した時に発生する磁束の変化を妨げる渦電流がその半導体基板に発生し、特性に損失が伴うことが知られている。

【0004】

即ち、巻き線状に形成された帯状導電層をトランスにおける一次コイルと考えると、不純物を含む半導体基板そのものは抵抗値が低いので高周波領域では短絡された二次コイルのように作用する。この二次コイルの存在による損失は、特に高周波領域において顕著に見られ、そのような半導体基板内の渦電流の発生を防止する為の提案がなされている。例えば、特開平7-183468号には、シリコン半導体基板の表面に複数のPN接合を形成し、その接合に生成される空乏層により、渦電流を抑制することが示されている。即ち、基板表面の渦電流の経路を複数の空乏層により分断し、渦電流を抑制する。あるいは、特開平7-235640号には、シリコン半導体基板の表面に複数のPN接合を形成し、さらにそのPN接合に制御された逆バイアス電圧を印加することで、その接合に形成される空乏層による容量を利用してLC複合回路素子を形成することが提案されている。この公知例においても、基板表面に形成される空乏層により渦電流の発生が抑えられることが示されている。

【0005】

図6は、かかる公知例のインダクタンス素子の構造を示す図である。P型の半導体基板10の表面にN型の不純物領域14が形成され、基板表面に複数のPN接合が形成される。そして、基板10の表面上に形成した絶縁膜12上に、渦巻き状の帯状の導電膜16が形成される。この帯状導電膜16の一端16Aは、図示しない配線に接続され、また、他端16Bは、絶縁膜12内に形成された下層の配線18に接続される。帯状導電膜16の一端から他端に向かって図中の矢印22の方向に電流を流すと、それにより磁束が渦巻き配線内に発生する。

【0006】

図6に示された構成では、複数のPN接合に空乏層が形成されるので、基板10の表面側に空乏層が多く形成され、帯状導電膜16からなるインダクタンス素子により発生した磁束に対して半導体基板10内に発生する渦電流の流れる抵抗を高くすることができ、渦電流を抑制し上記した渦電流による損失とインダクタンスの低下を防止することができる。

【0007】

【発明が解決しようとする課題】

しかしながら、上記の従来例は、半導体基板10の表面に複数の空乏層を形成するだけでも、依然として基板表面に渦電流は発生する。また、帯状導電膜の一次コイルと基板内の渦電流の二次コイルとの間には空乏化していない半導体領域が存在するので、両コイル間の相互インダクタンスは低くない。半導体基板の表面領域を全て空乏化することが考えられるが、実際に集積回路が形成されるシリコン半導体基板10の表面に、基板と反対導電型の不純物領域14を形成する場合、微細加工には自ずと限界がある。従って、基板表面が完全に空乏化する程度に複数のPN接合を近接して形成することは困難である。更に、集積回路が形成される半導体基板10はそれ自体高い不純物濃度を有するので、表面に形成

10

20

30

40

50

された P N 接合間に自然に延びる空乏層の幅はそれほど大きくはならない。その結果、せいぜい P N 接合に沿った薄い空乏層が形成されるに止まる。従って、基板表面は完全に空乏化することではなく、上記した通り従来例では、渦電流が発生する領域の抵抗を上げる程度の効果しかない。

#### 【 0 0 0 8 】

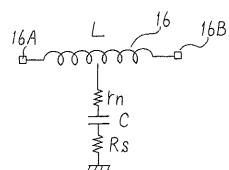

更に、図 7 の等価回路図に示される通り、基板 1 0 の不純物濃度が比較的高く、その基板内の抵抗  $R_s$  は比較的低い。また同様に、表面に形成された N 型不純物領域 1 4 の抵抗  $r_n$  も比較的低い。そのため、P N 接合により形成された容量  $C$  が、インダクタンス素子 L に電気的につながり、インダクタンス素子の特性に影響を与える。

#### 【 0 0 0 9 】

上記した通り、帯状導電膜 1 6 によるインダクタンス素子が一次コイルとなり、基板内の渦電流の経路が二次コイルとなることから、よりインダクタンス素子の損失をなくし特性を良くするためには、両コイル間の絶縁を強くして両コイル間の実効的な相互インダクタンスを低くすることが必要である。

#### 【 0 0 1 0 】

更に、図 5 に示された通り、帯状導電膜 1 6 に電流 2 2 を流すことにより、基板内に加えて、帯状導電膜 1 6 自体にも渦電流 2 0 が発生する。特に、内側に巻かれた帯状導電膜 1 6 には、多くの磁束が発生するので、渦電流 2 0 の発生が大きくなる。かかる渦電流も口スの原因となるので、避けることが要求される。その場合、帯状導電膜 1 6 の配線幅を狭くすることが考えられるが、配線幅を狭くすると、抵抗が大きくなり更にそれ自体のインダクタンス成分も大きくなり好ましくない。

#### 【 0 0 1 1 】

そこで、本発明は、半導体基板表面に形成される帯状導電膜によるインダクタンス素子と、半導体基板内の領域との間の絶縁性をより高くした構造のインダクタンス素子を提供することにある。

#### 【 0 0 1 2 】

更に、本発明は、半導体基板表面に形成される帯状導電膜自体に発生する渦電流を抑えた構造のインダクタンス素子を提供することにある。

#### 【 0 0 1 3 】

**【課題を解決するための手段】**

上記の目的を達成する為に、第 1 の本発明は、インダクタンス素子を構成する巻き線状の帯状導電膜の下の半導体基板表面に、複数の P N 接合を形成し、その P N 接合に逆バイアス電圧を印加し、基板表面を完全に空乏化する。P N 接合に逆バイアスを印加することで、基板表面の不純物濃度が高く隣接する P N 接合がある程度離間していても、その空乏層の伸びを大きくすることができ、完全に空乏化させることができる。

#### 【 0 0 1 4 】

更に、上記の目的を達成する為に、第 2 の発明は、インダクタンス素子を構成する巻き線状の帯状導電膜の下の半導体基板表面に、酸素のイオン注入法により形成される厚い絶縁領域を形成する。この絶縁領域は、通常の集積回路素子領域上に形成される配線用の薄い絶縁膜より大きな膜厚を有する。この厚い絶縁領域の存在により、インダクタンス素子の一次コイルと半導体基板内の渦電流による二次コイルとの間の実効的な相互インダクタンスを小さくすることができる。また、複数の P N 接合を利用した完全空乏化する場合よりも、より確実な絶縁が得られるので、インダクタンス素子の損失は少ない。

#### 【 0 0 1 5 】

更に、上記の目的を達成する為に、第 3 の発明では、巻き線状に形成される帯状導電膜に、巻き線方向に延びるスリットを形成し、帯状導電膜を巻き線方向に延びる複数の並列配線とする。かかる構成にすることにより、帯状導電膜内に発生する渦電流の経路をなくし、渦電流を抑制して特性損失を抑えることができる。

#### 【 0 0 1 6 】

更に、上記の目的を達成する為に、第 4 の発明では、巻き線状に形成される帯状導電膜を

10

20

30

40

50

、巻き線方向の導電率が巻き線方向と垂直方向の導電率よりも高い異方性導電性を有する材料で構成する。例えば、酸化物超電導体や有機導電材料を利用することにより、巻き線方向の導電率が高く、それとは垂直方向の導電率が低い帯状導電膜を形成することができる。かかる材料の場合は、帯状導電膜の巻き線方向の抵抗の増加を防止しつつ内部に発生する渦電流を抑えることができる。

【0017】

【発明の実施の形態】

以下、本発明の実施の形態について図面に従って説明する。しかしながら、本発明の技術的範囲がその実施の形態に限定されるものではない。

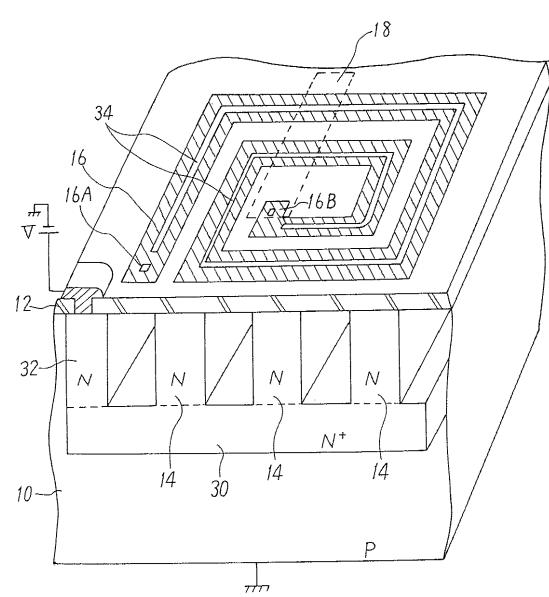

【0018】

図1は、実施の形態例のインダクタンス素子の構造図である。この例では、P型の半導体基板10の表面に複数のN型不純物領域14が形成され、表面に複数のPN接合が形成される。更に、半導体基板10の内部には、より濃度の高いN型の埋込み不純物領域30が形成される。この埋め込み不純物領域30は、例えば、高エネルギーイオン注入法により形成することができる。そして、この埋め込み不純物領域30は、N型不純物領域14と同時に形成されるN型の不純物領域32により基板表面に導出される。

【0019】

そして、半導体基板10とN型不純物涼気14との間のPN接合に対して、逆バイアス電圧Vが印加される。この逆バイアス電圧Vは、基板表面のPN接合から延びる空乏層がつながる程度の電圧である。

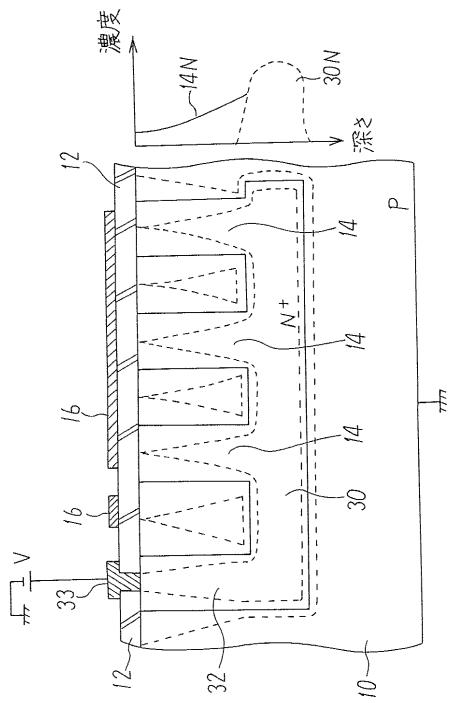

【0020】

図2は、図1のインダクタンス素子に逆バイアス電圧を印加した時の詳細断面図である。図中右側に示される不純物濃度分布のように、N型不純物領域14の不純物濃度分布14Nは、基板表面で濃度が低く、基板内部に向かって濃度が高くなる。また、埋込不純物領域30の不純物濃度分布30Nは、図示される通り、N型不純物領域14よりも高い濃度である。

【0021】

そして、基板10の表面領域でのPN接合間に印加される逆バイアス電圧Vは、基板表面の導電層33から、N型不純物領域32、N型の埋込不純物領域30を介してインダクタンス素子の下のPN接合を形成するN型不純物領域14に印加される。従って、そのPN接合から延びる空乏層は、破線に示した様に拡がる。即ち、基板10の表面側での空乏層の延びは大きく、隣接するPN接合から延びる空乏層がつながり、基板表面は完全に空乏化する。また、不純物濃度が高い基板内部のPN接合から拡がる空乏層の延びは、基板表面に比較して少ない。従って、基板内部の埋込不純物領域30から印加される電圧は、不純物領域14の垂直方向の非空乏領域(N型半導体領域)を介して、基板表面に有効に印加され、基板表面の完全空乏化が可能になる。

【0022】

図1の例では、P型半導体基板10の表面には、平面図で複数本のN型不純物領域14が形成されるが、本発明はかかる形状に限定されず、例えば、平面図で格子状あるいは微小領域をマトリクス状に配置した形状であっても良い。基板表面において、より多くのPN接合が終端する構造であれば、そのPN接合から延びる空乏層により基板表面が完全に空乏化しやすくなる。

【0023】

本実施の形態例では、インダクタンス素子を構成する巻き線状の帯状導電膜16が、上記のPN接合が形成された領域上の絶縁膜12上に形成される。この帯状導電膜16は、図1に示される通り、巻き線方向に延びるスリット34を有する。従って、帯状導電膜16は、巻き線方向に延びる複数の並列接続された配線構造となる。

【0024】

帯状導電膜16内にスリット34を形成することにより、帯状導電膜16の両端16A, 16B間に電流を流した場合でも、帯状導電膜16内に発生する渦電流を少なくすること

10

20

30

40

50

ができる。インダクタンス素子を構成する帯状導電膜 16 は、それ自体がインダクタンス成分を持たない様にある程度の幅をもつ必要がある。しかしながら、その線幅が大きすぎると、特に巻き線状の内周部分では、多くの磁束が貫通し、それに対する渦電流が帯状導電膜 16 内に発生する。そこで、本実施の形態例では、その帯状導電膜 16 内にスリット 34 を形成し、その渦電流を抑える。帯状導電膜 16 の幅方向の渦電流の流れる経路がなくなり、その分発生する渦電流はより小さい領域のみとなる。また、スリット 34 を形成しても、帯状導電膜 16 は並列接続されているので巻き線方向の抵抗が低くなることはない。

#### 【 0 0 2 5 】

このスリット 43 は、巻き線状の帯状導電膜 16 の内周の巻き線部分にのみ形成しても有効である。巻き線の外周よりも内周の部分でより多くの磁束が貫通するので、その部分の帯状導電膜 16 にスリットを形成するだけでも、有効に渦電流を抑制することができる。

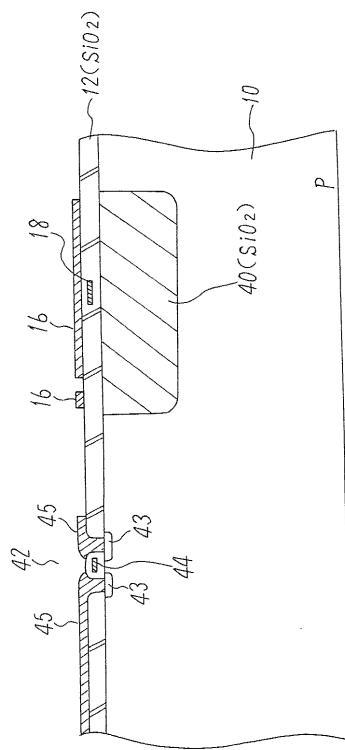

#### 【 0 0 2 6 】

図 3 は、別の実施の形態例のインダクタンス素子の断面図である。図 3 には、インダクタンス素子を構成する帯状導電膜 16 と、集積回路を構成する MOS トランジスタ 42 とが示される。通常の MOS トランジスタ 42 は、P 型基板の表面に形成した N 型ソース・ドレイン領域 43 と、ゲート酸化膜上に形成したゲート電極 44 と、基板表面に形成された絶縁膜 12 上に導出される配線層 45 等で構成される。かかる絶縁膜 12 は、例えば CVD 法等により形成されるシリコン酸化膜であるが、その膜厚は全体でせいぜい 5000 オングストローム程度である。

#### 【 0 0 2 7 】

それに対して、インダクタンス素子を構成する帯状導電膜 16 が形成される領域の下には、基板 10 の表面から内部に厚い絶縁領域 40 が形成される。この絶縁領域 40 は、例えばサイモックス法と呼ばれる半導体基板上に SOI (Silicon on Insulator) 構造を形成する場合に利用される方法により形成される。即ち、このサイモックス法によれば、基板表面に酸素イオンを注入することにより、半導体シリコン基板の表面から内部へ延びる厚い領域を酸化シリコン領域 40 に変えることができる。従って、この絶縁領域 40 は、例えばその膜厚が 10000 オングストローム以上あり、通常の集積回路素子上の配線用の絶縁膜 12 の膜厚よりもかなり厚くすることができる。

#### 【 0 0 2 8 】

この様に、インダクタンス素子を構成する帯状導電膜 16 の下に、配線用の絶縁膜 12 に加えて、基板 10 の表面から内部へ延びる厚い絶縁領域 40 を形成することにより、帯状導電膜 16 とその直下の基板内部の半導体領域との間が完全に絶縁される。また、その距離も大きくなり、帯状導電膜 16 による一次コイルと基板内部に発生する渦電流による二次コイルとの間の相互インダクタンスを小さくすることができる。また、基板内の渦電流の発生自体も抑制される。

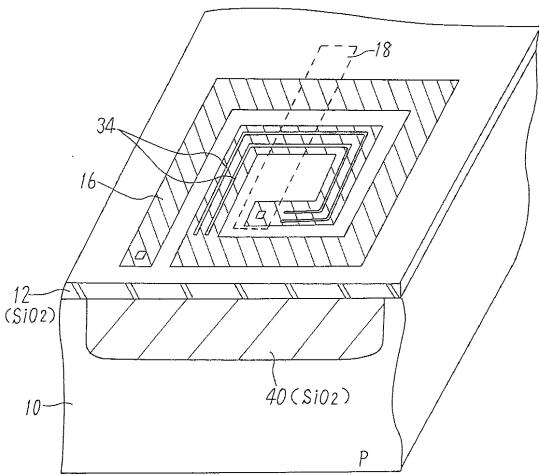

#### 【 0 0 2 9 】

図 4 は、図 3 のインダクタンス素子の一部断面斜視図である。図 4 に示される通り、帯状導電膜 16 の下には、厚い絶縁領域 40 が形成される。更に、図 4 の帯状導電膜 16 の巻き線の内周部分には、複数のスリット 34 が形成される。帯状導電膜 16 に電流が流れることにより発生する磁束密度がより高い巻き線の内周部分に、複数のスリット 34 を設けることにより、帯状導電膜 16 内に発生する渦電流をより効率的に抑えることができる。

#### 【 0 0 3 0 】

図 5 は、更に別のインダクタンス素子の構造を示す平面図である。この例は、インダクタンス素子を構成する帯状導電膜内に発生する渦電流を抑える為に、その帯状導電膜を、巻き線方向の導電率がその垂直方向の導電率よりも大きい異方性の導電率をもつ材料により形成する。かかる材料は、例えば、セラミック系の酸化物超電導体である、  $Y_2Ba_4Cu_7O_{15}$  や  $LaBa_2Cu_3O_7$  等である。或いは、別の材料として、ポリアセチレン等の有機導電材料である。これらの材料は、例えば、スパッタリング法や反応性蒸着法によりこれらの材料の薄膜を形成した後に、化学的エッティングやイオンエッティング法により任

10

20

30

40

50

意の形状に加工するなどの方法により形成することで、一定方向の導電率がそれに垂直な方向の導電率よりも大きくなるようにすることができる。

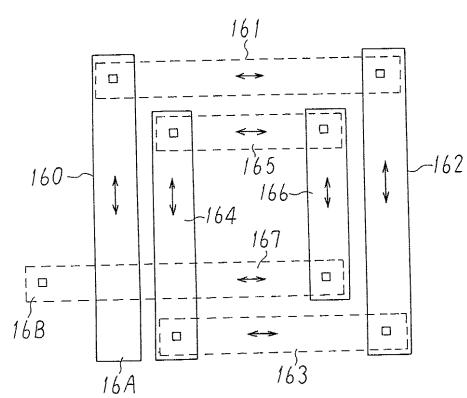

【0031】

図5に示された例では、巻き線状の帯状導電膜を、図中の水平方向の下層配線161, 163, 165, 167と、図中の垂直方向の上層配線160, 162, 164, 166とで構成する。上記した方法により、先ず下層配線用の異方性導電材料層を形成し、図中の横方向のパターンにエッティングして、下層配線161, 163, 165, 167を形成する。更に、その上に絶縁層を形成し上層と下層を接続するピア・ホールを形成し、さらに上層配線用の異方性導電材料層を形成し、図中の縦方向のパターンにエッティングして、上層配線160, 162, 164, 166を形成する。その結果、一端16Aから他端16Bまでの巻き線状の帯状導電膜が形成される。 10

【0032】

下層配線161, 163, 165, 167は、図中の矢印(図中水平方向)で示される巻き線方向の導電率が、それに垂直な方向の導電率よりも高い。また同様に、上層配線160, 162, 164, 166は、図中の矢印(図中垂直方向)で示される巻き線方向の導電率が、それに垂直な方向の導電率よりも高い。従って、図5のインダクタンスの帯状導電膜は、その巻き線方向の導電性を犠牲にすることなく、それ自身に発生する渦電流を抑制することができる。

【0033】

【発明の効果】

20

以上説明した通り、本発明によれば、半導体基板上に形成されるインダクタンス素子において、インダクタンス素子を構成する帯状導電膜の下の基板表面に複数のPN接合を形成し、そのPN接合に逆バイアス電圧を印加して、基板表面が完全に空乏化するようにしたので、基板表面で発生する渦電流を抑えることができる。更に、基板表面の帯状導電膜による一次コイルと基板内部に発生する渦電流による二次コイルとの間の相互インダクタンスを低くすることができる。従って、インダクタンス素子の特性の損失を少なくすることができる。

【0034】

また、本発明によれば、半導体基板上に形成されるインダクタンス素子において、インダクタンスを構成する帯状導電膜の下の基板表面内部に分厚い絶縁領域を形成したので、基板内に発生する渦電流を抑えることができる。また、その厚い絶縁領域により、基板表面の帯状導電膜による一次コイルと基板内部に発生する渦電流による二次コイルとの間の相互インダクタンスを低くすることができる。従って、インダクタンス素子の特性の損失を少なくすることができる。 30

【0035】

また、本発明によれば、半導体基板上に形成されるインダクタンス素子において、インダクタンスを構成する帯状導電膜にスリットを形成したので、その帯状導電膜自体に発生する渦電流を抑えることができる。従って、インダクタンス素子の特性の損失を少なくすることができる。

【0036】

更に、本発明によれば、半導体基板上に形成されるインダクタンス素子において、インダクタンスを構成する帯状導電膜を、巻き線方向の導電率がそれと垂直方向の導電率より高い異方性導電率を有する材料で構成されるので、帯状導電膜自体に発生する渦電流を抑えることができる。従って、インダクタンス素子の特性の損失を少なくすることができる。 40

【図面の簡単な説明】

【図1】実施の形態例のインダクタンス素子の構造図である。

【図2】図1のインダクタンス素子に逆バイアス電圧を印加した時の詳細断面図である。

【図3】別の実施の形態例のインダクタンス素子の断面図である。

【図4】図3のインダクタンス素子の一部断面斜視図である。

【図5】別のインダクタンス素子の構造を示す平面図である。 50

【図6】公知例のインダクタンス素子の構造を示す図である。

【図7】図6の等価回路図である。

【符号の説明】

- |               |              |

|---------------|--------------|

| 1 0           | P型の半導体基板     |

| 1 2           | 配線用の絶縁膜      |

| 1 4           | N型の不純物領域     |

| 1 6           | 巻き線状の帯状導電膜   |

| 2 0           | 渦電流          |

| 3 0           | N型の埋込不純物領域   |

| 3 2           | N型の不純物領域     |

| 3 4           | スリット         |

| 4 0           | 厚い絶縁領域       |

| 1 6 0 ~ 1 6 7 | 異方性導電率をもつ配線膜 |

10

【図1】

実施の形態例のインダクタンス素子

【図2】

図1の実施の形態例のインダクタンス素子

【図3】

別の実施の形態例のインダクタンス素子

【図4】

【図5】

別のインダクタンス素子の例

【図6】

従来例

【図7】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

H01L 21/822

H01L 21/3205

H01L 23/52

H01L 27/04