(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0131090

(43) 공개일자 2015년11월24일

(51) 국제특허분류(Int. Cl.)

*H01L 29/66* (2006.01) *H01L 21/762* (2006.01)

*H01L 21/765* (2006.01) *H01L 21/8238* (2006.01)

*H01L 27/02* (2006.01)

(52) CPC특허분류

*H01L 29/6681* (2013.01)

*H01L 21/7624* (2013.01)

(21) 출원번호 10-2015-7027562

(22) 출원일자(국제) 2014년03월10일

심사청구일자 없음

(85) 번역문제출일자 2015년10월05일

(86) 국제출원번호 PCT/US2014/022263

(87) 국제공개번호 WO 2014/159160

국제공개일자 2014년10월02일

(30) 우선권주장

13/799,955 2013년03월13일 미국(US)

(71) 출원인

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(72) 발명자

양, 빈

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

리, 시아

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

치담바람, 피알

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(74) 대리인

특허법인 남엔드남

전체 청구항 수 : 총 24 항

(54) 발명의 명칭 더미 게이트들에 의해 분리된 연속 액티브 영역들을 이용한 MOS(METAL OXIDE SEMICONDUCTOR) 절연 방식들 및 이와 관련된 방법들

### (57) 요 약

상세한 설명에 개시된 실시예들은 더미게이트들에 의해 분리되는 연속 액티브 영역들을 이용한 MOS(metal oxide semiconductor) 절연 방식들을 포함한다. MOS 디바이스는 n-금속 또는 p-금속으로 설명되는 일함수를 갖는 물질로 형성되는 액티브 영역을 포함한다. 액티브 커먼트들은 유사한 일함수를 갖는 물질들을 이용하여 이 액티브 영역상에 형성된다. 액티브 커먼트들 사이에 더미 게이트를 포지셔닝함으로써 절연이 달성된다. 더미 게이트는 액티브 영역의 물질과 관련하여 상반되는 일함수를 갖는 물질로 만들어진다. 예를 들어, 액티브 영역이 p-금속 물질이었다면, 더미 게이트는 n-금속으로 만들어졌을 것이고, 액티브 영역이 n-금속 물질이었다면, 더미 게이트는 p-금속으로 만들어졌을 것이다

### 대 표 도 - 도5

(52) CPC특허분류

*H01L 21/765* (2013.01)

*H01L 21/823842* (2013.01)

*H01L 21/823878* (2013.01)

*H01L 27/0207* (2013.01)

*H01L 29/785* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

MOS(metal oxide semiconductor) 디바이스로서,

제 1 n-금속 또는 p-금속 일함수를 갖는 제 1 물질;

상기 제 1 물질을 포함하는 제 1 게이트;

상기 제 1 물질을 포함하는 제 2 게이트;

상기 제 1 게이트와 상기 제 2 게이트 사이에 포지셔닝되며 상기 제 1 물질의 일함수와 상반되는 일함수를 갖는

제 2 물질을 포함하는 더미 게이트; 및

각각의 게이트 밑의 게이트 유전체

를 포함하며, 상기 게이트 유전체는 대략 18 초과의 유전 상수( $k$ )를 포함하는, MOS 디바이스.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 물질은 n-금속 일함수를 갖는 물질을 포함하는, MOS 디바이스.

#### 청구항 3

제 2 항에 있어서,

상기 제 2 물질은 p-금속 일함수를 갖는 물질을 포함하는, MOS 디바이스.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 물질은 p-금속 일함수를 갖는 물질을 포함하는, MOS 디바이스.

#### 청구항 5

제 4 항에 있어서,

상기 제 2 물질은 n-금속 일함수를 갖는 물질을 포함하는, MOS 디바이스.

#### 청구항 6

제 1 항에 있어서,

CMOS(complementary MOS) 디바이스를 형성하기 위해 제 2 MOS 디바이스를 더 포함하며,

상기 제 2 MOS 디바이스는,

상기 제 2 물질을 포함하는 제 3 게이트;

상기 제 2 물질을 포함하는 제 4 게이트; 및

상기 제 3 게이트와 상기 제 4 게이트 사이에 포지셔닝되며 상기 제 2 물질을 포함하는 제 2 더미 게이트

를 포함하는, MOS 디바이스.

#### 청구항 7

제 6 항에 있어서,

상기 제 1 MOS 디바이스와 상기 제 2 MOS 디바이스 사이의 STI(shallow trench isolation)를 더 포함하는, MOS 디바이스.

#### 청구항 8

제 1 항에 있어서,

상기 더미 게이트는 상기 게이트 유전체상에 포지셔닝되며 상기 더미 게이트 아래에 절연 주입 존(zone)이 없는(lack), MOS 디바이스.

#### 청구항 9

제 1 항에 있어서,

상기 MOS 디바이스는 실질적으로 평면형 디바이스인, MOS 디바이스.

#### 청구항 10

제 1 항에 있어서,

상기 MOS 디바이스는 FinFET(fin-based field effect transistor) 디바이스인, MOS 디바이스.

#### 청구항 11

제 1 항에 있어서,

상기 MOS 디바이스는 반도체 다이에 통합되는, MOS 디바이스.

#### 청구항 12

제 1 항에 있어서,

셋톱 박스, 엔터테인먼트 유닛, 네비게이션 디바이스, 통신 디바이스, 고정 로케이션 데이터 유닛, 모바일 로케이션 데이터 유닛, 모바일 폰, 셀룰러 폰, 컴퓨터, 휴대용 컴퓨터, 데스크탑 컴퓨터, PDA(personal digital assistant), 모니터, 컴퓨터 모니터, 텔레비전, 튜너, 라디오, 위성 라디오, 뮤직 플레이어, 디지털 뮤직 플레이어, 휴대용 뮤직 플레이어, 디지털 비디오 플레이어, 비디오 플레이어, DVD(digital video disc) 플레이어, 및 휴대용 디지털 비디오 플레이어로 이루어진 그룹에서 선택되는 디바이스를 더 포함하며, 상기 디바이스는 상기 MOS 디바이스에 통합되는, MOS 디바이스.

#### 청구항 13

MOS(metal oxide semiconductor) 디바이스로서,

제 1 n-금속 또는 p-금속 일함수를 갖기 위한 제 1 수단;

상기 제 1 수단을 포함하는 제 1 게이트 수단;

상기 제 1 수단을 포함하는 제 2 게이트 수단;

상기 제 1 게이트 수단과 상기 제 2 게이트 수단 사이에 포지셔닝되며 상기 제 1 수단의 일함수와 상반되는 일함수를 갖는 제 2 수단을 포함하는 더미 게이트 수단; 및

각각의 게이트 수단 밑의 게이트 유전체

를 포함하며, 상기 게이트 유전체는 대략 18 초과의 유전 상수(k)를 포함하는, MOS 디바이스.

#### 청구항 14

MOS(metal oxide semiconductor) 디바이스를 형성하는 방법으로서,

제 1 n-금속 또는 p-금속 일함수를 갖는 제 1 물질을 제공하는 단계;

액티브 영역 상에 게이트 유전체를 형성하는 단계 – 상기 게이트 유전체는 대략 18 초과의 유전 상수(k)를 포함함 –;

상기 게이트 유전체 상에 상기 제 1 물질을 포함하는 제 1 게이트를 형성하는 단계;

상기 게이트 유전체 상에 상기 제 1 물질을 포함하는 제 2 게이트를 형성하는 단계;

상기 게이트 유전체 상에 더미 게이트를 형성하는 단계 –상기 더미 게이트는 상기 제 1 물질의 일함수와 상반되는 일함수를 갖는 제 2 물질을 포함함–; 및

상기 제 1 물질의 일함수와 상반되는 일함수를 갖는 제 2 물질을 포함하는 상기 더미 게이트를 상기 제 1 게이트와 상기 제 2 게이트 사이에 포지셔닝하는 단계

를 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 15**

제 14 항에 있어서,

상기 더미 게이트를 형성하는 단계는 절연 주입 존이 없는 로케이션에 상기 더미 게이트를 형성하는 단계를 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 16**

제 14 항에 있어서,

상기 게이트 유전체를 형성하는 단계는 대략 20-25의 유전 상수를 갖는 상기 게이트 유전체를 형성하는 단계를 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 17**

제 14 항에 있어서,

상기 제 1 물질은 n-금속 일함수를 갖는 물질을 포함하며, 상기 제 2 물질은 p-금속 일함수를 갖는 물질을 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 18**

제 17 항에 있어서,

상기 제 2 게이트를 접지에 연결하는 단계를 더 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 19**

제 17 항에 있어서,

상기 제 2 게이트 가까이에 소스를 형성하는 단계를 더 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 20**

제 14 항에 있어서,

상기 제 1 물질은 p-금속 일함수를 갖는 물질을 포함하며, 상기 제 2 물질은 n-금속 일함수를 갖는 물질을 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 21**

제 20 항에 있어서,

전압원에 상기 제 2 게이트를 연결하는 단계를 더 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 22**

제 20 항에 있어서,

상기 제 2 게이트 가까이에 소스를 형성하는 단계를 더 포함하는, MOS 디바이스를 형성하는 방법.

### **청구항 23**

제 14 항에 있어서,

CMOS 디바이스를 형성하기 위해 상기 제 1 MOS 디바이스와 함께 상기 제 2 MOS 디바이스를 형성하는 단계를 더 포함하는, MOS 디바이스를 형성하는 방법.

#### 청구항 24

제 23 항에 있어서,

상기 제 2 MOS 디바이스를 형성하는 단계는, 상기 제 2 MOS 디바이스내에 더미 게이트를 형성하는 단계를 포함하는, MOS 디바이스를 형성하는 방법.

### 발명의 설명

#### 기술 분야

[0001] 본 출원은 "METAL OXIDE SEMICONDUCTOR (MOS) ISOLATION SCHEMES WITH CONTINUOUS ACTIVE AREAS SEPARATED BY DUMMY GATES AND RELATED METHODS"란 명칭으로 2013년 3월 13일자로 출원된 미국 특허 출원 일련 번호 13/799,955를 우선권으로 주장하며, 이는 전체 인용에 의해 본원에 포함된다.

[0002] 본 개시물의 기술은 금속 산화물 반도체(MOS)에 관한 것이다.

#### 배경 기술

[0003] 모바일 통신 디바이스들은 현재 사회에서 보편화되었다. 이들 모바일 디바이스들의 보급은 이러한 디바이스들상에서 현재 인에이블되는 다수의 기능들에 의해 부분적으로 이루어졌다. 이러한 기능들에 대한 요구는 프로세싱 능력 요건들을 증가시키며 보다 강력한 배터리들에 대한 필요성을 발생시킨다. 모바일 통신 디바이스의 하우징에 대한 제한된 공간내에서, 배터리들은 프로세싱 회로와 경쟁된다. 이러한 요인 및 다른 요인들이 회로내에서의 전력 소비 및 지속된 컴포넌트들의 소형화에 기여한다. 컴포넌트들의 소형화는, 금속 산화물 반도체들(MOS)을 포함하는 프로세싱 회로에서의 트랜지스터들 및 다른 반응성 엘리먼트들을 포함하여 프로세싱 회로의 모든 양상들에 영향을 미친다.

[0004] 역사적으로 MOS 디바이스들은, 증가하는 소형화 노력들로 인해, 예를 들어, 0.25 마이크로미터( $\mu\text{m}$ ) 스케일로부터 0.13  $\mu\text{m}$ 을 거쳐 28 나노미터(nm) 스케일로 발전하는 이익을 얻었으며, 현재의 노력들은 20nm 스케일에 공들이고 있다. 이러한 반도체 소형화는 집적 회로(IC)에서 MOS 디바이스들에 의해 점유되는 풋프린트 면적을 감소시켰을 뿐만 아니라, 이러한 IC를 동작시키기 위해 요구되는 전력을 감소시키고 동시에 동작 속도들을 개선 시켰다. MOS 디바이스들이 나노미터 스케일, 예를 들어, 90nm 스케일로 감소됨에 따라, IC에서 MOS 디바이스들에 의해 점유되는 풋프린트 면적은 예상대로 감소되었다. 그러나 MOS 디바이스들은 상당히 빠른 속도로 동작할 수 없으며, 이는, 전류 메커니즘(즉, 전자들 또는 정공들)의 모빌리티가 또한 선형적으로 개선되지 않았고(이는 모빌리티는 전류 메커니즘의 유효 질량의 함수이기 때문임) 유효 질량이 소형화에 따라 변하지 않았기 때문이다.

[0005] 추가로, 기존 MOS 디바이스들은 디바이스들 사이의 원하는 절연을 제공하기 위한 액티브 엘리먼트들 사이의 STI(shallow trench isolation)에 의존한다. 그러나 소형화가 나노미터 스케일에 도달함에 따라, STI는 IC 내에서의 귀중한 공간을 차지한다.

[0006] MOS 디바이스들이 나노미터 스케일에서 동작하는 속도를 개선시키기 위해 시도되는 다양한 기술들이 구현되었다. 일 예는 전류 메커니즘의 모빌리티를 개선시키기 위해 MOS 채널 엘리먼트상에 스트레스를 도입하는 것을 포함한다. 스트레스 유도 엘리먼트들은 스트레스를 제공하기 위한 스트레스원(stressor)의 물리적 차원들에 의존한다. 즉, 모빌리티 개선을 위한 큰 스트레스를 도입하기 위해, 최소화 목적들과는 상충되는 물리적으로 큰 스트레스원이 사용된다. 부가적으로, STI는 스트레스원들의 형성을 방해하며, 원하는 스트레스를 제공하는데 이용가능한 스트레스원의 물리적 차원들을 감소시킨다.

[0007] 스트레스 유도 엘리먼트들의 감소와 연관된 감소된 성능을 방지하기 위해 제안된 적어도 하나의 솔루션은 연속 액티브 영역을 통한 STI 브레이크들의 제거였다. STI 브레이크를 대신, 컴포넌트들 사이에 더미 게이

트가 삽입되었다. 그러나 이러한 더미 게이트들에 의해 제공되는 절연은 STI에 제공되는 절연보다 상태가 나쁘며 그리고/또는 더 높은 게이트 바이어스를 요구하며, 이는 결국 비용을 증가시키고 디바이스의 풋프린트를 증가시키는 전력 레일 요구와 같은 자체 문제점들을 갖게 된다. 따라서, 열화 없이 인접한 MOS 디바이스들을 동작시킬 수 있는 효과적인 절연 기술이 요구된다.

### 발명의 내용

[0008] 상세한 설명에 개시되는 실시예들은 더미 게이트들에 의해 분리되는 연속 액티브 영역들을 이용한 MOS(metal oxide semiconductor) 절연 방식들을 포함한다. 관련된 방법들이 또한 개시된다. 예시적인 실시예에서, MOS 디바이스는, n-금속 또는 p-금속으로서 설명되는 일함수를 갖는 물질로 형성된 게이트를 갖는 액티브 영역을 포함한다. 액티브 커먼트들은 유사한 일함수를 갖는 게이트 물질들을 이용하여, 이 액티브 영역상에 형성된다. 액티브 커먼트들 사이에 더미 게이트를 포지셔닝함으로써 절연이 달성된다(effectuated). 더미 게이트는 액티브 영역의 게이트 물질에 대해 상반되는 일함수를 갖는 물질로 만들어진다. 예를 들어, 액티브 영역내의 게이트가 p-금속 물질이었다면, 더미 게이트는 n-금속으로 만들어졌을 것이고, 액티브 영역내의 게이트가 n-금속 물질이었다면, 더미 게이트는 p-금속으로 만들어졌을 것이다. 이런 구조를 통해 달성되는 절연 방식은 누설 전류의 양을 효과적으로 감소시키며 MOS 엘리먼트들의 동작 속도를 개선시킨다. 이 절연 방식은 또한 STI(shallow trench isolation) 폭 및 누설 전류에 의한 제한없이, MOS 디바이스의 기술 스케일링으로부터 예상되는 대응하는 속도 증가를 구현하면서, MOS 디바이스가 최소화되도록 허용한다. 폴리게이트 MOS 노력들과는 달리, 본원에 개시되는 특정 실시예들의 게이트 유전체 막들은 비교적 높은 유전 상수(k)를 가지며, 이에 따라 반대의(reverse) 일함수 타입 게이트들이 더미 게이트 밑에 배치된 절연 주입 존에 대한 필요성을 제거하면서 원하는 절연을 제공하도록 허용된다.

[0009] 이와 관련하여, 일 실시예에서, MOS 디바이스가 개시된다. MOS 디바이스는 제 1 n-금속 또는 p-금속 일함수를 갖는 제 1 물질을 포함한다. MOS 디바이스는 또한 제 1 물질을 포함하는 제 1 게이트를 포함한다. MOS 디바이스는 또한 제 1 물질을 포함하는 제 2 게이트를 포함한다. MOS 디바이스는 또한 제 1 게이트와 제 2 게이트 사이에 포지셔닝되며 제 1 물질의 일함수와 상반되는 일함수를 갖는 제 2 물질을 포함하는 더미 게이트를 포함한다. MOS 디바이스는 또한, 각각의 게이트 밑에 게이트 유전체를 포함하며, 여기서 게이트 유전체는 대략 18 초과의 유전 상수(k)를 포함한다.

[0010] 다른 예시적 실시예에서, MOS 디바이스가 개시된다. MOS 디바이스는 제 1 n-금속 또는 p-금속 일함수를 갖는 제 1 수단을 포함한다. MOS 디바이스 또한 제 1 수단을 포함하는 제 1 게이트 수단을 포함한다. MOS 디바이스는 또한 제 1 수단을 포함하는 제 2 게이트 수단을 포함한다. MOS 디바이스는 또한, 제 1 게이트 수단과 제 2 게이트 수단 사이에 포지셔닝되며 제 1 수단의 일함수와 상반되는 일함수를 갖는 제 2 수단을 포함하는 더미 게이트 수단을 포함한다. MOS 디바이스는 또한 각각의 게이트 수단 밑에 게이트 유전체를 포함하며, 여기서 게이트 유전체는 대략 18 초과의 유전 상수(k)를 포함한다.

[0011] 다른 예시적 실시예에서, MOS 디바이스를 형성하는 방법이 개시된다. 방법은 제 1 n-금속 또는 p-금속 일함수를 갖는 제 1 물질을 제공하는 단계를 포함한다. 방법은 또한 액티브 영역상에 게이트 유전체를 형성하는 단계를 포함하며, 게이트 유전체는 대략 18 초과의 유전 상수(k)를 포함한다. 방법은 또한 게이트 유전체 위에 제 1 물질을 포함하는 제 1 게이트를 형성하는 단계를 포함한다. 방법은 또한 게이트 유전체 위에 더미 게이트를 형성하는 단계를 포함하며, 여기서 더미 게이트는 제 1 물질의 일함수와 상반되는 일함수를 갖는 제 2 물질을 포함한다. 방법은 또한 제 1 물질의 일함수와 상반되는 일함수를 갖는 제 2 물질을 포함하는 더미 게이트를 제 1 게이트와 제 2 게이트 사이에 포지셔닝하는 단계를 포함한다.

### 도면의 간단한 설명

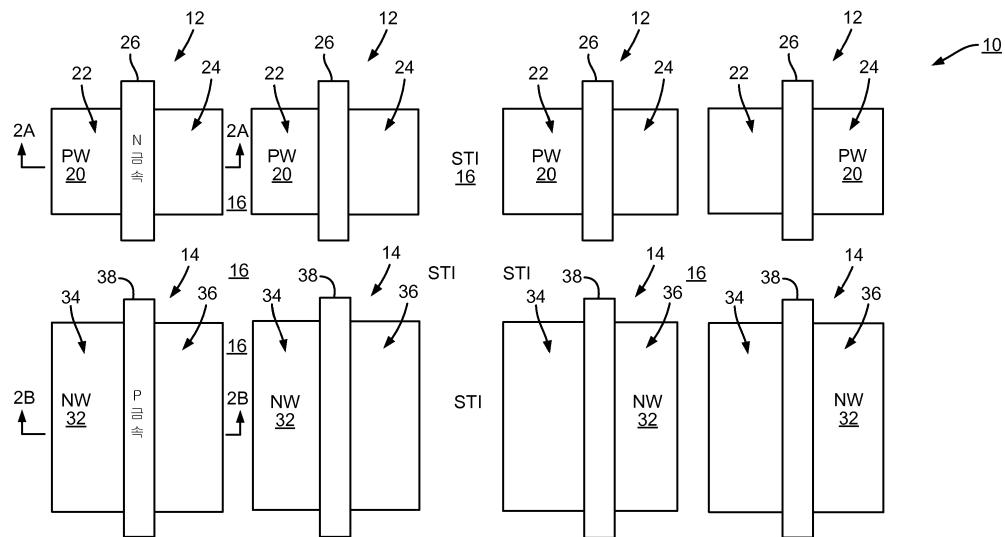

[0012] 도 1은 액티브 반도체 커먼트들을 절연시키기 위해 STI(shallow trench isolation)를 갖는 예시적인 통상적 CMOS(complementary MOS(metal oxide semiconductor))의 간략화된 상부 평면도이다;

[0013] 도 2a는 도 1의 라인 2A-2A를 따라 취한 n-금속 MOS(nMOS)의 횡단면도이다;

[0014] 도 2b는 도 1의 라인 2B-2B를 따라 취한 p-금속 MOS(pMOS)의 횡단면도이다;

[0015] 도 3은 전계 효과 트랜지스터(FET)을 절연시키는데 이용되는 더미 게이트 및 STI 브레이크(break)를 갖는 연속 액티브 영역을 갖게 형성된 예시적인 통상적 CMOS의 간략화된 상부 평면도이다;

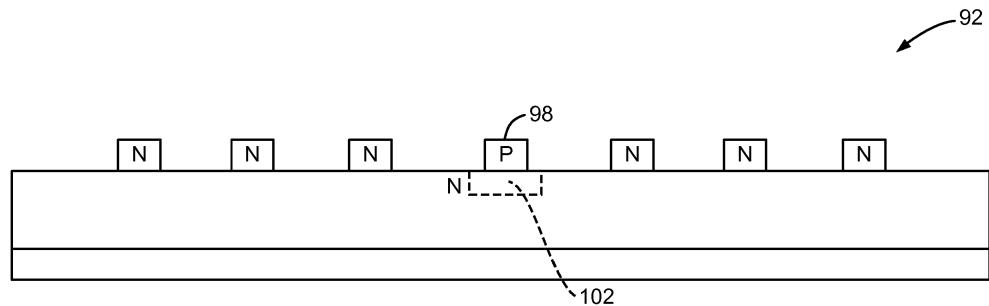

[0016] 도 4는 FET들을 절연시키는데 이용되는 더미 게이트를 갖는 연속 액티브 영역을 갖게 형성된 예시적인 통상적 CMOS의 간략화된 상부 평면도이다;

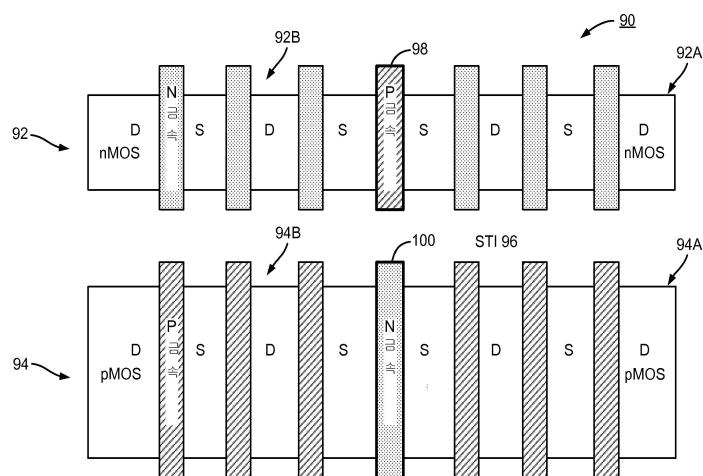

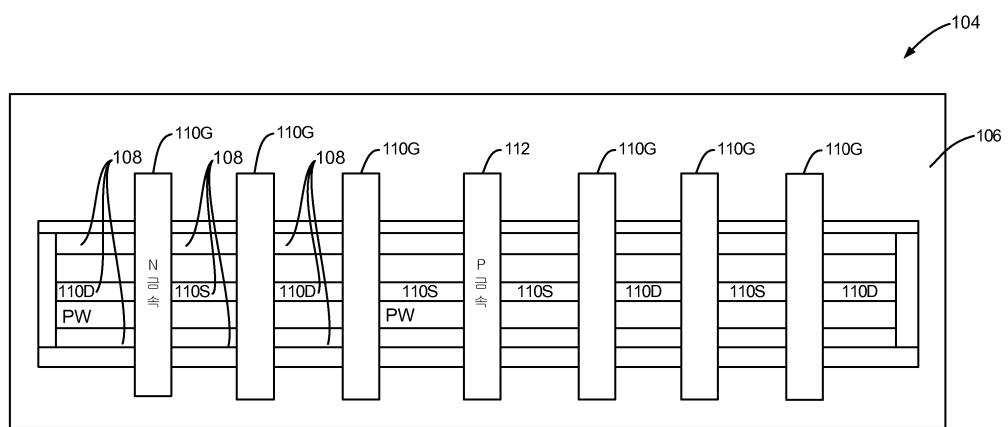

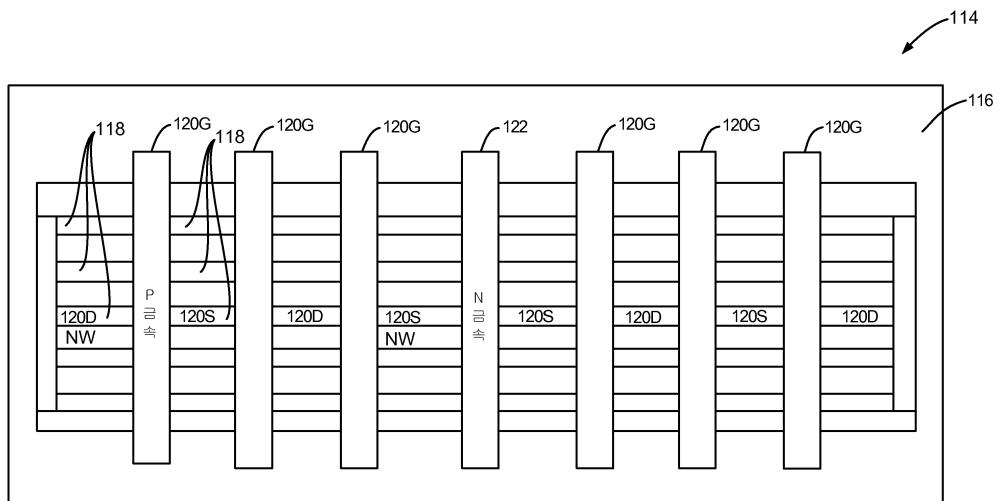

[0017] 도 5는 본 개시물의 예시적인 실시예에 따라, 연속 액티브 영역으로 형성되는 반대의(reverse) 일함수 더미 게이트를 갖는 예시적인 CMOS 디바이스의 간략화된 상부 평면도이다;

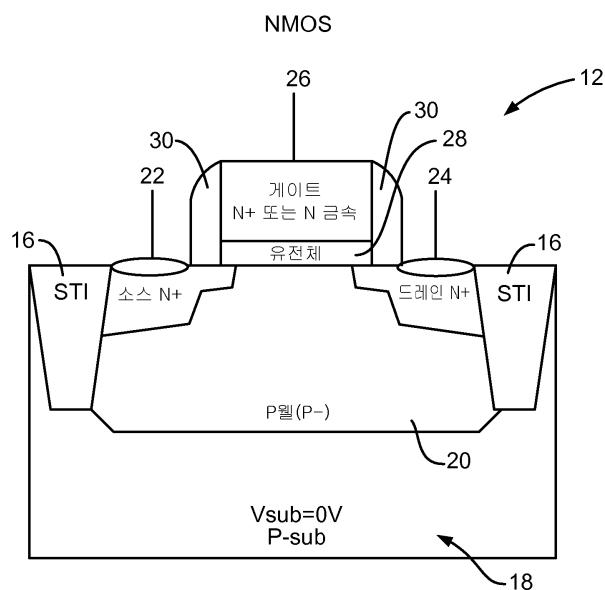

[0018] 도 6은 일반적으로 평면형인 구성을 갖는 도 4의 CMOS 디바이스내의 nMOS 디바이스에 대한 실시예의 획단면도이다;

[0019] 도 7a 및 도 7b는 본 개시물의 예시적 실시예에 따라, 더미 게이트들을 갖는 FinFET(fin-based field effect transistor) MOS 디바이스들의 간략화된 상부 평면도들이다; 그리고

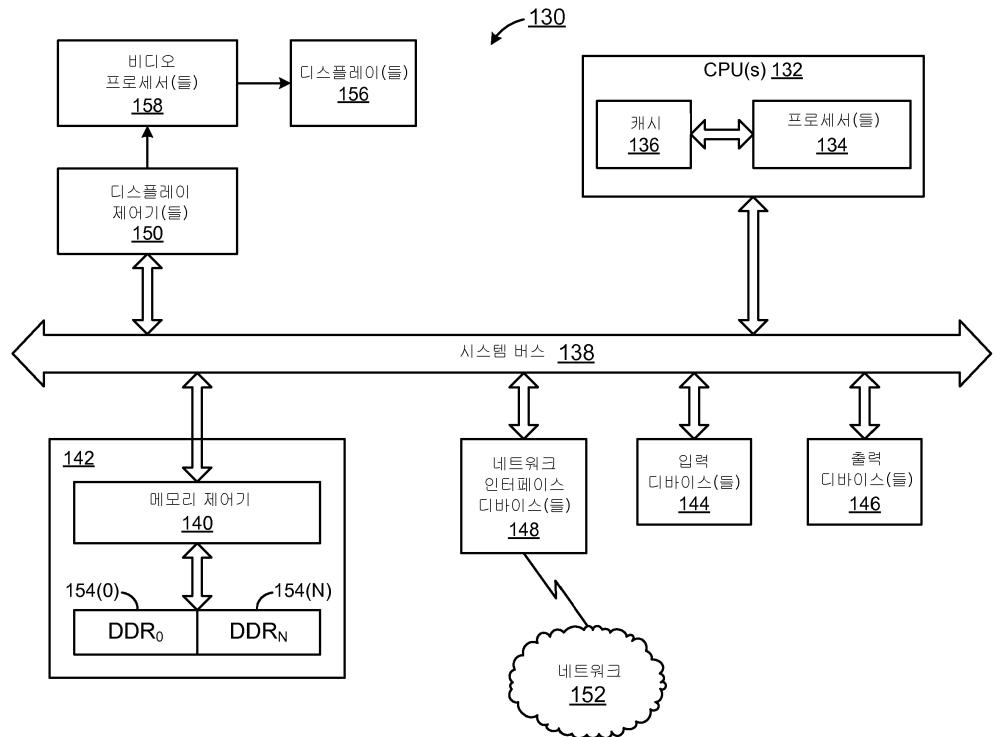

[0020] 도 8은 도 5의 CMOS 디바이스들을 포함할 수 있는 예시적인 프로세서-기반 시스템의 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0013] [0021] 이제 도면의 도들을 참조로, 본 개시물의 몇 개의 예시적 실시예들이 설명된다. 본원에서 예시적인"이라는 용어는 "예, 예증 또는 예시로서 기능하는"을 의미하도록 이용된다. "예시적인"으로서 본원에 설명된 임의의 실시예가 반드시 다른 실시예들보다 선호되거나 유리한 것으로 해석되는 것은 아니다.

[0014] [0022] 상세한 설명에서 개시되는 실시예들은 더미 게이트들에 의해 분리되는 연속 액티브 영역들을 이용하는 MOS(metal oxide semiconductor) 절연 방식들을 포함한다. 관련된 방법들이 또한 개시된다. 예시적인 실시예에서, MOS 디바이스는 n-금속 또는 p-금속인 것으로서 설명되는 일함수를 갖는 물질로 형성된 게이트를 갖는 액티브 영역을 포함한다. 액티브 커먼트들은 유사한 일함수를 갖는 게이트 물질들을 이용하여 이 액티브 영역 상에 형성된다. 절연은 액티브 커먼트들 사이에 더미 게이트를 포지셔닝함으로써 달성된다. 더미 게이트는 액티브 영역의 게이트 물질에 대해 상반되는 일함수를 갖는 물질로 만들어진다. 예를 들어, 액티브 영역내의 게이트가 p-금속 물질이었다면, 더미 게이트는 n-금속으로 만들어졌을 것이고 액티브 영역내의 게이트가 n-금속 물질이었다면, 더미 게이트는 p-금속으로 만들어졌을 것이다. 이런 구조를 통해 달성되는 절연 방식은 누설 전류의 양을 효과적으로 감소시키며 MOS 엘리먼트들의 동작 속도를 개선시킨다. 이 절연 방식은 또한, STI(shallow trench isolation) 폭 및 누설 전류에 의한 제한없이, MOS 디바이스의 기술 스케일링으로부터 예상되는 대응하는 속도 증가를 구현하면서, MOS 디바이스가 최소화되도록 허용한다. 폴리게이트 MOS 노력들과는 달리, 본원에 개시되는 특정 실시예들에서의 게이트 유전체 막들은 비교적 높은 유전 상수(k)를 가지며, 이에 따라 반대의(reverse) 일함수 타입 더미 게이트들이 더미 게이트 밑에 배치된 절연 주입 존에 대한 필요성을 제거하면서 원하는 절연을 제공하도록 허용된다.

[0015] [0023] 본 개시물에 따른 하나 또는 그 초과의 더미 게이트들을 이용하는 MOS 디바이스의 예시적인 실시예들을 처리하기 이전에, CMOS(complementary MOS) 디바이스내에서의 통상적 절연 프로세스들에 대한 간단한 개요가 아래에서 도 1-4를 참조로 제공된다. 도 1-4가 CMOS 디바이스들을 다루지만, CMOS 디바이스는 n-금속 일함수(즉, nMOS)를 갖는 MOS 디바이스 및 p-금속 일함수(즉, pMOS)를 갖는 MOS 디바이스로 만들어진다는 것이 인식되어야 한다. 이들 통상적인 절연 프로세스들의 설명은 더미 게이트들을 이용하는 실시예들의 설명을 돋기 위해 제공되며 도 5-7b와 관련하여 하기에서 논의된다.

[0016] [0024] 이와 관련하여, 도 1은 통상적인 CMOS 디바이스(10)의 블록도이다. CMOS 디바이스(10)는 하나 또는 그 초과의 nMOS 전계 효과 트랜지스터(FET)들(12) 및 하나 또는 그 초과의 pMOS FET들(14)로 형성된다. 각각의 FET(12, 14)은 STI(16)에 의해 다른 FET들(12, 14)과 분리된다.

[0017] [0025] 도 2a에서 더 잘 예시되는 것처럼, nMOS FET(12)는, 예시적인 실시예에서 실리콘 기판(18)상에 형성된다. 웨(20)은 기판(18)내에 형성되며, 예시적인 실시예에서, 웨(20)은 p-타입 페르미 에너지 레벨을 가지며(페르미 레벨들은 본원에서, 실리콘에서의 P 타입 또는 N 타입 도편트에 의해 유도되는, 실리콘 밴드 캡 내의 결합 에너지 밴드로 지칭됨) 본원에서 pwell(또는 pw)로 지칭될 수 있다. nMOS FET(12)는 소스(22), 드레인(24) 및 게이트(26)를 포함한다. 소스(22) 및 드레인(24)은 웨(20) 내에 형성되며 n+ 타입 페르미 에너지 레벨(즉, 전도 밴드에 매우 가까운 페르미 에너지 레벨)을 가질 수 있다. 게이트(26)는 웨(20) 위에 형성되며 산화물 층 등일 수 있는 게이트 유전체(28)에 의해 웨(20)과 분리된다. 게이트(26)는 n-금속 일함수를 갖는 물질로 형성된다. 부가적으로, 게이트(26)는 게이트(26) 양측(either side)상에 스페이서들(30)을 가질 수 있다. nMOS FET(12)는 소스(22), 드레인(24), 및 게이트(26)에 대한 전기적 콘택들(미도시)을 포함한다.

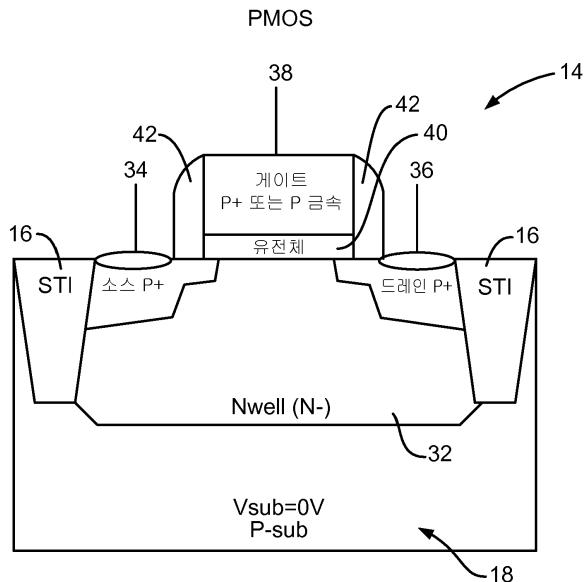

[0018] [0026] 마찬가지로, 도 2b에 예시된 것처럼, pMOS FET(14)은, 예시적인 실시예에서 실리콘 기판일 수 있는 기판

(18) 상에 형성된다. 웨(32)은 기판(18) 내에 형성되며, 예시적인 실시예에서, 웨(32)은 n-타입 페르미 에너지 레벨을 가지며 본원에서 nwell(또는 nw)로 지칭될 수 있다. pMOS FET(14)은 소스(34), 드레인(36) 및 게이트(38)를 포함한다. 소스(34) 및 드레인(36)은 웨(32) 내에 형성되며 p+ 타입 페르미 에너지 레벨을 가질 수 있다. 게이트(38)는 웨(32) 위에 형성되며 산화물 층 동일 수 있는 게이트 유전체(40)에 의해 웨(32)과 분리된다. 게이트(38)는 p-금속 일함수를 갖는 물질로 형성된다. 부가적으로, 게이트(38)는 게이트(38) 양측 상에 스페이서들(42)을 가질 수 있다. pMOS FET(14)는 소스(34), 드레인(36) 및 게이트(38)에 대한 전기적 콘택들(미도시)을 포함한다.

[0019] [0027] 도 1을 참조로 그리고 위에서 주목한 바와 같이, FET들(12, 14)은 STI(16)에 의해 서로 분리된다. STI(16)는 FET들(12, 14) 각각에 대한 효과적인 전기 절연을 제공한다. 통상적 구성들에서, STI(16)와 같은 STI 브레이크들에 의해 제공되는 절연은 개선된 스케일링 기술(Advanced Scaling Technology)의 경우  $10 \text{ pA}/\mu\text{m}$  범위내이다. STI(16)와 같은 STI 브레이크들은 다수의 예시들에서의 허용가능한 절연을 제공하지만, STI 브레이크들의 사용은 연속 제조 프로세스에 지장을 주며 엘리먼트들 사이에 브레이크를 생성하며, 이는 칩 크기를 증가시키고 구동 전류를 감소시며, 이는 결국 속도를 감소시키고 전력 소비를 증가시킨다.

[0020] [0028] 도 1-2b는 CMOS 디바이스(10)에 초점을 두었지만, 동일한 개념들 및 문제점들이 엄격한(strictly) nMOS 디바이스 또는 엄격한 pMOS 디바이스와 같은 다른 타입들의 MOS 디바이스들에 또한 적용가능하다는 것이 인식되어야 한다. 또한, CMOS 디바이스(10)가 평면형 디바이스인 것으로 예시되지만, 동일한 기술들이 FinFET 디바이스들에 또한 이용된다. FinFET은, 실리콘 기판 또는 SOI(silicon on insulator) 기판상에 구축되는 비평면형, 이중- 또는 삼중-게이트 트랜지스터를 설명하는데 이용되는 용어이다. FinFET의 특색있는 특징은, 전도성 채널이 디바이스의 채널을 형성하는 얇은 실리콘("fin") 부근에 있다는 것이다. 편의 길이(소스로부터 드레인의 방향으로 측정됨)는 디바이스의 유효 채널 길이를 결정한다.

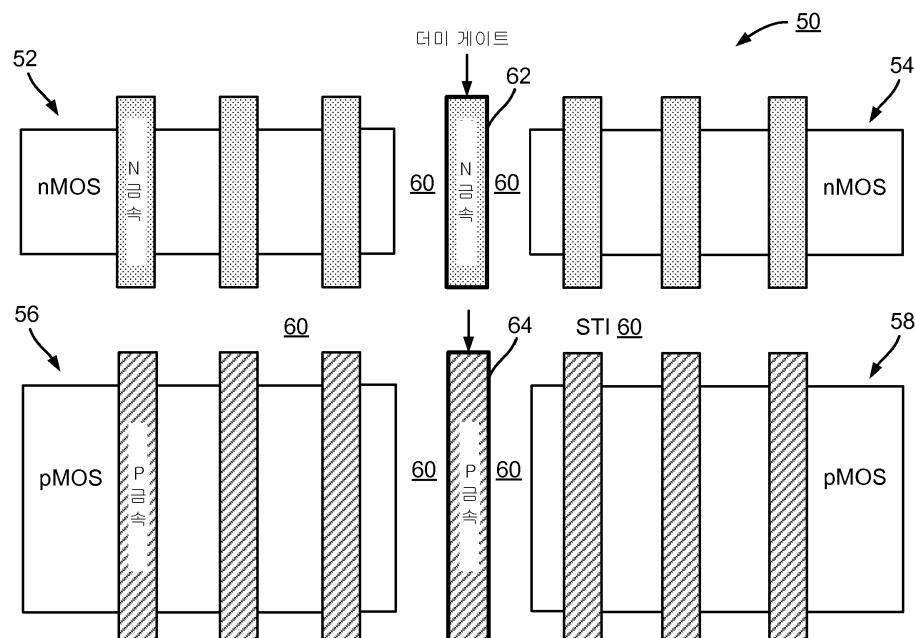

[0021] [0029] 도 3에 예시된 대안적인 통상적 접근방식은 STI를 더미 게이트와 결합한다. 이와 관련하여, 도 3에 예시된 것처럼, CMOS 디바이스(50)는 기판(미도시)상에 형성된다. CMOS 디바이스(50)는 제 1 pMOS FET(56) 및 제 2 pMOS FET(58)뿐만 아니라 제 1 nMOS FET(52) 및 제 2 nMOS FET(54)를 포함한다. FET들(52, 54, 56, 58)은 STI(60)에 의해 서로 분리된다. 부가적으로, 더미 게이트(62)는 nMOS FET들(52, 54) 사이에 포지셔닝된다. 더미 게이트(62)는 n-금속 일함수를 갖는다. 유사하게, 더미 게이트(64)는 pMOS FET들(56, 58) 사이에 포지셔닝된다. 더미 게이트(64)는 p-금속 일함수를 갖는다. 따라서, 더미 게이트들(62, 64)의 일함수는 더미 게이트를 분리하는 FET들(52, 54 또는 56, 58)의 일함수에 대응한다. 다시, STI(60) 및 더미 게이트들(62, 64)의 사용은 (예를 들어,  $\sim 10 \text{ pA}/\mu\text{m}$  범위내의) 허용가능한 절연을 제공하지만, STI(60)의 사용은 연속 액티브 영역에 브레이크를 도입한다. 앞서 주목된 바와 같이, STI(60)는 전류 메커니즘의 원하는 모빌리티를 달성하는데 충분한 크기의 스트레스원들을 생성하는 능력에 영향을 미치며, CMOS 디바이스(50)의 성능은 더 작은 크기들에서(예를 들어, 28 나노미터 또는 이 미만의 스케일에서)는 개선되지 않는다.

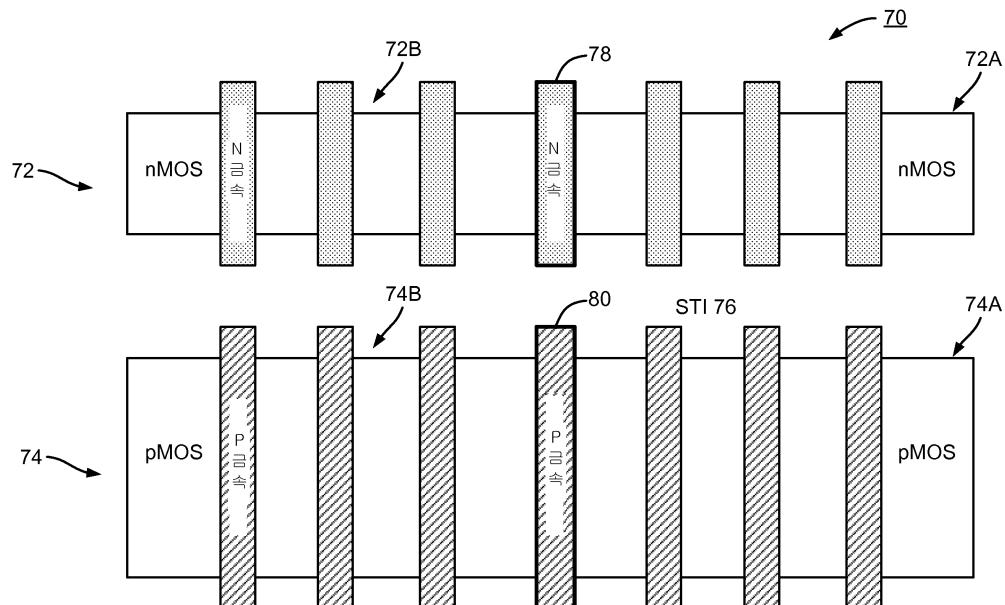

[0022] [0030] 또 다른 대안적인 통상적 접근방식이 도 4에 예시된다. 도 4는 연속 액티브 영역 방식을 통해 형성되는 CMOS 디바이스(70)를 예시한다. 특히, CMOS 디바이스(70)는 nMOS FET들(72A, 72B)(총칭하여 72) 및 pMOS FET들(74A, 74B)(총칭하여 74)를 포함한다. nMOS FET(72)는 STI(76)에 의해 pMOS FET(74)와 분리된다. 도 3의 CMOS 디바이스(50)와 달리, nMOS FET(72A)는 STI(76)에 의해 nMOS FET(72B)와 분리되지 않는다. 오히려, nMOS FET(72A) 및 nMOS FET(72B)는 연속 액티브 영역으로 형성되며 오직 더미 게이트(78)에 의해서만 분리된다. 더미 게이트(78)는 n-금속 일함수를 갖는다. 유사하게, pMOS FET(74A)는 STI(76)에 의해 pMOS FET(74B)와 분리되지 않는다. 오히려, pMOS FET(74A) 및 pMOS FET(74B)는 연속 액티브 영역으로 형성되며 오직 더미 게이트(80)에 의해서만 분리된다. 더미 게이트(80)는 p-금속 일함수를 갖는다. 이 예시적인 실시예는 연속 액티브 영역 방식으로 형성되는 장점을 갖지만, 더미 게이트들(78, 80)은 흔히 쌍을 이룬 FET들(72A, 72B) 또는 쌍을 이룬 FET들(74A, 74B) 간의 적절한 절연을 제공하지 못한다. 예를 들어, 20nm 스케일에 대한 전형적인 nMOS 구성들에서, 디바이스들은 매우 낮은 임계치 디바이스에 대해  $10 \text{ nA}/\mu\text{m}$ 를 가지며, 이는 STI 스타일 디바이스의 누설보다 대략 천 배 더 큰 것이다. 마찬가지로, 유사한 디바이스는 표준 임계 디바이스에 대해 대략  $350 \text{ pA}/\mu\text{m}$ 를 가지며, 이는 STI 스타일 디바이스의 누설보다 대략 35배 더 큰 것이다. 따라서, 하나의 nMOS FET(72A)로부터 nMOS FET(72B)으로(그리고 마찬가지로 pMOS FET(74A)로부터 pMOS FET(74B)으로) 더미 게이트(78)에 걸쳐 전류가 누설되며, 이는 CMOS 디바이스(70)의 성능을 저하시킨다. 누설 전류를 해결하기 위한 한가지 솔루션은 더미 게이트들(70, 80)에 대한 게이트 바이어스를 증가시키는 것이다. 예를 들어, nMOS FET(72)에서, 보통의 게이트 전압은 0V이지만, 전류 누설을 감소시키기 위해서는, 더미 게이트(78)에  $-0.5\text{V}$ 가 인가될 수 있다. 이러한 게이트 바이어스의 사용은 여분의 외부 전원장치를 요구하며, 이는 결국 디바이스의 풋프린트를 증가시키고 회

로 복잡도를 증가시킨다. 마찬가지로,  $-0.5\text{ V}$  게이트 바이어스로,  $V_{gs}$ 는  $V_{dd}$ (예를 들어,  $0.5\text{ V}$ )에 도달할 수 있으며, 이는 얇은 게이트 산화물들에 대해서는 너무 높고, 게이트의 불필요한 마모(wear)를 야기할 수 있다. 유사하게, pMOS FET(74)에서, 정상적으로 절연없이,  $V_g = 0\text{ V}$ 이지만 누설 전류를 감소시키기 위해서,  $V_g$ 는  $V_{dd}$  또는  $0.5\text{ V}$ 로 설정될 수 있다. 다시, 이 게이트 바이어스는 여분의 외부 전원장치를 요구하며 그리고/또는 게이트 산화물 신뢰도 문제를 야기한다. 어느 경우든, 더 작은 설계 스케일들에서 CMOS 디바이스(70)가 차선이다.

[0023]

[0031] 상반되는 일함수를 갖는 물질로 만들어진 절연 더미 게이트로 더미 게이트(78, 80)를 교체함으로써 통상적 디바이스들의 차선의 성능(예를 들어, 속도, 누설 전류 등)에 대한 솔루션이 발견되었다. 즉, FET가 n-금속 일함수를 가지면, 더미 게이트는 p-금속 일함수를 갖는다. 대안적으로, FET들이 p-금속 일함수를 가지면, 더미 게이트는 n-금속 일함수를 갖는다. 더미 게이트 물질 선택은 여분의 외부 전원장치의 요건 없이 절연 개선을 허용하며 이에 따라 회로 내 영역이 보존된다. 마찬가지로, 이를 반도체 디바이스들을 생성하는 프로세스는 통상적으로 높은-k/금속 게이트 프로세스에서의 과도한 변화들을 요구하지 않는다. 오히려, 새로운 더미 게이트에 대해, 반대 타입 게이트 마스크(CMOS에서 사용됨)는 더미 게이트를 배치하는데 이용된다. 테스팅은, 더미 게이트의 일함수를 반대로함으로써, 연속 액티브 영역 방식을 이용하는 CMOS 디바이스를 형성하는 능력을 계속 보존하면서 허용가능한 절연 레벨들이 달성됨이 도시된다. 즉, 이 예에서,  $10\text{ pA}/\mu\text{m}$  범위내의 절연이 제공된다. ON 상태에서 이용가능한 전류 또한 증가되는데, 이는 해당 영역이 FET들내에서 전류 메커니즘들의 모빌리티를 증가시키는 스트레스원 엘리먼트들의 생성을 위해 보존된다는 사실로 인한 것이다. 개선된 절연과 결합된 연속 액티브 영역 방식의 사용은 추가의 최소화 및 더 큰 설계 유연성을 허용한다.

[0024]

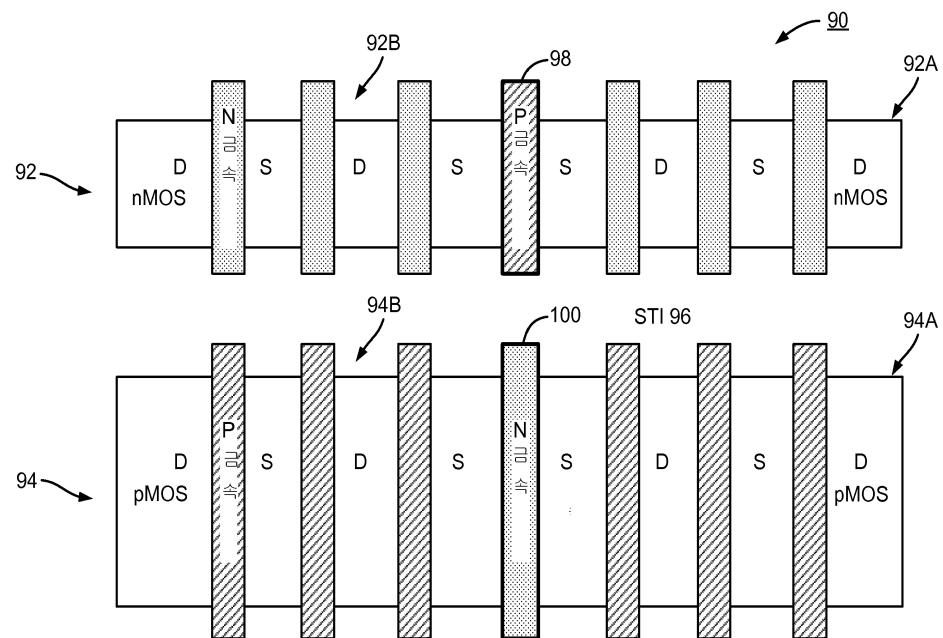

[0032] 이와 관련하여, 반대의 일함수들을 갖는 더미 게이트들을 이용하는 CMOS 디바이스(90)의 제 1 예시적 실시예가 도 5에 제공된다. 예시된 것처럼, CMOS 디바이스(90)는 연속 액티브 영역 방식을 통해 형성된다. 특히, CMOS 디바이스(90)는 nMOS FET들(92A, 92B)(총칭하여 92) 및 pMOS FET들(94A, 94B)(총칭하여 94)를 포함한다. nMOS FET(92)은 STI(96)에 의해 pMOS FET(94)와 분리된다. 도 4의 CMOS 디바이스(70)에 따라, nMOS FET(92A)은 STI(96)에 의해 nMOS FET(92B)와 분리되지 않는다. 오히려, nMOS FET(92A)와 nMOS FET(92B)는 연속 액티브 영역으로 형성되며 오직 더미 게이트(98)에 의해서만 분리된다. 더미 게이트(98)는 p-금속 일함수를 가지며 이에 따라 그가 이용되는 MOS 디바이스와 상반되는 일함수를 갖는다. 다른 식으로 말하면, 더미 게이트(98)는 반대의 일함수를 갖는다. 유사하게, pMOS FET(94A)는 STI(96)에 의해 pMOS FET(94B)와 분리되지 않는다. 오히려, pMOS FET(94A) 및 pMOS FET(94B)는 연속 액티브 영역으로 형성되며 오직 더미 게이트(100)에 의해서만 분리된다. 더미 게이트(100)는 n-금속 일함수를 가지며 이에 따라 그가 이용되는 MOS 디바이스와 상반되는 일함수를 갖는다. 다른 식으로 말하면, 더미 게이트(100)는 반대의 일함수를 갖는다. 도시되지 않았지만, 더미 게이트들(98, 100) 각각은 게이트 유전체들(28, 40)과 유사하게 게이트 유전체상에 포지셔닝된다는 것을 인식해야 한다. 예시적인 실시예에서, CMOS 디바이스(90)의 게이트 유전체는 높은 유전 상수( $k$ )를 갖는다. 예시적인 실시예에서,  $k$ 는 18 이상이며, 추가의 예시적 실시예에서,  $k$ 는 대략 20-25이다.

[0025]

[0033] 계속해서 도 5를 참조로, 예시적인 실시예에서, 더미 게이트(98)는  $V_{ss}$ 에 연결되며 더미 게이트(100)는  $V_{dd}$ 에 커플링된다. 주목된 것처럼, 반대의 일함수는 CMOS 디바이스(90)의 제조시 연속 액티브 영역 방식을 이용하는 제조자의 능력을 보존하면서, 허용가능한 절연 레벨들을 제공한다. 더미 게이트들(98, 100) 가까이에 소스를 배열함으로써, 절연 누설이 추가로 감소될 수 있다.

[0026]

[0034] 도 5는 nMOS FET(92) 및 pMOS FET(94) 둘 다를 갖는 CMOS 디바이스(90)를 예시하지만, 본 개시물의 개념들이 단지 nMOS 디바이스들만을 그리고/또는 단지 pMOS 디바이스들만을 포함하는 MOS 디바이스들에 통합될 수 있다는 것이 인식되어야 한다.

[0027]

[0035] 또한, 더미 게이트들(98, 100) 아래 절연 주입 존의 부재(absence)가 주목된다. 종래 기술들, 특히 예컨대 폴리게이트 기술들은, 더미 게이트에 의해 제공되는 절연을 개선시키기 위해 더미 게이트들 밑에 이러한 절연 주입 존(즉, 특정 타입의 도핑으로 주입된 존)을 이용했을 것이다. 이러한 절연 주입 존들은 절연 크기를 증가시키며, 일반적으로, 동일 레벨의 절연을 달성하지 못한다. nMOS 디바이스(92)의 횡단면도가 도 6에 제공되며, 이는 더미 게이트(98) 밑에 절연 주입 존이 없는 존(102)을 갖는다. pMOS 디바이스(94) 또한 더미 게이트(100) 아래에 절연 주입 존을 갖지 않는다는 것이 인식되어야 한다.

[0028]

[0036] 도 5의 CMOS 디바이스(90)는 잘 이해되는 바와 같이 일반적으로 평면형 구성을 갖지만, 본 개시물의 개념들이 이로 제한되는 것은 아니며 FinFET 설계로 확장될 수 있다. 도 7a 및 도 7b는 FinFET들에서 반대의 금속 더미 게이트들에 대한 2가지 버전들을 예시한다. 특히, 도 7a는, 핀들(108)이 게이트들(110G)을 따라 수직

으로 포지셔닝되는 액티브 영역(106)을 갖는 FinFET nMOS 디바이스(104)가 예시된다. FinFET nMOS 디바이스(104)는 소스들(110S) 및 드레인들(110D)을 더 포함한다. FinFET nMOS 디바이스(104)에서, 액티브 디바이스 게이트의 일 함수는 n-금속이며 대응하는 더미 게이트(112)는 p-금속 일함수를 갖는다. 더미 게이트(112) 가까이에 소스를 배열함으로써, 절연 누설이 추가로 감소될 수 있다.

[0029] 도 7a의 FinFET nMOS 디바이스(104)와 대조적으로, FinFET pMOS 디바이스(114)가 도 7b에 예시된다. FinFET pMOS 디바이스(114)는 액티브 영역(116) 및 펀들(118)을 포함한다. 마찬가지로, FinFET pMOS 디바이스(114)는 드레인들(120D), 소스들(120S) 및 게이트들(120G)을 포함한다. FinFET pMOS 디바이스(114)의 액티브 영역(116)은 p-금속 일함수를 가지며 대응하는 더미 게이트(122)는 n-금속 일함수를 갖는다. 더미 게이트(122) 가까이에 소스를 배열함으로써, 절연 누설이 추가로 감소될 수 있다.

[0030] [0038] nMOS 디바이스(104) 및 pMOS 디바이스(114)는 원활 경우 CMOS 디바이스에 어셈블리될 수 있다. 다시, 주입 절연 존의 부재 및 높은 게이트 유전체는 크기들이 점점 더 작아짐에도 속도가 개선되게 허용한다.

[0031] [0039] 본원에 개시된 실시예들에 따라 연속 액티브 영역들을 이용하는 CMOS 절연 방식들이 임의의 프로세서-기반 디바이스에 제공되거나 이에 통합될 수 있다. 제한 없이, 예들은 셋톱 박스, 엔터테인먼트 유닛, 네비게이션 디바이스, 통신 디바이스, 고정 로케이션 데이터 유닛, 모바일 로케이션 데이터 유닛, 모바일 폰, 셀룰러 폰, 컴퓨터, 휴대용 컴퓨터, 데스크탑 컴퓨터, PDA(personal digital assistant), 모니터, 컴퓨터 모니터, 텔레비전, 투너, 라디오, 위성 라디오, 뮤직 플레이어, 디지털 뮤직 플레이어, 휴대용 뮤직 플레이어, 디지털 비디오 플레이어, 비디오 플레이어, DVD(digital video disc) 플레이어, 및 휴대용 디지털 비디오 플레이어를 포함한다.

[0040] 이와 관련하여, 도 8은 CMOS 디바이스(90) 또는 MOS 디바이스들(92, 94, 104, 114)과 같은 CMOS 디바이스를 이용할 수 있는 프로세서-기반 시스템(130)의 예를 예시한다. 이 예에서, 프로세서 기반 시스템(130)은 하나 또는 그 초과의 CPU(central processing unit)들(132)을 포함하며, 이 각각은 하나 또는 그 초과의 프로세서들(134)을 포함한다. CPU(들)(132)는 일시적으로 저장된 데이터에 대한 신속한 액세스를 위해 프로세서(들)(134)에 커플링되는 캐시 메모리(136)를 가질 수 있다. CPU(들)(132)는 시스템 버스(138)에 커플링되며 프로세서-기반 시스템(130)에 포함된 마스터 디바이스들 및 슬레이브 디바이스들에 상호커플링될 수 있다. 잘 알려진 것처럼, CPU(들)(132)는 시스템 버스(138)를 통해 어드레스, 제어, 및 데이터 정보를 교환함으로써 이 다른 디바이스들과 통신한다. 예를 들어, CPU(들)(132)는 메모리 제어기(140)에 버스 트랜잭션 요청들을 통신할 수 있다. 도 8에는 예시되지 않았지만, 다수의 시스템 버스들(138)이 제공될 수 있으며, 여기서 각각의 시스템 버스(138)는 서로 다른 패브릭을 구성한다.

[0041] 다른 디바이스들이 시스템 버스(138)에 연결될 수 있다. 도 8에 예시된 것처럼, 이 디바이스들은, 예들로서, 메모리 시스템(142), 하나 또는 그 초과의 입력 디바이스들(144), 하나 또는 그 초과의 출력 디바이스들(146), 하나 또는 그 초과의 네트워크 인터페이스 디바이스들(148), 및 하나 또는 그 초과의 디스플레이 제어기들(150)을 포함한다. 입력 디바이스(들)(144)는, 이로 제한되는 것은 아니라, 입력 키들, 스위치들, 보이스 프로세서들 등을 비롯한 임의의 타입의 입력 디바이스를 포함할 수 있다. 출력 디바이스(들)(146)는, 이로 제한되는 것은 아니라, 오디오, 비디오, 다른 시각적 표시자들 등을 비롯한 임의의 타입의 출력 디바이스를 포함할 수 있다. 네트워크 인터페이스 디바이스(들)(148)는, 네트워크(152)로의 그리고 네트워크(152)로부터의 데이터 교환을 허용하도록 구성된 임의의 디바이스들일 수 있다. 네트워크(152)는, 이로 제한되는 것은 아니라, 유선 또는 무선 네트워크, 사설 또는 공공 네트워크, LAN(local area network), WLAN(wide local area network) 및 인터넷을 비롯한 임의의 타입의 네트워크일 수 있다. 네트워크 인터페이스 디바이스(들)(148)는 원하는 임의의 타입의 통신 프로토콜을 지원하도록 구성될 수 있다. 메모리 시스템(142)은 하나 또는 그 초과의 메모리 유닛들(154(0-N))을 포함할 수 있다.

[0042] CPU(들)(132)은 또한 하나 또는 그 초과의 디스플레이들(156)로 전송되는 정보를 제어하기 위해 시스템 버스(138)를 통해 디스플레이 제어기(들)(150)에 액세스하도록 구성될 수 있다. 디스플레이 제어기(들)(150)는, 디스플레이(들)(156)에 적합한 포맷으로 디스플레이될 정보를 프로세싱하는 하나 또는 그 초과의 비디오 프로세서들(158)을 통해 디스플레이될 정보를 디스플레이(들)(156)에 전송한다. 디스플레이(들)(156)은, 이로 제한되는 것은 아니라, CRT(cathode ray tube), LCD(liquid crystal display), 플라즈마 디스플레이 등을 비롯한 임의의 타입의 디스플레이를 포함할 수 있다.

[0043] 당업자들은 추가로, 본원에 개시된 실시예들과 결합하여 설명되는 다양한 예시적인 논리 블록들, 모듈들, 회로들 및 알고리즘들이, 전자 하드웨어로서, 메모리에 또는 다른 컴퓨터-판독가능한 매체에 저장되며

프로세서 또는 다른 프로세싱 디바이스에 의해 실행되는 명령들로서, 또는 이 둘의 조합들에 의해 구현될 수 있음을 인식할 것이다. 본원에서 설명되는 아비터들, 마스터 디바이스들, 및 슬레이브 디바이스들은, 예들로서, 임의의 회로, 하드웨어 컴포넌트, 집적 회로(IC) 또는 IC 칩에서 이용될 수 있다. 본원에 개시된 메모리는 임의의 타입 및 크기의 메모리일 수 있으며 원하는 임의의 타입의 정보를 저장하도록 구성될 수 있다. 이 상호교환성을 명확히 하기 위해, 다양한 예시적인 컴포넌트들, 블록들, 모듈들, 회로들, 및 단계들이 일반적으로 그들의 기능적 관점에서 설명되었다. 이러한 기능이 구현되는 방식은, 전체 시스템에 부과되는 설계 제약들, 설계 선택들, 및/또는 특정 애플리케이션에 의존한다. 당업자들은 각각의 특정 애플리케이션들에 대해 가변 방식들로 설명된 기능을 구현할 수 있지만, 이러한 구현 결정들이 본 개시물의 범위 이탈을 야기하는 것으로 해석되지 않아야 한다.

[0036]

[0044] 본 개시물에 설명된 실시예들과 관련하여 설명된 다양한 예시적인 논리 블록들, 모듈들 및 회로들은 프로세서, 디지털 신호 프로세서(DSP), 주문형 집적회로(ASIC), 필드 프로그래머블 게이트 어레이(FPGA) 또는 다른 프로그래머블 논리 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본원에서 설명된 기능들을 수행하도록 설계된 이들의 임의의 결합으로 구현 또는 수행될 수 있다. 프로세서는 마이크로프로세서일 수 있지만, 대안적으로, 프로세서는 임의의 종래의 프로세서, 제어기, 마이크로제어기 또는 상태 머신일 수 있다. 또한, 프로세서는 컴퓨팅 디바이스들의 결합, 예를 들어 DSP 및 마이크로프로세서의 결합, 다수의 마이크로프로세서들, DSP 코어와 결합된 하나 또는 그 초과의 마이크로프로세서들, 또는 임의의 다른 이러한 구성으로서 구현될 수 있다.

[0037]

[0045] 본 개시물에 설명된 실시예들은 하드웨어로 그리고 하드웨어에 저장된 명령들로 구현될 수 있으며, 예를 들어, RAM(Random Access Memory), 플래쉬 메모리, ROM(Read Only Memory), EPROM(Electrically Programmable ROM), EEPROM(Electrically Erasable Programmable ROM), 페지스터들, 하드 디스크, 제거가능한 디스크, CD-ROM, 또는 업계에 공지된 컴퓨터 판독가능 매체의 임의의 다른 형태로서 상주할 수 있다. 예시적인 저장 매체는 프로세서와 결합되어, 프로세서가 저장 매체로부터 정보를 판독하고 저장 매체에 정보를 기록할 수 있게 된다. 대안적으로, 저장 매체는 프로세서에 통합될 수 있다. 프로세서 및 저장 매체는 ASIC에 상주할 수 있다. ASIC은 원격 스테이션에 상주할 수 있다. 대안적으로, 프로세서 및 저장 매체는 원격 스테이션, 기지국 또는 서버에서 이산 컴포넌트로서 상주할 수 있다.

[0038]

[0046] 또한, 본원의 임의의 예시적 실시예들에서 설명되는 동작 단계들은 예들 및 논의를 제공하기 위해 설명됨이 주목된다. 설명된 동작들은 예시된 시퀀스들 이외에 다수의 상이한 시퀀스들로 수행될 수 있다. 또한, 단일 동작 단계로 설명되는 동작들은 실제로 다수의 상이한 단계들로 수행될 수 있다. 부가적으로, 예시적인 실시예들에서 논의되는 하나 또는 그 초과의 동작 단계들은 결합될 수 있다. 흐름도들로 예시되는 동작 단계들은 당업자들에게 명백한 것처럼 다수의 상이한 변경들로 처리될 수 있음이 이해될 것이다. 또한 당업자들은, 정보 및 신호들이 다양한 상이한 기법들 및 기술들 중 임의의 기법 및 기술을 이용하여 표현될 수 있음을 이해할 것이다. 예를 들어, 상기 설명 전반에 걸쳐 참조될 수 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들 및 칩들은 전압들, 전류들, 전자기파들, 자기장들 또는 자기 입자들, 광 필드 또는 광 입자들, 또는 이들의 임의의 조합에 의해 표현될 수 있다.

[0039]

[0047] 본 개시의 전술한 설명은 임의의 당업자가 본 개시를 이용하거나 또는 실시할 수 있도록 제공된다. 본 개시에 대한 다양한 변형들은 당업자들에게 용이하게 명백할 것이며, 본원에 정의된 일반적인 원리들은 본 개시의 사상 또는 범위를 벗어남이 없이 다른 변형들에 적용될 수 있다. 따라서, 본 개시는 본원에 설명된 예들 및 설계들로 제한되는 것이 아니라, 본원에 개시된 원리를 및 신규한 특징들과 일치하는 가장 넓은 범위를 따르도록 의도된다.

## 도면

## 도면1

(종래기술)

## 도면2a

(종래 기술)

## 도면2b

(종래 기술)

## 도면3

(종래 기술)

## 도면4

(종래 기술)

## 도면5

## 도면6

## 도면7a

## 도면7b

## 도면8