(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7254462号**

**(P7254462)**

(45)発行日 令和5年4月10日(2023.4.10)

(24)登録日 令和5年3月31日(2023.3.31)

(51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78  | 6 1 9 A |

| H 01 L | 29/786 (2006.01) | H 01 L | 27/06  | 1 0 2 A |

| H 01 L | 21/8234(2006.01) | H 01 L | 27/088 | E       |

| H 01 L | 27/06 (2006.01)  | H 01 L | 29/78  | 3 7 1   |

| H 01 L | 27/088(2006.01)  | H 01 L | 29/78  | 6 1 7 T |

請求項の数 2 (全63頁) 最終頁に続く

(21)出願番号 特願2018-150541(P2018-150541)

(22)出願日 平成30年8月9日(2018.8.9)

(65)公開番号 特開2020-27825(P2020-27825A)

(43)公開日 令和2年2月20日(2020.2.20)

審査請求日 令和3年8月3日(2021.8.3)

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

奥野 直樹

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

澤井 寛美

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

駒形 大樹

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

最終頁に続く

(54)【発明の名称】 半導体装置の作製方法

**(57)【特許請求の範囲】****【請求項1】**

基板上に第1の絶縁体を形成し、

前記第1の絶縁体の上に、第1の酸化膜、第2の酸化膜および第1の導電膜を順に成膜し、

前記第1の酸化膜、前記第2の酸化膜および前記第1の導電膜を加工して、第1の酸化物、酸化物層および導電体層を形成し、

前記第1の酸化物、前記酸化物層および前記導電体層を覆って第1の絶縁膜および第2の絶縁膜を順に成膜し、

前記酸化物層、前記導電体層、前記第1の絶縁膜および前記第2の絶縁膜に前記第1の酸化物が露出する開口を形成することで、

第2の酸化物、第3の酸化物、第1の導電体、第2の導電体、第2絶縁体および第3の絶縁体を形成し、

第3の酸化膜、第3の絶縁膜および第2の導電膜を順に成膜し、

平坦化処理を行うことによって、前記第3の酸化膜、前記第3の絶縁膜および前記第2の導電膜を前記第3の絶縁体の一部が露出するまで除去し、第4の酸化物、第4の絶縁体および第3の導電体を形成し、

第1の加熱処理を行い、

前記第1の加熱処理を行う時間は、24時間以上100時間以下であり、

第2の加熱処理を行い、

前記第3の導電体上に第4の絶縁膜を成膜する、半導体装置の作製方法。

【請求項2】

基板上に第1の絶縁体を形成し、

前記第1の絶縁体の上に、第1の酸化膜、第2の酸化膜および第1の導電膜を順に成膜し、

前記第1の酸化膜、前記第2の酸化膜および前記第1の導電膜を加工して、第1の酸化物

酸化物層および導電体層を形成し、

前記第1の酸化物、前記酸化物層および前記導電体層を覆って第1の絶縁膜および第2の

絶縁膜を順に成膜し、

前記酸化物層、前記導電体層、前記第1の絶縁膜および前記第2の絶縁膜に前記第1の酸

化物が露出する開口を形成することで、

第2の酸化物、第3の酸化物、第1の導電体、第2の導電体、第2絶縁体および第3の絶

縁体を形成し、

第3の酸化膜、第3の絶縁膜および第2の導電膜を順に成膜し、

平坦化処理を行うことによって、前記第3の酸化膜、前記第3の絶縁膜および前記第2の

導電膜を前記第3の絶縁体の一部が露出するまで除去し、第4の酸化物、第4の絶縁体お

よび第3の導電体を形成し、

第1の加熱処理を行い、

前記第1の加熱処理を行う時間は、24時間以上48時間以下であり、

第2の加熱処理を行い、

前記第3の導電体上に第4の絶縁膜を成膜する、半導体装置の作製方法。

10

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は、半導体装置、ならびに半導体装置の作製方法に関する。または、本発明の一態様は、半導体ウエハ、モジュール、および電子機器に関する。

【0002】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能し得る装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。表示装置（液晶表示装置、発光表示装置など）、投影装置、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置、および電子機器などは、半導体装置を有すると言える場合がある。

30

【0003】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

【背景技術】

【0004】

トランジスタに適用可能な半導体薄膜として、シリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。酸化物半導体としては、例えば、酸化インジウム、酸化亜鉛などの一元系金属の酸化物のみでなく、多元系金属の酸化物も知られている。多元系金属の酸化物の中でも、特に、 $In - Ga - Zn$ 酸化物（以下、IGZOとも呼ぶ）に関する研究が盛んに行われている。

40

【0005】

IGZOに関する研究により、酸化物半導体において、単結晶でも非晶質でもない、C A A C (c-axis aligned crystalline) 構造およびn c (nano crystalline) 構造が見出された（非特許文献1乃至非特許文献3参照）。非特許文献1および非特許文献2では、C A A C 構造を有する酸化物半導体を用いてトランジスタを作製する技術も開示されている。さらに、C A A C 構造およびn c 構造よりも結晶性の低い酸化物半導体でさえも、微小な結晶を有することが、非特許文献4および

50

非特許文献 5 に示されている。

#### 【0006】

さらに、IGZOを活性層として用いたトランジスタは極めて低いオフ電流を持ち（非特許文献 6 参照）、その特性を利用したLSIおよびディスプレイが報告されている（非特許文献 7 および非特許文献 8 参照）。

#### 【先行技術文献】

#### 【非特許文献】

#### 【0007】

- 【文献】S. Yamazaki et al., "SID Symposium Digest of Technical Papers", 2012, volume 43, issue 1, p. 183 - 186 10

S. Yamazaki et al., "Japanese Journal of Applied Physics", 2014, volume 53, Number 4 S, p. 04ED18-1 - 04ED18-10

S. Ito et al., "The Proceedings of AM-FPD'13 Digest of Technical Papers", 2013, p. 151 - 154

S. Yamazaki et al., "ECS Journal of Solid State Science and Technology", 2014, volume 3, issue 9, p. Q3012 - Q3022 20

S. Yamazaki, "ECS Transactions", 2014, volume 64, issue 10, p. 155 - 164

K. Kato et al., "Japanese Journal of Applied Physics", 2012, volume 51, p. 021201-1 - 021201-7

S. Matsuda et al., "2015 Symposium on VLSI Technology Digest of Technical Papers", 2015, p. T216 - T217

S. Amano et al., "SID Symposium Digest of Technical Papers", 2010, volume 41, issue 1, p. 626 - 629 30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

本発明の一態様は、信頼性が良好な半導体装置を提供することを課題の一つとする。または、本発明の一態様は、オン電流が大きい半導体装置を提供することを課題の一つとする。または、本発明の一態様は、高い周波数特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、微細化または高集積化が可能な半導体装置を提供することを課題の一つとする。または、本発明の一態様は、良好な電気特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、生産性の高い半導体装置を提供することを課題の一つとする。 40

#### 【0009】

本発明の一態様は、長期間においてデータの保持が可能な半導体装置を提供することを課題の一つとする。本発明の一態様は、情報の書き込み速度が速い半導体装置を提供することを課題の一つとする。本発明の一態様は、設計自由度が高い半導体装置を提供することを課題の一つとする。本発明の一態様は、消費電力を抑えることができる半導体装置を提供することを課題の一つとする。本発明の一態様は、新規な半導体装置を提供することを課題の一つとする。

#### 【0010】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の

一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】**

**【0011】**

本発明の一態様は、基板上に第1の絶縁体を形成し、第1の絶縁体の上に、第1の酸化膜、第2の酸化膜および第1の導電膜を順に成膜し、第1の酸化膜、第2の酸化膜および第1の導電膜を加工して、第1の酸化物、酸化物層および導電体層を形成し、第1の酸化物、酸化物層および導電体層を覆って第1の絶縁膜および第2の絶縁膜を順に成膜し、酸化物層、導電体層、第1の絶縁膜および第2の絶縁膜に第1の酸化物が露出する開口を形成することで、第2の酸化物、第3の酸化物、第1の導電体、第2の導電体、第2絶縁体および第3の絶縁体を形成し、第3の酸化膜、第3の絶縁膜および第2の導電膜を順に成膜し、平坦化処理を行うことによって、第3の酸化膜、第3の絶縁膜および第2の導電膜を第3の絶縁体の一部が露出するまで除去し、第4の酸化物、第4の絶縁体および第3の導電体を形成し、第1の加熱処理を行い、第2の加熱処理を行い、第3の導電体上に第4の絶縁膜を成膜する半導体装置の作製方法である。

10

**【0012】**

また、第1の加熱処理は、窒素雰囲気において、300以上450以下で行なうことが好ましい。

**【0013】**

20

また、第1の加熱処理の時間は、1時間以上行なうことが好ましい。

**【0014】**

また、第2の加熱処理および第4の絶縁膜の成膜は、減圧下において順に行なうことが好ましい。

**【0015】**

また、第4の絶縁体は、酸化アルミニウムまたは窒化シリコン、のいずれかを含むことが好ましい。

**【0016】**

また、第4の絶縁体は、第1の材料および第2の材料を含み、第1の材料は、第2の材料の下側に位置し、第2の材料の下面に接していることが好ましい。

30

**【0017】**

また、第1の材料は、酸化アルミニウムを含み、第2の材料は、窒化シリコンを含み、第2の材料は、第1の材料と異なる材料であることが好ましい。

**【0018】**

また、第1乃至第4の酸化物は、Inと、元素M(MはAl、Ga、Y、またはSn)と、Znと、を含むことが好ましい。

**【0019】**

また、本発明の一態様は、第1の絶縁体と、第1の絶縁体上の第1の酸化物と、第1の酸化物上の第2の酸化物および第3の酸化物と、第2の酸化物上の第1の導電体と、第3の酸化物上の第2の導電体と、第1の酸化物上の第4の酸化物と、第4の酸化物上の第2の絶縁体と、第2の絶縁体上の第3の導電体と、第3の導電体上の第3の絶縁体と、第3の絶縁体上の第4の絶縁体と、を有し、第4の酸化物は、第1の酸化物の上面、第1の導電体の側面、第2の導電体の側面、第2の酸化物の側面および第3の酸化物の側面と、それぞれ接し、第1の酸化物は、Inと、元素M(MはAl、Ga、Y、またはSn)と、Znと、を有し、第4の酸化物は、第1の酸化物が有する構成元素の少なくとも一を有し、第2の酸化物、および第3の酸化物は、それぞれ、元素Mを有し、第2の酸化物、および第3の酸化物は、第1の酸化物よりも元素Mの濃度が高い領域を有する半導体装置である。

40

**【0020】**

また、第3の絶縁体は、酸素、およびアルミニウムを含み、第4の絶縁体は、窒素、お

50

よりシリコンを含むことが好ましい。

**【発明の効果】**

**【0021】**

本発明の一態様により、信頼性が良好な半導体装置を提供することができる。または、本発明の一態様により、オン電流が大きい半導体装置を提供することができる。または、本発明の一態様により、高い周波数特性を有する半導体装置を提供することができる。または、本発明の一態様により、微細化または高集積化が可能な半導体装置を提供することができる。または、本発明の一態様により、良好な電気特性を有する半導体装置を提供することができる。または、本発明の一態様により、生産性の高い半導体装置を提供することができる。

10

**【0022】**

または、長期間においてデータの保持が可能な半導体装置を提供することができる。または、データの書き込み速度が速い半導体装置を提供することができる。または、設計自由度が高い半導体装置を提供することができる。または、消費電力を抑えることができる半導体装置を提供することができる。または、新規な半導体装置を提供することができる。

**【0023】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

20

**【図面の簡単な説明】**

**【0024】**

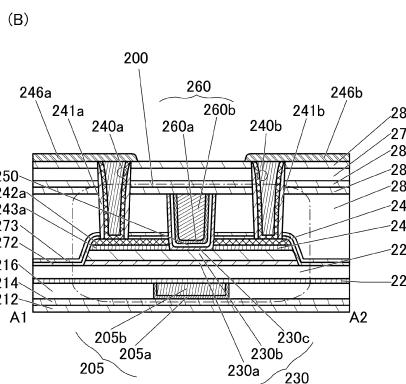

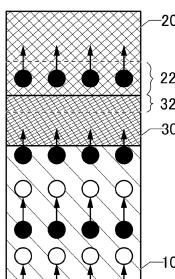

**【図1】**本発明の一態様に係る半導体装置の上面図および断面図。

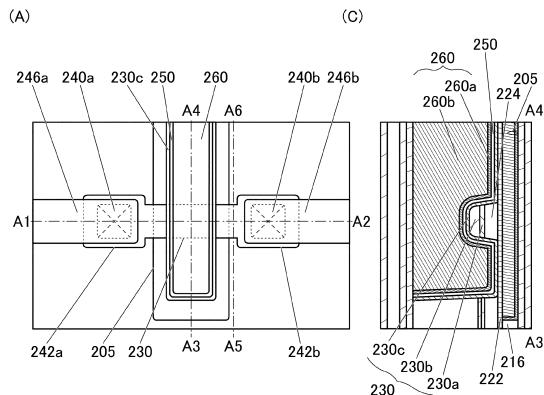

**【図2】**本発明の一態様に係る半導体装置の上面図および断面図。

**【図3】**本発明の一態様に係る半導体装置の断面図。

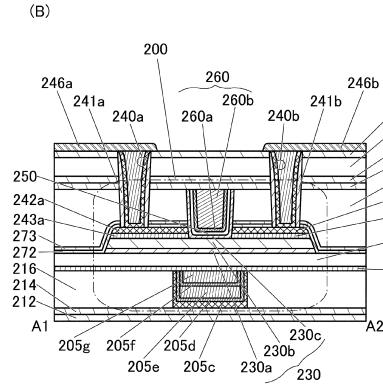

**【図4】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

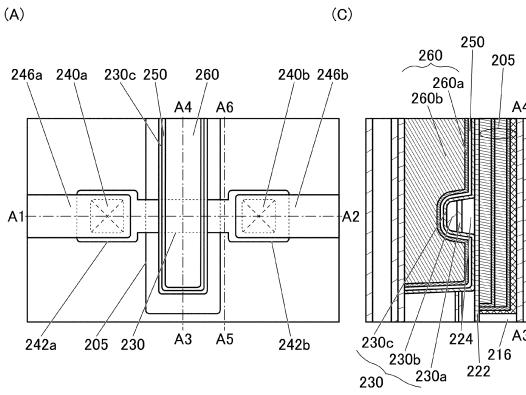

**【図5】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図6】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図7】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図8】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図9】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

30

**【図10】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図11】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図12】**本発明の一態様に係る半導体装置の作製方法を示す上面図および断面図。

**【図13】**酸化物半導体のエネルギー・バンド構造を説明する図。

**【図14】**酸化物半導体上に配置した導電体の酸化を説明する模式図。

**【図15】**酸化物半導体上に配置した導電体の酸化を説明する模式図。

**【図16】**酸化物半導体上に配置した導電体の酸化を説明する模式図。

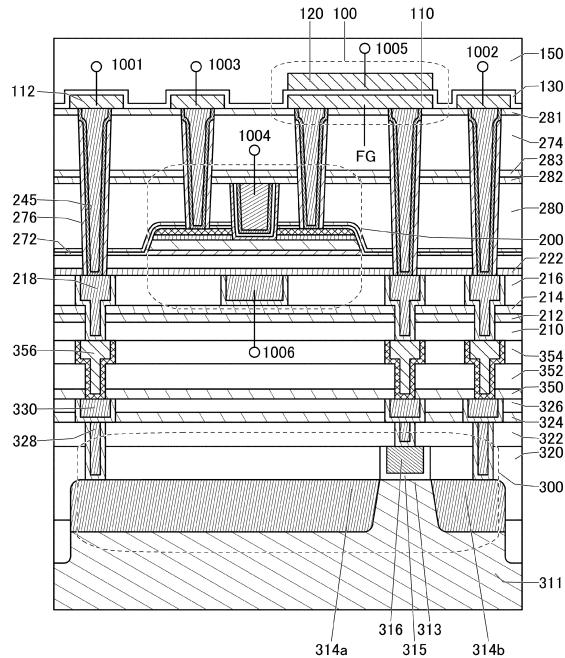

**【図17】**本発明の一態様に係る記憶装置の構成を示す断面図。

**【図18】**本発明の一態様に係る記憶装置の構成を示す断面図。

40

**【図19】**本発明の一態様に係る記憶装置の構成例を示すブロック図。

**【図20】**本発明の一態様に係る記憶装置の構成例を示す回路図。

**【図21】**本発明の一態様に係る半導体装置の模式図。

**【図22】**本発明の一態様に係る記憶装置の模式図。

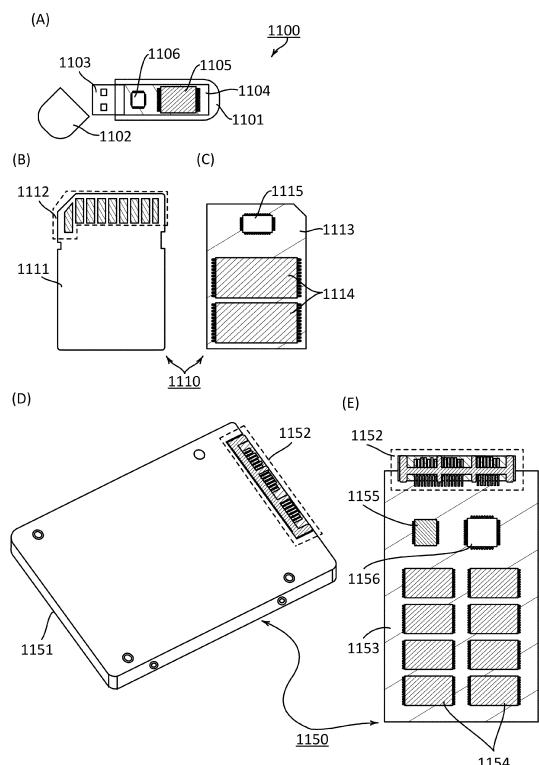

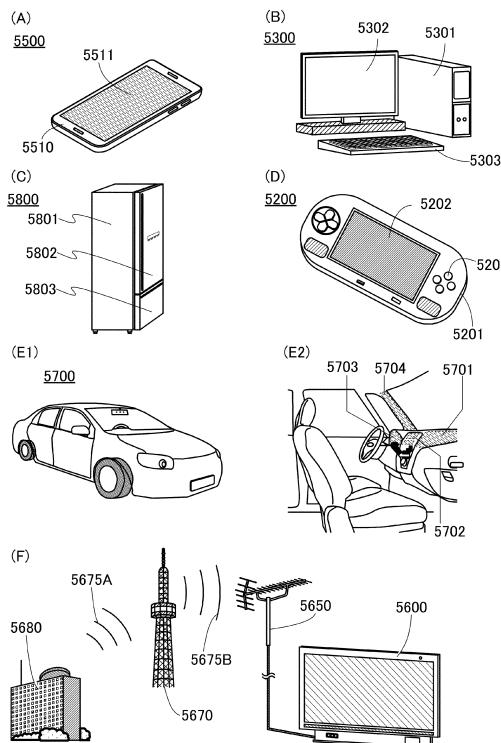

**【図23】**本発明の一態様に係る電子機器を示す図。

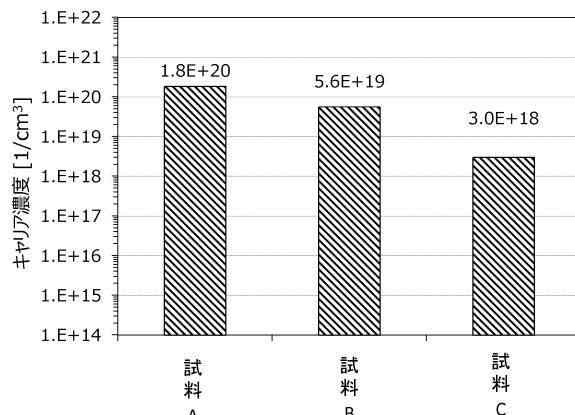

**【図24】**実施例の酸化物のキャリア濃度を示すグラフ。

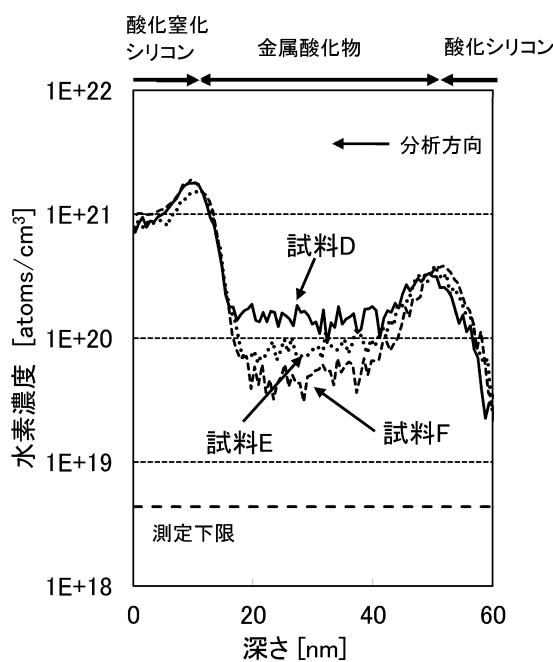

**【図25】**実施例の酸化物の水素濃度を示すグラフ。

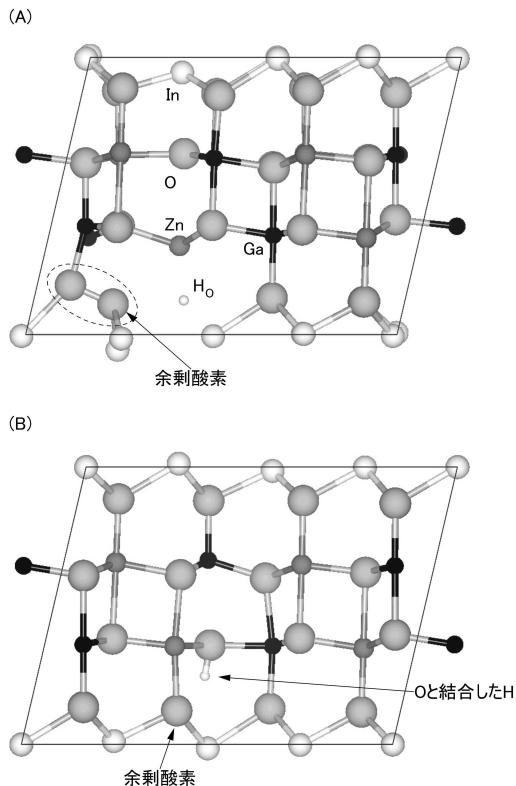

**【図26】**初期状態のモデルと最終状態のモデルを説明する図。

**【図27】**エネルギーの変化を説明する図。

**【発明を実施するための形態】**

50

**【 0 0 2 5 】**

以下、実施の形態について図面を参照しながら説明する。ただし、実施の形態は多くの異なる態様で実施することが可能であり、趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

**【 0 0 2 6 】**

また、図面において、大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお、図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。例えば、実際の製造工程において、エッティングなどの処理により層やレジストマスクなどが意図せずに目減りすることがあるが、理解を容易とするために図に反映しないことがある。また、図面において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

10

**【 0 0 2 7 】**

また、特に上面図（「平面図」ともいう）や斜視図などにおいて、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。

**【 0 0 2 8 】**

また、本明細書等において、第1、第2等として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

20

**【 0 0 2 9 】**

また、本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。したがって、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

**【 0 0 3 0 】**

30

例えば、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接的に接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。

**【 0 0 3 1 】**

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

**【 0 0 3 2 】**

40

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができる場合がある。

**【 0 0 3 3 】**

なお、本明細書等において、トランジスタの構造によっては、実際にチャネルの形成される領域（チャネル形成領域）におけるチャネル幅（以下、「実効的なチャネル幅」ともいう）と、トランジスタの上面図において示されるチャネル幅（以下、「見かけ上のチャネル幅」ともいう）と、が異なる場合がある。例えば、ゲートが半導体の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視でき

50

なくなる場合がある。例えば、微細かつゲートが半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル形成領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅の方が大きくなる。

#### 【 0 0 3 4 】

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

#### 【 0 0 3 5 】

本明細書では、単にチャネル幅と記載した場合には、見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅などは、断面TEM像などを解析することなどによって、値を決定することができる。

10

#### 【 0 0 3 6 】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物と言える。不純物が含まれることにより、例えば、半導体のDOS(Density of States)が高くなることや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、および酸化物半導体の主成分以外の遷移金属などがあり、例えば、水素、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、水も不純物として機能する場合がある。また、酸化物半導体の場合、例えば不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

20

#### 【 0 0 3 7 】

なお、本明細書等において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものである。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものである。

30

#### 【 0 0 3 8 】

また、本明細書等において、「絶縁体」という用語を、絶縁膜または絶縁層と言い換えることができる。また、「導電体」という用語を、導電膜または導電層と言い換えることができる。また、「半導体」という用語を、半導体膜または半導体層と言い換えることができる。

#### 【 0 0 3 9 】

また、本明細書等において、「平行」とは、二つの直線が-10度以上10度以下の角度で配置されている状態をいう。したがって、-5度以上5度以下の場合も含まれる。また、「略平行」とは、二つの直線が-30度以上30度以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80度以上100度以下の角度で配置されている状態をいう。したがって、85度以上95度以下の場合も含まれる。また、「略垂直」とは、二つの直線が60度以上120度以下の角度で配置されている状態をいう。

40

#### 【 0 0 4 0 】

なお、本明細書において、バリア膜とは、水、水素などの不純物および酸素の透過を抑制する機能を有する膜のことであり、当該バリア膜に導電性を有する場合は、導電性バリア膜と呼ぶことがある。

#### 【 0 0 4 1 】

本明細書等において、金属酸化物(metal oxide)とは、広い意味での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう)

50

などに分類される。例えば、トランジスタの半導体層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、O S F E TあるいはO Sトランジスタと記載する場合においては、酸化物または酸化物半導体を有するトランジスタと換言することができる。

#### 【0042】

また、本明細書等において、ノーマリーオフとは、ゲートに電位を印加しない、またはゲートに接地電位を与えたときに、トランジスタに流れるチャネル幅 $1 \mu m$ あたりの電流が、室温において $1 \times 10^{-20} A$ 以下、85において $1 \times 10^{-18} A$ 以下、または125において $1 \times 10^{-16} A$ 以下であることをいう。

#### 【0043】

##### (実施の形態1)

以下では、本発明の一態様に係るトランジスタ200を有する半導体装置の一例について説明する。なお、本発明の一態様においては、トランジスタ作製工程中における、加熱処理を特定の条件、または特定の範囲とすることによって、信頼性が良好な半導体装置を提供することができる。なお、トランジスタ作製工程中における加熱処理については、後述の半導体装置の作製方法にて、詳細を説明する。

#### 【0044】

##### <半導体装置の構成例>

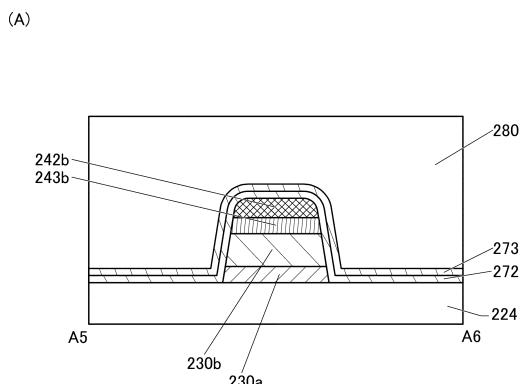

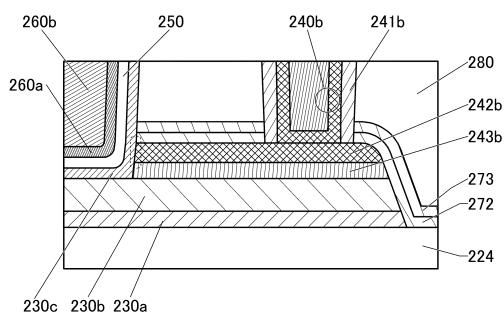

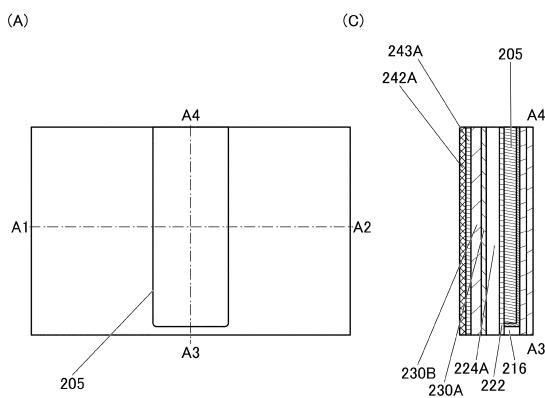

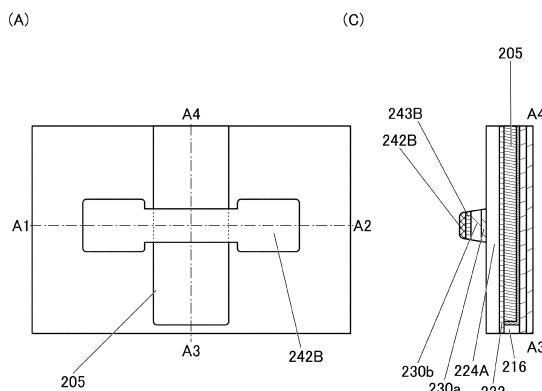

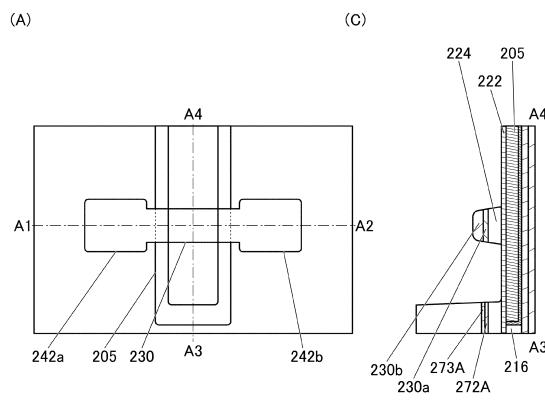

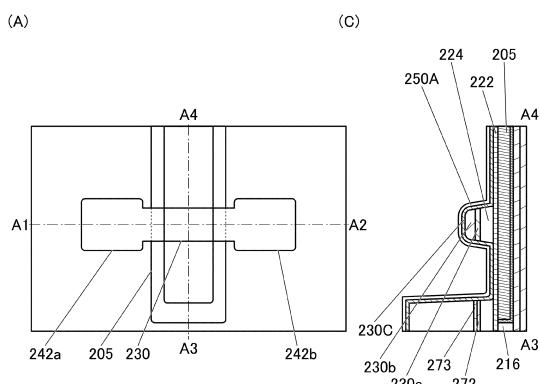

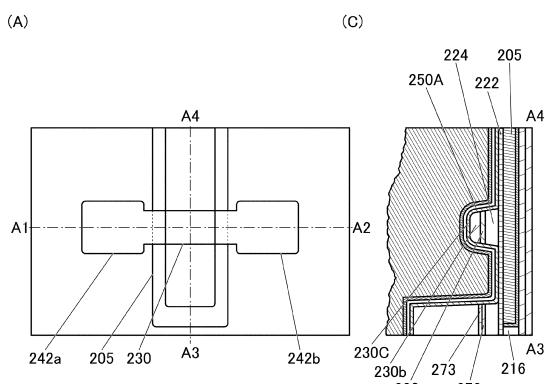

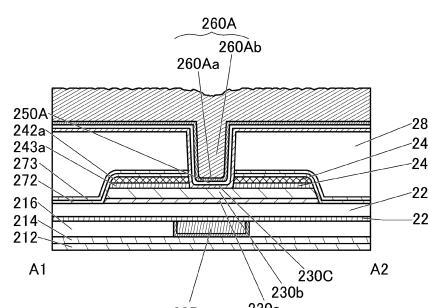

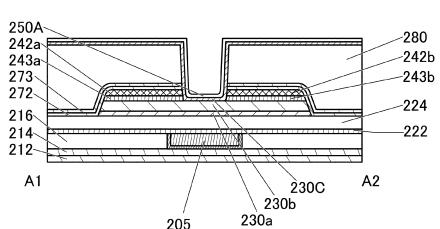

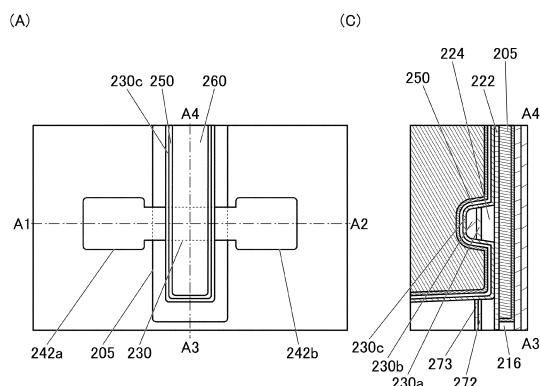

図1(A)、図1(B)、および図1(C)は、本発明の一態様に係るトランジスタ200、およびトランジスタ200周辺の上面図および断面図である。

#### 【0045】

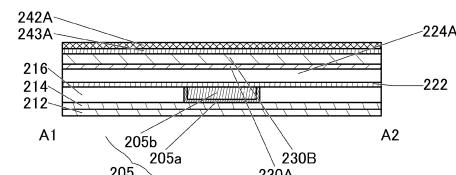

図1(A)は、トランジスタ200を有する半導体装置の上面図である。また、図1(B)、および図1(C)は、当該半導体装置の断面図である。ここで、図1(B)は、図1(A)にA1-A2の一点鎖線で示す部位の断面図であり、トランジスタ200のチャネル長方向の断面図でもある。また、図1(C)は、図1(A)にA3-A4の一点鎖線で示す部位の断面図であり、トランジスタ200のチャネル幅方向の断面図でもある。なお、図1(A)の上面図では、図の明瞭化のために一部の要素を省いている。

#### 【0046】

本発明の一態様の半導体装置は、基板(図示せず)上の絶縁体212と、絶縁体212上の絶縁体214と、絶縁体214上のトランジスタ200と、トランジスタ200上の絶縁体280と、絶縁体280上の絶縁体282と、絶縁体282上の絶縁体283と、絶縁体283上の絶縁体274と、絶縁体274上の絶縁体281と、を有する。絶縁体212、絶縁体214、絶縁体280、絶縁体282、絶縁体283、絶縁体274、および絶縁体281は層間膜として機能する。また、トランジスタ200と電気的に接続し、プラグとして機能する導電体240(導電体240a、および導電体240b)とを有する。なお、プラグとして機能する導電体240の側面に接して絶縁体241(絶縁体241a、および絶縁体241b)が設けられる。また、絶縁体281上、および導電体240上には、導電体240と電気的に接続し、配線として機能する導電体246(導電体246a、および導電体246b)が設けられる。

#### 【0047】

また、絶縁体272、絶縁体273、絶縁体280、絶縁体282、絶縁体283、絶縁体274、および絶縁体281の開口の内壁に接して絶縁体241aが設けられ、その側面に接して導電体240aの第1の導電体が設けられ、さらに内側に導電体240aの第2の導電体が設けられている。また、絶縁体272、絶縁体273、絶縁体280、絶縁体282、絶縁体283、絶縁体274、および絶縁体281の開口の内壁に接して絶縁体241bが設けられ、その側面に接して導電体240bの第1の導電体が設けられ、さらに内側に導電体240bの第2の導電体が設けられている。ここで、導電体240の上面の高さと、絶縁体281の上面の高さは同程度にできる。なお、トランジスタ200では、導電体240の第1の導電体および導電体240の第2の導電体を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体240を単

層、または3層以上の積層構造として設ける構成にしてもよい。構造体が積層構造を有する場合、形成順に序数を付与し、区別する場合がある。

#### 【0048】

##### [トランジスタ200]

図1に示すように、トランジスタ200は、絶縁体214上の絶縁体216と、絶縁体216に埋め込まれるように配置された導電体205（導電体205a、および導電体205b）と、絶縁体216上、および導電体205上の絶縁体222と、絶縁体222上の絶縁体224と、絶縁体224上の酸化物230aと、酸化物230a上の酸化物230bと、酸化物230b上の酸化物243aおよび酸化物243bと、酸化物243a上の導電体242aと、酸化物243b上の導電体242bと、酸化物230b上の酸化物230cと、酸化物230c上の絶縁体250と、絶縁体250上に位置し、酸化物230cと重なる導電体260（導電体260a、および導電体260b）と、絶縁体224の上面の一部、酸化物230aの側面、酸化物230bの側面、酸化物243aの側面、酸化物243bの側面、導電体242aの側面、導電体242aの上面、導電体242bの側面、および導電体242bの上面と接する絶縁体272と、絶縁体272上の絶縁体273と、を有する。また、酸化物230cは、酸化物243aの側面、酸化物243bの側面、導電体242aの側面および導電体242bの側面とそれぞれ接する。導電体260は、導電体260aおよび導電体260bを有し、導電体260bの底面および側面を包むように導電体260aが配置される。ここで、図1(B)に示すように、導電体260の上面は、絶縁体250の上面および酸化物230cの上面と略一致して配置される。また、絶縁体282は、導電体260、酸化物230c、絶縁体250、および絶縁体280のそれぞれの上面と接する。10 20

#### 【0049】

また、絶縁体222、絶縁体272、絶縁体273、絶縁体282、および絶縁体283は、水素（例えば、水素原子、水素分子など）の少なくとも一の拡散を抑制する機能を有することが好ましい。また、絶縁体222、絶縁体272、絶縁体273、および絶縁体282は、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有することが好ましい。例えば、絶縁体222、絶縁体272、絶縁体273、および絶縁体282は、それぞれ絶縁体224よりも酸素および水素の一方または双方の透過性が低いことが好ましい。絶縁体222、絶縁体272、絶縁体273、絶縁体282、および絶縁体283は、それぞれ絶縁体250よりも酸素および水素の一方または双方の透過性が低いことが好ましい。絶縁体222、絶縁体272、絶縁体273、絶縁体282、および絶縁体283は、それぞれ絶縁体280よりも酸素および水素の一方または双方の透過性が低いことが好ましい。30

#### 【0050】

図1(B)に示すように、絶縁体272は、導電体242aの上面と側面、導電体242bの上面と側面、酸化物243aの側面、酸化物243bの側面、酸化物230aの側面、酸化物230bの側面、および絶縁体224の上面に接することが好ましい。また、絶縁体272上に絶縁体273が接して設けられていることが好ましい。これにより、絶縁体280は、絶縁体272、および絶縁体273によって、絶縁体224および酸化物230と離隔される。40

#### 【0051】

また、酸化物230は、絶縁体224上の酸化物230aと、酸化物230a上の酸化物230bと、酸化物230b上に配置され、少なくとも一部が酸化物230bの上面に接する酸化物230cと、を有することが好ましい。

#### 【0052】

なお、トランジスタ200では、チャネル形成領域と、その近傍において、酸化物230a、酸化物230b、および酸化物230cの3層を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、酸化物230bの単層、酸化物230bと酸化物230aの2層構造、酸化物230bと酸化物230cの2層構造、または

4層以上の積層構造を設ける構成にしてもよい。また、トランジスタ200では、導電体260を2層の積層構造として示しているが、本発明はこれに限られるものではない。例えば、導電体260が、単層構造であってもよいし、3層以上の積層構造であってもよい。

#### 【0053】

ここで、導電体260は、トランジスタのゲートとして機能し、導電体242aおよび導電体242bは、それぞれソース電極またはドレイン電極として機能する。トランジスタ200は、ゲートとして機能する導電体260が、絶縁体280などによって形成される開口を埋めるように自己整合的に形成される。導電体260をこのように形成することにより、導電体242aと導電体242bの間の領域に、導電体260を位置合わせすることなく確実に配置することができる。

10

#### 【0054】

また、トランジスタ200は、チャネル形成領域を含む酸化物230（酸化物230a、酸化物230b、および酸化物230c）に、酸化物半導体として機能する金属酸化物（以下、酸化物半導体ともいう）を用いることが好ましい。

#### 【0055】

チャネル形成領域に酸化物半導体を用いたトランジスタ200は、非導通状態において極めてリーク電流（オフ電流）が小さいため、低消費電力の半導体装置を提供できる。また、酸化物半導体は、スパッタリング法などを用いて成膜できるため、高集積型の半導体装置を構成するトランジスタ200に用いることができる。

20

#### 【0056】

例えば、酸化物230として、In-M-Zn酸化物（元素Mは、アルミニウム、ガリウム、イットリウム、錫、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンクステン、またはマグネシウムなどから選ばれた一種、または複数種）等の金属酸化物を用いるとよい。特に、元素Mは、アルミニウム、ガリウム、イットリウム、または錫を用いるとよい。また、酸化物230として、In-Ga酸化物、In-Zn酸化物を用いてもよい。

#### 【0057】

酸化物230は、酸化物230aと、酸化物230a上の酸化物230bと、酸化物230b上の酸化物230cと、を有する。酸化物230b下に酸化物230aを有することで、酸化物230aよりも下方に形成された構造物から、酸化物230bへの不純物の拡散を抑制することができる。また、酸化物230b上に酸化物230cを有することで、酸化物230cよりも上方に形成された構造物から、酸化物230bへの不純物の拡散を抑制することができる。

30

#### 【0058】

なお、酸化物230は、各金属原子の原子数比が異なる酸化物により、積層構造を有することが好ましい。具体的には、酸化物230aに用いる金属酸化物において、構成元素中の元素Mの原子数比が、酸化物230bに用いる金属酸化物における、構成元素中の元素Mの原子数比より、大きいことが好ましい。また、酸化物230aに用いる金属酸化物において、Inに対する元素Mの原子数比が、酸化物230bに用いる金属酸化物における、Inに対する元素Mの原子数比より大きいことが好ましい。また、酸化物230bに用いる金属酸化物において、元素Mに対するInの原子数比が、酸化物230aに用いる金属酸化物における、元素Mに対するInの原子数比より大きいことが好ましい。また、酸化物230cは、酸化物230aまたは酸化物230bに用いることができる金属酸化物を、用いることができる。

40

#### 【0059】

また、酸化物230bは、結晶性を有することが好ましい。例えば、後述するCAAC-O<sub>S</sub> (c-axis aligned crystalline oxide semiconductor) を用いることが好ましい。CAAC-O<sub>S</sub>などの結晶性を有する酸化物は、不純物や欠陥（酸素欠損など）が少なく、結晶性の高い、緻密な構造を有してい

50

る。よって、ソース電極またはドレイン電極による、酸化物 230b からの酸素の引き抜きを抑制することができる。これにより、熱処理を行っても、酸化物 230b から酸素が引き抜かれることを低減できるので、トランジスタ 200 は、製造工程における高い温度（所謂サーマルバジェット）に対して安定である。

#### 【0060】

また、酸化物 230a および酸化物 230c の伝導帯下端のエネルギーが、酸化物 230b の伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物 230a および酸化物 230c の電子親和力が、酸化物 230b の電子親和力より小さいことが好ましい。

#### 【0061】

ここで、酸化物 230a、酸化物 230b、および酸化物 230c の接合部において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、酸化物 230a、酸化物 230b、および酸化物 230c の接合部における伝導帯下端のエネルギー準位は、連続的に変化または連続接合するともいいうことができる。このようにするために、酸化物 230a と酸化物 230b との界面、および酸化物 230b と酸化物 230c との界面において形成される混合層の欠陥準位密度を低くするとよい。

#### 【0062】

具体的には、酸化物 230a として、 $In : Ga : Zn = 1 : 3 : 4$  [原子数比]、または $1 : 1 : 0.5$  [原子数比] の金属酸化物を用いればよい。また、酸化物 230b として、 $In : Ga : Zn = 4 : 2 : 3$  [原子数比]、または $1 : 1 : 1$  [原子数比] の金属酸化物を用いればよい。また、酸化物 230c として、 $In : Ga : Zn = 1 : 3 : 4$  [原子数比]、 $Ga : Zn = 2 : 1$  [原子数比]、または $Ga : Zn = 2 : 5$  [原子数比] の金属酸化物を用いればよい。また、酸化物 230c を積層構造とする場合の具体例としては、 $In : Ga : Zn = 4 : 2 : 3$  [原子数比] と、 $In : Ga : Zn = 1 : 3 : 4$  [原子数比] との積層構造、 $Ga : Zn = 2 : 1$  [原子数比] と、 $In : Ga : Zn = 4 : 2 : 3$  [原子数比] との積層構造、 $Ga : Zn = 2 : 5$  [原子数比] と、 $In : Ga : Zn = 4 : 2 : 3$  [原子数比] との積層構造、酸化ガリウムと、 $In : Ga : Zn = 4 : 2 : 3$  [原子数比] との積層構造などが挙げられる。

#### 【0063】

このとき、キャリアの主たる経路は酸化物 230b となる。酸化物 230a、酸化物 230c を上述の構成とすることで、酸化物 230a と酸化物 230b との界面、および酸化物 230b と酸化物 230c との界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ 200 は高いオン電流、および高い周波数特性を得ることができる。

#### 【0064】

酸化物 230 は、酸化物半導体として機能する金属酸化物を用いることが好ましい。例えば、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上のものを用いることが好ましい。このように、エネルギーギャップの大きい金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。このようなトランジスタを用いることで、低消費電力の半導体装置を提供できる。

#### 【0065】

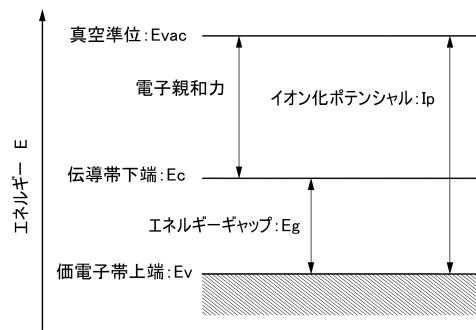

電子親和力または伝導帯下端のエネルギー準位  $E_c$  は、図 13 に示すように、真空準位と価電子帯上端のエネルギー  $E_v$ との差であるイオン化ポテンシャル  $I_p$  と、エネルギーギャップ  $E_g$  から求めることができる。イオン化ポテンシャル  $I_p$  は、例えば、紫外線光電子分光分析 (UPS : Ultraviolet Photoelectron Spectroscopy) 装置を用いて測定することができる。エネルギーギャップ  $E_g$  は、例えば、分光エリプソメータを用いて測定することができる。

#### 【0066】

また、酸化物半導体を用いたトランジスタは、酸化物半導体中のチャネル形成領域に不純物および酸素欠損が存在すると、電気特性が変動しやすく、信頼性が悪くなる場合があ

10

20

30

40

50

る。また、酸化物半導体中のチャネル形成領域に酸素欠損が含まれていると、トランジスタはノーマリーオン特性となりやすい。したがって、チャネル形成領域中の酸素欠損はできる限り低減されていることが好ましい。例えば、絶縁体250などを介して酸化物230に酸素を供給し、酸素欠損を補填すればよい。これにより、電気特性の変動を抑制し、安定した電気特性を有するとともに、信頼性を向上させたトランジスタを提供することができる。

#### 【0067】

また、酸化物半導体の近傍に配置された導電体が、金属、または合金からなる場合、酸化物半導体を構成する酸素原子により、当該導電体が酸化する場合がある。当該導電体が、酸化により導電性が低下する場合、半導体装置の電気特性のばらつきや、信頼性の低下などの原因となる蓋然性が高い。10

#### 【0068】

ここで、図14乃至図16を用いて、酸化物半導体が有する酸素原子による酸化物半導体と接する金属、または合金からなる構造体の酸化反応について説明する。以下では、具体的に、酸化物半導体としてIn-Ga-Zn酸化物、導電体として窒化タンタルを用いた場合の酸化反応について説明する。

#### 【0069】

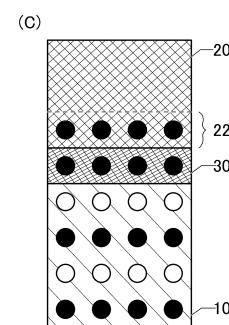

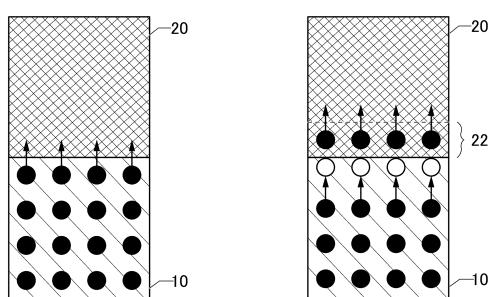

図14(A)は、In-Ga-Zn酸化物からなる酸化物半導体10と、および窒化タンタルからなる導電体20との積層体の断面において、界面近傍の領域を示す。なお、図中、各構造体に示す黒丸は酸素原子を示す。また、酸化物半導体10に示す白丸は、酸化物半導体中に生じた酸素欠損を示す。20

#### 【0070】

図14(B)は、導電体20の酸化反応の初期過程を示す。なお、導電体20において、酸素が低濃度で固溶した領域を酸素固溶領域22として示す。また、図14(C)は、導電体20の酸化反応により、生じた酸化物30の成長過程を示す。

#### 【0071】

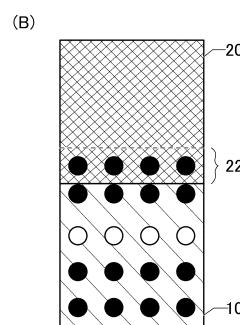

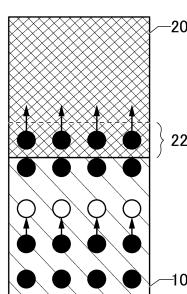

まず、図15を用いて、導電体20の酸化反応の初期過程を説明する。なお、図中矢印は、酸素原子の移動方向を示す。導電体20の酸化反応の初期過程では、導電体20の界面の金属原子タンタルと、酸化物半導体10の界面の酸素イオンが相互作用していると推測される。30

#### 【0072】

図15(A)に示すように、図中黒丸で示す酸素イオンは、酸化物半導体10と導電体20との界面に到達すると、導電体20の界面の金属原子タンタルと、吸着する。

#### 【0073】

図15(B)に示すように、酸素イオンが金属原子タンタルと吸着した状態で、加熱処理が行われた場合、酸素イオンは導電体20の内部に拡散し、窒化タンタル内部に、酸素固溶領域22が形成される(図15(B)参照)。なお、酸素固溶領域22が形成された時点では、まだ酸化反応は生じておらず、酸素イオンは、導電体20の内部に不純物として固溶した状態である。また、酸素イオンが、導電体20に拡散することで、酸化物半導体10の界面には、一時的に、酸素欠損が生じる場合がある。40

#### 【0074】

なお、導電体20が、酸素を固溶できる容量は、導電体20の結晶性、または緻密さに依存すると推測される。また、酸化物半導体10の界面の酸素イオンが、導電体20に固溶することで、酸化物半導体10の界面に生じた酸素欠損には、酸化物半導体10の内部の酸素原子が補填される(図15(C)参照)。

#### 【0075】

図15(A)乃至図15(C)に示す過程を繰り返すことにより、酸素固溶領域22中の酸素濃度は高くなる。ここで、酸素固溶領域22中の酸素の固溶が飽和すると、酸素固溶領域22中の金属原子タンタルの酸化が開始する。従って、図15(D)に示すように、酸化物半導体10と導電体20との間に、酸化タンタルを含む酸化物30が形成される。50

**【 0 0 7 6 】**

なお、金属の酸化反応の初期過程において、一般的には酸化物の核生成が生じることが知られている。一方で、酸化物半導体を用いた半導体装置の作製工程でかかる熱履歴は、比較的低温であるため、酸化物半導体 10 と導電体 20 との界面には非晶質の酸化物の薄膜が形成されると推測される。

**【 0 0 7 7 】**

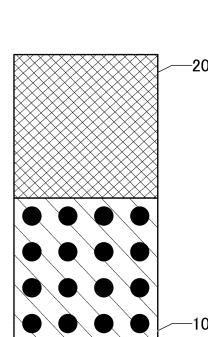

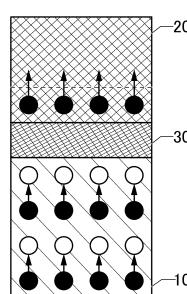

続いて、図 16 を用いて、酸化物半導体 10 と導電体 20 との間に生じた酸化物 30 の成長過程を説明する。酸化物 30 が生じることで、酸化物 30 と酸化物半導体 10 との界面は、酸素が欠乏し、酸素欠損の濃度が高い状態となる。つまり、酸化物半導体 10 中には、酸素欠損の濃度勾配が生じていると考えられる。

10

**【 0 0 7 8 】**

従って、図 16 (A) 乃至図 16 (C) に示すように、酸化物半導体 10 において、酸素欠損の濃度を均一化するため、酸化物半導体 10 の内部の酸素イオンが拡散する。当該酸素イオンが、酸化物 30 との界面に到達すると考えられる(図 16 (A) 参照)。さらに、当該到達した酸素イオンは、酸化物 30 が有する酸化タンタルの成長反応に使われ、酸化物 30 が増膜する(図 16 (B) および図 16 (C) 参照)。

**【 0 0 7 9 】**

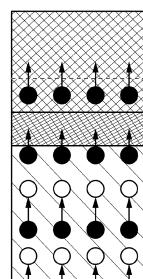

酸化タンタルを有する酸化物 30 において、界面の欠陥の影響を考慮しない場合、一般的には酸化反応は酸化物 30 の薄膜内の金属および酸素イオンの拡散速度に依存する。

20

**【 0 0 8 0 】**

従って、酸素イオンの拡散により、酸化物半導体 10 、および酸化物 30 の内部では、酸素濃度の勾配が生じる。その場合、酸化物 30 中での酸素イオンの拡散速度が、酸化物 30 における酸化タンタルの成長速度を決める要因になると推測できる。なお、拡散種が酸素イオンの場合は、酸化物 30 の酸化タンタル内で拡散し、酸化物 30 および導電体 20 の界面に到達することにより、新たな酸化タンタルを生成し、酸化物 30 の増膜が起こると考えられる。また、本酸化反応の成長過程において、導電体 20 の酸素固溶領域 22 は導電体 20 内部へと拡張していくと考えられる。

**【 0 0 8 1 】**

上述のような導電体の酸化反応を抑制するために、本発明の一態様のトランジスタ 200 は、図 1 (B) に示すように、酸化物 230 b と、ソース電極またはドレイン電極として機能する導電体 242 (導電体 242 a より導電体 242 b ) と、の間に酸化物 243 (酸化物 243 a および酸化物 243 b ) が配置されている。導電体 242 と、酸化物 230 とが接しない構成となるので、導電体 242 が、酸化物 230 の酸素を吸収することを抑制できる。つまり、導電体 242 の酸化を防止することで、導電体 242 の導電率の低下を抑制することができる。従って、酸化物 243 は、導電体 242 の酸化を抑制する機能を有することが好ましい。

30

**【 0 0 8 2 】**

従って、酸化物 243 は、酸素の透過を抑制する機能を有することが好ましい。ソース電極やドレイン電極として機能する導電体 242 と酸化物 230 b との間に酸素の透過を抑制する機能を有する酸化物 243 を配置することで、導電体 242 と、酸化物 230 b との間の電気抵抗が低減されるので好ましい。このような構成とすることで、トランジスタ 200 の電気特性およびトランジスタ 200 の信頼性を向上させることができる。

40

**【 0 0 8 3 】**

酸化物 243 として、元素 M を有する金属酸化物を用いてもよい。特に、元素 M は、アルミニウム、ガリウム、イットリウム、または錫を用いるとよい。酸化物 243 は、酸化物 230 b よりも元素 M の濃度が高いことが好ましい。また、酸化物 243 として、酸化ガリウムを用いてもよい。また、酸化物 243 として、In - M - Zn 酸化物等の金属酸化物を用いてもよい。具体的には、酸化物 243 に用いる金属酸化物において、In に対する元素 M の原子数比が、酸化物 230 b に用いる金属酸化物における、In に対する元素 M の原子数比より大きいことが好ましい。また、酸化物 243 の膜厚は、0.5 nm 以

50

上 5 nm 以下が好ましく、より好ましくは、1 nm 以上 3 nm 以下である。また、酸化物 243 は、結晶性を有すると好ましい。酸化物 243 が結晶性を有する場合、酸化物 230 中の酸素の放出を好適に抑制することが出来る。例えば、酸化物 243 としては、六方晶などの結晶構造であれば、酸化物 230 中の酸素の放出を抑制できる場合がある。

#### 【0084】

本発明の一態様であるトランジスタ 200 は、図 1 (B) (C) に示すように、絶縁体 282 と、絶縁体 250 とが、直接接する構造となっている。このような構造とすることで、絶縁体 280 に含まれる酸素が、導電体 260 に吸収され難くなる。従って、絶縁体 280 に含まれる酸素は、酸化物 230c を介して、酸化物 230a および酸化物 230b へ効率よく注入することができる。酸化物 230a 中および酸化物 230b 中の酸素欠損を低減し、トランジスタ 200 の電気特性および信頼性を向上させることができる。また、絶縁体 280 に含まれる水素などの不純物が絶縁体 250 へ混入することを抑えることができるので、トランジスタ 200 の電気特性および信頼性への悪影響を抑制することができる。絶縁体 282 としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、または酸化ハフニウムを用いることができる。

#### 【0085】

絶縁体 272、および絶縁体 273 は、水素や水などの不純物および酸素の透過を抑制する機能を有することが好ましい。

#### 【0086】

図 3 (A) は、図 1 (A) に A5 - A6 の一点鎖線で示す部位の断面を拡大した図であり、トランジスタ 200 のソース領域またはドレイン領域のチャネル幅方向の断面図である。図 3 (A) に示すように、導電体 242b の上面、導電体 242b の側面、酸化物 230a の側面、および酸化物 230b の側面は、絶縁体 272、および絶縁体 273 で覆う構造となっているので、導電体 242b の側面および導電体 242b の上面方向から導電体 242b への水素や水などの不純物および酸素の拡散を抑制することができる。また、導電体 242b の下面是酸化物 243b と接する構造となっており、酸化物 230b の酸素は、酸化物 243b によってブロックされるので導電体 242b へ拡散することを抑制する。従って、導電体 242b の周囲からの導電体 242b への酸素の拡散を抑制することができるので、導電体 242b の酸化を抑制することができる。尚、導電体 242a についても同様の効果を有する。また、酸化物 230a の側面、および酸化物 230b の側面方向から酸化物 230a および酸化物 230b への水素や水などの不純物の拡散を抑制することができる。絶縁体 272 としては、例えば、酸化アルミニウム、酸化ハフニウム、酸化ガリウム、インジウムガリウム亜鉛酸化物、酸化シリコン膜、窒化シリコン膜、または窒化酸化シリコン膜を用いることができる。また、絶縁体 273 としては、例えば、酸化アルミニウム、または酸化ハフニウムを用いることができる。

#### 【0087】

図 3 (B) は、図 1 (B) のトランジスタ 200 の右半分を拡大した図である。導電体 240b の左側の側面(図 3 (B) に点線で囲んだ箇所)は、酸化物 230c が接しており、絶縁体 250 からの水素や水などの不純物および酸素が導電体 240b へ拡散することを抑制することができる。また、導電体 240b の右側の側面は、絶縁体 272 が接しており、絶縁体 280 からの水素や水などの不純物および酸素が導電体 240b へ拡散することを抑制することができる。尚、導電体 240a についても、同様の効果を有する。

#### 【0088】

以上のように導電体 240 の周囲を水素や水などの不純物および酸素の透過を抑制する機能を有する絶縁体 272、酸化物 230c、および酸化物 243b で囲む構成とすることで、導電体 240 の酸化を抑制し、トランジスタ 200 の電気特性の向上およびトランジスタ 200 の信頼性を向上させることができる。

#### 【0089】

また、図 1 (C) に示すように、絶縁体 224 の底面を基準として、酸化物 230a および酸化物 230b と、導電体 260 とが、重ならない領域における導電体 260 の底面

10

20

30

40

50

の高さは、酸化物 230 b の底面の高さより低い位置に配置されていることが好ましい。また、酸化物 230 b と、導電体 260 とが、重ならない領域における導電体 260 の底面の高さと、酸化物 230 b の底面の高さとの差は、0 nm 以上 100 nm 以下、好ましくは、3 nm 以上 50 nm 以下、より好ましくは、5 nm 以上 20 nm 以下とする。

#### 【0090】

このように、ゲートとして機能する導電体 260 が、チャネル形成領域の酸化物 230 b の側面および上面を酸化物 230 c および絶縁体 250 を介して覆う構成となっており、導電体 260 の電界をチャネル形成領域の酸化物 230 b 全体に作用させやすくなる。よって、トランジスタ 200 のオン電流を増大させ、周波数特性を向上させることができると。

10

#### 【0091】

以上より、オン電流が大きいトランジスタを有する半導体装置を提供することができる。または、高い周波数特性を有するトランジスタを有する半導体装置を提供することができる。または、電気特性の変動を抑制し、安定した電気特性を有するとともに、信頼性を向上させた半導体装置を提供することができる。または、オフ電流が小さいトランジスタを有する半導体装置を提供することができる。

#### 【0092】

以下では、本発明の一態様に係るトランジスタ 200 を有する半導体装置の詳細な構成について説明する。

#### 【0093】

導電体 205 は、酸化物 230 、および導電体 260 と、重なるように配置する。また、導電体 205 は、絶縁体 214 および絶縁体 216 に埋め込まれて設けることが好ましい。

20

#### 【0094】

ここで、導電体 260 は、第 1 のゲート（トップゲートともいう）電極として機能する場合がある。また、導電体 205 は、第 2 のゲート（ボトムゲートともいう）電極として機能する場合がある。その場合、導電体 205 に印加する電位を、導電体 260 に印加する電位と、連動させず、独立して変化させることで、トランジスタ 200 の V<sub>th</sub> を制御することができる。特に、導電体 205 に負の電位を印加することにより、トランジスタ 200 の V<sub>th</sub> を 0 V より大きくし、オフ電流を低減することが可能となる。したがって、導電体 205 に負の電位を印加したほうが、印加しない場合よりも、導電体 260 に印加する電位が 0 V のときのドレイン電流を小さくすることができる。

30

#### 【0095】

なお、導電体 205 は、図 1 (A) に示すように、酸化物 230 の導電体 242 a および導電体 242 b と重ならない領域の大きさよりも、大きく設けるとよい。特に、図 1 (C) に示すように、導電体 205 は、酸化物 230 のチャネル幅方向と交わる端部よりも外側の領域においても、延伸していることが好ましい。つまり、酸化物 230 のチャネル幅方向における側面の外側において、導電体 205 と、導電体 260 とは、絶縁体を介して重畠していることが好ましい。または、導電体 205 を大きく設けることによって、導電体 205 形成以降の作製工程のプラズマを用いた処理において、局所的なチャージング（チャージアップと言う）の緩和ができる場合がある。ただし、本発明の一態様はこれに限定されない。導電体 205 は、少なくとも導電体 242 a と、導電体 242 b との間に位置する酸化物 230 と重畠すればよい。

40

#### 【0096】

上記構成を有することで、第 1 のゲートとしての機能を有する導電体 260 の電界と、第 2 のゲートとしての機能を有する導電体 205 の電界によって、チャネル形成領域を電気的に取り囲むことができる。本明細書において、第 1 のゲート、および第 2 のゲートの電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を、surround channel (S-channel) 構造とよぶ。

#### 【0097】

50

また、導電体 205a は、水または水素などの不純物および酸素の透過を抑制する導電体が好ましい。例えば、チタン、窒化チタン、タンタル、または窒化タンタルを用いることができる。また、導電体 205b は、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。なお、導電体 205 を 2 層で図示したが、3 層以上の多層構造としてもよい。

#### 【0098】

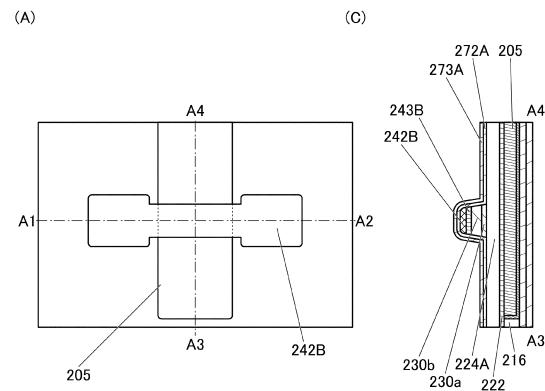

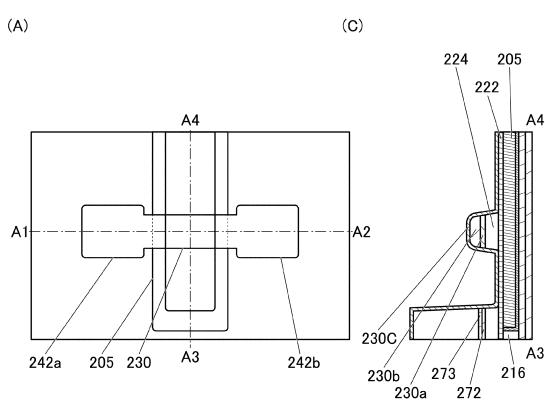

導電体 205 を 5 層とした一例を図 2 に示す。導電体 205 は、絶縁体 216 の開口の内壁に接して導電体 205c が形成され、さらに内側に導電体 205d が形成されている。また、導電体 205d の内側に導電体 205e が形成されている。さらに、導電体 205d の内壁に接し、かつ導電体 205e の上面に接するように導電体 205f が形成され、導電体 205f の内側に導電体 205g が形成されている。ここで、導電体 205c、導電体 205d、導電体 205e、および導電体 205f の上面の高さと、絶縁体 216 の上面の高さは同程度にできる。また、導電体 205c は、導電体 205a と同様の材料を用いることが好ましく、導電体 205e および導電体 205g は、導電体 205b と同様の材料を用いることが好ましい。

10

#### 【0099】

ここで、酸化物半導体と、酸化物半導体の下層に位置する絶縁体、または導電体と、酸化物半導体の上層に位置する絶縁体、または導電体とを、大気開放を行わずに、異なる膜種を連続成膜することで、不純物（特に、水素、水）の濃度が低減された、実質的に高純度真性である酸化物半導体膜を成膜することができるので好ましい。

20

#### 【0100】

例えば、6つの処理チャンバーを有する成膜装置を用いて、絶縁体 216、および導電体 205 上に配置される、絶縁体 222、絶縁体 224 となる絶縁膜、酸化物 230a となる酸化膜、酸化物 230b となる酸化膜、酸化物 243 となる酸化膜、および導電体 242 となる導電膜を順に連続成膜すればよい。

#### 【0101】

絶縁体 212、絶縁体 214、絶縁体 272、絶縁体 282、絶縁体 283 および絶縁体 281 は、水または水素などの不純物が、基板側から、または、上方からトランジスタ 200 に混入するのを抑制するバリア絶縁膜として機能することが好ましい。したがって、絶縁体 212、絶縁体 214、絶縁体 272、絶縁体 282、絶縁体 283 および絶縁体 281 は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子（N<sub>2</sub>O、NO、NO<sub>2</sub>など）、銅原子などの不純物の拡散を抑制する機能を有する（上記不純物が透過しにくい）絶縁性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有する（上記酸素が透過しにくい）絶縁性材料を用いることが好ましい。

30

#### 【0102】

例えば、絶縁体 212、絶縁体 283、および絶縁体 281 として、窒化シリコンなどを用い、絶縁体 214、絶縁体 272、および絶縁体 283 として、酸化アルミニウムなどを用いることが好ましい。これにより、水または水素などの不純物が絶縁体 212、および絶縁体 214 を介して、基板側からトランジスタ 200 側に拡散するのを抑制することができる。または、絶縁体 224 などに含まれる酸素が、絶縁体 212、および絶縁体 214 を介して基板側に、拡散するのを抑制することができる。また、水または水素などの不純物が絶縁体 272 よりも上方に配置されている絶縁体 280、および導電体 246 などから絶縁体 272 を介してトランジスタ 200 側に拡散するのを抑制することができる。この様に、トランジスタ 200 を、水または水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁体 212、絶縁体 214、絶縁体 282、および絶縁体 283 で取り囲む構造とすることが好ましい。

40

#### 【0103】

また、絶縁体 212、絶縁体 283、および絶縁体 281 の抵抗率を低くすることが好ましい場合がある。例えば、絶縁体 212、絶縁体 283、および絶縁体 281 の抵抗率

50

を概略  $1 \times 10^{13}$  cm とすることで、半導体装置作製工程のプラズマ等を用いる処理において、絶縁体 212、絶縁体 283、および絶縁体 281が、導電体 205、導電体 242 または導電体 260 のチャージアップを緩和することができる場合がある。絶縁体 212、絶縁体 283、および絶縁体 281 の抵抗率は、好ましくは、 $1 \times 10^{10}$  cm 以上  $1 \times 10^{15}$  cm 以下とする。

#### 【0104】

また、絶縁体 216、絶縁体 280、および絶縁体 274 は、絶縁体 214 よりも誘電率が低いことが好ましい。誘電率が低い材料を層間膜として、配線間に生じる寄生容量を低減することができる。例えば、絶縁体 216、絶縁体 280、および絶縁体 274 として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、または空孔を有する酸化シリコンなどを適宜用いればよい。10

#### 【0105】

絶縁体 222、および絶縁体 224 は、ゲート絶縁体としての機能を有する。

#### 【0106】

ここで、酸化物 230 と接する絶縁体 224 は、加熱により酸素を脱離することが好ましい。本明細書では、加熱により離脱する酸素を過剰酸素と呼ぶことがある。例えば、絶縁体 224 は、酸化シリコンまたは酸化窒化シリコンなどを適宜用いればよい。酸素を含む絶縁体を酸化物 230 に接して設けることにより、酸化物 230 中の酸素欠損を低減し、トランジスタ 200 の信頼性を向上させることができる。20

#### 【0107】

絶縁体 224 として、具体的には、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。加熱により酸素を脱離する酸化物とは、昇温脱離ガス分析 (TDS (Thermal Desorption Spectroscopy) 分析) にて、酸素分子の脱離量が  $1.0 \times 10^{18}$  molecules/cm<sup>3</sup> 以上、好ましくは  $1.0 \times 10^{19}$  molecules/cm<sup>3</sup> 以上、さらに好ましくは  $2.0 \times 10^{19}$  molecules/cm<sup>3</sup> 以上、または  $3.0 \times 10^{20}$  molecules/cm<sup>3</sup> 以上である酸化物膜である。なお、上記 TDS 分析時における膜の表面温度としては 100 以上 700 以下、または 100 以上 400 以下の範囲が好ましい。

#### 【0108】

絶縁体 222 は、水または水素などの不純物が、基板側からトランジスタ 200 に混入するのを抑制するバリア絶縁膜として機能することが好ましい。例えば、絶縁体 222 は、絶縁体 224 より水素透過性が低いことが好ましい。絶縁体 222、および絶縁体 272 によって、絶縁体 224 および酸化物 230 などを囲むことにより、外方から水または水素などの不純物がトランジスタ 200 に侵入することを抑制することができる。30

#### 【0109】

さらに、絶縁体 222 は、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有する（上記酸素が透過しにくい）ことが好ましい。例えば、絶縁体 222 は、絶縁体 224 より酸素透過性が低いことが好ましい。絶縁体 222 が、酸素や不純物の拡散を抑制する機能を有することで、酸化物 230 が有する酸素が、絶縁体 222 より下側へ拡散することを低減できるので、好ましい。また、導電体 205 が、絶縁体 224 や、酸化物 230 が有する酸素と反応することを抑制することができる。40

#### 【0110】

絶縁体 222 は、絶縁性材料であるアルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いるとよい。アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体として、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物（ハフニウムアルミネート）などを用いることが好ましい。このような材料を用いて絶縁体 222 を形成した場合、絶縁体 222 は、酸化物 230 からの酸素の放出や、トランジスタ 200 の周辺部から酸化物 230 への水素等の不純物の混入を抑制する層として機能する。50

**【0111】**

または、これらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニアを添加してもよい。またはこれらの絶縁体を窒化処理してもよい。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

**【0112】**

また、絶縁体222は、例えば、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニア、チタン酸ジルコン酸鉛(PZT)、チタン酸ストロンチウム(SrTiO<sub>3</sub>)または(Ba,Sr)TiO<sub>3</sub>(BST)などのいわゆるhig h-k材料を含む絶縁体を単層または積層で用いてもよい。トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体にhig h-k材料を用いることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。

10

**【0113】**

なお、絶縁体222、および絶縁体224が、2層以上の積層構造を有していてもよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。

**【0114】**

酸化物230b上には、酸化物243が設けられ、酸化物243上には、ソース電極、およびドレイン電極として機能する導電体242(導電体242a、および導電体242b)が設けられる。導電体242の膜厚は、例えば、1nm以上50nm以下、好ましくは2nm以上25nm以下、とすればよい。

20

**【0115】**

導電体242としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タンゲステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニア、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タンゲステン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。

30

**【0116】**

絶縁体250は、ゲート絶縁体として機能する。絶縁体250は、酸化物230cの上面に接して配置することが好ましい。絶縁体250は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対し安定であるため好ましい。

40

**【0117】**

絶縁体224と同様に、絶縁体250は、加熱により酸素が放出される絶縁体を用いて形成することが好ましい。加熱により酸素が放出される絶縁体を、絶縁体250として、酸化物230cの上面に接して設けることにより、酸化物230bのチャネル形成領域に効果的に酸素を供給することができる。また、絶縁体224と同様に、絶縁体250中の水または水素などの不純物濃度が低減されていることが好ましい。絶縁体250の膜厚は、1nm以上20nm以下とするのが好ましい。

**【0118】**

50

また、絶縁体 250 と導電体 260 との間に金属酸化物を設けてもよい。当該金属酸化物は、絶縁体 250 から導電体 260 への酸素拡散を抑制することが好ましい。酸素の拡散を抑制する金属酸化物を設けることで、絶縁体 250 から導電体 260 への酸素の拡散が抑制される。つまり、酸化物 230 へ供給する酸素量の減少を抑制することができる。また、絶縁体 250 の酸素による導電体 260 の酸化を抑制することができる。

#### 【0119】

また、当該金属酸化物は、ゲート絶縁体の一部としての機能を有する場合がある。したがって、絶縁体 250 に酸化シリコンや酸化窒化シリコンなどを用いる場合、当該金属酸化物は、比誘電率が高い  $h_{i g h-k}$  材料である金属酸化物を用いることが好ましい。ゲート絶縁体を、絶縁体 250 と当該金属酸化物との積層構造とすることで、熱に対して安定、かつ比誘電率の高い積層構造とすることができます。したがって、ゲート絶縁体の物理膜厚を保持したまま、トランジスタ動作時に印加するゲート電位の低減化が可能となる。また、ゲート絶縁体として機能する絶縁体の等価酸化膜厚 (EOT) の薄膜化が可能となる。

10

#### 【0120】

具体的には、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タンゲステン、チタン、タンタル、ニッケル、ゲルマニウム、または、マグネシウムなどから選ばれた一種、または二種以上が含まれた金属酸化物を用いることができる。特に、アルミニウム、またはハフニウムの一方または双方の酸化物を含む絶縁体である、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物（ハフニウムアルミネート）などを用いることが好ましい。

20

#### 【0121】

または、当該金属酸化物は、ゲートの一部としての機能を有する場合がある。この場合は、酸素を含む導電性材料をチャネル形成領域側に設けるとよい。酸素を含む導電性材料をチャネル形成領域側に設けることで、当該導電性材料から離脱した酸素がチャネル形成領域に供給されやすくなる。

#### 【0122】

特に、ゲートとして機能する導電体として、チャネルが形成される金属酸化物に含まれる金属元素および酸素を含む導電性材料を用いることが好ましい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。このような材料を用いることで、チャネルが形成される金属酸化物に含まれる水素を捕獲することができる場合がある。または、外方の絶縁体などから混入する水素を捕獲することができる場合がある。

30

#### 【0123】

導電体 260 は、図 1 では 2 層構造として示しているが、単層構造でもよいし、3 層以上の積層構造であってもよい。

#### 【0124】

導電体 260a は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子 ( $N_2O$ 、 $NO$ 、 $NO_2$  など)、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

40

#### 【0125】

また、導電体 260a が酸素の拡散を抑制する機能を持つことにより、絶縁体 250 に含まれる酸素により、導電体 260b が酸化して導電率が低下することを抑制することができる。酸素の拡散を抑制する機能を有する導電性材料としては、例えば、タンタル、窒化タンタル、ルテニウム、または酸化ルテニウムなどを用いることが好ましい。

#### 【0126】

50

また、導電体 260 b は、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体 260 は、配線としても機能するため、導電性が高い導電体を用いることが好ましい。例えば、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることができる。また、導電体 260 b は積層構造としてもよく、例えば、チタン、窒化チタンと上記導電性材料との積層構造としてもよい。

#### 【0127】

絶縁体 280 は、例えば、絶縁体 280 として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、または空孔を有する酸化シリコンなどを有することが好ましい。特に、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため好ましい。特に、酸化シリコン、酸化窒化シリコン、空孔を有する酸化シリコンなどの材料は、加熱により脱離する酸素を含む領域を容易に形成するため好ましい。

#### 【0128】

絶縁体 280 中の水または水素などの不純物濃度が低減されていることが好ましい。また、絶縁体 280 の上面は、平坦化されてもよい。

#### 【0129】

絶縁体 282 は、水または水素などの不純物が、上方から絶縁体 280 に混入するのを抑制するバリア絶縁膜として機能することが好ましい。絶縁体 282 としては、例えば、酸化アルミニウム、窒化シリコン、または窒化酸化シリコンなどの絶縁体を用いればよい。

#### 【0130】

また、絶縁体 282 の上に、層間膜として機能する絶縁体 274 を設けることが好ましい。絶縁体 274 は、絶縁体 224 などと同様に、膜中の水または水素などの不純物濃度が低減されていることが好ましい。

#### 【0131】

導電体 240 a および導電体 240 b は、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体 240 a および導電体 240 b は積層構造としてもよい。

#### 【0132】

また、導電体 240 を積層構造とする場合、絶縁体 281、絶縁体 274、絶縁体 282、絶縁体 280、絶縁体 273、および絶縁体 272 と接する導電体には、水または水素などの不純物の透過を抑制する機能を有する導電性材料を用いることが好ましい。例えば、タンタル、窒化タンタル、チタン、窒化チタン、ルテニウム、または酸化ルテニウムなどを用いることが好ましい。また、水または水素などの不純物の透過を抑制する機能を有する導電性材料は、単層または積層で用いてもよい。当該導電性材料を用いることで、絶縁体 280 に添加された酸素が導電体 240 a および導電体 240 b に吸収されるのを防ぐことができる。また、絶縁体 281 より上層から水または水素などの不純物が、導電体 240 a および導電体 240 b を通じて酸化物 230 に混入するのを抑制することができる。

#### 【0133】

絶縁体 241 a および絶縁体 241 b としては、例えば、酸化アルミニウム、窒化シリコン、または窒化酸化シリコンなどの絶縁体を用いればよい。絶縁体 241 a および絶縁体 241 b は、絶縁体 272、および絶縁体 273 に接して設けられるので、絶縁体 280 などから水または水素などの不純物が、導電体 240 a および導電体 240 b を通じて酸化物 230 に混入するのを抑制することができる。また、絶縁体 280 に含まれる酸素が導電体 240 a および導電体 240 b に吸収されるのを防ぐことができる。

#### 【0134】

また、導電体 240 a の上面、および導電体 240 b の上面に接して配線として機能する導電体 246 (導電体 246 a、および導電体 246 b) を配置してもよい。導電体 246 は、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、当該導電体は、積層構造としてもよく、例えば、チタン、窒化チタン

10

20

30

40

50

と上記導電性材料との積層としてもよい。なお、当該導電体は、絶縁体に設けられた開口に埋め込むように形成してもよい。

#### 【0135】

##### <半導体装置の構成材料>

以下では、半導体装置に用いることができる構成材料について説明する。

#### 【0136】

##### <基板>

トランジスタ200を形成する基板としては、例えば、絶縁体基板、半導体基板、または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板（イットリア安定化ジルコニア基板など）、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば、SOI（Silicon On Insulator）基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

10

20

#### 【0137】

##### <絶縁体>

絶縁体としては、絶縁性を有する酸化物、窒化物、酸化窒化物、窒化酸化物、金属酸化物、金属酸化窒化物、金属窒化酸化物などがある。

#### 【0138】

例えば、トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体に、high-k材料を用いることで物理膜厚を保ちながら、トランジスタ動作時の低電圧化が可能となる。一方、層間膜として機能する絶縁体には、比誘電率が低い材料を用いることで、配線間に生じる寄生容量を低減することができる。したがって、絶縁体の機能に応じて、材料を選択するとよい。

30

#### 【0139】

また、比誘電率の高い絶縁体としては、酸化ガリウム、酸化ハフニウム、酸化ジルコニアム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物、またはシリコンおよびハフニウムを有する窒化物などがある。

#### 【0140】

また、比誘電率が低い絶縁体としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコン、または樹脂などがある。

40

#### 【0141】

また、酸化物半導体を用いたトランジスタは、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体で囲うことによって、トランジスタの電気特性を安定にすることができる。水素などの不純物および酸素の透過を抑制する機能を有する絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニアム、ランタン、ネオジム、ハフニウム、またはタンタルを含む絶縁体を、単層で、または積層で用いればよい。具体的には、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体として、酸化アルミニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、

50

酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、または酸化タンタルなどの金属酸化物、窒化アルミニウム、窒化アルミニウムチタン、窒化チタン、窒化酸化シリコンまたは窒化シリコンなどの金属窒化物を用いることができる。

#### 【0142】

また、ゲート絶縁体として機能する絶縁体は、加熱により脱離する酸素を含む領域を有する絶縁体であることが好ましい。例えば、加熱により脱離する酸素を含む領域を有する酸化シリコンまたは酸化窒化シリコンを酸化物230と接する構造とすることで、酸化物230が有する酸素欠損を補償することができる。

#### 【0143】

<導電体>

導電体としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンなどから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タングステン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

#### 【0144】

また、上記の材料で形成される導電層を複数積層して用いてもよい。例えば、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、酸素を含む導電性材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。

#### 【0145】

なお、トランジスタのチャネル形成領域に酸化物を用いる場合において、ゲートとして機能する導電体には、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造を用いることが好ましい。この場合は、酸素を含む導電性材料をチャネル形成領域側に設けるとよい。酸素を含む導電性材料をチャネル形成領域側に設けることで、当該導電性材料から離脱した酸素がチャネル形成領域に供給されやすくなる。

#### 【0146】

特に、ゲートとして機能する導電体として、チャネルが形成される金属酸化物に含まれる金属元素および酸素を含む導電性材料を用いることが好ましい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。例えば、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。このような材料を用いることで、チャネルが形成される金属酸化物に含まれる水素を捕獲することができる場合がある。または、外方の絶縁体などから混入する水素を捕獲することができる場合がある。

#### 【0147】

<金属酸化物>

酸化物230として、酸化物半導体として機能する金属酸化物を用いることが好ましい

10

20

30

40

50

。以下では、本発明に係る酸化物 230 に適用可能な金属酸化物について説明する。

#### 【0148】

金属酸化物は、少なくともインジウムまたは亜鉛を含むことが好ましい。特に、インジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウムまたは錫などが含まれていることが好ましい。また、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

#### 【0149】

ここでは、金属酸化物が、インジウム、元素Mおよび亜鉛を有するIn-M-Zn酸化物である場合を考える。なお、元素Mは、アルミニウム、ガリウム、イットリウム、または錫などとする。そのほかの元素Mに適用可能な元素としては、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。

10

#### 【0150】

なお、本明細書等において、窒素を有する金属酸化物も金属酸化物(metal oxide)と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物(metal oxy nitride)と呼称してもよい。

#### 【0151】

20

#### [金属酸化物の構造]

酸化物半導体(金属酸化物)は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、CAAC-OS、多結晶酸化物半導体、nc-OS、擬似非晶質酸化物半導体(a-like OS: amorphous-like oxide semiconductor)、および非晶質酸化物半導体などがある。

#### 【0152】

CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域との間で格子配列の向きが変化している箇所を指す。

30

#### 【0153】

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合がある。また、歪みにおいて、五角形、および七角形などの格子配列を有する場合がある。なお、CAAC-OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウンダリーともいう)を確認することは難しい。すなわち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、CAAC-OSが、a-b面方向において酸素原子の配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためである。

#### 【0154】

40

また、CAAC-OSは、インジウム、および酸素を有する層(以下、In層)と、元素M、亜鉛、および酸素を有する層(以下、(M,Zn)層)とが積層した、層状の結晶構造(層状構造ともいう)を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能であり、(M,Zn)層の元素Mがインジウムと置換した場合、(In,M,Zn)層と表すこともできる。また、In層のインジウムが元素Mと置換した場合、(In,M)層と表すこともできる。

#### 【0155】

CAAC-OSは結晶性の高い金属酸化物である。一方、CAAC-OSは、明確な結晶粒界を確認することが難しいため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、金属酸化物の結晶性は不純物の混入や欠陥の生成などによって低下す

50

る場合があるため、C A A C - O S は不純物や欠陥（酸素欠損（V<sub>O</sub>: oxygen vacancyともいう）など）の少ない金属酸化物ともいえる。したがって、C A A C - O S を有する金属酸化物は、物理的性質が安定する。そのため、C A A C - O S を有する金属酸化物は熱に強く、信頼性が高い。

#### 【0156】

n c - O S は、微小な領域（例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。

10

#### 【0157】

なお、インジウムと、ガリウムと、亜鉛と、を有する金属酸化物の一種である、インジウム - ガリウム - 亜鉛酸化物（以下、I G Z O）は、上述のナノ結晶とすることで安定な構造をとる場合がある。特に、I G Z O は、大気中では結晶成長がし難い傾向があるため、大きな結晶（ここでは、数mmの結晶、または数cmの結晶）よりも小さな結晶（例えば、上述のナノ結晶）とする方が、構造的に安定となる場合がある。

#### 【0158】

a - l i k e O S は、n c - O S と非晶質酸化物半導体との間の構造を有する金属酸化物である。a - l i k e O S は、鬆または低密度領域を有する。すなわち、a - l i k e O S は、n c - O S およびC A A C - O S と比べて、結晶性が低い。

20

#### 【0159】

酸化物半導体（金属酸化物）は、多様な構造をとり、それぞれが異なる特性を有する。本発明の一態様の酸化物半導体は、非晶質酸化物半導体、多結晶酸化物半導体、a - l i k e O S 、n c - O S 、C A A C - O S のうち、二種以上を有していてもよい。

#### 【0160】

なお、本発明の一態様の半導体装置においては、酸化物半導体（金属酸化物）の構造に特に限定はないが、好ましくは結晶性を有すると好ましい。例えば、酸化物230をC A A C - O S 構造とし、酸化物243を六方晶の結晶構造とすることが出来る。酸化物230、及び酸化物243を上記の結晶構造とすることで、高い信頼性を有する半導体装置とすることが出来る。また、酸化物230a、酸化物230c、および酸化物243を概略同じ組成とすることができます。

30

#### 【0161】

##### [不純物]

ここで、金属酸化物中における各不純物の影響について説明する。

#### 【0162】

また、金属酸化物にアルカリ金属またはアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。したがって、アルカリ金属またはアルカリ土類金属が含まれている金属酸化物をチャネル形成領域に用いたトランジスタはノーマリーオン特性となりやすい。このため、金属酸化物中のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。具体的には、S I M S により得られる金属酸化物中のアルカリ金属またはアルカリ土類金属の濃度（二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる濃度）を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下にする。

40

#### 【0163】

また、金属酸化物に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。従って、水素が含まれている金属酸化物を用いたトランジスタは、ノーマリーオン特性となりやすい。

50

**【 0 1 6 4 】**

このため、金属酸化物中の水素はできる限り低減されていることが好ましい。具体的には、金属酸化物において、S I M Sにより得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>未満とする。不純物が十分に低減された金属酸化物をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

**【 0 1 6 5 】**

トランジスタの半導体に用いる金属酸化物として、結晶性の高い薄膜を用いることが好ましい。該薄膜を用いることで、トランジスタの安定性または信頼性を向上させることができる。該薄膜として、例えば、単結晶金属酸化物の薄膜または多結晶金属酸化物の薄膜が挙げられる。しかしながら、単結晶金属酸化物の薄膜または多結晶金属酸化物の薄膜を基板上に形成するには、高温またはレーザー加熱の工程が必要とされる。よって、製造工程のコストが増加し、さらに、スループットも低下してしまう。

10

**【 0 1 6 6 】**

2009年に、C A A C構造を有するIn-Ga-Zn酸化物(C A A C - I G Z Oと呼ぶ)が発見されたことが、非特許文献1および非特許文献2で報告されている。ここでは、C A A C - I G Z Oは、c軸配向性を有する、結晶粒界が明確に確認されない、低温で基板上に形成可能である、ことが報告されている。さらに、C A A C - I G Z Oを用いたトランジスタは、優れた電気特性および信頼性を有することが報告されている。

20

**【 0 1 6 7 】**

また、2013年には、n c構造を有するIn-Ga-Zn酸化物(n c - I G Z Oと呼ぶ)が発見された(非特許文献3参照)。ここでは、n c - I G Z Oは、微小な領域(例えば、1 nm以上3 nm以下の領域)において原子配列に周期性を有し、異なる該領域間で結晶方位に規則性が見られないことが報告されている。

**【 0 1 6 8 】**

非特許文献4および非特許文献5では、上記のC A A C - I G Z O、n c - I G Z O、および結晶性の低いI G Z Oのそれぞれの薄膜に対する電子線の照射による平均結晶サイズの推移が示されている。結晶性の低いI G Z Oの薄膜において、電子線が照射される前でさえ、1 nm程度の結晶性I G Z Oが観察されている。よって、ここでは、I G Z Oにおいて、完全な非晶質構造(completely amorphous structure)の存在を確認できなかった、と報告されている。さらに、結晶性の低いI G Z Oの薄膜と比べて、C A A C - I G Z Oの薄膜およびn c - I G Z Oの薄膜は電子線照射に対する安定性が高いことが示されている。よって、トランジスタの半導体として、C A A C - I G Z Oの薄膜またはn c - I G Z Oの薄膜を用いることが好ましい。

30

**【 0 1 6 9 】**

金属酸化物を用いたトランジスタは、非導通状態において極めてリーク電流が小さい、具体的には、トランジスタのチャネル幅1 μmあたりのオフ電流がy A / μm( $10^{-24}$  A / μm)オーダである、ことが非特許文献6に示されている。例えば、金属酸化物を用いたトランジスタのリーク電流が低いという特性を応用した低消費電力のC P Uなどが開示されている(非特許文献7参照)。

40

**【 0 1 7 0 】**

また、金属酸化物を用いたトランジスタのリーク電流が低いという特性を利用した、該トランジスタの表示装置への応用が報告されている(非特許文献8参照)。表示装置では、表示される画像が1秒間に数十回切り替っている。1秒間あたりの画像の切り替え回数はリフレッシュレートと呼ばれている。また、リフレッシュレートを駆動周波数と呼ぶこともある。このような人の目で知覚が困難である高速の画面の切り替えが、目の疲労の原因として考えられている。そこで、表示装置のリフレッシュレートを低下させて、画像の書き換え回数を減らすことが提案されている。また、リフレッシュレートを低下させた駆動により、表示装置の消費電力を低減することが可能である。このような駆動方法を、ア

50

イドリング・ストップ駆動と呼ぶ。

【0171】

C A A C 構造およびn c 構造の発見は、C A A C 構造またはn c 構造を有する金属酸化物を用いたトランジスタの電気特性および信頼性の向上、ならびに、製造工程のコスト低下およびスループットの向上に貢献している。また、該トランジスタのリーク電流が低いという特性を利用した、該トランジスタの表示装置およびL S Iへの応用研究が進められている。

【0172】

<半導体装置の作製方法>

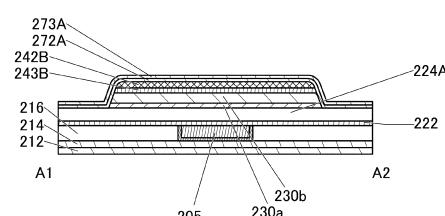

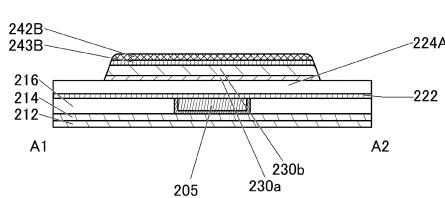

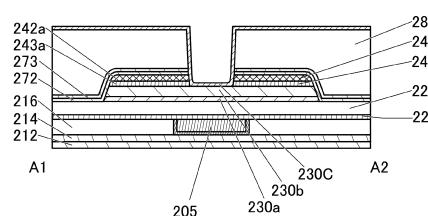

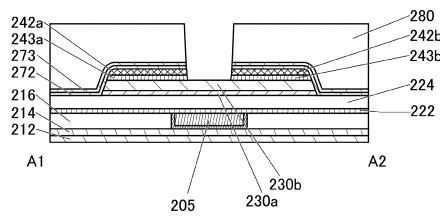

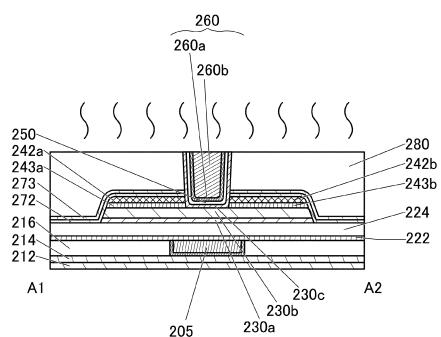

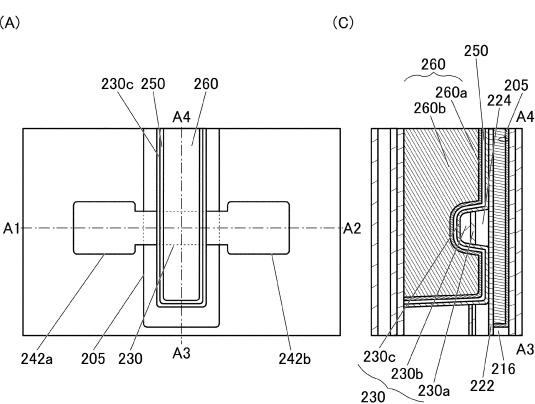

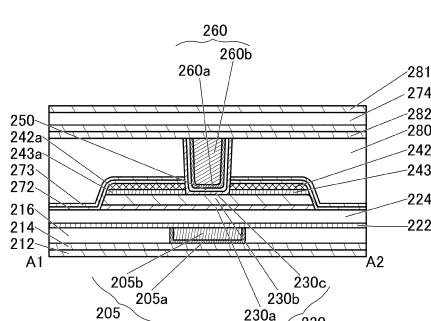

次に、図1に示す、本発明に係るトランジスタ200を有する半導体装置について、作製方法を図4乃至図12を用いて説明する。また、図4乃至図12において、各図の(A)は上面図を示す。また、各図の(B)は、(A)に示すA1-A2の一点鎖線で示す部位に対応する断面図であり、トランジスタ200のチャネル長方向の断面図でもある。また、各図の(C)は、(A)にA3-A4の一点鎖線で示す部位に対応する断面図であり、トランジスタ200のチャネル幅方向の断面図でもある。なお、各図の(A)の上面図では、図の明瞭化のために一部の要素を省いている。

10

【0173】

まず、基板(図示しない)を準備し、当該基板上に絶縁体212を成膜する。絶縁体212の成膜は、スパッタリング法、化学気相成長(C V D : C hemical V apor D e p o s i t i o n )法、分子線エピタキシー(M B E : M o l e c u l a r B e a m E p i t a x y )法、パルスレーザ堆積(P L D : P u l s e d L a s e r D e p o s i t i o n )法、またはA L D(A t o m i c L a y e r D e p o s i t i o n )法などを用いて行うことができる。

20

【0174】

なお、C V D法は、プラズマを利用するプラズマC V D(P E C V D : P la s m a E n h a n c e d C V D )法、熱を利用する熱C V D(T C V D : T her m a l C V D )法、光を利用する光C V D(P h o t o C V D )法などに分類できる。さらに用いる原料ガスによって金属C V D(M C V D : M e t a l C V D )法、有機金属C V D(M O C V D : M e t a l O rganic C V D )法に分けることができる。

30

【0175】

プラズマC V D法は、比較的低温で高品質の膜が得られる。また、熱C V D法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子(トランジスタ、容量素子など)などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱C V D法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱C V D法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

【0176】

また、A L D法は、原子の性質である自己制御性を利用して、一層ずつ原子を堆積することができる所以、極薄の成膜が可能、アスペクト比の高い構造への成膜が可能、ピンホールなどの欠陥の少ない成膜が可能、被覆性に優れた成膜が可能、および低温での成膜が可能、などの効果がある。また、A L D法には、プラズマを利用した成膜方法P E A L D(P la s m a E n h a n c e d A L D )法も含まれる。プラズマを利用して成膜することで、より低温での成膜が可能となり好ましい場合がある。なお、A L D法で用いるプリカーサには炭素などの不純物を含むものがある。このため、A L D法により設けられた膜は、他の成膜法により設けられた膜と比較して、炭素などの不純物を多く含む場合がある。なお、不純物の定量は、X線光電子分光法(X P S : X - r a y P h o t o e l e c t r o n S p e c t r o s c o p y )を用いて行うことができる。

40

【0177】

50

CVD法およびALD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、ALD法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、ALD法は、比較的成膜速度が遅いため、成膜速度の速いCVD法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

#### 【0178】

CVD法およびALD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法およびALD法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、CVD法およびALD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間を要しない分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。

10

#### 【0179】

本実施の形態では、絶縁体212として、CVD法によって窒化シリコンを成膜する。このように、絶縁体212として、窒化シリコンなどの銅が透過しにくい絶縁体を用いることにより、絶縁体212より下層(図示せず)の導電体に銅など拡散しやすい金属を用いても、当該金属が絶縁体212を介して上の層に拡散するのを抑制することができる。また、窒化シリコンのように水または水素などの不純物が透過しにくい絶縁体を用いることにより絶縁体212より下層から水または水素などの不純物の拡散を抑制することができる。

20

#### 【0180】

次に、絶縁体212上に絶縁体214を成膜する。絶縁体214の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。本実施の形態では、絶縁体214として、酸化アルミニウムを用いる。

#### 【0181】

次に、絶縁体214上に絶縁体216を成膜する。絶縁体216の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

30

#### 【0182】

次に、絶縁体216に絶縁体214に達する開口を形成する。開口とは、例えば、溝やスリットなども含まれる。また、開口が形成された領域を指して開口部とする場合がある。開口の形成はウェットエッチングを用いてもよいが、ドライエッチングを用いるほうが微細加工には好ましい。また、絶縁体214は、絶縁体216をエッチングして溝を形成する際のエッチングストップ膜として機能する絶縁体を選択することが好ましい。例えば、溝を形成する絶縁体216に酸化シリコン膜を用いた場合は、絶縁体214は窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜を用いるとよい。

#### 【0183】

開口の形成後に、導電体205となる導電膜を成膜する。該導電膜は、酸素の透過を抑制する機能を有する導電体を含むことが望ましい。たとえば、窒化タンタル、窒化タンゲステン、窒化チタンなどを用いることができる。またはタンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅、モリブデンタンゲステン合金との積層膜とすることができる。導電体205となる導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

40

#### 【0184】

本実施の形態では、導電体205となる導電膜として、多層構造とする。まず、スパッタリング法によって窒化タンタルを成膜し、当該窒化タンタルの上に窒化チタンを積層する。このような金属窒化物を導電体205となる導電膜の下層に用いることにより、後述

50

する導電体 205 となる導電膜の上層の導電膜として銅などの拡散しやすい金属を用いても、当該金属が導電体 205 から外に拡散するのを防ぐことができる。

#### 【0185】

次に、導電体 205 となる導電膜の上層の導電膜を成膜する。該導電膜の成膜は、メッキ法、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。本実施の形態では、導電体 205 となる導電膜の上層の導電膜として、銅などの低抵抗導電性材料を成膜する。

#### 【0186】

次に、CMP 处理 (Chemical Mechanical Polishing) を行うことで、導電体 205 となる導電膜の上層、ならびに導電体 205 となる導電膜の下層の一部を除去し、絶縁体 216 を露出する。その結果、開口部のみに、導電体 205 となる導電膜が残存する。これにより、上面が平坦な、導電体 205 を形成することができる。なお、当該 CMP 处理により、絶縁体 216 の一部が除去される場合がある（図 4 参照）。

10

#### 【0187】

ここからは、上記と異なる導電体 205 の形成方法について以下に説明する。

#### 【0188】

絶縁体 214 上に、導電体 205 となる導電膜を成膜する。導電体 205 となる導電膜の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。また、導電体 205 となる導電膜は、多層膜とすることができます。本実施の形態では、導電体 205 となる導電膜としてタンゲステンを成膜する。

20

#### 【0189】

次に、リソグラフィー法を用いて、導電体 205 となる導電膜を加工し、導電体 205 を形成する。

#### 【0190】

なお、リソグラフィー法では、まず、マスクを介してレジストを露光する。次に、露光された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電体、半導体または絶縁体などを所望の形状に加工することができる。例えば、KrF エキシマレーザ光、ArF エキシマレーザ光、EUV (Extreme Ultraviolet) 光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体（例えば水）を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、マスクは不要となる。なお、レジストマスクの除去には、アッティングなどのドライエッティング処理を行う、ウェットエッティング処理を行う、ドライエッティング処理後にウェットエッティング処理を行う、またはウェットエッティング処理後にドライエッティング処理を行うことができる。

30

#### 【0191】

また、レジストマスクの代わりに絶縁体や導電体からなるハードマスクを用いてもよい。ハードマスクを用いる場合、導電体 205 となる導電膜上にハードマスク材料となる絶縁膜や導電膜を形成し、その上にレジストマスクを形成し、ハードマスク材料をエッチングすることで所望の形状のハードマスクを形成することができる。導電体 205 となる導電膜のエッティングは、レジストマスクを除去してから行っても良いし、レジストマスクを残したまま行っても良い。後者の場合、エッティング中にレジストマスクが消失することがある。導電体 205 となる導電膜のエッティング後にハードマスクをエッティングにより除去しても良い。一方、ハードマスクの材料が後工程に影響が無い、あるいは後工程で利用できる場合、必ずしもハードマスクを除去する必要は無い。

40

#### 【0192】

ドライエッティング装置としては、平行平板型電極を有する容量結合型プラズマ (CCP : Capacitively Coupled Plasma) エッティング装置を用いるこ

50

とができる。平行平板型電極を有する容量結合型プラズマエッティング装置は、平行平板型電極の一方の電極に高周波電源を印加する構成でもよい。または平行平板型電極の一方の電極に複数の異なった高周波電源を印加する構成でもよい。または平行平板型電極それぞれに同じ周波数の高周波電源を印加する構成でもよい。または平行平板型電極それぞれに周波数の異なる高周波電源を印加する構成でもよい。または高密度プラズマ源を有するドライエッティング装置を用いることができる。高密度プラズマ源を有するドライエッティング装置は、例えば、誘導結合型プラズマ( I C P : Inductively Coupled Plasma )エッティング装置などを用いることができる。

#### 【 0 1 9 3 】

次に、絶縁体 214 上、導電体 205 上に絶縁体 216 となる絶縁膜を成膜する。絶縁体 216 となる絶縁体の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。本実施の形態では、絶縁体 216 となる絶縁膜として、CVD 法によって酸化シリコンを成膜する。

#### 【 0 1 9 4 】

ここで、絶縁体 216 となる絶縁膜の膜厚は、導電体 205 の膜厚以上とすることが好み。例えば、導電体 205 の膜厚を 1 とすると、絶縁体 216 となる絶縁膜の膜厚は、1 以上 3 以下とする。本実施の形態では、導電体 205 の膜厚の膜厚を 150 nm とし、絶縁体 216 となる絶縁膜の膜厚を 350 nm とする。

#### 【 0 1 9 5 】

次に、絶縁体 216 となる絶縁膜に CMP 处理を行うことで、絶縁体 216 となる絶縁膜の一部を除去し、導電体 205 の表面を露出させる。これにより、上面が平坦な、導電体 205 と、絶縁体 216 を形成することができる。以上が、導電体 205 の異なる形成方法である。

#### 【 0 1 9 6 】

次に、絶縁体 216 、および導電体 205 上に絶縁体 222 を成膜する。絶縁体 222 として、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を成膜するとよい。なお、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体として、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物(ハフニウムアルミネート)などを用いることが好み。アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体は、酸素、水素、および水に対するバリア性を有する。絶縁体 222 が、水素および水に対するバリア性を有することで、トランジスタ 200 の周辺に設けられた構造体に含まれる水素、および水が、絶縁体 222 を通じてトランジスタ 200 の内側へ拡散することが抑制され、酸化物 230 中の酸素欠損の生成を抑制することができる。

#### 【 0 1 9 7 】

絶縁体 222 の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。

#### 【 0 1 9 8 】

次に、絶縁体 222 上に絶縁膜 224A を成膜する。絶縁膜 224A の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。

#### 【 0 1 9 9 】

続いて、加熱処理を行うことが好み。加熱処理は、250 以上 650 以下、好みは 300 以上 500 以下、さらに好みは 320 以上 450 以下で行えばよい。なお、加熱処理は、窒素または不活性ガス雰囲気、または酸化性ガスを 10 ppm 以上、1 % 以上、もしくは 10 % 以上含む雰囲気で行う。また、加熱処理は減圧状態で行ってもよい。または、加熱処理は、窒素または不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上、1 % 以上、または 10 % 以上含む雰囲気で加熱処理を行ってもよい。

#### 【 0 2 0 0 】

10

20

30

40

50

本実施の形態では、窒素雰囲気にて 400 の温度で 1 時間の処理を行った後に、連続して酸素雰囲気にて 400 の温度で 1 時間の処理を行う。当該加熱処理によって、絶縁膜 224A に含まれる水、水素などの不純物を除去することができる。

#### 【0201】

また、加熱処理は、絶縁体 222 の成膜後に行ってよい。当該加熱処理は、上述した加熱処理条件を用いることができる。

#### 【0202】

ここで、絶縁膜 224A に過剰酸素領域を形成するために、減圧状態で酸素を含むプラズマ処理を行ってよい。酸素を含むプラズマ処理は、例えばマイクロ波を用いた高密度プラズマを発生させる電源を有する装置を用いることが好ましい。または、基板側に R F (Radio Frequency) を印加する電源を有してもよい。高密度プラズマを用いることより、高密度の酸素ラジカルを生成することができ、基板側に R F を印加することで、高密度プラズマによって生成された酸素ラジカルを効率よく絶縁膜 224A 内に導くことができる。または、この装置を用いて不活性ガスを含むプラズマ処理を行った後に、脱離した酸素を補うために酸素を含むプラズマ処理を行ってよい。なお、当該プラズマ処理の条件を適宜選択することにより、絶縁膜 224A に含まれる水、水素などの不純物を除去することができる。その場合、加熱処理は行わなくてもよい。

10

#### 【0203】

ここで、絶縁膜 224A 上に、例えば、スパッタリング法によって、酸化アルミニウムを成膜し、該酸化アルミニウムを絶縁膜 224A に達するまで、C M P を行ってよい。当該 C M P を行うことで絶縁膜 224A 表面の平坦化および絶縁膜 224A 表面の平滑化を行うことができる。当該酸化アルミニウムを絶縁膜 224A 上に配置して C M P を行うことで、C M P の終点検出が容易となる。また、C M P によって、絶縁膜 224A の一部が研磨されて、絶縁膜 224A の膜厚が薄くなることがあるが、絶縁膜 224A の成膜時に膜厚を調整すればよい。絶縁膜 224A 表面の平坦化および平滑化を行うことで、後に成膜する酸化物の被覆率の悪化を防止し、半導体装置の歩留りの低下を防ぐことができる場合がある。また、絶縁膜 224A 上に、スパッタリング法によって、酸化アルミニウムを成膜することにより、絶縁膜 224A に酸素を添加することができるので好ましい。

20

#### 【0204】

次に、絶縁膜 224A 上に、酸化膜 230A、酸化膜 230B を順に成膜する（図 4 参照）。なお、上記酸化膜は、大気環境にさらさずに連続して成膜することが好ましい。大気開放せずに成膜することで、酸化膜 230A、および酸化膜 230B 上に大気環境からの不純物または水分が付着することを防ぐことができ、酸化膜 230A と酸化膜 230B との界面近傍を清浄に保つことができる。

30

#### 【0205】

酸化膜 230A および、酸化膜 230B の成膜はスパッタリング法、C V D 法、M B E 法、P L D 法、または A L D 法などを用いて行うことができる。

#### 【0206】

例えば、酸化膜 230A、および酸化膜 230B をスパッタリング法によって成膜する場合は、スパッタリングガスとして酸素、または、酸素と希ガスの混合ガスを用いる。スパッタリングガスに含まれる酸素の割合を高めることで、成膜される酸化膜中の過剰酸素を増やすことができる。また、上記の酸化膜をスパッタリング法によって成膜する場合は、上記の I n - M - Z n 酸化物ターゲットを用いることができる。

40

#### 【0207】

特に、酸化膜 230A の成膜時に、スパッタリングガスに含まれる酸素の一部が絶縁膜 224A に供給される場合がある。したがって、酸化膜 230A のスパッタリングガスに含まれる酸素の割合は 70% 以上、好ましくは 80% 以上、より好ましくは 100% とすればよい。

#### 【0208】

また、酸化膜 230B をスパッタリング法で形成する場合、スパッタリングガスに含ま

50

れる酸素の割合を 1 % 以上 30 % 以下、好ましくは 5 % 以上 20 % 以下として成膜すると、酸素欠乏型の酸化物半導体が形成される。酸素欠乏型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い電界効果移動度が得られる。

#### 【 0 2 0 9 】

本実施の形態では、酸化膜 230A として、スパッタリング法によって、In : Ga : Zn = 1 : 1 : 0.5 [ 原子数比 ] ( 2 : 2 : 1 [ 原子数比 ] )、あるいは 1 : 3 : 4 [ 原子数比 ] のターゲットを用いて成膜する。また、酸化膜 230B として、スパッタリング法によって、In : Ga : Zn = 4 : 2 : 4.1 [ 原子数比 ]、あるいは 1 : 1 : 1 [ 原子数比 ] のターゲットを用いて成膜する。なお、各酸化膜は、成膜条件、および原子数比を適宜選択することで、酸化物 230 に求める特性に合わせて形成するとよい。

10

#### 【 0 2 1 0 】

次に、加熱処理を行ってもよい。加熱処理は、上述した加熱処理条件を用いることができる。加熱処理によって、酸化膜 230A、および酸化膜 230B 中の水、水素などの不純物を除去することなどができる。本実施の形態では、窒素雰囲気にて 400 の温度で 1 時間の処理を行った後に、連続して酸素雰囲気にて 400 の温度で 1 時間の処理を行う。

#### 【 0 2 1 1 】

次に、酸化膜 230B 上に酸化膜 243A を成膜する。酸化膜 243A の成膜はスパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。酸化膜 243A は、In に対する Ga の原子数比が、酸化膜 230B の In に対する Ga の原子数比より大きいことが好ましい。本実施の形態では、酸化膜 243A として、スパッタリング法によって、In : Ga : Zn = 1 : 3 : 4 [ 原子数比 ] のターゲットを用いて成膜する。次に、酸化膜 243A 上に導電膜 242A を成膜する。導電膜 242A の成膜はスパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる（図 4 参照）。

20

#### 【 0 2 1 2 】

次に、酸化膜 230A、酸化膜 230B、酸化膜 243A、および導電膜 242A を島状に加工して、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B を形成する（図 5 参照）。なお、図示しないが、当該工程において、絶縁膜 224A の酸化物 230a と重ならない領域の膜厚が薄くなることがある。

30

#### 【 0 2 1 3 】

ここで、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B は、少なくとも一部が導電体 205 と重なるように形成する。また、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B の側面は、絶縁体 222 の上面に対し、概略垂直であることが好ましい。酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B の側面が、絶縁体 222 の上面に対し、概略垂直であることで、複数のトランジスタ 200 を設ける際に、小面積化、高密度化が可能となる。または、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B と絶縁体 222 の上面のなす角が低い角度になる構成にしてもよい。その場合、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B の側面と絶縁体 222 の上面のなす角は 60 ° 以上 70 ° 未満が好ましい。この様な形状とすることで、これより後の工程において、絶縁体 272 などの被覆性が向上し、鬆などの欠陥を低減することができる。

40

#### 【 0 2 1 4 】

また、導電体層 242B の側面と導電体層 242B の上面との間に、湾曲面を有する。つまり、側面の端部と上面の端部は、湾曲していることが好ましい（以下、ラウンド状ともいう）。湾曲面は、例えば、導電体層 242B 層の端部において、曲率半径が、3 nm 以上 10 nm 以下、好ましくは、5 nm 以上 6 nm 以下とする。端部に角を有さないことで、以降の成膜工程における膜の被覆性が向上する。

#### 【 0 2 1 5 】

50

なお、当該酸化膜および導電膜の加工はリソグラフィー法を用いて行えばよい。また、当該加工はドライエッティング法やウェットエッティング法を用いることができる。ドライエッティング法による加工は微細加工に適している。

#### 【0216】

次に絶縁膜224A、酸化物230a、酸化物230b、酸化物層243B、および導電体層242Bの上に、絶縁膜272Aを成膜する(図6参照)。

#### 【0217】

絶縁膜272Aの成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。絶縁膜272Aは、酸素の透過を抑制する機能を有する絶縁膜を用いることが好ましい。例えば、スパッタリング法またはALD法によって、酸化アルミニウム、窒化シリコン、酸化シリコン、または、酸化ガリウムを成膜してもよい。

10

#### 【0218】

次に、絶縁膜272A上に、絶縁膜273Aを成膜する。絶縁膜273Aの成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。例えば、ALD法によって、酸化アルミニウムを成膜することが好ましい。本実施の形態では、ALD法によって、酸化アルミニウムを成膜する(図6参照)。なお、絶縁膜273Aを成膜しない構成とすることもできる。

#### 【0219】

次に、絶縁膜273A上に、絶縁体280となる絶縁膜を成膜する。絶縁体280となる絶縁膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。次に、絶縁体280となる絶縁膜にCMP処理を行い、上面が平坦な絶縁体280を形成する(図7参照)。

20

#### 【0220】

次に、絶縁体280の一部、絶縁膜273Aの一部、絶縁膜272Aの一部、酸化物層243B、および導電体層242Bの一部を加工して、酸化物230bに達する開口を形成する。該開口は、導電体205と重なるように形成することが好ましい。該開口の形成によって、酸化物243a、酸化物243b、導電体242a、導電体242b、絶縁体272、絶縁体273、および絶縁体224を形成する(図7参照)。

#### 【0221】

また、絶縁体280の一部、絶縁膜273Aの一部、絶縁膜272Aの一部、酸化物層243B、および導電体層242Bの一部の加工は、それぞれ異なる条件で加工してもよい。例えば、絶縁体280の一部をドライエッティング法で加工し、絶縁膜273Aの一部をウェットエッティング法で加工し、絶縁膜272Aの一部、酸化物層243B、および導電体層242Bの一部をドライエッティング法で加工してもよい。

30

#### 【0222】

これまでのドライエッティングなどの処理を行うことによって、エッティングガスなどに起因した不純物が酸化物230a、および酸化物230bなどの表面または内部に付着または拡散することがある。不純物としては、例えば、フッ素または塩素などがある。

#### 【0223】

上記の不純物などを除去するために、洗浄を行う。洗浄方法としては、洗浄液など用いたウェット洗浄、プラズマを用いたプラズマ処理、または熱処理による洗浄などがあり、上記洗浄を適宜組み合わせて行ってもよい。

40

#### 【0224】

ウェット洗浄としては、シウ酸、リン酸、アンモニア水、またはフッ化水素酸などを炭酸水または純水で希釈した水溶液を用いて洗浄処理を行ってもよい。または、純水または炭酸水を用いた超音波洗浄を行ってもよい。

#### 【0225】

次に、第1の加熱処理を行っても良い。第1の加熱処理は、酸素を含む雰囲気下で行うと好適である。または、第1の加熱処理は、減圧下で行い、大気に暴露することなく、連

50

続して酸化膜 230C を成膜してもよい。このような処理を行うことによって、酸化物 230b の表面などに表面に吸着している水分および水素を除去し、さらに酸化物 230a および酸化物 230b 中の水分濃度および水素濃度を低減させることができる。第 1 の加熱処理の温度は、100 以上 400 以下が好ましく、さらに好ましくは 150 以上 350 以下である。本実施の形態では、第 1 の加熱処理の温度を 200 とし、減圧下で行う(図 8 参照)。

#### 【0226】

ここで、酸化膜 230C は、少なくとも酸化物 230a の側面の一部、酸化物 230b の側面の一部および上面の一部、酸化物 243 の側面の一部、導電体 242 の側面の一部、絶縁体 272 の側面、絶縁体 273 の側面、および絶縁体 280 の側面と接するように設けられることが好ましい。導電体 242 は、酸化物 243、絶縁体 272、酸化膜 230C に囲まれることで、以降の工程において導電体 242 の酸化による導電率の低下を抑制することができる。

#### 【0227】

酸化膜 230C の成膜はスパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。酸化膜 230C として、In に対する Ga の原子数比が、酸化膜 230B の In に対する Ga の原子数比より大きいことが好ましい。本実施の形態では、酸化膜 230C として、スパッタリング法によって、In : Ga : Zn = 1 : 3 : 4 [原子数比] のターゲットを用いて成膜する。

#### 【0228】

尚、酸化膜 230C は、積層としてもよい。例えば、スパッタリング法によって、In : Ga : Zn = 4 : 2 : 4 . 1 [原子数比] のターゲットを用いて成膜して、連続して In : Ga : Zn = 1 : 3 : 4 [原子数比] のターゲットを用いて成膜してもよい。

#### 【0229】

特に、酸化膜 230C の成膜時に、スパッタリングガスに含まれる酸素の一部が酸化物 230a および酸化物 230b に供給される場合がある。または、酸化膜 230C の成膜時に、スパッタリングガスに含まれる酸素の一部が絶縁体 280 に供給される場合がある。したがって、酸化膜 230C のスパッタリングガスに含まれる酸素の割合は 70% 以上、好ましくは 80% 以上、より好ましくは 100% とすればよい。

#### 【0230】

次に、第 2 の加熱処理を行っても良い。第 2 の加熱処理は、減圧下で行い、大気に暴露することなく、連続して絶縁膜 250A を成膜してもよい。このような処理を行うことによって、酸化膜 230C の表面などに表面に吸着している水分および水素を除去し、さらに酸化物 230a、酸化物 230b および酸化膜 230C 中の水分濃度および水素濃度を低減させることができる。第 2 の加熱処理の温度は、100 以上 400 以下が好ましい。本実施の形態では、第 2 の加熱処理の温度を 200 とする(図 9 参照)。

#### 【0231】

絶縁膜 250A は、スパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて成膜することができる。絶縁膜 250A として、CVD 法により、酸化窒化シリコンを成膜することが好ましい。なお、絶縁膜 250A を成膜する際の成膜温度は、250 以上 450 未満、特に 350 前後とすることが好ましい。絶縁膜 250A を、350 で成膜することで、不純物が少ない絶縁体を成膜することができる。

#### 【0232】

次に、導電膜 260Aa および導電膜 260Ab を成膜する。導電膜 260Aa および導電膜 260Ab の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。例えば、CVD 法を用いることが好ましい。本実施の形態では、ALD 法を用いて、導電膜 260Aa を成膜し、CVD 法を用いて導電膜 260Ab を成膜する(図 10 参照)。

#### 【0233】

次に、CMP 处理によって、酸化膜 230C、絶縁膜 250A、導電膜 260Aa およ

10

20

30

40

50

び導電膜 260Ab を絶縁体 280 が露出するまで研磨することによって、酸化物 230c、絶縁体 250 および導電体 260（導電体 260a および導電体 260b）を形成する（図 11 参照）。

#### 【0234】

ここで、導電体 242 は、酸化物 243、絶縁体 272、酸化物 230c に囲まれるように設けられているため、導電体 242 の酸化による導電率の低下を抑制することができる。

#### 【0235】

次に、第 3 の加熱処理を行う。本発明の一態様では、第 3 の加熱処理を行うことによって、酸化膜 230C、絶縁体 280 中に含まれる不純物（代表的には、水、水素など）を好適に除去することが可能である。例えば、第 3 の加熱処理を行うことによって、酸化膜 230C 中に含まれる水、水素などを除去（脱水・脱水素化）することによって、酸化膜 230C を高純度真性に近づけることができる。また、第 3 の加熱処理を行うことによって、絶縁体 280 中に含まれる水、水素などを除去（脱水・脱水素化）することによって、酸化膜 230C に拡散しうる水、水素などをトランジスタの作製工程中で除去することができる（図 11 参照）。

10

#### 【0236】

なお、第 3 の加熱処理は、窒素雰囲気または、酸素が含まれる雰囲気で行うことができる。好ましくは、第 3 の加熱処理として、窒素と酸素とが含まれる雰囲気下で行うと好適である。窒素と酸素とが含まれる雰囲気下で行う場合、酸素の割合は、窒素と酸素の合計の 5% 以上 20% 以下とすることが好ましい。また、第 3 の加熱処理の温度は、好ましくは、300 以上 450 以下、より好ましくは、300 以上 400 以下である。代表的には、350、またはその近傍の温度が好適である。また、加熱処理時間は、100 時間以下、好ましくは、1 時間以上 48 時間以下である。代表的には、24 時間、またはその近傍の処理時間が好適である。該加熱処理を行うことで、酸化物 230、絶縁体 250 および絶縁体 280 中の水分濃度および水素濃度を低減させ、酸化物 230 のチャネル形成領域のキャリア密度を低減することができる。本実施の形態では、窒素雰囲気にて、350 の温度で、24 時間の加熱処理を行う。なお、第 3 の加熱処理によって、導電体 260 が酸化されない条件で実施するのが好ましい。

20

#### 【0237】

または、RTA 装置を用いて、RTA (Rapid thermal anneal) 処理を行ってもよい。RTA 処理とは、短時間にて高温の加熱処理を行うことである。例えば、窒素雰囲気にて、400 以上 700 以下の温度にて 60 秒以上、120 秒以下の加熱処理を行うことができる。なお、RTA 装置に用いる光源としては、ランプ方式を用いることができる。ランプ方式の RTA 装置を用いることで、処理タクトを高め、生産性を向上させることができる。

30

#### 【0238】

次に、第 4 の加熱処理を行っても良い。第 4 の加熱処理は、減圧下で行い、大気に暴露することなく、連続して、導電体 260 上、酸化物 230c 上、絶縁体 250 上、および絶縁体 280 上に、絶縁体 282 となる絶縁膜および絶縁体 283 となる絶縁膜を順に形成すると好ましい。このような処理を行うことによって、導電体 260 表面、酸化物 230c 表面、絶縁体 250 表面、および絶縁体 280 表面などに吸着している水分および水素を除去することができるので好ましい。絶縁体 282 となる絶縁膜および絶縁体 283 となる絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。絶縁体 282 となる絶縁膜としては、例えば、スパッタリング法によって、酸化アルミニウムを成膜することが好ましい。また、絶縁体 283 となる絶縁膜としては、例えば、スパッタリング法によって、窒化シリコンを成膜することが好ましい。このように絶縁体 282 および絶縁体 283 を配置することによって、外方から水または水素などの不純物が絶縁体 282 および絶縁体 283 を介してトランジスタ 200 へ拡散することを抑制できる。また、導電体 260 の上面に接して、絶縁体 2

40

50

82を形成することで、この後の加熱処理において、絶縁体280が有する酸素が導電体260へ吸収されることを抑制することができる（図12参照）。

#### 【0239】

上述のように本発明の一態様においては、第3の加熱処理を行うことによって、信頼性が良好な半導体装置を提供することができる。

#### 【0240】

次に、第5の加熱処理を行ってもよい。本実施の形態では、窒素雰囲気にて400の温度で1時間の処理を行う。該加熱処理によって、絶縁体282の成膜によって添加された酸素を絶縁体280へ注入することができる。また、該酸素は、酸化物230cを介して、酸化物230a、および酸化物230bへ注入することができる。

10

#### 【0241】

次に絶縁体283上に、絶縁体274となる絶縁体を成膜してもよい。絶縁体274となる絶縁膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる（図12参照）。

#### 【0242】

次に絶縁体274上に、絶縁体281となる絶縁体を成膜してもよい。絶縁体281となる絶縁膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。絶縁体281となる絶縁膜としては、例えば、スパッタリング法によって、窒化シリコンを成膜することが好ましい。（図12参照）。

20

#### 【0243】

次に、絶縁体272、絶縁体273、絶縁体280、絶縁体282、絶縁体283、絶縁体274および絶縁体281に、導電体242aおよび導電体242bに達する開口を形成する。当該開口の形成は、リソグラフィー法を用いて行えばよい。

#### 【0244】

次に、絶縁体241となる絶縁膜を成膜し、当該絶縁膜を異方性エッチングして絶縁体241を形成する。当該導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。絶縁体241となる絶縁膜としては、酸素の透過を抑制する機能を有する絶縁膜を用いることが好ましい。例えば、ALD法によって、酸化アルミニウムまたは窒化シリコンを成膜することが好ましい。また、異方性エッチングは、例えばドライエッティング法などを行えばよい。開口の側壁部をこのような構成とすることで、外方からの酸素の透過を抑制し、次に形成する導電体240aおよび導電体240bの酸化を防止することができる。また、導電体240aおよび導電体240bから、水、水素などの不純物が外部に拡散することを防ぐことができる。

30

#### 【0245】

次に、導電体240aおよび導電体240bとなる導電膜を成膜する。導電体240aおよび導電体240bとなる導電膜は、水、水素など不純物の透過を抑制する機能を有する導電体を含む積層構造とすることが望ましい。たとえば、窒化タンタル、窒化チタンなどと、タンゲステン、モリブデン、銅など、と、の積層とすることができる。導電体240となる導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

40

#### 【0246】

次に、CMP処理を行うことで、導電体240aおよび導電体240bとなる導電膜の一部を除去し、絶縁体281を露出する。その結果、上記開口のみに、当該導電膜が残存することで上面が平坦な導電体240aおよび導電体240bを形成することができる（図1参照）。なお、当該CMP処理により、絶縁体281の一部が除去される場合がある。

#### 【0247】

次に、導電体246となる導電膜を成膜する。導電体246となる導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

#### 【0248】

50

次に、導電体 246 となる導電膜をリソグラフィー法によって加工し、導電体 240a の上面と接する導電体 246a および導電体 240b の上面と接する導電体 246b を形成する(図1参照)。

#### 【0249】

以上により、図1に示すトランジスタ200を有する半導体装置を作製することができる。図4乃至図12に示すように、本実施の形態に示す半導体装置の作製方法を用いることで、トランジスタ200を作製することができる。

#### 【0250】

本発明の一態様により、オン電流の大きい半導体装置を提供することができる。または、本発明の一態様により、高い周波数特性を有する半導体装置を提供することができる。または、本発明の一態様により、信頼性が良好な半導体装置を提供することができる。または、本発明の一態様により、微細化または高集積化が可能な半導体装置を提供することができる。または、本発明の一態様により、良好な電気特性を有する半導体装置を提供することができる。または、本発明の一態様により、オフ電流の小さい半導体装置を提供することができる。または、本発明の一態様により、消費電力が低減された半導体装置を提供することができる。または、本発明の一態様により、生産性の高い半導体装置を提供することができる。

10

#### 【0251】

以上、本実施の形態に示す構成、方法などは、他の実施の形態および他の実施例に示す構成、構造、方法などと適宜組み合わせて用いることができる。

20

#### 【0252】

##### (実施の形態2)

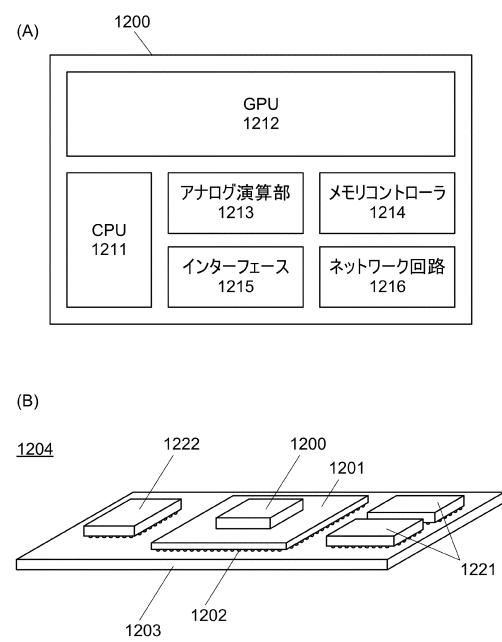

本実施の形態では、半導体装置の一形態を、図17および図18を用いて説明する。

#### 【0253】

##### [記憶装置1]

本発明の一態様である容量素子を使用した、半導体装置(記憶装置)の一例を図17に示す。本発明の一態様の半導体装置は、トランジスタ200はトランジスタ300の上方に設けられ、容量素子100はトランジスタ300、およびトランジスタ200の上方に設けられている。なお、トランジスタ200として、先の実施の形態で説明したトランジスタ200を用いることができる。

30

#### 【0254】

トランジスタ200は、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタである。トランジスタ200は、オフ電流が小さいため、これを記憶装置に用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、あるいは、リフレッシュ動作の頻度が極めて少ないため、記憶装置の消費電力を十分に低減することができる。

#### 【0255】

図17に示す半導体装置において、配線1001はトランジスタ300のソースと電気的に接続され、配線1002はトランジスタ300のドレインと電気的に接続されている。また、配線1003はトランジスタ200のソースおよびドレインの一方と電気的に接続され、配線1004はトランジスタ200の第1のゲートと電気的に接続され、配線1006はトランジスタ200の第2のゲートと電気的に接続されている。そして、トランジスタ300のゲート、およびトランジスタ200のソースおよびドレインの他方は、容量素子100の電極の一方と電気的に接続され、配線1005は容量素子100の電極の他方と電気的に接続されている。

40

#### 【0256】

また、図17に示す記憶装置は、マトリクス状に配置することで、メモリセルアレイを構成することができる。

#### 【0257】

<トランジスタ300>

50

トランジスタ 300 は、基板 311 上に設けられ、ゲートとして機能する導電体 316、ゲート絶縁体として機能する絶縁体 315、基板 311 の一部からなる半導体領域 313、およびソース領域またはドレイン領域として機能する低抵抗領域 314a、および低抵抗領域 314b を有する。トランジスタ 300 は、p チャネル型、あるいはn チャネル型のいずれでもよい。

#### 【0258】

ここで、図 17 に示すトランジスタ 300 はチャネルが形成される半導体領域 313（基板 311 の一部）が凸形状を有する。また、半導体領域 313 の側面および上面を、絶縁体 315 を介して、導電体 316 が覆うように設けられている。なお、導電体 316 は仕事関数を調整する材料を用いてもよい。このようなトランジスタ 300 は半導体基板の凸部を利用していることから F I N 型トランジスタとも呼ばれる。なお、凸部の上部に接して、凸部を形成するためのマスクとして機能する絶縁体を有していてもよい。また、ここでは半導体基板の一部を加工して凸部を形成する場合を示したが、S O I 基板を加工して凸形状を有する半導体膜を形成してもよい。

10

#### 【0259】

なお、図 17 に示すトランジスタ 300 は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

#### 【0260】

##### <容量素子 100 >

容量素子 100 は、トランジスタ 200 の上方に設けられる。容量素子 100 は、第 1 の電極として機能する導電体 110 と、第 2 の電極として機能する導電体 120、および誘電体として機能する絶縁体 130 を有する。

20

#### 【0261】

また、例えば、導電体 246 上に設けた導電体 112 と、導電体 110 は、同時に形成することができる。なお、導電体 112 は、容量素子 100、トランジスタ 200、またはトランジスタ 300 と電気的に接続するプラグ、または配線としての機能を有する。

#### 【0262】

図 17 では、導電体 112、および導電体 110 は単層構造を示したが、当該構成に限定されず、2 層以上の積層構造でもよい。例えば、バリア性を有する導電体と導電性が高い導電体との間に、バリア性を有する導電体、および導電性が高い導電体に対して密着性が高い導電体を形成してもよい。

30

#### 【0263】

また、絶縁体 130 は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化窒化ハフニウム、窒化酸化ハフニウム、窒化ハフニウムなどを用いればよく、積層または単層で設けることができる。

#### 【0264】

例えば、絶縁体 130 には、酸化窒化シリコンなどの絶縁耐力が大きい材料と、高誘電率 ( h i g h - k ) 材料との積層構造を用いることが好ましい。当該構成により、容量素子 100 は、高誘電率 ( h i g h - k ) の絶縁体を有することで、十分な容量を確保でき、絶縁耐力が大きい絶縁体を有することで、絶縁耐力が向上し、容量素子 100 の静電破壊を抑制することができる。

40

#### 【0265】

なお、高誘電率 ( h i g h - k ) 材料（高い比誘電率の材料）の絶縁体としては、酸化ガリウム、酸化ハフニウム、酸化ジルコニア、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物またはシリコンおよびハフニウムを有する窒化物などがある。

#### 【0266】

一方、絶縁耐力が大きい材料（低い比誘電率の材料）としては、酸化シリコン、酸化窒

50

化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンまたは樹脂などがある。

#### 【0267】

##### <配線層>

各構造体の間には、層間膜、配線、およびプラグ等が設けられた配線層が設けられてもよい。また、配線層は、設計に応じて複数層設けることができる。ここで、プラグまたは配線としての機能を有する導電体は、複数の構造をまとめて同一の符号を付与する場合がある。また、本明細書等において、配線と、配線と電気的に接続するプラグとが一体物であってもよい。すなわち、導電体の一部が配線として機能する場合、および導電体の一部がプラグとして機能する場合もある。

#### 【0268】

例えば、トランジスタ300上には、層間膜として、絶縁体320、絶縁体322、絶縁体324、および絶縁体326が順に積層して設けられている。また、絶縁体320、絶縁体322、絶縁体324、および絶縁体326には容量素子100、またはトランジスタ200と電気的に接続する導電体328、および導電体330等が埋め込まれている。なお、導電体328、および導電体330はプラグ、または配線として機能する。

#### 【0269】

また、層間膜として機能する絶縁体は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。例えば、絶縁体322の上面は、平坦性を高めるために化学機械研磨(CMP)法等を用いた平坦化処理により平坦化されている。

#### 【0270】

絶縁体326、および導電体330上に、配線層を設けてもよい。例えば、図17において、絶縁体350、絶縁体352、及び絶縁体354が順に積層して設けられている。また、絶縁体350、絶縁体352、及び絶縁体354には、導電体356が形成されている。導電体356は、プラグ、または配線として機能する。

#### 【0271】

同様に、絶縁体210、絶縁体212、絶縁体214、および絶縁体216には、導電体218、及びトランジスタ200を構成する導電体(導電体205)等が埋め込まれている。なお、導電体218は、容量素子100、またはトランジスタ300と電気的に接続するプラグ、または配線としての機能を有する。さらに、導電体120、および絶縁体130上には、絶縁体150が設けられている。

#### 【0272】

層間膜として用いることができる絶縁体としては、絶縁性を有する酸化物、窒化物、酸化窒化物、窒化酸化物、金属酸化物、金属酸化窒化物、金属窒化酸化物などがある。

#### 【0273】

例えば、層間膜として機能する絶縁体には、比誘電率が低い材料を用いることで、配線間に生じる寄生容量を低減することができる。したがって、絶縁体の機能に応じて、材料を選択するとよい。

#### 【0274】

例えば、絶縁体150、絶縁体210、絶縁体352、および絶縁体354等には、比誘電率の低い絶縁体を有することが好ましい。例えば、当該絶縁体は、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンまたは樹脂などを有することが好ましい。または、当該絶縁体は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコンまたは空孔を有する酸化シリコンと、樹脂との積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、樹脂と組み合わせることで、熱的に安定かつ比誘電率の低い積層構造とすることができます。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド(ナイロ

ン、アラミドなど)、ポリイミド、ポリカーボネートまたはアクリルなどがある。

【0275】

また、酸化物半導体を用いたトランジスタは、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体で囲うことによって、トランジスタの電気特性を安定にすることができる。従って、絶縁体214、絶縁体212および絶縁体350等には、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体を用いればよい。

【0276】

水素などの不純物および酸素の透過を抑制する機能を有する絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。具体的には、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体として、酸化アルミニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いることができる。

10

【0277】

配線、プラグに用いることができる導電体としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウムなどから選ばれた金属元素を1種以上含む材料を用いることができる。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

20

【0278】

例えば、導電体328、導電体330、導電体356、導電体218、および導電体112等としては、上記の材料で形成される金属材料、合金材料、金属窒化物材料、または金属酸化物材料などの導電性材料を、単層または積層して用いることができる。耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましく、タングステンを用いることが好ましい。または、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。低抵抗導電性材料を用いることで配線抵抗を低くすることができます。

30

【0279】

<酸化物半導体が設けられた層の配線、またはプラグ>

なお、トランジスタ200に、酸化物半導体を用いる場合、酸化物半導体の近傍に過剰酸素領域を有する絶縁体が設けることがある。その場合、該過剰酸素領域を有する絶縁体と、該過剰酸素領域を有する絶縁体に設ける導電体との間に、バリア性を有する絶縁体を設けることが好ましい。

【0280】

例えば、図17では、過剰酸素を有する絶縁体224と、導電体245との間に、絶縁体276を設けるとよい。絶縁体276と、絶縁体222、および絶縁体272とが接して設けられることで、絶縁体224、およびトランジスタ200は、バリア性を有する絶縁体により、封止する構造とすることができる。さらに、絶縁体276は、絶縁体280の一部とも接することが好ましい。絶縁体276が、絶縁体280まで延在していることで、酸素や不純物の拡散を、より抑制することができる。

40

【0281】

つまり、絶縁体276を設けることで、絶縁体224が有する過剰酸素が、導電体245に吸収されることを抑制することができる。また、絶縁体276を有することで、不純物である水素が、導電体245を介して、トランジスタ200へ拡散することを抑制することができる。

【0282】

なお、絶縁体276としては、水または水素などの不純物、および酸素の拡散を抑制す

50

る機能を有する絶縁性材料を用いるとよい。例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。また、他にも、例えば、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いることができる。

#### 【0283】

以上が構成例についての説明である。本構成を用いることで、酸化物半導体を有するトランジスタを用いた半導体装置において、電気特性の変動を抑制すると共に、信頼性を向上させることができる。または、オン電流が大きい酸化物半導体を有するトランジスタを提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを提供することができる。または、消費電力が低減された半導体装置を提供することができる。

10

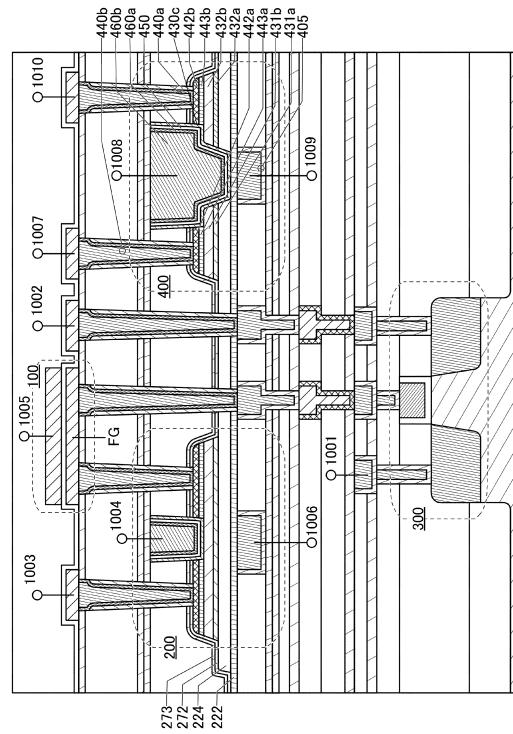

#### 【0284】

##### [記憶装置2]

本発明の一態様である半導体装置を使用した、記憶装置の一例を図18に示す。図18に示す記憶装置は、図17で示したトランジスタ200、トランジスタ300、および容量素子100を有する半導体装置に加え、トランジスタ400を有している。

#### 【0285】

トランジスタ400は、トランジスタ200の第2のゲート電圧を制御することができる。例えば、トランジスタ400の第1のゲート及び第2のゲートをソースとダイオード接続し、トランジスタ400のソースと、トランジスタ200の第2のゲートを接続する構成とする。当該構成でトランジスタ200の第2のゲートの負電位を保持するとき、トランジスタ400の第1のゲート-ソース間の電圧および、第2のゲート-ソース間の電圧は、0Vになる。トランジスタ400において、第2のゲート電圧及び第1のゲート電圧が0Vのときのドレイン電流が非常に小さいため、トランジスタ200およびトランジスタ400に電源供給をしなくとも、トランジスタ200の第2のゲートの負電位を長時間維持することができる。これにより、トランジスタ200、およびトランジスタ400を有する記憶装置は、長期にわたり記憶内容を保持することが可能である。

20

#### 【0286】

従って、図18において、配線1001はトランジスタ300のソースと電気的に接続され、配線1002はトランジスタ300のドレインと電気的に接続されている。また、配線1003はトランジスタ200のソースおよびドレインの一方と電気的に接続され、配線1004はトランジスタ200のゲートと電気的に接続され、配線1006はトランジスタ200のバックゲートと電気的に接続されている。そして、トランジスタ300のゲート、およびトランジスタ200のソースおよびドレインの他方は、容量素子100の電極の一方と電気的に接続され、配線1005は容量素子100の電極の他方と電気的に接続されている。配線1007はトランジスタ400のソースと電気的に接続され、配線1008はトランジスタ400のゲートと電気的に接続され、配線1009はトランジスタ400のバックゲートと電気的に接続され、配線1010はトランジスタ400のドレインと電気的に接続されている。ここで、配線1006、配線1007、配線1008、及び配線1009が電気的に接続されている。

30

#### 【0287】

また、図18に示す記憶装置は、図17に示す記憶装置と同様に、マトリクス状に配置することで、メモリセルアレイを構成することができる。なお、1個のトランジスタ400は、複数のトランジスタ200の第2のゲート電圧を制御することができる。そのため、トランジスタ400は、トランジスタ200よりも、少ない個数を設けるとよい。

40

#### 【0288】

##### <トランジスタ400>

トランジスタ400は、トランジスタ200と、同じ層に形成されており、並行して作製することができるトランジスタである。トランジスタ400は、第1のゲートとして機

50

能する導電体 460（導電体 460a、および導電体 460b）と、第 2 のゲートとして機能する導電体 405（導電体 405a、および導電体 405b）と、ゲート絶縁層として機能する絶縁体 222、および絶縁体 450 と、チャネル形成領域を有する酸化物 430c と、ソースとして機能する導電体 442a、酸化物 443a、酸化物 431a、および酸化物 431b と、ドレインとして機能する導電体 442b、酸化物 443b、酸化物 432a、および酸化物 432b と、プラグとして機能する導電体 440（導電体 440a、および導電体 440b）と、を有する。

#### 【0289】

トランジスタ 400において、導電体 405 は、導電体 205 と、同じ層である。酸化物 431a、および酸化物 432a は、酸化物 230a と、同じ層であり、酸化物 431b、および酸化物 432b は、酸化物 230b と、同じ層である。導電体 442 は、導電体 242 と、同じ層である。酸化物 443 は、酸化物 243 と、同じ層である。酸化物 430c は、酸化物 230c と、同じ層である。絶縁体 450 は、絶縁体 250 と、同じ層である。導電体 460 は、導電体 260 と、同じ層である。

10

#### 【0290】

なお、同じ層に形成された構造体は、同時に形成することができる。例えば、酸化物 430c は、酸化物 230c となる酸化膜を加工することで、形成することができる。

#### 【0291】

トランジスタ 400 の活性層として機能する酸化物 430c は、酸化物 230 などと同様に、酸素欠損が低減され、水素または水などの不純物が低減されている。これにより、トランジスタ 400 のしきい値電圧を 0V より大きくし、オフ電流を低減し、第 2 のゲート電圧及び第 1 のゲート電圧が 0V のときのドレイン電流を非常に小さくすることができる。

20

#### 【0292】

##### <ダイシングライン>

以下では、大面積基板を半導体素子ごとに分断することによって、複数の半導体装置をチップ状で取り出す場合に設けられるダイシングライン（スクライブライン、分断ライン、又は切断ラインと呼ぶ場合がある）について説明する。分断方法としては、例えば、まず、基板に半導体素子を分断するための溝（ダイシングライン）を形成した後、ダイシングラインにおいて切断し、複数の半導体装置に分断（分割）する場合がある。

30

#### 【0293】

ここで、例えば、図 18 に示すように、絶縁体 272 と、絶縁体 222 とが接する領域をダイシングラインとなるように設計することが好ましい。つまり、複数のトランジスタ 200 を有するメモリセル、およびトランジスタ 400 の外縁に設けられるダイシングラインとなる領域近傍において、絶縁体 224 に開口を設ける。また、絶縁体 224 の側面を覆うように、絶縁体 272 を設ける。

#### 【0294】

つまり、上記絶縁体 224 に設けた開口において、絶縁体 222 と、絶縁体 272 とが接する。例えば、このとき、絶縁体 222 と、絶縁体 272 を同材料及び同方法を用いて形成してもよい。絶縁体 222、および絶縁体 272 を、同材料、および同方法で設けることで、密着性を高めることができる。例えば、酸化アルミニウムを用いることが好ましい。

40

#### 【0295】

当該構造により、絶縁体 222、および絶縁体 272 で、絶縁体 224、トランジスタ 200、およびトランジスタ 400 を包み込むことができる。絶縁体 222、および絶縁体 272 は、酸素、水素、及び水の拡散を抑制する機能を有しているため、本実施の形態に示す半導体素子が形成された回路領域ごとに、基板を分断することにより、複数のチップに加工しても、分断した基板の側面方向から、水素又は水などの不純物が混入し、トランジスタ 200、およびトランジスタ 400 に拡散することを防ぐことができる。

#### 【0296】

50

また、当該構造により、絶縁体 224 の過剰酸素が絶縁体 272、および絶縁体 222 を介して外部に拡散することを防ぐことができる。従って、絶縁体 224 の過剰酸素は、効率的にトランジスタ 200、またはトランジスタ 400 におけるチャネルが形成される酸化物に供給される。当該酸素により、トランジスタ 200、またはトランジスタ 400 におけるチャネルが形成される酸化物の酸素欠損を低減することができる。これにより、トランジスタ 200、またはトランジスタ 400 におけるチャネルが形成される酸化物を欠陥準位密度が低い、安定な特性を有する酸化物半導体とすることができる。つまり、トランジスタ 200、またはトランジスタ 400 の電気特性の変動を抑制すると共に、信頼性を向上させることができる。

#### 【0297】

10

本実施の形態に示す構成、方法などは、他の実施の形態および他の実施例に示す構成、構造、方法などと適宜組み合わせて用いることができる。

#### 【0298】

##### (実施の形態 3)

本実施の形態では、図 19 および図 20 を用いて、本発明の一態様に係る、酸化物を半導体に用いたトランジスタ（以下、OSトランジスタと呼ぶ場合がある）、および容量素子が適用されている記憶装置（以下、OSメモリ装置と呼ぶ場合がある）について説明する。OSメモリ装置は、少なくとも容量素子と、容量素子の充放電を制御するOSトランジスタを有する記憶装置である。OSトランジスタのオフ電流は極めて小さいので、OSメモリ装置は優れた保持特性をもち、不揮発性メモリとして機能させることができる。

20

#### 【0299】

##### <記憶装置の構成例>

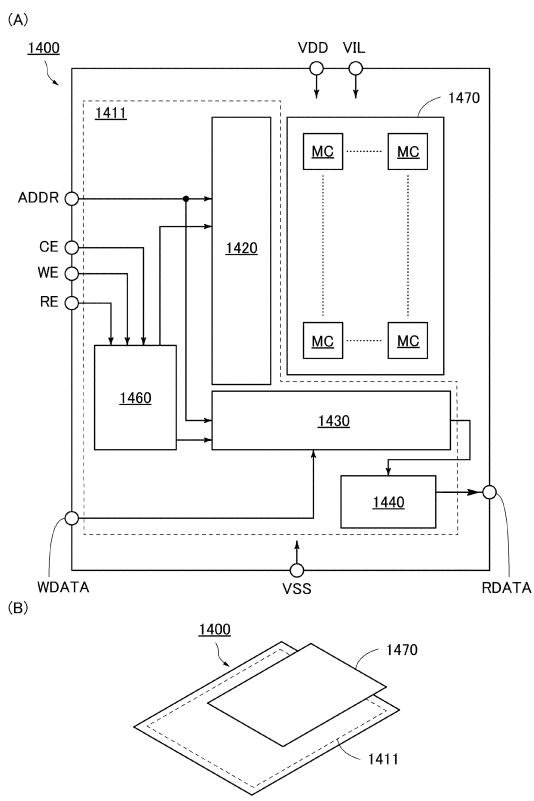

図 19 (A) に OS メモリ装置の構成の一例を示す。記憶装置 1400 は、周辺回路 1411、およびメモリセルアレイ 1470 を有する。周辺回路 1411 は、行回路 1420、列回路 1430、出力回路 1440、コントロールロジック回路 1460 を有する。

#### 【0300】

列回路 1430 は、例えば、列デコーダ、プリチャージ回路、センスアンプ、および書き込み回路等を有する。プリチャージ回路は、配線をプリチャージする機能を有する。センスアンプは、メモリセルから読み出されたデータ信号を増幅する機能を有する。なお、上記配線は、メモリセルアレイ 1470 が有するメモリセルに接続されている配線であり、詳しくは後述する。増幅されたデータ信号は、出力回路 1440 を介して、データ信号 DATA として記憶装置 1400 の外部に出力される。また、行回路 1420 は、例えば、行デコーダ、ワード線ドライバ回路等を有し、アクセスする行を選択することができる。

30

#### 【0301】

記憶装置 1400 には、外部から電源電圧として低電源電圧 (VSS)、周辺回路 1411 用の高電源電圧 (VDD)、メモリセルアレイ 1470 用の高電源電圧 (VIL) が供給される。また、記憶装置 1400 には、制御信号 (CE、WE、RE)、アドレス信号 ADDR、データ信号 WDATA が外部から入力される。アドレス信号 ADDR は、行デコーダおよび列デコーダに入力され、WDATA は書き込み回路に入力される。

40

#### 【0302】

コントロールロジック回路 1460 は、外部からの入力信号 (CE、WE、RE) を処理して、行デコーダ、列デコーダの制御信号を生成する。CE は、チップイネーブル信号であり、WE は、書き込みイネーブル信号であり、RE は、読み出しイネーブル信号である。コントロールロジック回路 1460 が処理する信号は、これに限定されるものではなく、必要に応じて、他の制御信号を入力すればよい。

#### 【0303】

メモリセルアレイ 1470 は、行列状に配置された、複数個のメモリセル MC と、複数の配線を有する。なお、メモリセルアレイ 1470 と行回路 1420 とを接続している配線の数は、メモリセル MC の構成、一列に有するメモリセル MC の数などによって決まる

50

。また、メモリセルアレイ 1470 と列回路 1430 とを接続している配線の数は、メモリセル MC の構成、一行に有するメモリセル MC の数などによって決まる。

#### 【0304】

なお、図 19 (A)において、周辺回路 1411 とメモリセルアレイ 1470 を同一平面上に形成する例について示したが、本実施の形態はこれに限られるものではない。例えば、図 19 (B) に示すように、周辺回路 1411 の一部の上に、メモリセルアレイ 1470 が重なるように設けられてもよい。例えば、メモリセルアレイ 1470 の下に重なるように、センスアンプを設ける構成にしてもよい。

#### 【0305】

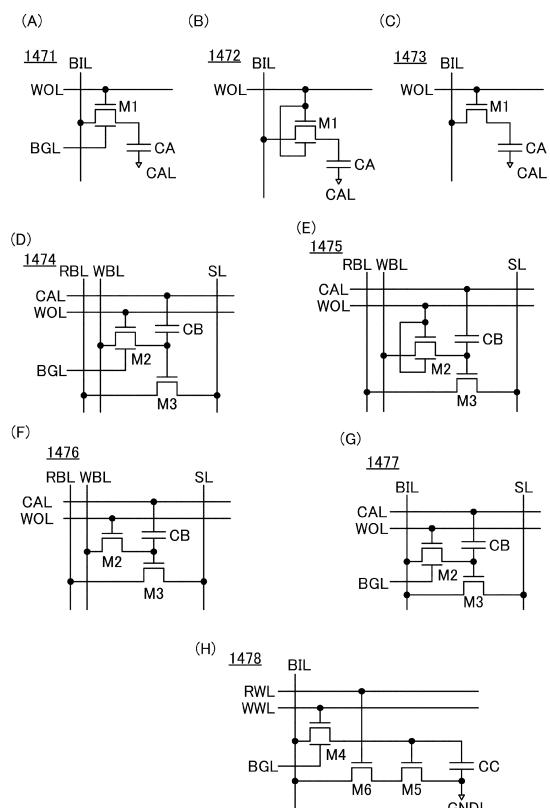

図 20 に上述のメモリセル MC に適用できるメモリセルの構成例について説明する。

10

#### 【0306】

#### [DOSRAM]

図 20 (A) 乃至 (C) に、DRAM のメモリセルの回路構成例を示す。本明細書等において、1OS トランジスタ 1 容量素子型のメモリセルを用いた DRAM を、DOSRAM (Dynamic Oxide Semiconductor Random Access Memory) と呼ぶ場合がある。図 20 (A) に示す、メモリセル 1471 は、トランジスタ M1 と、容量素子 CA と、を有する。なお、トランジスタ M1 は、ゲート (フロントゲートと呼ぶ場合がある)、及びバックゲートを有する。

#### 【0307】

トランジスタ M1 の第 1 端子は、容量素子 CA の第 1 端子と接続され、トランジスタ M1 の第 2 端子は、配線 BIL と接続され、トランジスタ M1 のゲートは、配線 WOL と接続され、トランジスタ M1 のバックゲートは、配線 BGL と接続されている。容量素子 CA の第 2 端子は、配線 CAL と接続されている。

20

#### 【0308】

配線 BIL は、ビット線として機能し、配線 WOL は、ワード線として機能する。配線 CAL は、容量素子 CA の第 2 端子に所定の電位を印加するための配線として機能する。データの書き込み時、及び読み出し時において、配線 CAL には、低レベル電位を印加するのが好ましい。配線 BGL は、トランジスタ M1 のバックゲートに電位を印加するための配線として機能する。配線 BGL に任意の電位を印加することによって、トランジスタ M1 のしきい値電圧を増減することができる。

30

#### 【0309】

また、メモリセル MC は、メモリセル 1471 に限定されず、回路構成の変更を行うことができる。例えば、メモリセル MC は、図 20 (B) に示すメモリセル 1472 のように、トランジスタ M1 のバックゲートが、配線 BGL でなく、配線 WOL と接続される構成にしてもよい。また、例えば、メモリセル MC は、図 20 (C) に示すメモリセル 1473 ように、シングルゲート構造のトランジスタ、つまりバックゲートを有さないトランジスタ M1 で構成されたメモリセルとしてもよい。

#### 【0310】

上記実施の形態に示す半導体装置をメモリセル 1471 等に用いる場合、トランジスタ M1 としてトランジスタ 200 を用い、容量素子 CA として容量素子 100 を用いることができる。トランジスタ M1 として OS トランジスタを用いることによって、トランジスタ M1 のリーク電流を非常に低くすることができる。つまり、書き込んだデータをトランジスタ M1 によって長時間保持することができるため、メモリセルのリフレッシュの頻度を少なくすることができる。また、メモリセルのリフレッシュ動作を不要にすることができる。また、リーク電流が非常に低いため、メモリセル 1471、メモリセル 1472、メモリセル 1473 に対して多値データ、又はアナログデータを保持することができる。

40

#### 【0311】

また、DOSRAMにおいて、上記のように、メモリセルアレイ 1470 の下に重なるように、センスアンプを設ける構成にすると、ビット線を短くすることができる。これにより、ビット線容量が小さくなり、メモリセルの保持容量を低減することができる。