RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

2 482 382

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 81 08977**

(54) Circuit à miroir de courant à haute impédance de sortie et à basse « perte de tension ».

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 03 F 1/56, 3/343.

(22) Date de dépôt..... 6 mai 1981.

(33) (32) (31) Priorité revendiquée : *Italie, 12 mai 1980, n° 21976 A/80.*

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 46 du 13-11-1981.

(71) Déposant : Société dite : SGS-ATES COMPONENTI ELETTRONICI SPA, résidant en Italie.

(72) Invention de : Marco Siligoni.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Office Blétry,

2, bd de Strasbourg, 75010 Paris.

La présente invention concerne les générateurs de courant à transistors et, plus précisément, un circuit à miroir de courant, particulièrement adapté pour être utilisé dans des circuits intégrés linéaires à basse tension d'alimentation.

5 Le montage de deux transistors "en miroir de courant" est connu en soi et est utilisé fréquemment dans le projetage de circuits intégrés..

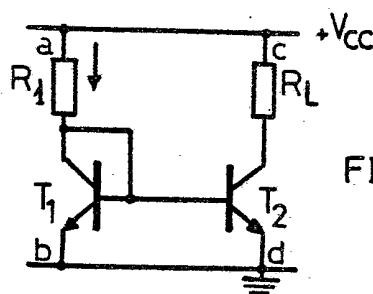

10 Un circuit de ce type est représenté sur la fig. 1. Les deux transistors, désignés par  $T_1$  et  $T_2$ , sont semblables et du type NPN. La base et l'émetteur de  $T_1$  sont reliés respectivement à la base et à l'émetteur de  $T_2$ . Le collecteur de  $T_1$  est connecté à la fois à la base commune des deux transistors et, par l'intermédiaire d'une résistance  $R_1$ , à une ligne d'alimentation  $+V_{cc}$ . Le collecteur de  $T_2$  est également raccordé à la ligne d'alimentation par l'intermédiaire d'une charge représentée 15 par une résistance  $R_L$ .

15 Si l'on examine le fonctionnement du circuit, on peut voir qu'il passe, à travers la branche a, un courant  $I_a = \frac{V_{cc} - V_{BE}}{R_1}$ ,  $V_{BE}$  étant la tension de la jonction base-émetteur du transistor  $T_1$ . Si l'on néglige les courants de base  $I_B$  par rapport aux courants de collecteur, ce qui est licite si le gain des transistors est suffisamment élevé, le courant qui passe par la branche b est égal à  $I_a$ . Etant donné que les deux transistors 20 sont semblables et ont la même tension base-émetteur ( $V_{BE}$ ), le courant qui passe dans la branche d est égal à celui qui passe dans la branche b. La branche c est parcourue par un courant  $I_C$  qui est à peu près égal à celui qui passe dans la branche d, ce qui fait que  $I_C = I_a$ . En conséquence, la charge  $R_L$  est 25 parcourue par un courant constant, déterminé par des paramètres de circuit fixés au préalable.

Un circuit du même type peut être réalisé avec deux transistors différents l'un de l'autre en ce qui concerne les dimensions et les caractéristiques de construction, donnant  $I_C = K I_a$ , K étant une constante. En outre, il est évident que 5 les deux transistors peuvent être du type PNP au lieu de NPN.

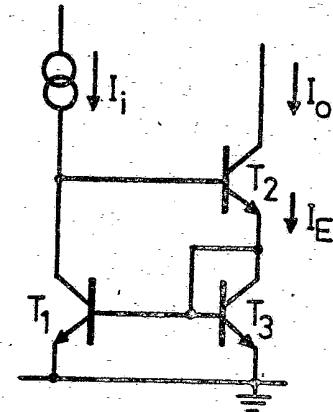

Un perfectionnement connu du circuit à miroir de courant représenté sur la fig. 1 est celui de la fig. 2, appelé "miroir de Wilson", dans laquelle on confie à un "circuit à miroir", comprenant les transistors  $T_1$  et  $T_3$ , la fonction de contrôler 10 le courant de base  $I_B$  du transistor  $T_2$  et, par suite, son courant de collecteur  $I_C = \beta I_B$ ,  $\beta$  étant le gain de courant de  $T_2$ .

Le transistor  $T_3$  joue le rôle de sonde de courant, sensible au courant d'émetteur  $I_E$  du transistor  $T_2$ . La base du transistor  $T_1$  est reliée à la base du transistor  $T_3$ . Le collecteur de  $T_3$  est relié à l'émetteur de  $T_2$  et directement à la 15 base de ce même transistor  $T_3$ . Le collecteur de  $T_1$  est relié à la base de  $T_2$ , dans laquelle arrive par conséquent le courant-somme du courant d'entrée  $I_i$  et du courant de collecteur de  $T_1$ .

Avec ce schéma, on peut maintenir constant le courant 20 de référence  $I_E$ . Toutefois, étant donné que le courant de collecteur de  $T_2$ ,  $I_C = \alpha I_E$ , est lié au courant d'émetteur par le paramètre qui est fonction de la tension collecteur-émetteur  $V_{CE}$ , le courant de sortie  $I_o = I_C$  dépend à son tour de la valeur 25 de cette tension. Un tel circuit ne garantit donc pas la constance du courant de sortie  $I_o$ .

Un générateur de courant idéal est caractérisé par une résistance interne infinie et par une chute de tension interne égale à zéro. Un générateur de courant réel doit avoir des caractéristiques qui s'approchent le mieux possible de celles 30 d'un générateur idéal. Un générateur de courant réel est donc d'autant meilleur que cette approximation est grande.

Le circuit d'un générateur de courant réel doit donc présenter à la sortie une impédance élevée et une "perte de tension" très basse, l'expression "perte de tension" désignant ci-après la tension minimale nécessaire pour que le circuit 35 maintienne ses caractéristiques de fonctionnement typiques.

Le circuit à "miroir de Wilson" a une impédance de sortie beaucoup plus élevée que celle d'un circuit du type

à "émetteur à la masse" indiqué sur la fig. 1 dans le rapport  $\beta/2 : 1$ , mais sa "perte de tension" est plus élevée ; en effet

$$V_{\min} = V_{CE \text{ sat } T_2} + V_{BE T_3}$$

5

$V_{CE \text{ sat } T_2}$  étant la tension collecteur-émetteur du transistor  $T_2$  à la limite de la saturation et  $V_{BE T_3}$  étant la tension base-émetteur du transistor  $T_3$ .

Un circuit suivant le schéma de la fig. 1 a par contre

10

$$V_{\min} = V_{CE \text{ sat } T_2}$$

On a donc cherché, avec d'autres schémas connus, à s'approcher davantage des caractéristiques du générateur de courant idéal. On connaît par exemple un circuit à miroir de courant semblable à celui qui est représenté sur la fig. 1, dans lequel des résistances appropriées  $R_E$  sont montées en série avec les émetteurs des transistors ; un tel montage permet d'augmenter l'impédance de sortie d'un facteur  $(1 + R_E/r_e)$  par rapport au circuit connu représenté sur la fig. 1,  $r_e$  représentant la résistance interne d'émetteur du transistor de la branche de sortie, mais en même temps la chute de tension accrue  $R_E I_E$  sur la résistance d'émetteur fait que la perte de tension augmente dans une mesure correspondante.

25

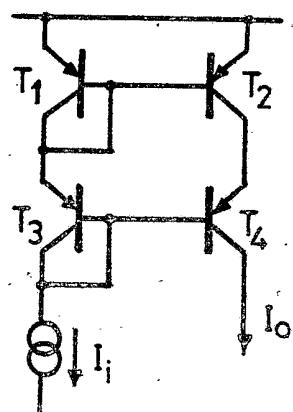

Un autre montage connu est le circuit à miroirs de courant "en cascade" représenté sur la fig. 3. Dans ce cas, on maintient en zone active le fonctionnement du transistor  $T_2$ , par l'entremise du transistor  $T_3$  monté en diode avec sa base court-circuitée sur le collecteur, et le transistor  $T_1$  impose, par l'intermédiaire du transistor  $T_2$ , le courant d'émetteur du transistor  $T_4$ , élévant l'impédance de sortie de celui-ci.

30

Cela ne permet toutefois pas de diminuer la perte de tension au-dessous de la valeur

35

$$V_{\min} = V_{BE T_2} + V_{CE \text{ sat } T_4}$$

$V_{BE T_2}$  étant la tension base-émetteur du transistor  $T_2$  et  $V_{CE \text{ sat } T_4}$  étant la tension de saturation du transistor  $T_4$ .

L'amélioration d'impédance de sortie par rapport au circuit de la fig. 1 est le même que celle qui est obtenue avec le miroir de Wilson, c'est-à-dire dans le rapport  $\beta/2 : 1$ .

Le but de la présente invention est de réaliser un circuit à miroir de courant qui ait la plus basse perte de tension qu'il soit possible d'obtenir dans un circuit à miroir de courant à transistors et qui ait en même temps une impédance de sortie plus élevée que celle des circuits connus à basse perte de tension, de telle sorte qu'il se prête particulièrement bien à une utilisation dans des circuits intégrés à basse tension d'alimentation.

Ce but est atteint avec un circuit transducteur de courant comportant une première borne de raccordement à un générateur de courant d'entrée, une deuxième et une troisième bornes de raccordement aux bornes d'un générateur de tension d'alimentation, et comprenant un circuit à miroir de courant principal à transistors, caractérisé en ce qu'il comprend un montage comparateur et amplificateur de courant, circuit à miroir de courant secondaire à transistors, ce circuit à miroir de courant comportant une branche d'entrée raccordée à l'une des branches de sortie du circuit à miroir principal, une branche de sortie raccordée à une première borne d'entrée du montage comparateur et amplificateur, ce montage comparateur et amplificateur comportant une seconde borne d'entrée raccordée au générateur de courant d'entrée et une borne de sortie raccordée à la branche d'entrée du circuit à miroir principal.

L'invention pourra être bien comprise à l'aide de la description détaillée qui suit, donnée purement à titre d'exemple et, par conséquent, non limitative, en référence aux dessins annexés qui, pour les trois premiers d'entre eux, ont été déjà pris en considération.

La fig. 1 est le schéma d'un circuit à miroir de courant de type connu, dans sa forme la plus simple.

La fig. 2 est le schéma d'un circuit à miroir de courant connu, appelé "miroir de Wilson".

La fig. 3 est le schéma d'un circuit connu, comprenant des "miroirs de courant" en cascade.

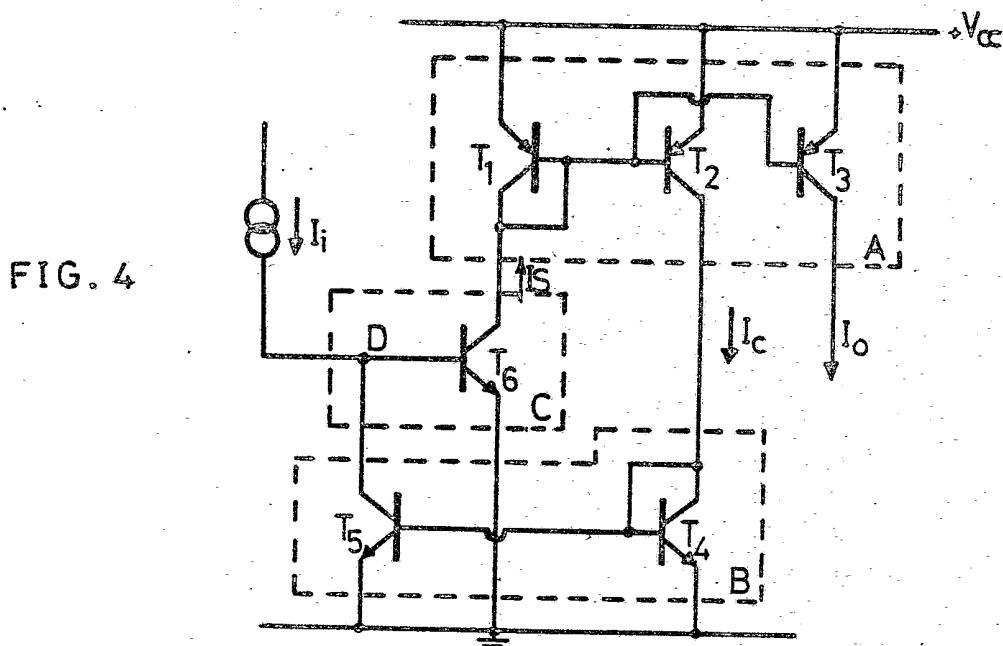

La fig. 4 est le schéma d'un circuit à miroir de courant suivant l'invention.

Si l'on examine le schéma de circuit de la fig. 4, on voit que celui-ci comprend six transistors désignés par  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ,  $T_5$  et  $T_6$ , parmi lesquels  $T_1$ ,  $T_2$  et  $T_3$  sont du type bipolaire PNP et  $T_4$ ,  $T_5$  et  $T_6$  sont du type bipolaire NPN.

Le transistor  $T_1$  est raccordé à la fois à  $T_2$  et à  $T_3$  suivant le schéma en miroir de courant. Le circuit ainsi constitué est délimité sur la fig. 4 par une ligne de tirets et il est désigné par la lettre A.

Les transistors  $T_4$  et  $T_5$  sont reliés entre eux suivant le schéma en miroir de courant désigné par la lettre B.

Le collecteur du transistor  $T_1$  et celui du transistor  $T_2$  sont connectés respectivement aux collecteurs des transistors  $T_6$  et  $T_4$ . Le collecteur du transistor  $T_5$  est relié à un générateur de courant d'entrée  $I_i$  et à la base du transistor  $T_6$  par le point de jonction D.

Le circuit constitué par le transistor  $T_6$  et le point de jonction D est désigné par la lettre C.

Les émetteurs des transistors  $T_1$ ,  $T_2$  et  $T_3$  sont raccordés au pôle positif  $+V_{CC}$  d'un générateur de tension d'alimentation, ceux des transistors  $T_4$ ,  $T_5$  et  $T_6$  sont reliés au pôle négatif du même générateur de tension.

D'après le schéma de la fig. 4, il n'est associé au transistor  $T_L$ , pour constituer un circuit à miroir de courant, que deux transistors ( $T_2$  et  $T_3$ ), mais de façon générale, beaucoup d'autres transistors peuvent être associés au transistor  $T_1$  suivant la même disposition.

Chacun des transistors raccordés de cette manière à  $T_1$  suivant le schéma en miroir de courant constitue un générateur de courant capable de piloter d'autres circuits. L'un de ces transistors, par exemple  $T_2$  dans le cas représenté sur la figure, est raccordé au miroir de courant B qui en détecte le courant de collecteur  $I_C$  et le transfère à la base de  $T_6$ , permettant le contrôle du courant  $I_C$  par rapport au courant d'entrée  $I_i$  et, au moyen de  $T_6$ , sa régulation.

De même, le courant de collecteur  $I_O$  de  $T_3$  (et des autres transistors éventuellement raccordés de la manière indiquée) est contrôlé et réglé automatiquement de façon identique.

Ce nouveau circuit à miroir de courant permet donc la régulation du courant de collecteur  $I_C$  en le contrôlant directement, contrairement à ce qui se produit dans le cas du "miroir de Wilson".

Pour faciliter le calcul, on considérera le cas dans lequel il est raccordé à la base de  $T_1$ , outre les transistors  $T_2$  et  $T_3$ , n-1 autres transistors semblables à  $T_2$  et à  $T_3$ .

Le courant de base du transistor  $T_6$  est

$$I_{B6} = I_i - I_{C5} = I_i - \beta I_{B5}$$

(les suffixes indiquant respectivement les courants d'émetteur, de collecteur et de base  $I_E$ ,  $I_C$ ,  $I_B$ , suivis du numéro du transistor auquel ils se rapportent).

Le courant de base du transistor  $T_5$  est lié au courant  $I_C$  par la relation.

$$I_C = I_{B5} + I_{B4} + I_{C4} = I_{B5} + I_{B4} + \beta I_{B4}$$

et, en conséquence, si  $I_{B4} = I_{B5}$ , il en résulte :  $I_{B5} = \frac{I_C}{2 + \beta}$

Le courant de base du transistor  $T_6$  est donc

$$I_{B6} = I_i - \frac{\beta}{2 + \beta} I_C \quad (1)$$

Le courant de collecteur du transistor  $T_6$  qui entre dans le miroir de courant A est

$$I_{C6} = \beta' I_{B1} + I_{B1} + I_{B2} + n I_B$$

$I_B$  étant le courant de base du transistor  $T_3$  et des autres transistors montés de façon semblable. Pour simplifier l'exemple, on peut poser  $I_B = I_{B2}$ . Par  $\beta'$ , on désigne le gain des transistors PNP (en général inférieur au gain  $\beta$  des transistors NPN du même circuit intégré). Avec  $I_{B2} = \frac{I_C}{\beta'}$ , le courant de base du transistor  $T_1$  est

$$I_{B1} = (n + 1) \frac{I_C}{\beta'}$$

Le courant de collecteur du transistor a alors pour valeur

$$I_{C6} = (n+1) \frac{\beta' + 1}{\beta'} I_C + (n+1) \frac{I_C}{\beta'} = (n+1) \frac{\beta' + 2}{\beta'} I_C \quad (2)$$

5 et, du fait que  $I_{C6} = \beta I_{B6}$ , il résulte de (1) et (2) que :

$$\beta I_i = \frac{\beta^2}{2 + \beta} I_C + (n+1) \frac{\beta' + 2}{\beta'} I_C$$

10 Etant donné que la valeur du gain est bien supérieure à 2, tant pour les transistors NPN que pour les transistors PNP, on peut appliquer l'approximation

$$\beta I_i = \beta I_C + (n+1) I_C$$

15 Pourvu que le nombre de transistors montés en miroir de courant (A) soit négligeable par rapport à la valeur  $\beta$ , on a

$$I_i \approx I_C \quad (3)$$

20 Quoi qu'il en soit, avec des dispositions connues des projeteurs de circuits linéaires, l'influence des courants de base sur les courants de collecteur peut être rendue minime et, en conséquence, l'équation (3) sera valable à plus forte raison.

25 Le circuit de l'invention a une perte de tension égale à

$$V_{min} = V_{CE \text{ sat } T_3}$$

30  $V_{CE \text{ sat } T_3}$  désignant la tension collecteur-émetteur du transistor  $T_3$  lorsqu'il fonctionne à la limite de saturation.

La perte de tension a donc une valeur constante et égale à la valeur minimale que l'on peut obtenir dans un circuit à miroir de courant à transistors.

35 L'impédance de sortie du circuit de l'invention est plus élevée que celle des circuits connus qui ont eux aussi une perte de tension faible et constante. En effet, le circuit de l'invention a une impédance de sortie  $\beta$  à la fois plus grande

que celle du circuit à miroir de courant à émetteur à la masse (fig. 1), c'est-à-dire que sa valeur est double de celle de l'impédance de sortie du "miroir de Wilson" et du circuit "à miroirs en cascade". En conséquence, le circuit de l'invention 5 s'approche davantage des caractéristiques d'un générateur de courant idéal que les montages connus ; il se prête donc à l'utilisation de tensions d'alimentation inférieures à celles qu'exigent les circuits des réalisations connues, caractéristique qui est très importante pour certaines applications à basse 10 tension d'alimentation.

Bien qu'il ait été illustré et décrit un seul exemple d'exécution de l'invention, il va de soi que de nombreuses variantes sont possibles sans que l'on s'écarte pour autant du cadre de l'invention. Par exemple, les connexions directes 15 entre bases et collecteurs des transistors  $T_1$  et  $T_4$  du circuit de la fig. 4 peuvent être remplacées chacune par une jonction base-émetteur d'un transistor. En outre, les transistors bipolaires pourraient être remplacés en totalité ou en partie par des transistors à effet de champ, avec des modifications appropriées du circuit, à la portée du spécialiste en la matière. 20

- REVENDICATIONS -

1. Circuit transducteur de courant, comportant une première borne de raccordement à un générateur de courant d'entrée ( $I_i$ ), une deuxième et une troisième bornes de raccordement aux bornes d'un générateur de tension d'alimentation, et comprenant 5 un circuit à miroir de courant principal (A) à transistors, présentant une branche d'entrée et au moins deux branches de sortie à chacune desquelles peut être connecté un circuit utilisateur, caractérisé en ce qu'il comprend un montage comparateur et amplificateur de courant (C) et un circuit à miroir de courant secondaire (B) à transistors, ce circuit à miroir de courant comportant une branche d'entrée raccordée à l'une des branches de sortie du circuit à miroir principal (A) et une branche de sortie raccordée à une première borne d'entrée du montage comparateur et amplificateur (C), ce montage comparateur et amplificateur (C) comportant une seconde borne d'entrée raccordée au générateur de courant d'entrée ( $I_i$ ) et une borne de sortie raccordée 10 à la branche d'entrée du circuit à miroir principal (A).

15

2. Circuit selon la revendication 1, dans lequel le circuit à miroir de courant principal (A) comprend un premier transistor ( $T_1$ ), un deuxième transistor ( $T_2$ ) et au moins un troisième transistor ( $T_3$ ) comportant chacun une première, une 20 seconde bornes et une borne de commande, la borne de commande du second transistor ( $T_2$ ) et la borne de commande du troisième transistor ( $T_3$ ) étant raccordées à la borne de commande du premier transistor ( $T_1$ ), et la première borne du premier transistor ( $T_1$ ), la première borne du deuxième transistor ( $T_2$ ) et la première 25 borne du troisième transistor ( $T_3$ ) étant raccordées à un même pôle d'un générateur de tension, un organe d'accouplement étant interposé entre la seconde borne et la borne de commande du

5 premier transistor ( $T_1$ ), caractérisé en ce que le circuit à miroir de courant secondaire (B) comprend un quatrième ( $T_4$ ) et un cinquième ( $T_5$ ) transistors ayant chacun une première, une seconde bornes et une borne de commande, la borne de commande du cinquième

10 transistor ( $T_5$ ) étant raccordée à la borne de commande du quatrième transistor ( $T_4$ ), la borne de commande et la seconde borne du quatrième transistor ( $T_4$ ) étant raccordées entre elles par un organe d'accouplement, les premières bornes du quatrième ( $T_4$ ) et du cinquième ( $T_5$ ) transistors étant connectées au pôle du générateur de tension opposé à celui auquel sont raccordés les transistors compris dans le circuit à miroir principal (A), la seconde borne du cinquième transistor ( $T_5$ ) étant la branche de sortie du circuit à miroir de courant secondaire (B) et la seconde borne du quatrième transistor ( $T_4$ ) étant la branche d'entrée du circuit à miroir de courant secondaire (B).

15 3. Circuit selon la revendication 1 ou 2, caractérisé en ce que le montage comparateur et amplificateur de courant (C) comprend un noeud comparateur (D) et un sixième transistor ( $T_6$ ) comportant une première borne raccordée au pôle du générateur de tension auquel sont raccordés le quatrième ( $T_4$ ) et le cinquième ( $T_5$ ) transistors, une seconde borne constituant la branche de sortie du montage et une borne de commande raccordée au noeud comparateur (D), ce noeud étant raccordé à la première et à la seconde bornes d'entrée du montage comparateur et amplificateur.

20 25 4. Circuit selon la revendication 2 ou 3, caractérisé en ce que le premier ( $T_1$ ), le deuxième ( $T_2$ ), le troisième ( $T_3$ ), le quatrième ( $T_4$ ), le cinquième ( $T_5$ ) et le sixième ( $T_6$ ) transistors sont des transistors bipolaires, la première borne, la borne de commande et la seconde borne de chacun d'entre eux étant respectivement l'émetteur, la base et le collecteur.

30 35 5. Circuit selon la revendication 2 ou 3, caractérisé en ce que le premier ( $T_1$ ), le deuxième ( $T_2$ ), le troisième ( $T_3$ ), le quatrième ( $T_4$ ), le cinquième ( $T_5$ ) et le sixième ( $T_6$ ) transistors sont des transistors à effet de champ, la première borne, la borne de commande et la seconde borne de chacun d'entre eux étant respectivement la "source", la gâchette" et le "drain".

6. Circuit selon l'une quelconque des revendications 1 à 5, caractérisé en ce que tout le circuit est intégré dans un bloc monolithique de semiconducteur.

1/1

2482382

FIG. 1

FIG. 2

FIG. 3

FIG. 4