(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4804760号

(P4804760)

(45) 発行日 平成23年11月2日(2011.11.2)

(24) 登録日 平成23年8月19日(2011.8.19)

|               |                                |

|---------------|--------------------------------|

| (51) Int.Cl.  | F 1                            |

| HO 1 L 41/22  | (2006.01) HO 1 L 41/22 Z       |

| HO 1 L 41/083 | (2006.01) HO 1 L 41/08 Q       |

| HO 1 L 41/24  | (2006.01) HO 1 L 41/22 A       |

| HO 1 L 41/18  | (2006.01) HO 1 L 41/18 1 O 1 Z |

| HO 4 R 17/00  | (2006.01) HO 4 R 17/00         |

請求項の数 10 (全 16 頁)

(21) 出願番号 特願2005-14730 (P2005-14730)

(22) 出願日 平成17年1月21日 (2005.1.21)

(65) 公開番号 特開2006-203077 (P2006-203077A)

(43) 公開日 平成18年8月3日 (2006.8.3)

審査請求日 平成19年7月3日 (2007.7.3)

(73) 特許権者 306037311

富士フィルム株式会社

東京都港区西麻布2丁目26番30号

(74) 代理人 100075281

弁理士 小林 和憲

(74) 代理人 100095234

弁理士 飯嶋 茂

(74) 代理人 100117536

弁理士 小林 英了

(72) 発明者 和田 貢

神奈川県足柄上郡開成町宮台798番地

富士写真フィルム株式会社内

審査官 井原 純

最終頁に続く

(54) 【発明の名称】積層型圧電構造体の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1電極層、圧電体層、第2電極層、圧電体層の順に繰り返し積層されてなる積層体と、この積層体の1つの側面に形成され、前記第1電極層と電気的に接続されるとともに、前記第2電極層と第1絶縁膜を介して絶縁された第1側面電極と、

前記積層体の他の側面に形成され、前記第2電極層と電気的に接続されるとともに、前記第1電極層と第2絶縁膜を介して絶縁された第2側面電極とを備えてなる積層型圧電構造体の製造方法において、

切断加工前のワークピースとして、第1電極層、圧電体層、第2電極層、圧電体層の順に繰り返し積層され、前記圧電体層によって前記第1電極層と前記第2電極層とが絶縁されるとともに、前記各第1電極層の一部が共通に接続された第1共通電極部と、前記各第2電極層の一部が共通に接続された第2共通電極部とを有するものを用い、

前記ワークピースに、前記第1電極層と前記第1共通電極部との接続および前記第2電極層と前記第2共通電極部との接続を分離しないように、前記第1および第2共通電極部以外を第1方向に沿って複数個所切断することにより、複数の平行な第1溝を形成する工程と、

前記各第1溝内の側面における前記第1電極層の露出部に前記第1絶縁膜を形成する工程と、

前記各第1溝にレジスト材を埋入する工程と、

10

20

隣接する前記第1溝の中間位置に、前記各第1溝に平行に第2溝を形成する工程と、前記各第2溝内の側面における前記第2電極層の露出部に前記第2絶縁膜を形成する工程と、

前記レジスト材を除去する工程と、

前記第1および第2溝内の側面に前記第1および第2側面電極をそれぞれ形成する工程と、

前記第1および第2共通電極部を切り落とす工程と、

を含むことを特徴とする積層型圧電構造体の製造方法。

**【請求項2】**

前記第1方向に交わる第2方向に沿って前記ワークピースを複数に切断する工程をさらに含むことを特徴とする請求項1記載の積層型圧電構造体の製造方法。 10

**【請求項3】**

基板上に、第1領域と、この第1領域に一部が重なる第2領域とを設定し、前記第1領域に前記第1電極層を積層、前記第1領域および前記第2領域との重なり部分に前記圧電体層を積層、前記第2領域に前記第2電極層を積層することによって前記ワークピースを形成することを特徴とする請求項1または2記載の積層型圧電構造体の製造方法。

**【請求項4】**

前記第1および第2電極層をスパッタ法または蒸着法によって形成することを特徴とする請求項3記載の積層型圧電構造体の製造方法。

**【請求項5】**

前記圧電体層をエアロゾルデポジション法によって形成することを特徴とする請求項3または4記載の積層型圧電構造体の製造方法。 20

**【請求項6】**

前記ワークピースは、圧電体層の端部がテーパ状に形成され、このテーパ部は、前記第1および第2電極層の端部を覆っていることを特徴とする請求項1から5いずれか1項に記載の積層型圧電構造体の製造方法。

**【請求項7】**

前記第1および第2共通電極部に所定の電圧を印加して、前記圧電体層のポーリング処理を行うことを特徴とする請求項1から6いずれか1項に記載の積層型圧電構造体の製造方法。 30

**【請求項8】**

前記ワークピースの切断は、ダイサーまたはサンドブラストを用いて行うことを特徴とする請求項1から7いずれか1項に記載の積層型圧電構造体の製造方法。

**【請求項9】**

前記第1および第2共通電極部を選択的に電着用の電極として用い、電圧が印加された前記第1および第2電極層の露出部に絶縁材料を電着させることによって前記第1および第2絶縁膜を形成することを特徴とする請求項1から8いずれか1項に記載の積層型圧電構造体の製造方法。

**【請求項10】**

前記第1および第2共通電極部を選択的に電解メッキ用の電極として用い、電圧が印加された前記第1および第2電極層の露出部に金属メッキ膜を形成し、この金属メッキ膜を、酸化、窒化、硫化、またはフッ化して絶縁化することによって前記第1および第2絶縁膜を形成することを特徴とする請求項1から9いずれか1項に記載の積層型圧電構造体の製造方法。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、圧電体層と電極層とが交互に積層されてなる積層型圧電構造体の製造方法に関する。

**【背景技術】**

## 【0002】

圧電体層の上下に電極層が形成されてなる圧電素子は、圧電アクチュエータや超音波トランスデューサなどの用途に利用されている。近年の微細加工技術の進歩に伴い、圧電素子の微細化および圧電素子を複数配列したアレイの集積化、小型化が進んでいる。

## 【0003】

このような圧電素子を単に微細化すると、面積の低下に伴って電極間の容量が減少して電気インピーダンスが上昇するので、圧電素子を駆動するための信号回路とのインピーダンスマッチングが取れず、電力が供給され難くなり、圧電素子の性能が低下するという問題があった。そこで、素子を微細化するとともに電極間容量を大きくするために、複数の圧電体層と複数の電極層とを交互に積層し、電極層を一層おきに共通に接続した積層型圧電素子が知られている（例えば、特許文献1参照）。

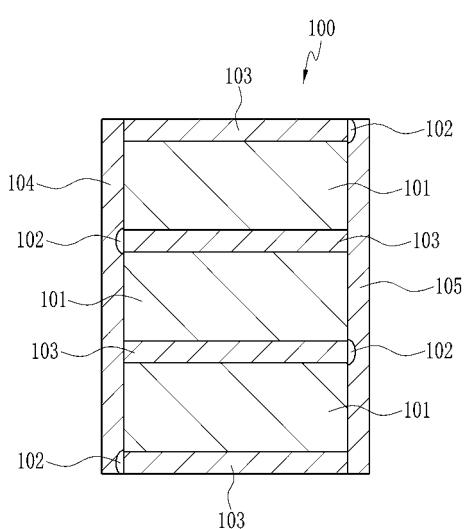

## 【0004】

図24は、特許文献1に記載の従来の積層型圧電素子の構造を示す。積層型圧電素子100は、複数の圧電体層101、端部に絶縁膜102が形成された複数の電極層103、および2つの側面電極104、105を備えている。側面電極104、105の各々には、電極層103が一層おきに接続されるとともに、電極層103が一層おきに絶縁膜102によって絶縁されている。側面電極104と側面電極105との間に所定電圧を与えると、圧電効果によって各圧電体層101が伸縮する。

## 【0005】

このような積層型圧電素子100を製造する方法として、まず、圧電体層101と電極層103とを交互に積層し、対向する2つの側面における電極層103の露出部分に交互に絶縁膜102を形成した後、該側面を覆うように側面電極104、105を形成する方法が用いられている。ところで、積層型圧電素子100を1次元または2次元状に配列したアレイを製造する場合には、素子間の狭い溝の中で電極層103の露出部分に選択的に絶縁膜102を形成しなければならず、絶縁膜102の形成に際して従来の印刷技術やフォトリソグラフィ技術が実施できない場合が多い。

## 【0006】

このため、特許文献1では、電着液中において電極層103の露出部分に樹脂イオンを電着させることで絶縁膜102を形成するようにしている。

## 【特許文献1】特開2003-174209号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0007】

しかしながら、特許文献1記載の方法で絶縁膜102を形成するには、電極層103に電圧を印加するために電圧供給用の配線を別途設ける必要がある。このような配線を設けるには、半導体素子などの製造工程で用いられるワイヤボンディング法による方法が考えられるが、各電極層103にワイヤボンディングを行うと製造工程への負担が大きく、製造コスト的に問題がある。また、電極層103の積層間隔がおよそ100μm以下の場合には、精度的にワイヤボンディング法を用いることができないといった問題がある。

## 【0008】

また、圧電体層101には、例えばPZT（チタン酸ジルコン酸鉛）などの材料が用いられる。圧電体層101の圧電性能を高めるために、側面電極104と側面電極105との間に高電圧を印加して圧電材料に分極反転を行わせるポーリング処理が製造工程中に行われる。このポーリング処理に要される電圧は600V程度であり、積層型圧電素子100を圧電アクチュエータや超音波トランスデューサとして動作させるための電圧より大きく、数倍～数十倍大きい。従って、このポーリング処理時には、絶縁膜102に高電圧が印加されるため、絶縁破壊が生じることのないように絶縁膜102の厚みを十分厚くする必要がある。このため、アレイを製造する場合には、隣接する積層型圧電素子100間の間隔を大きくせざるをえず、上記製造方法では、アレイの高集積化、小型化に関して問題がある。

10

20

30

40

50

## 【0009】

また、積層型圧電素子100にポーリング処理を行った場合には、電極層103の間だけでなく、電極層103と側面電極104, 105との間にも電界が生じるため、圧電体層101内の分極の方向および強度は均一とはならない。このため、圧電体層101の圧電性能を充分に高めることができないといった問題がある。また、絶縁膜102の膜厚および絶縁性、電極層103と側面電極104, 105との接触具合などのばらつきによってポーリング処理による分極反転効果にばらつき生じることが考えられ、これによりアレイを構成する積層型圧電素子100間に性能差が生じることも問題として挙げられる。

## 【0010】

本発明は、上記の事情を考慮してなされたものであり、電極層を側面電極から絶縁するための絶縁膜を容易に形成することができる製造方法を提供することを第1の目的とする。また、積層型圧電素子アレイを高集積化、小型化することができる製造方法を提供することを第2の目的とする。また、圧電体層内の分極方向を揃えて圧電性能を充分に高めることができる製造方法を提供することを第3の目的とする。また、アレイを構成する積層型圧電素子間の圧電性能差を低減することができる製造方法を提供することを第4の目的とする。

## 【課題を解決するための手段】

## 【0011】

上記目的を達成するために、請求項1記載の発明の積層型圧電構造体の製造方法は、第1電極層、圧電体層、第2電極層、圧電体層の順に繰り返し積層されてなる積層体と、この積層体の1つの側面に形成され、前記第1電極層と電気的に接続されるとともに、前記第2電極層と第1絶縁膜を介して絶縁された第1側面電極と、前記積層体の他の側面に形成され、前記第2電極層と電気的に接続されるとともに、前記第1電極層と第2絶縁膜を介して絶縁された第2側面電極とを備えてなる積層型圧電構造体の製造方法において、切断加工前のワークピースとして、第1電極層、圧電体層、第2電極層、圧電体層の順に繰り返し積層され、前記圧電体層によって前記第1電極層と前記第2電極層とが絶縁されるとともに、前記各第1電極層の一部が共通に接続された第1共通電極部と、前記各第2電極層の一部が共通に接続された第2共通電極部とを有するものを用いることを特徴とする。

## 【0012】

なお、基板上に、第1領域と、この第1領域に一部が重なる第2領域とを設定し、前記第1領域に前記第1電極層を積層、前記第1領域および前記第2領域との重なり部分に前記圧電体層を積層、前記第2領域に前記第2電極層を積層することによって前記ワークピースを形成することが好ましい。

## 【0013】

また、前記第1および第2電極層をスパッタ法または蒸着法によって形成することが好ましい。また、前記圧電体層をエアロゾルデポジション法によって形成することが好ましい。

## 【0014】

また、前記ワークピースは、圧電体層の端部がテーパ状に形成され、このテーパ部は、前記第1および第2電極層の端部を覆っていることが好ましい。また、前記第1および第2共通電極部に所定の電圧を印加して、前記圧電体層のポーリング処理を行うことが好ましい。

## 【0015】

また、前記ワークピースの端部を切断して第1および第2側面を形成する工程と、前記第1側面における前記第1電極層の露出部に前記第1絶縁膜を形成する工程と、前記第2側面における前記第2電極層の露出部に前記第2絶縁膜を形成する工程と、前記第1および第2側面に前記第1および第2側面電極をそれぞれ形成する工程と、前記第1および第2共通電極部を切り落とす工程と、前記ワークピースを、前記第1および第2側面電極を複数に分割するように複数に切断する工程と、を含むことが好ましい。

10

20

30

40

50

## 【0016】

また、前記ワークピースに、前記第1電極層と前記第1共通電極部との接続および前記第2電極層と前記第2共通電極部との接続を分離しないように、前記第1および第2共通電極部以外を第1方向に沿って複数個所切断することにより、複数の平行な第1溝を形成する工程と、前記各第1溝内の側面における前記第1電極層の露出部に前記第1絶縁膜を形成する工程と、前記各第1溝にレジスト材を埋入する工程と、隣接する前記第1溝の中間位置に、前記各第1溝に平行に第2溝を形成する工程と、前記各第2溝内の側面における前記第2電極層の露出部に前記第2絶縁膜を形成する工程と、前記レジスト材を除去する工程と、前記第1および第2溝内の側面に前記第1および第2側面電極をそれぞれ形成する工程と、前記第1および第2共通電極部を切り落とす工程と、を含むことが好ましい。

10

## 【0017】

また、前記第1方向に交わる第2方向に沿って前記ワークピースを複数に切断する工程をさらに含むことが好ましい。また、前記ワークピースの切断は、ダイサーまたはサンドブラストを用いて行うことが好ましい。

## 【0018】

また、前記第1および第2共通電極部を選択的に電着用の電極として用い、電圧が印加された前記第1および第2電極層の露出部に絶縁材料を電着させることによって前記第1および第2絶縁膜を形成することが好ましい。また、前記第1および第2共通電極部を選択的に電解メッキ用の電極として用い、電圧が印加された前記第1および第2電極層の露出部に金属メッキ膜を形成し、この金属メッキ膜を、酸化、窒化、硫化、またはフッ化して絶縁化することによって前記第1および第2絶縁膜を形成することが好ましい。

20

## 【発明の効果】

## 【0019】

本発明によれば、切断加工前のワークピースとして、第1電極層、圧電体層、第2電極層、圧電体層の順に繰り返し積層され、圧電体層によって第1電極層と第2電極層とが絶縁されるとともに、各第1電極層の一部が共通に接続された第1共通電極部と、各第2電極層の一部が共通に接続された第2共通電極部とを有するものを用いるので、第1および第2共通電極部を選択的に電着用または電解メッキ用の電極として用いることにより、電極層を側面電極から絶縁するための絶縁膜を容易に形成することができる。

30

## 【0020】

本発明によれば、第1および第2側面電極を形成する前に圧電体層のポーリング処理を行い、上記絶縁膜にポーリング処理時の電圧が印加されることはないので、上記絶縁膜を薄くすることができ、この結果、アレイを高集積化、小型化することができる。また、第1および第2側面電極を形成する前に圧電体層のポーリング処理を行うことで、圧電体層内の分極方向が上下方向に揃うので、圧電性能を充分に高めることができる。また、圧電体層内の分極方向が均一になるので、アレイを構成する素子間の圧電性能差を低減することができる。

## 【発明を実施するための最良の形態】

## 【0021】

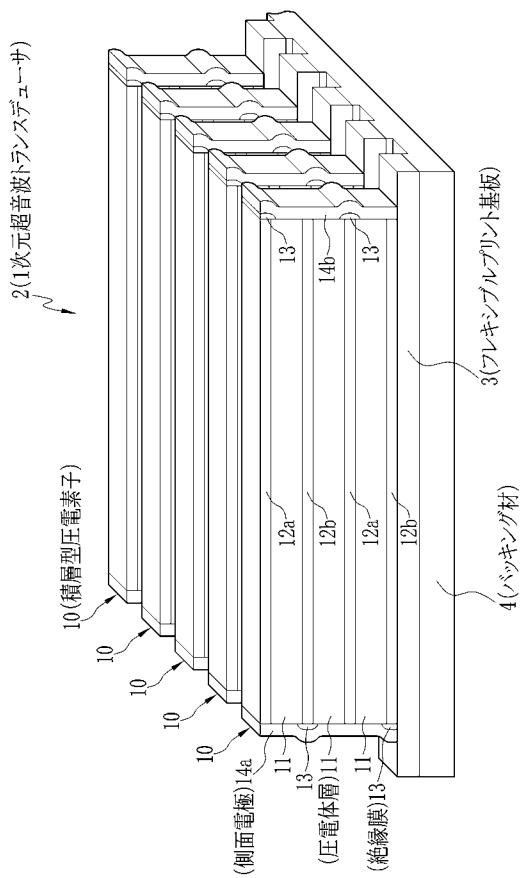

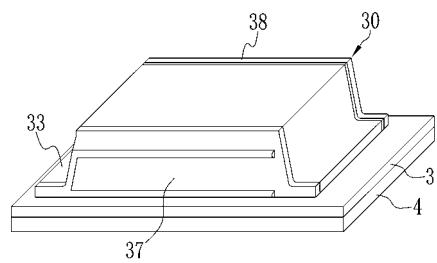

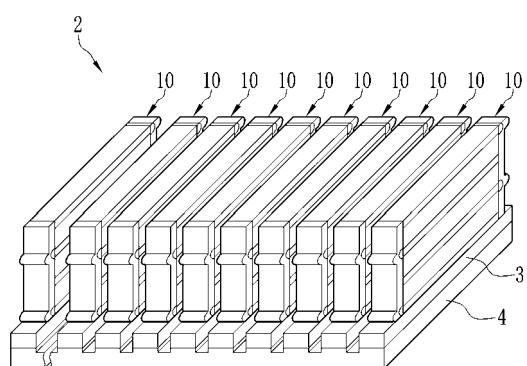

図1は、本発明の第1実施形態に係わる積層型圧電素子10が1次元状に配列されてなる1次元超音波トランスデューサ2を示す。各積層型圧電素子10は、例えば、長手方向の長さが約4mm、幅が約90μm、高さが約300μmの構造体であり、フレキシブルプリント(FPC)基板3上に固着されている。また、FPC基板3は、可撓性を有するバッキング材4上に固着されている。

40

## 【0022】

なお、バッキング材4を適宜の形状にすることによって、1次元超音波トランスデューサ2をいわゆるラジアル型やコンベックス型とすることができます。また、隣接する積層型圧電素子10間(溝部)にウレタンやエポキシ樹脂などの充填材(不図示)を充填し、さらに積層型圧電素子10全体を覆うように音響レンズ(不図示)を形成するようにしても

50

よい。

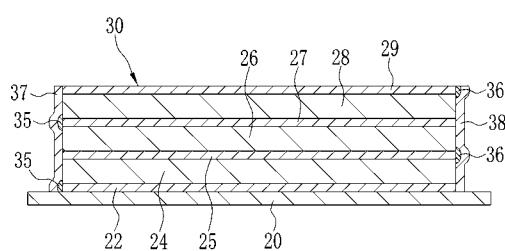

【0023】

積層型圧電素子10は、3つの圧電体層11と、各圧電体層11の上下に形成された電極層12a, 12bと、各電極層12a, 12bの1つの端面に形成された絶縁膜13と、対向する側面に形成された側面電極14a, 14bとから構成されている。電極層12aは、側面電極14aに接続されており、電極層12bは、側面電極14bに接続されている。なお、圧電体層の積層数は3層に限られず、適宜の数としてよく、例えば7層としてもよい。また、側面電極の形成部は、対向する2つの側面に限られず、異なる2つの面であればよい。

【0024】

圧電体層11は、90μm程度の厚さを有しており、材料としては、主たる化学組成としてPbZrO<sub>3</sub>およびPbTiO<sub>3</sub>を含む2元系固溶体であるPZT(チタン酸ジルコン酸鉛:Pb Zirconate Titanate)が用いられる。電極層12a, 12bは、3μm程度の厚さを有しており、材料としては酸化されにくい導電性材料が好ましく、白金(Pt)などが用いられる。

【0025】

絶縁膜13は、10μm程度の厚さを有しており、材料としては、アクリル系樹脂、フッ素系樹脂、ポリイミド系樹脂などの樹脂、ガラスやアルミナ(Al<sub>2</sub>O<sub>3</sub>)、ニッケル(Ni)などの金属酸化物などが用いられる。絶縁膜13は、電極層12aを側面電極14bから絶縁するため、および電極層12bを側面電極14aから絶縁するために設けられている。

【0026】

圧電体層11は、電極層12a, 12bに印加されたパルス電圧によって伸縮し、所定の周波数(例えば5~30MHz)の超音波を発生する。また逆に、圧電体層11は、外部からの超音波を受けて、超音波の周波数に応じた電圧を電極層12a, 12bに生成する。このように、1次元超音波トランスデューサ2は、超音波の送受信を行うことを可能とするものである。

【0027】

上記のように積層型圧電素子10には圧電体層11が複数積層されているので、単層の場合と比べて、圧電体層11に対向する電極の面積が大きく(つまり電極間容量が大きく)、電気的インピーダンスを下げることができる。従って、積層型圧電素子10に印加される電圧のロスが低減し、積層型圧電素子10は印加される電圧に対して効率よく駆動される。

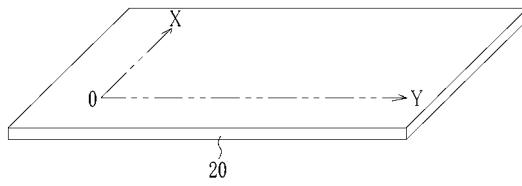

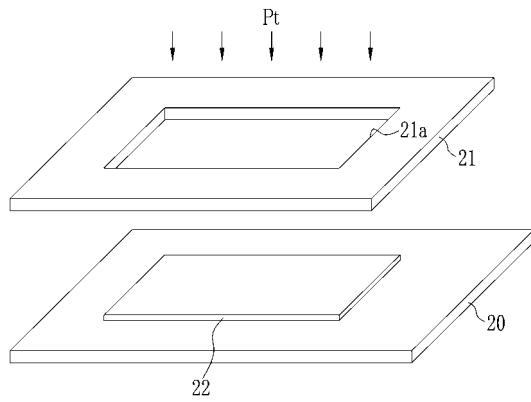

【0028】

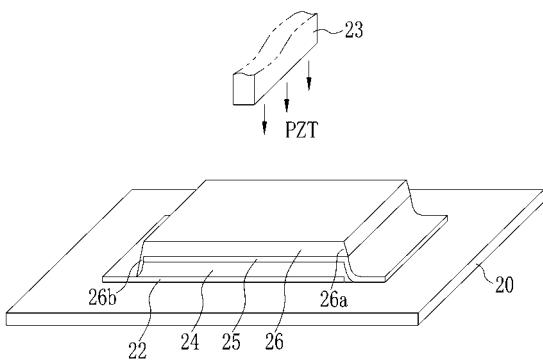

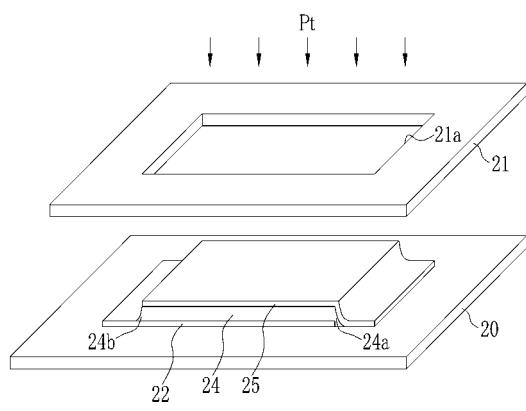

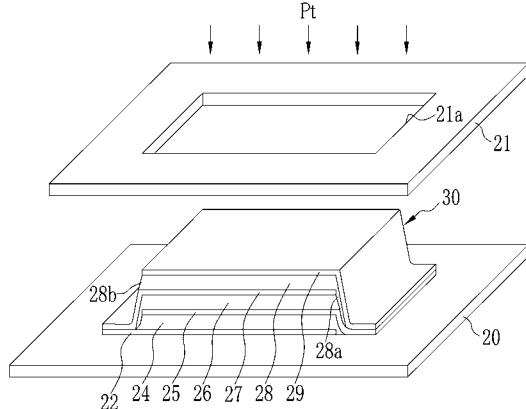

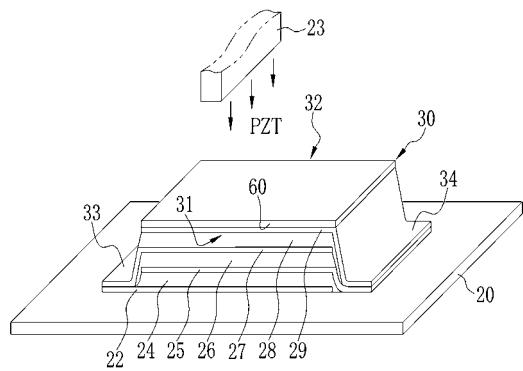

次に、1次元超音波トランスデューサ2の製造方法について、図2~図15を参照しながら説明する。図2において、まず、積層型圧電素子10を形成するためのベース部材としてシリコンなどからなる基板20を用意する。基板20上には、以下の説明で用いる座標を図示している。図3において、X方向に約4mm、Y方向に約45mmの矩形開口21aを有するマスク21を用いて白金(Pt)をスパッタリングし、基板20上のX=0~4mm, Y=0~25mmの領域に厚さ約3μmの電極層22を形成する。

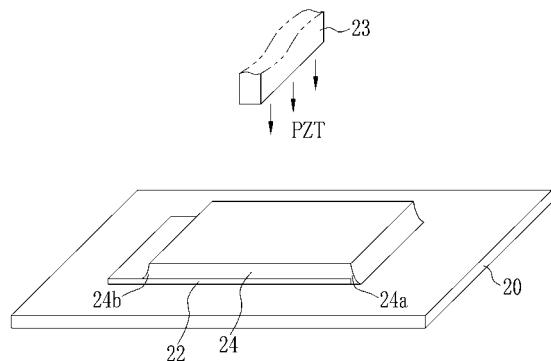

【0029】

図4において、X方向に4mmの長さを有するノズル23からエアロゾルデポジション(Aerosol Deposition: AD)法によってPZTの粉体(例えば、平均粒径0.3μmのPZT単結晶粉体)を基板20に向けて射出するとともに、ノズル23と基板20に対してY方向に移動させることによって、X=0~4mm, Y=5~25mmの領域に厚さ約90μmの圧電体層24を形成する。AD法とは、不図示のエアロゾル生成容器によって生成された粉体を高速に吹き付けて堆積させる周知の成膜方法であり、ガスデポジション、ジェットプリンティング、噴射堆積法とも称されている。

【0030】

ノズル23をY=5~25mmの領域で往復運動させて上記厚さ約90μmの圧電体層

10

20

30

40

50

24を形成すると、圧電体層24の両端部に、Y方向に例えば200μm程度の幅を有する裾状のテーパ部24a, 24bが形成される。このように圧電体層24を形成することによって、電極層22の右端部は、圧電体層24のテーパ部24aによって覆われる。電極層22の左端部は、圧電体層24によって覆われず露出している。なお、テーパ部24a, 24bのY方向の幅を調整するには、ノズル23の移動速度を制御すればよい。また、ノズル23を移動させずに固設し、基板20を可動ステージに積載して移動させるようにもよい。

【0031】

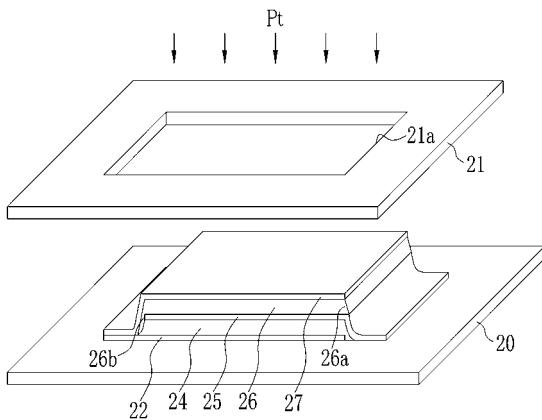

図5において、上記マスク21を用いて白金(Pt)をスパッタリングし、X=0~4mm, Y=5~30mmの領域に厚さ約3μmの電極層25を形成する。電極層25は、圧電体層24の上面およびテーパ部24aの表面を覆い、電極層22とは絶縁される。次いで、図6において、上記AD法を実施し、X=0~4mm, Y=5~25mmの領域に厚さ約90μmの圧電体層26を形成する。圧電体層26の両端部には、テーパ部26a, 26bが形成され、テーパ部26bが電極層25の左端部を覆う。

【0032】

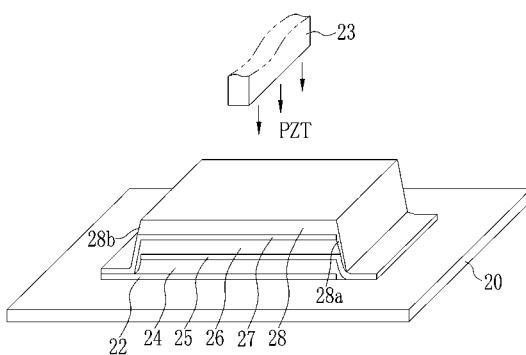

図7において、上記マスク21を用いて白金(Pt)をスパッタリングし、X=0~4mm, Y=0~25mmの領域に厚さ約3μmの電極層27を形成する。電極層27は、左端部(X=0~4mm, Y=0~5mmの領域)において電極層22と接続され、電極層25とは絶縁される。図8において、上記AD法を実施し、X=0~4mm, Y=5~25mmの領域に厚さ約90μmの圧電体層28を形成する。圧電体層28の両端部には、テーパ部28a, 28bが形成され、テーパ部28aが電極層27の右端部を覆う。

【0033】

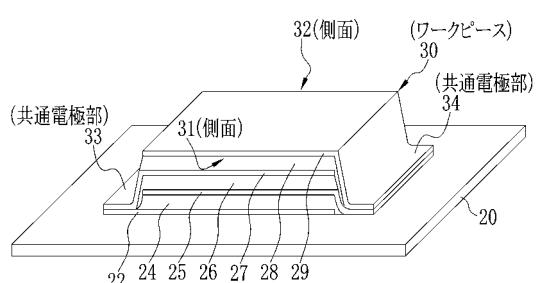

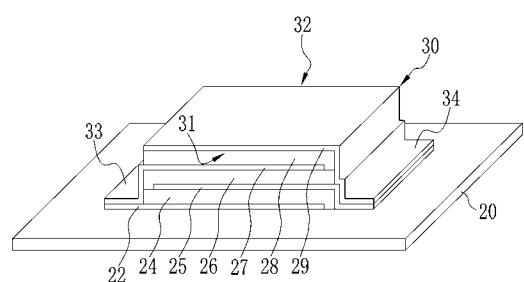

そして、図9において、上記マスク21を用いて白金(Pt)をスパッタリングし、X=0~4mm, Y=5~30mmの領域に厚さ約3μmの電極層29を形成する。電極層29は、右端部(X=0~4mm, Y=25~30mmの領域)において電極層25と接続され、電極層27とは絶縁される。このようにして、基板20上にワークピース(被加工物)30が形成される。

【0034】

ワークピース30は、スパッタリングとAD法とを繰り返し実施して形成したものであるため、これにより形成される側面(図中の前面および背面)は平坦ではない。このため、基板20に垂直でかつX=0mmを通る仮想平面、および基板20に垂直でかつX=4mmを通る仮想平面に沿ってワークピース30に対してダイシングを行い、図10に示すように、平坦な側面31, 32を形成し、電極層22, 25, 27, 29の端面を側面31, 32から露出させる。なお、ワークピース30において、電極層22および電極層27が共通に接続された部分を共通電極部33、電極層25および電極層29が共通に接続された部分を共通電極部34と称することとする。

【0035】

次いで、このワークピース30を絶縁オイル中などで150程度に加熱し、共通電極部33と共に電極部34との間に600V程度の電圧を印加することによって、圧電体層24, 26, 28に対してボーリング(分極反転)処理を実施する。これにより、圧電体層24, 26, 28の平坦部分の分極方向は上下方向に揃い、均一になる。

【0036】

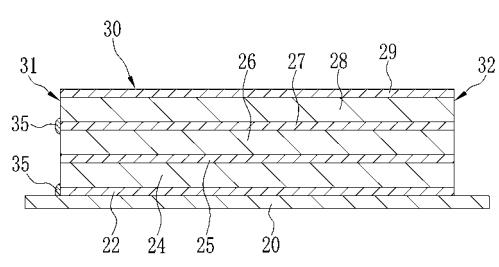

この後、ワークピース30の側面31を電着性を有する絶縁材料(アクリル系樹脂、フッ素系樹脂、ポリイミド系樹脂など樹脂、ガラスやアルミナ(Al<sub>2</sub>O<sub>3</sub>)など)を含む電着液に浸し、該電着液と共に電極部33との間に適度な電位を印加することにより、電気泳動によって、図11に示すように、側面31における電極層22, 27の露出端面およびその近傍に厚さ約10μmの絶縁膜35を形成する。図11は、基板20に垂直でかつY=15mmを通る仮想平面に沿うワークピース30の縦断面図である。

【0037】

次いで、ワークピース30の側面32を上記電着液中に浸し、該電着液と共に電極部3

10

20

30

40

50

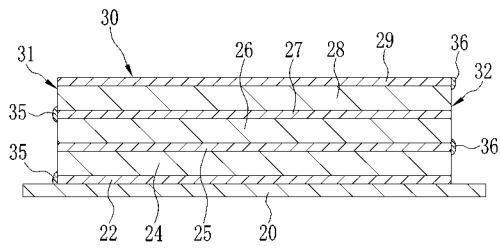

4との間に適度な電位を印加することにより、図12に示すように、側面32における電極層25, 29の露出端面およびその近傍に厚さ約10μmの絶縁膜36を形成する。なお、上記電着法に代えて、下記第2実施形態で示す電解メッキおよびその絶縁化による方法で絶縁膜35, 36を形成するようにしてもよい。

【0038】

次いで、無電解メッキ法を用いて、銀(Ag)、銅(Cu)、ニッケル(Ni)、金(Au)、クロム(Cr)などの金属で側面31, 32をメッキし、図13に示すように側面電極37, 38をそれぞれ形成する。側面電極37は、電極層25, 29に電気的に接続され、電極層22, 27とは絶縁膜35を介して絶縁されている。側面電極38は、電極層22, 27に電気的に接続され、電極層25, 29とは絶縁膜35を介して絶縁されている。

10

【0039】

この後、ワークピース30から基板20を、剥離、研磨、エッチングなどの方法によって分離する。図14において、基板20から分離されたワークピース30を可撓性を有するバッキング材4上に固着されたFPC基板3に接着する。詳しくは、FPC基板3には、Y方向に120μm程度のピッチで芯線(不図示)が配設されており、この芯線の露出部に銀(Ag)ペーストなどの導電性接着材を塗布し、芯線とワークピース30の電極層22とを接着させる。

【0040】

そして、図15に示すように、ダイサー(ブレードを用いたダイシング装置)を用いてワークピース30を、FPC基板3にY方向に配設された芯線の間ににおいてY方向に約30μmの幅でバッキング材4の上部に到るまでダイシングする(ダイシング方向X方向)。また、このダイシング時に、共通電極部33, 34およびテーパ部を切り落とす。これにより、図1に示した1次元超音波トランスデューサ2が作成される。

20

【0041】

なお、上記ポーリング処理は、ワークピース30が形成されてから側面電極37, 38を形成するまでの間に行えばよく、例えば絶縁膜35, 36を形成した直後に行うようにしてもよい。

【0042】

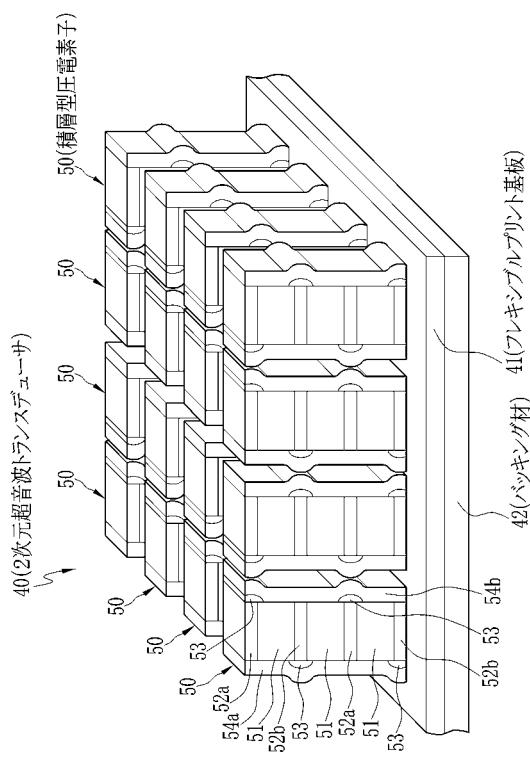

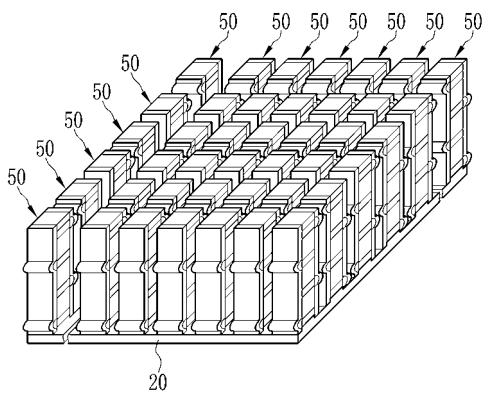

次に、図16は、本発明の第2実施形態に係わる積層型圧電素子50が2次元状に配列されてなる2次元超音波トランスデューサ40を示す。各積層型圧電素子50は、例えば、約100μm角の底面を有する柱状の構造体であり、FPC基板41上に固着されている。また、FPC基板41は、可撓性を有するバッキング材42上に固着されている。

30

【0043】

なお、バッキング材42を適宜の形状にすることによって、2次元超音波トランスデューサ40をいわゆるラジアル型やコンベックス型とすることができます。また、隣接する積層型圧電素子50間(溝部)にウレタンやエポキシ樹脂などの充填材(不図示)を充填し、さらに積層型圧電素子50全体を覆うように音響レンズ(不図示)を形成するようにしてもよい。

【0044】

積層型圧電素子50は、3つの圧電体層51と、各圧電体層51の上下に形成された電極層52a, 52bと、各電極層52a, 52bの1つの端面に形成された絶縁膜53と、対向する側面に形成された側面電極54a, 54bとから構成されている。電極層52aは、側面電極54aに接続されており、電極層52bは、側面電極54bに接続されている。なお、圧電体層の積層数は3層に限られず、適宜の数としてよく、例えば7層としてもよい。また、側面電極の形成部は、対向する2つの側面に限られず、異なる2つの面であればよい。

40

【0045】

なお、圧電体層51、電極層52a, 52b、絶縁膜53、側面電極54a, 54bの各材料は、上記第1実施形態と同様である。2次元超音波トランスデューサ40は、上記

50

第1実施形態の1次元超音波トランスデューサ2と同様に、超音波の送受信を行うことを可能とするものである。

【0046】

次に、2次元超音波トランスデューサ40の製造方法について、図17～図22を参照しながら説明する。まず、上記第1実施形態で説明した図2～図10の製造工程を実施し、図10に示すワークピース30を形成する。ただし、本第2実施形態では、図2に示す基板20上のX=0～11mm、Y=0～20mmの領域にワークピース30を形成する。圧電体層24, 26, 28の平坦部は、Y=5～15mmの領域に形成され、共通電極部33はY=0～5mmの領域内、共通電極部34はY=15～20mmの領域内に形成される。

10

【0047】

図17において、上記AD法を実施し、電極層29上のX=0～15mm、Y=5～15mmの領域に膜厚数μmの保護膜60をPZTなどの材料で形成する。なお、AD法に代えて、蒸着法、スパッタ法、塗布法などを用いてもよく、保護膜60を有機ポリマーなどのレジスト材で形成するようにしてもよい。

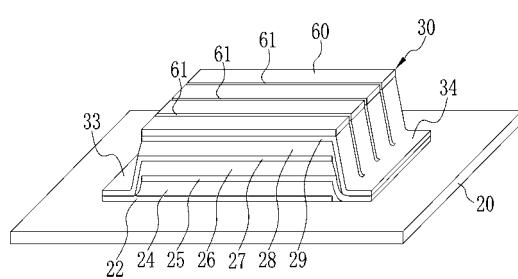

【0048】

図18において、ダイサーを用いてワークピース30をX方向に約300μmのピッチでダイシングし(ダイシング方向Y方向)、X方向に約50μmの幅を有する溝61を形成する。このダイシングの際には、Y=5～15mmの領域の圧電体層24, 26, 28および電極層22, 25, 27, 29を完全に切断するが、共通電極部33, 34は完全には切断しない。同図には、簡略化のために溝61を3本のみ図示しているが、実際には33本の溝61が形成される。

20

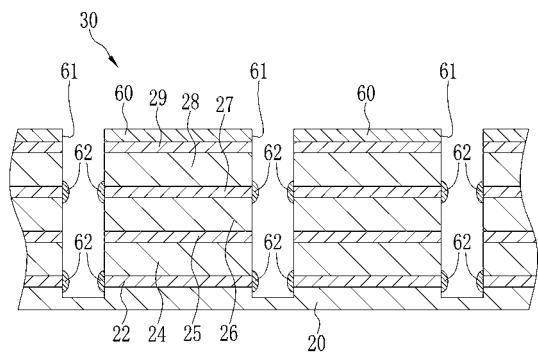

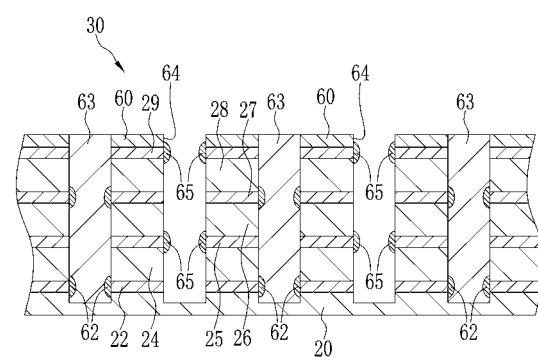

【0049】

この後、溝61が形成されたワークピース30の共通電極部33以外の部分を、ニッケル(Ni)イオンを含む電解メッキ液に浸し、該電解メッキ液と共に通電極部33との間に適度な電位を印加することにより、図19に示すように、溝61内の電極層22, 27の露出端面およびその近傍に厚さ約10μmのメッキ膜62を形成する。図19は、基板20に垂直でかつY=10mmを通る仮想平面に沿うワークピース30の縦断面図である。

【0050】

次いで、図20に示すように、有機ポリマーなどのレジスト材63を溝61に埋入する。また、隣接する2つの溝61の中間位置をY方向にダイシングし、同図に示すように溝61と平行な溝64を形成する。溝61の場合と同様に、このダイシングの際には、Y=5～15mmの領域の圧電体層24, 26, 28および電極層22, 25, 27, 29を完全に切断するが、共通電極部33, 34は完全には切断しない。

30

【0051】

この状態で、ワークピース30の共通電極部34以外の部分を上記電解メッキ液に浸し、該電解メッキ液と共に通電極部34との間に適度な電位を印加することにより、同図に示すように、溝64内の電極層25, 29の露出端面およびその近傍に厚さ約10μmのメッキ膜65を形成する。なお、上記電解メッキ液に使用するイオンは、ニッケル(Ni)イオンでなくてもよく、銅(Cu)、銀(Ag)、アルミニウム(Al)、チタン(Ti)などのイオンでもよい。

40

【0052】

この後、溝61に埋入したレジスト材63を除去し、ワークピース30を空气中で熱処理(例えば700で3時間)することにより、メッキ膜62, 65を酸化させ、メッキ膜62, 65を絶縁化する。なお、ニッケル(Ni)イオン以外の上記イオンを使用してメッキ膜62, 65を形成した場合には、空气中での熱酸化に加え、水蒸気中で熱酸化させることも好適である。また、アルミニウム(Al)を用いる場合には、陽極酸化法を用いてメッキ膜62, 65を絶縁化してもよい。また、酸化に代えて、窒化、硫化、フッ化などによってメッキ膜62, 65の絶縁化を行ってもよい。さらに、この電解メッキおよびその絶縁化による方法に代えて、上記第1実施形態で示した電着法を用いてもよい。

50

## 【0053】

次いで、このワークピース30を絶縁オイル中などで150程度に加熱し、共通電極部33と共に電極部34との間に600V程度の電圧を印加することによって、圧電体層24, 26, 28に対してポーリング(分極反転)処理を実施する。これにより、圧電体層24, 26, 28の平坦部分の分極方向は上下方向に揃い、均一になる。

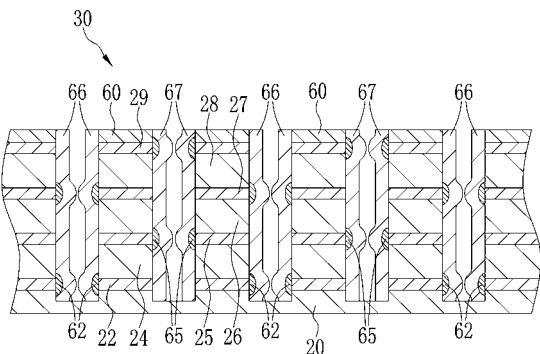

## 【0054】

この後、無電解メッキ法を用いて、銀(Ag)、銅(Cu)、ニッケル(Ni)、金(Au)、クロム(Cr)などの金属でワークピース30の表面をメッキし、保護膜60上に形成されるメッキ膜を除去する。これにより、図21に示すように、側面電極66, 67が形成される。側面電極66は、電極層25, 29に電気的に接続され、電極層22, 27とは絶縁化されたメッキ膜62を介して絶縁されている。側面電極67は、電極層22, 27に電気的に接続され、電極層25, 29とは絶縁化されたメッキ膜65を介して絶縁されている。

10

## 【0055】

次いで、ダイサーを用いてワークピース30を、Y方向に約150μmのピッチおよび約50μmの幅で65箇所ダイシングする(ダイシング方向X方向)。このダイシングの際には、X=0~11mmの領域の圧電体層24, 26, 28および電極層22, 25, 27, 29を完全に切断するが、基板20は完全には切断せず底部が繋がった状態にする。また、このダイシング時に、共通電極部33, 34およびテーパ部を切り落とす。これにより、図22に示すように、底面が約100μm角の柱状の積層型圧電素子50が2次元状に64×64個配列された状態で形成される。

20

## 【0056】

この後、隣接する積層型圧電素子50間(溝部)にウレタンやエポキシ樹脂などの充填材(不図示)を充填した上で、基板20を剥離、研磨、エッティングなどの方法によって除去する。そして、基板20が除去された積層型圧電素子50の2次元アレイを、可撓性を有するバックング材42上に固着されたFPC基板41に接着することで、図16に示した2次元超音波トランステューサ40が形成される。

## 【0057】

なお、上記ポーリング処理は、ワークピース30が形成されてから側面電極66, 67を形成するまでの間に行えばよく、例えば溝61, 64を形成する前のワークピース30を形成した直後に行うようにしてもよい。

30

## 【0058】

上記第1および第2実施形態においては、無電解メッキ法を用いて各側面電極を形成したが、無電解メッキ法に代えて、蒸着法、スパッタ法、塗布法などを用いて側面電極を形成してもよい。蒸着法またはスパッタ法に使用する材料としては、金(Au)、白金(Pt)、チタン(Ti)などが挙げられる。塗布法に使用する材料としては、銀(Ag)ペーストや導電性樹脂などが挙げられる。

## 【0059】

また、上記第1および第2実施形態においては、スパッタ法(スパッタリング)を用いて各電極層を形成したが、スパッタ法に代えて、蒸着法などを用いて電極層を形成してもよい。

40

## 【0060】

また、上記第1および第2実施形態においては、ダイサーを用いてワークピース30をダイシングしたが、ダイサーに代えて、サンドblastなどの方法を用いてもよい。

## 【0061】

また、上記第1および第2実施形態においては、ワークピース30内の圧電体層24, 26, 28の両端部をテーパ状にしたが、必ずしもこのようにする必要はなく、図23に示すようにテーパ部を形成せずに、圧電体層24, 26, 28の厚さを全体にわたってほぼ均一にするようにしてもよい。ワークピース30は、圧電体層と電極層が交互に積層され、電極層が一層おきに共通に接続されたものであればよい。

50

## 【図面の簡単な説明】

## 【0062】

【図1】本発明の第1実施形態に係わる1次元超音波トランスデューサの斜視図である。

【図2】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図3】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図4】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図5】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図6】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図7】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図8】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図9】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図10】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図11】1次元超音波トランスデューサの製造工程を示す縦断面図である。

【図12】1次元超音波トランスデューサの製造工程を示す縦断面図である。

【図13】1次元超音波トランスデューサの製造工程を示す縦断面図である。

【図14】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図15】1次元超音波トランスデューサの製造工程を示す斜視図である。

【図16】本発明の第2実施形態に係わる2次元超音波トランスデューサの斜視図である。

。

【図17】2次元超音波トランスデューサの製造工程を示す斜視図である。

【図18】2次元超音波トランスデューサの製造工程を示す斜視図である。

【図19】2次元超音波トランスデューサの製造工程を示す縦断面図である。

【図20】2次元超音波トランスデューサの製造工程を示す縦断面図である。

【図21】2次元超音波トランスデューサの製造工程を示す縦断面図である。

【図22】2次元超音波トランスデューサの製造工程を示す斜視図である。

【図23】ワーカピースの変形例を示す斜視図である。

【図24】従来の積層型圧電素子の構造を示す縦断面図である。

## 【符号の説明】

## 【0063】

2 1次元超音波トランスデューサ

30

10 積層型圧電素子

11 圧電体層

12a, 12b 電極層

13 絶縁膜

14a, 14b 側面電極

20 基板

21 マスク

22, 25, 27, 29 電極層

23 ノズル

24, 26, 28 圧電体層

40

30 ワーカピース

33, 34 共通電極部

35, 36 絶縁膜

37, 38 側面電極

40 2次元超音波トランスデューサ

50 積層型圧電素子

51 圧電体層

52a, 52b 電極層

53 絶縁膜

54a, 54b 側面電極

50

6 1 , 6 4 溝

6 2 , 6 5 メッキ膜

6 3 レジスト材

6 6 , 6 7 側面電極

【 四 1 】

【 図 2 】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【 図 1 4 】

### 【図13】

( 図 15 )

【図16】

### 【図17】

【図18】

【図19】

### 【図21】

【図20】

【図22】

### 【図23】

【図24】

---

フロントページの続き

(56)参考文献 特開平07-135347(JP,A)

特開2004-072013(JP,A)

特開平11-112260(JP,A)

特開平11-135850(JP,A)

特開2004-119934(JP,A)

特開2003-174209(JP,A)

特開平09-023030(JP,A)

特開2003-282988(JP,A)

特開平02-164084(JP,A)

特開平03-012974(JP,A)

特開2003-069372(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 41/22

H01L 41/083

H01L 41/18

H01L 41/24

H04R 17/00