(19)

REPUBLIK

ÖSTERREICH

Patentamt

(10) Nummer:

AT 407 681 B

(12)

# PATENTSCHRIFT

(21) Anmeldenummer: 819/95

(22) Anmeldetag: 15.05.1995

(42) Beginn der Patentdauer: 15.09.2000

(45) Ausgabetag: 25.05.2001

(51) Int. Cl.<sup>7</sup>: H03K 17/08

(56) Entgegenhaltungen:

DE 3741713A1 DE 3905645A1 DE 4012382A1

DE 4237119C1 EP 0327881A1 EP 0369048A1

EP 0384937A1

(73) Patentinhaber:

ELIN EBG TRACTION GMBH

A-1141 WIEN (AT).

(72) Erfinder:

NASCIMENTO-SINGER JAIR SEBASTIAO DO

DIPL.ING.

DORMITZ (DE).

SCHAMBOCK HANS DIPL.ING.

OBERSDORF, NIEDERÖSTERREICH (AT).

## (54) VERFAHREN ZUR ABSCHALTUNG EINES SPANNUNGSGESTEUERTEN HALBLEITERS

AT 407 681 B

(57) Bei einem Verfahren zur Abschaltung eines spannungsgesteuerten Halbleiters, vorzugsweise eines IGBTs (insulated gate bipolar transistor) wird beim Erreichen bzw. Überschreiten eines einstellbaren Schwellwertes der Halbleiterdurchlaßspannung, entspricht im allgemeinen einem Laststromgrenzwert, der Abschaltwiderstand im Steuerkreis während der Abschaltphase erhöht.

Eine entsprechende Anordnung besteht aus einer Schaltung zur Erfassung der Durchlaßspannung für den Halbleiter die am Kollektor bzw. Drain des Halbleiters angeschlossen ist. An die ist ein aus zwei Widerständen bestehender Spannungsteiler gegen den Emitter bzw. Source angeschlossen. An den Verbindungspunkt der beiden Widerstände ist ein Komparator mit einstellbarem Schwellwert angeschlossen, dem ein UND-Glied nachgeschaltet ist, dessen zweiter Eingang mit einer monostabilen Kippstufe verbunden ist, der ein Inverter vorgeschaltet ist, dem die Ausschaltflanke des Ansteuersignales für den Halbleiter zuführbar ist. Dem UND-Glied ist eine weitere monostabile Kippstufe nachgeschaltet, die einen Transistor ansteuert, der einen Kollektor- und einen Kollektor-Emitterwiderstand

aufweist, die zwischen Basis bzw. Gate und Emitter bzw. Source angeordnet sind. Während der Abschaltphase des Halbleiters, sofern die Halbleiterdurchlaßspannung den Schwellwert des Komparators überschreitet, sperrt der Transistor.

Fig. 1

Die Erfindung betrifft ein Verfahren zur Abschaltung eines spannungsgesteuerten Halbleiter-Schalters, vorzugsweise eines IGBTs (insulated gate bipolar transistor).

Die heute hauptsächlich in der Leistungselektronik für Pulsstromrichter verwendeten IGBTs sind bipolare Transistoren mit integrierter FET-Eingangsstufe, welche nur eine geringe Ansteuerleistung benötigen. Durch ihre Anwendung bei Stromrichtern sind Schaltfrequenzen außerhalb des Hörbereiches möglich. Die technologischen Grenzen für hohe Sperrspannungen liegen bei den IGBTs ebenfalls sehr günstig. Die IGBTs gehören somit zu jener Gruppe schneller neuer Halbleiterschalter, die über den Steueranschluß (Gate) spannungsgesteuert, in Stromrichterschaltungen eingesetzt werden.

Es ist bekannt, die Bremsung der Stromübernahme während des Kommutierungsvorganges (IGBT - Freilaufdiode) bei Stromrichterschaltungen mit IGBTs über den Gateanschluß durch einen vergrößerten Gatewiderstand zu realisieren. Insbesondere erfordert das Abschalten von hohen IGBT-Strömen relativ hohe Gate-Abschaltwiderstände um die unvermeidlichen Induktionsspannungsspitzen begrenzt zu halten. Die aus obigen Gründen erwünschte Erhöhung der Gatewiderstände führt zu einem unerwünschten Anstieg der Schaltzeiten inklusive Schaltverzögerungen und zu einer Zunahme der Schaltverluste. Es muß daher immer in bezug auf den Gatewiderstand ein unbefriedigender Kompromiß eingegangen werden.

Die Aufgabe der Erfindung besteht nun darin, ein Verfahren zu schaffen, mit dem die obigen Nachteile vermieden werden.

Die Aufgabe wird durch die Erfindung gelöst, welche dadurch gekennzeichnet ist, daß beim Erreichen bzw. Überschreiten eines einstellbaren Schwellwertes der Halbleiterdurchlaßspannung, der im allgemeinen einem Laststromgrenzwert entspricht, der Abschaltwiderstand im Steuerkreis während der Abschaltphase erhöht wird und daß die bezogen auf den Laststrom des Halbleiters temperaturunabhängige Steuerung der Durchlaßspannung kompensiert wird. Dadurch ist erstmals ein selektives Abschalten der Halbleiterschalter bei Stromrichterschaltungen möglich, bei welchem überdies der bei IGBT's übliche positive Temperaturkoeffizient der Durchlaßspannung berücksichtigt ist, der sich in einem meist unzulässig hohen Streubereich des zugehörigen Stromes auswirkt.

Bei einer erfindungsgemäßen Anordnung zur Durchführung des Verfahrens daß eine Schaltung zur Erfassung der Durchlaßspannung für den Halbleiterschalter am Kollektor bzw. Drain des Halbleiterschalters angeschlossen ist, an die ein aus zwei Widerständen bestehender Spannungsteiler gegen den Emitter bzw. Source angeschlossen ist, und daß an den Verbindungspunkt der beiden Widerstände ein Komparator mit einstellbarem Schwellwert angeschlossen ist, dem ein UND-Glied nachgeschaltet ist, dessen zweiter Eingang mit einer monostabilen Kippstufe verbunden ist, der ein Inverter vorgeschaltet ist, dem die Ausschaltflanke des Ansteuersignales für den Halbleiterschalter zuführbar ist, und daß dem UND-Glied eine weitere monostabile Kippstufe nachgeschaltet ist, die einen Transistor ansteuert, der einen Kollektor- und einen Kollektor-Emitterwiderstand aufweist, und daß die Serienschaltung dieser beiden Widerstände mit dem Basis- bzw. Gateanschluß des Halbleiterschalters verbunden und über einen weiteren Halbleiterschalter an einer negativen Spannung angeschlossen ist, und daß während der Abschaltphase des Halbleiterschalters, soferne die Halbleiterdurchlaßspannung den Schwellwert des Komparators überschreitet, der Transistor sperrt. Dies ist eine mögliche Realisierung des erfindungsgemäßen Verfahrens.

Nach einer Ausgestaltung besteht der Komparator aus einem Operationsverstärker mit Eingangs- und Gegenkopplungswiderstand, wobei an den invertierenden Eingang des Operationsverstärkers der Schwellwert für das Überschreiten der Durchlaßspannung des Halbleiterschalters gelangt. Dadurch kann auf einfachste Weise, u.zw. durch Vorgeben der Spannung am invertierenden Eingang des Operationsverstärkers, der Schwellwert eingestellt werden.

Eine weitere Ausgestaltung besteht darin, daß der mit dem Emitter bzw. Source des Halbleiterschalters verbundene Widerstand des Spannungsteilers einen negativen Temperaturkoeffizienten aufweist. Dadurch kann die Temperaturabhängigkeit des Halbleiterschalters ausreichend gemindert werden.

Von Vorteil ist, daß anstelle des Spannungsteilers der Eingangswiderstand des Komparators mit dem Ausgang der Schaltung zur Erfassung der Durchlaßspannung verbunden ist, und daß anstelle des Schwellwertes an den invertierenden Eingang des Operationsverstärkers einerseits über einen Widerstand eine positive Versorgungsspannung gelangt, und andererseits dieser Eingang über einen Widerstand mit positivem Temperaturkoeffizienten mit Nullpotential verbunden ist.

Nachfolgend wird die Erfindung noch anhand der Zeichnungen näher erläutert.

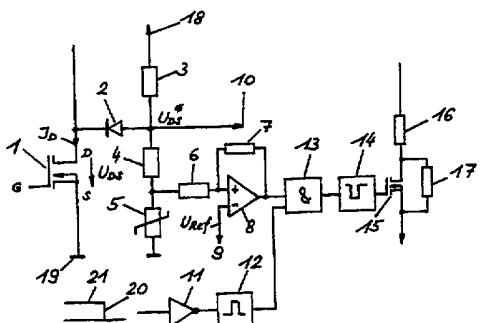

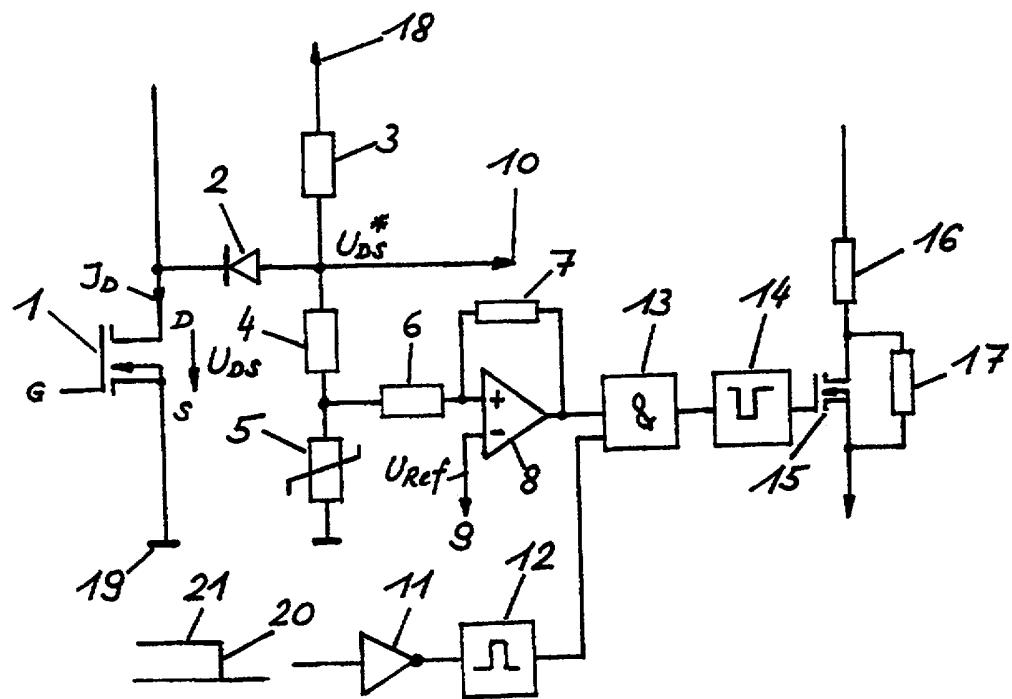

Die Fig. 1 zeigt eine mögliche Anordnung zur Durchführung des Verfahrens und in Fig. 2 sind Spannung und Strom am Halbleiterschalter, sowie Signale in der Anordnung während der Abschaltphase des Halbleiterschalters dargestellt.

Bei Fig. 1 ist der Drain-Anschluß D des Halbleiterschalters 1, der ein IGBT ist, welcher z.B. ein Halbleiterschalter eines Zweipunkt-Wechselrichterschaltpoles sein kann, mit der Katode einer Diode 2 verbunden. Der Halbleiterschalter 1, bei dem hier der Source-Anschluß S an Nullpotential 19 liegt, wird über den Gate-Anschluß G angesteuert. Die Anode der Diode 2 ist mit einem Widerstand 3, der von einer positiven Spannung, angelegt bei 18, gespeist wird, mit einem Spannungssteiler 4, 5 und einer bei 10 angeschlossenen Schaltung, welche die Höhe der Durchlaßspannung erfaßt, verbunden. Der aus den beiden Widerständen 4, 5 bestehende Spannungsteiler liegt zwischen der Anode der Diode 2 und Nullpotential 19, wobei der mit Nullpotential 19 verbundene Widerstand 5 temperaturabhängig ist und einen negativen Temperaturkoeffizienten aufweist. Zwischen den beiden Widerständen 4, 5 des Spannungsteilers ist ein Komparator angeschlossen, der aus einem Operationsverstärker 8 mit Eingangs- 6 und Gegenkopplungswiderstand 7 besteht. Am invertierenden Eingang 9 des Operationsverstärkers 8 liegt ein Schwellwert  $U_{Ref}$  an. Dem Komparator 6, 7, 8 ist ein UND-Glied 13 nachgeschaltet, bei dem der zweite Eingang mit einer monostabilen Kippstufe 12 verbunden ist, die eingeschaltig einen Inverter 11 aufweist, dem die Ausschaltflanke 20 des Ansteuersignales 21 für den Halbleiterschalter 1 zugeführt wird. Dem UND-Glied 13 ist eine weitere monostabile Kippstufe 14 nachgeschaltet, die einen Transistor 15 ansteuert, der einen Kollektor- 16 und einen Kollektor-Emitterwiderstand 17 aufweist. Die beiden Widerstände 16, 17 sind zwischen dem Gate- G des Halbleiterschalters 1 und über einen Halbleiterschalter an eine negative Spannung geschaltet, deren Bezug der Source Anschluß S des Halbleiterschalters 1 ist. Im Normalfall ist der Transistor 15 immer leitend, wodurch für den Gatewiderstand des IGBTs 1 nur der Widerstand 16 maßgebend ist. Der Transistor 15 sperrt nur während der Abschaltphase des IGBTs 1, soferne die Halbleiterdurchlaßspannung  $U_{DS}$  den Schwellwert  $U_{Ref}$  des Komparators 6, 7, 8 überschreitet.

Bei der monostabilen Kippstufe 12 ist eine metastabile Zeit von 0,5  $\mu$ s und bei der Kippstufe 14 eine Zeit von 4  $\mu$ s eingestellt.

Im regulären Fall bei durchgeschaltetem IGBT 1 ist die Spannung  $U_{DS}^*$  an der Anode der Diode 2 die Durchlaßspannung  $U_{DS}$  des IGBTs 1 zusätzlich des Spannungsabfalles an der Diode 2. Soferne im durchgeschalteten Zustand des IGBTs 1 die Durchlaßspannung  $U_{DS}$  durch einen zu großen Laststrom die positive Spannung an 18 erreicht, nimmt die Spannung  $U_{DS}^*$  diese positive Spannung an. Dadurch kippt abhängig vom eingestellten Schwellwert  $U_{Ref}$  der Komparator 6, 7, 8 am Ausgang. Soferne die bei 10 angeschlossene Durchlaßspannungsüberwachung für den IGBT 1 nicht sofort angesprochen hat, wird bei der nächsten Ausschaltflanke 20 für den IGBT 1 die monostabile Kippstufe 12 aktiviert und das UND-Glied 13 ändert am Ausgang den Zustand. Dadurch wird über die monostabile Kippstufe 14 der Transistor 15 während der Abschaltphase des IGBTs 1 für eine Zeit von 4  $\mu$ s gesperrt, wodurch für den Gatewiderstand des IGBTs 1 die Widerstände 16, 17 wirksam sind, d.h. er ist in dieser Zeit sehr hoch.

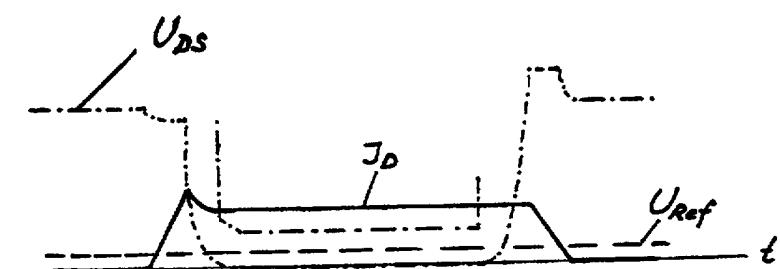

In Fig. 2 ist der Verlauf der Durchlaßspannung  $U_{DS}$ , des Drainstromes  $I_d$  und des Schwellwertes  $U_{Ref}$  des Komparators 6, 7, 8 beim Ein- (links) und Ausschalten (rechts) des Halbleiterschalters 1 dargestellt. Die Durchlaßspannung  $U_{DS}$  liegt hier zwar über dem Schwellwert  $U_{Ref}$ , aber noch unter der Ansprechschwelle einer Durchlaßspannungsüberwachung, wodurch der IGBT 1 nur mit erhöhtem Gatewiderstand abgeschaltet wird.

#### PATENTANSPRÜCHE:

1. Verfahren zur Abschaltung eines spannungsgesteuerten Halbleiterschalters, vorzugsweise eines IGBTs (insulated gate bipolar transistor), dadurch gekennzeichnet, daß beim Erreichen bzw. Überschreiten eines einstellbaren Schwellwertes ( $U_{Ref}$ ) der Halbleiterdurchlaßspannung ( $U_{DS}$ ), der im allgemeinen einem Laststromgrenzwert entspricht, der Abschaltwiderstand (16, 17) im Steuerkreis während der Abschaltphase erhöht wird, und daß die bezogen auf den Laststrom ( $I_d$ ) des Halbleiterschalters (1) temperaturabhängige

- 5 Streuung der Durchlaßspannung ( $U_{DS}$ ) kompensiert wird.

- 10 2. Anordnung zur Durchführung des Verfahrens nach Anspruch 1, **dadurch gekennzeichnet**, daß eine Schaltung zur Erfassung der Durchlaßspannung ( $U_{DS}$ ) für den Halbleiterschalter (1) am Kollektor- bzw. Drainanschluß (D) des Halbleiterschalters (1) angeschlossen ist, an die ein aus zwei Widerständen (4, 5) bestehender Spannungsteiler gegen den Emitter- bzw. Sourceanschluß (S) angeschlossen ist, und daß an den Verbindungspunkt der beiden Widerstände (4, 5) ein Komparator (6, 7, 8) mit einstellbarem Schwellwert ( $U_{Ref}$ ) angeschlossen ist, dem ein UND-Glied (13) nachgeschaltet ist, dessen zweiter Eingang mit dem Ausgang einer monostabilen Kippstufe (12) verbunden ist, der ein Inverter (11) vorgeschaltet ist, dem die Ausschaltflanke (20) des Ansteuersignales (21) für den Halbleiterschalter (1) zugeführt wird, und daß dem UND-Glied (13) eine weitere monostabile Kippstufe (14) nachgeschaltet ist, die einen Transistor (15) ansteuert, der einen Kollektor (16) und einen Kollektor-Emitterwiderstand (17) aufweist, und daß die Serienschaltung dieser beiden Widerstände (16, 17) mit dem Basis- bzw. Gateanschluß (G) des Halbleiterschalters (1) verbunden und über einen weiteren Halbleiterschalter an einer negativen Spannung angeschlossen ist, wobei während der durch die Ausschaltflanke (20) des Ansteuersignales (21) eingeleiteten Abschaltphase des Halbleiterschalters (1), soferne die Halbleiterdurchlaßspannung ( $U_{DS}$ ) den Schwellwert ( $U_{Ref}$ ) des Komparators (6, 7, 8) überschreitet, der Transistor (15) für eine durch die monostabile Kippstufe (14) bestimmte Zeit sperrt.

- 15 3. Anordnung nach Anspruch 2, **dadurch gekennzeichnet**, daß der mit dem Emitter- bzw. Sourceanschluß (S) des Halbleiterschalters (1) verbundene Widerstand (5) des Spannungsteilers (4, 5) einen negativen Temperaturkoeffizienten aufweist.

- 20 4. Anordnung nach Anspruch 2, **dadurch gekennzeichnet**, daß anstelle des Spannungsteilers (4, 5) der Eingangswiderstand (6) des Komparators (6, 7, 8) mit dem Ausgang der Schaltung zur Erfassung der Durchlaßspannung ( $U_{DS}$ ) verbunden ist, und daß anstelle des Schwellwertes ( $U_{Ref}$ ) an den invertierenden Eingang des Operationsverstärkers (8) einerseits über einen Widerstand eine positive Versorgungsspannung gelangt, und andererseits dieser Eingang über einen Widerstand mit positivem Temperaturkoeffizienten mit Nullpotential (19) verbunden ist.

## HIEZU 1 BLATT ZEICHNUNGEN

35

40

45

50

55

Fig. 1

Fig. 2