# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51)Int. Cl.

HO1L 27/115 (2006.01) HO1L 21/8247 (2006.01)

(21) 출원번호

10-2006-0097666

(22) 출원일자

2006년10월04일

심사청구일자 없음

(11) 공개번호

10-2008-0031594

(43) 공개일자

2008년04월10일

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

신상민

서울 송파구 잠실본동 199-3 백옥빌라 202호

설광수

경기 수원시 영통구 영통동 신나무실5단지아파트 522 - 1503

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 12 항

## (54) 전하 트랩형 메모리 소자

## (57) 요 약

기판 상에 형성된 터널 절연막; 및 이 터널 절연막 상에 형성되고, 전이금속이 도핑된 고유전율 절연막으로 된 전하 트랩층;을 포함하며, 터널 절연막이 전하 트랩층의 금속과 반응하거나 이 금속이 기판쪽으로 확산되는 것을 방지하도록 형성된 것을 특징으로 하는 전하 트랩형 메모리 소자가 개시되어 있다.

## **대표도** - 도1

## (72) 발명자

## 박상진

경기 용인시 기흥구 영덕동 대명레이크빌아파트 107-1701

## 성정헌

경기 용인시 기흥구 보정동 동아솔레시티아파트 120-1501

## 최상무

경기 용인시 기흥구 농서동 삼성종합기술원 기숙사 C-206

## 특허청구의 범위

#### 청구항 1

기판 상에 형성된 터널 절연막; 및

상기 터널 절연막 상에 형성되고, 전이금속이 도핑된 고유전율 절연막으로 된 전하 트랩층;을 포함하며,

상기 터널 절연막은 상기 전하 트랩층의 금속과 반응하거나 이 금속이 상기 기판쪽으로 확산되는 것을 방지하도 록 형성된 것을 특징으로 하는 전하 트랩형 메모리 소자.

#### 청구항 2

제1항에 있어서, 상기 고유전율 절연막은,  $SiO_2$ ,  $HfO_2$ ,  $ZrO_2$ ,  $Si_3N_4$ ,  $Al_2O_3$ , HfSiON, HfON 및 HfAlO을 포함하는 그룹으로부터 선택된 어느 하나로 이루어진 것을 특징으로 하는 전하 트랩형 메모리 소자.

### 청구항 3

제2항에 있어서, 상기 전이금속은 d-오비탈에 원자가 전자를 가진 금속인 것을 특징으로 하는 전하 트랩형 메모리 소자.

## 청구항 4

제1항에 있어서, 상기 전이금속은 d-오비탈에 원자가 전자를 가진 금속인 것을 특징으로 하는 전하 트랩형 메모리 소자.

## 청구항 5

제4항에 있어서, 상기 고유전율 절연막은  $HfO_2$ 막이고, 상기 고유전율 절연막내에 도핑된 전이금속은, Ta, V, Ru 및 Nb를 포함하는 그룹으로부터 선택된 적어도 하나 이상인 것을 특징으로 하는 전하 트랩형 메모리 소자.

#### 청구항 6

제4항에 있어서, 상기 고유전율 절연막은  $Al_2O_3$ 막이고, 상기 고유전율 절연막 내에 도핑된 전이금속은 W, Ru, Mo, Ni, Nb, V 및 Ti를 포함하는 그룹으로부터 선택된 적어도 하나 이상인 것을 특징으로 하는 전하 트랩형 메모리 소자.

## 청구항 7

제1항에 있어서, 상기 전이금속은 0.01~15%(atomic %) 도핑된 것을 특징으로 하는 전하 트랩형 메모리 소자.

## 청구항 8

제1항에 있어서, 상기 전이금속은 상기 유전막 내에 전자 트랩과 정공 트랩을 동시에 형성하도록 적어도 두 종 류 이상 도핑된 것을 특징으로 하는 전하 트랩형 메모리 소자.

## 청구항 9

제1항 내지 제8항 중 어느 한 항에 있어서, 상기 터널 절연막은 실리콘 질화막으로 이루어진 것을 특징으로 하는 전하 트랩형 메모리 소자.

## 청구항 10

제9항에 있어서, 상기 전하 트랩층 상에 형성된 블록킹 절연막; 및

상기 블록킹 절연막 상에 형성된 게이트 전극;을 더 포함하는 것을 특징으로 하는 전하 트랩형 메모리 소자.

#### 청구항 11

제1항 내지 제8항 중 어느 한 항에 있어서, 상기 터널 절연막은 실리콘 질화막 및 실리콘 산화막의 이중층 구조로 이루어지고.

상기 기판 상에, 실리콘 산화막, 실리콘 질화막 및 전하 트랩층 순서로 적충된 것을 특징으로 하는 전하 트랩형 메모리 소자.

#### 청구항 12

제11항에 있어서, 상기 전하 트랩층 상에 형성된 블록킹 절연막; 및

상기 블록킹 절연막 상에 형성된 게이트 전극;을 더 포함하는 것을 특징으로 하는 전하 트랩형 메모리 소자.

### 명세서

### 발명의 상세한 설명

## 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

- <13> 본 발명은 반도체 메모리 소자에 관한 것으로, 보다 상세하게는 전하 트랩형 메모리 소자에 관한 것이다.

- <14> 반도체 메모리 장치 중 비휘발성 메모리 장치는 전원 공급이 차단되더라도 저장된 데이터가 소멸되지 않고 보존되는 저장장치이다.

- <15> 비휘발성 반도체 메모리 장치를 구성하는 기본 요소인 메모리 셀의 구성은 비휘발성 반도체 메모리 장치가 사용되는 분야에 따라 달라지게 된다.

- <16> 현재 널리 사용되고 있는 고용량 비휘발성 반도체 메모리 장치로서, NAND(not and)형 플래시 반도체 메모리 장치의 경우, 그 트랜지스터의 게이트는 전하(charge)가 저장되는, 즉 데이터가 저장되는 플로팅 게이트(floating gate)와 이를 제어하는 컨트롤 게이트(control gate)가 순차적으로 적충된 구조를 갖는다.

- <17> 이러한 플래시 반도체 메모리 장치에 있어서, 해마다 증가하고 있는 메모리 용량의 확대 요구를 충족시키기 위해서, 메모리 셀 크기는 급속도로 축소되고 있다. 또한, 셀 크기의 축소에 맞추어, 플로팅 게이트의 수직방향의 높이를 효과적으로 줄여 나가는 것이 요구되고 있다.

- <18> 메모리 셀의 수직방향의 높이를 효과적으로 줄이는 동시에, 메모리 셀이 가지는 메모리 특성, 예를 들어, 누설 전류에 의해 저장된 데이터를 장시간 온전하게 유지하는 특성인 리텐션(retention) 특성을 유지하기 위하여, 전 하를 저장하는 수단으로서, 플로팅 게이트가 아닌 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)을 사용하여 구성된 SONOS(Silicon-Oxide-Nitride-Oxide-Semiconductor)나 MONOS(Metal-Oxide- Nitride-Oxide-Semiconductor) 메모리 소자로 대 표되는 MOIOS(metal-oxide- insulator-oxide-semiconductor)구조를 갖는 반도체 메모리 장치가 제안되었고, 이 에 대한 활발한 연구가 진행되고 있다. 여기서, SONOS는 컨트롤 게이트 물질로 실리콘을 사용하고, MONOS는 컨 트롤 게이트 물질로 금속을 사용한다는 점에서 차이가 있다.

- <19> MOIOS 메모리 소자는 전하를 저장하는 수단으로서 플로팅 게이트 대신에 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)과 같은 전하 트랩 층(charge trap layer)을 사용한다. 즉, MOIOS 메모리 소자는 플래시 반도체 메모리 장치의 메모리 셀의 구성에서 기판과 컨트롤 게이트 사이의 적충물(플로팅 게이트와 그 상하에 적충된 절연충들로 구성된 적충물)을 산화막(Oxide), 질화막(Nitride) 및 산화막(Oxide)이 순차적으로 적충된 적충물(ONO)로 대체한 것으로, 상기 질화막에 전하가 트랩됨에 따라 문턱전압(threshold voltage)이 이동(shift)되는 특성을 이용하는 메모리 소자이다.

- <20> SONOS 메모리 소자에 대한 보다 자세한 내용은 Technical Digest of International Electron Device Meeting(IEDM 2002, December), 927쪽-930쪽에 C.T. Swift외 다수의 이름으로 실린 "An Embedded 90nm SONOS Nonvolatile Memory Utilizing Hot Electron Programming and Uniform Tunnel Erase"에 기재되어 있다.

- <21> SONOS형 메모리 소자의 기본 구조는 다음과 같다. 소오스 및 드레인 영역 사이의 반도체 기판 상에, 즉 채널 영역상에 양단이 소오스 및 드레인 영역과 접촉되도록 터널 절연막으로서 제1실리콘 산화막(SiO<sub>2</sub>)이 형성되어 있다. 제1실리콘 산화막은 전하의 터널링을 위한 막이다. 제1실리콘 산화막상에 전합 트랩층으로서 실리콘 질화막(Si<sub>2</sub>N<sub>4</sub>)이 형성되어 있다. 질화막은 실질적으로 데이터가 저장되는 물질막으로써, 제1실리콘 산화막을 터널링한 전하가 트랩된다. 이러한 질화막상에 상기 전하가 질화막을 통과하여 위쪽으로 이동되는 것을 차단하기 위한 블록킹 절연막으로서 제2실리콘 산화막이 형성되어 있다. 제2실리콘 산화막상에는 게이트 전극이 형성되어

있다.

- <22> 그러나, 이러한 일반적인 구조의 SONOS형 메모리 소자는 실리콘 질화막과 실리콘 산화막들의 유전율이 낮고, 실리콘 질화막 내에 트랩 사이트(trap site) 밀도가 충분치 못하여, 동작 전압이 높고, 데이터를 기록하는 속도 (프로그램 속도)와, 수직, 수평 방향의 전하 리텐션(retension) 시간이 원하는 만큼 충분치 못하다는 문제가 있다

- <23> 최근에는, 상기 블로킹 절연막으로써 실리콘 산화막 대신, 알루미늄 산화막(Al<sub>2</sub>O<sub>3</sub>)을 사용함으로써 상기 실리콘 산화막을 사용하였을 때보다 프로그램 속도 및 리텐션 특성이 개선되었다는 사실이 보고된 바 있다.

- <24> 상기 보고에 대한 보다 자세한 내용은 Extended Abstract of 2002 International Conf. on Solid State Device and Materials, Nagoya, Japan, Sept. 2002, 162쪽-163쪽에 C. Lee외 다수의 이름으로 실린 "Novel Structure of SiO<sub>2</sub>/SiN/High-k dielectric, Al<sub>2</sub>O<sub>3</sub> for SONOS type flash memory"에 기재되어 있다.

- <25> 그러나 알루미늄 산화막 재질의 블로킹 절연막이 실리콘 질화막으로부터 전하가 빠져나가는 것을 어느 정도 억제해 줄 수는 있지만, 실리콘 질화막 자체 내의 트랩 사이트 밀도는 여전히 충분치 못하기 때문에, 알루미늄 산화막 사용에 따른 리텐션 특성 개선 정도는 미미한 수준에 불과하다.

## 발명이 이루고자 하는 기술적 과제

<26> 본 발명은 상기한 바와 같은 종래의 문제점을 개선하기 위해 안출된 것으로, 전하 트랩층 물질의 밴드갭 내에 분명히 정의된 안정된 전하 트랩을 만들고, 여기에 전하를 트랩하여 종래의 SONOS형 메모리 소자보다 리텐션 특성이 우수한 전하 트랩형 메모리 소자를 제공하는데 그 목적이 있다.

## 발명의 구성 및 작용

- <27> 상기 목적을 달성하기 위한 본 발명에 따른 전하 트랩형 메모리 소자는 기판 상에 형성된 터널 절연막; 및 상기 터널 절연막 상에 형성되고, 전이금속이 도핑된 고유전율 절연막으로 된 전하 트랩층;을 포함하며, 상기 터널 절연막은 상기 전하 트랩층의 금속과 반응하거나 이 금속이 상기 기판쪽으로 확산되는 것을 방지하도록 형성된 것을 특징으로 한다.

- <28> 상기 고유전율 절연막은, SiO<sub>2</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, HfSiON, HfON 및 HfAlO을 포함하는 그룹으로부터 선택 된 어느 하나로 이루어질 수 있다.

- <29> 상기 전이금속은 d-오비탈에 원자가 전자를 가진 금속인 것이 바람직하다.

- <30> 구체적으로, 상기 고유전율 절연막은 HfO2막이고, 상기 고유전율 절연막내에 도핑된 전이금속은, Ta, V, Ru 및 Nb를 포함하는 그룹으로부터 선택된 적어도 하나 이상일 수 있다.

- <31> 다른 예로서, 상기 고유전율 절연막은 Al<sub>2</sub>O<sub>3</sub>막이고, 상기 고유전율 절연막 내에 도핑된 전이금속은 W, Ru, Mo, Ni, Nb, V 및 Ti를 포함하는 그룹으로부터 선택된 적어도 하나 이상일 수 있다.

- <32> 상기 전이금속은 0.01~15%(atomic %) 도핑된 것이 바람직하다.

- <33> 상기 전이금속은 상기 유전막 내에 전자 트랩과 정공 트랩을 동시에 형성하도록 적어도 두 종류 이상 도핑된 것이 바람직하다.

- <34> 본 발명의 일 특징에 따르면, 상기 터널 절연막은 실리콘 질화막으로 이루어질 수 있다.

- <35> 본 발명의 다른 특징에 따르면, 상기 터널 절연막은 실리콘 질화막 및 실리콘 산화막의 이중층 구조로 이루어지고, 상기 기판 상에, 실리콘 산화막, 실리콘 질화막 및 전하 트랩층 순서로 적층될 수 있다.

- <36> 상기 전하 트랩층 상에 형성된 블록킹 절연막; 및 상기 블록킹 절연막 상에 형성된 게이트 전극;을 더 포함할수 있다.

- <37> 이하, 첨부된 도면들을 참조하면서 본 발명에 따른 전하 트랩형 메모리 소자의 바람직한 실시예들을 상세히 설명한다.

- <38> 본 발명에서는 비휘발성 반도체 메모리 소자의 전하 트랩층으로 유전율이 약 10 이상인 고유전율 절연막(high-k dielectric)을 사용하고, 상기 고유전율 절연막 내에 전이금속(transition metal) 원소(d-오비탈(orbital)에

원자가 전자를 가진 금속)을 도핑함으로써 고유전율 절연막의 밴드갭(band-gaP) 내에 분명히 정의된 안정된 전하 트랩(trap) 즉, 열적 자극(thermal excitation)에 안정적인 깊은 트랩(deep trap)을 형성한다.

- <39> 깊은 트랩은 가전대(valence band)와 전도대(conduction band)로부터 멀리 떨어진 에너지 레벨을 가지며, 이러한 깊은 트랩에 채워진 전자 또는 정공은 열적 자극에 의해 쉽게 전도대나 가전대로 여기되지 못한다. 한편, 깊은 트랩에 대비되는 얕은 트랩(shallow trap)은 전도대 바로 아래나 가전대 바로 위의 에너지 레벨을 가지며, 이러한 얕은 트랩에 채워진 전자 또는 정공은 열적 자극에 의해 쉽게 여기되어 전기 전도에 기여한다.

- <40> 앞서 언급한 바와 같이, 본 발명에서는 전하 트랩층 내에 열적 자극에 안정적인 깊은 트랩을 만들어주는데, 이경우 트랩된 전하들은 쉽게 여기될 수 없으므로 메모리 소자의 리텐션 특성이 개선된다. 더욱이, 본 발명에서 형성하는 깊은 트랩의 에너지 레벨은 도핑되는 전이금속의 종류에 따라 적절히 조절될 수 있고, 그 분포가 넓지 (broad) 않고 불연속적(discrete)이기 때문에, 적절히 선택된 전이금속에 의해 형성된 트랩 내에 포획된 전하는 열적으로 여기될 가능성이 더욱 적다.

- <41> 특히, 본 발명에서는 깊은 트랩을 고유전율 절연막 내에 형성하는데 고유전율 절연막은 유전율이 높아 등가 환산 두께(equivalence of thickness: EOT)에서 종래의 전하 트랩층으로 사용되는 실리콘 질화막 보다 많은 전하트랩을 가질 수 있다. 또한, 고유전율 절연막은 종래의 전하 트랩층으로 사용되는 비정질의 실리콘 질화막과 달리 잘 결정화되어 있기 때문에 본질적으로 그 내부에 형성되는 트랩의 안정성이 높다.

- <42> 이와 같은 이유로 본 발명은 전하 트랩층의 트랩 사이트 밀도를 높임과 아울러 트랩의 열적 안정성을 높여 비휘 발성 반도체 메모리 소자의 리텐션 특성을 개선할 수 있다.

- <43> 또한, 본 발명에서는, 전이금속이 도핑된 고유전율 절연막을 전하트랩층으로 사용할 경우, 통상적인 터널 절연 막으로 사용되는 전하 트랩층 아래의 얇은 실리콘 산화막이 금속과 반응하여 금속-실리콘 화합물을 만들거나 더욱 하부의 실리콘 채널 영역으로 금속이 확산해 들어가는 현상이 나타나는데, 이를 막기 위하여, 터널 절연막을 예컨대, 실리콘 질화막을 포함하도록 형성하므로, 전하 트랩층의 금속과 반응하거나 이 금속이 기판쪽으로 확산되는 것을 방지할 수 있다.

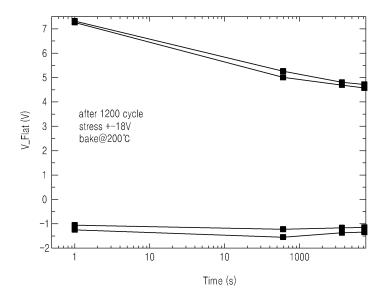

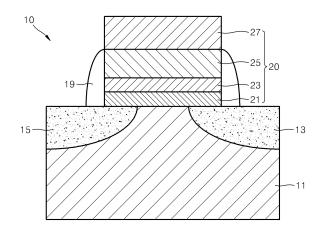

- <44> 도 1은 본 발명의 일 실시예에 따른 전하 트랩형 메모리 소자(10)를 개략적으로 보여준다. 도 1에서의 각 층이 나 영역들의 두께는 명확성을 위해 과장되게 도시하였다.

- <45> 도 1을 참조하면, 전하 트랩형 메모리 소자(10)는, 기판(11) 상에 게이트 구조체(20)를 구비한다.

- <46> 상기 기판(11)에는 소정의 도전성 불순물이 도핑된 제1 및 제2불순물 영역(13)(15)이 형성되어 있다. 제1 및 제2불순물 영역(13)(15) 중 하나는 드레인(D), 나머지 하나는 소스(S)로 사용될 수 있다.

- <47> 상기 게이트 구조체(20)는 전하 트랩층(23)을 포함한다. 상기 기판(11)과 전하 트랩층(23) 사이에는 터널 절연막(21)이 마련되어 있다. 이 터널 절연막(21)은 제1 및 제2불순물 영역(13)(15)과 접촉하도록 상기 기판(11) 상에 형성된다. 전하 트랩층(23) 상에는 블록킹 절연막(25)이 형성되며, 블록킹 절연막(25) 상에 게이트 전극(27)이 형성될 수 있다. 기판(11) 상에 터널 절연막(21), 전하 트랩층(23), 블록킹 절연막(25) 및 게이트 전극(27) 순서로 적층된다. 도 1에서 참조번호 19는 스페이서(spacer)를 나타낸다.

- <48> 본 발명의 전하 트랩층(23)은 d-오비탈(orbital)에 원자가 전자를 갖는 전이금속 원자가 도핑된 고유전율 절연 막으로 이루어진다.

- <49> 이때, 상기 고유전율 절연막은 유전율이 10 이상인 SiO<sub>2</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, HfSiON, HfON 및 HfAlO을 포 함하는 그룹으로부터 선택된 어느 하나로 이루어진 것이 바람직하다.

- <50> 고유전율 절연막을 베이스 매트릭스(base matrix)로 쓰는 이유는 프로그램 효율을 높이고, 같은 환산 두께(EO T)에서 질화막 대비 많은 전하 트랩을 지닐 수 있는 이점이 있기 때문이다.

- <51> 상기 고유전율 절연막 내에 도핑되는 전이금속은 한 종류일 수도 있고, 경우에 따라서는, 두 종류 이상일 수도 있다. 도핑되는 전이금속이 두 종류 이상인 경우, 고유전율 절연막 내에 전자 트랩과 정공 트랩을 동시에 형성하여 보다 많은 수의 전자 트랩과 정공 트랩을 동시에 형성될 수 있다. 도핑된 전이 금속 원자는 고유전율 절연막 분자 구조의 금속 원자나 산소 원자 자리를 치환해 들어가 안정된 트랩을 형성하게 된다. 도핑된 전이 금속원자는 d-오비탈(orbital)에 원자가 전자를 가진 금속이면 무엇이든 무방하나, 특히, HfO2 절연막에 도핑할 전이금속 원자는 Ta, V, Ru 및 Nb 등이 적당하다.

- <52> 이때, 도핑되는 전이금속의 농도는 0.01~15%(atomic %)인 것이 바람직하다.

- <53> 예를 들어, 만약, 결함이 없이 완벽한 구조를 갖는 HfO<sub>2</sub>막 내에 Ta, V, Ru 및 Nb 등의 전이금속이 도핑되면, 도 핑되는 전이금속의 최외곽 전자의 개수가 Hf의 그것과 다르므로, 결합에 참여하지 않는 잉여 전자나 정공이 발 생한다. 이와 같이 발생된 잉여 전자와 정공은 각각 정공 트랩과 전자 트랩으로 작용할 수 있다.

- <54> HfO2막 내에 전이금속이 도핑되면 도핑된 전이금속 원자는 Hf(하프늄) 원자나 0(산소) 원자와 치환되거나, HfO2 단위 셀(unit cell) 내부에 들어가거나, 기존 원자의 빈자리에 들어갈 수도 있는데, 그에 의해 형성되는 트랩의 안정적인 에너지 레벨은 양자역학적 계산에 의해 결정된다. 그러므로, 트랩의 에너지 레벨은 도핑되는 전이금속 의 종류에 따라 달라질 수 있다.

- <55> Ta, V, Ru 및 Nb는 HfO2막 내에 깊은 트랩을 형성하면서, 아울러 보다 많은 트랩 사이트를 만든다. 그러므로, 전하 트랩층(24)으로 사용하는 고유전율 절연막이 HfO2막인 경우, 도핑되는 전이금속으로는 Ta, V, Ru 및 Nb 등이 적당하다.

- <56> 따라서, 상기 고유전율 절연막이  $HfO_2$ 로 이루어진 경우, 여기에 도핑되는 전이금속은 Ta, V, Ru 및 Nb 등을 포함하는 그룹으로부터 선택된 적어도 하나 이상인 것이 바람직하다.

- <57> 한편, Al<sub>2</sub>O<sub>3</sub>막 내에 전이금속이 도핑되면, 도핑된 전이금속 원자는 Al(알루미늄) 원자나 O(산소) 원자와 치환되거나, 기존 원자간 결합 외에 끼어 새로운 결합을 만들거나 기존 원자의 빈자리에 들어갈 수도 있는데, 그에 의해 형성되는 트랩의 안정적인 에너지 레벨은 양자역학적 계산에 의해 결정된다. 그러므로, 트랩의 에너지 레벨은 도핑되는 전이금속의 종류에 따라 달라질 수 있다.

- <58> W, Ru, Mo, Ni, Nb, V 및 Ti가 Al<sub>2</sub>O<sub>3</sub>막 내에 깊은 트랩을 형성하면서, 아울러 보다 많은 트랩 사이트를 만든다. 그러므로, 전하 트랩층(23)으로 사용하는 고유전막이 Al<sub>2</sub>O<sub>3</sub>막인 경우, 도핑되는 전이금속으로는 W, Ru, Mo, Ni, Nb, V 및 Ti 등이 적당하다.

- <59> 따라서, 상기 고유전율 절연막이 Al<sub>2</sub>O<sub>3</sub>막으로 이루어진 경우, 여기에 도핑되는 전이금속은 W, Ru, Mo, Ni, Nb, V 및 Ti를 포함하는 그룹으로부터 선택된 적어 하나 이상인 것이 바람직하다.

- <60> 여기서, 전하 트랩충(23)으로서 고유전율 절연막에 전이금속을 도핑하여, 깊은 트랩을 형성하는 것에 대한 보다 자세한 설명은 본 출원인에 의해 제안된 대한민국특허출원 제2006-70886(출원일 2006년 7월 27일)을 참조하는 것으로 하고, 여기서는 보다 자세한 설명은 생략한다.

- 본 실시예에 있어서, 상기 터널 절연막(21)은 단층 구조로 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)으로 형성된다. 이때, 실리콘 질화막은, 통상적인 전하 트랩형 메모리 소자에서 터널 절연막으로 사용되는 실리콘 산화막에 대비하여, 불순물 농도가 높지 않고(즉, 불순물의 농도가 실리콘 산화막과 비견될만하고) 실리콘과의 계면 특성이 우수하도록 형성되는 것이 바람직하다. 이러한 양질의 실리콘 질화막을 형성하기 위해, 상기 터널 절연막(21)을 이루는 실리콘 질화막은 제트 기상 증착(Jet Vapor Depositon)과 같은 특수한 제법을 사용하여 형성될 수 있다.

- <62> 상기와 같은 특수한 제법에 의해 실리콘 질화막을 형성하면, 실리콘 산화막에 대비하여 불순물 농도가 높지 않고 실리콘과의 계면 특성이 우수한 결함 없는 실리콘 질화막(defect-less Si<sub>3</sub>N<sub>4</sub>)을 형성할 수 있다.

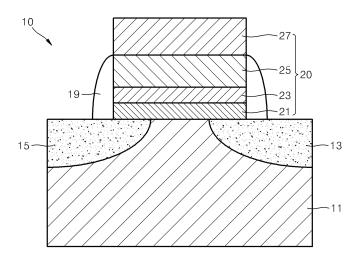

- <63> 대안으로, 도 2에서와 같이, 터널 절연막(31)은 실리콘 질화막(33)과 실리콘 산화막(32)의 이중층 구조로 이루 어질 수도 있다.

- <64> 도 2는 본 발명의 다른 실시예에 따른 전하 트랩형 메모리 소자(30)를 개략적으로 보여준다. 도 2에서, 도 1에서와 동일 참조부호는 동일 부재를 나타내므로, 전술한 바를 참조하는 것으로 하고, 여기서는 반복적인 설명을 생략한다. 도 2에서의 각 층이나 영역들의 두께는 명확성을 위해 과장되게 도시하였다.

- <65> 도 2를 참조하면, 본 발명의 다른 실시예에 따른 전하 트랩형 메모리 소자(30)에서, 게이트 구조체(20')는, 실리콘 질화막(33) 및 실리콘 산화막(32)의 이중층 구조로 이루어진 터널 절연막(31)을 구비하며, 기판(11) 상에 실리콘 산화막(32), 실리콘 질화막(33) 및 전하 트랩층(23) 순서로 적층된다.

- <66> 이 경우, 실리콘 산화막(32)이 실리콘으로된 기판과 직접 계면을 형성하므로, 실리콘 질화막(33)은 보통의 성장 법으로 길러질 수 있다. 특수한 제법으로 만들어지지 않은 실리콘 질화막(33)이라도 전하 트랩층으로부터 금속

확산을 막거나 금속-실리콘 화합물 생성을 막는 구실을 할 수 있다.

- <67> 따라서, 본 실시예에서는, 터널 절연막(31)을 보통의 성장법으로 만들어진 실리콘 질화막(33)과 실리콘 산화막 (32)의 복층 구조로 구성한다.

- <68> 물론, 본 실시예의 경우에, 실리콘 질화막(33)을 상기한 특수한 제법으로 형성하는 것도 가능하다.

- <69> 한편, 상기 터널 절연막(21 또는 31)과 전하 트랩층(23)이 기존 산화막에 비해 유전율이 높은 물질로 형성되므로, 상기 블록킹 절연막(25)도 유전율이 높고 밴드갭이 큰 고유전율 박막을 사용하는 것이 바람직하다. 예를 들어, 상기 블록킹 절연막(25)은 Si<sub>3</sub>N4, HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, ZrO<sub>2</sub> 또는 Al<sub>2</sub>O<sub>3</sub> 막으로 이루어질 수 있다.

- <70> 상기 게이트 전극(27)은 일 함수(work function)이 큰 금속막으로 이루어진 것이 바람직하다. 예를 들어, 게이트 전극(27)은 골드(Au) 나 알루미늄 막으로 이루어진 질 수 있다. 이외에도 상기 게이트 전극(27)은 통상적으로 반도체 메모리 소자의 게이트 전극으로 사용되는 Ru, TaN 금속 또는 NiSi 등의 실리 사이드 물질로 형성될수 있다.

- <71> 상기한 바와 같이, 본 발명은 전하 트랩층(23)으로 전이 금속이 도핑된 고유전율 박막을 사용하고, 터널 절연막 (21 또는 31: 터널링 장벽)으로 실리콘 질화막을 사용하는 전하 트랩형 메모리 소자의 게이트 스택을 제공한다.

- <72> 상기한 바와 같이 본 발명에 따른 전하 트랩형 메모리 소자(10)(30)는, 전하 트랩층(23)을 전이 금속이 도핑된 고유전율 절연막(doped high-k dielectrics)으로 형성하고, 터널 절연막(21)(31)을 결합이 없는 실리콘 질화막의 단층 구조로 형성하거나, 실리콘 질화막(33)과 실리콘 산화막(32)의 이중층 구조로 형성함으로써 금속과 실리콘의 결합을 막도록 되어 있다.

- <73> 전기적 특성 측면에서 본 발명은, 실리콘 질화막을 터널 절연막으로 사용함으로써 전하 트랩층에 도포된 금속과 실리콘의 결합을 줄이고 금속의 확산을 막아 터널 절연막에 불순물을 만들지 못하게 함으로써, 외부 전기적 스 트레스가 가해질 경우 생길 수 있는 전하 누설 경로를 차단할 수 있다. 이러한 특성은 소자의 전하 리텐션 (charge retention) 특성과 밀접한 관련이 있다.

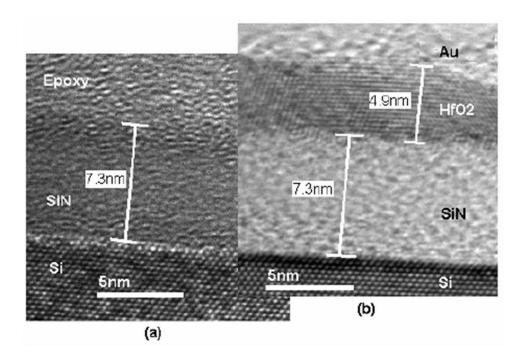

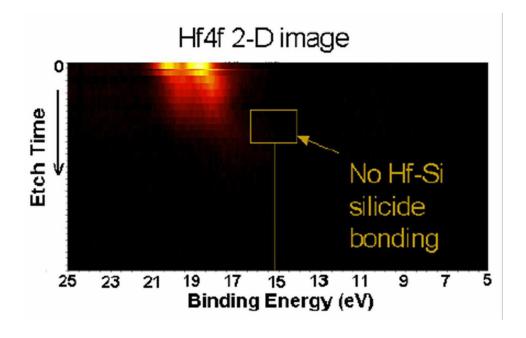

- <74> 도 3은 실리콘 질화막과 고유전율 절연막의 단면 TEM 사진을 보여준다. 도 4는 도 3의 실리콘 질화막과 고유전율 절연막의 계면에서 금속-실리콘 결합이 존재하지 않음을 보여주는 XPS 깊이 프로파일(depth profile)이다.

- <75> 도 3에서 알 수 있는 바와 같이, 실리콘 질화막(SiN) 상에 에폭시(Epoxy)층을 형성한 경우와, 실리콘 질화막 (SiN) 상에 고유전율 절연막인 HfO<sub>2</sub> 층을 형성한 경우를 비교하여 보면, 실리콘 질화막의 층 두께가 변화가 없으며, 실리콘 질화막과 고유전율 절연막인 HfO<sub>2</sub> 층 사이의 계면에 금속-실리콘 결합이 존재하지 않음을 알 수 있다. 이는 도 4의 XPS 깊이 프로파일로부터도 알 수 있다.

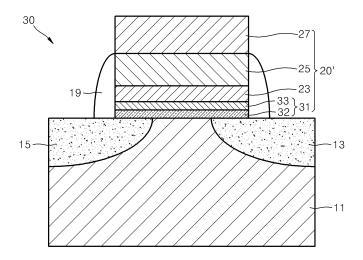

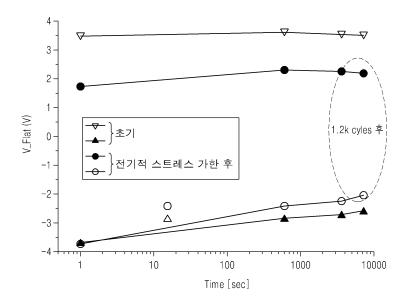

- <76> 도 5는 실리콘 질화막을 터널 절연막으로 사용하였을 때의 게이트 스택 캐패시터(gate stack capacitor)에서 얻은 고온 리텐션 결과를 보여준다. 도 5의 결과를 얻기 위해 Al / Al<sub>2</sub>O<sub>3</sub> / Ta+HfO<sub>2</sub> / Si<sub>3</sub>N<sub>4</sub> / Si의 게이트 스택을 가지도록 본 발명의 샘플을 형성하였다. 도 5에서 가로축은 경과 시간, 세로축은 시간 경과에 따른 플랫 밴드 전압(V-Flat)을 나타낸다.

- <77> 도 5에서는 상기의 게이트 스택을 가지도록 형성한 본 발명의 샘플에 전기적 스트레스를 전혀 가하지 않은 초기 상태와, +18V, -18V의 1.2k 사이클링(cycling)의 전기적 스트레스를 가한 다음의 리텐션 특성을 비교하여 보여 준다. 도 5의 결과는 본 발명의 샘플을 200℃로 가열한(bake) 상태에서 측정한 것이다.

- <78> 도 5를 살펴보면, 두 가지 모두 위쪽 그래프(트랩된 전자에 대한 것임)는 큰 차이가 없이 일정함을 보여주고 있다.

- <79> 도 6은 비교예로서, 실리콘 산화막을 터널 절연막으로 사용하였을 때의 게이트 스택 캐패시터(gate stack capacitor)에서 얻은 고온 리텐션 결과를 보여준다. 도 6의 결과를 얻기 위해 Al / Al<sub>2</sub>O<sub>3</sub> / Ta+HfO<sub>2</sub> / SiO<sub>2</sub> / Si 의 게이트 스택을 가지도록 비교 샘플을 형성하였다. 도 6에서 가로축은 경과 시간, 세로축은 시간 경과에 따른 플랫 밴드 전압(V-Flat)을 나타낸다.

- <80> 도 6에서는 상기의 게이트 스택을 가지도록 형성한 비교 샘플에 +18V, -18V의 1.2k 사이클링(cycling)의 전기적 스트레스를 가한 다음의 리텐션 특성을 비교하여 보여준다. 도 6의 결과는 비교 샘플을 200℃로 가열한(bake) 상태에서 측정한 것이다.

- <81> 비교 샘플에서 전체 스택의 등가 환산 두께(EOT)는 본 발명의 샘플과 동일하게 즉, 비교 샘픔의 실리콘 산화막의 등가 환산 두께는 본 발명의 샘플에서의 실리콘 질화막과 동일하게 맞추었다.

- <82> 도 6에서 상단의 그래프는, 전자의 리텐션 특성, 하단의 그래프는 정공의 리텐션 특성을 보여준다.

- <83> 도 5 및 도 6을 비교해보면, 종래와 같이, 터널 절연막을 실리콘 산화막으로 형성하는 경우, 1.2k 리사이클링의 전기적 스트레스를 가하면, 전자의 리텐션 특성이 본 발명에 비해 좋지 않음을 알 수 있다.

- <84> 도 5 및 도 6의 비교로부터 알 수 있는 바와 같이, 본 발명에서와 같이 실리콘 질화막을 터널 절연막에 사용하면, 고유전율 전하 트랩층을 구비하는 전하 트랩형 메모리 소자에서 전자의 리텐션 특성이 우수하게 되어, 멀티레벨 프로그래밍(multi-level programming)에 더욱 중요한 전자의 리텐션 특성을 개선하는데 뚜렷한 효과를 보여준다.

## 발명의 효과

<85> 상기한 바와 같은 본 발명에 따르면, 전하 트랩층을 전이금속이 도핑된 고유전율 절연막으로 형성하고, 금속-실 리콘 화합물을 만들거나 더욱 하부의 실리콘 채널 영역으로 금속이 확산해 들어가는 현상을 방지하도록 터널 절 연막에 실리콘 질화막을 사용하여 함으로써, 전하 트랩층 물질의 밴드갭 내에 분명히 정의된 안정된 전하 트랩을 만들고, 여기에 전하를 트랩하여 리텐션 특성이 우수한 전하 트랩형 비휘발성 반도체 메모리 소자를 실현할수 있다.

## 도면의 간단한 설명

- <!> 도 1은 본 발명의 일 실시예에 따른 전하 트랩형 비휘발성 메모리 소자를 개략적으로 보여준다.

- <2> 도 2는 본 발명의 다른 실시예에 따른 전하 트랩형 비휘발성 메모리 소자를 개략적으로 보여준다.

- <3> 도 3은 실리콘 질화막과 고유전율 절연막의 단면 TEM 사진을 보여준다.

- <4> 도 4는 도 3의 실리콘 질화막과 고유전율 절연막의 계면에서 금속-실리콘 결합이 존재하지 않음을 보여주는 XPS 깊이 프로파일(depth profile)이다.

- <5> 도 5는 실리콘 질화막을 터널 절연막으로 사용하였을 때의 게이트 스택 캐패시터(gate stack capacitor)에서 얻은 고온 리텐션 결과를 보여준다.

- <6> 도 6은 비교예로서, 실리콘 산화막을 터널 절연막으로 사용하였을 때의 게이트 스택 캐패시터(gate stack capacitor)에서 얻은 고온 리텐션 결과를 보여준다.

- <7> <도면의 주요부분에 대한 부호의 설명>

- <8> 10,30...전하 트랩형 메모리 소자 20,20'....게이트 구조체

- < >> 11...기판 21,31...터널 절연막

- <10> 23...전하 트랩층 25...블록킹 절연막

- <11> 27...게이트 전극 32...실리콘 산화막

- <12> 33...실리콘 질화막

# 도면

# 도면1

## 도면2

도면3

도면4

# *도면5*

# 도면6