(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3746552号

(P3746552)

(45) 発行日 平成18年2月15日(2006.2.15)

(24) 登録日 平成17年12月2日(2005.12.2)

(51) Int.CI.

HO2J 3/04 (2006.01)

F 1

HO2J 3/04

C

請求項の数 1 (全 6 頁)

(21) 出願番号 特願平7-316210

(22) 出願日 平成7年12月5日(1995.12.5)

(65) 公開番号 特開平9-163611

(43) 公開日 平成9年6月20日(1997.6.20)

審査請求日 平成14年8月20日(2002.8.20)

(73) 特許権者 000144991

株式会社四国総合研究所

香川県高松市屋島西町2109番地8

(73) 特許権者 000006105

株式会社明電舎

東京都品川区大崎2丁目1番17号

(74) 代理人 100096459

弁理士 橋本 剛

(72) 発明者 松下 邦雄

香川県高松市屋島西町2109番地8 株式会社四国総合研究所内

(72) 発明者 大辺 実

東京都品川区大崎2丁目1番17号 株式会社明電舎内

最終頁に続く

(54) 【発明の名称】瞬時電圧低下対策装置の異常確認方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電力系統に母線連絡遮断器を介して連系される自家発電機と、この電力系統と自家発電機との系統間に瞬時電圧低下対策装置を設置し、この瞬時電圧低下対策装置の主回路素子として常時はオン状態に維持されるサイリスタスイッチを用い、このサイリスタスイッチの破損有無を確認する方法において、

前記サイリスタスイッチの破損有無確認時の判定開始信号が信号発生回路に入力された時、信号発生回路を介してオン動作中のサイリスタスイッチに対して前記母線連絡遮断器の動作時間より短い時間に設定された  $t_1$  時間のオフ指令を出力し、このオフ指令出力中に前記電力系統に流れる電流を検出して予め設定された設定電流との偏差信号を算出すると共に、サイリスタスイッチのオフ待ち時間  $t_2$  に設定された判定信号が信号発生回路より出力された時、前記検出電流値が設定電流値以下の場合にはサイリスタスイッチが正常と判断し、前記設定電流以上流れている場合には異常と判断することを特徴とした瞬時電圧低下対策装置の異常確認方法。

## 【発明の詳細な説明】

## 【0001】

## 【産業上の利用分野】

本発明は、電力系統と連系するコーチェネレーションシステムにおいて、電力系統側の瞬時電圧低下によるコーチェネ側の発電機あるいは負荷機器のダウンを防止する瞬時電圧低下対策装置の主回路素子あるいは主回路素子保護用サージアブソーバーの破損の有無を検

とする瞬時電圧低下対策装置の異常確認方法に関する。

**【0002】**

**【従来の技術】**

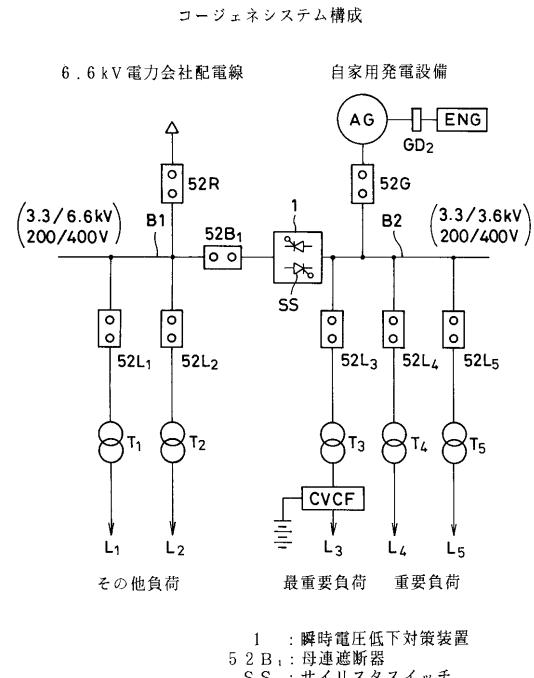

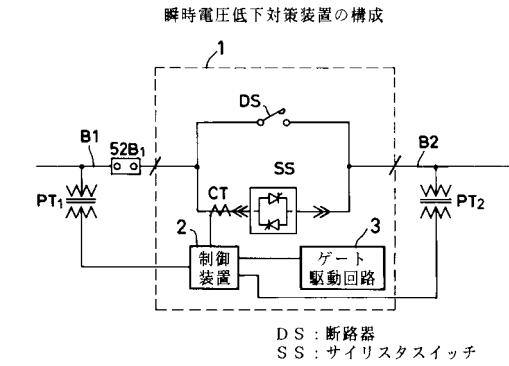

従来、瞬時電圧低下対策装置としては特許文献1(特開平6-343229号)が公知となっている。これは、図4、図5に示すように、電力系統側母線B<sub>1</sub>と自家発電設備側母線B<sub>2</sub>とを連絡する母線連絡遮断器52B<sub>1</sub>と直列に接続しておき、電力系統側事故時に生ずる母線B<sub>1</sub>ないしB<sub>2</sub>の瞬時電圧低下を制御装置2で検出し、ゲート駆動回路3により装置主回路のサイリスタスイッチSSを1サイクル以内にオフとして、母線B<sub>2</sub>に連がっている重要負荷L<sub>3</sub>～L<sub>5</sub>に電圧低下の影響を与えることなく、発電機AGから給電させるものである。

10

**【0003】**

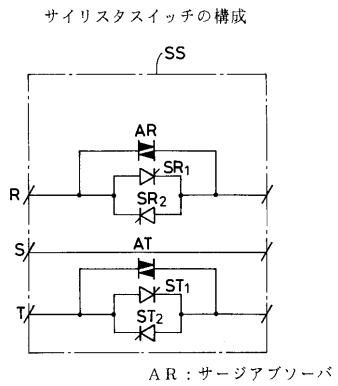

瞬時電圧低下対策装置1のサイリスタスイッチSSは、図6に示すように2相サイリスタスイッチとなっており、一般にR相とT相の2相を逆並列接続のサイリスタ素子S<sub>R1</sub>、S<sub>R2</sub>とS<sub>T1</sub>、S<sub>T2</sub>と、この逆並列接続のサイリスタ素子を保護するサーダブソーバA<sub>R</sub>、A<sub>T</sub>で構成されている。

また、特許文献2(特開平4-193040号)のようなものも公知となっている。この文献のものは、無停電切替装置の各半導体スイッチと直列に零相変流器を設け、各相の半導体スイッチを1相毎に微少時間オンさせて零相電流を確認することによって半導体スイッチの健全性の有無を確認するものである。

20

**【0004】**

**【発明が解決しようとする課題】**

上記瞬時電圧低下対策装置は常時サイリスタスイッチがオン状態で使用されている。ところで、何らかの過電流や系統解列時に発生した素子両端に印加される過電圧によりサイリスタ素子又はサーダブソーバが破損したとしても、サイリスタやサーダブソーバはショート状態となるため、常時オン状態にあるサイリスタスイッチのサイリスタ素子及びサーダブソーバが破損しているかどうか分からぬ。

**【0005】**

万一破損していた場合には、系統での瞬時電圧低下時にサイリスタスイッチをオフ動作させてもショート状態となっているため、系統から解列することはできない。そのため母線連絡遮断器(動作時間約0.3秒)が動作するまでに、発電機又は重要負荷がダウンしてしまう。

30

**【0006】**

本発明は、従来のこのような問題点に鑑みてなされたものであり、その目的とするところは、運転状態でサイリスタスイッチのサイリスタ素子及びサーダブソーバの破損を検出できる瞬時電圧対策装置の異常確認方法を提供するものである。

**【0007】**

**【課題を解決するための手段】**

上記目的を達成するために、本発明は、電力系統に母線連絡遮断器を介して連系される自家発電機と、この電力系統と自家発電機との系統間に瞬時電圧低下対策装置を設置し、この瞬時電圧低下対策装置の主回路素子として常時はオン状態に維持されるサイリスタスイッチを用い、このサイリスタスイッチの破損有無を確認する方法において、

40

前記サイリスタスイッチの破損有無確認時の判定開始信号が信号発生回路に入力された時、信号発生回路を介してオン動作中のサイリスタスイッチに対して前記母線連絡遮断器の動作時間より短い時間に設定されたt<sub>1</sub>時間のオフ指令を出力し、このオフ指令出力中に前記電力系統に流れる電流を検出して予め設定された設定電流との偏差信号を算出すると共に、サイリスタスイッチのオフ待ち時間t<sub>2</sub>に設定された判定信号が信号発生回路より出力された時、前記検出電流値が設定電流値以下の場合にサイリスタスイッチが正常と判断し、前記設定電流以上流れている場合には異常と判断することを特徴としたものである。

**【0008】**

50

### 【実施例】

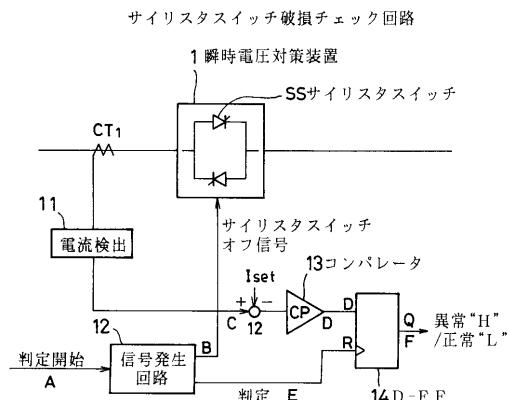

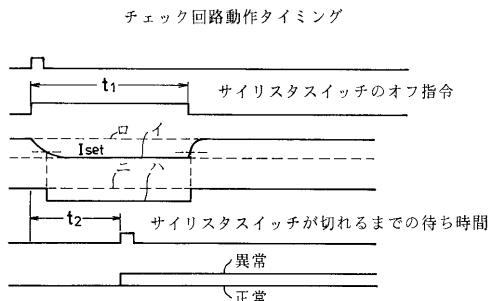

本発明の実施例について図1～図3を参照して説明する。まず、図1について、SSは瞬時電圧低下対策装置1のサイリスタスイッチ、11は装置1の主回路電流を検出して電流信号C(電流検出値 $I_d$ )を出力する電流検出器、12は主回路破損チェック用点検ボタンを押すことにより発生、又は制御回路により定期的に発生する判定開始信号Aの入力により装置1のサイリスタスイッチSSのオフ指令Bを一定時間 $t_1$ (例えば約2/f秒、f:周波数)出力すると共に、一定時間 $t_2$ (例えば約1/f)後に判定用信号Eを出力する信号発生回路、13は電流検出値 $I_d$ と電流設定信号Isetを比較して、電流がほぼ0であることが検出されると出力信号Dが“L”となるコンパレータ、14は信号D、Eが入力端子D、クロック端子Rに入力するDフリップフロップである。

10

### 【0009】

次に、この実施例の動作について図2を用いて説明する。フリップフロップ14は制御回路の立上がり時に初期化され出力端子Qの出力が“L”となっている。信号発生回路12は判定開始信号Aが入力すると、サイリスタスイッチのオフ指令Bを出力する。このオフ指令Bは装置1のゲート駆動回路3(図5)に入力し、サイリスタスイッチSSにオフ信号が出力される。サイリスタスイッチSSが正常であればサイリスタスイッチSSがオフとなり、電流検出信号Cは実線1のようになるので、コンパレータ13の出力信号Dは実線8のようになる。信号Dが“L”となってもフリップフロップ14の端子Qの出力は変化せず、さらに判定用信号Eが発生した時点でフリップフロップ14の端子Dの入力は“L”であるので、端子Qの出力は“L”的ままであるので、サイリスタスイッチSSは正常と判定される。

20

### 【0010】

また、サイリスタスイッチSSが異常であればサイリスタスイッチオフ指令Bが出力してもサイリスタスイッチSSはON状態となっているので、電流検出信号Cは破線1のようになり、電流設定信号Isetより大きいので、コンパレータの出力信号Dは破線2のようになる。このため判定用信号Eが発生するとフリップフロップ14の出力端子Qの出力は“H”となってサイリスタスイッチSSは異常と判定される。なお、上記コンパレータ13による電流ほぼ0の検出は3相各相電流について行い、各相コンパレータ13の出力は論理和でフリップフロップ14に出力する。

30

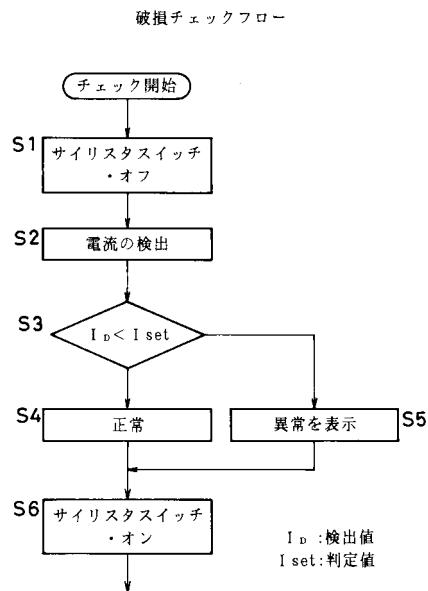

### 【0011】

図1の破損チェック回路は、瞬時電圧低下対策装置1の制御装置2に用いられているCPUにより構成され、図3のフローで破損チェックを行う。人間のボタン操作又は制御回路により判定開始信号Aが発生すると、チェック開始となり、(ステップ)S1でサイリスタスイッチSSのオフ指令を発生させてサイリスタスイッチをオフとし、S2でオフ指令発生中の主回路の3相の各電流を検出し、S3で各相の検出電流 $I_d$ と電流設定値Isetとの比較を行い、3相とも電流がほぼ0であることが検出されれば、S4で正常と判定し、そうでなければ主回路素子ショートと見做してS5で異常と判定し、判定が終わるとS6でサイリスタスイッチオン指令を出力して破損チェックを終了する。

### 【0012】

上記オフ指令が出てからオン指令が出るまでの時間は1～数サイクルであり、この間サイリスタスイッチSSがオフとなり、系統から自家発電側が解列されることになるが、この程度の時間では発電機及びその負荷に対して支障はなく、また、この間に生ずる発電機の電圧位相と系統電圧の位相差は数度程度であるので、解列後の投入に際しては過大な電流は流れることはない。

40

### 【0013】

### 【発明の効果】

本発明は、上述のとおり構成されているので、次に記載する効果を奏する。

### 【0014】

(1) 装置を停止させたり、サイリスタスイッチ部を母線から引き抜いたりして点検する必要がない。

50

【 0 0 1 5 】

(2) 装置を運転状態で発電機や負荷に影響を与えることなく安全かつ容易にチェックができる。

【 0 0 1 6 】

(3) 運転状態において制御回路により定期的にチェックができるので、装置の信頼性が向上する。

## 【図面の簡単な説明】

【図1】実施例にかかる瞬時電圧低下対策装置の破損チェック回路構成図。

【図2】実施例の動作を説明するタイミング図。

### 【図3】実施例の破損チェックフロー図。

【図4】瞬時電圧低下対策装置を施したコーディエネシステム構成図。

【図5】瞬時電圧低下対策装置の構成説明図。

【図6】サイリスタスイッチの構成図。

## 【符号の説明】

1 ... 瞬時電圧低下対策装置

## 2. 制御装置

### 3. ゲート制御回路

## 1.1 ... 電流検出器

1 2 ... 信号発生回路

### 1.3 ... コンパレータ

1 4 ... D フリップフロップ

## SS... サイリスタスイッチ

$S_{B1}, S_{B2}, S_{T1}, S_{T2} \dots$  サイリスタ素子

A<sub>R</sub>, A<sub>T</sub>... サージアブソーバ

【 図 1 】

〔 四 2 〕

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 小野 正明

東京都品川区大崎2丁目1番17号 株式会社明電舎内

審査官 杉田 恵一

(56)参考文献 特開平4 - 193040 (JP, A)

特開平6 - 46526 (JP, A)

特開平6 - 343229 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02H 7/20

H02J 3/00 - 3/50