(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4757013号

(P4757013)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月10日(2011.6.10)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/347 (2011.01)  | HO4N 5/335 470 |

| HO4N 5/353 (2011.01)  | HO4N 5/335 530 |

| HO4N 5/374 (2011.01)  | HO4N 5/335 740 |

| HO4N 9/07 (2006.01)   | HO4N 9/07 A    |

| HO1L 27/146 (2006.01) | HO1L 27/14 A   |

請求項の数 8 (全 16 頁)

(21) 出願番号 特願2005-365421 (P2005-365421)

(22) 出願日 平成17年12月19日 (2005.12.19)

(65) 公開番号 特開2007-173986 (P2007-173986A)

(43) 公開日 平成19年7月5日 (2007.7.5)

審査請求日 平成20年12月4日 (2008.12.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 鈴木 将一

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及びその制御方法、コンピュータプログラム及び記憶媒体

## (57) 【特許請求の範囲】

## 【請求項 1】

入射光量に応じた電荷を発生して蓄積する受光部を含む複数の画素回路を備えた撮像手段と、

前記受光部をリセットするリセット手段と、

前記撮像手段から電荷信号を1ライン毎に読み出す読出手段と、

前記リセット手段により前記受光部がリセットされてから前記読出手段により1ラインの前記電荷信号を読み出すまでの1ラインの蓄積時間が同じフレーム内のライン間で異なる場合に、補正値を算出し該補正値を用いて該ライン間の蓄積時間のずれを補償する補正手段と、

を有し、

所定の閾値を越える前記補正値が算出された場合に、前記補正手段は、前記閾値を前記補正値として設定することを特徴とする撮像装置。

## 【請求項 2】

前記補正手段は、基準蓄積時間を補償の対象となるラインの蓄積時間で除算して得られる商に基づいて前記補正値を算出することを特徴とする請求項 1 に記載の撮像装置。

## 【請求項 3】

前記撮像手段は、複数色の電荷信号を出力し、前記補正手段は、前記補正値を色毎に算出することを特徴とする請求項 2 に記載の撮像装置。

## 【請求項 4】

10

20

入射光量に応じた電荷を発生して蓄積する受光部を含む複数の画素回路を備えた撮像部において、画像データを生成する撮像装置の制御方法であって、

前記受光部をリセットするリセット工程と、

前記撮像部から電荷信号を1ライン毎に読み出す読出工程と、

前記リセット工程において前記受光部がリセットされてから前記読出工程により1ラインの前記電荷信号を読み出すまでの1ラインの蓄積時間が同じフレーム内のライン間で異なる場合に、補正値を算出し該補正値を用いて該ライン間の蓄積時間のずれを補償する補正工程と、

を有し、

所定の閾値を越える前記補正値が算出された場合に、前記補正工程では、前記閾値を前記補正値として設定することを特徴とする撮像装置の制御方法。

10

#### 【請求項5】

前記補正工程では、基準蓄積時間を補償の対象となるラインの蓄積時間で除算して得られる商に基づいて前記補正値が算出されることを特徴とする請求項4に記載の撮像装置の制御方法。

#### 【請求項6】

前記撮像部は、複数色の電荷信号を出力し、前記補正工程では、前記補正値が色毎に算出されることを特徴とする請求項5に記載の撮像装置の制御方法。

#### 【請求項7】

請求項4乃至6のいずれか1項に記載の撮像装置の制御方法をコンピュータに実行させるためのコンピュータプログラム。

20

#### 【請求項8】

請求項7に記載のコンピュータプログラムを格納したコンピュータで読み取り可能な記憶媒体。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、光電変換素子を有する固体撮像装置に関し、特にCMOSセンサを用いた時の電子ズーム高画質化に関する。

#### 【背景技術】

30

#### 【0002】

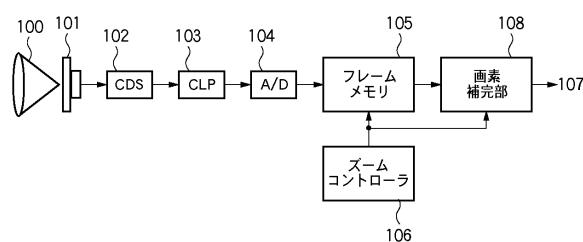

CCDカメラにおける電子式ズーム処理のための構成は、例えば図1に示すようになる。図1において、100はレンズ、101は電荷結合素子(CCD)、102は相関二重サンプリング回路(CDS)、103はクランプ回路(CLIP)である。また、104はアナログディジタルコンバータ(A/D)、105はフレームメモリ、106はズームコントローラ、108は画素補完部、107は画像出力である。

#### 【0003】

このような構成において、光学画像はレンズ100を通って撮像素子であるCCD101の受光面に結像する。CCD101の受光面で結像した光学像は2次元的に配置された光電変換部で光電荷に変換され順次、出力に転送される。相関二重サンプリング回路102により、CCD101の出力信号からCCD特有のリセットノイズが除去され、リセットノイズが除去されサンプルホールドされたビデオ信号が形成される。

40

#### 【0004】

また、クランプ回路103はダークレベルのクランプを行い、A/Dコンバータ104は入力されたアナログ信号をデジタル信号に変換する。フレームメモリ105は、1フレームの全画素データを記録する為のメモリである。ズームコントローラ106は、例えば2倍ズームの画像データが欲しい時、CCDの中心からの一部の領域のみ読み出す。

#### 【0005】

近年では、安価で複雑なタイミング発生回路を必要とせず且つ单一電源で動作して消費電力も少ない等の理由により、CMOS撮像センサを用いるケースが増えてきている。さ

50

らに、CMOS撮像センサは、CMOS撮像センサの任意の領域のみを画像として取り込むことができるという、CCD撮像素子にはない特徴を有する。

#### 【0006】

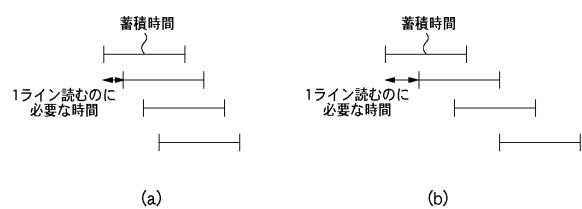

次に任意の領域を読む出すことができるCMOS撮像センサの高画質電子ズーム方式の説明をする（特許文献1を参照。）。図2はCMOSの電子ズーム動作の概念図である。図2(a)は通常モード時の読み出しを示しており、図2(b)はズームモード時の読み出しを示している。通常モード時には、例えば固体撮像素子の4画素を加算した値を1画素分の画素値として読み出しを行う。図2(a)の太枠の範囲内については、塗り潰しで示す画素の信号として、該画素とその右、右斜め下、下の4画素値を加算した値が読み出される。つまり、縦横8×8画素の範囲から4×4画素文の信号が読み出されることになる。 10

#### 【0007】

これに対し、ズームモード時には、8×8画素の太枠範囲内の中央の連続した4×4画素の領域（塗り潰し部分）が、非加算でそのまま読み出される。この場合には、太枠範囲内の中央部分を拡大して表示させることができる。しかも、読み出す画素数は通常モード時と同じであり、信号処理による画素数の水増しを行わなくても良い結果、電子ズーム時の画質を高画質化することができる。

【特許文献1】特開2001-78081号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

20

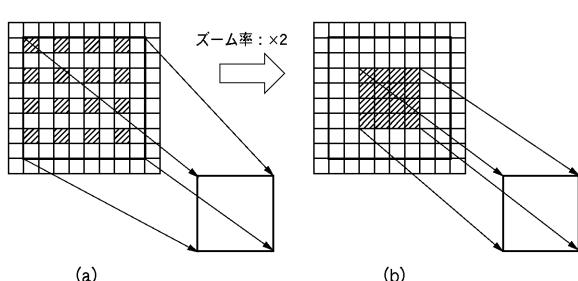

ブロック読み出し可能なCMOSセンサにおいて光電荷を蓄積する場合、蓄積開始タイミングがライン毎に制御されるので、ライン毎に光電荷を蓄積する時間がずれてしまう。このラインごとの時間的ずれは1ライン読み出すのに必要な時間だけずれる。この1ライン読み出すのに必要な時間は以下の式で算出することができる。

$$1\text{ ライン読み出し時間} = \text{HBLK} \times \text{+Skip} \times \text{+水平画素数} \times \text{基準クロック時間} \quad \text{式(1)}$$

（ 、 は垂直方向加算方法により決定する値）

例として垂直2画素加算平均を行う駆動について図3に示す。この場合、 は2、 は1である。即ち、1ラインの読み出し時間は、以下の時間の合計によって求められる。即ち、1ライン目を転送するのに必要な時間HBLK、2ライン目をスキップするのに必要な時間Skip、3ライン目を転送するのに必要な時間HBLK、1ライン目と3ライン目を加算平均した画素を水平画素分転送するのに必要な時間である。 30

#### 【0009】

また、水平画素分を転送するのに必要な時間は、基準クロック時間（駆動周波数）にも依存する。つまり1ライン読み出し時間は垂直方向加算方法、駆動周波数により変化する。この結果、画面上下の蓄積開始時間のずれはこれらの撮像駆動の変更により異なる。

#### 【0010】

図4は、1ライン読み出し時間に基づく蓄積時間のずれを説明するための図である。図4(a)と図4(b)とでは、図4(b)の方が1ライン読み出し時間が長くなっている。ここで、1ライン読み出し時間がより短くなる図4(a)のような駆動方法を「撮像駆動A」とよび、1ライン読み出し時間がより長くなる図4(b)のような駆動方法を「撮像駆動B」とよぶことにする。なお、撮像駆動Aでは、画面上下の蓄積時間のずれが撮像駆動Bに比べて小さくなっている。 40

#### 【0011】

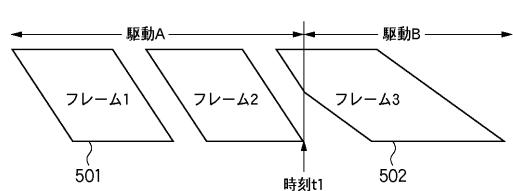

次にEVF、動画等において駆動が変化する場合につき、図5を参照して説明する。図5において、501は撮像駆動Aで駆動されているフレームの画素の蓄積時間と読み出し時間の合計を示している。図5では、前フレームの読み出しが行われたラインについては、次フレームについての光電荷の蓄積が開始されており、前のフレームの読み出し期間と次のフレームの蓄積開始タイミングが重なっている。502は、時刻t1において撮像駆動Aから撮像駆動Bに切り替わった場合の、蓄積時間及び読み出し期間の合計を示している。なお、この駆動の切換タイミングは、フレーム2の画素の読み出しが終了した後の、VBLK（垂直ブ

50

ランキング)期間中に行われる。即ち、駆動切換前のラインは、撮像駆動Aに対応する蓄積開始タイミングが設定され、切換後のラインは撮像駆動Bに対応する蓄積開始タイミングが設定されることとなる。

#### 【0012】

図5に示す例では、時刻t1以前は撮像駆動Aで駆動していたのに対し、時刻t1において撮像駆動Bに切り換えられる。するとフレーム3のリセット開始時刻は時刻t1より前であるため時刻t1以前の期間では蓄積開始タイミングのずれに基づく傾きは、撮像駆動Aに対応している。しかし時刻t1以降は撮像駆動Bに切り換えられるため、読み出時間が撮像駆動Aとは異なり、長くなる。この結果、時刻t1以降にリセットが開始されるラインについては、リセット開始タイミングのずれが撮像駆動Bに対応したものとなり、該ずれに基づく傾きは異なるものとなってしまう。この場合にフレームレートを維持しようとすれば、フレーム3の画面上下において蓄積時間の差が生じてしまう。10

#### 【0013】

このように、上記のような例を一例として、前フレームの読み出しが間にかかる期間とがオーバーラップする場合に、駆動方法を切り換えた場合には、次フレーム内で蓄積時間に差が生じてしまい、出力画像の品位が低下してしまう。

#### 【0014】

そこで、本発明は、駆動方法を切り換えた場合であっても、次フレーム内で蓄積時間の差が生ずることを防ぎ、出力画像の品位を維持することを目的とする。

#### 【課題を解決するための手段】

#### 【0015】

上記課題を解決するための本発明は、撮像装置であって、入射光量に応じた電荷を発生して蓄積する受光部を含む複数の画素回路を備えた撮像手段と、前記受光部をリセットするリセット手段と、前記撮像手段から電荷信号を1ライン毎に読み出す読み出手段と、前記リセット手段により前記受光部がリセットされてから前記読み出手段により1ラインの前記電荷信号を読み出すまでの1ラインの蓄積時間が同じフレーム内のライン間で異なる場合に、補正值を算出し該補正值を用いて該ライン間の蓄積時間のずれを補償する補正手段と、を有し、所定の閾値を越える補正值が算出された場合に、前記補正手段は、前記閾値を前記補正值として設定することを特徴とする。20

また、入射光量に応じた電荷を発生して蓄積する受光部を含む複数の画素回路を備えた撮像部において、画像データを生成する撮像装置の制御方法であって、前記受光部をリセットするリセット工程と、前記撮像部から電荷信号を1ライン毎に読み出す読み出工程と、前記リセット工程において前記受光部がリセットされてから前記読み出工程により1ラインの前記電荷信号を読み出すまでの1ラインの蓄積時間が同じフレーム内のライン間で異なる場合に、補正值を算出し該補正值を用いて該ライン間の蓄積時間のずれを補償する補正工程と、を有し、所定の閾値を越える前記補正值が算出された場合に、前記補正工程では、前記閾値を前記補正值として設定することを特徴とする。30

#### 【発明の効果】

#### 【0016】

本発明によれば、フレーム内のライン間での蓄積時間の差によるレベル差が生じることを防ぎ、出力画像の品位を維持することができる。40

#### 【発明を実施するための最良の形態】

#### 【0017】

本発明の実施形態について、図面を参照しつつ詳細に説明する。

#### 【0018】

##### [第1の実施形態]

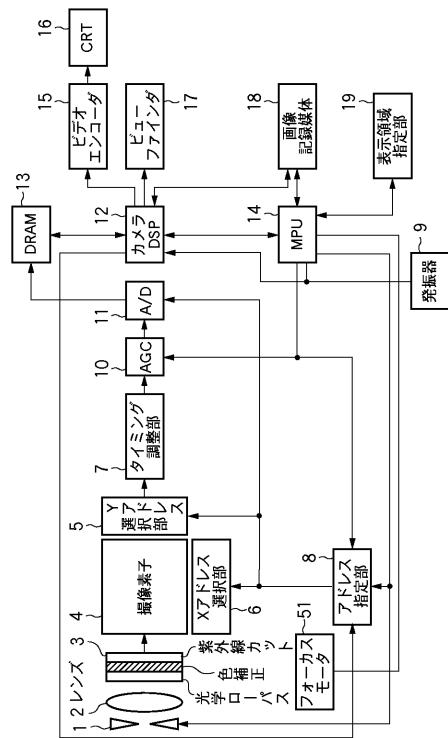

図6における撮像装置において、被写体からの光が絞り羽根1を通り、レンズ2により撮像素子4へ結像されることにより、光電変換が行われる。フィルター群3は、モアレ等を防ぐ為に光の高域をカットする光学ローパス・フィルター、色補正フィルター、および赤外線カットする為のフィルター等が組み合わされて構成されている。50

## 【0019】

撮像素子4で変換された光信号は、アドレス指定部8からの信号によりXアドレス選択部6及びYアドレス選択部5で、2次元で画素位置選択が行われ、タイミング調整部7に読み出される。このタイミング調整部7では、撮像素子4からの出力(1~複数本)のタイミング調整が行われる。

## 【0020】

そして、タイミング調整部7から出力された信号は、AGC(オートゲインコントロール)10により電圧を制御され、A/D変換器11でデジタル信号に変換される。カメラDSP12は、動画または静止画の画像処理を行う。またMPU14は、この画像処理の際に使われるパラメータをカメラDSP12に設定したり、AE、AF処理を行ったりする。10

## 【0021】

なお、AF制御は、フォーカス・モーター51によりフォーカス・レンズ(図示せず)を前後に動かして行う。画像処理する際の一時的な記憶領域としてDRAM13が用いられ、不揮発性の記憶領域として画像記録媒体18が用いられる。画像記録媒体18は、例えば、スマート・メディア、磁気テープ、または光ディスク等である。この画像処理後の表示を行う為にビデオエンコーダ15、および、CRT16等が設けられている。

## 【0022】

また、ビューファインダー17は、例えばLCDの様なもので画像記録媒体18に記憶する前に被写体を確認したりする為に用いられる。これらの出力部は、CRT16、および、ビューファインダー17に限らずプリンタ等を用いてもよい。20

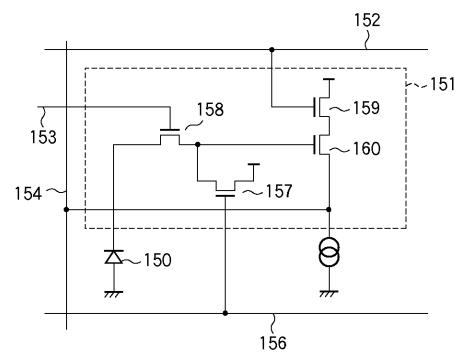

## 【0023】

次に、本実施形態に対応する撮像素子4は、1画素回路と読出回路とから構成されるものであり、まず1画素回路の構成及び動作について図7を参照して説明する。

## 【0024】

図7において、158はフォトダイオード(以下PDという。)150で蓄積された電荷を増幅MOSトランジスタ160のゲートを浮遊構造としたフローティング・デフェュージョン(以下、FDという。)に転送する為の電位障壁操作用転送ゲートのMOSトランジスタである。

## 【0025】

また、157は該PD150の電荷をリセットする為のリセットMOSトランジスタである。そして、ライン選択用のMOSトランジスタとして159が設けられている。なお、これらのMOSトランジスタのゲートは、各々、PD150の電荷を転送する転送信号線153、FDをリセットするリセット信号線156、および選択信号線152に接続されている。30

## 【0026】

ここで、PD150に蓄積された電荷は、まず、リセット信号線156によりリセットトランジスタ157がオンしリセットされたFDへ、転送信号線153により選択されたMOSトランジスタ158を通して転送される。次に、選択信号線152により選択された選択MOSトランジスタ159を介してソースフォロワMOSトランジスタ160で増幅され、読み出し線154へ読み出される。40

## 【0027】

本実施形態では、このような1画素回路の集合からなる撮像領域を利用した電子ズーム動作を行う場合、ズームモード(テレ)時には、画素値の加算を行わずに、撮像領域の一部の領域に含まれる画素を1画素ずつ読み出す。或いは、後述する通常モード(ワイド)よりも加算数を少なくして画素値を加算する。例えば、図12に示すような撮像領域1301が、撮像素子4により撮像可能な領域全体を示すとした場合、ズームモード時は領域1301内の領域1302に含まれる画素について読み出しが行われることになる。このような撮像動作を本実施形態では「撮像動作A」と呼ぶ。一方、通常モード(ワイド)時は、撮像領域の全体1301について、所定数の画素(例えば、 $2 \times 2 = 4$ 画素)を加算50

して読み出しを行う。このような撮像動作を本実施形態では「撮像動作B」と呼ぶ。

**【0028】**

なお、撮像動作Bにおける加算画素数は2ライン(4画素)に限られるものではなく、4ライン(16画素)加算であってもよいし、その場合に撮像動作Aにおいては非加算とせず、2ライン(4画素)加算としてもよい。

**【0029】**

撮像駆動Aにおいて非加算読み出しを行う場合、領域1302に含まれる1ライン分の画素値を読出回路内の保持容量に保存し、その後加算を行わずに水平出力線から読み出すまでの期間が、1水平期間(水平期間A)となる。一方、撮像駆動Bでは、2ライン分の画素値を順次、読出回路内の保持容量に保持し、その後加算して水平出力線から読み出すこととなる。従って、加算後の画素値を読み出すまでの期間が1水平期間(水平期間B)となる。即ち、水平期間Aは水平期間Bよりも短くなる。10

**【0030】**

次に、図8を参照して、図7の1画素回路が複数配列された画素部801と読出回路802とを含む回路構成について説明する。図8では簡易化のために $2 \times 2$ 画素のみが示されている。

**【0031】**

まず、撮像駆動Aにおいて画素値の加算を行わない場合(非加算制御)は、PD150-1の電荷は、図8に示されるMOSトランジスタ161-1が信号線169により導通されることで容量162-1へ該電荷は蓄積される。同様に、PD150-2の電荷は、信号線156-1, 153-1, 152-1、および、169のPD150-1の読み出し制御の際に容量164-1へ読み出される。続いて、信号線167-1と信号線167-2が交互にオンされることで、PD150-1, PD150-2の撮像信号は順次に増幅器171を通して読み出される。垂直方向への動作は156-2, 153-2, 152-2の制御から上記と同様の動作により行われる。20

**【0032】**

次に、撮像駆動Bにおいて画素値の加算を行う場合(加算制御)は、図8に示される信号線156-1, 153-1, 152-1及び169の制御で、PD150-1, PD150-2の電荷が、容量162-1, 164-1にそれぞれ蓄積される。続いて、信号線156-2, 153-2, 152-2、および170の制御で、PD150-3, PD150-4の電荷が、各々、容量162-2, 164-2へ蓄積される。この後、信号線167-1と信号線167-2を同時にオンすれば、PD150-1乃至PD150-4の電荷を加算した撮像信号が増幅器171を通して読み出される。30

**【0033】**

以上の構成により、撮像駆動A及び撮像駆動Bでの動作を行わせることができる。

**【0034】**

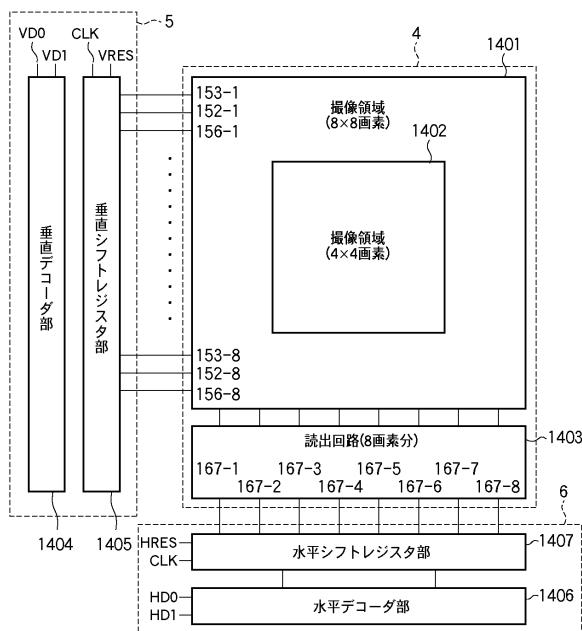

撮像駆動Aにおいて、撮像領域1301のうちの一部の領域1302を選択して画素値の読出を行うこととなる。このような一部の領域を選択するための構成について、図13を参照して説明する。

**【0035】**

図13は本実施形態に対応する、撮像素子4、Yアドレス選択部5及びXアドレス選択部6の構成をより詳細に示す図である。40

**【0036】**

図13では、撮像素子4は $8 \times 8$ 画素で構成される撮像領域1401と、水平方向の8画素に対応した読出回路1403で構成される。また、撮像領域1402は、撮像領域1401内の $4 \times 4$ 画素の領域であり、撮像駆動Aでは撮像領域1402の画素値が非加算で読み出される。一方、撮像駆動Bの場合には、撮像領域1401の画素値が加算されて読み出される。なお、ここでの加算は $2 \times 2$ 画素加算とする。

**【0037】**

Yアドレス選択部5は、垂直デコーダ部1404と垂直シフトレジスタ1405で構成50

され、Xアドレス選択部6は水平デコーダ部1406と水平シフトレジスタ1407で構成される。垂直デコーダ1404の入力は、VD0～VD1が入力され、垂直シフトレジスタ部1405はクロックパルス(CLK)と垂直リセットパルス(VRES)が入力できるようになっている。垂直シフトレジスタ部1405からは、選択信号152、転送信号153、リセット信号156が出力される。また、水平デコーダ1406の入力も、HD0～HD1が入力され、水平シフトレジスタ部1407にはクロックパルス(CLK)と水平リセットパルス(HRES)とが入力される。

#### 【0038】

垂直デコーダ1404及び水平デコーダ1406は、全体の撮像領域である1401を選択するか、或いは、一部の撮像領域である1402を選択するかを決定するために利用される。撮像領域の選択については、水平部と垂直部とはほぼ同様に機能するので、以下、水平方向について説明する。

10

#### 【0039】

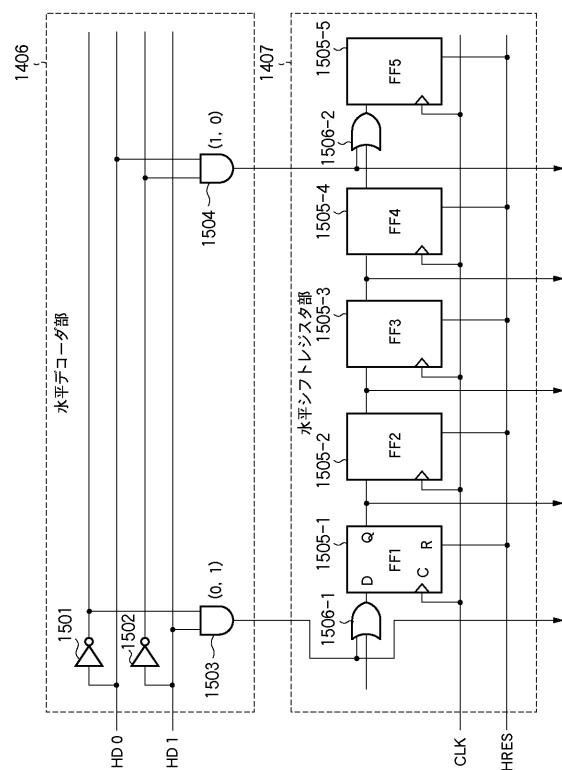

図14に水平デコーダ部1406と水平シフトレジスタ部1407の構成の一例を示す。

。

#### 【0040】

まず、水平デコーダ部1406の入力HD0～HD1は、2本(bit)である。これに対し、撮像領域1401は、水平方向には2画素、4画素、2画素の3つに分割されるので、撮像領域1402を選択する場合には、中央の4画素が選択されるようすればよい。そこで、(HD0、HD1)の組合せとして、例えば、最初の2画素を選択する場合を(0, 0)とし、次の4画素を選択する場合を(0, 1)とし、最後の2画素を選択する場合を(1, 0)とすることができる。

20

#### 【0041】

水平シフトレジスタ部1407は、水平デコーダ部1406と撮像領域1401との間に位置し、水平デコーダ部1406から得られる信号をクロックパルスCLKによりシフトする。同時に、撮像領域1401内の画素回路に、画素値の水平出力線への読出を信号167を出力する。走査を止めるときは水平リセットパルスHRESにより、水平シフトレジスタ部1407の内容を消去することができる。

#### 【0042】

図14において、水平デコーダ部1406は、入力としてHD0を下位桁、HD1を上位桁とし、インバータ1501及び1502とAND回路1503及び1504とで構成される。水平シフトレジスタ部1407は、D型フリップフロップ1501-1から1505-5と、OR回路1506-1及び1506-2で構成される。尚、図14では、水平方向8画素のうち撮像領域1402に対応する4画素が選択される場合を説明するために簡略化して記載したものである。従って、水平シフトレジスタ部1407内のフリップフロップは一部のみを記載しており、本来であれば8画素分が配列される構成となる。

30

#### 【0043】

なお、図14に示す構成以外に、水平デコーダ部1406の回路として、ANDやインバータ以外の素子を用いたり、水平シフトレジスタ部1407の構成を従来例のようにクロックドインバータで構成してもよい。

40

#### 【0044】

水平デコーダ部1406の入力に(HD0, HD1)に(0, 1)が入力されると、撮像領域1402の4画素の内、左端の画素のための読出回路へ信号167が出力される。また、それと同時にフリップフロップ1505-1(FF1)が選択される。その後クロックパルスCLKによりFF2(1505-2)、FF3(1505-3)及びFF4(1505-4)と順次1クロック毎にシフトされる。FF4(1505-4)の出力はOR回路1506-2を介してFF5(1505-5)に入力される。従って、撮像領域1402に対応する4画素のみを選択する場合には、AND回路1504に対し(HD0、HD1)として(1, 0)を入力せず、リセットパルスHRESを入力すればよい。また、該4画素に続く2画素を更に選択する場合には、(HD0、HD1)として(1, 0)

50

を入力し、AND回路1504の出力が1となるようにすればよい。

**【0045】**

なお、垂直シフトレジスタ部1405を同様に走査することにより、撮像領域1401のうち $4 \times 4$ 画素領域の1402を選択することができる。

**【0046】**

以上のようにすれば、全体の撮像領域のうち、一部の撮像領域のみを選択することが可能となる。

**【0047】**

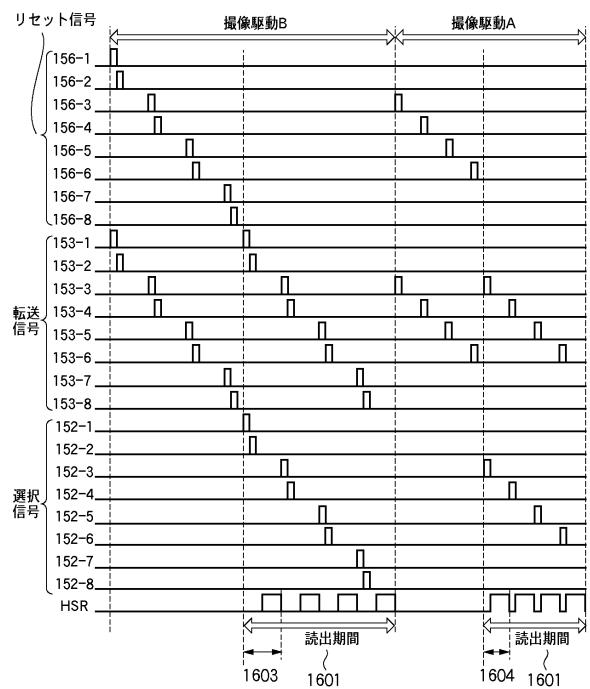

図15に、図13に対応する制御信号のタイミングチャートを示す。ここで、1601は、撮像駆動Bにおける読出期間を示し、1602は撮像駆動Aにおける読出期間を示している。10

**【0048】**

1603は、撮像駆動Bにおける1水平期間を表し、2組の選択信号、例えば152-1及び152-2により画素値を読み出した後、これらを加算して水平出力線から読み出すのに要する時間である。一方、1604は、撮像駆動Aにおける1水平期間を表し、単一の選択信号線、例えば152-3により画素値を読み出した後、水平出力線から読み出すのに要する時間である。ここで、1水平期間1603は1水平期間1604よりも長い。また、読出期間1601及び読出期間1602は、このような1水平期間1603及び1水平期間1604の集合として構成される。従って、図15に示すように水平出力線から読み出される画素数が同じ場合には、読出期間1601は読出期間1602よりも長くなってしまう。20

**【0049】**

次に、本実施形態における処理を説明する。まず、電子ズーム倍率の変更を受け付けると、それに伴って撮像駆動方式が変更される。その際に生ずるフレーム内蓄積時間ずれを補償するために補正が行われる。本実施形態では明暗差が生じるラインに対して、ゲイン補正值によりゲイン補正を行う。なお、本実施形態では、電子ズーム倍率の変更を受け付けたことに伴い駆動方式の変更する場合、読出が終了した直後のVBLK期間中に該駆動方式の変更が行われるものとする。

**【0050】**

本実施形態において、ゲイン補正值は変更前後の駆動方式に対応する蓄積時間と読出時間とに基づいて算出することができる。図9にゲイン補正值の算出方法を説明するための図を示す。30

**【0051】**

図9(a)では、蓄積時間として3通りの場合を記載している。蓄積時間1では、各画素回路のリセット開始タイミングが太線901のように設定される。この場合、時刻t1以前におけるリセット開始タイミングは、撮像駆動Aに対応しており、時刻t1以降のリセット開始タイミングは撮像駆動Bに対応することとなる。蓄積時間1は、リセット開始タイミング901と読み出しタイミング904との差分として与えられることとなる。なお、時刻t1は駆動Aで読み出しが行われたフレーム910内の全ての画素値の読み出しが終了した時点とする。40

**【0052】**

次に、蓄積時間2では、蓄積時間1よりも遅いタイミングでリセットが開始され、細線902のようにリセット開始タイミングが設定される。ここでも、時刻t1前後でリセット開始タイミングが変更される。蓄積時間1は、リセット開始タイミング902と読み出しタイミング904との差分として与えられることとなる。

**【0053】**

更に、蓄積時間3では、時刻t1以降にリセットが開始され、リセット開始タイミングは一点鎖線903のように設定される。ここでのリセット開始タイミングは全体として撮像駆動Bに対応している。蓄積時間3は、リセット開始タイミング903と読み出しタイミング904との差分として与えられることとなる。50

## 【0054】

このような3通りの蓄積時間において、1フレーム内の画素値のバラツキを補正するために、本実施形態では蓄積時間の差に応じたゲイン調整を行う。

## 【0055】

時刻t1以前において、リセット開始タイミング901及び902の傾きは、撮像駆動Aに対応する傾きであって既知である。従って、時刻t1経過までにリセットが開始入れるライン数をカウントすることができる。また、カウントされた各ラインにおける蓄積時間1及び蓄積時間2は、それぞれリセット開始タイミング901及び902と、読み出しタイミング904との差分で算出される。そこで、時刻t1以前における画素値を補正するためのゲイン補正值(ga)は、1フレームにおける基準蓄積時間905を、蓄積時間1又は蓄積時間2で割った値として求めることができる。蓄積時間1の場合のゲイン補正值をga1とし、蓄積時間2の場合のゲイン補正值をga2とすると、以下のように算出することができる。

## 【0056】

$$g_a1 = (\text{基準蓄積時間 } 1) / \text{蓄積時間 } 1$$

$$g_a2 = (\text{基準蓄積時間 } 2) / \text{蓄積時間 } 2$$

一方、図9の所定値906より蓄積時間が短い場合には、ゲイン補正を行わない。これは、前のフレームの読み出しが終了した後にリセット動作が開始されるために、既に駆動方式が切り替わっているためである。従って、蓄積時間3の場合についてはゲイン補正是行われない。これにより、S/Nの劣化を最小限にとどめることができると可能である。

## 【0057】

このようにして求められたゲイン補正值(ga)と、1フレームの垂直ラインのライン番号(I)との対応関係は、図9(b)に示すようになる。図9(b)において、蓄積時間1の場合、ゲイン補正值は、画面最上部(I=1)からライン番号I1までは、907に示す直線上のいずれかの値が適用される。ライン番号I1以降のゲイン補正值は“1”が適用される。蓄積時間2の場合、ゲイン補正值は、画面最上部(I=1)からライン番号I2までは、908に示す直線上のいずれかの値が適用される。ライン番号I2以降のゲイン補正值は“1”が適用される。蓄積時間3の場合には、ゲイン補正值は常に“1”である(909)。

## 【0058】

本実施形態ではまた、このゲイン補正值を色毎に設定可能である。これはライン毎の蓄積時間のずれにより、例えば黒レベルが変化する懸念があるためである。この結果、赤(R)、緑(G)、青(B)の三色で構成される色バランスがライン毎でずれるため、輝度補正と同時に色バランスの補正を行う。

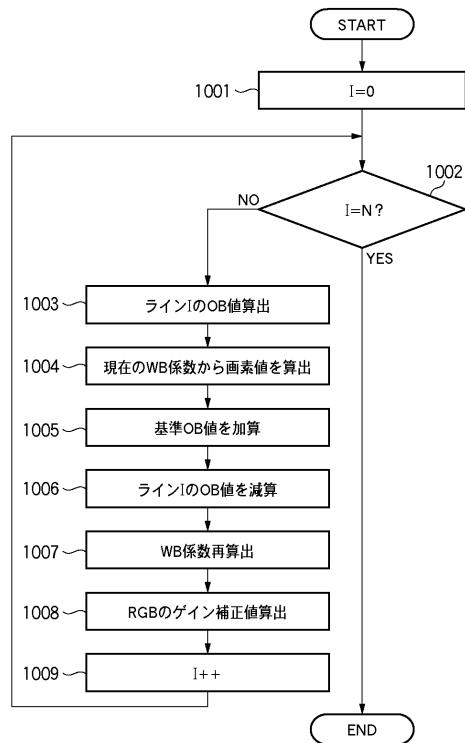

## 【0059】

この色毎のゲイン補正值算出方法について図10のフローチャートを参照して説明する。なお、図10のフローチャートに対応する処理は、カメラDSP12において実行される。

## 【0060】

まず、ステップS1001では、ゲイン補正值を算出するラインの番号(I)がリセットされる。続くステップS1002では、ライン番号Iが、補正を行うライン数であるNに一致するか否かが判定される。このライン数Nは、図9における、時刻t1以前にリセット動作が開始されたライン数に対応する値である。もし、ライン番号IがNに一致する場合には(ステップS1002において「YES」)、ゲイン補正值の算出が必要なラインについて、算出処理が終了したこととなるので、本処理を終了する。一方、Nに一致しない場合には(ステップS1002において「NO」)、ステップS1003に移行する。

## 【0061】

ステップS1003では、ゲイン補正值の算出対象であるライン(I)におけるOB(Optical Black)値が算出される。OB値は、画素値の黒レベルを補正するための値であつ

10

20

30

40

50

て、ライン( I )の黒レベル検出画素の画素値に基づいて算出することができる。次に、ステップ S 1 0 0 4において、現在の WB(ホワイトバランス)係数の逆数が算出され、画素値に変換される。更に、ステップ S 1 0 0 5では、信号処理に用いる OB 値(「基準 OB 値」という。)を加算することで OB 減算前の画素値を算出する。この基準 OB 値とは、1フレーム内の画素に対して共通に用いられる OB 値である。本実施形態の場合、時刻 t 1 以前にリセット動作が開始された画素は蓄積時間が異なるので、基準 OB 値をそのまま適用することができない。そこで、ステップ S 1 0 0 5では、該 OB 値で減算される以前の値に戻している。

#### 【 0 0 6 2 】

ステップ S 1 0 0 6では、ステップ S 1 0 0 3で算出されたライン OB 値が減算される。更に、ステップ S 1 0 0 7では、新たに算出された画素値の逆数を求めることにより WB 係数が再算出される。続いて、ステップ S 1 0 0 8では、ステップ S 1 0 0 7で算出された WB 係数と、1フレーム内の画素に対して共通に用いられる WB 係数との比が算出され、蓄積時間から算出したゲイン補正值に乗算される。これにより、色毎のゲイン補正值が算出される。ステップ S 1 0 0 9では、Iをインクリメントして、ステップ S 1 0 0 2に戻る。

10

#### 【 0 0 6 3 】

以上の処理はゲイン補正を行うライン全てについて行われる。このような処理により、ライン毎のゲイン補正值を算出することができる。

#### 【 0 0 6 4 】

20

以上のように、本実施形態では、撮影中に撮像駆動が切り替わった場合でも、蓄積時間の異なるラインにゲイン補正をかけることで、画面上下の明暗差を補償できる。また、色毎のゲイン補正值を算出して、黒レベルが変化を抑制して色バランスを維持することができる。

#### 【 0 0 6 5 】

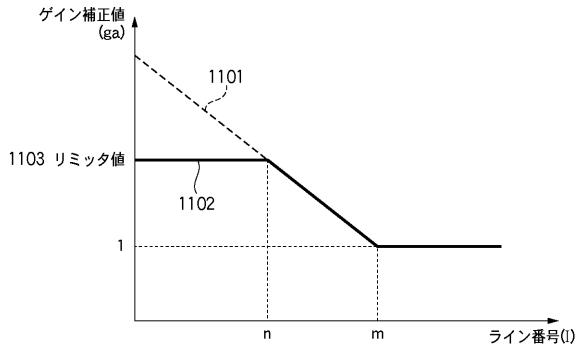

##### [ 第 2 の 実 施 形 態 ]

上記の第 1 の実施形態では、算出されたゲイン補正值を用いて画面上下の明暗差を完全に補正する場合を説明した。しかし、このような補正方式では、ゲイン補正を行ったラインの S / N 比が悪くなる弊害がある。

#### 【 0 0 6 6 】

30

そこで本実施形態では、EVF 表示など、記録メディアに保存されない時のみ完全補正を行い、動画撮影時などの場合は補正ゲインにリミッタ値を設けて、画面上下の明暗と S / N 比のトレードオフを考慮した補正を行うことを特徴とする。

#### 【 0 0 6 7 】

図 1 1 に、本実施形態に対応するゲイン補正值とライン番号との関係を示す。図 1 1 において、1 1 0 1 は、ライン n までの画素について適用されるゲイン補正值のうち、リミッタをかける以前のものの推移を示している。1 1 0 2 は、ライン n までの画素について適用されるゲイン補正值のうち、リミッタをかけたものの推移を示している。このように、本実施形態では、ゲイン補正值が所定の閾値に相当するリミッタ値 1 1 0 3 を超える場合には、ゲイン補正值がリミッタ値 1 1 0 3 に設定される。即ち、図 1 1 の場合では、画面最上部からライン n までは、ゲイン補正值がリミッタ値 1 1 0 3 に設定されることとなる。これにより、当該領域における S / N 比の悪化を抑制することができる。

40

#### 【 0 0 6 8 】

また、ゲイン補正值が所定の閾値であるリミッタ値 1 1 0 3 を下回る、図 1 1 のライン n からライン m までについては、算出されたゲイン補正值をそのまま適用することができる。また、ライン m 以降、画面最下部までは、基準蓄積時間が確保されているため、ゲイン補正值は 1、即ちゲイン補正是行われない。

#### 【 0 0 6 9 】

このように、本実施形態では、動画撮影時などにおいて、画面上下の明暗と S / N 比のトレードオフを考慮した補正を行うことができる。

50

**【 0 0 7 0 】**

なお、S/N比の弊害を完全に除くために、撮影駆動が切り替わったために画面上下に蓄積時間差が生じてしまうフレームを、撮像駆動が切り替わる前のフレームで置き換えてよい。

**【 0 0 7 1 】****[ その他の実施形態 ]**

なお、本発明は、複数の機器（例えばホストコンピュータ、インターフェイス機器、リーダ、プリンタなど）から構成されるシステムに適用しても、一つの機器からなる装置（例えば、複写機、ファクシミリ装置など）に適用してもよい。

**【 0 0 7 2 】**

10

また、本発明の目的は、前述した機能を実現するソフトウェアのプログラムコードを記録した記憶媒体を、システムに供給し、そのシステムがプログラムコードを読み出し実行することによっても達成される。この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現し、そのプログラムコードを記憶した記憶媒体は本発明を構成する。また、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているオペレーティングシステム（OS）などが実際の処理の一部または全部を行い、その処理によって前述した機能が実現される場合も含まれる。

**【 0 0 7 3 】**

20

さらに、以下の形態で実現しても構わない。すなわち、記憶媒体から読み出されたプログラムコードを、コンピュータに挿入された機能拡張カードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込む。そして、そのプログラムコードの指示に基づき、その機能拡張カードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行って、前述した機能が実現される場合も含まれる。

**【 0 0 7 4 】**

本発明を上記記憶媒体に適用する場合、その記憶媒体には、先に説明したフローチャートに対応するプログラムコードが格納されることになる。

**【 図面の簡単な説明 】****【 0 0 7 5 】**

【図1】CCDを用いた電子式ズーム処理の構成例を示すブロック図である。

【図2】部分読出を利用した高画質電子ズームの概念を説明するための図である。

30

【図3】垂直2画素加算平均におけるライン蓄積時間差の概念を説明するための図である。

【図4】撮像駆動が切り換えられた場合の、1ライン読出時間の変化を説明するための図である。

【図5】撮像駆動を切り換えた場合に、1画面内で上下で蓄積時間がずれる場合を説明するための図である。

【図6】本発明の実施形態に対応する撮像装置の構成の一例を示す図である。

【図7】本発明の実施形態に対応する1画素回路の構成の一例を示す図である。

【図8】本発明の実施形態に対応する画素回路と読出回路の構成の一例を示す図である。

【図9】本発明の第1の実施形態に対応する、ゲイン補正值の算出方法を説明するための図である。

40

【図10】本発明の実施形態に対応する色毎のゲイン補正值算出方法の処理の一例を示すフローチャートである。

【図11】本発明の第2の実施形態に対応する、ゲイン補正值の算出方法を説明するための図である。

【図12】本発明の実施形態において、撮像駆動Aと撮像駆動Bとで画素値が読み出される撮像領域の違いを説明するための図である。

【図13】本発明の実施形態に対応する、撮像領域の一部の領域の画素値を読み出すための構成の一例を示す図である。

【図14】本発明の実施形態に対応する、水平デコーダ部1406及び水平シフトレジス

50

タ部 1 4 0 7 の構成の一例を示す図である。

【図 1】本発明の実施形態に対応する、制御信号のタイミングチャートの一例である。

【図 1】

【図 4】

【図 2】

【図 5】

【図 3】

| 加算前 |   | 加算後 |   | 1ライン読み出す時間 |      |      |             |

|-----|---|-----|---|------------|------|------|-------------|

| R   | G | R   | G | HBLK       | Skip | HBLK | 水平画素を読み出す時間 |

| ⊕   |   | ⊕   |   | HBLK       | Skip | HBLK | 水平画素を読み出す時間 |

| G   | B | G   | B | HBLK       | Skip | HBLK | 水平画素を読み出す時間 |

| ⊕   |   | ⊕   |   |            |      |      |             |

| R   | G |     |   |            |      |      |             |

| G   | B |     |   |            |      |      |             |

(a)

(b)

(c)

【図6】

【図7】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

審査官 鈴木 肇

- (56)参考文献 特開2002-330329(JP,A)

特開2001-016508(JP,A)

特開2005-229321(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 5/222 - 5/257

H04N 9/04 - 9/11

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762