(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4314096号

(P4314096)

(45) 発行日 平成21年8月12日(2009.8.12)

(24) 登録日 平成21年5月22日(2009.5.22)

(51) Int.CI.

G O 1 R 31/28 (2006.01)

F 1

G O 1 R 31/28

H

請求項の数 10 (全 27 頁)

(21) 出願番号 特願2003-374912 (P2003-374912)

(22) 出願日 平成15年11月4日 (2003.11.4)

(65) 公開番号 特開2005-140555 (P2005-140555A)

(43) 公開日 平成17年6月2日 (2005.6.2)

審査請求日 平成18年11月6日 (2006.11.6)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100125254

弁理士 別役 重尚

(72) 発明者 渡辺 宏

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 池田 達治

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 高橋 一也

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】半導体集積回路検査装置および半導体集積回路検査方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体集積回路の複数の出力端子にそれぞれ接続される複数の抵抗器と、

前記複数の抵抗器に所定の電圧を印加する印加手段と、

前記半導体集積回路の入力端子に所定の動作パターン信号を入力する入力手段と、

前記入力手段による所定の動作パターン信号の入力によって前記複数の抵抗器にそれ

れ流れる電流量の総和を測定する測定手段と、

前記出力端子が同一の抵抗値を有する抵抗器と夫々接続される第1の状態と、前記出力

端子が互いに異なる抵抗値を有する抵抗器と夫々接続される第2の状態との間で複数の出

力端子に対する複数の抵抗器の接続状態を切替え制御する制御手段と、

前記測定手段によって測定された電流量の総和と、前記半導体集積回路の代わりに予め

正常に動作することが確認されている半導体集積回路と同一機能を持った良品サンプルに

前記所定の動作パターン信号を入力した際の前記測定手段によって測定された電流量の総

和の正常値とを比較する比較手段と、

前記比較手段による比較結果に基づき、前記半導体集積回路が正常であるか否かを判定

する判定手段とを有し、

前記判定手段は、前記第1の状態および前記第2の状態の両方において、前記測定され

た電流量の総和が正常であると判定したときに前記半導体集積回路が正常であると判定す

ることを特徴とする半導体集積回路検査装置。

## 【請求項 2】

10

20

前記所定の動作パターン信号は、複数の動作ステップから成り、

前記測定手段および前記比較手段は、前記所定の動作パターン信号の動作ステップ毎に

、前記測定および前記比較をそれぞれ行うことを特徴とする請求項1記載の半導体集積回路検査装置。

**【請求項 3】**

前記半導体集積回路の複数の出力端子を複数のブロックに分割し、

前記複数のブロックの各々に対して個別に、前記印加手段と前記入力手段と前記測定手段と前記比較手段と前記判定手段とを動作させることを特徴とする請求項1又は2記載の半導体集積回路検査装置。

**【請求項 4】**

前記複数の抵抗器が、前記半導体集積回路の複数の出力端子に、それぞれバッファを介して接続されることを特徴とする請求項1又は2記載の半導体集積回路検査装置。

**【請求項 5】**

前記複数のバッファから信号を出力するタイミングを制御する制御信号を、前記動作パターン信号に同期して、前記複数のバッファに出力する制御信号出力手段を更に有することを特徴とする請求項4記載の半導体集積回路検査装置。

**【請求項 6】**

前記複数のバッファの各々に同時に制御信号が入力することを特徴とする請求項5記載の半導体集積回路検査装置。

**【請求項 7】**

前記複数のバッファの各々に個別に制御信号が入力することを特徴とする請求項5記載の半導体集積回路検査装置。

**【請求項 8】**

前記制御信号出力手段が、前記判定手段によって異常であると判定された動作ステップにおいて、前記制御信号を前記複数のバッファのそれぞれに順次入力させ、前記判定手段によって出力端子を順に判定することを特徴とする請求項7記載の半導体集積回路検査装置。

**【請求項 9】**

前記比較手段が、電流量の総和の正常値として所定幅の判定基準ゾーンを有し、

前記半導体集積回路に対して前記測定手段によって測定した電流量が、前記判定基準ゾーン内に収まっているか否かを判別し、前記測定手段によって測定した電流量が前記判定基準ゾーン内に収まっていない場合に、前記半導体集積回路に異常があると決定することを特徴とする請求項2記載の半導体集積回路検査装置。

**【請求項 10】**

半導体集積回路の複数の出力端子にそれぞれ接続される複数の抵抗器を備えた半導体集積回路検査装置における半導体集積回路検査方法であって、

前記複数の抵抗器に所定の電圧を印加する印加ステップと、

前記半導体集積回路の入力端子に所定の動作パターン信号を入力する入力ステップと、

前記所定の動作パターン信号の入力によって前記複数の抵抗器にそれぞれ流れる電流量の総和を測定する測定ステップと、

前記出力端子が同一の抵抗値を有する抵抗器と夫々接続される第1の状態と、前記出力端子が互いに異なる抵抗値を有する抵抗器と夫々接続される第2の状態との間で複数の出力端子に対する複数の抵抗器の接続状態を切替え制御する制御ステップと、

前記測定ステップによって測定された電流量の総和と、前記半導体集積回路の代わりに予め正常に動作することが確認されている半導体集積回路と同一機能を持った良品サンプルに前記所定の動作パターン信号を入力した際の前記測定ステップにおいて測定された電流量の総和の正常値とを比較する比較ステップと、

前記比較ステップにおける比較結果に基づき、前記半導体集積回路が正常であるか否かを判定する判定ステップとを有し、

前記判定ステップにおいて、前記第1の状態および前記第2の状態の両方において前記

10

20

30

40

50

測定された電流量の総和が正常であると判定したときに前記半導体集積回路が正常であると判定することを特徴とする半導体集積回路検査方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路検査装置および半導体集積回路検査方法に関し、特に、半導体集積回路の機能検査を行う半導体集積回路検査装置、該装置に適用される半導体集積回路検査方法に関する。

【背景技術】

【0002】

10

従来、論理回路を含む半導体集積回路の機能検査では、該半導体集積回路の機能を検査するための所定のテストパターンを半導体集積回路に入力し、該半導体集積回路から出力された出力パターンを出力パターン期待値と比較することによって、良品／不良品の判定を行う方法が用いられている（例えば、非特許文献1参照）。この所定のテストパターンは、該テストパターンを半導体集積回路に入力したときに該半導体集積回路から出力されるべき出力パターンの期待値が、論理シミュレーション等によって予め判明しているようなテストパターンである。

【0003】

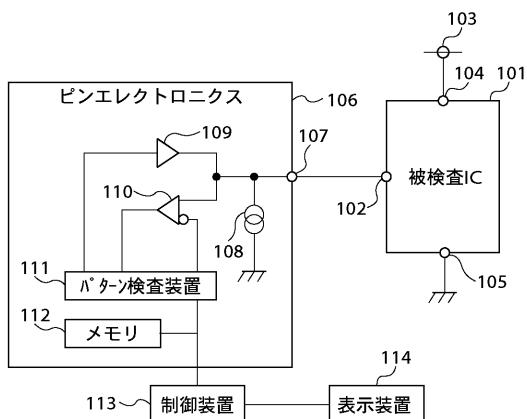

図16は、従来の半導体集積回路の検査装置の構成例を示す図である。

【0004】

20

被検査IC101の信号端子102は、ピンエレクトロニクス106の入出力端子107へ接続される。

【0005】

入出力端子107は、ドライバ109、コンパレータ110、負荷108へ接続される。ドライバ109、コンパレータ110は、パターン検査装置111へ接続される。

【0006】

30

パターン検査装置111は、被検査IC101の機能を検査するためのパターン信号をメモリ112から読み書きし、信号端子102が入力状態である場合、メモリ112から読み出したパターン信号をドライバ109へ送り、ドライバ109がそれを被検査IC101へ送る。信号端子102が出力状態である場合は、信号端子102を介して被検査IC101から出力される出力パターンをコンパレータ110が受け、それをパターン検査装置111がメモリ112へ貯える。

【0007】

負荷108には、信号端子102の出力論理（ハイレベルやローレベル）に応じて負荷電流が流れる。なお、ドライバ109は、信号端子102が出力状態である場合、出力をハイインピーダンス状態に切替えて、余計な電流が流れ込まないようにする。

【0008】

メモリ112へ貯えられた被検査IC101の出力パターンは、制御装置113により期待値と比較され、一致しているか否かが表示装置114に表示される。

【0009】

40

被検査IC101の信号端子102が、図16には1つだけ図示されるが、実際には複数存在し、ピンエレクトロニクス106は、被検査IC101が持つ信号端子の数と同数だけ備えられる。また、被検査IC101の電源端子104は、検査装置に内蔵される電源103などに接続され、GND端子105も検査装置のGNDへ接地される。

【0010】

従来の検査装置は、例えば以上のように構成され、このような検査装置として一般にLSI(ASIC)テスタなどが用いられている。

【非特許文献1】「VLSI試験／故障解析技術」、株式会社トリケップス、1992年、p.119～120

【発明の開示】

50

**【発明が解決しようとする課題】**

**【0011】**

ところで、上記従来の出力パターンの期待値が判明しているテストパターンによる検査方法では、測定対象となる半導体集積回路の規模が増大するにつれて、全ての論理状態をシミュレーションしたテストパターンを作成することが困難となり、テストパターンでの未検出領域が存在することになってしまう。その結果、半導体集積回路を構成部品の1つとする機械装置等において、上記の未検出領域で該機械装置が使用されたときに、正常動作しないという不具合が発生する虞があった。

**【0012】**

こうした不具合が発生した場合、機械装置の不良現象に基づき論理シミュレーション及び故障シミュレーションを行い、その不良現象を検出可能なテストパターンを作成し、そのテストパターンを当初のテストパターンに追加する方法がとられていた。10

**【0013】**

しかしながら、機械装置内の使用において半導体集積回路の論理状態を確認することが困難な場合も多く、またシミュレーションによる方法は膨大な量のデータを処理しなければならず、もっと簡易な方法が求められていた。

**【0014】**

また、図16に示す上記従来の検査装置では次のような問題点があった。

**【0015】**

(1) 被検査IC101の出力端子や入出力端子などの複数の端子の出力状態を、コンパレータ110によって常時監視する必要があった。20

**【0016】**

(2) 制御装置113が、コンパレータ110で検出された被検査IC101の信号端子102の出力状態を、メモリ112に格納されている出力パターンの期待値と高速で比較しなければならなかった。

**【0017】**

(3) 被検査IC101の端子数が多い場合、また、複数の被検査ICを一度に検査するパラレルテストを行う場合、コンパレータ110を多数用意したり、メモリ112の容量を大きくしたりする必要があり、このため、LSIテストの規模が大きくなってしまう。また、複数の端子に対して同時に高速で検査・判定を行う必要があり、これは高度の技術が要求され、検査装置の高コスト化が避けられない。30

**【0018】**

本発明はこのような問題点に鑑みてなされたものであって、論理シミュレーション及び故障シミュレーションを行わず、半導体集積回路の良品／不良品の判定を簡易に行うことを利用した半導体集積回路検査装置および半導体集積回路検査方法を提供することを目的とする。

**【0019】**

また、小型化、高速処理化、低コスト化を図った半導体集積回路検査装置および半導体集積回路検査方法を提供することを他の目的とする。

**【課題を解決するための手段】**

**【0020】**

上記目的を達成するために、請求項1記載の半導体集積回路検査装置は、半導体集積回路の複数の出力端子にそれぞれ接続される複数の抵抗器と、前記複数の抵抗器に所定の電圧を印加する印加手段と、前記半導体集積回路の入力端子に所定の動作パターン信号を入力する入力手段と、前記入力手段による所定の動作パターン信号の入力によって前記複数の抵抗器にそれぞれ流れる電流量の総和を測定する測定手段と、前記出力端子が同一の抵抗値を有する抵抗器と夫々接続される第1の状態と、前記出力端子が互いに異なる抵抗値を有する抵抗器と夫々接続される第2の状態との間で複数の出力端子に対する複数の抵抗器の接続状態を切替え制御する制御手段と、前記測定手段によって測定された電流量の総和と、前記半導体集積回路の代わりに予め正常に動作することが確認されている半導体集50

積回路と同一機能を持った良品サンプルに前記所定の動作パターン信号を入力した際の前記測定手段によって測定された電流量の総和の正常値とを比較する比較手段と、前記比較手段による比較結果に基づき、前記半導体集積回路が正常であるか否かを判定する判定手段とを有し、前記判定手段は、前記第1の状態および前記第2の状態の両方において、前記測定された電流量の総和が正常であると判定したときに前記半導体集積回路が正常であると判定することを特徴とする。

#### 【0025】

また、請求項10記載の半導体集積回路検査方法は、半導体集積回路の複数の出力端子にそれぞれ接続される複数の抵抗器を備えた半導体集積回路検査装置における半導体集積回路検査方法であって、前記複数の抵抗器に所定の電圧を印加する印加ステップと、前記半導体集積回路の入力端子に所定の動作パターン信号を入力する入力ステップと、前記所定の動作パターン信号の入力によって前記複数の抵抗器にそれぞれ流れる電流量の総和を測定する測定ステップと、前記出力端子が同一の抵抗値を有する抵抗器と夫々接続される第1の状態と、前記出力端子が互いに異なる抵抗値を有する抵抗器と夫々接続される第2の状態との間で複数の出力端子に対する複数の抵抗器の接続状態を切替え制御する制御ステップと、前記測定ステップによって測定された電流量の総和と、前記半導体集積回路の代わりに予め正常に動作することが確認されている半導体集積回路と同一機能を持った良品サンプルに前記所定の動作パターン信号を入力した際の前記測定ステップにおいて測定された電流量の総和の正常値とを比較する比較ステップと、前記比較ステップにおける比較結果に基づき、前記半導体集積回路が正常であるか否かを判定する判定ステップとを有し、前記判定ステップにおいて、前記第1の状態および前記第2の状態の両方において前記測定された電流量の総和が正常であると判定したときに前記半導体集積回路が正常であると判定することを特徴とする。

10

#### 【発明の効果】

#### 【0030】

本発明によれば、出力端子が同一の抵抗値を有する抵抗器と夫々接続される第1の状態、および出力端子が互いに異なる抵抗値を有する抵抗器と夫々接続される第2の状態の両方において、複数の抵抗器に夫々流れた電流量の総和が正常であると判定したときに半導体集積回路が正常であると判定するので、論理シミュレーションおよび故障シミュレーションを行わず、半導体集積回路の良品／不良品の判定を簡易に行うことができる。

20

#### 【発明を実施するための最良の形態】

#### 【0046】

以下、本発明を実施するための最良の形態について、図面を参照して説明する。

#### 【0047】

##### 〔第1の実施の形態〕

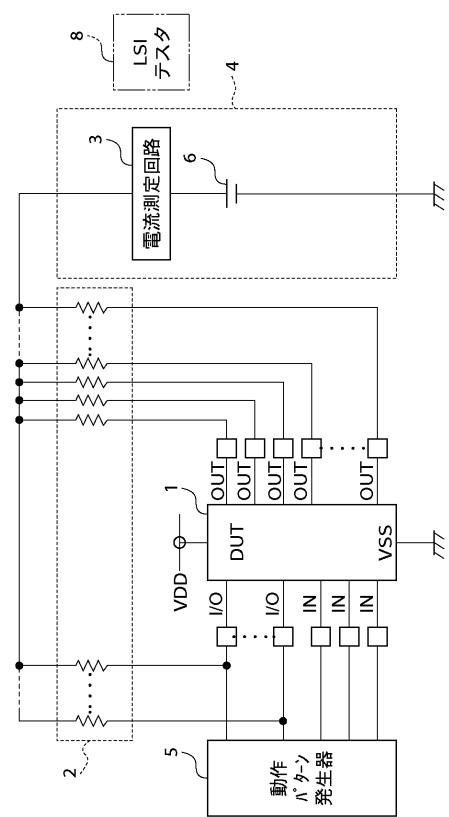

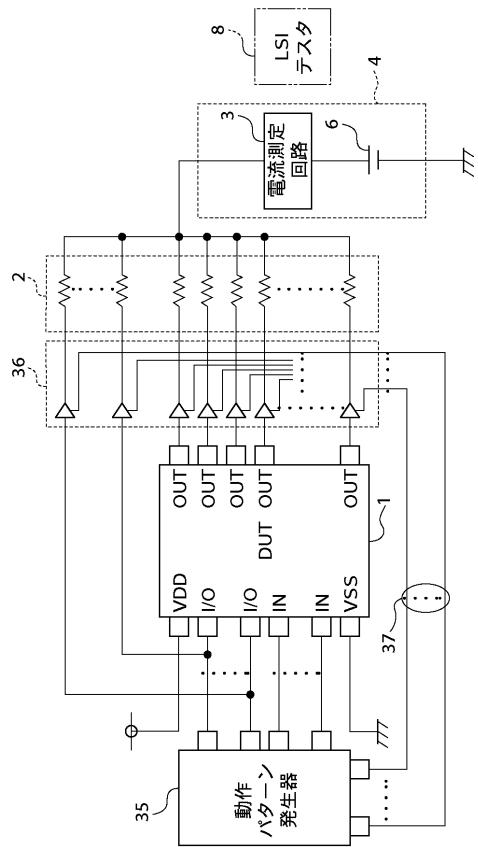

図1は、本発明に係る第1の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。

#### 【0048】

図中1は、検査対象となる論理回路を含む半導体集積回路(DUT)であり、該DUT1の出力端子(OUT)及び入出力端子(I/O)の全てが抵抗ユニット2を介して電圧印加回路4に接続される。抵抗ユニット2は、並列に接続された同じ抵抗値の複数の抵抗を含み、該複数の抵抗の各一端がDUT1の出力端子及び入出力端子にそれぞれ接続され、各他端が短絡して電圧印加回路4に接続される。電圧印加回路4は、マイナス端が接地された直流電源6と、該直流電源6のプラス端と抵抗ユニット2との間に設けられた電流測定回路3とからなり、電圧印加回路4は、DUT1の電源電圧VDD端子の電位と同電位を出力する。

30

#### 【0049】

5は動作パターン発生器であり、DUTを構成部品の一つとする機械装置での使用に基づいて決まる、DUTの機能を検査するための所定の動作パターン(論理信号0,1)を発生し、DUT1の入力端子(IN)及び入力状態の入出力端子(I/O)に出力する。

40

50

この結果、所定の動作パターンの動作ステップ毎の静止状態（過渡状態から安定状態に遷移した後の状態）において、DUT 1 の各出力端子（OUT）から出力論理信号（0, 1）が出力され、この状態で、出力端子（OUT）及び入出力端子（I/O）にそれぞれ接続された抵抗ユニット 2 の各抵抗に流れる電流の総和を、電流測定回路 3 が測定する。なお、電流測定回路 3 を含む電圧印加回路 4 及び動作パターン発生器 5 は LSI テスタ 8 で構成され、LSI テスタ 8 は、後述の測定結果の保存や比較等の情報処理機能を備えている。

#### 【0050】

一方、上記の所定の動作パターンの入力で正常に動作することが確認されている、DUT 1 と同一機能の半導体集積回路（以下「良品サンプル」という）を DUT 1 に代わって用いて、図 1 に示す構成において所定の動作パターンの動作ステップ毎に抵抗ユニット 2 の各抵抗にそれぞれ流れる電流の総和を電流測定回路 3 によって予め測定しておき、この測定結果を LSI テスタ 8 に保存しておく。そして LSI テスタ 8 が、この良品サンプルを用いて予め得られた測定結果と、DUT 1 によって得られた測定結果とを動作ステップ毎に比較する。

10

#### 【0051】

なお、DUT 1 や良品サンプルに入力される所定の動作パターンは、論理シミュレーションにより出力期待値が予め求められているものである必要はない。また、電流測定回路 3 は、電圧印加回路 4 から出力される電圧値と、抵抗ユニット 2 を構成する 1 つの抵抗の値とで計算される、該 1 つの抵抗を流れる電流値の測定分解能を有するとともに、該 1 つの抵抗を流れる電流値に、抵抗ユニット 2 を構成する全抵抗の数を乗算して得られる電流値をカバーできる測定レンジを有する。

20

#### 【0052】

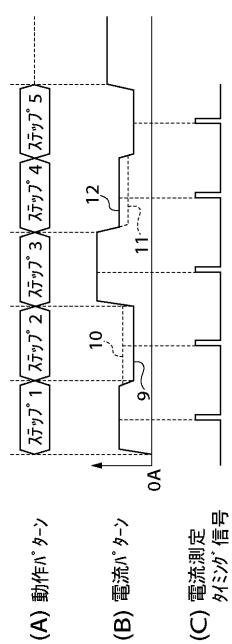

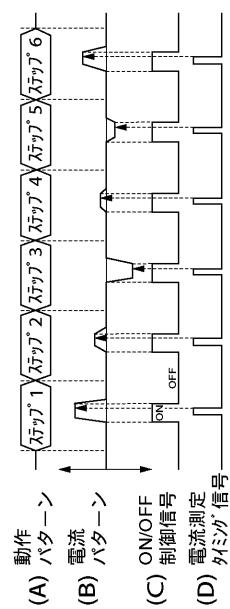

図 2 は、動作パターン発生器 5 から発生される所定の動作パターンと、電流測定回路 3 で測定される電流値とを示すタイミングチャートである。

#### 【0053】

図 2において（A）は、動作パターン発生器 5 から DUT 1 に入力される動作パターンを示し、（B）は、抵抗ユニット 2 を流れる電流の総和のパターン（以下「電流パターン」という）を示し、（C）は電流測定タイミング信号を示し、該電流測定タイミング信号に応じて電流測定回路 3 で電流測定が行われる。

30

#### 【0054】

電流測定タイミング信号は、動作パターンの各動作ステップにおける静止状態時に発生されるように設定されており、該電流測定タイミング信号に応じて電流測定回路 3 が、良品サンプルと DUT 1 とに対して電流測定を実施し、LSI テスタ 8 が、動作ステップ毎に測定された両電流値を動作ステップ毎に比較する。

#### 【0055】

各動作ステップにおいて電流測定回路 3 によって測定される電流値について、次に説明する。すなわち、電圧印加回路 4 の抵抗ユニット 2 側の電圧を DUT 1 の電源電圧 VDD 端子と同電位としたため、各動作ステップで、DUT 1 の出力端子（OUT）において出力論理が 0（出力電圧が低レベル）となる出力端子と、各動作ステップで出力状態になる DUT 1 の入出力端子（I/O）において出力論理が 0 となる入出力端子とに接続された、抵抗ユニット 2 を構成する各抵抗にだけ電流が流れる。そのため、電流測定回路 3 によって測定される電流値は、抵抗ユニット 2 を構成する 1 つの抵抗に流れる電流値に、前記の出力端子の数と入出力端子の数との和を乗算した値になる。

40

#### 【0056】

電流測定回路 3 によって測定された DUT 1 に関する電流値が、良品サンプルに関する電流値と異なる動作ステップが存在した場合は、その動作ステップにおける DUT 1 の論理 0 の端子の総数が、良品サンプルと異なることを意味し、それは良品サンプルと異なる出力論理の端子が存在し、DUT 1 が不良品であることを意味する。

#### 【0057】

50

例えば図2(B)に示す動作ステップ2において、9は良品サンプルでの電流パターンを示し、10はDUT1での電流パターンを示し、また動作ステップ4においては、11がDUT1での電流パターン、12が良品サンプルでの電流パターンを示す。動作ステップ2においては、DUT1での電流値が良品サンプルよりも大きくなっているが、これは動作ステップ2において、出力論理0の端子数が良品サンプルよりもDUT1の方が多くなっていることを意味し、また動作ステップ4においては、DUT1での電流値が良品サンプルよりも小さく、これは、動作ステップ4において出力論理0の端子数が良品サンプルよりもDUT1の方が少ないことを意味する。このように、電流パターンの違いから、この2つの動作ステップにおいて、DUT1が、良品サンプルと異なっていることが検出される。

10

#### 【0058】

以上のように、第1の実施の形態では、DUTの出力端子及び入出力端子の全てを、同一抵抗値の複数の抵抗をそれぞれ介して、電流測定回路を備えた電圧発生回路に接続し、所定の動作パターンの動作ステップ毎に、前記複数の抵抗を流れる電流値の総和を、DUTの良品サンプルにおける同電流値の総和と比較し、DUTの良品／不良品の判定を行う。これによって、従来のように、動作パターンの出力期待値を予めシミュレーションして求めることなしに、論理回路を含む半導体集積回路の良品／不良品の判定が可能となる。

#### 【0059】

なお、上記の第1の実施の形態において、後述の第2の実施の形態のように、DUTの出力端子及び入出力端子を複数のブロックに分割して、各ブロックごとに電流測定および比較を行うようにしてもよい。また、後述の第3の実施の形態のように、ブロック分割を繰り返してDUTの出力異常端子を絞り込むようにしてもよい。

20

#### 【0060】

##### 〔第2の実施の形態〕

第1の実施の形態においては、DUTに所定の動作パターンを入力し、これに応じて出力論理が0となったDUTの端子数を、良品サンプルに入力した同一の所定動作パターンに応じて出力論理が0となった端子数と、所定動作パターンの動作ステップ毎に比較して、DUTの良品／不良品の判定を行っている。

#### 【0061】

上記の端子数の比較は、具体的には、DUTの出力端子及び入出力端子（出力状態）にそれぞれ接続した抵抗に、動作ステップ毎の静止状態時に流れる電流の総和を、良品サンプルでの同電流の総和と比較することで、DUTの良否の判定を行っている。

30

#### 【0062】

ところで、第1の実施の形態では、出力論理が1になるべき出力端子（出力状態の入出力端子も含む）に出力論理0が出力され、また同時に、出力論理が0になるべき出力端子に出力論理1が出力され、かつ、それらの出力論理0が出力された端子数と、出力論理1が出力された端子数とが同数であった場合、このDUTは、本来不良と判定されるべきにも拘らず、良品と誤判定されてしまう。これは、DUTの出力端子及び入出力端子にそれぞれ接続された各抵抗の抵抗値が全て同一であるためであり、第2の実施の形態では、こうした上記の誤判定を防止するようにしたものである。

40

#### 【0063】

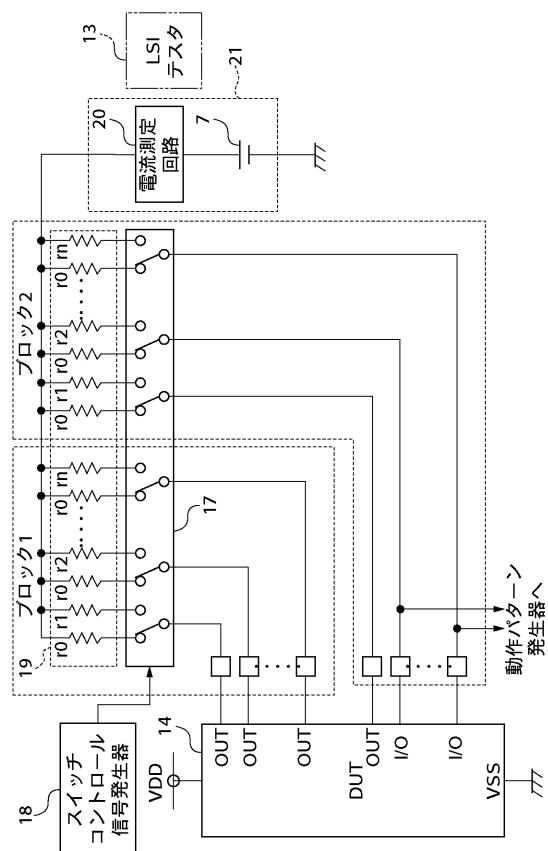

図3は、第2の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

#### 【0064】

図中14は、検査対象となる論理回路を含む半導体集積回路（DUT）であり、該DUT14の出力端子（OUT）及び入出力端子（I/O）の全てがスイッチ17および抵抗ユニット19を介して電圧印加回路21に接続される。抵抗ユニット19は、後述のブロックごとに、並列に接続された同じ抵抗値 $r_0$ のn個の抵抗と、互いに異なる抵抗値 $r_1 \sim r_n$ のn個の抵抗とを含み、該4n個の抵抗の各一端がスイッチ17の一方側各端子にそれぞれ接続され、各他端が短絡して電圧印加回路21に接続される。スイッチ17の他方側各端子は、DUT14の出力端子及び入出力端子にそれぞれ接続される。DUT14の

50

出力端子及び入出力端子、スイッチ 17 並びに抵抗ユニット 19 は、DUT14 の端子数 n ごとに分割され、例えば 2 つのブロック（ブロック 1, 2）にそれぞれ分割される。

#### 【0065】

スイッチ 17 は、リレーなどで構成され、スイッチコントロール信号発生器 18 からの信号に応じて、ブロック毎に 3 つの接続形態をとる。例えばブロック 1 を例に挙げて説明すると、第 1 の接続形態では、ブロック 1 に属する DUT14 の出力端子（OUT）を抵抗値  $r_0$  の n 個の抵抗にそれぞれ接続し、第 2 の接続形態では、ブロック 1 に属する DUT14 の出力端子を抵抗値  $r_1 \sim r_n$  の n 個の抵抗にそれぞれ接続し、第 3 の接続形態では、ブロック 1 に属する DUT14 の出力端子をいずれの抵抗にも接続しない。ブロック 2 でも同様な接続形態となるが、ブロック 2 では、ブロック 2 に属する DUT14 の端子が OUT 端子（OUT）及び入出力端子（I/O）になる点がブロック 1 とは異なっている。なおスイッチ 17 は、ブロック 1 とブロック 2 とで異なる接続形態を同時に選択することができる。

#### 【0066】

電圧印加回路 21 は、マイナス端が接地された直流電源 7 と、該直流電源 7 のプラス端と抵抗ユニット 19 との間に設けられた電流測定回路 20 とからなり、電圧印加回路 21 は、DUT14 の電源電圧 VDD 端子の電位と同電位を出力する。

#### 【0067】

第 2 の実施の形態における動作パターン発生器は、第 1 の実施の形態の動作パターン発生器と同一であり、DUT を構成部品の一つとする機械装置での使用に基づいて決まる所定の動作パターンを発生して、DUT14 の入力端子（図示を省略）および入出力端子（I/O）に出力する。なお、この所定の動作パターンも第 1 の実施の形態と同じく、論理シミュレーションにより出力期待値を予め求めておく必要がないものである。

#### 【0068】

電流測定回路 20 は、抵抗ユニット 19 の各抵抗に流れる電流の総和を測定する。なお、電流測定回路 20 を含む電圧印加回路 21、動作パターン発生器、及びスイッチコントロール信号発生器 18 は LS1 テスタ 13 で構成され、該 LS1 テスタ 13 は、電流測定回路 20 で得られた測定結果の保存、それらの比較、スイッチ 17 の動作制御等の情報処理・制御機能を備えている。

#### 【0069】

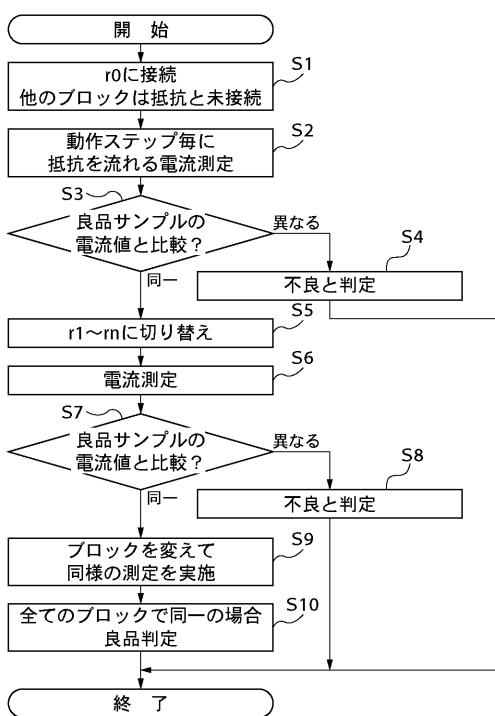

図 4 は、第 2 の実施の形態における LS1 テスタ 13 において実行される DUT に対する検査処理の手順を示すフローチャートである。

#### 【0070】

まずステップ S1 において、スイッチコントロール信号発生器 18 からスイッチ 17 に、ブロック 1 ではスイッチ 17 が第 1 の接続形態になるように、ブロック 2 ではスイッチ 17 が第 3 の接続形態になるように制御するスイッチコントロール信号を出力させる。これによって、DUT14 のブロック 1 における出力端子（OUT）が、スイッチ 17 を介して、抵抗ユニット 19 のブロック 1 における抵抗値  $r_0$  の各抵抗にそれぞれ接続され、一方、DUT14 のブロック 2 における出力端子（OUT）および入出力端子（I/O）は、スイッチ 17 を介して、いずれの抵抗にも接続されない。

#### 【0071】

ステップ S2 では、動作パターン発生器から DUT14 の入力端子（図 4 では図示を省略）及び入出力端子に所定の動作パターンを入力し、該所定の動作パターンの各動作ステップの静止状態時において、DUT14 の出力端子及び入出力端子（ブロック 2 の場合）にそれぞれ接続された抵抗ユニット 19 の各抵抗に流れる電流の総和を電流測定回路 20 で測定する。なお、電流測定回路 20 は、抵抗ユニット 19 を構成する各抵抗にそれぞれ流れる電流量を識別して検出可能な測定分解能を有するとともに、抵抗ユニット 19 を構成する各抵抗にそれぞれ流れる電流の総和をカバーできる測定レンジを有するものとする。

#### 【0072】

10

20

30

40

50

次にステップS3で、ステップS2で測定された動作ステップ毎の電流値を、DUT14に代わって良品サンプルを用いてステップS2と同様の手順で予め測定した動作ステップ毎の電流値と比較し、その結果、電流値が異なる動作ステップが存在した場合は、ステップS4へ進んで、DUT14は不良であると判定する。

#### 【0073】

一方、良品サンプルと電流値の異なる動作ステップが存在しない場合は、ステップS5へ進んで、スイッチコントロール信号発生器18からスイッチ17に、ブロック1ではスイッチ17が第2の接続形態になるように、ブロック2ではスイッチ17が第3の接続形態になるように制御するスイッチコントロール信号を出力させる。これによって、DUT14のブロック1における出力端子(OUT)が、スイッチ17を介して、抵抗ユニット19のブロック1における抵抗値 $r_1 \sim r_n$ の各抵抗にそれぞれ接続され、一方、DUT14のブロック2における出力端子(OUT)および入出力端子(I/O)は、スイッチ17を介して、いずれの抵抗にも接続されない。10

#### 【0074】

ステップS6では、ステップS2と同一の所定の動作パターンを動作パターン発生器からDUT14に入力し、該所定の動作パターンの各動作ステップの静止状態時において、DUT14の出力端子及び入出力端子(ブロック2の場合)にそれぞれ接続された抵抗ユニット19の各抵抗に流れる電流の総和を電流測定回路20で測定する。

#### 【0075】

次にステップS7で、ステップS6で測定された動作ステップ毎の電流値を、DUT14に代わって良品サンプルを用いてステップS6と同様の手順で予め測定した動作ステップ毎の電流値と比較し、その結果、電流値が異なる動作ステップが存在した場合は、ステップS8へ進んで、DUT14は不良であると判定する。20

#### 【0076】

一方、良品サンプルと電流値の異なる動作ステップが存在しない場合は、ステップS9へ進んで、他のブロックに対して、ステップS1～S8と同様の処理を実施する。すなわち、本実施の形態のようにブロックが2つ存在し、ブロック1に対してステップS1～S8の処理が実施された場合は、今度はブロック2に対してステップS1～S8と同様の処理が実施され、この場合は、ブロック1でスイッチ17が第3の接続形態になるように制御される。30

#### 【0077】

そして全てのブロックに対してステップS1～S8と同様の処理が実施された場合、次のステップS10に進んで、全てのブロックにおけるDUT14と良品サンプルとの測定結果が一致した場合は、DUT14が良品であると判定する。

#### 【0078】

かくして、出力論理が1になるべき出力端子に出力論理0が出力され、また同時に、出力論理が0になるべき出力端子に出力論理1が出力され、かつ、それらの出力論理0が出力された端子数と、出力論理1が出力された端子数とが同数であって場合、第1の実施の形態では、このDUTが、本来不良と判定されるべきにも拘らず、良品と誤判定されてしまう。しかし、こうした場合であっても、第2の実施の形態では、スイッチ17を第2の接続形態に制御することによって、DUTの出力端子及び入出力端子にそれぞれ接続される各抵抗の抵抗値を互いに異なる $r_1 \sim r_n$ に切り換えることができ、これによって、各抵抗を流れる電流量がそれぞれ異なることになる。したがって、端子数がDUTと良品サンプルとで同数であっても、各抵抗を流れる電流の総和はDUTと良品サンプルとで異なり、第2の実施の形態では、上記の誤判定を防止することができる。40

#### 【0079】

また逆に、各抵抗の抵抗値が互いに異なる場合の測定で、各抵抗を流れる電流の総和がDUTと良品サンプルとで同じであったとしても、各抵抗の抵抗値を互いに同一にした測定で、端子数がDUTと良品サンプルとで異なる場合(各抵抗を流れる電流の総和がDUTと良品サンプルとで異なる場合)には、DUTは不良品と判定する。50

**【0080】**

このように、第2の実施の形態では、各抵抗の抵抗値が同一の場合と互いに異なる場合との両方で、DUTの良品／不良品の判定を確実に行うことが可能となる。

**【0081】**

なお、抵抗ユニット19において各抵抗の抵抗値を互いに異ならせての電流測定では、抵抗値の高い抵抗に流れる電流値が小さくなる。所定の測定分解能と測定レンジとを備えた電流測定回路20が、抵抗値の最も高い抵抗に流れる最小の電流値を識別して検出するとともに、各抵抗を流れる電流の総和を測定できるためには、測定対象のDUTの端子数に制限を設ける必要がある。そのため、第2の実施の形態では、DUTの出力端子および入出力端子の全てを、複数のブロックに分けて、ブロック毎に測定を行っている。したがって、DUTの出力端子および入出力端子の全ての端子数から、分割すべきブロック数が決まる。ブロックに分割しなくても、電流測定回路20が、抵抗値の最も高い抵抗に流れる最小の電流値を識別して検出でき、かつ各抵抗を流れる電流の総和を測定できるならば、ブロックに分割する必要はない。10

**【0082】****〔第3の実施の形態〕**

次に第3の実施の形態を説明する。

**【0083】**

第3の実施の形態の構成は、基本的に第2の実施の形態の構成と同一であるので、第3の実施の形態の説明では、第2の実施の形態の構成を流用する。20

**【0084】**

第3の実施の形態では、図4に示す第2の実施の形態のフローチャートのステップS4またはステップS8で不良と判定されたDUTのブロックに対して、更にブロックの分割を繰り返して、不良となっている端子を絞り込むようにしている。

**【0085】**

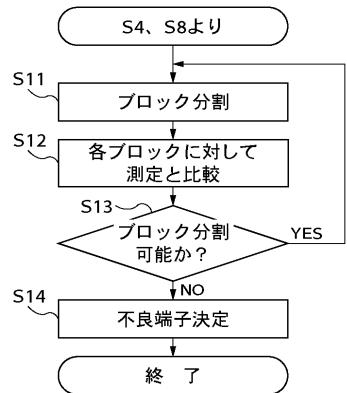

図5は、第3の実施の形態における不良端子の絞り込み手順を示すフローチャートである。

**【0086】**

このフローチャートは、図4に示す第2の実施の形態のフローチャートのステップS4またはステップS8の実行後に実行されるものである。30

**【0087】**

まずステップS11において、第2の実施の形態のステップS4またはステップS8で不良と判定されたDUTのブロックを複数のブロックに分割する。

**【0088】**

次のステップS12で、ステップS11で分割された各ブロックに対して、図4に示す第2の実施の形態のステップS1～S9と同様な電流測定および比較を行い、不良ブロックを特定する。

**【0089】**

ステップS13では、ステップS11で特定された不良ブロックが更に分割可能か否かを判別する。すなわち、該不良ブロック内にDUTの端子が複数存在してそれらを分割可能か否かを判別する。分割可能であればステップ11に戻り、分割不可能であればステップS14へ進んで、ステップS11で特定された不良ブロック内に含まれるDUTの端子に不良が存在すると決定する。40

**【0090】****〔第4の実施の形態〕**

第1の実施の形態において、電流測定回路3での測定精度(S/N比)を上げるために、抵抗ユニット2を構成する各抵抗の抵抗値を小さく設定して、各抵抗のうちの1つの抵抗において、対応のDUTの出力端子または入出力端子から論理出力1(高レベル出力)が出力されている時と、論理出力0(低レベル出力)が出力されている時に該1つの抵抗にそれぞれ流れる電流値の差を大きくすることが考えられるが、一方で、DUTの1端子あ50

たりの出力電流には制限があり、DUTによっては、測定に必要なS/N比にするための出力電流を得られない場合があり得る。また、DUTにおいて1端子あたりの出力電流は制限内であっても、出力端子及び入出力端子の全ての出力電流を大きくすると、DUTの消費電力の制限を越えてしまうために、出力電流を大きくできない場合が考えられる。

#### 【0091】

第4の実施の形態では、こうした問題を解決するようにしている。

#### 【0092】

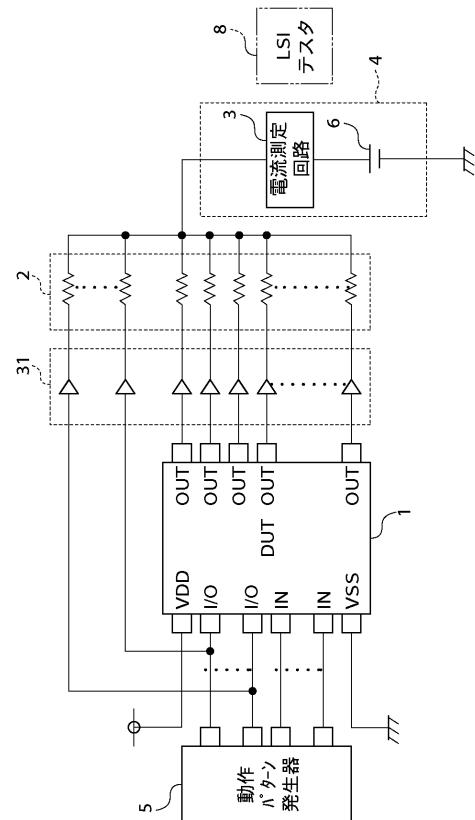

図6は、第4の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。

#### 【0093】

第4の実施の形態の構成は、基本的に第1の実施の形態の構成と同じであるので、同一構成部分には同一の参照符号を付して、その説明を省略する。

#### 【0094】

第4の実施の形態では、DUT1の出力端子(OUT)及び入出力端子(I/O)の全てと抵抗ユニット2との間にバッファユニット31が新たに設けられる。バッファユニット31は、DUT1の出力端子(OUT)及び入出力端子(I/O)の各々と個別に接続される複数のバッファから構成され、該複数のバッファは、抵抗ユニット2を構成する複数の抵抗とそれぞれ接続される。

#### 【0095】

バッファユニット31は、入力インピーダンスが高く、一方、出力インピーダンスが低く、また入力信号電圧を増幅して出力できる所定の出力能力を備えている。

#### 【0096】

バッファユニット31の入力インピーダンスが高いため、バッファユニット31に接続されるDUT1の出力端子及び入出力端子に対して負荷側からの影響がほとんどなく、また、DUT1の出力電流が小さくなるので、DUT1の消費電力が許容消費電力を超えることもない。

#### 【0097】

また、バッファユニット31の出力能力が高いので、DUT1の出力端子及び入出力端子に直接接続することができないような、DUT1の出力端子及び入出力端子の出力能力を超えさせてしまう抵抗値を持った抵抗を接続することが可能であり、これによって、論理出力1(高レベル出力)が出力されている時と、論理出力0(低レベル出力)が出力されている時に、抵抗ユニット2の1つの抵抗にそれぞれ流れる電流値の差を、バッファユニット31の出力能力の範囲内で大きくすることができる。

#### 【0098】

##### 〔第5の実施の形態〕

第1の実施の形態において、DUT1の出力端子及び入出力端子の各出力は、電流測定回路3が電流測定するタイミングに至るまでの期間、不安定な出力状態で推移するので、測定タイミングにおける抵抗ユニット2の各抵抗にそれぞれ流れる電流が互いに均一ではなく、また該各電流の合計量が時間的に均一ではなく、そのため各抵抗での発熱量が互いに均一ではなく、また抵抗ユニット2全体の発熱量が時間的に均一ではない。したがって、この発熱のために抵抗ユニット2の各抵抗の抵抗値が本来とは異なった値になっているとともに、互いに異なっている。また、抵抗ユニット2全体に流れる合計電流が時間的に均一でないため、電流測定回路3に流れる電流量も時間的に均一でなく、これによって、電流測定回路3自身の発熱量も時間的に一定ではない。そのため、電流測定回路3によって得られる測定値には、熱による誤差が含まれてしまう。かくして、第1の実施の形態では、電流測定回路3によって得られる測定値には、抵抗ユニット2の各抵抗の熱による相互の抵抗値の違いに起因する誤差と、電流測定回路3自身の熱による時間的な測定誤差との両方を含むことになる。

#### 【0099】

第5の実施の形態では、こうした問題を解決するようにしている。

10

20

30

40

50

**【0100】**

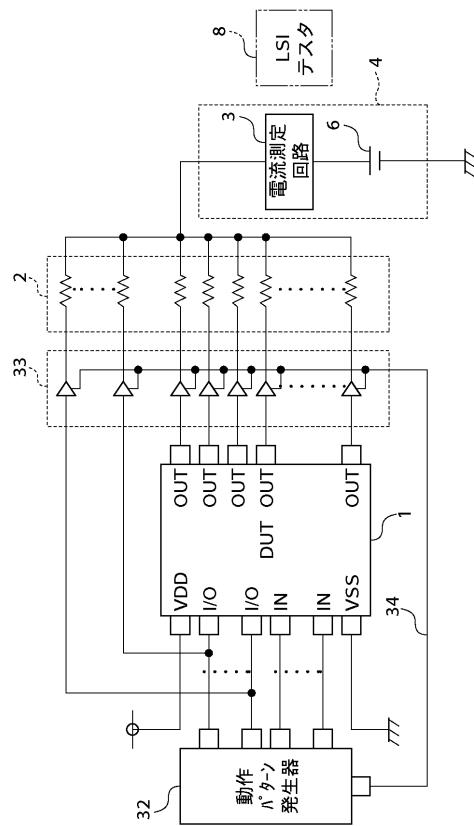

図7は、第5の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。

**【0101】**

第5の実施の形態の構成は、基本的に第1の実施の形態の構成と同じであるので、同一構成部分には同一の参照符号を付して、その説明を省略する。

**【0102】**

第5の実施の形態でも、第4の実施の形態と同様に、DUT1の出力端子(OUT)及び入出力端子(I/O)の全てと抵抗ユニット2との間にバッファユニット33が新たに設けられる。バッファユニット33は、DUT1の出力端子(OUT)及び入出力端子(I/O)の各々と個別に接続される複数のバッファから構成され、該複数のバッファは、抵抗ユニット2を構成する複数の抵抗とそれぞれ接続される。バッファユニット33は、入力インピーダンスが高く、一方、出力インピーダンスが低く、また入力信号電圧を増幅して出力できる所定の出力能力を備えている。10

**【0103】**

さらにバッファユニット33は、動作パターン発生器32からライン34を介して送られるON/OFF制御信号に応じて、バッファユニット33を構成する各バッファから同時に出力を行ったり、該出力を同時に停止(各バッファの出力インピーダンスを高くする)したりする機能を備える。

**【0104】**

動作パターン発生器32は、第1の実施の形態の動作パターン発生器5と同一の機能の他に、電流測定タイミング信号に同期してON/OFF制御信号を出力する機能を備える。20

**【0105】**

図8は、第5の実施の形態においてON/OFF制御信号に応じて抵抗ユニット2に流れれる電流パターンを示すタイミングチャートである。

**【0106】**

動作パターン発生器32は、所定の動作パターン(A)をDUT1に出力すると同時に、ON/OFF制御信号(C)をバッファユニット33へ出力する。ON/OFF制御信号のON期間は、所定の動作パターン(A)を入力されたDUT1が、各動作ステップにおいて比較的安定した電流パターン(B)を出力できる期間に設定され、このON期間において、DUT1からの出力論理信号に基づいた電流(電流パターン)が抵抗ユニット2に流れれる。この電流量を電流測定回路3が測定する。30

**【0107】**

ON/OFF制御信号のOFF期間には、抵抗ユニット2に全く電流が流れない。このため、OFF期間には、抵抗ユニット2や電流測定回路3で被測定電流に基づく発熱が発生せず、発熱に起因する電流測定回路3での電流測定値の誤差は解消され、抵抗ユニット2に流れれる電流の総和に関するDUT1と良品サンプルとの比較をより精度良く行うことができる。

**【0108】****[第6の実施の形態]**

第3の実施の形態においては、不良判定となったDUTの出力異常端子を絞り込むために、DUT1と抵抗ユニット2を構成する各抵抗とをそれぞれ個別に接続できるスイッチ17を設けるとともに、抵抗ユニット2に、互いに異なる抵抗値の複数の抵抗を追加し、DUT1に接続すべき抵抗ユニット2の各抵抗をスイッチ17で個別に選択できるようにしているが、この第3の実施の形態の構成では、回路規模が大きくなってしまうという問題がある。

**【0109】**

第6の実施の形態では、こうした問題を解決するようにしている。

**【0110】**

10

20

30

40

50

図9は、第6の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。

#### 【0111】

第6の実施の形態の構成は、基本的に第1の実施の形態の構成と同じであるので、同一構成部分には同一の参照符号を付して、その説明を省略する。

#### 【0112】

第6の実施の形態でも、第4の実施の形態と同様に、DUT1の出力端子(OUT)及び入出力端子(I/O)の全てと抵抗ユニット2との間にバッファユニット36が新たに設けられる。バッファユニット36は、DUT1の出力端子(OUT)及び入出力端子(I/O)の各々と個別に接続される複数のバッファから構成され、該複数のバッファは、抵抗ユニット2を構成する複数の抵抗とそれぞれ接続される。バッファユニット36は、10 入力インピーダンスが高く、一方、出力インピーダンスが低く、また入力信号電圧を增幅して出力できる所定の出力能力を備えている。

#### 【0113】

さらにバッファユニット36は、動作パターン発生器35から複数のライン37を介してそれぞれ送られる各ON/OFF制御信号に応じて、バッファユニット36を構成する各バッファから個別に出力を行ったり、該出力を停止したりする機能を備える。

#### 【0114】

動作パターン発生器35は、第1の実施の形態の動作パターン発生器5と同一の機能の他に、電流測定タイミング信号に同期して各ON/OFF制御信号を、バッファユニット36の各バッファに個別に出力する機能を備える。20

#### 【0115】

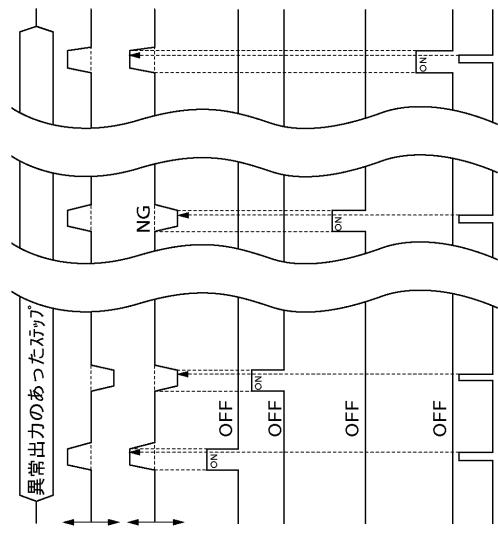

図10は、第6の実施の形態において各ON/OFF制御信号に応じて抵抗ユニット2に流れる電流パターンおよび出力異常端子の絞込みを示すタイミングチャートである。

#### 【0116】

まず、第5の実施の形態と同様に、各ON/OFF制御信号を同一の信号形態にして、バッファユニット36の各バッファに対して、所定の動作パターンの動作ステップ毎に、同時に出力して、DUT1での電流パターンを良品サンプルでの電流パターンと比較する。この結果、ある動作ステップで電流パターンが異なっていた場合、この動作ステップにおいて、出力異常端子の絞込みを次のように行う。30

#### 【0117】

動作パターン発生器35は、電流パターンが異なっていた動作ステップを動作パターン(A)として出力しながら、ON状態のON/OFF制御信号をバッファユニット36の各バッファに対して順に出力する((D)～(G))。このON状態のON/OFF制御信号を出力されているバッファ以外の残りのバッファにはOFF状態のON/OFF制御信号を出力する。そして、ON状態のON/OFF制御信号を出力されているバッファに接続された抵抗にのみ流れる電流を電流測定回路3で測定して、該測定値(C)を、同じ状態で予め得られた良品サンプルの測定値(B)と比較して、ON状態のON/OFF制御信号を出力しているバッファに接続されたDUTの端子に対する出力異常判別を行う。40

#### 【0118】

図10(C)にマーク「NG」で示すように、DUT1での電流パターン(C)と良品サンプルでの電流パターン(B)とが異なる値となった時、ON状態のON/OFF制御信号を出力しているバッファを特定することにより、該バッファに接続されているDUT1の出力端子もしくは入出力端子を出力異常端子と特定することができる。

#### 【0119】

この特定方法では、DUT1に所定の動作パターンを何度も入力する必要は無く、DUT1と良品サンプルとの各測定値が異なった動作ステップに入った状態を維持したまま、動作パターン発生器35から出力するON/OFF制御信号を操作するだけでよいため、出力異常端子を特定するまでの所要時間の短縮を図ることができる。50

**【0120】****〔第7の実施の形態〕**

第7の実施の形態の構成は、基本的に第1の実施の形態の構成と同じであるので、第7の実施の形態の説明では、第1の実施の形態の構成を流用する。

**【0121】**

第7の実施の形態では、抵抗ユニット2が、異なる抵抗値をもった各抵抗から構成される他の抵抗ユニットと交換可能であり、また、電流測定回路3の測定レンジを変更可能であるものとする。また、LSIテスト8によって行われる検査処理が第1の実施の形態と異なっている。

**【0122】**

第7の実施の形態では、良品サンプルに対して、所定の動作パターンの全動作ステップに亘って電流測定を行い、得られた動作ステップ毎の電流量の総和の内、最大電流値と最小電流値と求め、これらの最大電流値と最小電流値とを基に、最大電流値と最小電流値とをそれぞれ中心として所定幅を持った2つの判定基準ゾーンを作成する。次に、DUTに対して同様に、所定の動作パターンの全動作ステップに亘って電流測定を行い、得られた動作ステップ毎の電流量の総和の内、最大電流値と最小電流値とを求め、これらの最大電流値と最小電流値とが、上記の2つの判定基準ゾーン内にそれぞれ収まるか否かを判別して、DUTに対する良品／不良品の判定を行う。

**【0123】**

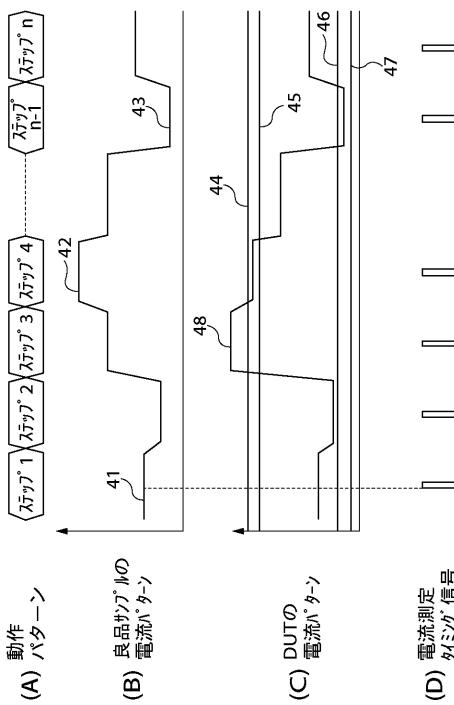

図11は、第7の実施の形態における判定基準ゾーンを含む電流パターンを示すタイミングチャートである。

**【0124】**

図中41は、(A)に示す所定の動作パターンの動作ステップ1における良品サンプルから得られる電流値であり、電流測定回路3によって測定された電流値である。(B)に示す42は、良品サンプルの全動作ステップに亘る電流パターンの中で最大電流値を示し、43は、良品サンプルの全動作ステップに亘る電流パターンの中で最小電流値を示す。(C)に示す44は、最大電流値42を基に決定された最大電流値判定基準ゾーンの上限値を示し、45は、最大電流値判定基準ゾーンの下限値を示す。46は、最小電流値43を基に決定された最小電流値判定基準ゾーンの上限値を示し、47は、最小電流値判定基準ゾーンの下限値を示す。

**【0125】**

最大電流値判定基準ゾーンの上限値44は、良品サンプルの最大電流値42に、抵抗ユニット2の1つの抵抗を流れる電流値の50%を加えた値であり、最大電流値判定基準ゾーンの下限値45は、良品サンプルの最大電流値42から、抵抗ユニット2の1つの抵抗を流れる電流値の50%を減じた値である。最小電流値判定基準ゾーンの上限値46は、良品サンプルの最小電流値43に、抵抗ユニット2の1つの抵抗を流れる電流値の50%を加えた値であり、最小電流値判定基準ゾーンの下限値47は、良品サンプルの最小電流値43から、抵抗ユニット2の1つの抵抗を流れる電流値の50%を減じた値である。

**【0126】**

例えば、DUTに対して実施した電流測定で得られた電流パターン(C)における48は、全動作ステップの中の最大電流値を示す。この最大電流値48は、最大電流値判定基準ゾーンの上限値44を超えており、DUTは不良品と判定する。

**【0127】**

また同様に、DUTにおける最大電流値が最大電流値判定基準ゾーンの下限値45を下回る場合、DUTにおける全動作ステップの中の最小電流値が最小電流値の判定基準の上限値46を超える場合、DUTにおける最小電流値が最小電流値判定基準ゾーンの下限値47を下回る場合も、DUTを不良品と判定する。

**【0128】**

以上のように、判定基準ゾーンを利用して簡易的にDUTの良品／不良品の選別を行う。これを「第1次選別」とする。

10

20

30

40

50

**【0129】**

次に、第1の実施の形態と同様に、電流パターンを動作ステップ毎に良品サンプルとDUTとで比較してDUTの良品／不良品の選別を行う「第2次選別」を実施するが、その前に、電流測定回路3の測定レンジに対する最適設定と、抵抗ユニット2の各抵抗の抵抗値に対する最適設定を行う。

**【0130】**

第2次選別は、第1の実施の形態で説明したように、所定の動作パターンの動作ステップ毎に出力論理0となる端子数を電流値に変換して、良品／不良品を選別する方法であることから、電流測定回路3は、DUTの電流の流れる端子の総数が1つでも異なった場合の電流差を検出できる分解能が必要である一方、全動作ステップの中での最大電流値が測定できる電流測定レンジを持つ必要がある。10

**【0131】**

ところで、抵抗ユニット2を構成する各抵抗の抵抗値を小さく設定して、各抵抗にそれぞれ流れる電流値を大きくすると、電流の流れる端子数の違いによる電流差も大きくなるが、全動作ステップの中での最大電流値も大きくなり、電流測定回路4の電流測定レンジも大きくする必要がある。電流測定レンジを大きくした場合、電流測定回路4の最小分解能が大きくなってしまう。また、測定対象のDUTの端子数が多い場合も電流測定レンジを大きくする必要がある。

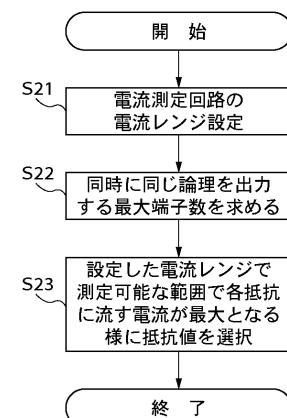

**【0132】**

図12は、電流測定回路4の最適な電流測定レンジを設定し、また抵抗ユニットの各抵抗の最適な抵抗値を選択するための処理の手順を示すフローチャートである。この処理は、情報処理機能を備えたLSIテスタ8によって実行されるが、その一部をLSIテスタ8の利用者が行うようにしてもよい。20

**【0133】**

まずステップS21において、第1次選別で得た良品サンプルの全動作ステップの中での最大電流値42を基に、電流測定回路4の電流測定レンジを、最大電流値42を測定できる条件下で測定レンジが最も低くなるように設定する。

**【0134】**

次にステップS22で、良品サンプルの最大電流値42を基に、良品サンプルにおいて全動作ステップの中で、出力論理が同時に0となる端子の数が最大となる場合の端子数を求める。30

**【0135】**

ステップS23では、ステップS22で求めた最大端子数を基に、ステップS21で設定した電流測定レンジで測定可能な範囲で、抵抗ユニット2を構成する各抵抗に流れる電流値が最大となるような抵抗値を持った抵抗ユニットを抵抗ユニット2用に選択する。

**【0136】**

このようにして設定された電流測定レンジを備えた電流測定回路3と、各抵抗が上記のように選択された抵抗値を持った抵抗ユニット2とを用いて、第2次選別を行う。

**【0137】**

これにより、まず第1次選別を行うことで、最大電流値または最小電流値が良品サンプルと異なるDUTについては、簡易にDUTの良品／不良品の判定ができる、第2次選別の実行を省略でき、検査時間を短縮することができる。40

**【0138】**

また、第2次選別では、電流測定回路3の電流測定レンジの最適化と、抵抗ユニット2を構成する各抵抗の抵抗値の最適化とを前もって行うので、DUTの良品／不良品の判定をより精度よく行うことができる。

**【0139】**

なお、第7の実施の形態では、良品サンプルにおける最大電流値および最小電流値を検出して、それらから作成された最大電流値判定基準ゾーンおよび最小電流値判定基準ゾーンを用いて、DUTの良品／不良品の判定を行っているが、これに代わって、良品サンプ50

ルにおける最大電流値または最小電流値を検出して、それから作成された最大電流値判定基準ゾーンまたは最小電流値判定基準ゾーンを用いて、D U T における最大電流値または最小電流値を対応の判定基準ゾーンと比較することによって D U T の良品 / 不良品の判定を行うようにしてもよい。

#### 【 0 1 4 0 】

##### 〔 第 8 の実施の形態 〕

第 8 の実施の形態の半導体集積回路検査装置では、被検査 I C ( 半導体集積回路 ) と同じ機能を持ち正常に動作する標準 I C ( 良品サンプル ) を、被検査 I C に対して対に並べて検査を行う。

#### 【 0 1 4 1 】

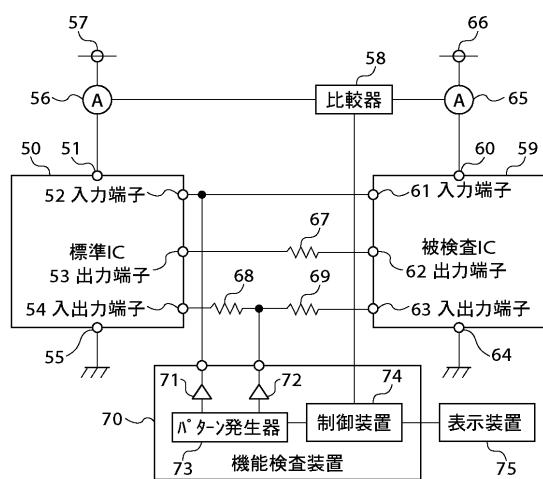

図 13 は、第 8 の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

#### 【 0 1 4 2 】

標準 I C 5 0 は、被検査 I C 5 9 と同じ機能をもった検査の基準となる I C であり、D C 及び A C の電気特性や機能が正常であって、予め良品サンプルとして確認されたものである。なお、標準 I C 5 0 の実際の端子は多数存在するが、図 13 では、入力端子 5 2 、出力端子 5 3 、入出力端子 5 4 を代表例として説明する。被検査 I C 5 9 も同様である。

#### 【 0 1 4 3 】

標準 I C 5 0 の入力端子 5 2 は、被検査 I C 5 9 の入力端子 6 1 及び機能検査装置 7 0 のドライバ 7 1 へ接続され、出力端子 5 3 は、被検査 I C 5 9 の出力端子 6 2 へ抵抗器 6 7 を介して接続される。

#### 【 0 1 4 4 】

標準 I C 5 0 の入出力端子 5 4 は、被検査 I C 5 9 の入出力端子 6 3 に抵抗器 6 8 と抵抗器 6 9 とを介して接続される。抵抗器 6 8 と抵抗器 6 9 との接続点には機能検査装置 7 0 のドライバ 7 2 が接続される。

#### 【 0 1 4 5 】

ドライバ 7 1 , 7 2 は、パターン発生器 7 3 から被検査 I C 5 9 の機能検査のためのパターン信号を入力される。

#### 【 0 1 4 6 】

次に、標準 I C 5 0 、被検査 I C 5 9 の電源端子 5 1 、電源端子 6 0 に電流計 5 6 、電流計 6 5 をそれぞれ介して、機能検査装置 7 0 より供給される電源 5 7 、電源 6 6 をそれぞれ接続する。

#### 【 0 1 4 7 】

電流計 5 6 、電流計 6 5 での検出値は比較器 5 8 へそれぞれ送られ、比較器 5 8 は、2 つの検出値の絶対値の差を所定のレベルと比較し、その結果を制御装置 7 4 へ送るようにする。

#### 【 0 1 4 8 】

制御装置 7 4 は、比較器 5 8 の結果から被検査 I C 5 9 の良否を判定して、その判定結果を表示装置 7 5 へ送る。2 つの検出値の絶対値の差が所定のレベルを超えていたり、被検査 I C 5 9 は不良品と判定される。

#### 【 0 1 4 9 】

次に、動作について説明する。

#### 【 0 1 5 0 】

初めに、機能検査装置 7 0 のパターン発生器 7 3 から、被検査 I C 5 9 を検査するためのパターン信号をドライバ 7 1 , 7 2 へ送り、該パターン信号がドライバ 7 1 , 7 2 から入力端子 5 2 、入力端子 6 1 、及び入力状態の入出力端子 5 4 、入出力端子 6 3 に対して送られる。これによって、標準 I C 5 0 及び被検査 I C 5 9 は動作を開始し、入力パターン信号の各動作ステップ ( ベクター ) に従った出力を始める。

#### 【 0 1 5 1 】

標準 I C 5 0 及び被検査 I C 5 9 の各出力端子及び入出力端子同士は、抵抗器を介して

10

20

30

40

50

ショート状態にあり、もし被検査 I C 5 9 に欠陥があり正常な信号を出力しない場合、標準 I C 5 0 から被検査 I C 5 9 へ、もしくは被検査 I C 5 9 から標準 I C 5 0 へ、抵抗器 6 7 や抵抗器 6 8、6 9 を介して出力電流が流れる。

#### 【 0 1 5 2 】

この出力電流の電流値は、「高レベル」を出力している端子の電圧から、「低レベル」を出力している端子の電圧を減算し(こうして得られた値は通常、電源電圧とほぼ等しい値に相当)、この電圧を抵抗器 6 7 の抵抗値で除算した値、あるいは抵抗器 6 8 の抵抗値と抵抗器 6 9 の抵抗値との和で除算した値となる。

#### 【 0 1 5 3 】

そして上記の出力電流は、標準 I C 5 0 から被検査 I C 5 9 へ、またはその逆方向に流れるので、2つの I C の電源端子 5 1, 6 0 に流れる電流量に差が生じることになる。 10

#### 【 0 1 5 4 】

この2つの I C の電源端子 5 1, 6 0 に流れる電流量を、電流計 5 6、電流計 6 5 で検出し、比較器 5 8 が、2つの電流量の差の絶対値を所定値と比較する。そして比較器 5 8 は、2つの電流量の差の絶対値が所定値以上である場合には、比較器 5 8 より制御装置 7 4 へ信号を送り、被検査 I C 5 9 を不良品と判定して表示装置 7 5 へ検査結果を表示させる。

#### 【 0 1 5 5 】

なお、入出力端子 5 4、入出力端子 6 3 が出力状態の時、入出力端子 6 3 がハイインピーダンスになる不良の場合、入出力端子 6 3 に電流が流れないので、入出力端子 5 4 にも電流が流れず、したがって比較器 5 8 で電流差は検出されない。そこで、パターン発生器 7 3 が、出力論理と反対の論理の出力をドライバ 7 2 に出力させ、入出力端子 5 4 に電流が流れるようにして、比較器 5 8 で電流差が検出できるようにする。これによって、入出力端子 6 3 がハイインピーダンスになる不良でも、該不良を検出できるようとする。 20

#### 【 0 1 5 6 】

また、入出力端子 5 4、入出力端子 6 3 がハイインピーダンス状態の時は、パターン発生器 7 3 がドライバ 7 2 を、パターン信号の1動作ステップ(ベクター)内で「高レベル」、「低レベル」に切り替え、どちらのレベルでも比較器 5 8 で電流差が検出できないとき、入出力端子 5 4、入出力端子 6 3 がともにハイインピーダンス状態であるとする。

#### 【 0 1 5 7 】

同様に、被検査 I C 5 9 の出力端子 6 2 がハイインピーダンス(H i - Z もしくは、3-state)機能を持つ場合も、上記の入出力端子 6 3 での検出方法と同じ方法でハイインピーダンスの状態を検出する。 30

#### 【 0 1 5 8 】

なお、上記の第8の実施の形態では、電源端子 5 1 や電源端子 6 0 の側に電流計 5 6、電流計 6 5 を接続しているが、電流計を GND 端子 5 5、GND 端子 6 4 の側へ接続したり、電源端子及び GND 端子の両側へ挿入するようにして、精度の高い検査を行うようにしてもよい。

#### 【 0 1 5 9 】

また、電流計 5 6、電流計 6 5 を、ピーク値を検出タイプの電流形で代えたり、電流波形を積分するタイプの電流形で代えたりすることも可能である。 40

#### 【 0 1 6 0 】

##### 〔 第9の実施の形態 〕

第9の実施の形態では、パターン発生器が、被検査 I C (半導体集積回路)の出力論理の期待値を出力し、該パターン発生器を、被検査 I C に対して対にして並べて検査を行う。

#### 【 0 1 6 1 】

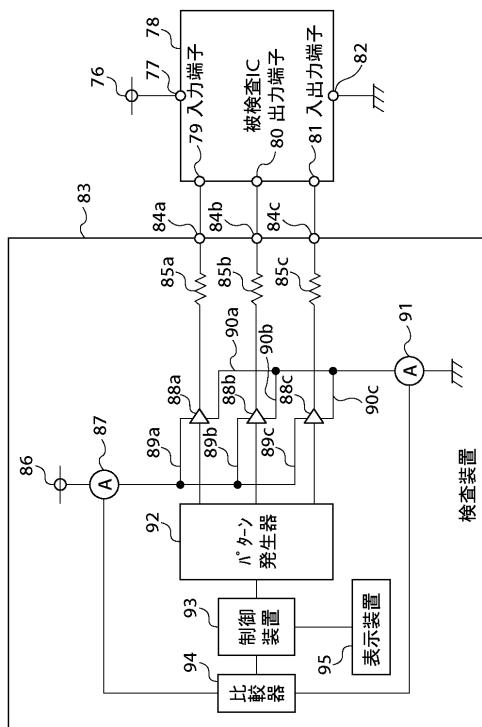

図14は、第9の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

#### 【 0 1 6 2 】

被検査 I C 7 8 の電源端子 7 7 は、検査装置 8 3 より供給される電源 7 6 へ接続され、 50

GND端子82はGNDへ接地される。被検査IC78の入力端子79、出力端子80、入出力端子81は、検査装置83の出力端子84a～84cへそれぞれ接続させる。

**【0163】**

出力端子84a～84cは、抵抗器85a～85cをそれぞれ介してドライバ88a～88cへ接続される。ドライバ88a～88cの電源端子89a～89cはまとめて電流計87を介して電源86へ接続される。電源86は、被検査IC78の電源76の電圧と同じ電圧に設定される。

**【0164】**

ドライバ88a～88cのGND端子90a～90cはまとめて電流計91を介してGNDへ接地される。

10

**【0165】**

ドライバ88a～88cにはパターン発生器92から被検査IC78の機能検査のためのパターン信号が入力される。このパターン信号は、機能検査のための入力論理とその時の出力論理の期待値とから構成される。

**【0166】**

パターン発生器92は、制御装置93で制御される。電流計87、電流計91の検出値は比較器94へ送られ、比較器94は、2つの検出値の少なくとも一方を所定レベルと比較し、その結果を制御装置93へ送る。

**【0167】**

制御装置93は、比較器94からの比較結果から被検査IC78の良否を判定して、その判定結果を表示装置95へ送る。2つの検出値の少なくとも一方が所定レベルを超えていれば、被検査IC78が不良品と判定される。

20

**【0168】**

次に動作について説明する。

**【0169】**

初めに、検査装置83のパターン発生器92が、被検査IC78を検査するためのパターン信号をドライバ88a、ドライバ88cを介して被検査IC78の入力端子79や入出力端子81へ出力する。このパターン信号を受け取った被検査IC59は動作を開始し、入力パターン信号に従った出力を始める。

**【0170】**

30

被検査IC78の出力端子80及び入出力端子81は、抵抗器85b、抵抗器85cをそれぞれ介して検査装置83のドライバ88b、ドライバ88cとショート状態にあるので、もし被検査IC78に欠陥があって正常な信号を出力しない場合、検査装置83のドライバ88b、ドライバ88cから被検査IC78へ、もしくは被検査IC78からドライバ88b、ドライバ88cへ、抵抗器85b、抵抗器85cを介して電流が流れる。

**【0171】**

被検査IC78が良品である場合、ドライバ88bの出力と被検査IC78の出力端子80の信号、あるいはドライバ88cの出力と入出力端子81の信号とは、レベルが一致していて、電流計87、電流計91には、ドライバ88a～88cがスイッチングする時の瞬間的な貫通電流以外の電流はほとんど流れない。

40

**【0172】**

しかし、被検査IC78が不良品である場合には、ドライバ88bやドライバ88cが電流をソースあるいはシンクするので、電流計87、電流計91のいずれか、又は両方に大きな電流が流れることになる。

**【0173】**

比較器94が、電流計87、電流計91で検出した2つの電流値を所定値（電源電圧を抵抗器85bまたは抵抗器85cの抵抗値で除算して得られた電流値に相当）と比較し、その比較結果を制御装置93へ送る。制御装置93は、2つの電流値が所定値以上であるという比較結果ならば、被検査IC78を不良品と判定して、表示装置95にその判定結果を表示させる。

50

## 【0174】

なお、被検査IC78の入出力端子81がハイインピーダンス状態であることが疑われる場合は、パターン発生器92が、ドライバ88cをパターン信号の1動作ステップ(1ベクター)内で「高レベル」、「低レベル」に切り替える。これらのどちらのレベルでも電流計87、電流計91に電流が流れないことによって、入出力端子81のハイインピーダンス状態を確認することができる。

## 【0175】

同様に、被検査IC78の出力端子80がハイインピーダンス(Hi-Zもしくは、3-state)機能を持つ場合も、入出力端子81に対する上記のレベル切換と同じ方法によって、出力端子80のハイインピーダンスの状態を確認することができる。

10

## 【0176】

なお、抵抗器85aは、出力端子84a～84cと同じ回路構成となるように挿入しているが、特に必要が無ければ省略してもよい。

## 【0177】

また、第9の実施の形態では、ドライバ88a～88cの電源端子89a～89c、GND端子90a～90cをそれぞれまとめて電流計87、電流計91へ接続しているが、これに代わって、ドライバ88a～88cの各々に電流計を用意したり、ドライバ88a～88cの各々に、電流計87、電流計91を接続する、しないを選択可能にしてもよい。これによって、被検査IC78の各端子毎の特性をより高い精度で検査することも可能となる。

20

## 【0178】

また、第9の実施の形態では、ドライバ88bと出力端子80との間に抵抗器85bを挿入しているが、この抵抗器85bをコンデンサなど他の部品や回路で代えることが可能である。また、電流計87、電流計91を、ピーク値を検出タイプの電流形で代えたり、電流波形を積分するタイプの電流形で代えたりすることも可能である。

## 【0179】

## 〔第10の実施の形態〕

第10の実施の形態は、第9の実施の形態の半導体集積回路検査装置の入出力端子の検査方法を発展させたものである。

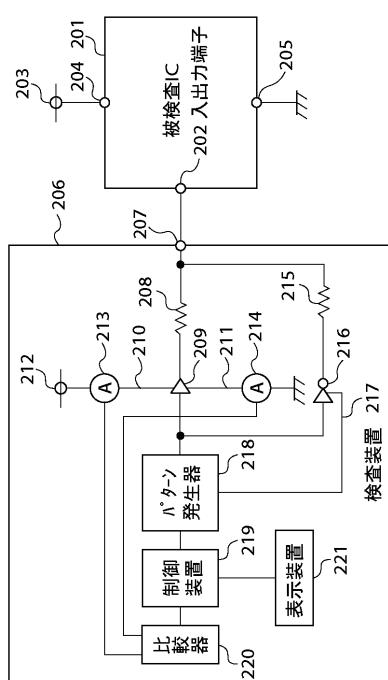

## 【0180】

30

図15は、第10の実施の形態における半導体集積回路の入出力端子用の検査装置の構成を示すブロック図である。

## 【0181】

被検査IC201の電源端子204は電源203へ接続され、GND端子205はGNDへ接地される。被検査IC201の入出力端子202は検査装置206の出力端子207へ接続させる。

## 【0182】

出力端子207は抵抗器208を介してドライバ209へ接続され、ドライバ209はパターン発生器218へ接続される。パターン発生器218は、被検査IC201の機能検査のためのパターン信号をドライバ209に出力する。このパターン信号は、被検査IC201の機能検査のための入力パターン及びこの入力パターンに応じて被検査IC201が正常であれば出力するだろう期待値を含む。

40

## 【0183】

ドライバ209の電源端子210は、電流計213を介して電源212へ接続される。電源212は、被検査IC201の電源203の電圧と同じ電圧に設定される。ドライバ209のGND端子211は電流計214を介してGNDへ接地される。

## 【0184】

また、出力端子207は抵抗器215へも接続され、抵抗器215はハイインピーダンス検査用ドライバ216へ接続される。ハイインピーダンス検査用ドライバ216はパターン発生器218へ接続され、パターン発生器218に接続されたドライバ209が出力

50

する論理信号に対して反転した論理信号（負論理の出力信号）を出力する。

**【0185】**

なお、ハイインピーダンス検査用ドライバ216には出力イネーブル端子217を設け、この出力イネーブル端子217にパターン発生器218から、パターン信号に応じてイネーブル信号およびディセーブル信号が入力される。ハイインピーダンス検査用ドライバ216は、イネーブル信号が入力されると出力状態になり、ディセーブル信号が入力されるとハイインピーダンス状態になって出力しない状態になる。

**【0186】**

パターン発生器218は制御装置219で制御される。

**【0187】**

電流計213、電流計214の検出値は比較器220へ送られ、比較器220は、2つの検出値の少なくとも一方を所定値と比較し、その比較結果を制御装置219へ送る。制御装置219は、2つの検出値の少なくとも一方が所定値を超えていれば、被検査IC201が不良品であると判定し、その判定結果を表示装置221へ送り、表示させる。

**【0188】**

なお、図15では被検査IC201に1端子だけの入出力端子202を図示するが、実際には入出力端子は複数存在し、ドライバおよびハイインピーダンス検査用ドライバも各入出力端子に対応して複数存在し、複数のドライバは、図14に示す第9の実施の形態のように、電流計213、電流計214に接続される。

**【0189】**

次に動作について説明する。

**【0190】**

被検査IC201の入出力端子202が入力状態もしくはハイインピーダンス状態を疑われる時は、パターン発生器218が、ハイインピーダンス検査用ドライバ216の出力イネーブル端子217にディセーブル信号を出力して、ハイインピーダンス検査用ドライバ216の出力をハイインピーダンス状態にする。

**【0191】**

そしてパターン発生器218は、被検査IC201の入出力端子202が入力状態であれば、ドライバ209を介して被検査IC201へパターン信号を出力する。また、被検査IC201の入出力端子202がハイインピーダンス状態を疑われる場合は、ドライバ209の出力を「高レベル」、「低レベル」に切り替えて、どちらのレベルでも電流計213、214に電流が流れないことからハイインピーダンス状態を確認する。

**【0192】**

以上の動作は第9の実施の形態の場合と同じである。

**【0193】**

次に被検査IC201の入出力端子202が出力状態へ変わった時、パターン発生器218はハイインピーダンス検査用ドライバ216の出力イネーブル端子217にイネーブル信号を出力して、ハイインピーダンス検査用ドライバ216を出力状態にする。この出力状態になったハイインピーダンス検査用ドライバ216は、パターン発生器218から送られたパターン信号を反転して出力するので、ドライバ209の出力論理に対して反転した負論理（反対の出力信号）を出力する。

**【0194】**

もし、被検査IC201の入出力端子202の出力が「高レベル」で、期待値も「高レベル」であるとすると、ドライバ209の出力も「高レベル」であり、抵抗器208に電流は流れない。しかしこのとき、ハイインピーダンス検査用ドライバ216は「低レベル」を出力するので、入出力端子202との間に電位差が生じて、入出力端子202から抵抗器215を介してハイインピーダンス検査用ドライバ216側へ電流が流れる。なお、ドライバ209も「高レベル」を出力しているが、抵抗器208が介在するので、ドライバ209からハイインピーダンス検査用ドライバ216側へ電流はほとんど流れない。ドライバ209にほとんど電流が流れないので、被検査IC201は良品と判定される。

10

20

30

40

50

**【 0 1 9 5 】**

次に、被検査 I C 2 0 1 の入出力端子 2 0 2 の期待値が「高レベル」であるのに、入出力端子 2 0 2 がハイインピーダンス状態となる不良について、以下に説明する。

**【 0 1 9 6 】**

もし、パターン発生器 2 1 8 が、ハイインピーダンス検査用ドライバ 2 1 6 の出力イネーブル端子 2 1 7 にディセーブル信号を出力していて、ハイインピーダンス検査用ドライバ 2 1 6 の出力がハイインピーダンス状態になっている場合、被検査 I C 2 0 1 の入出力端子 2 0 2 の期待値が「高レベル」、すなわち、ドライバ 2 0 9 の出力が「高レベル」であり、このとき、入出力端子 2 0 2 がハイインピーダンス状態であるとすると、抵抗器 2 0 8 には電流が流れず、入出力端子 2 0 2 がハイインピーダンス状態となる不良を検出できない。つまり、ハイインピーダンス検査用ドライバ 2 1 6 が存在しないような、第 9 の実施の形態の装置では、入出力端子 2 0 2 がハイインピーダンス状態となる不良を検出できないことがわかる。10

**【 0 1 9 7 】**

そこで第 1 0 の実施の形態ではこうした場合に、パターン発生器 2 1 8 が、ハイインピーダンス検査用ドライバ 2 1 6 の出力イネーブル端子 2 1 7 にイネーブル信号を出力していて、出力イネーブル端子 2 1 7 を出力状態にする。そのため、ハイインピーダンス検査用ドライバ 2 1 6 は、ドライバ 2 0 9 の出力が「高レベル」であるので、「低レベル」を出力する。このとき、入出力端子 2 0 2 がハイインピーダンス状態になっているならば、「高レベル」であるドライバ 2 0 9 から抵抗器 2 0 8 、抵抗器 2 1 5 を介してハイインピーダンス検査用ドライバ 2 1 6 へ電流が流れ込む。この電流が電流計 2 1 3 によって検出されるので、被検査 I C 2 0 1 が不良であると判定され、入出力端子 2 0 2 がハイインピーダンス状態となる不良が検出され得る。20

**【 0 1 9 8 】**

なお、第 1 0 の実施の形態において比較器 2 2 0 で用いる比較基準としての所定値は、第 9 の実施の形態と異なり、電源 2 1 2 の電源電圧を、抵抗器 2 0 8 の抵抗値と抵抗器 2 1 5 の抵抗値との和で除算して得た値である。

**【 0 1 9 9 】**

以上の説明では、被検査 I C 2 0 1 の入出力端子 2 0 2 の期待値が「高レベル」であり、入出力端子 2 0 2 がハイインピーダンス状態の不良である場合であったが、被検査 I C 2 0 1 の入出力端子 2 0 2 の期待値が「低レベル」であり、入出力端子 2 0 2 がハイインピーダンス状態の不良である場合は、ハイインピーダンス検査用ドライバ 2 1 6 が「高レベル」を出力するので、ハイインピーダンス検査用ドライバ 2 1 6 から抵抗器 2 1 5 、抵抗器 2 0 8 を介してドライバ 2 0 9 に電流が流れ、この電流が電流計 2 1 4 で検出される。したがって、この場合も被検査 I C 2 0 1 が不良であると判定され、入出力端子 2 0 2 がハイインピーダンス状態となる不良が検出され得る。30

**【 0 2 0 0 】**

一般的に、半導体集積回路の機能検査（ファンクション検査）は D C 電気特性検査後に実施されるので、入出力端子を持たない L S I 、出力端子にハイインピーダンス機能のない L S I では、オープン不良などのハイインピーダンス状態となる不良が、D C 電気特性検査によって検出される。しかし、内部ロジックのコントロールによって入出力端子がハイインピーダンス状態となる L S I では、内部ロジックの論理的不良によりハイインピーダンス状態となることも想定されるので、本実施の形態のような検査装置が有効となる。40

**【 0 2 0 1 】**

なお、上記の各実施の形態では、被検査半導体集積回路（ I C ）と、良品サンプル（標準 I C ）あるいは検査装置との出力信号の不一致を各電源端子に流れる電流によって検出することを原理の根幹としており、電源端子に流れる電流波形をどの様に観測して検出するかは、対象となる I C に合わせて選択されるべきものであり、また、その検出値の比較の方法も、対象となる I C に合わせて選択されるべきものである。

**【 0 2 0 2 】**

10

20

30

40

50

なおまた、本発明は、デジタル I C だけでなく、D / A コンバータなどのアナログ I C の検査にも適用可能である。

【図面の簡単な説明】

【0203】

【図 1】本発明に係る第 1 の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

【図 2】動作パターン発生器から発生される所定の動作パターンと、電流測定回路で測定される電流値とを示すタイミングチャートである。

【図 3】第 2 の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

【図 4】第 2 の実施の形態における L S I テスターにおいて実行される D U T に対する検査処理の手順を示すフローチャートである。 10

【図 5】第 3 の実施の形態における不良端子の絞り込み手順を示すフローチャートである。

【図 6】第 4 の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。

【図 7】第 5 の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。

【図 8】第 5 の実施の形態において O N / O F F 制御信号に応じて抵抗に流れる電流パターンを示すタイミングチャートである。

【図 9】第 6 の実施の形態における半導体集積回路検査装置の構成を示すブロック図である。 20

【図 10】第 6 の実施の形態において各 O N / O F F 制御信号に応じて抵抗に流れる電流パターンおよび出力異常端子の絞込みを示すタイミングチャートである。

【図 11】第 7 の実施の形態における判定基準ゾーンを含む電流パターンを示すタイミングチャートである。

【図 12】電流測定回路の最適な電流測定レンジを設定し、また抵抗ユニットの各抵抗の最適な抵抗値を選択するための処理の手順を示すフローチャートである。

【図 13】第 8 の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

【図 14】第 9 の実施の形態の半導体集積回路検査装置の構成を示すブロック図である。

【図 15】第 10 の実施の形態における半導体集積回路の入出力端子用の検査装置の構成を示すブロック図である。 30

【図 16】従来の半導体集積回路の検査装置の構成例を示す図である。

【符号の説明】

【0204】

- 1 半導体集積回路 ( D U T )

- 2 抵抗ユニット ( 複数の抵抗器 )

- 3 電流測定回路 ( 測定手段 )

- 4 電圧印加回路 ( 印加手段 )

- 5 動作パターン発生器 ( 入力手段 )

- 6 直流電源

- 7 直流電源

- 8 L S I テスター ( 比較手段、判定手段 )

- 13 L S I テスター

- 14 半導体集積回路 ( D U T )

- 17 スイッチ

- 18 スイッチコントロール信号発生器

- 19 抵抗

- 20 電流測定回路

- 21 電圧印加回路

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

- (A) 動作パターン

(B) 良品サンプルの電流パターン

(C) DUTの電流パターン

(D) 制御信号1

ON/OFF

OFF

(E) 制御信号2

ON/OFF

OFF

(F) 制御信号K

ON/OFF

(G) 制御信号N

ON/OFF

(H) 外ミック信号

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

審査官 関根 洋之

(56)参考文献 特開2002-168923(JP,A)

特開2002-181894(JP,A)

特開平08-285925(JP,A)

特開平05-341006(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 01 R 31 / 28