(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-219515

(P2010-219515A)

(43) 公開日 平成22年9月30日(2010.9.30)

(51) Int.Cl.

**H01L 29/786** (2006.01)

**H01L 29/78** (2006.01)

**H01L 29/12** (2006.01)

**H01L 29/739** (2006.01)

**H01L 21/336** (2006.01)

F 1

H01L 29/78 616V

H01L 29/78 618B

H01L 29/78 652G

H01L 29/78 652T

H01L 29/78 622

テーマコード(参考)

5F11O

審査請求 未請求 請求項の数 12 O L (全 19 頁) 最終頁に続く

(21) 出願番号

特願2010-34356 (P2010-34356)

(22) 出願日

平成22年2月19日 (2010.2.19)

(31) 優先権主張番号

特願2009-37717 (P2009-37717)

(32) 優先日

平成21年2月20日 (2009.2.20)

(33) 優先権主張国

日本国 (JP)

(71) 出願人

000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者

山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者

荒井 康行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 半導体装置及びその作製方法

## (57) 【要約】

【課題】炭化珪素半導体を含む半導体装置を提供すること、又は炭化珪素半導体を含む半導体装置の生産性の向上を図ることを目的とする。

【解決手段】半導体層若しくは半導体基板の少なくとも一部がエネルギーギャップの大きな半導体領域で構成する。該エネルギーギャップの大きな半導体領域は、好ましくは炭化珪素で形成され、少なくとも絶縁層を介して設けられるゲート電極と重なる位置に設けられる。該半導体領域がチャネル形成領域に含まれる構成することで絶縁破壊耐圧を向上させる。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

絶縁表面に設けられた一導電型の半導体層と、

前記半導体層の少なくとも一部に設けられた炭化物半導体領域と、

前記炭化物半導体領域上に設けられたゲート絶縁層及び該ゲート絶縁層上に設けられた

ゲート電極と、

前記ゲート電極と少なくとも一部が重なり少なくとも前記炭化物半導体領域を含んで構

成される一導電型とは逆の導電型の第1不純物領域と、

前記第1不純物領域の内側であって前記ゲート電極の略外側に設けられ少なくとも前記

炭化物半導体領域を含んで構成される一導電型の第2不純物領域と、

前記第1不純物領域及び前記第2不純物領域と接するソース電極と、

前記半導体層と接するドレイン電極と

を有することを特徴とする半導体装置。

10

**【請求項 2】**

絶縁表面に設けられた一導電型の半導体層と、

前記半導体層の少なくとも一部に設けられた炭化物半導体領域と、

前記炭化物半導体領域上に設けられたゲート絶縁層及び該ゲート絶縁層上に設けられた

ゲート電極と、

前記ゲート電極と少なくとも一部が重なり少なくとも前記炭化物半導体領域を含んで構

成される一導電型とは逆の導電型の第1不純物領域と、

前記第1不純物領域の内側であって該ゲート電極の略外側に設けられ少なくとも前記炭

化物半導体領域を含んで構成される一導電型の第2不純物領域と、

前記半導体層の前記第1不純物領域の外側に設けられた一導電型とは逆の導電型の第3

不純物領域と、

前記第1不純物領域及び前記第2不純物領域と接するエミッタ電極と、

前記第3不純物領域と接するコレクタ電極と

を有することを特徴とする半導体装置。

20

**【請求項 3】**

請求項1又は2において、前記半導体層が単結晶シリコンであり、前記炭化物半導体領

域が炭化珪素であることを特徴とする半導体装置。

30

**【請求項 4】**

一導電型の半導体基板の一方の面の少なくとも一部に設けられた炭化物半導体領域と、

前記炭化物半導体領域上に設けられたゲート絶縁層及び該ゲート絶縁層上に設けられた

ゲート電極と、

前記ゲート電極と少なくとも一部が重なり少なくとも前記炭化物半導体領域を含んで構

成される一導電型とは逆の導電型の第1不純物領域と、

前記第1不純物領域の内側であって前記ゲート電極の略外側に設けられ少なくとも前記炭

化物半導体領域を含んで構成される一導電型の第2不純物領域と、

前記第1不純物領域及び前記第2不純物領域と接するソース電極と、

前記半導体基板の一方の面とは反対側の面に設けられたドレイン電極と

を有することを特徴とする半導体装置。

40

**【請求項 5】**

一導電型の半導体基板の一方の面の少なくとも一部に設けられた炭化物半導体領域と、

前記炭化物半導体領域上に設けられたゲート絶縁層及び該ゲート絶縁層上に設けられた

ゲート電極と、

前記ゲート電極と少なくとも一部が重なり少なくとも前記炭化物半導体領域を含んで構

成される一導電型とは逆の導電型の第1不純物領域と、

前記第1不純物領域の内側であって該ゲート電極の略外側に設けられ少なくとも前記炭

化物半導体領域を含んで構成される一導電型の第2不純物領域と、

前記半導体基板の一方の面とは反対側の面に設けられた一導電型とは逆の導電型の第3

50

不純物領域と、

前記第1不純物領域及び前記第2不純物領域と接するエミッタ電極と、

前記第3不純物領域と接するコレクタ電極と

を有することを特徴とする半導体装置。

【請求項6】

請求項4又は5において、前記半導体基板が単結晶シリコンであり、前記炭化物半導体領域が炭化珪素であることを特徴とする半導体装置。

【請求項7】

一導電型の半導体層を炭化物気体を含む雰囲気中で加熱して該半導体層の表層部を炭化して炭化物半導体領域を形成し、

前記炭化物半導体領域を含むように一導電型とは逆の導電型の第1不純物領域を前記半導体層に形成し、

前記第1不純物領域の内側に少なくとも炭化物半導体領域を含むように一導電型の第2不純物領域を形成し、

前記半導体層上にゲート絶縁層を介して前記第1不純物領域を少なくとも一部が重なるようにゲート電極を形成し、

前記第2不純物領域及び前記第1不純物領域の一部と接するソース電極及び前記半導体層と接するドレイン電極とを形成すること

を特徴とする半導体装置の作製方法。

【請求項8】

一導電型の半導体層を炭化物気体を含む雰囲気中で加熱して該半導体層の表層部を炭化して炭化物半導体領域を形成し、

前記炭化物半導体領域を含むように一導電型とは逆の導電型の第1不純物領域を前記半導体層に形成し、

前記第1不純物領域の内側に少なくとも炭化物半導体領域を含むように一導電型の第2不純物領域を形成し、

前記半導体層の前記第1不純物領域の外側に一導電型とは逆の導電型の第3不純物領域を形成し、

前記半導体層上にゲート絶縁層を介して前記第1不純物領域を少なくとも一部が重なるようにゲート電極を形成し、

前記第2不純物領域及び前記第1不純物領域の一部と接するソース電極及び前記第3不純物領域と接するドレイン電極とを形成すること

を特徴とする半導体装置の作製方法。

【請求項9】

請求項7又は8のいずれか一項において、前記炭化物半導体領域の形成は、炭化水素気体を含む雰囲気中で前記半導体層を加熱しつつレーザ光を照射して行うこと特徴とする半導体装置の作製方法。

【請求項10】

一導電型の半導体基板を炭化物気体を含む雰囲気中で加熱して該半導体基板の一面の表層部を炭化して炭化物半導体領域を形成し、

前記炭化物半導体領域を含むように一導電型とは逆の導電型の第1不純物領域を前記半導体基板に形成し、

前記第1不純物領域の内側に少なくとも炭化物半導体領域を含むように一導電型の第2不純物領域を形成し、

前記半導体基板上にゲート絶縁層を介して前記第1不純物領域を少なくとも一部が重なるようにゲート電極を形成し、

前記第2不純物領域及び前記第1不純物領域の一部と接するソース電極及び前記半導体基板の一面と反対側の面と接するドレイン電極とを形成すること

を特徴とする半導体装置の作製方法。

【請求項11】

10

20

30

40

50

一導電型の半導体基板を炭化物気体を含む雰囲気中で加熱して該半導体基板の一面の表層部を炭化して炭化物半導体領域を形成し、

前記炭化物半導体領域を含むように一導電型とは逆の導電型の第1不純物領域を前記半導体基板に形成し、

前記第1不純物領域の内側に少なくとも炭化物半導体領域を含むように一導電型の第2不純物領域を形成し、

前記半導体基板の一面とは反対側の面に一導電型とは逆の導電型の第3不純物領域を形成し、

前記半導体基板上にゲート絶縁層を介して前記第1不純物領域を少なくとも一部が重なるようにゲート電極を形成し、

前記第2不純物領域及び前記第1不純物領域の一部と接するソース電極及び前記第3不純物領域と接するドレイン電極とを形成すること

を特徴とする半導体装置の作製方法。

【請求項12】

請求項10又は11のいずれか一項において、前記炭化物半導体領域の形成は、炭化水素気体を含む雰囲気中で前記半導体基板を加熱しつつレーザ光を照射して行うこと特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

開示される発明の一は半導体装置及びその作製方法に係り、その一形態は比較的大きな電力を制御する半導体装置に関する。

【背景技術】

【0002】

炭化珪素半導体のエネルギーギャップは3.02eV(4H-SiC)であり、シリコン半導体の1.12eVと比較して約3倍の大きさを有している。シリコン半導体の絶縁破壊電界が0.3MV/cmであるのに対し、炭化珪素半導体は絶縁破壊電界が3.5MV/cmと10倍以上優れた値を有している。このため、炭化珪素半導体はインバータやコンバータに代表される電力機器への用途が期待されている。

【0003】

このようなメリットを期待されつつも、炭化珪素半導体を利用したトランジスタが実用化されないのは、炭化珪素半導体基板の品質の低さと、基板の大口径化が困難なことに原因があるとされている。

【0004】

具体的には炭化珪素基板の欠陥を低減する必要があることが判明している。炭化珪素基板にはマイクロパイプと呼ばれる中空貫通欠陥があり、これがトランジスタの中に一つでも含まれると、トランジスタとして機能しなくなってしまうことが問題となっている。さらに炭化珪素基板には、中空貫通欠陥以外にも、転位などの欠陥が多く含まれている。そのため、高品質な炭化珪素基板を作製するために、例えば、ホモエピタキシャル成長及びヘテロエピタキシャル成長によって高品質の炭化珪素半導体層を半導体基板上に成長させようとする試みがなされている(特許文献1、2参照)。

【0005】

しかし、炭化珪素基板の品質改善の試みがなされているとしても、基板サイズが小さいという問題は依然として解消されていない。単結晶シリコン基板のサイズが12インチであるのに対し、炭化珪素基板のサイズは未だ3インチが主流である。これは炭化珪素半導体は、結晶成長の制御が難しいことに起因している。結局のところ炭化珪素半導体を用いたデバイスは、理想的には高性能が期待されているにもかかわらず、結晶品質の悪さと生産性の低さから実用化が遅れているのが実情である。

【先行技術文献】

【特許文献】

10

20

30

40

50

## 【0006】

【特許文献1】特開2006-032655号公報

【特許文献2】特開2006-036613号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

このような問題に鑑み、本発明の一形態は、炭化珪素半導体を含む半導体装置を提供することを目的の一とする。

このような問題に鑑み、本発明の一形態は、炭化珪素半導体を含む半導体装置の生産性の向上を図ることを他の目的の一とする。

10

## 【課題を解決するための手段】

## 【0008】

本発明の一実施形態は、半導体基板の全てを炭化珪素半導体とするのではなく、半導体基板の少なくとも一部に炭化珪素半導体層が含まれるようにすることで上記課題を解決するものである。半導体基板としてシリコン半導体基板を用いれば基板の大口径化が可能であり、その一表面を炭化珪素化することで、大面積の炭化珪素半導体層を有する半導体基板とすることができる。このような半導体基板を用いることでトランジスタなどの素子の能動領域の一部又は全部を炭化珪素半導体で形成した半導体装置を得ることができる。

## 【0009】

本発明の一実施形態に係る半導体装置は、絶縁表面に設けられた半導体層を含み、半導体層の少なくとも一部が半導体層のエネルギーギャップよりも大きな半導体領域で構成される半導体装置である。該エネルギーギャップの大きな半導体領域は、少なくとも絶縁層を介して設けられるゲート電極と重なる位置に設けられる。半導体層よりもエネルギーギャップの大きい半導体領域がチャネル形成領域に含まれる構成とすることで絶縁破壊耐圧を向上させるように作用する。半導体層は単結晶又は多結晶であることが好ましく、半導体層のエネルギーギャップよりも大きな半導体領域も結晶構造を有していることが好ましい。半導体層を構成する材料の一はシリコン半導体であり、これに対してエネルギーギャップの大きな半導体材料として炭化物半導体の組み合わせが好適である。炭化物半導体として炭化珪素を用いることが好ましい。シリコン半導体としては単結晶シリコンが好ましく、多結晶シリコンを適用することも可能である。

20

## 【0010】

本発明の一実施形態に係る半導体装置は、絶縁表面に設けられた一導電型の半導体層と、半導体層の少なくとも一部に設けられた炭化物半導体領域と、半導体領域上に設けられたゲート絶縁層と該ゲート絶縁層上に設けられたゲート電極と、ゲート電極と少なくとも一部が重なり少なくとも該炭化物半導体領域を含んで構成される一導電型とは逆の導電型の第1不純物領域と、第1不純物領域の内側であって該ゲート電極の略外側に設けられ少なくとも該炭化物半導体領域を含んで構成される一導電型の第2不純物領域と、第1不純物領域及び第2不純物領域と接するソース電極と、半導体層と接するドレイン電極とを有する半導体装置である。

30

## 【0011】

本発明の一実施形態に係る半導体装置は、絶縁表面に設けられた一導電型の半導体層と、半導体層の少なくとも一部に設けられた炭化物半導体領域と、半導体層上に設けられたゲート絶縁層と該ゲート絶縁層上に設けられたゲート電極と、ゲート電極と少なくとも一部が重なり少なくとも該炭化物半導体領域を含んで構成される一導電型とは逆の導電型の第1不純物領域と、第1不純物領域の内側であって該ゲート電極の略外側に設けられ少なくとも該炭化物半導体領域を含んで構成される一導電型の第2不純物領域と、第1不純物領域及び第2不純物領域と接するエミッタ電極と、半導体層に設けられた一導電型とは逆の導電型の第3不純物領域と接するコレクタ電極を有する半導体装置である。

40

## 【0012】

上記半導体装置の一態様において、半導体層は単結晶であることが好ましいが、多結晶

50

であっても適用することができる。また、絶縁表面に設けられる半導体層に代えて半導体基板を適用することもできる。

【0013】

半導体を、炭化物気体を含む雰囲気中で加熱して該半導体の表層部を炭化して炭化物半導体領域を形成し、炭化物半導体領域にチャネル形成領域が形成されるように絶縁層を挟んでゲート電極を形成する工程を含む半導体装置の作製方法である。

この炭化処理は半導体基板に対して行うものの他、絶縁表面を有する基板上に設けられた半導体層に対して行われるものも含む。

炭化物気体にはメタン、プロパンなどの炭化水素気体が好適には用いられる。

【0014】

炭化処理における加熱処理において、基板の加熱に加えてレーザ光を半導体に対して照射しても良い。レーザ光は半導体の全面を一度に照射する場合の他、パルスレーザ又は連続発振レーザを逐次照射する方法が適用可能である。

【0015】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を限定して示すものではない。また、第1、第2として付される序数詞が付された名称は、発明を特定するための事項として固有の名称を示すものではない。

【発明の効果】

【0016】

トランジスタのチャネル形成領域の一部又は全部を炭化物半導体領域で構成することにより、耐圧の高い半導体装置を得ることができる。

半導体層が設けられた基板又は半導体基板を、炭化物気体を含む雰囲気中で加熱処理することにより、炭化珪素半導体層を形成することができる。この場合において、半導体層又は半導体基板が大面積化した場合でも、加熱処理を行う装置の大型化をすれば良いので、生産性を損なうことなく炭化珪素半導体を含む半導体装置を製造することができる。

【図面の簡単な説明】

【0017】

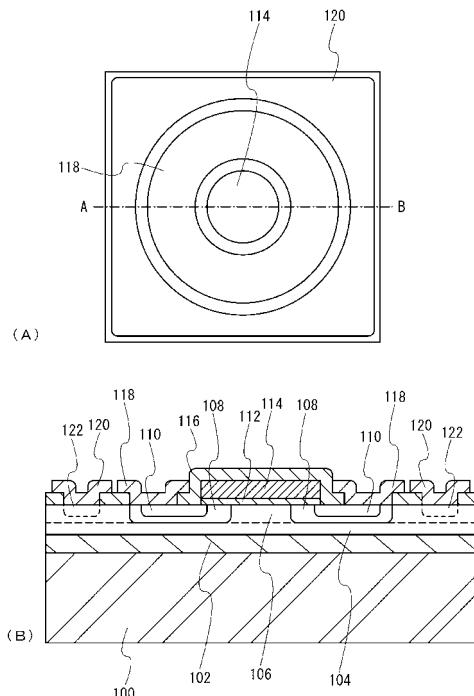

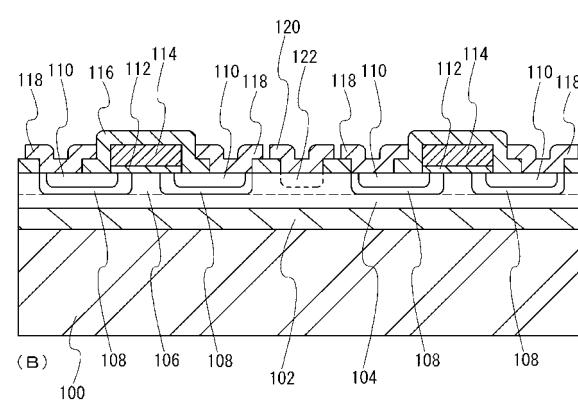

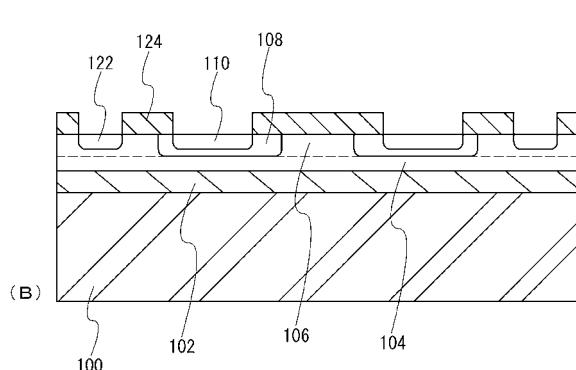

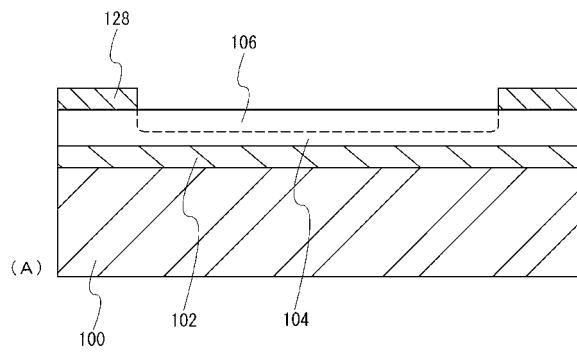

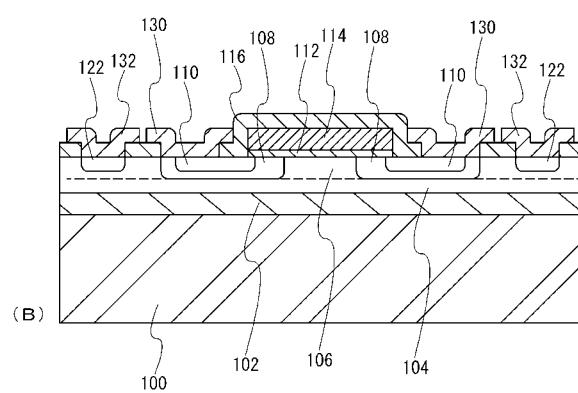

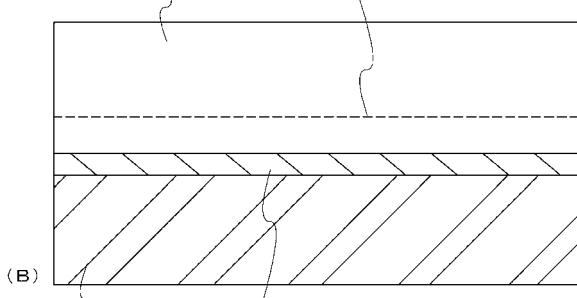

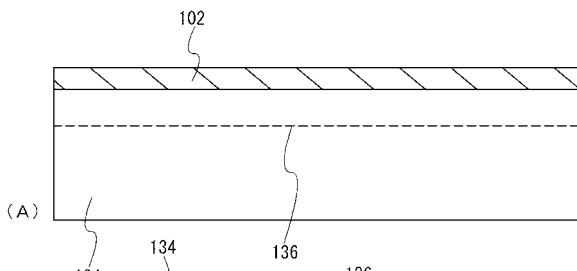

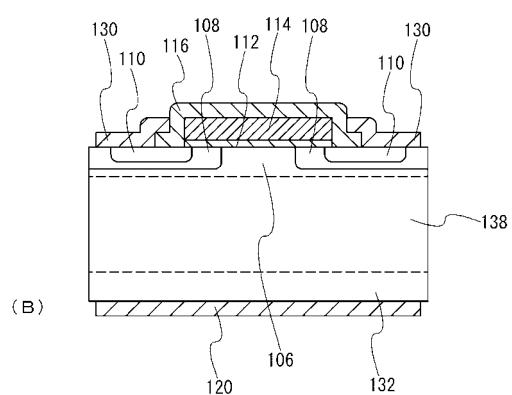

【図1】支持基板上に絶縁層を介して半導体層が設けられたSOI構造を有する半導体装置の一形態を示し、(A)は平面図、(B)は断面図を示す。

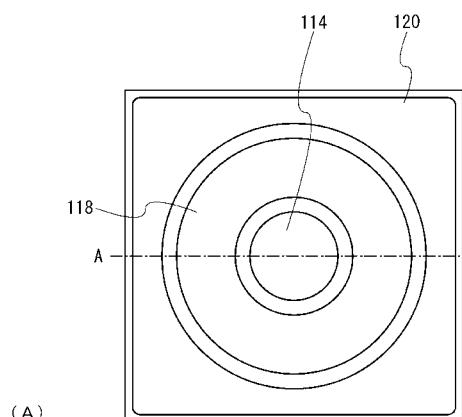

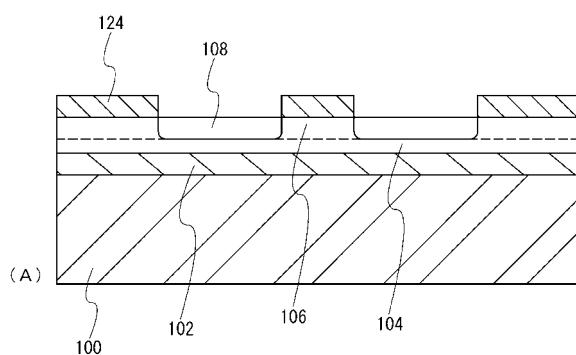

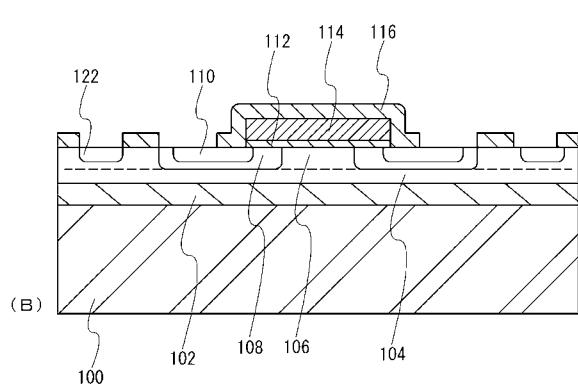

【図2】支持基板上に絶縁層を介して半導体層が設けられたSOI構造を有する半導体装置の一形態を示し、(A)は平面図、(B)は断面図を示す。

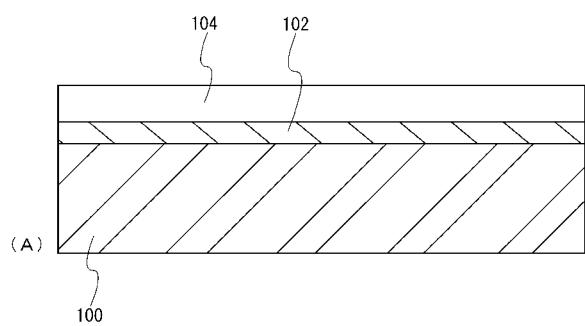

【図3】SOI構造を有する半導体装置の製造工程の一例を説明する図。

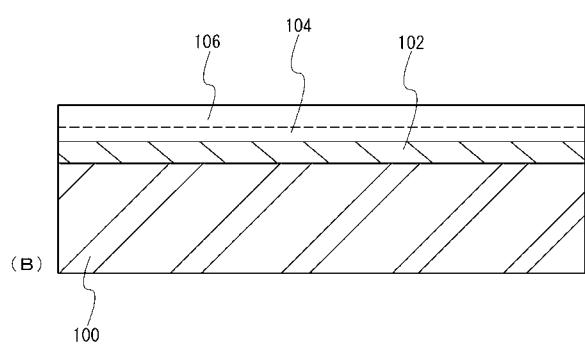

【図4】SOI構造を有する半導体装置の製造工程の一例を説明する図。

【図5】SOI構造を有する半導体装置の製造工程の一例を説明する図。

【図6】SOI構造を有する半導体装置の製造工程の一例を説明する図。

【図7】支持基板上に絶縁層を介して半導体層が設けられたSOI構造を有する半導体装置の一形態を示し、(A)は平面図、(B)は断面図を示す。

【図8】SOI構造を有する基板の作製方法を説明する図。

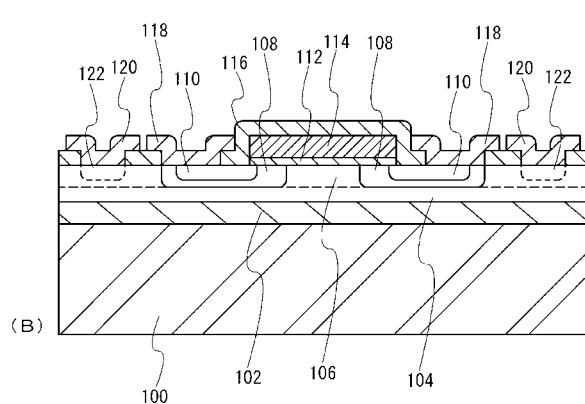

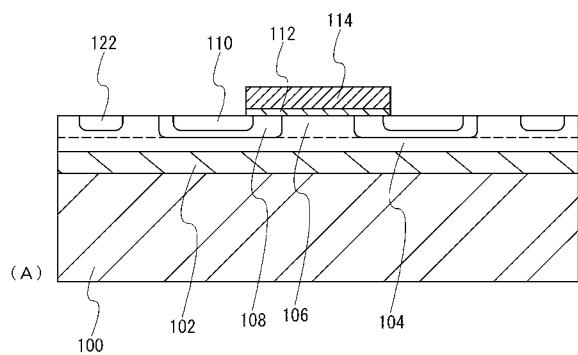

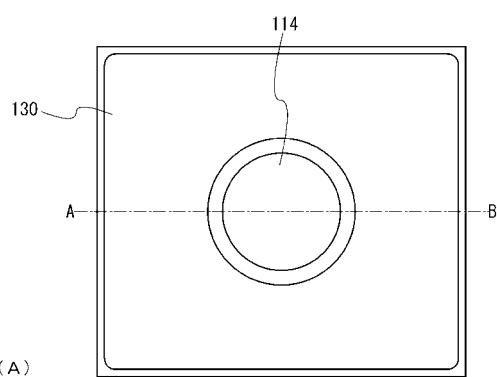

【図9】半導体基板に構成される半導体装置の一形態を示し、(A)は平面図、(B)は断面図を示す。

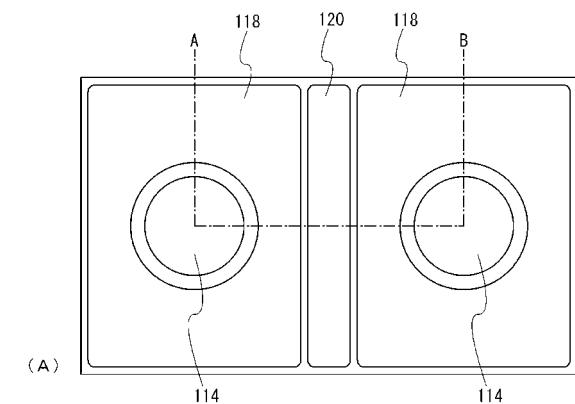

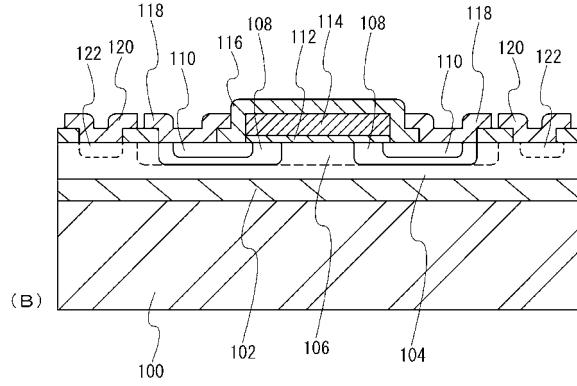

【図10】半導体基板に構成される半導体装置の一形態を示し、(A)は平面図、(B)は断面図を示す。

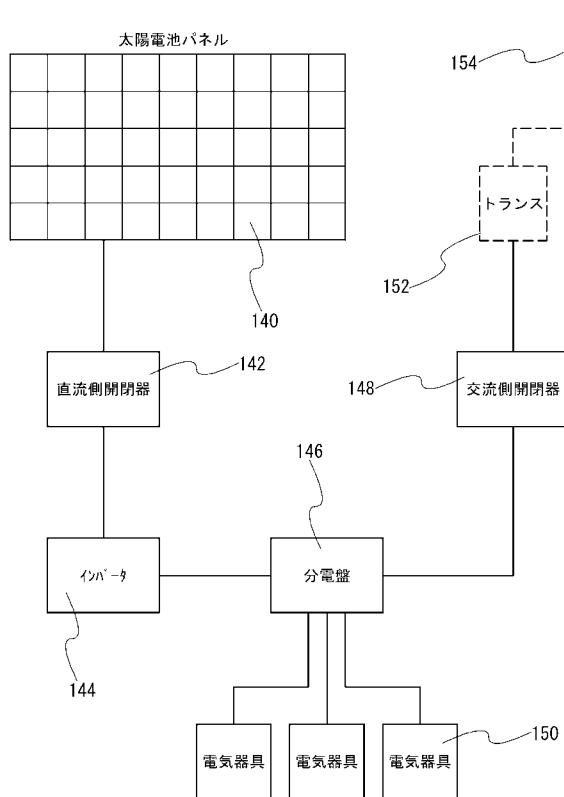

【図11】インバータを備えた太陽光発電システムの一例を示す

【発明を実施するための形態】

【0018】

開示される発明の実施の形態について図面を用いて以下に説明する。但し、開示される発明は以下の説明に限定されず、その発明の趣旨及びその範囲から逸脱することなくその形態及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。したがって、開示される発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。以下に説明する実施の形態において、同じものを指す符号は異なる図面間で共通して

用いる場合がある。

【0019】

(実施の形態1)

本形態は、支持基板上に絶縁層を介して半導体層が設けられたS O I構造を有する半導体装置の一例を示す。本形態は、炭化珪素半導体を含む半導体装置を提供するための構成を例示する。

図1(A)は半導体装置の平面図を示し、図1(B)はこの平面図のA-B切断線に対応する断面図を示す。

【0020】

図1(A)は、ゲート電極114の周囲にソース電極118が設けられている半導体装置の平面図を示している。ドレイン電極120はソース電極118の外側に設けられている。

以下、図1(A)及び(B)の断面図を参照して、本形態に係る半導体装置の構成を説明する。

【0021】

<支持基板>

支持基板100は絶縁基板、半導体基板、金属基板など平坦な表面を有する基板が適用可能である。しかしながら、支持基板100は500以上の中熱性のあるものが好ましい。

【0022】

支持基板としては石英基板を用いることが好ましいが、歪み点が700以上のガラス基板を用いることもできる。

半導体基板の代表例はシリコン基板(シリコンウエハー)である。シリコン基板は、表面が研磨され平坦化されたものであれば良く、いわゆる太陽電池級のシリコン基板のように廉価な基板を適用することもできる。例えば支持基板として純度6N(99.9999%)~7N(99.99999%)程度のシリコン基板を適用することができる。この場合にはシリコン基板の表面を、塩化水素を0.5体積%~10体積%(好ましくは3体積%)の割合で含む酸化雰囲気中で700~1150、好ましくは800~1050に加熱して酸化膜を形成しておくことが好ましい。

金属基板を用いる場合は、表面を平坦に研磨し、次に説明する絶縁層を形成する。

【0023】

<支持基板上の絶縁層>

支持基板100上に設けられる絶縁層102は、平坦性を有することが好ましい。そのため絶縁層102として、酸化シリコン、酸窒化シリコン、窒化シリコンなどが適用される。これらのシリコンを成分として含む絶縁層は、スパッタリング法、気相成長法で形成することができる。

【0024】

支持基板としてシリコン基板を用いる場合には、熱酸化法によって表面に絶縁層を形成しても良い。シリコン基板が太陽電池級のものである場合には、HClを含む酸素雰囲気中でシリコン基板を熱酸化することで、金属などの不純物を低減することができる。

【0025】

<半導体層>

支持基板100に絶縁層102を介して設けられる半導体層104は、単結晶半導体が好ましく、多結晶半導体で代替することもできる。代表的には単結晶シリコン半導体が適用される。

半導体層104はn型又はp型のいずれか一方の導電型を有する。半導体層104の厚さは50nmから500nm程度であれば良い。

【0026】

<炭化物半導体領域>

半導体層104の表面には炭化物半導体領域106が設けられる。この炭化物半導体領

10

20

30

40

50

域 106 は、シリコン半導体よりもエネルギー・ギャップの広い半導体領域である。

この炭化物半導体領域 106 は、半導体層 104 と同様にシリコンを成分として含む半導体材料が好ましい。好適には炭化珪素半導体である。炭化物半導体領域 106 は、半導体層 104 の表面から少なくとも 5 nm から 15 nm 程度の深さで形成される。半導体層 104 がシリコン半導体の場合、炭化物半導体領域 106 は炭化珪素で構成される。

【0027】

炭化物半導体領域 106 は、半導体層 104 の全面に設けられていても良いし、後述するようにトランジスタのチャネル形成領域に該当する領域に選択的に設けられていても良い。このように炭化珪素基板そのものを作製するのではなく、結晶化した半導体層に炭化珪素半導体領域を形成することで、結晶性の良い炭化珪素半導体領域を得ることができる。そして、この炭化珪素半導体領域を使ってトランジスタなどの半導体素子を作製することができる。

10

【0028】

<第1不純物領域>

第1不純物領域 108 は、半導体層 104 とは逆の導電型を有する領域である。例えば、半導体層 104 が n 型であれば、第1不純物領域 108 は p 型の領域となる。

【0029】

第1不純物領域 108 は、ゲート電極 114 とソース電極 118 と重畳するように設けられる。第1不純物領域 108 は、炭化物半導体領域 106 と同程度の厚さを有していれば良い。電流は、チャネル形成領域（ゲート電極 114 と重畳する第1不純物領域 108）を介してソース電極 118 とドレイン電極 120 の間を流れるので、第1不純物領域 108 の下側に半導体層 104 が残存するようにしておく必要がある。

20

【0030】

<第2不純物領域>

第2不純物領域 110 は第1不純物領域 108 の内側に設けられる。第2不純物領域 110 は半導体層 104 と同じ導電型を有する。第2不純物領域 110 はゲート電極 114 の縁部からソース電極 118 と重なる領域に設けられる。第2不純物領域 110 は、いわゆるソース領域として機能する。

30

【0031】

第2不純物領域 110 の厚さは、第1不純物領域 108 の底部に達しない厚さで形成される。半導体層 104 と同じ導電型であるため、第1不純物領域 108 を貫通してしまうとソース電極 118 とドレイン電極 120 が実質的に短絡してしまうからである。

【0032】

<ゲート絶縁層>

ゲート絶縁層 112 は半導体層 104（炭化物半導体領域 106 を含む）を酸化して形成される絶縁膜、又は半導体層 104 上に絶縁膜を堆積することで形成される。

40

【0033】

半導体層 104（炭化物半導体領域 106 を含む）の酸化は、ドライ酸化法、水素と酸素を燃焼させて水蒸気を作り該水蒸気と酸素で酸化するパイロジェニック酸化法（ウエット酸化法）、酸素に塩化水素を混合して熱酸化を行う方法などにより行うことができる。また、半導体層 104（炭化物半導体領域 106 を含む）の表面にプラズマ処理を行ってゲート絶縁層 112 を形成しても良い。この場合のプラズマ処理は、プラズマ中で生成した酸素ラジカルを半導体表面に作用させて酸化する方法であり、低温でも酸化反応が進むという特性がある。そのため、比較的酸化しにくい炭化珪素半導体に対しても 1000 以下の温度で酸化膜を形成することができる。

【0034】

半導体層 104（炭化物半導体領域 106 を含む）の上にゲート絶縁層 112 を堆積するには熱 CVD 法やプラズマ CVD 法を適用することができ、これによって酸化シリコン膜や酸窒化シリコン膜を形成することができる。

50

【0035】

## &lt;ゲート電極&gt;

ゲート電極 114 はゲート絶縁層 112 の上に設けられている。ゲート電極 114 はゲート絶縁層 112 上に設けられることで、半導体層 104 (炭化物半導体領域 106 を含む) と絶縁されている。

ゲート電極 114 の上層側は好ましくは絶縁層 116 で覆われている。絶縁層 116 によりソース電極 118 と確実に絶縁される。

## 【0036】

## &lt;ソース電極及びドレイン電極&gt;

ソース電極 118 は第 2 不純物領域 110 に接触するように設けられる。また、ソース電極 118 は第 2 不純物領域 110 のみならず、ゲート電極 114 の外側領域で第 1 不純物領域 108 とも接触するように配置されている。この配置により、ソース電極 118 と隣接するドレイン電極 120 の間には実質的に p-n 接合が形成される。

## 【0037】

通常動作時においては、ソース電極 118 が負にバイアスされドレイン電極 120 が正にバイアスされるので、ソース電極 118 とドレイン電極 120 との間に形成される p-n 接合は逆方向にバイアスされることとなる。それにより、ソース電極 118 とドレイン電極 120 との間のリーク電流が低減する。

## 【0038】

ドレイン電極 120 はソース電極 118 の外側領域に設けられる。ドレイン電極 120 は第 2 不純物領域 110 と同じ導電型の第 3 不純物領域 122 と接触している。電流が流れる経路から見て、ソース電極 118 とドレイン電極 120 との間には第 2 不純物領域 110、第 1 不純物領域 108、炭化物半導体領域 106、半導体層 104、及び第 3 不純物領域 122 が存在する。ここで、炭化物半導体で形成される第 1 不純物領域 108、炭化物半導体領域 106 が電流経路に存在することにより耐圧を高めることができる。

## 【0039】

## &lt;変形例&gt;

図 2 (A) 及び (B) は一つのドレイン電極 120 に対して、その両側に一対のゲート電極 114 及びソース電極 118 を配設した半導体装置の一例を示す。支持基板 100 にチャネル形成領域が二カ所設けられ、ドレイン電極 120 を二つのソース電極 118 で挟む構成とすることで、装置の小型化を図りつつ大電流を流すことができる。このような半導体装置は電流定格の大きい用途に適している。

## 【0040】

## &lt;半導体装置の動作&gt;

半導体層 104 を n 型、第 1 不純物領域 108 を p 型、第 2 不純物領域 110 を n 型とすると、ソース電極 118 とドレイン電極 120 との間には n-p-n 接合が介在し、ゲート電極にバイアスを印加しない場合には僅かな電流しか流れない。

## 【0041】

ゲート電極 114 に正バイアスを印加すると、ゲート電極 114 と重なる第 1 不純物領域 108 のゲート絶縁層 112 の界面側に負の電荷 (電子) が誘起され、ソース電極 118 とドレイン電極 120 間に電流が流れる。チャネル形成領域は、炭化物半導体領域 106 の中に形成された第 1 不純物領域 108 において、ゲート電極 114 と重なる領域に形成される。

## 【0042】

チャネル形成領域が炭化物半導体領域 106 の領域の中に形成された第 1 不純物領域 108 に形成されると絶縁破壊電圧が向上する。これは、Si-C 結合の原子間距離が約 0.18 nm と短く、結合エネルギーが高く、炭化珪素半導体がシリコン半導体に比べ約 3 倍のエネルギー・ギャップを有していることに起因している。

## 【0043】

このため炭化物半導体でチャネル形成領域を形成すると、シリコン半導体でチャネル形成領域を形成した場合に比べて固有オン抵抗が 2 衍半ほど小さくて済む。また、熱伝導度

がシリコンの3倍ほど大きいので熱放散性が良い。それにより、半導体装置が扱える単位面積当たりの電流密度が大きくなる。

【0044】

(実施の形態2)

本形態では、図3、図4及び図5を参照して、実施の形態1で示す半導体装置の作製方法の一例を示す。本形態は、炭化珪素半導体を含む半導体装置を提供することを目的のーとし、また、炭化珪素半導体を含む半導体装置の生産性の向上を図ることを目的のーとしている。

【0045】

<支持基板の作製又は準備(図3(A)を参照)>

支持基板100上に絶縁層102を介して半導体層104を設ける。この構造は、絶縁表面上に半導体層が設けられた所謂SOI構造である。従って、貼り合わせSOI基板、SIMOX(Separation by Implanted Oxygen)基板など市販されているSOI基板を適用することもできる。

半導体層104の材質は、単結晶シリコンが好適でありその他の半導体材料を用いることができる。半導体層104は、例えばn型の導電型を有している。

【0046】

<炭化物半導体領域の形成(図3(B)を参照)>

半導体層104表面に炭化物半導体領域106を形成する。炭化物半導体領域106は半導体層104よりもエネルギーギャップが広くなるように、半導体層104の母体材料のエネルギーギャップを広げる作用のある元素を含ませる。例えば、半導体層104に特定の元素を含浸させる処理を行う。

【0047】

具体例としては、半導体層104が単結晶シリコン半導体である場合、水素ガスをキャリアガスとしてメタン又はプロパンなど炭化水素気体を混合した混合気体雰囲気中で、1000乃至1300、好ましくは1100から1250で加熱処理を行う。この処理により、半導体層104の表面から5nm乃至20nmの深さに炭素が含浸し、炭化物半導体領域106を形成することができる。

【0048】

また、水素と炭化水素気体の混合気体中で、半導体層104にレーザ光を照射して、炭素を半導体層104に含浸させても良い。この場合、レーザ光は半導体層104の少なくとも表層部が溶融するように照射することが好ましい。この処理において500乃至1000に加熱しながら行うと、炭化物半導体領域106の形成が容易となり、レーザ照射後の再単結晶化もより促進される。

【0049】

単結晶シリコンのエネルギーギャップが1.12eVであるのに対し、炭化珪素のエネルギーギャップは2.2eVから3.1eV程度ある(例えば4H-SiCのエネルギーギャップは3.02eVである)。炭素を単結晶シリコンに導入することにより、概略2倍から3倍のエネルギーギャップ拡大効果を得ることができる。

また、このエネルギーギャップが拡大した領域の厚さをさらに増加させるために、炭化物半導体領域106の上に炭化珪素層をエピタキシャル成長させても良い。

【0050】

<第1不純物領域の形成(図4(A)を参照)>

半導体層104上に第1マスク層124を形成する。この第1マスク層124は第1不純物領域108が形成されるべき位置に開口部が設けられている。

第1不純物領域108に半導体層104とは逆の導電型を付与する不純物元素を添加する。半導体層104がn型であれば、p型の導電型を付与する硼素を添加する。

【0051】

<第2不純物領域の形成(図4(B)を参照)>

半導体層104上に第2マスク層126を形成する。この第2マスク層126は第2不

10

20

30

40

50

純物領域 110 が形成されるべき位置に開口部が設けられている。すなわち、第 1 不純物領域 108 の内側領域に開口部が配設されるように第 2 マスク層 126 を設ける。

【0052】

第 2 不純物領域 110 に半導体層 104 と同じ導電型を付与する不純物元素を添加する。半導体層 104 が n 型であれば、n 型の導電型を付与するリン又はヒ素を添加する。このとき、第 2 不純物領域 110 と同じ導電型を有する第 3 不純物領域 122 を同時に形成しても良い。なお、第 3 不純物領域 122 は必須なものではなく、ドレイン電極 120 とオーミックコンタクトをとりやすくするために設けることが好ましい領域である。

【0053】

< 絶縁ゲートの形成 (図 5 (A) を参照) >

ゲート絶縁層 112 は半導体層 104 (炭化物半導体領域 106 を含む) の表面を酸化することにより形成される。あるいは半導体層 104 上に絶縁膜を堆積することにより形成される。

酸化法として、ドライ酸化法、水素を燃焼させて水蒸気を作り該水蒸気と酸素で酸化するパイロジェニック酸化法 (ウェット酸化法)、酸素に塩化水素を混合して行う HCl 酸化法などを適用することができる。

また、酸化法の別形態としてプラズマ酸化法によりゲート絶縁層を形成しても良い。プラズマ酸化法は、プラズマ中で生成した酸素ラジカルを半導体表面に作用させて酸化する方法であり、低温でも酸化反応が進むという特性がある。

ゲート絶縁層 112 を堆積法で形成する場合には、熱 CVD 法又はプラズマ CVD 法などが適用され、この方法によって酸化シリコン膜、酸窒化シリコン膜などが形成される。

【0054】

ゲート絶縁層 112 の上にゲート電極 114 を形成する。ゲート電極 114 はポリシリコン又は金属材料で形成する。金属材料としては、モリブデン、タンクステン、チタンなどの金属若しくはこれら高融点金属の合金を用いれば良い。ゲート電極 114 は、ゲート絶縁層 112 を介して炭化物半導体領域 106 及び第 1 不純物領域 108 と重なるように設けられる。この構造において、ゲート電極 114 と第 1 不純物領域 108 が重畳する領域がチャネル形成領域となる。なお、ゲート電極 114 の配置を図 1 (A) の平面図で見ると、ゲート電極 114 はソース電極 118 に囲まれるように配置される。

【0055】

< 保護膜の形成 (図 5 (B) を参照) >

ゲート電極 114 上に絶縁層 116 を形成する。そして絶縁層 116 にコンタクトホールを形成する。その後、絶縁層 116 に形成されたコンタクトホールの位置に合わせて、ソース電極 118 及びドレイン電極 120 を形成すれば、図 1 (A) 及び (B) で示す半導体装置を得ることができる。

【0056】

上記の工程に従えば炭化物半導体領域 106 を含む半導体装置を得ることができる。この作製方法は半導体層 104 に炭素を含浸させる処理を含むので、支持基板 100 が大面積化しても、支持基板 100 の面積に対応した半導体層 104 を設けることは容易であるので、大面積の炭化物半導体領域 106 を得ることも容易である。すなわち、大口径の炭化珪素基板を製造しなくとも、炭化珪素半導体領域を半導体層の表面に形成することで、高耐圧で低損失の特性を有する半導体装置を得ることができる。さらに、本形態の作製方法によれば、炭化珪素半導体を含む半導体装置の生産性の向上を図ることができる。

【0057】

< 選択的に変成層を形成する変形例 (図 6 (A) 及び (B) を参照) >

半導体層 104 に炭化物半導体領域 106 を形成する際に、開口部を有する第 3 マスク層 128 を設けておくと、炭化物半導体領域 106 を選択的に形成することができる。炭化物半導体領域 106 を形成するための処理温度は高温であるので、第 3 マスク層 128 は酸化シリコン又は窒化シリコンなどで形成することが好ましい。

【0058】

10

20

30

40

50

なお第1不純物領域108がゲート電極114と重なる領域がチャネル形成領域となるので、第1不純物領域108が炭化物半導体領域106の中に形成されるようにすれば、図1の半導体装置と同様の作用効果を得ることができる。

#### 【0059】

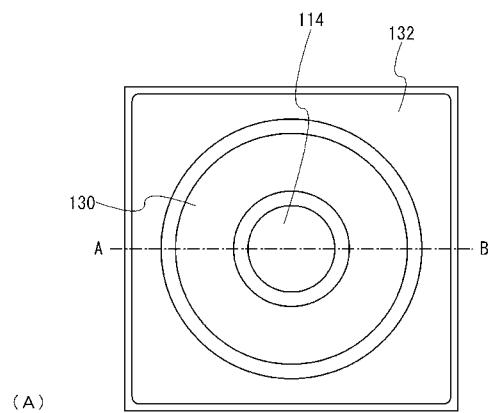

##### (実施の形態3)

本形態は、支持基板上に絶縁層を介して半導体層が設けられたSOI構造を有し、バイポーラ動作をする半導体装置の一例を示す。本形態は、炭化珪素半導体を含む半導体装置を提供するための構成を例示する。

図7(A)は半導体装置の平面図を示し、図7(B)はこの平面図のA-B切断線に対応する断面図を示す。

10

#### 【0060】

本形態に係る半導体装置は、図1で説明する半導体装置と基本的な構造は同じであるが、第3不純物領域122が第1不純物領域108と同じ導電型である点が異なっている。また、エミッタ電極130は第1不純物領域108及び第2不純物領域110と接触し、コレクタ電極132は第3不純物領域122と接触している。

#### 【0061】

実施の形態1と同様に、本形態に係る半導体装置はゲート電極114に正のバイアスを印加すると第1不純物領域108にチャネル領域が形成される。ここで、第3不純物領域122をp型としたことにより、オン状態では第3不純物領域122から半導体層104にホールが注入される。それにより、オン状態となる電圧が低くなる。すなわち、高耐圧で大容量の半導体装置を得ることができる。

20

#### 【0062】

本形態に係る半導体装置は、入力側に絶縁ゲート型電界効果トランジスタの構成を有し、出力側がバイポーラトランジスタの構成を備えたものである。この半導体装置は、ゲート電極114とエミッタ電極130間の電圧で駆動され、ゲート電極114への入力信号によってオン・オフ動作をする。

この半導体装置は、スイッチング動作の高速化を図ることが可能である。さらに、この半導体装置はオン抵抗が低いことから自己発熱が抑えられ、大電力の制御をする用途に好適となる。

30

#### 【0063】

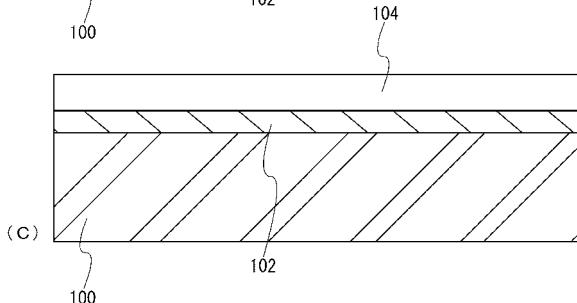

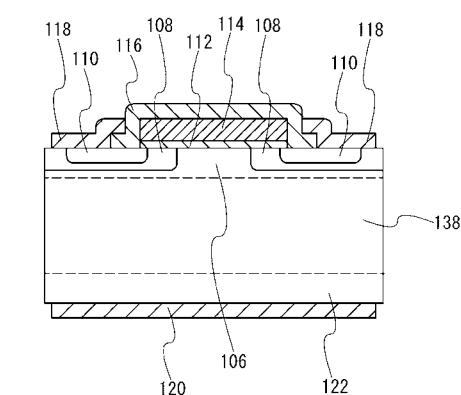

##### (実施の形態4)

本形態は、実施の形態1乃至3で示す支持基板100上に半導体層104を設ける方法の一例を示す。

#### 【0064】

##### <半導体基板に分離層を形成する段階(図8(A))>

半導体基板134にイオンを導入して損傷層136を形成する。半導体基板134は単結晶半導体又は多結晶半導体である。

半導体基板134として、代表的には単結晶シリコン半導体基板が用いられる。半導体基板134に設けられる絶縁層102は酸化シリコン、酸窒化シリコン又は窒化シリコンなどにより形成される。半導体基板134に損傷層136を形成する際、イオンが照射されて半導体基板134の表面の平坦性が損なわれてしまうことがあるため、絶縁層102を設けることが好ましい。

40

#### 【0065】

半導体基板134の表面から所定の深さに損傷層136を形成するためには、水素イオンを含むイオンビームを半導体基板134に照射する。例えば、水素イオンに水素クラスターイオンを混在させ、表面から一定の深さの領域に損傷層136を形成する。水素クラスターイオンとして、例えば $H_3^+$ イオンが適用される。

水素クラスターイオンを適用することで、ドーザ量を一定とした場合でも水素を多く半導体基板134に導入することができ、損傷層136の形成を容易にする。

#### 【0066】

50

半導体基板 134 の表面から損傷層 136 までの深さは、水素イオンの加速エネルギーによって制御される。損傷層 136 の深さにより半導体基板 134 から分離される半導体層 104 の厚さが決まる。

損傷層 136 は半導体基板 134 の表面から 1 μm 未満の深さ、すなわち 50 nm 乃至 500 nm の深さに水素濃度のピーク位置が存在するように形成する。

#### 【0067】

<支持基板に半導体基板を貼り合わせる段階(図8(B))>

半導体基板 134 の絶縁層 102 が形成された面を支持基板 100 に密着させる。支持基板 100 に絶縁層 102 が密着することにより、水素結合力やファン・デル・ワールス力が作用して、支持基板 100 に半導体基板 134 が固定される。

10

#### 【0068】

支持基板 100 及び絶縁層 102 の表面が親水性であると、水酸基や水分子が有効に作用して水素結合を形成しやすくなる。さらに熱処理を行うと水分子が分解しシラノール基(Si-OH)を形成して水素結合が促進される。さらに高温で熱処理をすると、水素が抜けてシロキサン結合(O-Si-O)が形成されて共有結合となり、半導体基板 134 と支持基板 100 の結合強度が向上する。

#### 【0069】

<半導体基板を分離し支持基板上に半導体層を形成する段階(図8(C))>

半導体基板 134 を支持基板 100 に貼り合わせた状態で熱処理を行う。熱処理は 400 から 700 の温度範囲で行う。熱処理によって損傷層 136 が脆化し、支持基板 100 上に半導体層 104 を残した状態で半導体基板 134 を分離させることができる。

20

このような基板を使用して実施の形態 1 及び 2 の半導体装置を製造することができる。

#### 【0070】

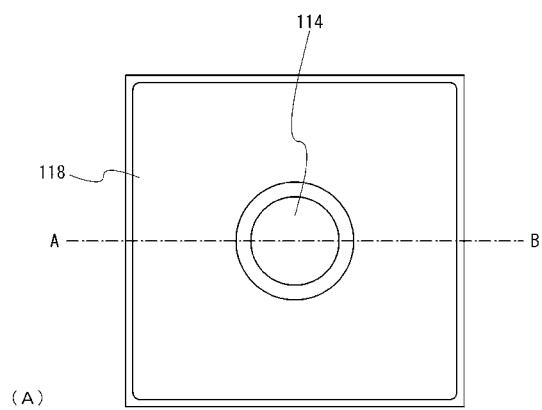

(実施の形態 5)

本形態は、半導体基板を用いた半導体装置の一例を示す。本形態は、炭化珪素半導体を含む半導体装置を提供するための構成を例示する。

図9(A)は半導体装置の平面図を示し、図9(B)はこの平面図の A - B 切断線に対応する断面図を示す。

#### 【0071】

図9(A)及び(B)は半導体基板 138 の表面に炭化物半導体領域 106 が設けられ、この炭化物半導体領域 106 にチャネル領域の全部又は一部が形成される半導体装置の一例を示す。

30

#### 【0072】

ゲート電極 114、第1不純物領域 108、第2不純物領域 110、ソース電極 118 の構成は実施の形態 1 と同様である。ドレイン電極 120 は半導体基板 138 の裏面(ゲート電極が設けられる面と反対側の面)に設けられている。なお、ドレイン電極 120 が半導体基板 138 と接触する領域に、第2不純物領域 110 と同じ導電型を有する第3不純物領域 122 が設けられていても良い。

#### 【0073】

半導体基板 138 の表面側には炭化物半導体領域 106 が設けられている。半導体基板 138 を構成する半導体材料と比べ、炭化物半導体領域 106 のエネルギー・ギャップは大きい値を有している。半導体基板 138 が単結晶シリコン半導体であれば、炭化物半導体領域 106 は炭化珪素半導体が適用される。

40

#### 【0074】

炭化物半導体領域 106 は、半導体基板 138 の表面から少なくとも 5 nm 乃至 15 nm の深さにまで形成される。第1不純物領域 108 の(半導体基板の表面からの)深さは、炭化物半導体領域 106 よりも浅くても良いし、炭化物半導体領域 106 と同程度の深さ又はそれよりも深く形成されていても良い。したがって、チャネル形成領域は炭化物半導体領域 106 を少なくとも一部に含んで形成されるとみなすこともできる。

50

#### 【0075】

半導体基板 138 を n 型、第 1 不純物領域 108 を p 型、第 2 不純物領域 110 を n 型とすると、ソース電極 118 とドレイン電極 120 は n p n 接合が介在し、ゲート電極 114 にバイアスを印加しない場合には僅かな電流しか流れない。

#### 【0076】

ゲート電極 114 に正バイアスを印加すると、ゲート電極 114 と重なる第 1 不純物領域 108 のゲート絶縁層 112 との界面側に負の電荷（電子）が誘起され、ソース電極 118 とドレイン電極 120 間に電流が流れる。チャネル形成領域は第 1 不純物領域 108 に形成される。

#### 【0077】

チャネル形成領域が炭化物半導体領域 106 の領域に形成されると絶縁破壊電圧が向上する。これは Si - C 結合の原子間距離が約 0.18 nm と短く、結合エネルギーが高く、炭化珪素半導体がシリコン半導体に比べ約 3 倍のエネルギー・ギャップを有していることに起因している。

#### 【0078】

そのためチャネル形成領域が炭化物半導体領域 106 に形成されるようにすると、シリコン半導体基板にチャネル形成領域を構成した場合に比べて固有オン抵抗が 2 枝半ほど小さくて済む。また、熱伝導度がシリコンの 3 倍ほど大きいので熱放散性が良い。それにより、半導体装置が扱える単位面積当たりの電流密度が大きくなる。

#### 【0079】

##### （実施の形態 6）

本形態は、半導体基板を用いバイポーラ動作をする半導体装置の一例を示す。本形態は、炭化珪素半導体を含む半導体装置を提供するための構成を例示する。

図 10 (A) は半導体装置の平面図を示し、図 10 (B) はこの平面図の A - B 切断線に対応する断面図を示す。

#### 【0080】

図 10 (A) 及び (B) は半導体基板 138 の表面に炭化物半導体領域 106 が設けられ、その領域にチャネル形成領域が含まれると共にバイポーラ動作をする半導体装置の一例を示す。

本形態の半導体装置は、実施の形態 3 における半導体装置と構成及び動作原理は同様である。

#### 【0081】

半導体基板 138 の表面側には、炭化物半導体領域 106 が設けられている。

実施の形態 3 における半導体装置と同様に、本形態の半導体装置もゲート電極 114 に正のバイアスを印加すると第 1 不純物領域 108 にチャネルが形成される。第 3 不純物領域 122 を p 型としたことにより、オン状態では第 3 不純物領域 122 より半導体層 104 にホールが注入される。それにより、オン状態となる電圧が低くなる。

#### 【0082】

本形態に係る半導体装置は、入力側に絶縁ゲート型電界効果トランジスタの構成を有し、出力側がバイポーラトランジスタの構成を備えたものである。この半導体装置は、ゲート電極 114 とエミッタ電極 130 間の電圧で駆動され、ゲート電極 114 への入力信号によってオン・オフ動作をする。

この半導体装置の構成は、スイッチング動作を高速化することが可能であり、オン抵抗が低いことから自己発熱が抑えられ、大電力の制御をすることが容易となる。

#### 【0083】

##### （実施の形態 7）

本形態は、図 11 を参照して、インバータを備えた太陽光発電システムの一例を示す。この太陽光発電システムは、住宅等に設置される構成を示す。

#### 【0084】

この住宅用の太陽光発電システムは、発電した電気を住宅内で消費することができるが、余剰電力は配電線 154 に戻すことができる。また太陽光発電システムが発電すること

10

20

30

40

50

ができない夜間や発電量が低下する雨天時には、配電線 154 から電気の供給を受けることができる。

【0085】

太陽光のエネルギーを電気エネルギーに変換する太陽電池パネル 140 は、直流電力を生成する。インバータ 144 は、その直流電力を交流電力に変換する。インバータ 144 から出力される交流電力は、各種の電気器具 150 を動作させる電力として使用される。

【0086】

住宅内で消費されず余った電力は、配電線 154 に繋いで電力会社に売却することも可能である。直流開閉器 142 は太陽電池パネル 140 とインバータ 144 とを接続又は遮断を制御するために設けられている。また、交流開閉器 148 はトランス 152 を介して配電線 154 と分電盤 146 との接続又は遮断を制御するために設けられている。

10

【0087】

インバータに実施の形態 1 乃至 6 の半導体装置を適用することにより、インバータを小型化することができ、電力損失の少ない高効率の太陽光発電システムを実現することができる。

【符号の説明】

【0088】

|     |          |

|-----|----------|

| 100 | 支持基板     |

| 102 | 絶縁層      |

| 104 | 半導体層     |

| 106 | 炭化物半導体領域 |

| 108 | 第1不純物領域  |

| 110 | 第2不純物領域  |

| 112 | ゲート絶縁層   |

| 114 | ゲート電極    |

| 116 | 絶縁層      |

| 118 | ソース電極    |

| 120 | ドレイン電極   |

| 122 | 第3不純物領域  |

| 124 | 第1マスク層   |

| 126 | 第2マスク層   |

| 128 | 第3マスク層   |

| 130 | エミッタ電極   |

| 132 | コレクタ電極   |

| 134 | 半導体基板    |

| 136 | 損傷層      |

| 138 | 半導体基板    |

| 140 | 太陽電池パネル  |

| 142 | 直流開閉器    |

| 144 | インバータ    |

| 146 | 分電盤      |

| 148 | 交流開閉器    |

| 150 | 電気器具     |

| 152 | トランス     |

| 154 | 配電線      |

20

30

40

【図1】

(A)

(B)

【図2】

(A)

(B)

(B)

【図3】

(A)

(B)

【図4】

(A)

(B)

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

## フロントページの続き

| (51) Int.CI.                    | F I            | テーマコード(参考) |

|---------------------------------|----------------|------------|

| <i>H 0 1 L 21/265 (2006.01)</i> | H 0 1 L 29/78  | 6 5 5 A    |

|                                 | H 0 1 L 29/78  | 6 1 6 U    |

|                                 | H 0 1 L 29/78  | 6 1 6 L    |

|                                 | H 0 1 L 29/78  | 6 1 3      |

|                                 | H 0 1 L 21/265 | Q          |

F ターム(参考) 5F110 AA13 AA28 BB12 CC02 DD01 DD02 DD03 DD05 DD06 DD13

DD14 DD15 EE04 EE06 EE09 EE24 FF02 FF04 FF22 FF23

FF29 FF30 GG01 GG02 GG12 GG13 GG19 GG25 GG32 GG41

GG42 HJ01 HK08 HK09 HK13 HK14 HK21 HM04 HM12 NN02

QQ17