(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6418861号

(P6418861)

(45) 発行日 平成30年11月7日(2018.11.7)

(24) 登録日 平成30年10月19日(2018.10.19)

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| (51) Int.Cl.  | F 1       |        |       |         |

| HO 1 L 21/336 | (2006.01) | HO 1 L | 29/78 | 6 1 7 J |

| HO 1 L 29/786 | (2006.01) | HO 1 L | 29/78 | 6 1 8 B |

| HO 1 L 21/28  | (2006.01) | HO 1 L | 29/78 | 6 1 6 V |

| HO 1 L 29/417 | (2006.01) | HO 1 L | 29/78 | 6 1 7 N |

| GO 2 F 1/1368 | (2006.01) | HO 1 L | 29/78 | 6 1 7 K |

請求項の数 3 (全 63 頁) 最終頁に続く

|              |                              |           |                                                |

|--------------|------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2014-189001 (P2014-189001) | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成26年9月17日 (2014.9.17)       | (72) 発明者  | 石原 典隆<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号    | 特開2015-84416 (P2015-84416A)  | (72) 発明者  | 太田 将志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成27年4月30日 (2015.4.30)       | (72) 発明者  | 津吹 将志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日        | 平成29年9月12日 (2017.9.12)       |           |                                                |

| (31) 優先権主張番号 | 特願2013-196333 (P2013-196333) |           |                                                |

| (32) 優先日     | 平成25年9月23日 (2013.9.23)       |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                     |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極層と、

前記ゲート電極層と接するゲート絶縁層と、

前記ゲート絶縁層を介して前記ゲート電極層と重なる酸化物半導体層と、

前記酸化物半導体層と接し、前記酸化物半導体層を介して前記ゲート絶縁層と重なる金属酸化物層と

前記金属酸化物層に接し、銅を含む一対の電極層と、を有し、

前記金属酸化物層は、In-M酸化物 (Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf) で構成され、

前記金属酸化物層に含まれるInとMの原子数比をIn : M = x : yとしたとき、y / (x + y)は、0.75以上1未満であることを特徴とする半導体装置。

## 【請求項 2】

第1のゲート電極層と、

前記第1のゲート電極層と接する第1のゲート絶縁層と、

前記第1のゲート絶縁層を介して前記第1のゲート電極層と重なる酸化物半導体層と、

前記酸化物半導体層と接し、前記酸化物半導体層を介して前記第1のゲート絶縁層と重なる金属酸化物層と

前記金属酸化物層に接し、銅を含む一対の電極層と、

前記一対の電極層上に接する第2のゲート絶縁層と、

10

20

前記第2のゲート絶縁層及び前記金属酸化物層を介して、前記酸化物半導体層と重なる第2のゲート電極層と、を有し、

前記金属酸化物層は、In-M酸化物（Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf）で構成され、

前記金属酸化物層に含まれるInとMの原子数比をIn : M = x : yとしたとき、y / (x + y)は、0.75以上1未満であり、

前記第1のゲート電極層及び前記第2のゲート電極層は、電気的に接続されることを特徴とする半導体装置。

【請求項3】

請求項1又は2において、

10

前記元素Mとして、ガリウムを含有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、物、方法、又は製造方法に関する。又は、本発明は、プロセス、マシン、マニュファクチャ、又は組成物（コンポジション・オブ・マター）に関する。特に、本発明の一態様は、半導体装置及びその作製方法に関する。

【0002】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。電気光学装置、画像表示装置（単に表示装置とも表記する）、半導体回路、発光装置、蓄電装置、記憶装置及び電子機器は半導体装置を有する場合がある。

20

【背景技術】

【0003】

液晶表示装置や発光表示装置に代表される表示装置や集積回路（IC）の多くに用いられているトランジスタの半導体材料として、アモルファスシリコン、単結晶シリコン、又は多結晶シリコンなどのシリコン半導体が知られている。また、その他の半導体材料として酸化物半導体が注目されている。例えば、酸化物半導体として、酸化亜鉛又はIn-Ga-Zn系酸化物をチャネルに用いたトランジスタを表示装置に適用する技術が開示されている（特許文献1）。又は、酸化物半導体として、多結晶In-Ga酸化物をチャネルに用いたトランジスタを表示装置に適用する技術が開示されている（非特許文献1）。

30

【0004】

また、表示装置の大面積化及び高精細化に伴う、配線抵抗の増大及び寄生容量の増大に起因する配線遅延を抑制するため、銅、アルミニウム、金、銀等の低抵抗材料を用いて配線を形成する技術が検討されている（特許文献2）。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007-096055号公報

【特許文献2】特開2004-133422号公報

【非特許文献】

40

【0006】

【非特許文献1】Yasuhiro Terai et al. , 「A Polycrystalline Oxide TFT Driven AM-OLED Display」、IDW'11、pp. 61-64

【発明の概要】

【発明が解決しようとする課題】

【0007】

酸化物半導体を用いたトランジスタにおいて、酸化物半導体層中に含まれる不純物（代表的には、絶縁層の構成元素であるシリコンや、炭素、配線の構成材料である銅等）が多いと、トランジスタの電気特性（例えば、オン電流特性）の低下要因となる。

50

## 【0008】

そこで、本発明の一態様は、酸化物半導体を用いたトランジスタ等の半導体装置において、酸化物半導体層に含まれる不純物濃度を低減することを課題の一とする。又は、本発明の一態様は、酸化物半導体を用いた半導体装置などにおいて、電気特性を向上させることを課題の一とする。又は、本発明の一態様は、酸化物半導体を用いた半導体装置などにおいて、信頼性を向上させることを課題の一とする。又は、本発明の一態様は、新規な半導体装置などを提供することを課題の一とする。

## 【0009】

なお、これらの課題の記載は、他の課題の記載を妨げるものではない。また、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。また、上記以外の課題は、明細書等の記載から自ずと明らかになるものであり、明細書等の記載から上記以外の課題を抽出することが可能である。 10

## 【課題を解決するための手段】

## 【0010】

本発明の一態様は、酸化物半導体層と、酸化物半導体層と接し、In - M酸化物 (Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf) で構成される金属酸化物層と、金属酸化物層に接し、銅、アルミニウム、金又は銀を含む導電層と、を有し、金属酸化物層に含まれるInとMの原子数比をIn : M = x : yとしたとき、y / (x + y) は、0.75以上1未満である半導体装置である。 20

## 【0011】

または、本発明の一態様は、ゲート電極層と、ゲート電極層と接するゲート絶縁層と、ゲート絶縁層を介してゲート電極層と対向する酸化物半導体層と、酸化物半導体層と接し、In - M酸化物 (Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf) で構成される金属酸化物層と金属酸化物層に接し、銅、アルミニウム、金又は銀を含む一対の電極層と、を有し、金属酸化物層に含まれるInとMの原子数比をIn : M = x : yとしたとき、y / (x + y) は、0.75以上1未満である半導体装置である。 20

## 【0012】

または、本発明の一態様は、第1のゲート電極層と、第1のゲート電極層と接する第1のゲート絶縁層と、第1のゲート絶縁層を介して第1のゲート電極層と対向する酸化物半導体層と、酸化物半導体層と接し、In - M酸化物 (Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf) で構成される金属酸化物層と金属酸化物層に接し、銅、アルミニウム、金又は銀を含む一対の電極層と、一対の電極層上に接する第2のゲート絶縁層と、第2のゲート絶縁層を介して、酸化物半導体層と対向する第2のゲート電極層と、を有し、金属酸化物層に含まれるInとMの原子数比をIn : M = x : yとしたとき、y / (x + y) は、0.75以上1未満であり、第1のゲート電極層及び第2のゲート電極層は、第1のゲート絶縁層及び第2のゲート絶縁層に設けられた開口部において電気的に接続する半導体装置である。 30

## 【0013】

上記の半導体装置において、酸化物半導体層は、一対の電極層とそれぞれ接する第1の側面及び第2の側面と、第1のゲート電極層又は第2のゲート電極層と対向する第3の側面及び第4の側面と、を有していてもよい。 40

## 【0014】

または、上記の半導体装置において、元素Mとして、ガリウムを含有することが好ましい。

## 【0015】

または、上記の半導体装置において、酸化物半導体層は、第1の酸化物半導体層と、第1の酸化物半導体層と金属酸化物層の間に位置する第2の酸化物半導体層と、の積層構造を有していてもよい。その場合、第2の酸化物半導体層の電子親和力は、第1の酸化物半導体層の電子親和力よりも小さく、且つ金属酸化物層の電子親和力よりも大きいことが好ましい。 50

## 【0016】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

## 【0017】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

10

## 【発明の効果】

## 【0018】

本発明の一態様によって、酸化物半導体層に含まれる不純物濃度を低減することができる。又は、本発明の一態様によって、酸化物半導体を用いた半導体装置などにおいて、電気特性を向上させることができる。又は、本発明の一態様によって、酸化物半導体を用いた半導体装置などの信頼性を向上させることができる。又は、本発明の一態様によって、新規な半導体装置などを提供することができる。なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

20

## 【図面の簡単な説明】

## 【0019】

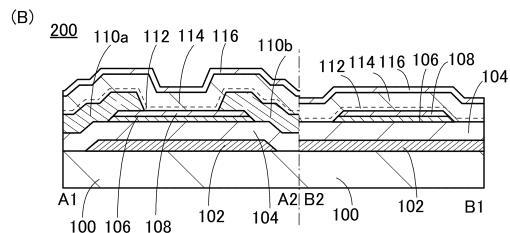

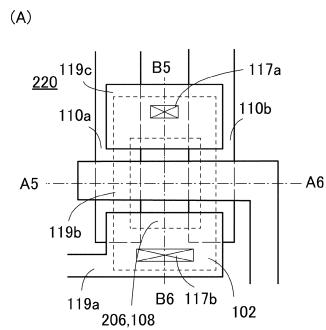

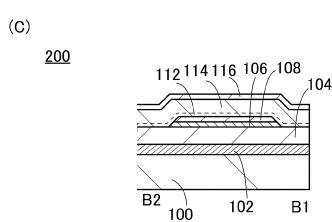

【図1】本発明の一態様に係るトランジスタを示す平面図及び断面図。

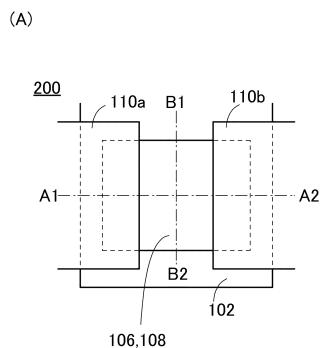

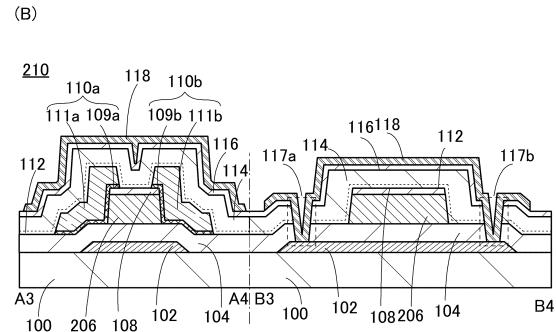

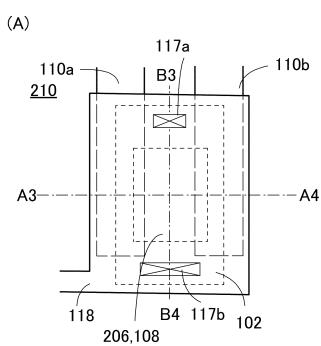

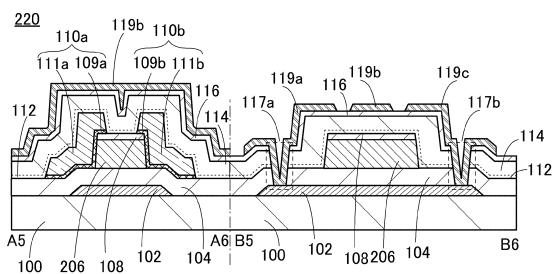

【図2】本発明の一態様に係るトランジスタを示す平面図及び断面図。

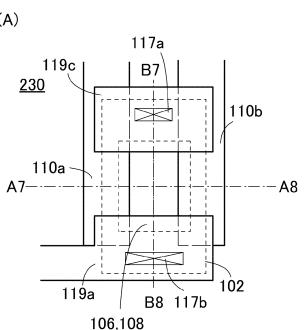

【図3】本発明の一態様に係るトランジスタを示す平面図及び断面図。

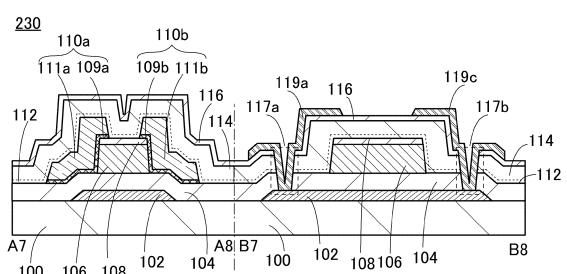

【図4】本発明の一態様に係るトランジスタを示す平面図及び断面図。

【図5】本発明の一態様に係るトランジスタの作製工程を示す図。

【図6】本発明の一態様に係るトランジスタの作製工程を示す図。

【図7】本発明の一態様に係るトランジスタを示す平面図、断面図及びバンド図。

30

【図8】C A A C - O S の断面におけるC s 補正高分解能T E M像、およびC A A C - O S の断面模式図。

【図9】酸化物半導体膜のナノビーム電子回折パターンを示す図、及び透過電子回折測定装置の一例を示す図。

【図10】透過電子回折測定による構造解析の一例を示す図、及び平面T E M像。

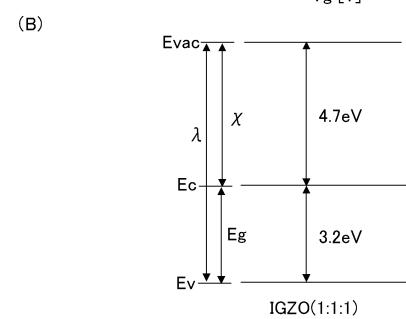

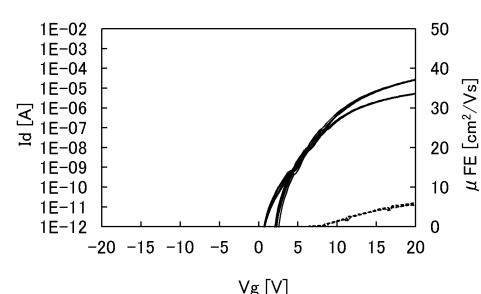

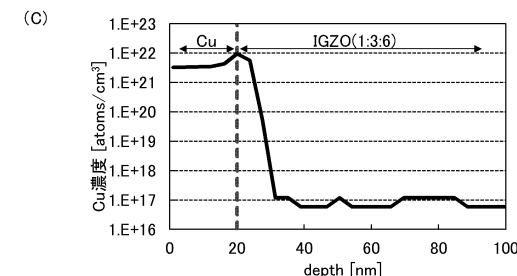

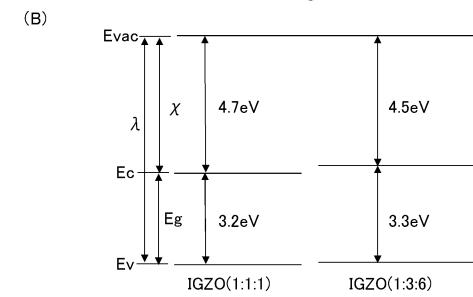

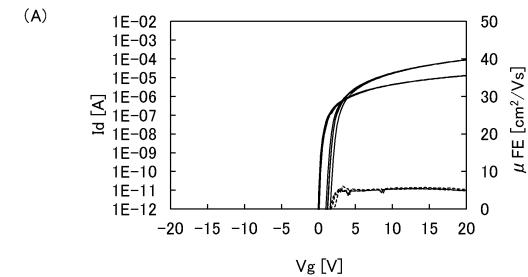

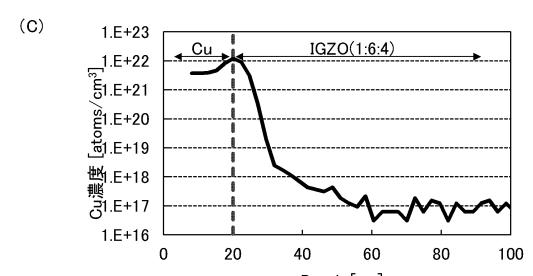

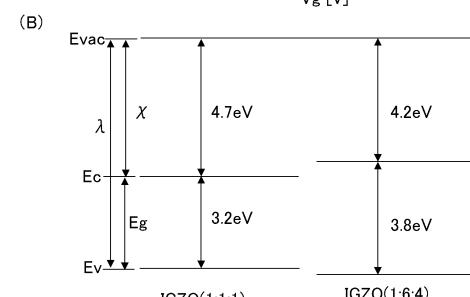

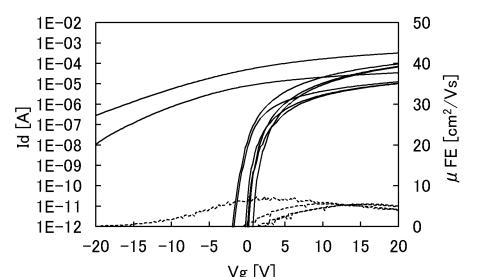

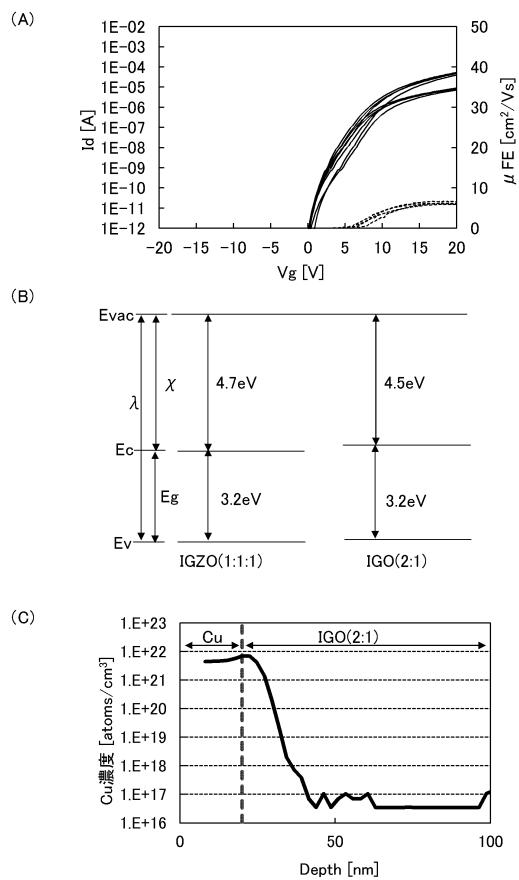

【図11】トランジスタのI d - V g 特性、バンドダイヤグラム図、及びS I M S分析結果を説明する図。

【図12】トランジスタのI d - V g 特性、及びバンドダイヤグラム図。

【図13】トランジスタのI d - V g 特性、バンドダイヤグラム図、及びS I M S分析結果を説明する図。

40

【図14】トランジスタのI d - V g 特性、バンドダイヤグラム図、及びS I M S分析結果を説明する図。

【図15】トランジスタのI d - V g 特性、バンドダイヤグラム図、及びS I M S分析結果を説明する図。

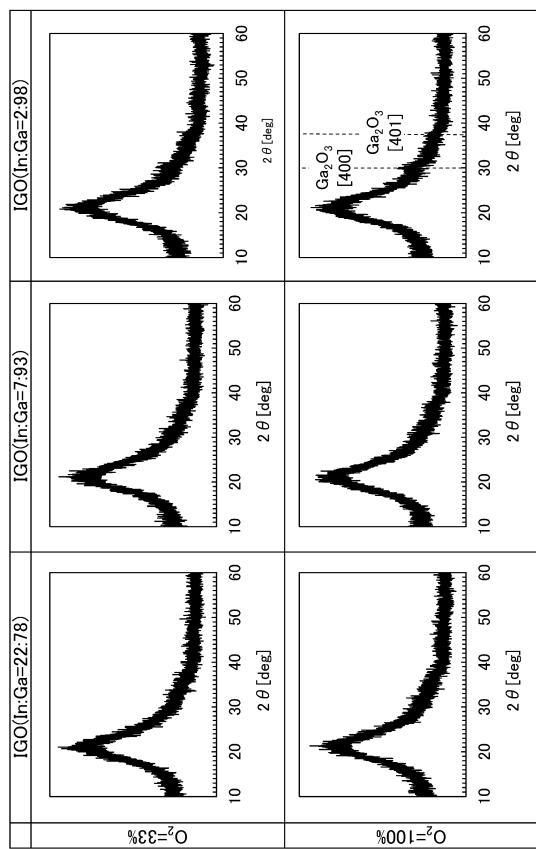

【図16】X R D測定結果を説明する図。

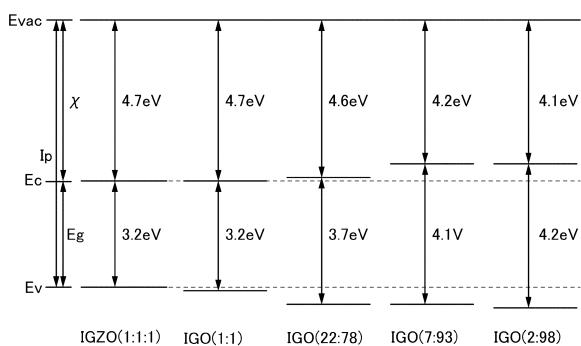

【図17】バンドダイヤグラムを説明する図。

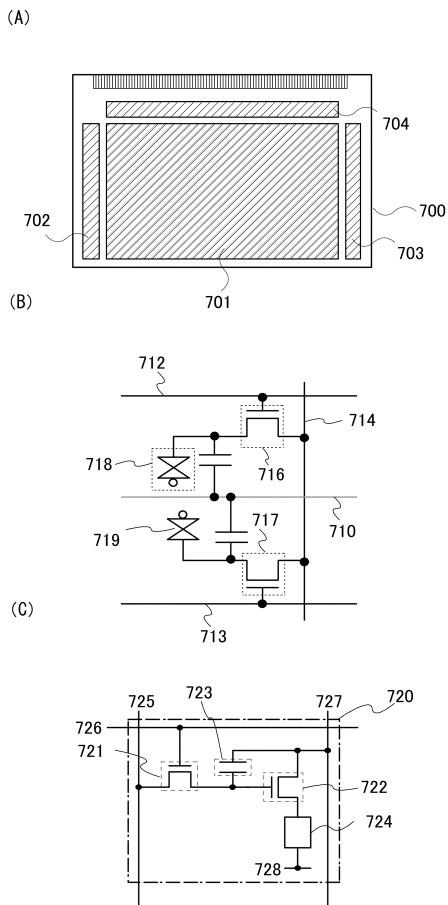

【図18】本発明の一態様に係る表示装置の構成を示す図及び回路図。

【図19】本発明の一態様に係る表示モジュールを説明する図。

【図20】本発明の一態様に係る電子機器を説明する図。

【図21】本発明の一態様に係るトランジスタを示す断面図及びバンド図。

50

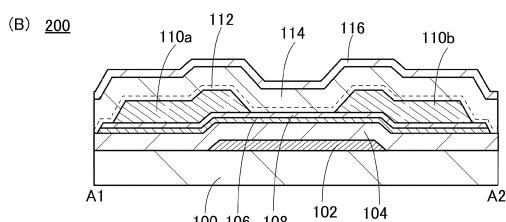

【図22】本発明の一態様に係るトランジスタを示す平面図及び断面図。

【図23】C A A C - O Sの平面におけるC s補正高分解能T E M像。

【図24】C A A C - O Sおよび単結晶酸化物半導体のX R Dによる構造解析を説明する図。

【図25】C A A C - O Sの電子回折パターンを示す図。

【図26】I n - G a - Z n酸化物の電子照射による結晶部の変化を示す図。

【図27】C A A C - O Sおよびn c - O Sの成膜モデルを説明する模式図。

【図28】I n G a Z n O <sub>4</sub>の結晶、およびペレットを説明する図。

【図29】C A A C - O Sの成膜モデルを説明する模式図。

【発明を実施するための形態】

10

【0020】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態において、同一部分又は同様の機能を有する部分には、同一の符号又は同一のハッチパターンを異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0021】

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

20

【0022】

また、本明細書等にて用いる第1、第2等の序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば「第1の」を「第2の」又は「第3の」等と適宜置き換えて説明することができる。

【0023】

また、「ソース」や「ドレイン」の機能は、回路動作において電流の方向が変化する場合などには適宜入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」の用語は入れ替えて用いることができる。

【0024】

また、本明細書等において、「上」や「下」の用語は、構成要素の位置関係が「直上」又は「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極層」との表現であれば、ゲート絶縁層とゲート電極層との間に他の構成要素を含むものを除外しない。「下」についても同様である。

30

【0025】

本明細書等において「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

【0026】

また、本明細書等において、結晶が三方晶又は菱面体晶である場合、六方晶系として表す。

40

【0027】

(実施の形態1)

本実施の形態では、本発明の一態様である半導体装置及びその作製方法について。図1乃至図6を参照して説明する。

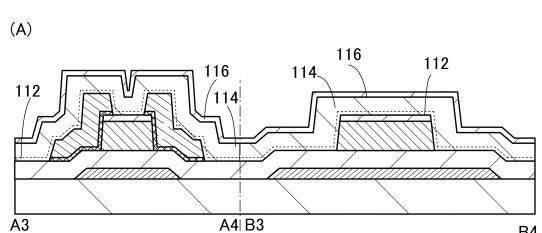

【0028】

<トランジスタの構成例1>

図1(A)及び図1(B)に本実施の形態の半導体装置が有するトランジスタ200の平面図及び断面図を示す。図1に示すトランジスタ200は、チャネルエッチ型のトランジスタである。図1(A)は、トランジスタ200の平面図であり、図1(B)は、図1(

50

A) の一点鎖線 A 1 - A 2 間及び B 1 - B 2 間の断面図である。なお、図 1 (A) では明瞭化のため、基板 100、トランジスタ 200 の構成要素の一部（例えば、ゲート絶縁層）等を省略して図示している。

【0029】

図 1 (A) 及び図 1 (B) に示すトランジスタ 200 は、基板 100 上に形成されたゲート電極層 102 と、ゲート電極層 102 と接するゲート絶縁層 104 と、ゲート絶縁層 104 を介してゲート電極層 102 と対向する酸化物半導体層 106 と、酸化物半導体層 106 上の金属酸化物層 108 と、金属酸化物層 108 に接する一対の電極層 110a、110b と、を含んで構成される。また、一対の電極層 110a、電極層 110b 及び金属酸化物層 108 上に形成された酸化物絶縁層 112、酸化物絶縁層 114 及び窒化物絶縁層 116 をトランジスタ 200 の構成要素に含めてよい。

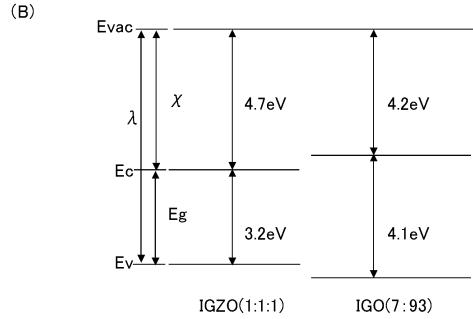

【0030】

トランジスタ 200 において、チャネルが形成される酸化物半導体層 106 の上面に接して設けられる金属酸化物層 108 は、一対の電極層 110a、110b の構成元素が酸化物半導体層 106 に拡散することを抑制するバリア層として機能する。又は、金属酸化物層 108 を設けることで、酸化物半導体層 106 の上層に設けられた酸化物絶縁層 112 等の構成元素が、酸化物半導体層 106 に混入することを抑制することもできる。チャネルが形成される酸化物半導体層 106 への不純物の混入を抑制することで、トランジスタ 200 の電気特性の低下を抑制することができる。

【0031】

金属酸化物層 108 には、In - M 酸化物 (M は、Ti、Ga、Y、Zr、La、Ce、Nd または Hf) で表される金属酸化物を用いることができる。ただし、金属酸化物層 108 がチャネル形成領域の一部として機能することを防止するため、導電率が十分に低い材料を用いるものとする。または、金属酸化物層 108 には、電子親和力（真空準位と伝導帯下端のエネルギー差）が酸化物半導体層 106 よりも小さく、伝導帯下端のエネルギーが酸化物半導体層 106 の伝導帯下端エネルギーと差分（バンドオフセット）を有する材料を用いるものとする。また、ドレイン電圧の大きさに依存したしきい値電圧の差が生じることを抑制するためには、金属酸化物層 108 の伝導帯下端のエネルギーが、酸化物半導体層 106 の伝導帯下端のエネルギーよりも 0.2 eV 以上真空準位に近い材料、好みしくは 0.5 eV 以上真空準位に近い材料を適用することが好みしい。

【0032】

また、In に対する元素 M の原子数比を高めることで、金属酸化物層 108 のエネルギーギャップを大きくし、電子親和力を小さくすることができる。よって、酸化物半導体層 106 との間に伝導帯のバンドオフセットを形成し、金属酸化物層 108 にチャネルが形成されることを抑制するためには、金属酸化物層 108 は、In : M = x : y [原子数比] とすると、y / (x + y) を、0.75 以上 1 未満、好みしくは、0.78 以上 1 未満、より好みしくは 0.80 以上 1 未満とすることが好みしい。ただし、金属酸化物層 108 は、主成分であるインジウム、M 及び酸素以外の元素が不純物として混入していてもよい。その際の不純物の割合は、0.1% 以下が好みしい。In : M = x : y [原子数比] の測定は、誘導結合プラズマ質量分析法 (Inductively Coupled Plasma Mass Spectrometry : ICP-MS 分析法) により行うことができる。例えば In : M = x : y [原子数比] とする場合、In : M = x : y は、ターゲットの組成ではなく、スパッタリング法により得られる金属酸化物膜の組成を指しており、y / (x + y) を、0.75 以上 1 未満とする。

【0033】

また、金属酸化物層 108 をスパッタリング法によって形成する場合、In に対する元素 M の原子数比を高めることで、成膜時のパーティクル数を低減させることが可能である。パーティクル数を低減させるためには、In : M = x : y [原子数比] とすると、y / (x + y) を、0.90 以上、例えば 0.93 とするとよい。ただし、金属酸化物層 108 をスパッタリング法によって形成する場合、In に対する M の原子数比が高すぎると、タ

10

20

30

40

50

一ゲットの絶縁性が高く、DC放電を用いた成膜が困難となり、RF放電を適用する必要が生じる。よって、大面積基板への対応が可能なDC放電を用いて成膜を行うためには、 $y / (x + y)$ を0.96以下、好ましくは0.95以下、例えば0.93とするとよい。大面積基板に対応した成膜方法を適用することで、半導体装置の生産性を高めることができる。

【0034】

なお、トランジスタ200において、チャネルが形成される酸化物半導体層106は、側面においてソース電極層及びドレイン電極層として機能する一対の電極層110a、110bと接し、当該接する領域においてソース領域及びドレイン領域が形成される。そのため、金属酸化物層108は、絶縁性を有していてもよい。

10

【0035】

なお、金属酸化物層108は、膜中にスピネル型の結晶構造が含まれないことが好ましい。金属酸化物層108の膜中にスピネル型の結晶構造を含む場合、当該スピネル型の結晶構造に起因して一対の電極層110a、110bの構成元素が酸化物半導体層106へ拡散してしまう場合があるためである。例えば、金属酸化物層108としてIn-M酸化物を適用し、Mとして2価の金属原子（例えば、亜鉛など）を含まない構成とすることで、スピネル型の結晶構造を含有しない金属酸化物層108を形成することができるため好ましい。

【0036】

金属酸化物層108の膜厚は、一対の電極層110a、110bの構成元素が酸化物半導体層106に拡散することを抑制することのできる膜厚以上であって、酸化物絶縁層112から酸化物半導体層106への酸素の供給を抑制する膜厚未満とする。例えば、金属酸化物層108の膜厚が10nm以上であると、一対の電極層110a、110bの構成元素の酸化物半導体層106への拡散を抑制することができる。また、金属酸化物層108の膜厚を100nm以下とすると、酸化物絶縁層112、114から酸化物半導体層106へ効果的に酸素を供給することができる。

20

【0037】

また、本実施の形態に示すトランジスタ200において、ソース電極層及びドレイン電極層として機能する一対の電極層110a、110bとしては、銅、アルミニウム、金、又は銀等の低抵抗材料からなる単体金属、若しくは合金、又はこれらを主成分とする化合物を含む、単層構造又は積層構造とすることが好ましい。一対の電極層110a、110bは配線としても機能するため、当該電極層を銅、アルミニウム、金又は銀等の低抵抗材料を含んで形成することで、基板100として大面積基板を用いた場合においても配線遅延を抑制した半導体装置を作製することが可能となる。

30

【0038】

一対の電極層110a、110bを2層構造とする場合、2層目の導電層の膜厚を大きくし、且つ銅、アルミニウム、金、又は銀等の低抵抗材料からなる単体金属、若しくは合金、又はこれらを主成分とする化合物を含む導電層とし、酸化物半導体層106の側面及び金属酸化物層108の側面及び上面に接する1層目の導電層には、上述の2層目の導電体に対するバリア層として機能する導電体を用いて形成することが好ましい。例えば、チタン、タンタル、モリブデン、タンゲステンの単体金属若しくは合金、又は窒化チタン、窒化タンタル、窒化モリブデン、窒化タンゲステン等を含む導電層をバリア層として用いることができる。また、一対の電極層110a、110bを3層構造とする場合、上述の1層目及び2層目上に接して、2層目の導電体に対するバリア層として機能する導電体を用いて3層目の導電層を形成することが好ましい。

40

【0039】

例えば、一対の電極層110a、110bを2層構造とする場合、チタン膜上にアルミニウム膜を積層した構造、タンゲステン膜上に銅膜を積層した構造、タンゲステン膜上にアルミニウム膜を積層した構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層した構造、チタン膜上に銅膜を積層した構造、タンゲステン膜上に銅膜を積層した構造等を

50

用いることが好ましい。また、一対の電極層 110a、110b を 3 層構造とする場合、1 層目及び 3 層目には、チタン、窒化チタン、モリブデン、又は窒化モリブデンでなる膜を形成し、2 層目には、銅、アルミニウム、金又は銀等の低抵抗材料でなる膜を形成することが好ましい。

【0040】

本実施の形態で示すトランジスタ 200 は、ソース電極層及びドレイン電極層として機能する一対の電極層として、銅、アルミニウム、金、又は銀等の低抵抗材料を含む電極層を用いることで、配線遅延を抑制した半導体装置を作製することができる。さらに、一対の電極層と接して、バリア層として機能する金属酸化物層 108 を設けることで、電気特性の低下を抑制し、良好な電気特性を有する半導体装置を提供することが可能となる。

10

【0041】

なお、電極層 110a、及び、電極層 110b の形成と、酸化物半導体層 106、及び、金属酸化物層 108 の形成とを、ハーフトーンマスク（または、グレートーンマスク、位相差マスクなど）を用いて形成することによって、マスク数を減らして、プロセス工程数を減らすようにしてもよい。この場合、レジストをアッシングすることなどにより、パターンを形成する。したがって、電極層 110a、及び、電極層 110b の下には、必ず、酸化物半導体層 106、及び、金属酸化物層 108 が設けられこととなる。図 1 において、ハーフトーンを用いた場合の平面図と断面図とを、図 22(A)(B)(C) に示す。

【0042】

20

以下に、本実施の形態の半導体装置に含まれるその他の構成要素について、詳細に説明する。

【0043】

（基板）

基板 100 の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板 100 として用いてよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板 100 として用いてよい。なお、基板 100 として、ガラス基板を用いる場合、第 6 世代 (1500 mm × 1850 mm)、第 7 世代 (1870 mm × 2200 mm)、第 8 世代 (2200 mm × 2400 mm)、第 9 世代 (2400 mm × 2800 mm)、第 10 世代 (2950 mm × 3400 mm) 等の大面積基板を用いることで、大型の表示装置を作製することができる。

30

【0044】

また、基板 100 として、可撓性基板を用い、可撓性基板上に直接、トランジスタ 200 を形成してもよい。または、基板 100 とトランジスタ 200 の間に剥離層を設けてよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板 100 より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ 200 は耐熱性の劣る基板や可撓性の基板にも転載できる。

40

【0045】

（ゲート電極層）

ゲート電極層 102 は、クロム、銅、アルミニウム、金、銀、亜鉛、モリブデン、タンタル、チタン、タングステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いてよい。また、ゲート電極層 102 は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜または窒化タングステン膜上にタングステン膜

50

を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

【0046】

また、ゲート電極層102は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

10

【0047】

また、ゲート電極層102とゲート絶縁層104との間に、In-Ga-Zn系酸窒化物半導体膜、In-Sn系酸窒化物半導体膜、In-Ga系酸窒化物半導体膜、In-Zn系酸窒化物半導体膜、Sn系酸窒化物半導体膜、In系酸窒化物半導体膜、金属窒化膜(InN、ZnN等)等を設けてもよい。これらの膜は5eV、好ましくは5.5eV以上の仕事関数を有し、酸化物半導体の電子親和力よりも大きい値であるため、酸化物半導体を用いたトランジスタのしきい値電圧をプラスにシフトすることができ、所謂ノーマリーオフ特性のスイッチング素子を実現できる。例えば、In-Ga-Zn系酸窒化物半導体膜を用いる場合、少なくとも酸化物半導体層106より高い窒素濃度、具体的には7原子%以上のIn-Ga-Zn系酸窒化物半導体膜を用いる。

20

【0048】

(ゲート絶縁層)

ゲート絶縁層104は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物などを用いればよく、積層または単層で設ける。

【0049】

また、ゲート絶縁層104として、ハフニウムシリケート(HfSiO<sub>x</sub>)、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、窒素が添加されたハフニウムアルミニート(HfAl<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用いることでトランジスタのゲートリークを低減できる。

30

【0050】

ゲート絶縁層104の厚さは、5nm以上400nm以下、より好ましくは10nm以上300nm以下、より好ましくは50nm以上250nm以下とするとよい。

【0051】

(酸化物半導体層)

酸化物半導体層106は、代表的には、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物(Mは、Ti、Ga、Y、Zr、La、Ce、Nd、またはHf)がある。

【0052】

酸化物半導体層106がIn-M-Zn酸化物(Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)の場合、In-M-Zn酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In-M、Zn>Mを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:M:Zn=1:1:1、In:M:Zn=1:1:1.2、In:M:Zn=3:1:2が好ましい。なお、成膜される酸化物半導体層106の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。

40

【0053】

なお、酸化物半導体層106がIn-M-Zn酸化物であるとき、Zn及びOを除いてのInとMの原子数比率は、好ましくはInが25atomic%より高く、Mが75atomic%未満、さらに好ましくはInが34atomic%より高く、Mが66atomic%

50

mic %未満とする。

【0054】

酸化物半導体層106は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタ200のオフ電流を低減することができる。

【0055】

酸化物半導体層106の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

【0056】

酸化物半導体層106としては、キャリア密度の低い酸化物半導体層を用いる。例えば、酸化物半導体層106は、キャリア密度が $1 \times 10^{17}$ 個/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ 個/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{13}$ 個/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{11}$ 個/cm<sup>3</sup>以下とする。

【0057】

なお、これらに限られず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体層106のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

【0058】

なお、酸化物半導体層106として、不純物濃度が低く、欠陥準位密度の低い酸化物半導体層を用いることで、さらに優れた電気特性を有するトランジスタを作製することができ好ましい。ここでは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体層にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが多い。また、高純度真性または実質的に高純度真性である酸化物半導体層は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体層は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長Lが $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} \text{ A}$ 以下という特性を得ることができる。

【0059】

従って、当該高純度真性、又は実質的に高純度真性の酸化物半導体層にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとすることができます。なお、酸化物半導体膜のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体層にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

【0060】

酸化物半導体層に含まれる水素は金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することができる。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体層106は水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体層106において、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる水素濃

10

20

30

40

50

度を、 $2 \times 10^{20}$  atoms/cm<sup>3</sup> 以下、好ましくは $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、 $5 \times 10^{18}$  atoms/cm<sup>3</sup> 未満、好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup> 以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup> 以下とする。

#### 【0061】

酸化物半導体層106において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体層106において酸素欠損が増加し、n型化してしまう。このため、酸化物半導体層106におけるシリコンや炭素の濃度、または金属酸化物層108と、酸化物半導体層106との界面近傍のシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、好ましくは $2 \times 10^{17}$  atoms/cm<sup>3</sup> 以下とする。

#### 【0062】

また、酸化物半導体層106において、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、好ましくは $2 \times 10^{16}$  atoms/cm<sup>3</sup> 以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体層106のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

#### 【0063】

また、酸化物半導体層106に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。従って、当該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下にすることが好ましい。

#### 【0064】

また、酸化物半導体層106は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、後述する CAAc-O<sub>S</sub> (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶構造、後述する微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、 CAAc-O<sub>S</sub> は最も欠陥準位密度が低い。

#### 【0065】

酸化物半導体層106は、例えば非晶質構造でもよい。非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

#### 【0066】

なお、酸化物半導体層106が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、 CAAc-O<sub>S</sub> の領域、単結晶構造の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、 CAAc-O<sub>S</sub> の領域、単結晶構造の領域のいずれか二種以上の領域を有する場合がある。また、混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、 CAAc-O<sub>S</sub> の領域、単結晶構造の領域のいずれか二種以上の領域の積層構造を有する場合がある。なお、酸化物半導体層106に接する金属酸化物層108は、例えば非晶質構造、微結晶構造、多結晶構造等とすることができます。

#### 【0067】

また、酸化物半導体層106と接して酸化物半導体と異なる構成元素（例えばシリコン）を有する絶縁層を設けた場合、酸化物半導体層106と該絶縁層との界面には、異種接合、不純物の混入等に起因した界面準位が形成されることがある。本実施の形態のトランジスタ200では、酸化物半導体層106と、酸化物半導体と異なる構成元素（例えばシリコン）を有しうる酸化物絶縁層112との間に、酸化物半導体と構成元素が同じである金

10

20

30

40

50

属酸化物層 108 が設けられている。このため、金属酸化物層 108 と酸化物絶縁層 112 の間ににおいて、不純物及び欠陥によりトラップ準位が形成されても、当該トラップ準位と酸化物半導体層 106との間には隔たりがある。この結果、酸化物半導体層 106 を流れる電子がトラップ準位に捕獲されにくく、トランジスタのオン電流を増大させることができると共に、電界効果移動度を高めることができる。また、トラップ準位に電子が捕獲されると、該電子がマイナスの固定電荷となってしまう。この結果、トランジスタのしきい値電圧が変動してしまう。しかしながら、酸化物半導体層 106 とトラップ準位との間に隔たりがあるため、トラップ準位における電子の捕獲を低減することが可能であり、しきい値電圧の変動を低減することができる。

## 【0068】

10

また、金属酸化物層 108 に含まれる元素 M は、酸素との結合力が高いため、元素 M の原子数比が高い金属酸化物層 108 は酸素欠損を形成しにくい。よって、金属酸化物層 108 に接する酸化物半導体層 106 における酸素欠損量を低減することが可能である。

## 【0069】

## (酸化物絶縁層)

酸化物絶縁層 112 は、酸素を透過する酸化物絶縁膜である。なお、酸化物絶縁層 112 は、後に形成する酸化物絶縁層 114 を形成する際の、金属酸化物層 108 及び酸化物半導体層 106 へのダメージ緩和膜としても機能する。

## 【0070】

20

酸化物絶縁層 112 としては、厚さが 5 nm 以上 150 nm 以下、好ましくは 5 nm 以上 50 nm 以下の酸化シリコン、酸化窒化シリコン等を用いることができる。なお、本明細書中において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

## 【0071】

また、酸化物絶縁層 112 は、欠陥量が少ないことが好ましく、代表的には、 ESR 測定により、シリコンのダングリングボンドに由来する  $g = 2.001$  に現れる信号のスピントン密度が  $3 \times 10^{17} \text{ spins/cm}^3$  以下であることが好ましい。これは、酸化物絶縁層 112 に含まれる欠陥密度が多いと、当該欠陥に酸素が結合してしまい、酸化物絶縁層 112 における酸素の透過量が減少してしまうためである。

30

## 【0072】

また、酸化物絶縁層 112 と金属酸化物層 108との界面における欠陥量が少ないことが好ましく、代表的には、 ESR 測定により、金属酸化物層 108 の欠陥に由来する  $g = 1.89$  以上  $1.96$  以下に現れる信号のスピントン密度が  $1 \times 10^{17} \text{ spins/cm}^3$  以下、さらには検出下限以下であることが好ましい。

## 【0073】

なお、酸化物絶縁層 112 においては、外部から酸化物絶縁層 112 に入った酸素が全て酸化物絶縁層 112 の外部に移動せず、酸化物絶縁層 112 にとどまる酸素もある。また、酸化物絶縁層 112 に酸素が入ると共に、酸化物絶縁層 112 に含まれる酸素が酸化物絶縁層 112 の外部へ移動することで、酸化物絶縁層 112 において酸素の移動が生じる場合もある。酸化物絶縁層 112 として酸素を透過する酸化物絶縁膜を形成すると、酸化物絶縁層 112 上に設けられる、酸化物絶縁層 114 から脱離する酸素を、酸化物絶縁層 112 を介して酸化物半導体層 106 に移動させることができる。

40

## 【0074】

酸化物絶縁層 112 に接するように酸化物絶縁層 114 が形成されている。酸化物絶縁層 114 は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、 TDS 分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18} \text{ atoms/cm}^3$  以上、好ましくは  $3.0 \times 10^{20} \text{ atoms/cm}^3$  以上である酸化物絶縁膜

50

縁膜である。なお、上記TDS分析時における基板温度としては100 以上700 以下、または100 以上500 以下の範囲が好ましい。

【0075】

酸化物絶縁層114としては、厚さが30 nm以上500 nm以下、好ましくは50 nm以上400 nm以下の、酸化シリコン、酸化窒化シリコン等を用いることができる。

【0076】

また、酸化物絶縁層114は、欠陥量が少ないことが好ましく、代表的には、ESR測定により、シリコンのダングリングボンドに由来する  $g = 2.001$  に現れる信号のスピントン密度が  $1.5 \times 10^{18} \text{ spins/cm}^3$  未満、更には  $1 \times 10^{18} \text{ spins/cm}^3$  以下であることが好ましい。なお、酸化物絶縁層114は、酸化物絶縁層112と比較して酸化物半導体層106から離れているため、酸化物絶縁層112より、欠陥密度が多くともよい。

10

【0077】

(窒化物絶縁層)

酸化物絶縁層114上に、酸素、水素、水、アルカリ金属、アルカリ土類金属等のプロッキング効果を有する窒化物絶縁層116を設けることで、酸化物半導体層106からの酸素の外部への拡散と、外部から酸化物半導体層106への水素、水等の侵入を防ぐことができる。窒化物絶縁層としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、酸素、水素、水、アルカリ金属、アルカリ土類金属等のプロッキング効果を有する窒化物絶縁層の代わりに、酸素、水素、水等のプロッキング効果を有する酸化物絶縁層としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

20

【0078】

<トランジスタの構成例2>

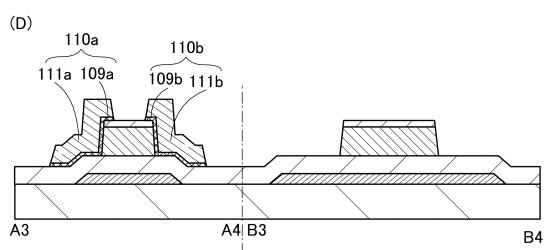

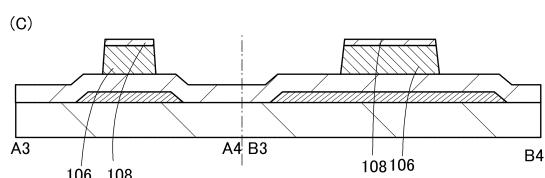

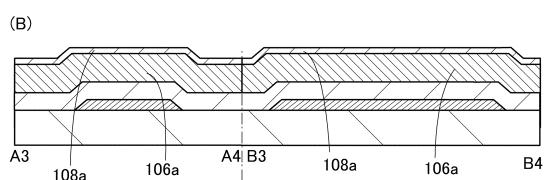

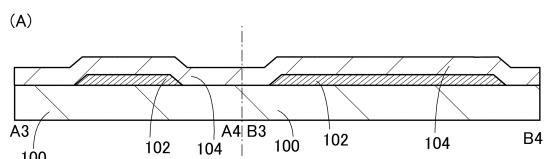

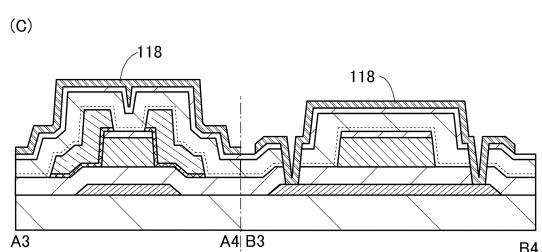

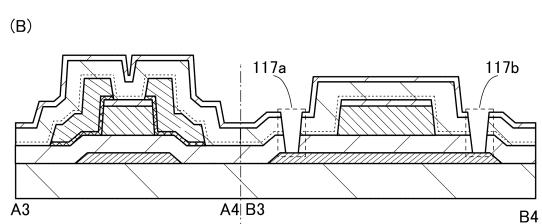

図2(A)及び図2(B)に本実施の形態の半導体装置が有するトランジスタ210の平面図及び断面図を示す。図2(A)は、トランジスタ210の平面図であり、図2(B)は、図2(A)の一点鎖線A3-A4間及びB3-B4間の断面図である。なお、図2(A)では明瞭化のため、基板100、トランジスタ210の構成要素の一部(例えば、ゲート絶縁層)等を省略して図示している。

30

【0079】

図2(A)及び図2(B)に示すトランジスタ210は、基板100上に形成されたゲート電極層102と、ゲート電極層102と接するゲート絶縁層104と、ゲート絶縁層104を介してゲート電極層102と対向する酸化物半導体層206と、酸化物半導体層206上の金属酸化物層108と、金属酸化物層108に接する一対の電極層110a、110bと、一対の電極層110a、電極層110b及び金属酸化物層108上に形成された酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116と、窒化物絶縁層116を上に設けられた電極層118と、を有する。

40

【0080】

トランジスタ210において、電極層118はバックゲート電極として機能する。また、電極層118と酸化物半導体層206との間に設けられた酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116を含む積層構造は、バックゲート電極に対するゲート絶縁層として機能する。また、電極層118は、ゲート絶縁層104、酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116に設けられた開口部117a、117bにおいて、ゲート電極層102に接続される。よって、電極層118とゲート電極層102とは、同じ電位が与えられる。

【0081】

図2に示すトランジスタ210は、窒化物絶縁層116上にバックゲート電極として機能する電極層118を有する点において、図1のトランジスタ200と相違する。その他の

50

構成は、トランジスタ200と同様であり、同様の効果を奏することができる。すなわち、トランジスタ210は、低抵抗材料を含む一対の電極層110a、110bと、チャネルが形成される酸化物半導体層206との間にバリア層として機能する金属酸化物層108を有する。これによって、酸化物半導体層206への不純物の混入及び拡散を抑制することができる。したがって、トランジスタ210は電気特性の低下が抑制されたトランジスタである。トランジスタ210の各構成要素の詳細は、トランジスタ200についての説明を参照することができる。

#### 【0082】

また、図2に示すトランジスタ210に含まれる酸化物半導体層206は、トランジスタ200に含まれる酸化物半導体層106と同様の材料を用いて構成され、膜厚が100nm以上、例えば100nm以上1000nm以下、好ましくは200nm以上1000nm以下である。また、トランジスタ210のチャネル長（一対の電極層110a、110b間の距離）は、0.5μm以上2μm以下とすることが好ましく、0.5μm以上1μm以下とすることがより好ましい。

#### 【0083】

図2(B)の断面図に示すように、酸化物半導体層206は、ゲート電極層102と、電極層118(バックゲート電極)のそれぞれと対向するように位置し、2つのゲート電極層に挟まれている。バックゲート電極として機能する電極層118のチャネル長方向の長さ及びチャネル幅方向の長さは、酸化物半導体層206のチャネル長方向の長さ及びチャネル幅方向の長さよりもそれぞれ長く、酸化物半導体層206の全体は、絶縁層(酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116)を介して電極層118に覆われている。また、電極層118とゲート電極層102とは、ゲート絶縁層104、酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116に設けられた開口部117a、117bにおいて接続されるため、酸化物半導体層206のチャネル幅方向の側面は、絶縁層(酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116)を介してバックゲート電極(電極層118)と対向している。

#### 【0084】

このような構成を有することで、トランジスタ210に含まれる酸化物半導体層206を、ゲート電極層102及び電極層118の電界によって電気的に囲むことができる。トランジスタ210のように、ゲート電極層及びバックゲート電極層の電界によって、チャネルが形成される酸化物半導体層を電気的に囲むトランジスタのデバイス構造をsurrounded channel(s-channel)構造と呼ぶことができる。

#### 【0085】

トランジスタ210は、s-channel構造を有するため、ゲート電極層102によってチャネルを誘起させるための電界を効果的に酸化物半導体層206に印加することができるため、トランジスタ210の電流駆動能力が向上し、高いオン電流特性を得ることが可能となる。また、オン電流を高くすることが可能であるため、トランジスタ210を微細化することが可能となる。また、トランジスタ210は、チャネルがゲート電極層102及び電極層118によって囲まれた構造を有するため、トランジスタ210の機械的強度を高めることができる。

#### 【0086】

なお、トランジスタ210の構造において、開口部117a、117bのいずれか一方を形成して、該開口部において電極層118及びゲート電極層102とを接続する構成としてもよい。

#### 【0087】

なお、トランジスタ210に含まれる一対の電極層110a、110bは、第1の導電層109a、109bと、第2の導電層111a、111bとの積層構造を有する。第1の導電層109a、109bには、先の電極層110a、110bの説明において1層目として例示した材料を適宜用いることができる。また、第2の導電層111a、111bには、先の電極層110a、110bの説明において2層目として例示した材料を適宜用い

10

20

30

40

50

ることができる。なお、トランジスタ 210 に含まれる一対の電極層 110a、110b は銅、アルミニウム、金又は銀を含んで構成される限り、図 2 の構成に限定されるものではなく、単層構造としてもよいし、3 層以上の積層構造としてもよい。

【0088】

<トランジスタの構成例 3>

図 3 (A) 及び図 3 (B) に本実施の形態の半導体装置が有するトランジスタ 220 の平面図及び断面図を示す。トランジスタ 220 は、図 2 のトランジスタ 210 の変形例である。図 3 (A) は、トランジスタ 220 の平面図であり、図 3 (B) は、図 3 (A) の一点鎖線 A5 - A6 間及び B5 - B6 間の断面図である。なお、図 3 (A) では明瞭化のため、基板 100、トランジスタ 220 の構成要素の一部（例えば、ゲート絶縁層）等を省略して図示している。

10

【0089】

図 3 (A) 及び図 3 (B) に示すトランジスタ 220 は、基板 100 上に形成されたゲート電極層 102 と、ゲート電極層 102 と接するゲート絶縁層 104 と、ゲート絶縁層 104 を介してゲート電極層 102 と対向する酸化物半導体層 206 と、酸化物半導体層 206 上のバリア層として機能する金属酸化物層 108 と、金属酸化物層 108 に接する一対の電極層 110a、110b と、一対の電極層 110a、電極層 110b 及び金属酸化物層 108 上に形成された酸化物絶縁層 112、酸化物絶縁層 114 及び窒化物絶縁層 116 と、窒化物絶縁層 116 を上に設けられた電極層 119a、119b、119c と、を有する。

20

【0090】

トランジスタ 220 において、金属酸化物層 108 及び絶縁層（酸化物絶縁層 112、酸化物絶縁層 114 及び窒化物絶縁層 116）を介して酸化物半導体層 206 と重なる電極層 119b は、バックゲート電極として機能する。また、電極層 119b と同じ層で形成される電極層 119a、119c は、ゲート絶縁層 104、酸化物絶縁層 112、酸化物絶縁層 114、及び窒化物絶縁層 116 に設けられた開口部 117a、117b においてそれぞれゲート電極層 102 と接続する。すなわち、電極層 119a、119c はゲート電極層 102 の一部として機能する。

【0091】

トランジスタ 220 は、トランジスタ 210 において、バックゲート電極として機能する電極層 118 が分離した構成を有する点において相違する。その他の構成はトランジスタ 210 と同様とすることができる。トランジスタ 220 の構成の詳細は、先のトランジスタ 210 についての説明を参照することが可能である。

30

【0092】

トランジスタ 220 に含まれる電極層 119a、119c は、上面形状において酸化物半導体層 206 と重なる領域を有し、開口部 117a、117b において酸化物半導体層 206 の側面と対向する。よって、トランジスタ 220 もトランジスタ 210 と同様に、酸化物半導体層 206 がゲート電極層 102、電極層 119a、119b、119c によって電気的に囲まれた s - channel 構造を有するため、ゲート電極層 102 によってチャネルを誘起させるための電界を効果的に酸化物半導体層 206 に印加することができる。よって、トランジスタ 220 の電流駆動能力が向上し、高いオン電流特性を得ることが可能となる。

40

【0093】

また、トランジスタ 220 では、バックゲート電極として機能する電極層 119b が、ゲート電極層 102 と電気的に接続されていないため、ゲート電極層 102 と電極層 119b に異なる電位や信号を入力することができる。よって、バックゲート電極として機能する電極層 119b への入力信号や入力電位によりトランジスタ 220 のしきい値電圧をプラス方向またはマイナス方向へシフトさせることができるとなる。トランジスタ 220 のしきい値電圧を適宜制御することにより、半導体装置の動作時にトランジスタ 220 をエンハンスマント型又はデプレッション型に適宜変更することが可能である。

50

## 【0094】

## &lt;トランジスタの構成例4&gt;

図4(A)及び図4(B)に本実施の形態の半導体装置が有するトランジスタ230の平面図及び断面図を示す。トランジスタ230は、図2のトランジスタ210、図3のトランジスタ220の変形例である。図4(A)は、トランジスタ230の平面図であり、図4(B)は、図4(A)の一点鎖線A7-A8間及びB7-B8間の断面図である。なお、図4(A)では明瞭化のため、基板100、トランジスタ230の構成要素の一部(例えば、ゲート絶縁層)等を省略して図示している。

## 【0095】

図4(A)及び図4(B)に示すトランジスタ230は、基板100上に形成されたゲート電極層102と、ゲート電極層102と接するゲート絶縁層104と、ゲート絶縁層104を介してゲート電極層102と対向する酸化物半導体層106と、酸化物半導体層106上のバリア層として機能する金属酸化物層108と、金属酸化物層108に接する一对の電極層110a、110bと、一对の電極層110a、電極層110b及び金属酸化物層108上に形成された酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116と、窒化物絶縁層116を上に設けられた電極層119a、119cと、を有する。

10

## 【0096】

トランジスタ230は、金属酸化物層108及び絶縁層(酸化物絶縁層112、酸化物絶縁層114及び窒化物絶縁層116)を介して酸化物半導体層106と重なる領域を有する電極層119a、119cを有する。また、電極層119a、119cは、ゲート絶縁層104、酸化物絶縁層112、酸化物絶縁層114、及び窒化物絶縁層116に設けられた開口部117a、117bにおいてそれぞれゲート電極層102と接続し、ゲート電極層102の一部として機能する。すなわち、トランジスタ230は、トランジスタ220からバックゲート電極として機能する電極層119bを省略した構成を有する。なお、トランジスタ220又はトランジスタ230において、電極層119a、119cのいずれか一方のみを有する構成としてもよい。

20

## 【0097】

トランジスタ210及びトランジスタ220と同様に、トランジスタ230においても酸化物半導体層206の上面、下面、対向する2つの側面に対向するゲート電極層(ゲート電極層102、電極層119a、119c)を有するため、酸化物半導体層206を電気的に囲むs-channel構造とすることができる。よって、トランジスタ230は、電流駆動能力が向上し、高いオン電流特性を有するトランジスタとすることが可能となる。トランジスタ230の各構成要素の詳細は、先のトランジスタ210、220についての説明を参照することができる。

30

## 【0098】

なお、本実施の形態に係るトランジスタは、上記の構造のそれを自由に組み合わせることが可能である。

## 【0099】

## &lt;トランジスタの作製方法&gt;

以下に、本実施の形態のトランジスタの作製方法を図5及び図6を用いて説明する。以下では、代表的にトランジスタ210の作製方法を例に説明する。

40

## 【0100】

まず、基板100上に導電膜を形成し、該導電膜を、フォトリソグラフィ工程を用いて加工してゲート電極層102を形成する。次いで、ゲート電極層102上にゲート絶縁層104を形成する(図5(A)参照)。

## 【0101】

ゲート電極層102を構成する導電膜は、スパッタリング法、化学気相堆積(CVD)法、真空蒸着法、パルスレーザ堆積(PLD)法、を用いて形成することができる。又は、塗布法や印刷法で形成することができる。成膜方法としては、スパッタリング法、プラズマ化学気相堆積(PECVD)法が代表的であるが、有機金属化学気相堆積(MOCVD)

50

) 法等の熱 CVD 法、又は原子層堆積 (ALD) 法を用いてもよい。

【0102】

熱 CVD 法は、チャンバー内を大気圧または減圧下とし、原料ガスと酸化剤を同時にチャンバー内に送り、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい成膜方法である。熱 CVD 法は、プラズマを用いない成膜方法のため、プラズマダメージによる欠陥が生成されることがないという利点を有する。

【0103】

また、ALD 法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ（高速バルブとも呼ぶ）を切り替えて 2 種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第 1 の原料ガスと同時またはその後に不活性ガス（アルゴン、或いは窒素など）などを導入し、第 2 の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキャリアガスとなり、また、第 2 の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第 1 の原料ガスを排出した後、第 2 の原料ガスを導入してもよい。第 1 の原料ガスが基板の表面に吸着して第 1 の単原子層を成膜し、後から導入される第 2 の原料ガスと反応して、第 2 の単原子層が第 1 の単原子層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なトランジスタを作製する場合に適している。

10

【0104】

本実施の形態では、基板 100 としてガラス基板を用い、ゲート電極層 102 として厚さ 100 nm のタンゲステン層をスパッタリング法で形成する。

【0105】

なお、例えば、ALD を利用する成膜装置によりタンゲステン層を成膜する場合には、WF<sub>6</sub> ガスと B<sub>2</sub>H<sub>6</sub> ガスを順次繰り返し導入して初期タンゲステン層を形成し、その後、WF<sub>6</sub> ガスと H<sub>2</sub> ガスを同時に導入してタンゲステン層を形成する。なお、B<sub>2</sub>H<sub>6</sub> ガスに代えて SiH<sub>4</sub> ガスを用いてもよい。

20

【0106】

ゲート絶縁層 104 は、スパッタリング法、PECVD 法、熱 CVD 法、真空蒸着法、PLD 法等を用いて形成することができる。ここでは、PECVD 法により、ゲート絶縁層 104 として厚さ 400 nm の窒化シリコン膜と厚さ 50 nm の酸化窒化シリコン膜を積層して形成する。

30

【0107】

また、熱 CVD 法でゲート絶縁層 104 を構成する膜を形成してもよい。例えば、酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体（ハフニウムアルコキシド溶液、代表的にはテトラキスジメチルアミドハフニウム (TDMAH)）を気化させた原料ガスと、酸化剤としてオゾン (O<sub>3</sub>) の 2 種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式は Hf [N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> である。また、他の材料液としては、テトラキス（エチルメチルアミド）ハフニウムなどがある。

40

【0108】

例えば、酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体 (TMA など) を気化させた原料ガスと、酸化剤として H<sub>2</sub>O の 2 種類のガスを用いる。なお、トリメチルアルミニウムの化学式は Al (CH<sub>3</sub>)<sub>3</sub> である。また、他の材料液としては、トリス（ジメチルアミド）アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス (2, 2, 6, 6 - テトラメチル - 3, 5 - ヘプタンジオナート) などがある。

【0109】

例えば、酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着さ

50

せ、吸着物に含まれる塩素を除去し、酸化性ガス（O<sub>2</sub>、一酸化二窒素）のラジカルを供給して吸着物と反応させる。

【0110】

次いで、ゲート絶縁層104上に酸化物半導体層106となる酸化物半導体膜106aと、金属酸化物層108となる金属酸化物膜108aの積層膜を形成する（図5（B）参照）。

【0111】

本実施の形態では、In-Ga-Zn酸化物ターゲット（In:Ga:Zn=1:1:1）を用いたスパッタリング法により、酸化物半導体膜106aとしてIn-Ga-Zn酸化物膜を形成する。また、In-Ga酸化物ターゲット（In:Ga=7:93）を用いたスパッタリング法により、金属酸化物膜108aとしてIn-Ga酸化物膜を形成する。金属酸化物膜108aは、酸化物半導体膜として、あるいは絶縁膜として形成される。なお、酸化物半導体膜106a及び金属酸化物膜108aに適用可能な構成元素及び組成はこれに限られるものではない。

【0112】

スパッタリング法で酸化物半導体膜106a、金属酸化物膜108aを形成する場合、プラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。ただし、大面積基板への対応が可能なDC放電を用いて成膜を行うと、半導体装置の生産性を高めることができるため好ましい。金属酸化物膜108aを、DC放電を用いたスパッタリング法で成膜するためには、In:M=x:y[原子数比]としたときに、y/(x+y)を0.96以下、好ましくは0.95以下、例えば0.93とするとよい。

【0113】

スパッタリングガスは、希ガス（代表的にはアルゴン）、酸素、希ガス及び酸素の混合ガスを適宜用いる。なお、混合ガスの場合、希ガスに対して酸素のガス比を高めることができが好ましい。

【0114】

なお、スパッタリング装置におけるチャンバーは、酸化物半導体膜106aにとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（5×10<sup>-7</sup>Pa～1×10<sup>-4</sup>Pa程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体、特に炭素または水素を含む気体が逆流しないようにしておくことが好ましい。また、酸化物半導体膜106aに接する金属酸化物膜108aに含まれる水等の不純物も可能な限り除去することが好ましいため、金属酸化物膜108aを成膜するためのチャンバーも高真空排気されていることが望ましい。

【0115】

高純度真性または実質的に高純度真性である酸化物半導体膜を得るためにには、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下、より好ましくは-120以下にまで高純度化したガスを用いることで酸化物半導体膜106a、金属酸化物膜108aに水分等が取り込まれることを可能な限り防ぐことができる。

【0116】

なお、スパッタリング法に代えて、ALDを利用する成膜装置により酸化物半導体膜106a及び/又は金属酸化物膜108aを形成することができる。例えば、In-Ga-Zn酸化物膜を成膜する場合には、In(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>3</sub>ガスを順次繰り返し導入してInO<sub>2</sub>層を形成し、その後、Ga(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>3</sub>ガスを同時に導入してGaO層を形成し、更にその後Zn(CH<sub>3</sub>)<sub>2</sub>とO<sub>3</sub>ガスを同時に導入してZnO層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜてInGaO<sub>2</sub>層やInZnO<sub>2</sub>層、GaInO層、ZnInO層、GaZnO層などの混合化合

10

20

30

40

50

物層を形成してもよい。なお、O<sub>3</sub>ガスに変えてAr等の不活性ガスでバブリングしたH<sub>2</sub>Oガスを用いてもよいが、Hを含まないO<sub>3</sub>ガスを用いる方が好ましい。また、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスに代えて、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いてもよい。また、Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスにかえて、Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いてもよい。また、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスにかえて、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いてもよい。また、Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>ガスを用いてもよい。

#### 【0117】

次いで、金属酸化物膜108a上にフォトレジストマスクを用いたフォトリソグラフィ工程によりレジストマスクを形成した後、該レジストマスクを用いて金属酸化物膜108a及び酸化物半導体膜106aをエッチングして素子分離し、酸化物半導体層106及び金属酸化物層108を形成する(図5(C)参照)。ここでエッチングには、ウェットエッチング法を好ましく適用することができる。ただし、ドライエッチング法を用いてもよいし、双方を組み合わせて用いてもよい。

#### 【0118】

酸化物半導体層106の形成後、150以上基板の歪み点未満、好ましくは200以上450以下、さらに好ましくは300以上450以下の加熱処理を行ってもよい。ここで加熱処理は、酸化物半導体層の高純度化処理の一つであり、酸化物半導体層106に含まれる水素、水等を低減することができる。なお、水素、水等の低減を目的とした加熱処理は、酸化物半導体層106を島状に加工する前に行ってもよい。例えば、酸化物半導体膜106aの成膜後であって、金属酸化物膜108aの成膜前に加熱処理を行うことも可能である。その場合、金属酸化物膜108aの成膜温度を室温としてもよい。

#### 【0119】

酸化物半導体層106への加熱処理は、電気炉、RTA装置等を用いることができる。RTA装置を用いることで、短時間に限り基板の歪み点以上の温度で熱処理を行うことができる。そのため、加熱時間を短縮することが可能となる。

#### 【0120】

なお、酸化物半導体層106への加熱処理は、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウム等)の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい。また、窒素または希ガス雰囲気で加熱処理した後、酸素または超乾燥空気雰囲気で加熱してもよい。この結果、酸化物半導体層中に含まれる水素、水等を脱離させると共に、酸化物半導体層中に酸素を供給することができる。この結果、酸化物半導体層中に含まれる酸素欠損量を低減することができる。

#### 【0121】

次いで、酸化物半導体層106の側面、及び金属酸化物層108の側面及び上面に接する一対の電極層110a、110bを形成する(図5(D)参照)。

#### 【0122】

ここでは、スパッタリング法により、第1の導電層109a、109bとなる厚さ50nmのタンゲステン膜と、第2の導電層111a、111bとなる厚さ300nmの銅膜を形成する。そして銅膜上にフォトレジストマスクを用いたフォトリソグラフィ工程によりレジストマスクを形成した後、該レジストマスクを用いてタンゲステン膜及び銅膜を加工することで、一対の電極層110a、110bとする。なお、上述したように、タンゲステン膜、銅膜等の導電膜をALD法、熱CVD法で形成してもよい。この場合、酸化物半導体層106及び金属酸化物層108にプラズマダメージを与えずに導電膜を形成することができる。

#### 【0123】

例えば、銅膜のエッチングには、ウェットエッチング法を用い、タンゲステン膜のエッチングにはSF<sub>6</sub>を用いたドライエッチング法を適用すると、銅膜の表面にフッ化物が形成され、該フッ化物により銅膜からの銅が酸化物半導体層106に拡散することを抑制する

10

20

30

40

50

ことができる。また、金属酸化物層 108 は酸化物半導体層 106 に対するエッティング保護膜としても機能することができる。

#### 【0124】

次いで、一対の電極層 110a、110b 上に酸化物絶縁層 112 を形成する。その後、酸化物絶縁層 112 上に酸化物絶縁層 114 を形成する（図 6（A）参照）。

#### 【0125】

なお、酸化物絶縁層 112 を形成した後、大気に曝すことなく、連続的に酸化物絶縁層 114 を形成することが好ましい。酸化物絶縁層 112 を形成後、大気開放せず、原料ガスの流量、圧力、高周波電力及び基板温度の一以上を調整して、酸化物絶縁層 114 を連続的に形成することで、酸化物絶縁層 112 と酸化物絶縁層 114 の界面において大気成分由来の不純物濃度を低減することができるとともに、酸化物絶縁層 114 に含まれる酸素を酸化物半導体層 106 に移動させることができ、酸化物半導体層 106 の酸素欠損量を低減することが可能となる。

#### 【0126】

例えば、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 180 以上 400 以下、さらに好ましくは 200 以上 370 以下に保持し、処理室内に原料ガスを導入して処理室内における圧力を 20 Pa 以上 250 Pa 以下、さらに好ましくは 100 Pa 以上 250 Pa 以下とし、処理室内に設けられる電極に高周波電力を供給する条件により、酸化物絶縁層 112 として酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

10

#### 【0127】

上記成膜条件を用いることで、酸化物絶縁層 112 として酸素を透過する酸化物絶縁層を形成することができる。また、金属酸化物層 108 及び酸化物絶縁層 112 を設けることで、後に形成する酸化物絶縁層 114 の形成工程において、酸化物半導体層 106 へのダメージ低減が可能である。

20

#### 【0128】

なお、上記成膜条件において、基板温度を 300 以上 400 以下、さらに好ましくは 320 以上 370 以下とすることで、シリコン及び酸素の結合力が強くなる。この結果、酸化物絶縁層 112 として、酸素が透過し、緻密であり、且つ硬い酸化物絶縁層、代表的には、25 において 0.5 重量 % のフッ酸を用いた場合のエッティング速度が 10 nm / 分以下、好ましくは 8 nm / 分以下である酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

30

#### 【0129】

また、酸化物絶縁層 112 の成膜工程において、加熱をしながら酸化物絶縁層 112 を形成することは、酸化物半導体層 106 及びそれに接する金属酸化物層 108 に含まれる水素、水等の脱離に対しても有効である。酸化物半導体層 106 に含まれる水素は、プラズマ中で発生した酸素ラジカルと結合し、水となる。酸化物絶縁層 112 の成膜工程に基板が加熱されているため、酸素及び水素の結合により生成された水は酸化物半導体層 106 から脱離する。すなわち、酸化物絶縁層 112 をプラズマ CVD 法によって形成することで、酸化物半導体層 106 に含まれる水、水素等の含有量を低減することができる。

40

#### 【0130】

さらには、処理室の圧力を 100 Pa 以上 250 Pa 以下とすることで、酸化物絶縁層 112 に含まれる水の含有量が少なくなるため、トランジスタ 210 の電気特性のばらつきを低減すると共に、しきい値電圧の変動を抑制することができる。

#### 【0131】

なお、酸化物絶縁層 112 の成膜時には、酸化物半導体層 106 へのダメージをできるだけ抑えることが好ましい。トランジスタの信頼性を向上させるために後に形成される酸化物絶縁層 114 を、膜中の欠陥が低減されるような条件下で形成する場合、該酸化物絶縁層 114 の酸素脱離量が低減しやすく、酸化物半導体層 106 の欠陥を十分に低減することが困難な場合があるからである。そこで、酸化物絶縁層 112 の成膜時には、処理室の

50

圧力を100Pa以上250Pa以下とすることが好ましい。このような条件で成膜を行うことで、酸化物半導体層106へのダメージを低減することができる。

【0132】

なお、シリコンを含む堆積性気体に対する酸化性気体量を100倍以上とすることで、酸化物絶縁層112に含まれる水素含有量を低減することが可能である。この結果、酸化物半導体層106に混入する水素量を低減できるため、トランジスタのしきい値電圧のマイナスシフトを抑制することができる。

【0133】

酸化物絶縁層114としては、プラズマCVD装置の真空排気された処理室内に載置された基板を180以上280以下、さらに好ましくは200以上240以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm<sup>2</sup>以上0.5W/cm<sup>2</sup>以下、さらに好ましくは0.25W/cm<sup>2</sup>以上0.35W/cm<sup>2</sup>以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成する。

10

【0134】

酸化物絶縁層114の成膜条件として、上記圧力の反応室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、酸化物絶縁層114中における酸素含有量が化学量論比よりも多くなる。一方、基板温度が、上記温度で形成された膜では、シリコンと酸素の結合力が弱いため、後の工程の加熱処理により膜中の酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化物絶縁層を形成することができる。

20

【0135】

なお、酸化物絶縁層114の形成工程において、酸化物絶縁層112が金属酸化物層108の保護膜となる。また、金属酸化物層108が酸化物半導体層106の保護膜となる。これらの結果、酸化物半導体層106へのダメージを低減しつつ、パワー密度の高い高周波電力を用いて酸化物絶縁層114を形成することができる。

【0136】

なお、酸化物絶縁層114の成膜条件において、酸化性気体に対するシリコンを含む堆積性気体の流量を増加することで、酸化物絶縁層114の欠陥量を低減することが可能である。代表的には、ESR測定により、シリコンのダンギングボンドに由来するg = 2.001に現れる信号のスピントン密度が $6 \times 10^{17}$ spins/cm<sup>3</sup>未満、好ましくは $3 \times 10^{17}$ spins/cm<sup>3</sup>以下、好ましくは $1.5 \times 10^{17}$ spins/cm<sup>3</sup>以下である欠陥量の少ない酸化物絶縁層を形成することができる。この結果トランジスタの信頼性を高めることができる。

30

【0137】

酸化物絶縁層112、114を形成した後、加熱処理を行う。当該加熱処理により、酸化物絶縁層114に含まれる酸素の一部を酸化物半導体層106に移動させ、酸化物半導体層106に含まれる酸素欠損量をさらに低減することができる。加熱処理後に、窒化物絶縁層116を形成する。

40

【0138】

酸化物絶縁層112、114に水、水素等が含まれる場合、水、水素等をブロッキングする機能を有する窒化物絶縁層116を形成後に加熱処理を行うと、酸化物絶縁層112、114に含まれる水、水素等が酸化物半導体層106に移動し、酸化物半導体層106に欠陥が生じてしまう。よって、窒化物絶縁層116の形成前に加熱処理を行うことで、酸化物絶縁層112、114に含まれる水、水素を効果的に低減させることができる。

【0139】

なお、酸化物絶縁層114を、加熱しながら酸化物絶縁層112上に形成することで、酸化物半導体層106に酸素を移動させ、酸化物半導体層106に含まれる酸素欠損を低減

50

することが可能であるため、この加熱処理を行わなくともよい場合がある。

【0140】

酸化物絶縁層112、114への加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、さらに好ましくは320以上370以下とする。加熱処理は、窒素、酸素、超乾燥空気（水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）、または希ガス（アルゴン、ヘリウム等）の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい該加熱処理には、電気炉、RTA装置等を用いることができる。

【0141】

ここでは、窒素及び酸素雰囲気で、350、1時間の加熱処理を行う。その後、窒化物絶縁層116を形成する（図6（A）参照）。

【0142】

窒化物絶縁層116をプラズマCVD法で形成する場合、基板温度は300以上400以下に、好ましくは320以上370以下にすることで、緻密な膜を形成できるため好ましい。

【0143】

例えば、窒化物絶縁層116としてプラズマCVD法により窒化シリコン膜を形成する場合、シリコンを含む堆積性気体、窒素、及びアンモニアを原料ガスとして用いことが好ましい。窒素と比較して少量のアンモニアを用いることで、プラズマ中でアンモニアが解離し、活性種が発生する。当該活性種が、シリコンを含む堆積性気体に含まれるシリコン及び水素の結合、及び窒素の三重結合を切断する。この結果、シリコン及び窒素の結合が促進され、シリコン及び水素の結合が少なく、欠陥が少なく、緻密な窒化シリコン膜を形成することができる。一方、窒素に対するアンモニアの量が多いと、シリコンを含む堆積性気体及び窒素の分解が進まず、シリコン及び水素結合が残存してしまい、欠陥が増大した、且つ粗な窒化シリコン膜が形成されてしまう。これらのため、原料ガスにおいて、アンモニアに対する窒素の流量比を5以上50以下、10以上50以下とすることが好ましい。

【0144】

ここでは、窒化物絶縁層116として、プラズマCVD装置を用いて、シラン、窒素、及びアンモニアの原料ガスから、厚さ50nmの窒化シリコン膜を形成する。流量は、シランが50sccm、窒素が5000sccmであり、アンモニアが100sccmである。処理室の圧力を100Pa、基板温度を350とし、27.12MHzの高周波電源を用いて1000Wの高周波電力を平行平板電極に供給する。PECVD装置は電極面積が6000cm<sup>2</sup>である平行平板型のプラズマCVD装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると1.7×10<sup>-1</sup>W/cm<sup>2</sup>である。

【0145】

窒化物絶縁層116の形成後に、加熱処理を行ってもよい。該加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。この加熱処理を行う際には、酸化物絶縁層112、114の水素および水が低減されているため、上述したような酸化物半導体層106の欠陥の発生は抑えられている。

【0146】

次に、窒化物絶縁層116上にフォトマスクを用いたフォトリソグラフィ工程によりレジストマスクを形成する。該レジストマスクを用いて、窒化物絶縁層116、酸化物絶縁層112、114、及びゲート絶縁層104をエッチングして、開口部117a、117bを形成する（図6（B）参照）。

【0147】

レジストマスクを除去した後、窒化物絶縁層116上に導電膜を形成し、該導電膜を加工してバックゲート電極として機能する電極層118を形成する（図6（C）参照）。

10

20

30

40

50

## 【0148】

以上の工程により、本実施の形態に係るトランジスタ210を形成することができる。なお、本実施の形態に係る他のトランジスタも、トランジスタ210と同様に作製することが可能である。

## 【0149】

上述したように、本実施の形態で示すトランジスタは、ソース電極層及びドレイン電極層として機能する一対の電極層として、銅、アルミニウム、金、又は銀等の低抵抗材料を含む電極層を用いることで、配線遅延を抑制した半導体装置を作製することができる。さらに、一対の電極層と接して、バリア層として機能する金属酸化物層を設けることで、電気特性の低下を抑制し、良好な電気特性を有する半導体装置を提供することができる。

10

## 【0150】

また、本実施の形態に係る作製工程によって、チャネル形成領域を含む酸化物半導体層の酸素欠陥が低減され、不純物の濃度が低減された信頼性の高いトランジスタを作製することが可能である。

## 【0151】

さらに、本実施の形態に係るトランジスタは、チャネルエッチ型のトランジスタであって、不純物混入を抑制するためのバリア層として機能する金属酸化物層108を、酸化物半導体層106と同じマスクを用いて加工するため、チャネル保護型のトランジスタを形成する場合と比較してマスク枚数を削減することが可能である。よって、半導体装置の作製コストを低減させることができる。

20

## 【0152】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

## 【0153】

## (実施の形態2)

本実施の形態では、本発明の一態様のトランジスタに含まれる酸化物半導体層の構成について詳述する。

## 【0154】

以下に酸化物半導体層の有しうる構造について説明する。

## 【0155】

酸化物半導体層は、例えば非単結晶酸化物半導体層と単結晶酸化物半導体層とに分けられる。または、酸化物半導体層は、例えば、結晶性酸化物半導体層と非晶質酸化物半導体層とに分けられる。

30

## 【0156】

なお、非単結晶酸化物半導体としては、C A A C - O S ( C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r )、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。また、結晶性酸化物半導体としては、単結晶酸化物半導体、C A A C - O S 、多結晶酸化物半導体、微結晶酸化物半導体などがある。

## 【0157】

40

まずは、C A A C - O S 膜について説明する。

## 【0158】

C A A C - O S 膜は、c 軸配向した複数の結晶部（ペレットともいう。）を有する酸化物半導体層の一つである。

## 【0159】

透過型電子顕微鏡（T E M : T r a n s m i s s i o n E l e c t r o n M i c r o s c o p e ）によって、C A A C - O S の明視野像および回折パターンの複合解析像（高分解能T E M像ともいう。）を観察することで複数のペレットを確認することができる。一方、高分解能T E M像によっても明確なペレット同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、C A A C - O S は、結

50

晶粒界に起因する電子移動度の低下が起こりにくいといえる。

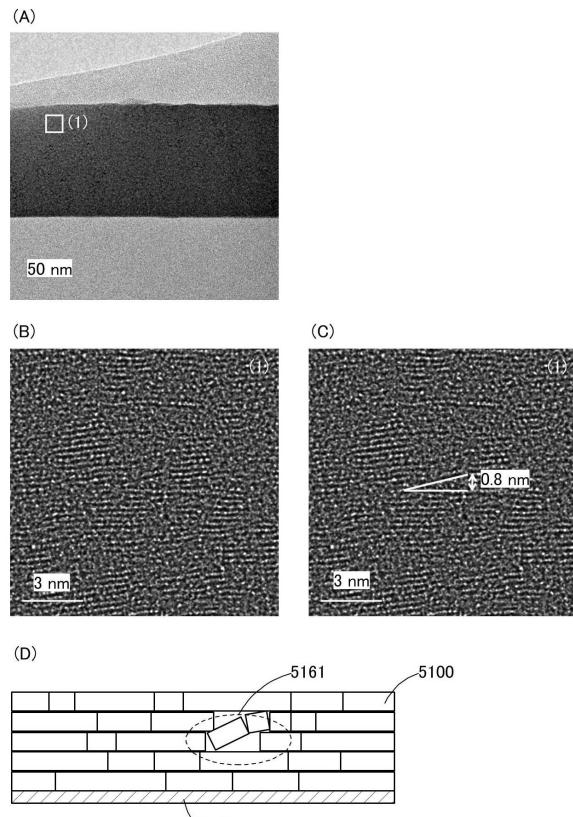

【0160】

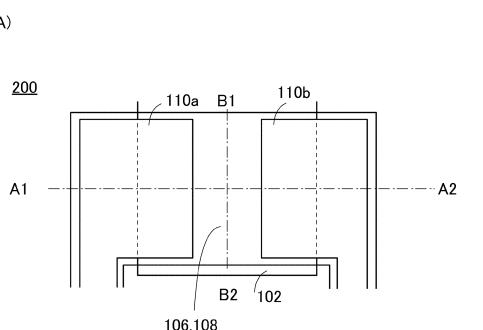

例えば、図8(A)に示すように、試料面と略平行な方向から、CAAC-OSの断面の高分解能TEM像を観察する。ここでは、球面収差補正(Spherical Aberration Corrector)機能を用いてTEM像を観察する。なお、球面収差補正機能を用いた高分解能TEM像を、以下では、特にCs補正高分解能TEM像と呼ぶ。なお、Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって行うことができる。

【0161】

図8(A)の領域(1)を拡大したCs補正高分解能TEM像を図8(B)に示す。図8(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OSの膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-OSの被形成面または上面と平行に配列する。

【0162】

図8(B)において、CAAC-OSは特徴的な原子配列を有する。図8(C)は、特徴的な原子配列を、補助線で示したものである。図8(B)および図8(C)より、ペレット一つの大きさは1nm以上3nm以下程度であり、ペレットとペレットとの傾きにより生じる隙間の大きさは0.8nm程度であることがわかる。したがって、ペレットを、ナノ結晶(nc:nanocrysta1)と呼ぶこともできる。

【0163】

ここで、Cs補正高分解能TEM像から、基板5120上のCAAC-OSのペレット5100の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる(図8(D)参照。)。図8(C)で観察されたペレットとペレットとの間で傾きが生じている箇所は、図8(D)に示す領域5161に相当する。

【0164】

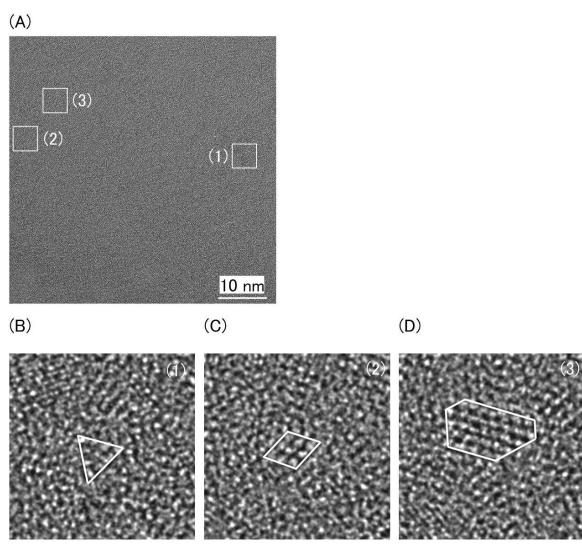

また、例えば、図23(A)に示すように、試料面と略垂直な方向から、CAAC-OSの平面のCs補正高分解能TEM像を観察する。図23(A)の領域(1)、領域(2)および領域(3)を拡大したCs補正高分解能TEM像を、それぞれ図23(B)、図23(C)および図23(D)に示す。図23(B)、図23(C)および図23(D)より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

【0165】

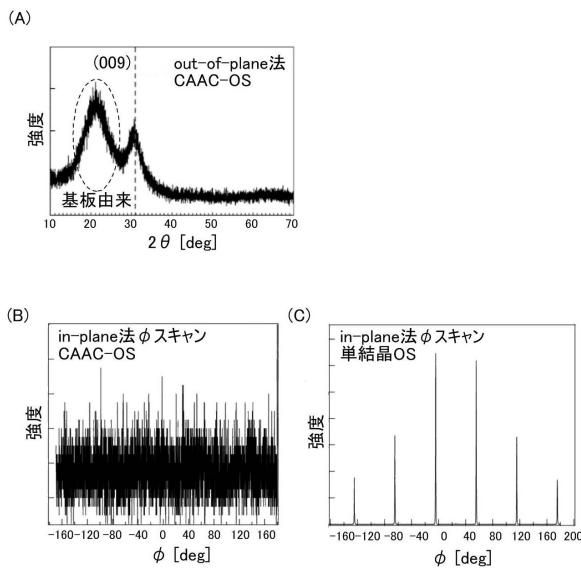

例えば、 $InGaZnO_4$ の結晶を有するCAAC-OSに対し、X線回折(XRD:X-Ray Diffraction)装置を用いてout-of-plane法による構造解析を行うと、図24(A)に示すように回折角(2)が31°近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$ の結晶の(009)面に帰属されることから、CAAC-OSの結晶がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

【0166】

なお、 $InGaZnO_4$ の結晶を有するCAAC-OSのout-of-plane法による構造解析では、2が31°近傍のピークの他に、2が36°近傍にもピークが現れる場合がある。2が36°近傍のピークは、CAAC-OS中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-OSは、2が31°近傍にピークを示し、2が36°近傍にピークを示さないことが好ましい。

【0167】

一方、CAAC-OSに対し、c軸に略垂直な方向からX線を入射させるin-plane法による構造解析を行うと、2が56°近傍にピークが現れる。このピークは、 $InGaZnO_4$ の結晶の(110)面に帰属される。CAAC-OSの場合は、2を56°近傍に固定し、試料面の法線ベクトルを軸(軸)として試料を回転させながら分析(スキャン)を行っても、図24(B)に示すように明瞭なピークは現れない。これに対

10

20

30

40

50

し、 $InGaZnO_4$  の単結晶酸化物半導体であれば、2 を 56° 近傍に固定してスキャンした場合、図 24 (C) に示すように (110) 面と等価な結晶面に帰属されるピークが 6 本観察される。したがって、XRD を用いた構造解析から、CAAC-OS は、a 軸および b 軸の配向が不規則であることが確認できる。

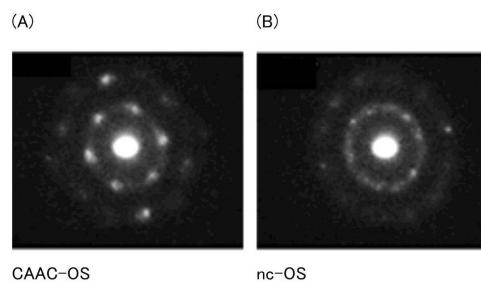

#### 【0168】

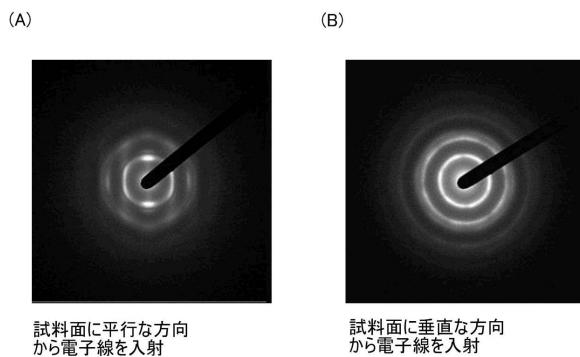

次に、CAAC-OS である  $In-Ga-Zn$  酸化物に対し、試料面に平行な方向からプローブ径が 300 nm の電子線を入射させたときの回折パターン（制限視野透過電子回折パターンともいう。）を図 25 (A) に示す。図 25 (A) より、例えば、 $InGaZnO_4$  の結晶の (009) 面に起因するスポットが確認される。したがって、電子回折によつても、CAAC-OS に含まれるペレットが c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直な方向からプローブ径が 300 nm の電子線を入射させたときの回折パターンを図 25 (B) に示す。図 25 (B) より、リング状の回折パターンが確認される。したがって、電子回折によつても、CAAC-OS に含まれるペレットの a 軸および b 軸は配向性を有さないことがわかる。なお、図 25 (B) における第 1 リングは、 $InGaZnO_4$  の結晶の (010) 面および (100) 面などに起因すると考えられる。また、図 25 (B) における第 2 リングは (110) 面などに起因すると考えられる。

#### 【0169】

このように、それぞれのペレット（ナノ結晶）の c 軸が、被形成面または上面に略垂直な方向を向いていることから、CAAC-OS を CANC (C-Axis Aligned nanocrystals) を有する酸化物半導体と呼ぶこともできる。

#### 【0170】

CAAC-OS は、不純物濃度の低い酸化物半導体である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体の主成分以外の元素である。特に、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体内部に含まれると、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

#### 【0171】

また、CAAC-OS は、欠陥準位密度の低い酸化物半導体である。例えば、酸化物半導体中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0172】

また、CAAC-OS を用いたトランジスタは、可視光や紫外光の照射による電気特性的変動が小さい。

#### 【0173】

次に、微結晶酸化物半導体層について説明する。

#### 【0174】

微結晶酸化物半導体は、高分解能 TEM 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体に含まれる結晶部は、1 nm 以上 100 nm 以下、または 1 nm 以上 10 nm 以下の大きさであることが多い。特に、1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の微結晶であるナノ結晶を有する酸化物半導体を、nc-OS (nanocrystalline Oxide Semiconductor) と呼ぶ。また、nc-OS は、例えば、高分解能 TEM 像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、CAAC-OS におけるペレットと同じ起源を有する可能性がある。そのため、以下では nc-OS の結晶部をペレットと呼ぶ場合がある。

#### 【0175】

10

20

30

40

50

n c - O S は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O S に対し、ペレットよりも大きい径の X 線を用いる XRD 装置を用いて構造解析を行うと、out-of-plane 法による解析では、結晶面を示すピークが検出されない。また、n c - O S に対し、ペレットよりも大きいプローブ径（例えば 50 nm 以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S に対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O S に対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、n c - O S に対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

10

#### 【0176】

このように、それぞれのペレット（ナノ結晶）の結晶方位が規則性を有さないことから、n c - O S を NANC (Non-Aligned nanocrystals) を有する酸化物半導体と呼ぶこともできる。

#### 【0177】

n c - O S は、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O S は、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - O S は、CAC - O S と比べて欠陥準位密度が高くなる。

20

#### 【0178】

次に、非晶質酸化物半導体について説明する。

#### 【0179】

非晶質酸化物半導体は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体である。石英のような無定形状態を有する酸化物半導体が一例である。

#### 【0180】

非晶質酸化物半導体は、高分解能 TEM 像において結晶部を確認することができない。

30

#### 【0181】

非晶質酸化物半導体に対し、XRD 装置を用いた構造解析を行うと、out-of-plane 法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

#### 【0182】

非晶質構造については、様々な見解が示されている。例えば、原子配列に全く秩序性を有さない構造を完全な非晶質構造（completely amorphous structure）と呼ぶ場合がある。また、最近接原子間距離または第 2 近接原子間距離まで秩序性を有し、かつ長距離秩序性を有さない構造を非晶質構造と呼ぶ場合もある。したがって、最も厳格な定義によれば、僅かでも原子配列に秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。また、少なくとも、長距離秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。よって、結晶部を有することから、例えば、CAC - O S および n c - O S を、非晶質酸化物半導体または完全な非晶質酸化物半導体と呼ぶことはできない。

40

#### 【0183】

なお、酸化物半導体は、n c - O S と非晶質酸化物半導体との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体を、特に非晶質ライク酸化物半導体（a-like OS: amorphous-like Oxide Semiconductor）

50

uctor) と呼ぶ。

【0184】

a-like OS は、高分解能 TEM 像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能 TEM 像において、明確に結晶部を確認することができる領域と、結晶部を確認することのできない領域と、を有する。

【0185】

以下では、酸化物半導体の構造による電子照射の影響の違いについて説明する。

【0186】

a-like OS、nc-OS および CAAC-OS を準備する。いずれの試料も In-Ga-Zn 酸化物である。

10

【0187】

まず、各試料の高分解能断面 TEM 像を取得する。高分解能断面 TEM 像により、各試料は、いずれも結晶部を有することがわかる。

【0188】

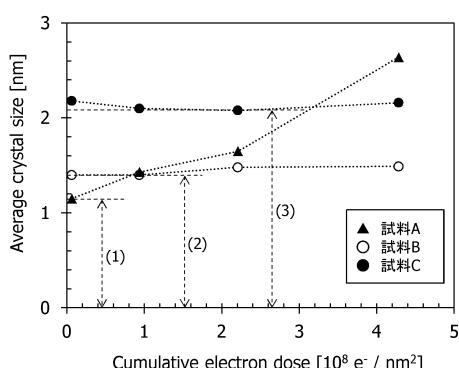

さらに、各試料の結晶部の大きさを計測する。図 26 は、各試料の結晶部（22箇所から 45 箇所）の平均の大きさの変化を調査した例である。図 26 より、a-like OS は、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図 26 中に（1）で示すように、TEM による観察初期においては 1.2 nm 程度の大きさだった結晶部が、累積照射量が  $4.2 \times 10^8 e^- / nm^2$  においては 2.6 nm 程度の大きさまで成長していることがわかる。一方、nc-OS および CAAC-OS は、電子照射開始時から電子の累積照射量が  $4.2 \times 10^8 e^- / nm^2$  になるまでの範囲で、電子の累積照射量によらず結晶部の大きさに変化が見られないことがわかる。具体的には、図 26 中の（2）で示すように、TEM による観察の経過によらず、結晶部の大きさは 1.4 nm 程度であることがわかる。また、図 26 中の（3）で示すように、TEM による観察の経過によらず、結晶部の大きさは 2.1 nm 程度であることがわかる。

20

【0189】

このように、a-like OS は、TEM による観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質な nc-OS、および CAAC-OS であれば、TEM による観察程度の微量な電子照射による結晶化はほとんど見られないことがわかる。

30

【0190】

なお、a-like OS および nc-OS の結晶部の大きさの計測は、高分解能 TEM 像を用いて行うことができる。例えば、InGaZnO<sub>4</sub> の結晶は層状構造を有し、In-O 層の間に、Ga-Zn-O 層を 2 層有する。InGaZnO<sub>4</sub> の結晶の単位格子は、In-O 層を 3 層有し、また Ga-Zn-O 層を 6 層有する、計 9 層が c 軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、(009) 面の格子面間隔 (d 値ともいう。) と同程度であり、結晶構造解析からその値は 0.29 nm と求められている。そのため、高分解能 TEM 像における格子縞に着目し、格子縞の間隔が 0.28 nm 以上 0.30 nm 以下である箇所においては、それぞれの格子縞が InGaZnO<sub>4</sub> の結晶の a-b 面に対応する。

40

【0191】

また、酸化物半導体は、構造ごとに密度が異なる場合がある。例えば、ある酸化物半導体の組成がわかれば、該組成と同じ組成における単結晶の密度と比較することにより、その酸化物半導体の構造を推定することができる。例えば、単結晶の密度に対し、a-like OS の密度は 78.6% 以上 92.3% 未満となる。また、例えば、単結晶の密度に対し、nc-OS の密度および CAAC-OS の密度は 92.3% 以上 100% 未満となる。なお、単結晶の密度に対し密度が 78% 未満となる酸化物半導体は、成膜すること 자체が困難である。

【0192】

上記について、具体例を用いて説明する。例えば、In : Ga : Zn = 1 : 1 : 1 [原子

50

数比]を満たす酸化物半導体において、菱面体晶構造を有する単結晶 $InGaZnO_4$ の密度は $6.357\text{ g/cm}^3$ となる。よって、例えば、 $In:Ga:Zn = 1:1:1$  [原子数比]を満たす酸化物半導体において、 $a\text{-like OS}$ の密度は $5.0\text{ g/cm}^3$ 以上 $5.9\text{ g/cm}^3$ 未満となる。また、例えば、 $In:Ga:Zn = 1:1:1$  [原子数比]を満たす酸化物半導体において、 $nc\text{-OS}$ の密度および $CAAC\text{-OS}$ の密度は $5.9\text{ g/cm}^3$ 以上 $6.3\text{ g/cm}^3$ 未満となる。

#### 【0193】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成の単結晶に相当する密度を算出することができる。所望の組成の単結晶の密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて算出すればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて算出することが好ましい。

10

#### 【0194】

なお、酸化物半導体は、例えば、非晶質酸化物半導体、 $a\text{-like OS}$ 、微結晶酸化物半導体、 $CAAC\text{-OS}$ のうち、二種以上を有する積層膜であってもよい。

#### 【0195】

不純物濃度が低く、欠陥準位密度が低い(酸素欠損が少ない)酸化物半導体は、キャリア密度を低くすることができる。したがって、そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。 $CAAC\text{-OS}$ および $nc\text{-OS}$ は、 $a\text{-like OS}$ および非晶質酸化物半導体よりも不純物濃度が低く、欠陥準位密度が低い。即ち、高純度真性または実質的に高純度真性な酸化物半導体となりやすい。したがって、 $CAAC\text{-OS}$ または $nc\text{-OS}$ を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性な酸化物半導体は、キャリアトラップが少ない。そのため、 $CAAC\text{-OS}$ または $nc\text{-OS}$ を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体を用いたトランジスタは、電気特性が不安定となる場合がある。

20

#### <成膜モデル>

30

以下では、 $CAAC\text{-OS}$ および $nc\text{-OS}$ の成膜モデルの一例について説明する。

#### 【0196】

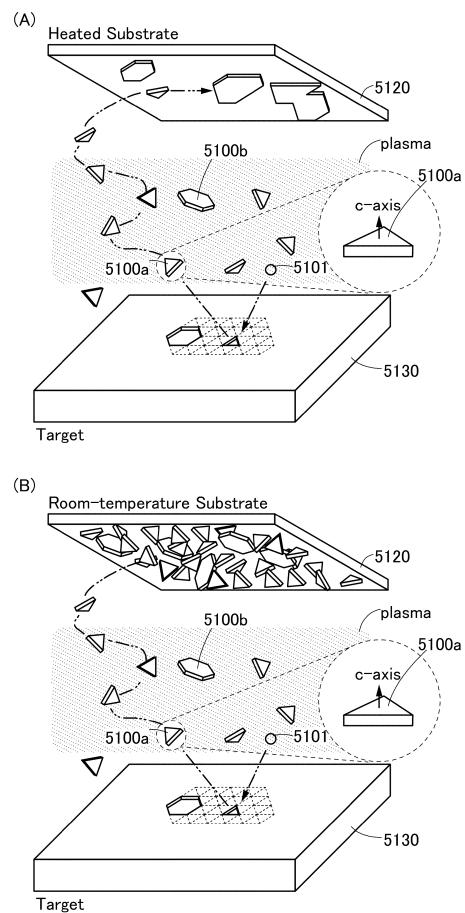

図27(A)は、スパッタリング法により $CAAC\text{-OS}$ が成膜される様子を示した成膜室内の模式図である。

#### 【0197】

ターゲット5130は、バッキングプレートに接着されている。バッキングプレートを介してターゲット5130と向かい合う位置には、複数のマグネットが配置される。該複数のマグネットによって磁場が生じている。マグネットの配置や構成などについては、上述した成膜室の記載を参照する。マグネットの磁場を利用して成膜速度を高めるスパッタリング法は、マグネットロンスパッタリング法と呼ばれる。

40

#### 【0198】

ターゲット5130は、多結晶構造を有し、いずれかの結晶粒には劈開面が含まれる。

#### 【0199】

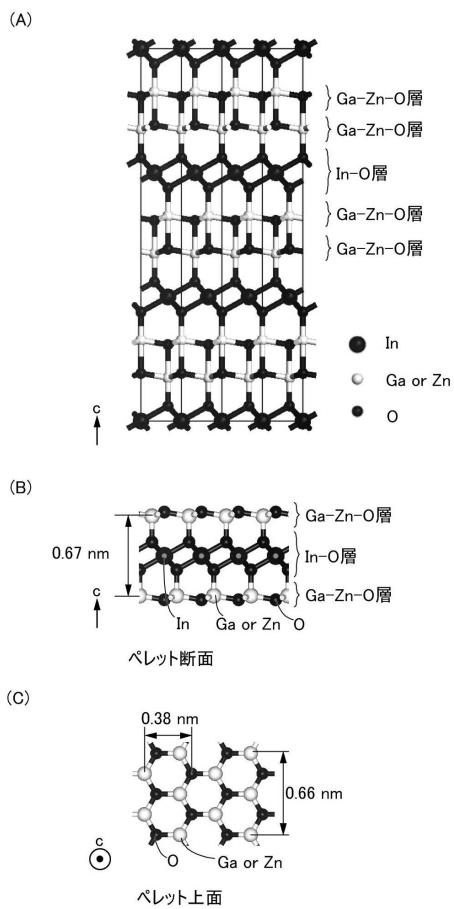

一例として、 $In\text{-Ga\text{-}Zn}$ 酸化物を有するターゲット5130の劈開面について説明する。図28(A)に、ターゲット5130に含まれる $InGaZnO_4$ の結晶の構造を示す。なお、図28(A)は、c軸を上向きとし、b軸に平行な方向から $InGaZnO_4$ の結晶を観察した場合の構造である。

#### 【0200】

図28(A)より、近接する二つの $Ga\text{-Zn\text{-}O}$ 層において、それぞれの層における酸素原子同士が近距離に配置されていることがわかる。そして、酸素原子が負の電荷を有す

50

ることにより、近接する二つの Ga - Zn - O 層は互いに反発する。その結果、InGaZnO<sub>4</sub> の結晶は、近接する二つの Ga - Zn - O 層の間に劈開面を有する。

#### 【0201】

基板 5120 は、ターゲット 5130 と向かい合うように配置しており、その距離 d (ターゲット - 基板間距離 (T - S 間距離) ともいう。) は 0.01m 以上 1m 以下、好ましくは 0.02m 以上 0.5m 以下とする。成膜室内は、ほとんどが成膜ガス (例えば、酸素、アルゴン、または酸素を 5 体積 % 以上の割合で含む混合ガス) で満たされ、0.01 Pa 以上 100 Pa 以下、好ましくは 0.1 Pa 以上 10 Pa 以下に制御される。ここで、ターゲット 5130 に一定以上の電圧を印加することで、放電が始まり、プラズマが確認される。なお、ターゲット 5130 の近傍には磁場によって、高密度プラズマ領域が形成される。高密度プラズマ領域では、成膜ガスがイオン化することで、イオン 5101 が生じる。イオン 5101 は、例えば、酸素の陽イオン (O<sup>+</sup>) やアルゴンの陽イオン (Ar<sup>+</sup>) などである。

#### 【0202】

イオン 5101 は、電界によってターゲット 5130 側に加速され、やがてターゲット 5130 と衝突する。このとき、劈開面から平板状またはペレット状のスパッタ粒子であるペレット 5100a およびペレット 5100b が剥離し、叩き出される。なお、ペレット 5100a およびペレット 5100b は、イオン 5101 の衝突の衝撃によって、構造に歪みが生じる場合がある。

#### 【0203】

ペレット 5100a は、三角形、例えば正三角形の平面を有する平板状またはペレット状のスパッタ粒子である。また、ペレット 5100b は、六角形、例えば正六角形の平面を有する平板状またはペレット状のスパッタ粒子である。なお、ペレット 5100a およびペレット 5100b などの平板状またはペレット状のスパッタ粒子を総称してペレット 5100 と呼ぶ。ペレット 5100 の平面の形状は、三角形、六角形に限定されない、例えば、三角形が複数個合わさった形状となる場合がある。例えば、三角形 (例えば、正三角形) が 2 個合わさった四角形 (例えば、ひし形) となる場合もある。

#### 【0204】

ペレット 5100 は、成膜ガスの種類などに応じて厚さが決定する。理由は後述するが、ペレット 5100 の厚さは、均一にすることが好ましい。また、スパッタ粒子は厚みのないペレット状である方が、厚みのあるサイコロ状であるよりも好ましい。例えば、ペレット 5100 は、厚さを 0.4 nm 以上 1 nm 以下、好ましくは 0.6 nm 以上 0.8 nm 以下とする。また、例えば、ペレット 5100 は、幅を 1 nm 以上 3 nm 以下、好ましくは 1.2 nm 以上 2.5 nm 以下とする。ペレット 5100 は、上述の図 26 中の (1) で説明した初期核に相当する。例えば、In - Ga - Zn 酸化物を有するターゲット 5130 にイオン 5101 を衝突させる場合、図 28 (B) に示すように、Ga - Zn - O 層、In - O 層および Ga - Zn - O 層の 3 層を有するペレット 5100 が飛び出してくる。なお、図 28 (C) は、ペレット 5100 を c 軸に平行な方向から観察した場合の構造である。したがって、ペレット 5100 は、二つの Ga - Zn - O 層 (パン) と、In - O 層 (具) と、を有するナノサイズのサンドイッチ構造と呼ぶことができる。

#### 【0205】

ペレット 5100 は、プラズマを通過する際に電荷を受け取ることで、側面が負または正に帯電する場合がある。ペレット 5100 は、側面に酸素原子を有し、当該酸素原子が負に帯電する可能性がある。このように、側面が同じ極性の電荷を帯びることにより、電荷同士の反発が起こり、平板状の形状を維持することが可能となる。なお、CAC - OS が、In - Ga - Zn 酸化物である場合、インジウム原子と結合した酸素原子が負に帯電する可能性がある。または、インジウム原子、ガリウム原子または亜鉛原子と結合した酸素原子が負に帯電する可能性がある。また、ペレット 5100 は、プラズマを通過する際にインジウム原子、ガリウム原子、亜鉛原子および酸素原子などと結合することで成長する場合がある。これは、上述の図 26 中の (2) と (1) の大きさの違いに相当する。こ

10

20

30

40

50

ここで、基板 5120 が室温程度である場合、ペレット 5100 がこれ以上成長しないため  $n_c$  - OS となる（図 27 (B) 参照。）。成膜可能な温度が室温程度であることから、基板 5120 が大面積である場合でも  $n_c$  - OS の成膜は可能である。なお、ペレット 5100 をプラズマ中で成長させるためには、スパッタリング法における成膜電力を高くすることが有効である。成膜電力を高くすることで、ペレット 5100 の構造を安定にすることができる。

#### 【0206】

図 27 (A) および図 27 (B) に示すように、例えば、ペレット 5100 は、プラズマ中を風のように飛翔し、ひらひらと基板 5120 上まで舞い上がっていく。ペレット 5100 は電荷を帯びているため、ほかのペレット 5100 が既に堆積している領域が近づくと、斥力が生じる。ここで、基板 5120 の上面では、基板 5120 の上面に平行な向きの磁場（水平磁場ともいう。）が生じている。また、基板 5120 およびターゲット 5130 間には、電位差が与えられているため、基板 5120 からターゲット 5130 に向けて電流が流れている。したがって、ペレット 5100 は、基板 5120 の上面において、磁場および電流の作用によって、力（ローレンツ力）を受ける。このことは、フレミングの左手の法則によって理解できる。

#### 【0207】

ペレット 5100 は、原子一つと比べると質量が大きい。そのため、基板 5120 の上面を移動するためには何らかの力を外部から印加することが重要となる。その力の一つが磁場および電流の作用で生じる力である可能性がある。なお、ペレット 5100 に与える力を大きくするためには、基板 5120 の上面において、基板 5120 の上面に平行な向きの磁場が 10 G 以上、好ましくは 20 G 以上、さらに好ましくは 30 G 以上、より好ましくは 50 G 以上となる領域を設けるとよい。または、基板 5120 の上面において、基板 5120 の上面に平行な向きの磁場が、基板 5120 の上面に垂直な向きの磁場の 1.5 倍以上、好ましくは 2 倍以上、さらに好ましくは 3 倍以上、より好ましくは 5 倍以上となる領域を設けるとよい。

#### 【0208】

このとき、マグネットユニットまたは / および基板 5120 が相対的に移動すること、または回転することによって、基板 5120 の上面における水平磁場の向きは変化し続ける。したがって、基板 5120 の上面において、ペレット 5100 は、様々な方向への力を受け、様々な方向へ移動することができる。

#### 【0209】

また、図 27 (A) に示すように基板 5120 が加熱されている場合、ペレット 5100 と基板 5120 との間で摩擦などによる抵抗が小さい状態となっている。その結果、ペレット 5100 は、基板 5120 の上面を滑空するように移動する。ペレット 5100 の移動は、平板面を基板 5120 に向けた状態で起こる。その後、既に堆積しているほかのペレット 5100 の側面まで到達すると、側面同士が結合する。このとき、ペレット 5100 の側面にある酸素原子が脱離する。脱離した酸素原子によって、CAC - OS 中の酸素欠損が埋まる場合があるため、欠陥準位密度の低いCAC - OS となる。なお、基板 5120 の上面の温度は、例えば、100 以上 500 未満、150 以上 450 未満、または 170 以上 400 未満とすればよい。即ち、基板 5120 が大面積である場合でも CAC - OS の成膜は可能である。

#### 【0210】

また、ペレット 5100 が基板 5120 上で加熱されることにより、原子が再配列し、イオン 5101 の衝突で生じた構造の歪みが緩和される。歪みの緩和されたペレット 5100 は、ほぼ単結晶となる。ペレット 5100 がほぼ単結晶となることにより、ペレット 5100 同士が結合した後に加熱されたとしても、ペレット 5100 自体の伸縮はほとんど起こり得ない。したがって、ペレット 5100 間の隙間が広がることで結晶粒界などの欠陥を形成し、クレバス化することができない。

#### 【0211】

10

20

30

40

50

また、C A A C - O S は、単結晶酸化物半導体が一枚板のようになっているのではなく、ペレット 5100 (ナノ結晶) の集合体がレンガまたはブロックが積み重なったような配列をしている。また、その間には結晶粒界を有さない。そのため、成膜時の加熱、成膜後の加熱または曲げなどで、C A A C - O S に縮みなどの変形が生じた場合でも、局部応力を緩和する、または歪みを逃がすことが可能である。したがって、可とう性を有する半導体装置に適した構造である。なお、n c - O S は、ペレット 5100 (ナノ結晶) が無秩序に積み重なったような配列となる。

#### 【0212】

ターゲットをイオンでスパッタした際に、ペレットだけでなく、酸化亜鉛などが飛び出す場合がある。酸化亜鉛はペレットよりも軽量であるため、先に基板 5120 の上面に到達する。そして、0.1 nm 以上 10 nm 以下、0.2 nm 以上 5 nm、または 0.5 nm 以上 2 nm 以下の酸化亜鉛層 5102 を形成する。図 29 に断面模式図を示す。

10

#### 【0213】

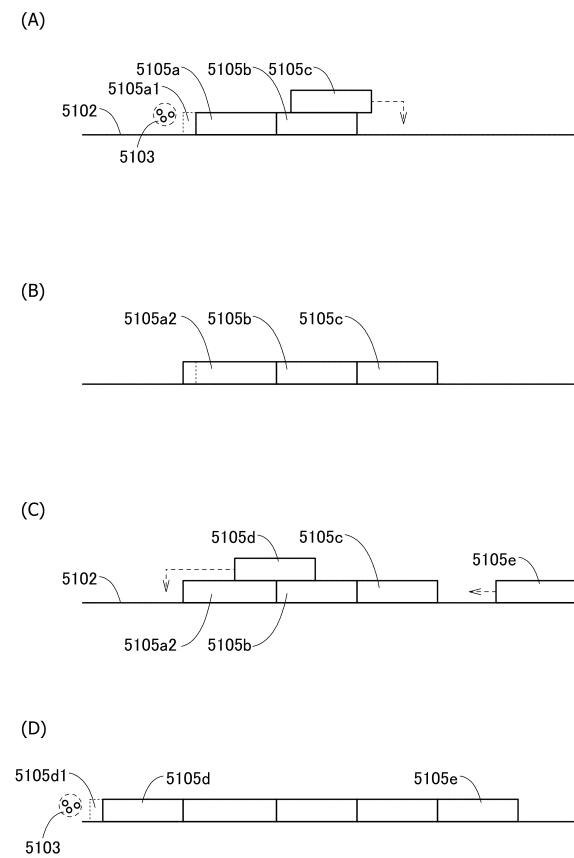

図 29 (A) に示すように、酸化亜鉛層 5102 上にはペレット 5105a と、ペレット 5105b と、が堆積する。ここで、ペレット 5105a とペレット 5105b とは、互いに側面が接するように配置している。また、ペレット 5105c は、ペレット 5105b 上に堆積した後、ペレット 5105b 上を滑るように移動する。また、ペレット 5105a の別の側面において、酸化亜鉛とともにターゲットから飛び出した複数の粒子 5103 が基板 5120 の加熱により結晶化し、領域 5105a1 を形成する。なお、複数の粒子 5103 は、酸素、亜鉛、インジウムおよびガリウムなどを含む可能性がある。

20

#### 【0214】

そして、図 29 (B) に示すように、領域 5105a1 は、ペレット 5105a と同化し、ペレット 5105a2 となる。また、ペレット 5105c は、その側面がペレット 5105b の別の側面と接するように配置する。

#### 【0215】

次に、図 29 (C) に示すように、さらにペレット 5105d がペレット 5105a2 上およびペレット 5105b 上に堆積した後、ペレット 5105a2 上およびペレット 5105b 上を滑るように移動する。また、ペレット 5105c の別の側面に向けて、さらにペレット 5105e が酸化亜鉛層 5102 上を滑るように移動する。

30

#### 【0216】

そして、図 29 (D) に示すように、ペレット 5105d は、その側面がペレット 5105a2 の側面と接するように配置する。また、ペレット 5105e は、その側面がペレット 5105c の別の側面と接するように配置する。また、ペレット 5105d の別の側面において、酸化亜鉛とともにターゲットから飛び出した複数の粒子 5103 が基板 5120 の加熱により結晶化し、領域 5105d1 を形成する。

#### 【0217】

以上のように、堆積したペレット同士が接するように配置し、ペレットの側面において結晶成長が起こることで、基板 5120 上に C A A C - O S が形成される。したがって、C A A C - O S は、n c - O S よりも一つ一つのペレットが大きくなる。これは、上述の図 26 中の (3) と (2) の大きさの違いに相当する。

40

#### 【0218】

また、ペレット 5100 の隙間が極めて小さくなることで、あたかも一つの大きなペレットが形成される場合がある。大きなペレットは、単結晶構造を有する。例えば、大きなペレットの大きさが、上面から見て 10 nm 以上 200 nm 以下、15 nm 以上 100 nm 以下、または 20 nm 以上 50 nm 以下となる場合がある。したがって、トランジスタのチャネル形成領域が、大きなペレットよりも小さい場合、チャネル形成領域として単結晶構造を有する領域を用いることができる。また、ペレットが大きくなることで、トランジスタのチャネル形成領域、ソース領域およびドレイン領域として単結晶構造を有する領域を用いることができる場合がある。

#### 【0219】

50

このように、トランジスタのチャネル形成領域などが、単結晶構造を有する領域に形成されることによって、トランジスタの周波数特性を高くすることができる場合がある。

【0220】

以上のようなモデルにより、ペレット5100が基板5120上に堆積していくと考えられる。したがって、エピタキシャル成長とは異なり、被形成面が結晶構造を有さない場合においても、CAC-OSの成膜が可能であることがわかる。例えば、基板5120の上面（被形成面）の構造が非晶質構造（例えば非晶質酸化シリコン）であっても、CAC-OSを成膜することは可能である。

【0221】

また、CAC-OSは、被形成面である基板5120の上面に凹凸がある場合でも、その形状に沿ってペレット5100が配列することがわかる。例えば、基板5120の上面が原子レベルで平坦な場合、ペレット5100はa b面と平行な平面である平板面を下に向けて並置するため、厚さが均一で平坦、かつ高い結晶性を有する層が形成される。そして、当該層がn段（nは自然数。）積み重なることで、CAC-OSを得ることができる。

【0222】

一方、基板5120の上面が凹凸を有する場合でも、CAC-OSは、ペレット5100が凸面に沿って並置した層がn段（nは自然数。）積み重なった構造となる。基板5120が凹凸を有するため、CAC-OSは、ペレット5100間に隙間が生じやすい場合がある。ただし、ペレット5100間で分子間力が働き、凹凸があってもペレット間の隙間はなるべく小さくなるように配列する。したがって、凹凸があっても高い結晶性を有するCAC-OSとができる。

【0223】

したがって、CAC-OSは、レーザ結晶化が不要であり、大面積のガラス基板などであっても均一な成膜が可能である。

【0224】

このようなモデルによってCAC-OSが成膜されるため、スパッタ粒子が厚みのないペレット状である方が好ましい。なお、スパッタ粒子が厚みのあるサイコロ状である場合、基板5120上に向ける面が一定とならず、厚さや結晶の配向を均一にできない場合がある。

【0225】

以上に示した成膜モデルにより、非晶質構造を有する被形成面上であっても、高い結晶性を有するCAC-OSを得ることができる。

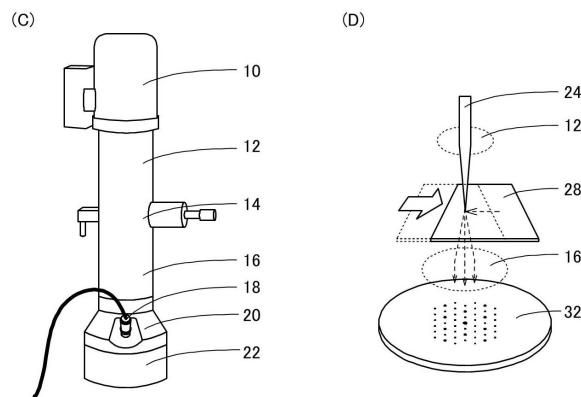

【0226】

図9(C)に、電子銃室10と、電子銃室10の下の光学系12と、光学系12の下の試料室14と、試料室14の下の光学系16と、光学系16の下の観察室20と、観察室20に設置されたカメラ18と、観察室20の下のフィルム室22と、を有する透過電子回折測定装置を示す。カメラ18は、観察室20内部に向けて設置される。なお、フィルム室22を有さなくても構わない。

【0227】

また、図9(D)に、図9(C)で示した透過電子回折測定装置内部の構造を示す。透過電子回折測定装置内部では、電子銃室10に設置された電子銃から放出された電子が、光学系12を介して試料室14に配置された物質28に照射される。物質28を通過した電子は、光学系16を介して観察室20内部に設置された蛍光板32に入射する。蛍光板32では、入射した電子の強度に応じたパターンが現れることで透過電子回折パターンを測定することができる。

【0228】

カメラ18は、蛍光板32を向いて設置されており、蛍光板32に現れたパターンを撮影することができる。カメラのレンズの中央、および蛍光板32の上面を通る直線と、蛍光板32の上面と、の為す角度は、例えば、15°以上80°以下、30°以上75°。

10

20

30

40

50

以下、または45°以上70°以下とする。該角度が小さいほど、カメラ18で撮影される透過電子回折パターンは歪みが大きくなる。ただし、あらかじめ該角度がわかっているれば、得られた透過電子回折パターンの歪みを補正することも可能である。なお、カメラ18をフィルム室22に設置しても構わない場合がある。例えば、カメラ18をフィルム室22に、電子24の入射方向と対向するように設置してもよい。この場合、蛍光板32の裏面から歪みの少ない透過電子回折パターンを撮影することができる。

#### 【0229】

試料室14には、試料である物質28を固定するためのホルダが設置されている。ホルダは、物質28を通過する電子を透過するような構造をしている。ホルダは、例えば、物質28をX軸、Y軸、Z軸などに移動させる機能を有していてもよい。ホルダの移動機能は、例えば、1nm以上10nm以下、5nm以上50nm以下、10nm以上100nm以下、50nm以上500nm以下、100nm以上1μm以下の範囲で移動させる精度を有すればよい。これらの範囲は、物質28の構造によって最適な範囲を設定すればよい。

10

#### 【0230】

次に、上述した透過電子回折測定装置を用いて、物質の透過電子回折パターンを測定する方法について説明する。

#### 【0231】

例えば、図9(D)に示すように物質におけるナノビームである電子24の照射位置を変化させる(スキャンする)ことで、物質の構造が変化していく様子を確認することができる。このとき、物質28がC AAC-O S膜であれば、図9(A)に示したような回折パターンが観測される。または、物質28がn c-O S膜であれば、図9(B)に示したような回折パターンが観測される。

20

#### 【0232】

ところで、物質28がC AAC-O S膜であったとしても、部分的にn c-O S膜などと同様の回折パターンが観測される場合がある。したがって、C AAC-O S膜の良否は、一定の範囲におけるC AAC-O S膜の回折パターンが観測される領域の割合(C AAC化率ともいう。)で表すことができる場合がある。例えば、良質なC AAC-O S膜であれば、C AAC化率は、60%以上、好ましくは80%以上、さらに好ましくは90%以上、より好ましくは95%以上となる。なお、C AAC-O S膜と異なる回折パターンが観測される領域を非C AAC化率と表記する。

30

#### 【0233】

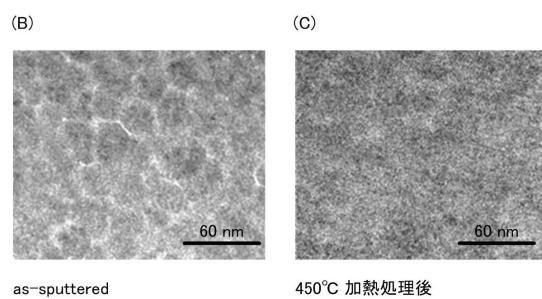

一例として、成膜直後(as-sputteredと表記。)、または酸素を含む雰囲気における450℃加熱処理後のC AAC-O S膜を有する各試料の上面に対し、スキャンしながら透過電子回折パターンを取得した。ここでは、5nm/秒の速度で60秒間スキャンしながら回折パターンを観測し、観測された回折パターンを0.5秒ごとに静止画に変換することで、C AAC化率を導出した。なお、電子線としては、プローブ径が1nmのナノ電子ビームを用いた。なお、同様の測定は6試料に対して行った。そしてC AAC化率の算出には、6試料における平均値を用いた。

40

#### 【0234】

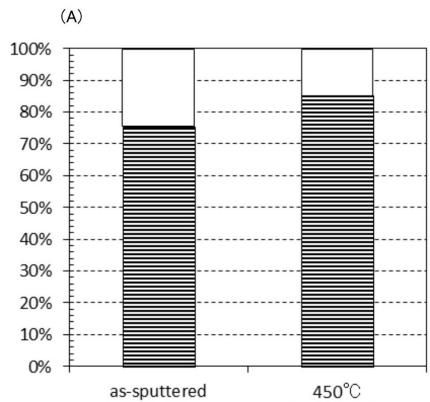

各試料におけるC AAC化率を図10(A)に示す。成膜直後のC AAC-O S膜のC AAC化率は75.7%(非C AAC化率は24.3%)であった。また、450℃加熱処理後のC AAC-O S膜のC AAC化率は85.3%(非C AAC化率は14.7%)であった。成膜直後と比べて、450℃加熱処理後のC AAC化率が高いことがわかる。即ち、高い温度(例えば400℃以上)における加熱処理によって、非C AAC化率が低くなる(C AAC化率が高くなる)ことがわかる。また、500℃未満の加熱処理においても高いC AAC化率を有するC AAC-O S膜が得られることがわかる。

#### 【0235】

ここで、C AAC-O S膜と異なる回折パターンのほとんどはn c-O S膜と同様の回折パターンであった。また、測定領域において非晶質酸化物半導体膜は、確認することができ

50

きなかった。したがって、加熱処理によって、n c - O S 膜と同様の構造を有する領域が、隣接する領域の構造の影響を受けて再配列し、C A A C 化していることが示唆される。

【0236】

図10 (B) および図10 (C) は、成膜直後および450 加熱処理後のC A A C - O S 膜の平面TEM像である。図10 (B) と図10 (C) とを比較することにより、450 加熱処理後のC A A C - O S 膜は、膜質がより均質であることがわかる。即ち、高い温度における加熱処理によって、C A A C - O S 膜の膜質が向上することがわかる。

【0237】

このような測定方法を用いれば、複数の構造を有する酸化物半導体層の構造解析が可能となる場合がある。

10

【0238】

以上のいずれかの構成を有する酸化物半導体層を用いて本発明の一態様に係るトランジスタを構成することができる。

【0239】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

【0240】

(実施の形態3)

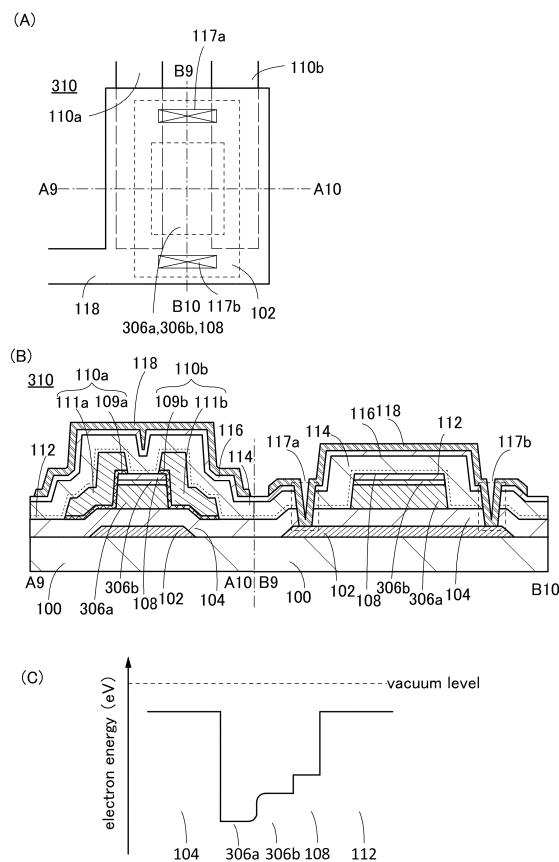

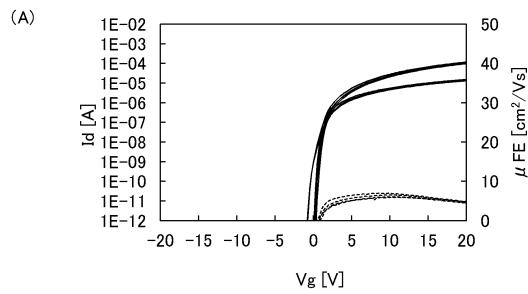

本実施の形態では、実施の形態1と異なる構成を有するトランジスタを備える半導体装置について図7を参照して説明する。本実施の形態で説明するトランジスタは、実施の形態1と比較して、酸化物半導体層を複数備えた多層膜を有する点が異なる。ここでは、実施の形態1の図2で示した半導体装置を用いて、トランジスタの詳細を説明する。

20

【0241】

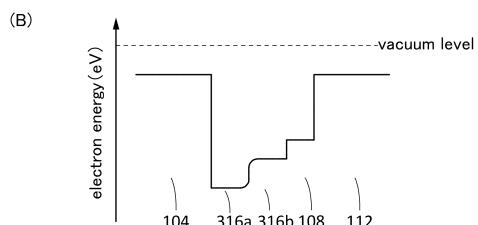

図7 (A) 及び図7 (B) に本実施の形態の半導体装置が有するトランジスタ310の平面図及び断面図を示す。図7 (A) は、トランジスタ310の平面図であり、図7 (B) は、図7 (A) の一点鎖線A9 - A10間及びB9 - B10間の断面図である。なお、図7 (A) では明瞭化のため、基板100、トランジスタ310の構成要素の一部(例えば、ゲート絶縁層)等を省略して図示している。また、図7 (C) に、トランジスタ310に含まれる積層構造のバンド図を示す。

【0242】

30

図7に示す半導体装置に含まれるトランジスタ310は、ゲート絶縁層104と、金属酸化物層108との間に設けられた酸化物半導体層が、酸化物半導体層306aと酸化物半導体層306bの積層構造を有する点において、図2に示したトランジスタ210と異なる。その他の構成は、図2と同様であり、先の説明を参照することができる。

【0243】

トランジスタ310において、酸化物半導体層306a及び酸化物半導体層306bとしては、少なくともIn若しくはZnを含む金属酸化物で形成され、代表的には、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物(MはTi、Ga、Y、Zr、La、Ce、NdまたはHf)である。また、酸化物半導体層306bは、酸化物半導体層306aよりも伝導帯の下端のエネルギーが真空準位に近く、代表的には、酸化物半導体層306bの伝導帯の下端のエネルギーと、酸化物半導体層306aの伝導帯の下端のエネルギーとの差が、0.05eV以上、0.07eV以上、0.1eV以上、0.15eV以上、又は0.5eV以上、且つ2eV以下、又は1eV以下である。即ち、酸化物半導体層306bの電子親和力と、酸化物半導体層306aの電子親和力との差が、0.05eV以上、0.07eV以上、0.1eV以上、0.15eV以上、又は0.5eV以上、且つ2eV以下、又は1eV以下である。

40

【0244】

このような構成を有することで、トランジスタ310に電圧を印加した際に酸化物半導体層306aが電流の主な経路となり、チャネル領域として機能する。また、酸化物半導体層306bは、チャネルが形成される酸化物半導体層306aを構成する金属元素の一種

50

以上から構成される酸化物半導体層であるため、酸化物半導体層306aと酸化物半導体層306bとの界面において、界面散乱が起こりにくい。従って、該界面においてはキャリアの動きが阻害されないため、トランジスタの電界効果移動度が高くなる。

【0245】

酸化物半導体層306bがIn-M-Zn酸化物であるとき、元素MとしてTi、Ga、Y、Zr、La、Ce、NdまたはHfをInより高い原子数比で有することで、酸化物半導体層306bのエネルギーギャップを大きく、電子親和力を小さくし。よって、酸化物半導体層306aとの電子親和力の差を元素Mの組成によって制御することが可能となる場合がある。また、Ti、Ga、Y、Zr、La、Ce、NdまたはHfは、酸素との結合力が強い金属元素であるため、これらの元素をInより高い原子数比で有することで、酸素欠損が生じにくくなる。

【0246】

酸化物半導体層306bがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInとMの原子数比率は、好ましくは、Inが50atomic%未満、Mが50atomic%以上、さらに好ましくは、Inが25atomic%未満、Mが75atomic%以上とする。

【0247】

また、酸化物半導体層306a及び酸化物半導体層306bが、In-M-Zn酸化物(MはTi、Ga、Y、Zr、La、Ce、NdまたはHf)の場合、酸化物半導体層306aと比較して、酸化物半導体層306bに含まれるM(Ti、Ga、Y、Zr、La、Ce、NdまたはHf)の原子数比が大きく、代表的には、酸化物半導体層306aに含まれる上記原子と比較して、1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比である。

【0248】

また、酸化物半導体層306a及び酸化物半導体層306bが、In-M-Zn酸化物(MはTi、Ga、Y、Zr、La、Ce、NdまたはHf)の場合、酸化物半導体層306aをIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、酸化物半導体層306bをIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]とすると、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも大きく、好ましくは、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも1.5倍以上である。より好ましくは、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも2倍以上大きく、さらに好ましくは、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも3倍以上又は4倍以上大きい。このとき、酸化物半導体層において、y<sub>1</sub>がx<sub>1</sub>以上であると、当該酸化物半導体層を用いたトランジスタに安定した電気特性を付与できるため好ましい。ただし、y<sub>1</sub>がx<sub>1</sub>の3倍以上になると、当該酸化物半導体層を用いたトランジスタの電界効果移動度が低下してしまうため、y<sub>1</sub>はx<sub>1</sub>の3倍未満であると好ましい。酸化物半導体層の組成は、誘導結合プラズマ質量分析法(ICP-MS分析法)により測定できる。例えば、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1としたターゲット(In:Ga:Zn=1:1:0.5)を用い、スパッタ法でのアルゴンガス流量を40sccmとした条件で得られる金属酸化物膜は、In<sub>0.95</sub>Ga<sub>0.05</sub>Zn<sub>0.41</sub>O<sub>3.33</sub>である。また、測定方法をラザフォード後方散乱分析法(Rutherford Backscattering Spectrometry:RBS分析法)に変えて定量化することもできる。

【0249】

酸化物半導体層306aがIn-M-Zn酸化物(Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)の場合、酸化物半導体層306aを成膜するために用いるターゲットにおいて、金属元素の原子数比をIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub>とすると、x<sub>1</sub>/y<sub>1</sub>は、1/3以上6以下、さらには1以上6以下であって、z<sub>1</sub>/y<sub>1</sub>は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、z<sub>1</sub>/y<sub>1</sub>を1以上6以下とすることで、酸化物半導体層306aとしてCAC-O<sub>5</sub>膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、In:M:Zn=1:1:1、In:M:Zn=1:1:1.2、In:M:Zn=3:1:2等がある。

10

20

30

40

50

## 【0250】

なお、酸化物半導体層306aを成膜するためのターゲットとして、 $In : M : Zn = 1 : 1 : z_{10}$ であるターゲットを用いる場合、 $z_{10}$ を1以上1.4以下とすることが好ましく、 $z_{10}$ を1以上1.3以下とすることがより好ましい。例えば、 $In : M : Zn = 1 : 1 : 1.5$ とすると、ターゲットが白濁し、DC電源又はAC電源を用いたスパッタリング成膜が困難となる場合があるためである。このようなターゲットには、RF電源を用いた成膜を適用することが可能であるが、半導体装置の生産性を考慮した場合、DC電源又はAC電源を用いたスパッタリング成膜が可能であるターゲットを用いることが望ましい。

## 【0251】

酸化物半導体層306bがIn-M-Zn酸化物（Mは、Ti、Ga、Y、Zr、La、Ce、NdまたはHf）の場合、酸化物半導体層306bを成膜するために用いるターゲットにおいて、金属元素の原子数比を $In : M : Zn = x_2 : y_2 : z_2$ とすると、 $x_2 / y_2 < x_1 / y_1$ であって、 $z_2 / y_2$ は、1/3以上6以下、さらには1以上6以下であることが好ましい。また、インジウムに対するMの原子数比率を大きくすることで、酸化物半導体層306bのエネルギーギャップを大きく、電子親和力を小さくすることが可能であるため、 $y_2 / x_2$ を3以上、又は4以上とすることが好ましい。ターゲットの金属元素の原子数比の代表例としては、 $In : M : Zn = 1 : 3 : 2$ 、 $In : M : Zn = 1 : 3 : 4$ 、 $In : M : Zn = 1 : 3 : 5$ 、 $In : M : Zn = 1 : 3 : 6$ 、 $In : M : Zn = 1 : 4 : 2$ 、 $In : M : Zn = 1 : 4 : 4$ 、 $In : M : Zn = 1 : 4 : 5$ 等がある。

10

## 【0252】

例えば、酸化物半導体層306bを成膜するためのターゲットとして、 $In : M : Zn = 1 : 3 : z_{20}$ であるターゲットを用いる場合、 $z_{20}$ を2以上5以下とすることが好ましい。又は、酸化物半導体層306bを成膜するためのターゲットとして、 $In : M : Zn = 1 : 4 : z_{30}$ であるターゲットを用いる場合 $z_{30}$ を2以上5以下とすることが好ましい。

## 【0253】

なお、酸化物半導体層306a及び酸化物半導体層306bの原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス40%の変動を含む。

## 【0254】

酸化物半導体層306aと酸化物半導体層306bは、結晶部を有することが好ましく、同一の結晶構造を有していることがより好ましい。酸化物半導体層306aと酸化物半導体層306bとが異なる結晶構造を有する場合、2層の界面がヘテロ結晶構造部となり欠陥が生じることがあるためである。ヘテロ結晶構造部は、例えばグレインバウンダリーとみなすこともできる。

20

## 【0255】

酸化物半導体層306aには、不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）酸化物半導体層である、CAC-OS膜を用いることがより好ましい。なお、不純物濃度が低く、欠陥準位密度が低いことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体層は、キャリア発生源が少ないと、キャリア密度を低くすることができる。従って、当該酸化物半導体層をチャネルに用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体層は、キャリアトラップが少ない。そのため、当該酸化物半導体層をチャネルに用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。また、CAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

40

## 【0256】

なお、酸化物半導体層306aを成膜するためのターゲットとして $In : M : Zn = 1 : 1 : 1.2$ を用いると、成膜された酸化物半導体層306aの膜中にスピネル構造が形成

50

されにくく、C A A C 化率を高めることができると好ましい。

【0257】

また、酸化物半導体層306aがC A A C - O S 膜である場合、酸化物半導体層306aと接して形成される酸化物半導体層306bが異なる結晶構造を有すると、2層の界面にグレインバウンダリーが形成され、膜中に欠陥が生じる場合があるため、酸化物半導体層306bにもC A A C - O S 膜を用いることが好ましい。

【0258】

一方、酸化物半導体層306a、306bへの不純物混入を抑制するためのバリア層として機能する金属酸化物層108として、例えばIn-Ga酸化物層を形成する場合、該In-Ga酸化物層は、非晶質構造、n c - O S 膜と同様の結晶構造、又は、単斜晶を形成する場合があるものの、C A A C - O S 膜と同様の結晶構造を有することが困難である。よって、チャネルが形成される酸化物半導体層306aと、金属酸化物層108とを接する態様とする場合、当該2層の界面で異種(ヘテロ)構造が形成される場合がある。本実施の形態で示すトランジスタ310では、チャネルが形成される酸化物半導体層306aと、金属酸化物層108との間に酸化物半導体層306bを設けることで、異種構造の接する領域をキャリアの流れる酸化物半導体層306aとは離間させることができるとなる。ただし、酸化物半導体層306bは膜中にスピネル構造を有していてもよい。金属酸化物層108を設けることで、一対の電極層110a、110bの構成元素が酸化物半導体層306bに拡散することを抑制することができるため、酸化物半導体層306b中にスピネル構造が存在していたとしても、当該スピネル構造に起因した銅等の金属元素のチャネルへの拡散が防止されるためである。

【0259】

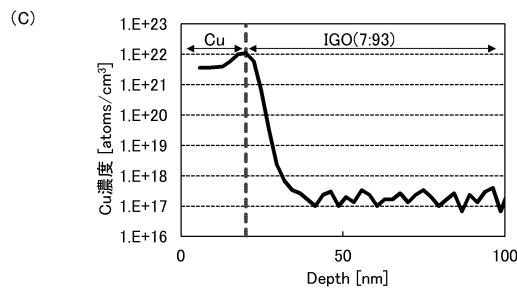

図7(C)は、ゲート絶縁層104、酸化物半導体層306a、酸化物半導体層306b、金属酸化物層108及び酸化物絶縁層112を有する積層構造の膜厚方向のバンド構造の一例である。バンド構造は、理解を容易にするためゲート絶縁層104、酸化物半導体層306a、酸化物半導体層306b、金属酸化物層108及び酸化物絶縁層112の伝導帯下端のエネルギー(Ec)を示す。

【0260】

図7(C)に示すように、酸化物半導体層306a及び酸化物半導体層306bにおいて、伝導帯下端のエネルギーは障壁が無くなだらかに変化する(連続接合ともいう)。換言すると、連続的に変化するともいうことができる。このようなバンド構造を有するためには、酸化物半導体層306aと酸化物半導体層306bとの界面において、トラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないことが好ましい。仮に、積層された酸化物半導体層の間に不純物が混在していると、エネルギー-バンドの連続性が失われ、界面でキャリアがトラップされ、あるいは再結合して、消滅してしまうためである。

【0261】

酸化物半導体層306aと酸化物半導体層306bとに連続接合を形成するためには、一口ドロック室を備えたマルチチャンバー方式の成膜装置(スパッタリング装置)を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。

【0262】

図7(C)の構成とすることで酸化物半導体層306aがウェル(井戸)となり、当該積層構造を用いたトランジスタにおいて、チャネル領域が酸化物半導体層306aに形成されることがわかる。

【0263】

なお、図8(A)に示すように、金属酸化物層108と、酸化物絶縁層112との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得るもの、金属酸化物層108が設けられることにより、酸化物半導体層306a、306bと該トラップ準位とを遠ざけることができる。また、金属酸化物層108と酸化物半導体層306bとの間にヘテロ結晶構造に起因する欠陥を有していたとしても、酸化物半導体層306bが設けられる

10

20

30

40

50

ことにより、酸化物半導体層 306a への該欠陥の影響を抑制することができる。ここで、酸化物半導体層 306a と酸化物半導体層 306b との伝導帯下端のエネルギー差が小さい場合、酸化物半導体層 306a の電子が該エネルギー差を越えてトラップ準位に達することがある。トラップ準位に電子が捕獲されることで、絶縁膜界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。したがって、酸化物半導体層 306a と酸化物半導体層 306b との伝導帯下端のエネルギー差を、0.1 eV 以上、好ましくは 0.15 eV 以上とすると、トランジスタのしきい値電圧の変動が低減され、安定した電気特性となるため好適である。

#### 【0264】

また、酸化物半導体層 306a と酸化物半導体層 306b との伝導帯下端のエネルギー差を、0.1 eV 以上、好ましくは 0.15 eV 以上とすると、金属酸化物層 108 と、酸化物絶縁層 112 との界面近傍に存在しうるトラップ準位が酸化物半導体層 306b 及びそれに接する酸化物半導体層 306a に影響することを抑制することができるため、好ましい。

10

#### 【0265】

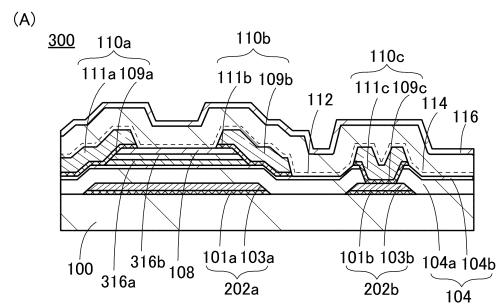

なお、本実施の形態で示す積層構造を有するトランジスタは、図 7 の構成に限られない。例えば、図 21 (A) に示すトランジスタ 300 のように、実施の形態 1 のトランジスタ 200 で示す構成において、ゲート絶縁層 104 と、金属酸化物層 108 との間に設けられた酸化物半導体層が、酸化物半導体層 316a と酸化物半導体層 316b との積層構造を有する構成としてもよい。なお、図 21 (A) では、トランジスタ 300 のチャネル長方向の断面と、ゲート電極層 202a と同じ層に形成された電極層 202b と、一対の電極層 110a、110b と同じ層に形成された電極層 110c との接続部の断面を図示している。

20

#### 【0266】

また、図 21 (A) に示すトランジスタ 300 では、ゲート電極層 202a 及びゲート電極層 202b と同じ層に形成された電極層 202b として、第 1 の導電層 101a、101b と、第 2 の導電層 103a、103b の積層構造を有する。第 1 の導電層 101a、101b としては、一対の電極層 110a、110b の第 1 の導電層 109a、109b と同様の材料を適用することができる。また、第 2 の導電層 103a、103b としては、一対の電極層 110a、110b の第 2 の導電層 111a、111b と同様の材料を適用することができる。

30

#### 【0267】

ゲート電極層 202a、電極層 202b として、銅、アルミニウム、金又は銀等の低抵抗材料を含んで形成することで、基板 100 として大面積基板を用いた場合においても配線遅延を抑制した半導体装置を作製することができる。なお、ゲート電極層 202a、電極層 202b として、上述の低抵抗材料を含む電極層を形成した場合、ゲート絶縁層 104 として、窒化物絶縁層 104a 及び酸化物絶縁層 104b の積層構造を含み、酸化物絶縁層 104b において酸化物半導体層 316a と接する構造とすることが好ましい。ゲート絶縁層 104 に含まれる窒化物絶縁層 104a は、上述の低抵抗材料の拡散を防ぐためのバリア層として用いることができる。また、酸化物絶縁層 104b は、窒化物絶縁層 104a から酸化物半導体層 316a、316b への窒素の拡散を防止するとともに、酸化物半導体層 316a、316b への酸素の供給源として機能しうる。

40

#### 【0268】

トランジスタ 300 に含まれる酸化物半導体層 316a の構成は、上述のトランジスタ 310 の酸化物半導体層 306a と同様とすることができます、先の記載を参照することができる。また、酸化物半導体層 316b の構成は、上述のトランジスタ 310 の酸化物半導体層 306b と同様とすることができます、先の記載を参照することができる。よって、トランジスタ 300 に含まれるゲート絶縁層 104、酸化物半導体層 316a、酸化物半導体層 316b、金属酸化物層 108 及び酸化物絶縁層 112 を有する積層構造の膜厚方向のバンド構造は、図 21 (B) に示すように酸化物半導体層 316a がウェル (井戸

50

)となり、当該積層構造を用いたトランジスタにおいて、チャネル領域が酸化物半導体層 316a に形成される。

【0269】

なお、トランジスタ 300において、電極層 202b と、電極層 110cとの接続は、金属酸化物膜、及び酸化物半導体膜を島状に加工した後、ゲート絶縁層 104に開口部を形成し、電極層 202b を露出させる。その後、一対の電極層 110a、110b 及び電極層 110c を形成するための導電膜を形成し、該導電膜を加工することで、電極層 202b と電極層 110cとを接続することができる。

【0270】

本実施の形態で示す構成とすることで、チャネル形成領域を含む酸化物半導体層の不純物濃度が低減された信頼性の高いトランジスタとすることが可能である。さらに、チャネルが界面準位の影響を受けにくい構造とことができ、界面準位に起因したオン電流の低下が起こりにくい。したがって、オン電流が高く、S 値の低いトランジスタとができる。また、界面準位に起因した電気特性の変動が起こりにくく、信頼性の高いトランジスタとなる。

【0271】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

【0272】

(実施の形態 4)

本実施の形態では、本発明の一態様の半導体装置として表示パネルの構成例について説明する。

【0273】

<表示パネル>

以下では、上述したトランジスタなどの半導体装置を含む表示パネルについて説明する。

【0274】

図 18 (A) は、本発明の一態様の表示パネルの上面図であり、図 18 (B) は、本発明の一態様の表示パネルの画素に液晶素子を適用する場合に用いることができる画素回路を説明するための回路図である。また、図 18 (C) は、本発明の一態様の表示パネルの画素に有機EL素子を適用する場合に用いることができる画素回路を説明するための回路図である。

【0275】

画素部に配置するトランジスタは、実施の形態 1 又は実施の形態 3 に示す構成を有するトランジスタを適用することができる。また、当該トランジスタは n チャネル型とすることが容易なので、駆動回路のうち、n チャネル型トランジスタで構成することができる駆動回路の一部を画素部のトランジスタと同一基板上に形成する。このように、画素部や駆動回路に実施の形態 1 又は実施の形態 3 に示すトランジスタを用いることにより、信頼性の高い表示装置を提供することができる。

【0276】

アクティブマトリクス型表示装置のブロック図の一例を図 18 (A) に示す。表示装置の基板 700 上には、画素部 701、第 1 の走査線駆動回路 702、第 2 の走査線駆動回路 703、信号線駆動回路 704 を有する。画素部 701 には、複数の信号線が信号線駆動回路 704 から延伸して配置され、複数の走査線が第 1 の走査線駆動回路 702、及び第 2 の走査線駆動回路 703 から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に設けられている。また、表示装置の基板 700 は FPC (Flexible Printed Circuit) 等の接続部を介して、タイミング制御回路 (コントローラ、制御 I C ともいう) に接続されている。

【0277】

図 18 (A) では、第 1 の走査線駆動回路 702、第 2 の走査線駆動回路 703、信号線

10

20

30

40

50

駆動回路 704 は、画素部 701 と同じ基板 700 上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板 700 外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板 700 上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0278】

〔液晶パネル〕

表示パネルの一態様として、液晶パネルの画素の回路構成の一例を図 18 (B) に示す。ここでは、VA 型液晶表示パネルの画素に適用することができる画素回路を示す。

【0279】

この画素回路は、一つの画素に複数の画素電極層を有する構成に適用できる。それぞれの画素電極層は異なるトランジスタに接続され、各トランジスタは異なるゲート信号で駆動できるように構成されている。これにより、マルチドメイン設計された画素の個々の画素電極層に印加する信号を、独立して制御できる。

【0280】

トランジスタ 716 のゲート配線 712 と、トランジスタ 717 のゲート配線 713 には、異なるゲート信号を与えることができるよう分離されている。一方、データ線として機能するソース電極層又はドレイン電極層 714 は、トランジスタ 716 とトランジスタ 717 で共通に用いられている。トランジスタ 716 とトランジスタ 717 は実施の形態 3 で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い液晶表示パネルを提供することができる。

【0281】

トランジスタ 716 と電気的に接続する第 1 の画素電極層と、トランジスタ 717 と電気的に接続する第 2 の画素電極層の形状について説明する。第 1 の画素電極層と第 2 の画素電極層の形状は、スリットによって分離されている。第 1 の画素電極層は V 字型に広がる形状を有し、第 2 の画素電極層は第 1 の画素電極層の外側を囲むように形成される。

【0282】

トランジスタ 716 のゲート電極はゲート配線 712 と接続され、トランジスタ 717 のゲート電極はゲート配線 713 と接続されている。ゲート配線 712 とゲート配線 713 に異なるゲート信号を与えてトランジスタ 716 とトランジスタ 717 の動作タイミングを異らせ、液晶の配向を制御できる。

【0283】

また、容量配線 710 と、誘電体として機能するゲート絶縁層と、第 1 の画素電極層又は第 2 の画素電極層と電気的に接続する容量電極とで保持容量を形成してもよい。

【0284】

マルチドメイン構造は、一画素に第 1 の液晶素子 718 と第 2 の液晶素子 719 を備える。第 1 の液晶素子 718 は第 1 の画素電極層と対向電極層とその間の液晶層とで構成され、第 2 の液晶素子 719 は第 2 の画素電極層と対向電極層とその間の液晶層とで構成される。

【0285】

なお、図 18 (B) に示す画素回路は、これに限定されない。例えば、図 18 (B) に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ、センサ、又は論理回路などを追加してもよい。

【0286】

〔有機 E L パネル〕

表示パネルの他の一態様として、有機 E L パネルの画素の回路構成の一例を図 18 (C) に示す。

【0287】

有機 E L 素子は、発光素子に電圧を印加することにより、一対の電極の一方から電子が、他方から正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして

10

20

30

40

50

、電子及び正孔が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0288】

図18(C)は、適用可能な画素回路の一例を示す図である。ここではnチャネル型のトランジスタを1つの画素に2つ用いる例を示す。なお、本発明の一態様の金属酸化物膜は、nチャネル型のトランジスタのチャネル形成領域に用いることができる。また、当該画素回路は、デジタル時間階調駆動を適用することができる。

【0289】

適用可能な画素回路の構成及びデジタル時間階調駆動を適用した場合の画素の動作について説明する。 10

【0290】

画素720は、スイッチング用トランジスタ721、駆動用トランジスタ722、発光素子724及び容量素子723を有している。スイッチング用トランジスタ721は、ゲート電極層が走査線726に接続され、第1電極(ソース電極層及びドレイン電極層の一方)が信号線725に接続され、第2電極(ソース電極層及びドレイン電極層の他方)が駆動用トランジスタ722のゲート電極層に接続されている。駆動用トランジスタ722は、ゲート電極層が容量素子723を介して電源線727に接続され、第1電極が電源線727に接続され、第2電極が発光素子724の第1電極(画素電極)に接続されている。発光素子724の第2電極は共通電極728に相当する。共通電極728は、同一基板上に形成される共通電位線と電気的に接続される。 20

【0291】

スイッチング用トランジスタ721及び駆動用トランジスタ722は実施の形態3で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い有機EL表示パネルを提供することができる。

【0292】

発光素子724の第2電極(共通電極728)の電位は低電源電位に設定する。なお、低電源電位とは、電源線727に設定される高電源電位より低い電位であり、例えばGND、0Vなどを低電源電位として設定することができる。発光素子724の順方向のしきい値電圧以上となるように高電源電位と低電源電位を設定し、その電位差を発光素子724に印加することにより、発光素子724に電流を流して発光させる。なお、発光素子724の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。 30

【0293】

なお、容量素子723は駆動用トランジスタ722のゲート容量を代用することにより省略できる。駆動用トランジスタ722のゲート容量については、チャネル形成領域とゲート電極層との間で容量が形成されていてもよい。

【0294】

次に、駆動用トランジスタ722に入力する信号について説明する。電圧入力電圧駆動方式の場合、駆動用トランジスタ722が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を、駆動用トランジスタ722に入力する。なお、駆動用トランジスタ722を線形領域で動作させるために、電源線727の電圧よりも高い電圧を駆動用トランジスタ722のゲート電極層にかける。また、信号線725には、電源線電圧に駆動用トランジスタ722のしきい値電圧Vthを加えた値以上の電圧をかける。 40

【0295】

アナログ階調駆動を行う場合、駆動用トランジスタ722のゲート電極層に発光素子724の順方向電圧に駆動用トランジスタ722のしきい値電圧Vthを加えた値以上の電圧をかける。なお、駆動用トランジスタ722が飽和領域で動作するようにビデオ信号を入力し、発光素子724に電流を流す。また、駆動用トランジスタ722を飽和領域で動作させるために、電源線727の電位を、駆動用トランジスタ722のゲート電位より高く 50

する。ビデオ信号をアナログとすることで、発光素子 724 にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

【0296】

なお、画素回路の構成は、図 18 (C) に示す画素構成に限定されない。例えば、図 18 (C) に示す画素回路にスイッチ、抵抗素子、容量素子、センサ、トランジスタ又は論理回路などを追加してもよい。

【0297】

図 18 で例示した回路に実施の形態 1 又は実施の形態 3 で例示したトランジスタを適用する場合、低電位側にソース電極層、高電位側にドレイン電極層がそれぞれ電気的に接続される構成とする。

10

【0298】

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置の一例としては、E L (エレクトロルミネッセンス) 素子 (有機物及び無機物を含む E L 素子、有機 E L 素子、無機 E L 素子)、L E D (白色 L E D、赤色 L E D、緑色 L E D、青色 L E D など)、トランジスタ (電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ (G L V)、プラズマディスプレイ (P D P)、M E M S (マイクロ・エレクトロ・メカニカル・システム)、デジタルマイクロミラー・デバイス (D M D)、D M S (デジタル・マイクロ・シャッター)、I M O D (インターフェアレンス・モジュレーション) 素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有するものがある。E L 素子を用いた表示装置の一例としては、E L ディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニングディスプレイ (F E D) 又はS E D 方式平面型ディスプレイ (S E D: Surface - conduction E lectron - emitter D isplay) などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ (透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ) などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。

20

【0299】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0300】

(実施の形態 5)

本実施の形態では、本発明の一態様の半導体装置を適用した表示モジュールについて、説明する。また、本発明の一態様の半導体装置が適用された電子機器の構成例について説明する。

30

【0301】

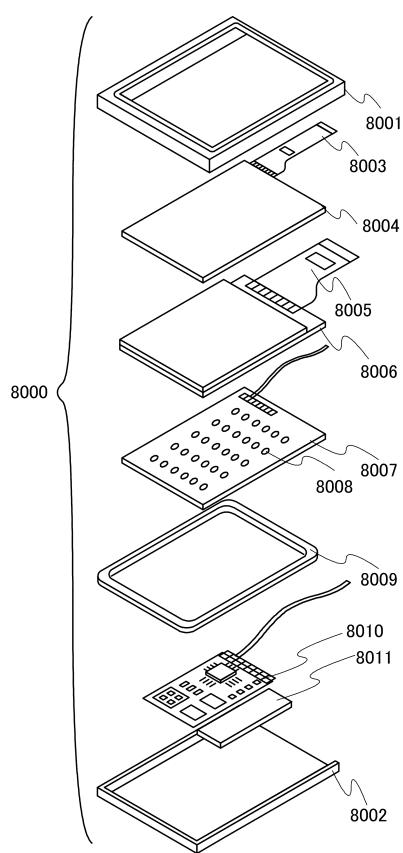

図 19 に示す表示モジュール 8000 は、上部カバー 8001 と下部カバー 8002 との間に、F P C 8003 に接続されたタッチパネル 8004、F P C 8005 に接続された表示パネル 8006、バックライトユニット 8007、フレーム 8009、プリント基板 8010、バッテリー 8011 を有する。なお、バックライトユニット 8007、バッテリー 8011、タッチパネル 8004 などは、設けられない場合もある。

40

【0302】

本発明の一態様の半導体装置は、例えば、表示パネル 8006 に用いることができる。

【0303】

上部カバー 8001 及び下部カバー 8002 は、タッチパネル 8004 及び表示パネル 8006 のサイズに合わせて、形状や寸法を適宜変更することができる。

50

## 【0304】

タッチパネル8004は、抵抗膜方式または静電容量方式のタッチパネルを表示パネル8006に重畠して用いることができる。また、表示パネル8006の対向基板（封止基板）に、タッチパネル機能を持たせるようにすることも可能である。または、表示パネル8006の各画素内に光センサを設け、光学式のタッチパネルとすることも可能である。または、表示パネル8006の各画素内にタッチセンサ用電極を設け、容量型式のタッチパネルとすることも可能である。

## 【0305】

バックライトユニット8007は、光源8008を有する。光源8008をバックライトユニット8007の端部に設け、光拡散板を用いる構成としてもよい。

10

## 【0306】

フレーム8009は、表示パネル8006の保護機能の他、プリント基板8010の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム8009は、放熱板としての機能を有していてもよい。

## 【0307】

プリント基板8010は、電源回路、ビデオ信号及びクロック信号を出力するための信号処理回路を有する。電源回路に電力を供給する電源としては、外部の商用電源であってもよいし、別途設けたバッテリー8011による電源であってもよい。バッテリー8011は、商用電源を用いる場合には、省略可能である。

20

## 【0308】

また、表示モジュール8000には、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。

## 【0309】

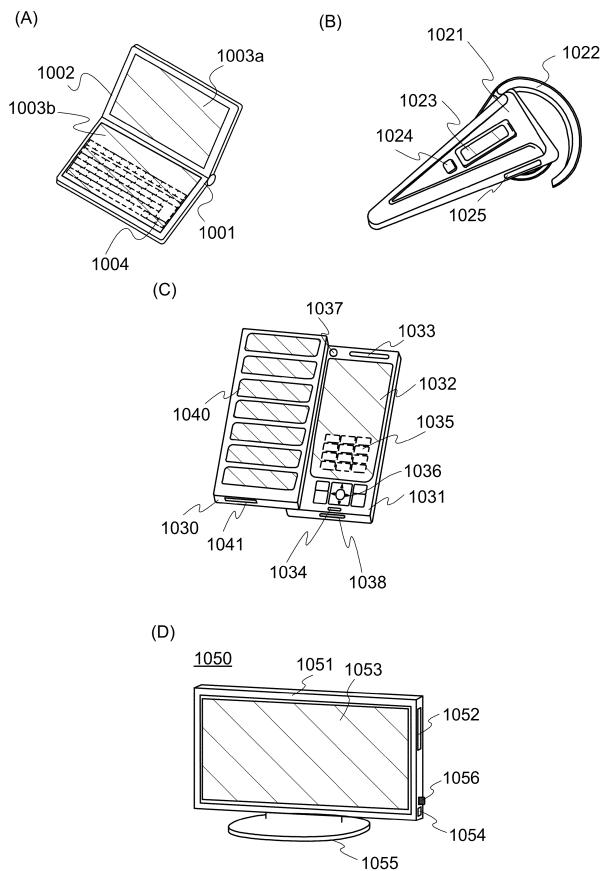

図20は、本発明の一態様の半導体装置を含む電子機器の外観図である。

## 【0310】