(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7032212号

(P7032212)

(45)発行日 令和4年3月8日(2022.3.8)

(24)登録日 令和4年2月28日(2022.2.28)

(51)国際特許分類

|        |                 |     |        |       |         |

|--------|-----------------|-----|--------|-------|---------|

| H 01 L | 21/60 (2006.01) | F I | H 01 L | 21/60 | 3 1 1 Q |

| H 01 L | 23/12 (2006.01) |     | H 01 L | 23/12 | 5 0 1 B |

| H 05 K | 3/34 (2006.01)  |     | H 05 K | 3/34  | 5 0 1 E |

|        |                 |     | H 05 K | 3/34  | 5 0 5 A |

請求項の数 10 (全14頁)

(21)出願番号 特願2018-70751(P2018-70751)

(22)出願日 平成30年4月2日(2018.4.2)

(65)公開番号 特開2019-186243(P2019-186243)

A)

(43)公開日 令和1年10月24日(2019.10.24)

審査請求日 令和2年12月28日(2020.12.28)

(73)特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74)代理人 100107766

弁理士 伊東 忠重

100070150

弁理士 伊東 忠彦

(72)発明者 竹内 昭

長野県長野市小島田町80番地 新光電

気工業株式会社内

田中 輝

長野県長野市小島田町80番地 新光電

気工業株式会社内

審査官 西村 治郎

最終頁に続く

(54)【発明の名称】 配線基板、半導体パッケージ及び配線基板の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

配線基板の一方の面に設けられた複数の第1の接続端子及び複数の第2の接続端子、

を有し、

前記第1の接続端子は、

第1の直径を有し、表面が平坦又は凸状の第1の柱状電極と、

前記第1の柱状電極上の第1のバンプと、

を有し、

前記第2の接続端子は、

前記第1の直径よりも大きな第2の直径を有し、表面が凹状の第2の柱状電極と、

前記第2の柱状電極上の第2のバンプと、

を有し、

前記第1の接続端子同士のピッチが前記第2の接続端子同士のピッチより狭く、

前記第1のバンプ及び前記第2のバンプの融点は、前記第1の柱状電極及び前記第2の柱

状電極の融点よりも低いことを特徴とする配線基板。

## 【請求項2】

前記第1の柱状電極及び前記第2の柱状電極は、銅若しくはニッケル又はこれらの両方を

含み、

前記第1のバンプ及び前記第2のバンプは、錫又ははんだを含むことを特徴とする請求項

1に記載の配線基板。

**【請求項 3】**

前記第1の柱状電極の表面が凸状の曲面であり、

前記第2の柱状電極の表面が凹状の曲面であることを特徴とする請求項1又は2に記載の配線基板。

**【請求項 4】**

前記第1のバンプの表面が凸状の曲面であり、

前記第2のバンプの表面が凸状の曲面であることを特徴とする請求項1乃至3のいずれか1項に記載の配線基板。

**【請求項 5】**

第1の接続部と第2の接続部とを有する配線層と、

前記配線層上に設けられたソルダレジスト層と、

前記ソルダレジスト層を貫通し、前記第1の接続部を露出する第1のピアホールと、

前記ソルダレジスト層を貫通し、前記第2の接続部を露出する第2のピアホールと、

を有し、

前記第1の柱状電極は、前記第1の接続部上に、前記第1のピアホールを通じて前記ソルダレジスト層の表面より上方に突出するよう設けられ、

前記第2の柱状電極は、前記第2の接続部上に、前記第2のピアホールを通じて前記ソルダレジスト層の表面より上方に突出するよう設けられていることを特徴とする請求項1乃至4のいずれか1項に記載の配線基板。

**【請求項 6】**

請求項1乃至5のいずれか1項に記載の配線基板と、

前記配線基板に実装された半導体チップと、

を有し、

前記半導体チップは、

前記第1の接続端子に接続された第3の接続端子と、

前記第2の接続端子に接続された第4の接続端子と、

を有することを特徴とする半導体パッケージ。

**【請求項 7】**

配線基板の一方の面に、電解めっき法により、第1の直径を有し、表面が平坦又は凸状の複数の第1の柱状電極と、前記第1の直径よりも大きな第2の直径を有し、表面が凹状の複数の第2の柱状電極と、を形成する工程と、

電解めっき法により、前記第1の柱状電極上の第1のバンプと、前記第2の柱状電極上の第2のバンプと、を形成する工程と、

を有し、

前記第1の柱状電極同士のピッチが前記第2の柱状電極同士のピッチより狭く、

前記第1のバンプ及び前記第2のバンプの融点は、前記第1の柱状電極及び前記第2の柱状電極の融点よりも低く、

前記第1のバンプ及び前記第2のバンプの形成後に、前記第1のバンプ及び前記第2のバンプの融点以上、前記第1の柱状電極及び前記第2の柱状電極の融点未満の温度でリフローを行う工程を有することを特徴とする配線基板の製造方法。

**【請求項 8】**

前記第1の柱状電極と前記第2の柱状電極とを形成する工程において、

前記第1の柱状電極の表面を凸状の曲面とし、前記第2の柱状電極の表面を凹状の曲面とすることを特徴とする請求項7に記載の配線基板の製造方法。

**【請求項 9】**

前記リフローを行う工程において、

前記第1のバンプの表面を凸状の曲面とし、前記第2のバンプの表面を凸状の曲面とすることを特徴とする請求項7又は8に記載の配線基板の製造方法。

**【請求項 10】**

前記第1の柱状電極と前記第2の柱状電極とを形成する工程の前に、

10

20

30

40

50

第1の接続部と第2の接続部とを有する配線層を形成する工程と、

前記配線層上にソルダレジスト層を形成する工程と、

前記ソルダレジスト層を貫通し、前記第1の接続部を露出する第1のビアホールと、前記ソルダレジスト層を貫通し、前記第2の接続部を露出する第2のビアホールと、を形成する工程と、

を有し、

前記第1の柱状電極と前記第2の柱状電極とを形成する工程において、

前記第1の接続部上に、前記第1のビアホールを通じて前記ソルダレジスト層の表面より上方に突出するように前記第1の柱状電極を形成し、

前記第2の接続部上に、前記第2のビアホールを通じて前記ソルダレジスト層の表面より上方に突出するように前記第2の柱状電極を形成することを特徴とする請求項7乃至9のいずれか1項に記載の配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板、半導体パッケージ及び配線基板の製造方法に関する。

【背景技術】

【0002】

近年、半導体チップの接続端子の多端子化に伴い、直径が異なる複数の接続端子を有する半導体チップが用いられている。このような半導体チップに対応するため、半導体チップを搭載する半導体パッケージに用いられる配線基板にも、直径が異なる複数の接続端子を設けることが求められている。一般に、配線基板の接続端子には、銅(Cu)等のポスト及びその上のバンプが含まれる。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2007-103878号公報

特開2017-152646号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、直径が異なる接続端子を含む半導体パッケージでは、配線基板と半導体チップとの間で接続不良が生じることがある。例えば、直径が大きな接続端子(以下、大径端子ということがある)に関し、2つの大径端子間でバンプ同士の短絡が生じことがある。また、直径が小さな接続端子(以下、小径端子ということがある)に関し、小径端子と半導体チップの接続端子とが接触できず、断線が生じことがある。このような短絡及び断線は、直径が異なる接続端子を含む半導体パッケージの接続信頼性の低下につながる。

【0005】

本発明は、接続信頼性を向上することができる配線基板、半導体パッケージ及び配線基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

配線基板の一態様は、配線基板の一方の面に設けられた複数の第1の接続端子及び複数の第2の接続端子を有する。前記第1の接続端子は、第1の直径を有し、表面が平坦又は凸状の第1の柱状電極と、前記第1の柱状電極上の第1のバンプと、を有する。前記第2の接続端子は、前記第1の直径よりも大きな第2の直径を有し、表面が凹状の第2の柱状電極と、前記第2の柱状電極上の第2のバンプと、を有する。前記第1の接続端子同士のピッチが前記第2の接続端子同士のピッチより狭い。前記第1のバンプ及び前記第2のバンプの融点は、前記第1の柱状電極及び前記第2の柱状電極の融点よりも低い。

【発明の効果】

10

20

30

40

50

## 【0007】

開示の技術によれば、接続信頼性を向上することができる。

## 【図面の簡単な説明】

## 【0008】

【図1】半導体パッケージに含まれる接続端子の例を示す断面図である。

【図2】半導体パッケージに含まれる接続端子の他の例を示す断面図である。

【図3】第1の実施形態に係る配線基板の構造を示す断面図である。

【図4】第1の実施形態に係る配線基板の製造方法を示す断面図（その1）である。

【図5】第1の実施形態に係る配線基板の製造方法を示す断面図（その2）である。

【図6】第1の実施形態に係る配線基板の製造方法を示す断面図（その3）である。

10

【図7】第1の実施形態に含まれる接続端子の形成方法を示す断面図（その1）である。

【図8】第1の実施形態に含まれる接続端子の形成方法を示す断面図（その2）である。

【図9】第1の実施形態に含まれる接続端子の形成方法を示す断面図（その3）である。

【図10】第2の実施形態に係る半導体パッケージを示す断面図である。

## 【発明を実施するための形態】

## 【0009】

本発明者らは、従来の半導体パッケージにおいて短絡及び断線が生じる原因を究明すべく鋭意検討を行った。そして、本発明者らによる詳細な解析の結果、小径端子と大径端子との間で、ポストの高さを揃えているにも拘わらず、小径端子が大径端子よりも低くなっていることが明らかになった。ここで、この新たな知見について説明する。

20

## 【0010】

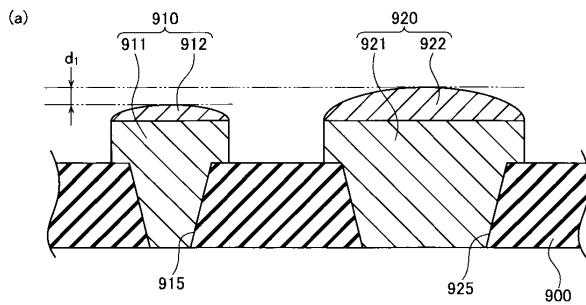

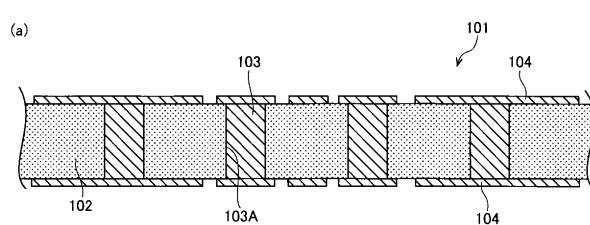

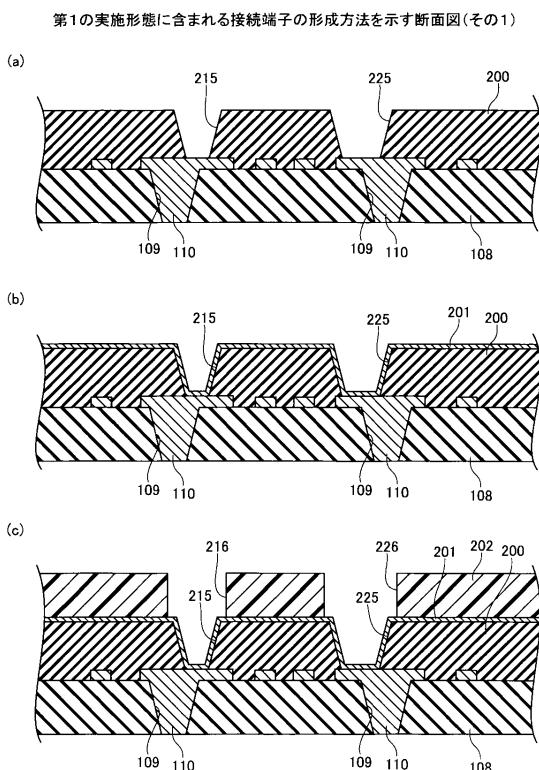

図1は、半導体パッケージに含まれる接続端子の例を示す断面図である。図1(a)及び(b)に示すように、これらの例では、ソルダレジスト層900に小径端子用のビアホール915及び大径端子用のビアホール925が形成されている。ビアホール925の直径はビアホール915の直径よりも大きい。そして、ビアホール915内にポスト911が形成され、ビアホール925内にポスト911よりも直径が大きいポスト921が形成されている。また、ポスト911上にバンプ912が形成され、ポスト921上にバンプ922が形成されている。ポスト911及びバンプ912が小径端子910に含まれ、ポスト921及びバンプ922が大径端子920に含まれる。例えば、ポスト911及び921は電解銅めっき法により形成され、バンプ912及びバンプ922は電解錫めっき法により形成される。これらの形成後にバンプ912及びバンプ922のリフローが行われて小径端子910及び大径端子920が形成される。

30

## 【0011】

図1(a)に示す例では、ポスト911及び921の表面が平坦であり、これらの高さが揃っている。表面が平坦なポスト911及び921の高さを揃えた場合、リフローにより、バンプ922の中央の厚さがバンプ912の中央の厚さよりも大きくなり、大径端子920が小径端子910よりも高くなる。

## 【0012】

また、図1(b)に示す例のように、ポスト911の表面が平坦になり、ポスト921の表面が凸状になることがある。この場合も、リフローにより、バンプ922の中央の厚さがバンプ912の中央の厚さよりも大きくなり、大径端子920が小径端子910よりも高くなる。

40

## 【0013】

また、図1(b)に示す例における頂部の高さの差d2は、図1(a)に示す例における頂部の高さの差d1だけよりも大きく、大径端子920と小径端子910との高さの相違がより顕著となる。

## 【0014】

そして、小径端子910と大径端子920との間に高さの相違がある配線基板に半導体チップがフリップチップ実装されると、大径端子920が半導体チップの接続端子に接触する一方で、小径端子910が半導体チップの接続端子に接触できず、断線が生じることが

50

ある。また、大径端子 920 に含まれるバンプ 922 がリフロー時に過剰になって横方向に漏れ出し、バンプ 922 間で短絡が生じることがある。

【0015】

図 1 に例示していないが、大径端子 920 だけでなく小径端子 910 の表面が凸状になることがある。この場合も、大径端子 920 が小径端子 910 よりも高くなり、断線及び短絡が生じるおそれがある。

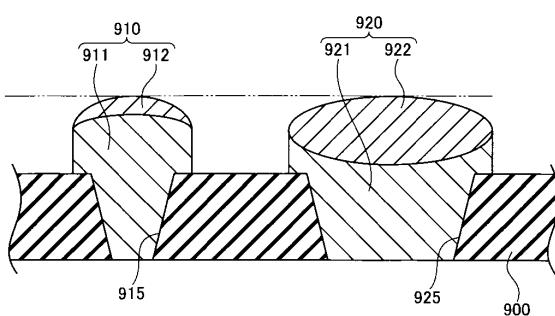

【0016】

これらの現象はこれまで解説されておらず、その対策もとられていない。このような状況下で本発明者らが更に鋭意検討を行った結果、図 2 に示すように、大径端子 920 に含まれるポスト 921 の表面を凹状にすることで、リフロー後において小径端子 910 及び大径端子 920 の高さがほぼ揃い、上記のような断線及び短絡を抑制し、接続信頼性を向上できることが明らかになった。

10

【0017】

本発明者らは、これらの新たな知見に基づいて、以下のような実施形態に想到した。以下、実施形態について添付の図面を参照しながら具体的に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複した説明を省くことがある。

【0018】

(第 1 の実施形態)

第 1 の実施形態について説明する。第 1 の実施形態は配線基板に関する。

20

【0019】

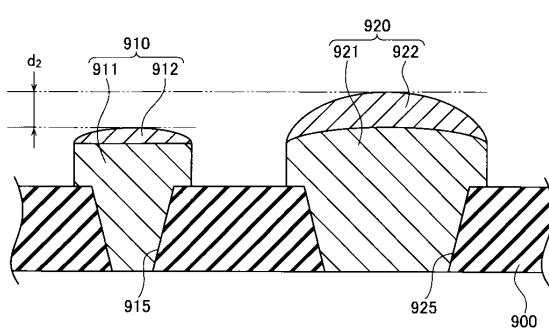

[配線基板の構造]

先ず、配線基板の構造について説明する。図 3 は、第 1 の実施形態に係る配線基板の構造を示す断面図である。

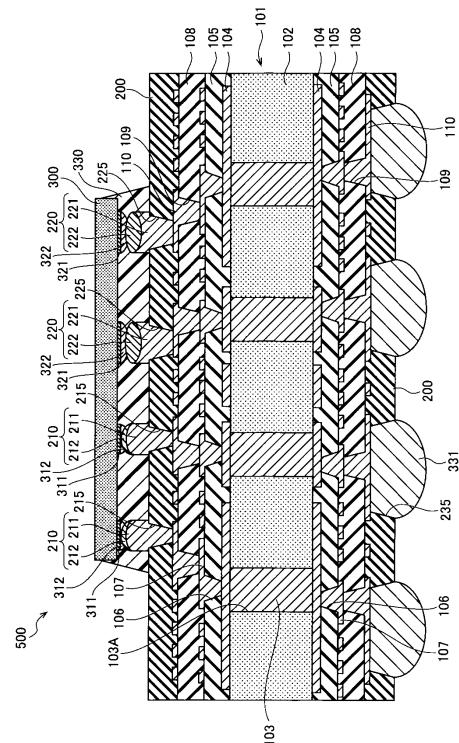

【0020】

図 3 に示すように、第 1 の実施形態に係る配線基板 100 は、支持体としてコア配線基板 101 を含む。コア配線基板 101 はガラスエポキシ樹脂や、ビスマレイミドトリアジン樹脂等の絶縁材料から形成されるコア基板 102 を含む。コア基板 102 の両面に銅等からなる第 1 の配線層 104 が形成されている。コア基板 102 には厚さ方向に貫通するスルーホール 103A が形成されており、スルーホール 103A 内に貫通導体 103 が設けられている。コア基板 102 の両側の第 1 の配線層 104 は貫通導体 103 を介して相互に接続されている。スルーホール 103A の側壁にスルーホールめっき層が形成され、スルーホール 103A の残りの孔には樹脂体が充填されていてもよい。この場合、コア基板 102 の両側の第 1 の配線層 104 はスルーホールめっき層を介して相互に接続される。

30

【0021】

コア基板 102 の両側に第 1 の絶縁層 105 が形成されている。第 1 の絶縁層 105 には、第 1 の配線層 104 の接続部に到達するビアホール 106 が形成されており、第 1 の絶縁層 105 上に、ビアホール 106 内のビア導体を介して第 1 の配線層 104 に接続される第 2 の配線層 107 が形成されている。更に、コア基板 102 の両側において、第 1 の絶縁層 105 上に第 2 の絶縁層 108 が形成されている。第 2 の絶縁層 108 には、第 2 の配線層 107 の接続部に到達するビアホール 109 が形成されており、第 2 の絶縁層 108 上に、ビアホール 109 内のビア導体を介して第 2 の配線層 107 に接続される第 3 の配線層 110 が形成されている。

40

【0022】

コア基板 102 の両側において、第 2 の絶縁層 108 上にソルダレジスト層 200 が形成されている。コア基板 102 の半導体チップと接続される側のソルダレジスト層 200 に第 3 の配線層 110 の接続部に達する第 1 のビアホール 215 及び第 2 のビアホール 225 が形成されている。第 2 のビアホール 225 の直径は第 1 のビアホール 215 の直径よりも大きい。例えば、第 1 のビアホール 215 及び第 2 のビアホール 225 の深さは 15  $\mu\text{m}$  ~ 25  $\mu\text{m}$  である。また、第 1 のビアホール 215 の最下部の直径は 10  $\mu\text{m}$  ~ 15

50

$\mu\text{m}$ 、最上部の直径は $22\mu\text{m} \sim 27\mu\text{m}$ であり、第2のビアホール225の最下部の直径は $40\mu\text{m} \sim 50\mu\text{m}$ 、最上部の直径は $55\mu\text{m} \sim 60\mu\text{m}$ である。コア基板102の反対側のソルダレジスト層200には第3の配線層110の接続部に達する開口部235が形成されている。

【0023】

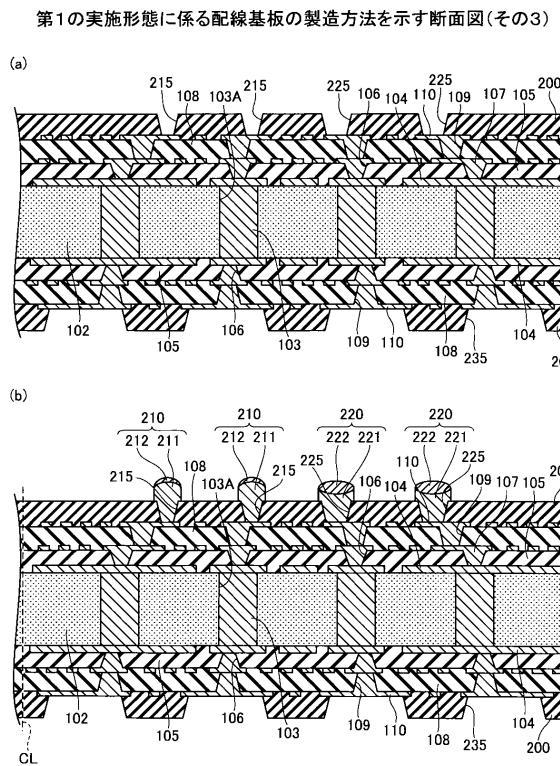

コア基板102の半導体チップと接続される側において、第3の配線層110の接続部上に、第1のビアホール215を通じてソルダレジスト層200の上方まで突出する第1の接続端子210、及び第2のビアホール225を通じてソルダレジスト層200の上方まで突出する第2の接続端子220が形成されている。第1の接続端子210は第1のポスト211及び第1のバンプ212を含み、第2の接続端子220は第2のポスト221及び第2のバンプ222を含む。第1のポスト211の表面は曲面状の凸状であり、第2のポスト221の表面は曲面状の凹状である。第1の接続端子210及び第2の接続端子220の頂部のソルダレジスト層200の表面を基準とする高さは、例えば $15\mu\text{m} \sim 25\mu\text{m}$ であり、互いに同等である。第1のポスト211は第1の柱状電極の一例であり、第2のポスト221は第2の柱状電極の一例である。

10

【0024】

第1のバンプ212及び第2のバンプ222の融点は第1のポスト211及び第2のポスト221の融点よりも低く、例えば、第1のポスト211及び第2のポストは銅(Cu)若しくはニッケル(Ni)又はこれらの両方を含み、第1のバンプ212及び第2のバンプ222は錫(Sn)又ははんだを含む。例えば、第1のポスト211及び第2のポストは電解めっき法により形成された銅めっき膜を有し、その上にニッケルめっき膜が形成されていてもよい。はんだとしては、錫銀(SnAg)系合金、錫亜鉛(SnZn)系合金及び錫銅(SnCu)系合金等の無鉛はんだ、並びに鉛錫(PbSn)系合金の有鉛はんだが例示される。

20

【0025】

このように、本実施形態においては、第1のポスト211の表面が凸状であるのに対し、第2のポスト221の表面が凹状であり、第1の接続端子210及び第2の接続端子220の頂部の高さが互いに同等である。このため、半導体チップのフリップチップ実装の際に、小径端子である第1の接続端子210は半導体チップの接続端子に確実に電気的に接続され、大径端子である第2の接続端子220に関しては、第2のバンプ222の漏れ出しが防止される。従って、本実施形態によれば接続信頼性を向上することができる。

30

【0026】

なお、第1の接続端子210及び第2の接続端子220の高さが互いに完全に一致している必要はなく、フリップチップ実装の際のリフローにおいて第1のバンプ212及び第2のバンプ222が溶融するため、高さに多少のずれがあっても従来の半導体パッケージで生じるような短絡及び断線を抑制することができる。また、第1のポスト211の表面が平坦であっても、同様の効果を得ることができる。

【0027】

その一方、小径ポストの表面が凹状で、大径ポストの表面が平坦又は凹状である場合、リフロー時に、小径ポスト上のバンプの突出量が抑制されると共に、大径ポスト上のバンプがより一層突出することになる。このため、小径ポストを含む小径の接続端子が、大径ポストを含む大径の接続端子より著しく低くなり、これらの間の高さの相違が大きくなる。従って、このような配線基板に半導体チップが実装されると、断線や短絡がより一層生じやすくなり、半導体パッケージの信頼性が低下してしまう。

40

【0028】

なお、第1の接続端子210及び第2の接続端子220のピッチが均等である必要はなく、例えば、第1の接続端子210同士のピッチが第2の接続端子220同士のピッチよりも狭くてもよい。

【0029】

[配線基板の製造方法]

50

次に、配線基板の製造方法について説明する。図4～図6は、第1の実施形態に係る配線基板の製造方法を示す断面図である。

#### 【0030】

先ず、図4(a)に示すように、支持体としてコア配線基板101を準備する。コア配線基板101はコア基板102及び第1の配線層104を備えている。コア基板102には厚さ方向に貫通するスルーホール103Aが形成されており、スルーホール103A内に貫通導体103が設けられている。例えば、スルーホール103Aはドリルやレーザを用いた加工等により形成することができ、貫通導体103及び第1の配線層104はめっき法及びフォトリソグラフィ等により形成することができる。なお、コア配線基板101としては、配線基板100が複数個取れる大判の基板が使用される。つまり、コア配線基板101は、配線基板100に対応する構造体が形成される複数の領域を有している。

10

#### 【0031】

次いで、図4(b)に示すように、コア基板102の両側に未硬化の樹脂フィルムを貼付し、加熱処理して硬化させることにより、第1の絶縁層105を形成する。第1の絶縁層105は、エポキシ樹脂又はポリイミド樹脂等の絶縁樹脂から形成される。液状樹脂を塗布することにより、第1の絶縁層105を形成してもよい。その後、コア基板102の両側の第1の絶縁層105をレーザで加工することにより、第1の配線層104の接続部に到達するビアホール106を第1の絶縁層105に形成する。

#### 【0032】

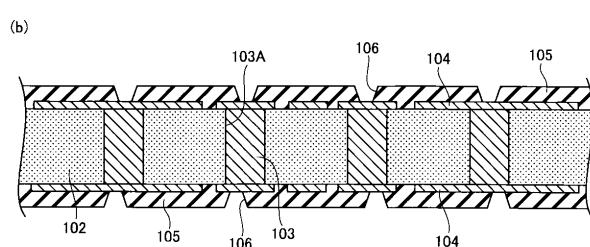

続いて、図5(a)に示すように、コア基板102の両側において、ビアホール106内のビア導体を介して第1の配線層104に接続される第2の配線層107を第1の絶縁層105上に形成する。

20

#### 【0033】

第2の配線層107はセミアディティブ法によって形成することができる。ここで、第2の配線層107の形成方法について詳しく説明する。先ず、第1の絶縁層105上及びビアホール106の内面に無電解めっき法又はスパッタ法により、銅等からなるシード層(不図示)を形成する。次いで、第2の配線層107を形成する部分に開口部が設けられためっきレジスト層(不図示)を形成する。続いて、シード層をめっき給電経路に利用する電解めっき法により、めっきレジスト層の開口部に銅等からなる金属めっき層を形成する。その後、めっきレジスト層を除去する。次いで、金属めっき層をマスクにしてシード層をウェットエッチングにより除去する。このようにして、シード層及び金属めっき層を含む第2の配線層107を形成することができる。

30

#### 【0034】

第2の配線層107の形成後、図5(b)に示すように、コア基板102の両側において、第1の絶縁層105上に、第2の配線層107の接続部上にビアホール109が設けられた第2の絶縁層108を形成する。第2の絶縁層108は、第1の絶縁層105と同様の方法で形成することができる。

#### 【0035】

更に、同じく図5(b)に示すように、コア基板102の両側において、ビアホール109内のビア導体を介して第2の配線層107に接続される第3の配線層110を第2の絶縁層108上に形成する。第3の配線層110は、第2の配線層107と同様の方法で形成することができる。

40

#### 【0036】

次いで、図6(a)に示すように、コア基板102の両側において、第2の絶縁層108上にソルダレジスト層200を形成する。その後、コア基板102の半導体チップと接続される側のソルダレジスト層200に第3の配線層110の接続部に達する第1のビアホール215及び第2のビアホール225を形成する。第2のビアホール225の直径は第1のビアホール215の直径よりも大きくする。また、コア基板102の反対側のソルダレジスト層200に第3の配線層110の接続部に達する開口部235を形成する。

#### 【0037】

50

ソルダレジスト層 200 は、感光性のエポキシ樹脂又はアクリル樹脂等の絶縁樹脂から形成される。樹脂フィルムの貼り付け又は液状樹脂の塗布により、ソルダレジスト層 200 を形成してもよい。第 1 のビアホール 215、第 2 のビアホール 225 及び開口部 235 は、露光及び現像により形成することができる。ソルダレジスト層 200 に非感光性のエポキシ樹脂又はポリイミド樹脂等の絶縁樹脂を用いてもよい。この場合、第 1 のビアホール 215、第 2 のビアホール 225 及び開口部 235 は、レーザ加工又はプラスト処理により形成することができる。

#### 【 0038 】

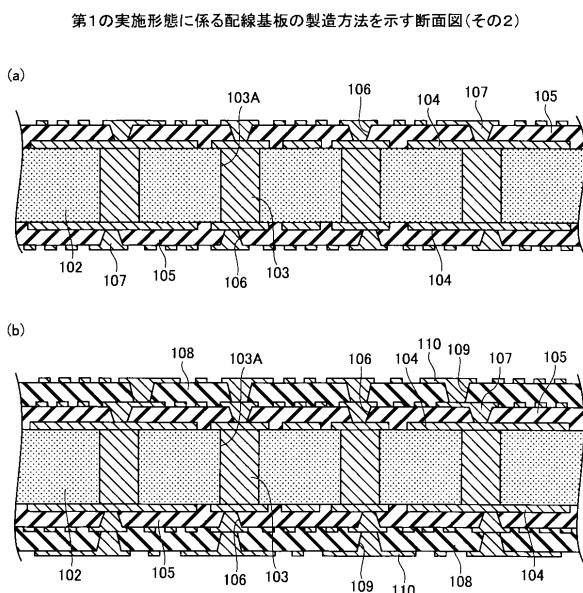

続いて、図 6 ( b ) に示すように、コア基板 102 の半導体チップと接続される側において、第 3 の配線層 110 の接続部上に、第 1 のビアホール 215 を通じてソルダレジスト層 200 の上方まで突出する第 1 の接続端子 210、及び第 2 のビアホール 225 を通じてソルダレジスト層 200 の上方まで突出する第 2 の接続端子 220 を形成する。第 1 の接続端子 210 は第 1 のポスト 211 及び第 1 のバンプ 212 を含み、第 2 の接続端子 220 は第 2 のポスト 221 及び第 2 のバンプ 222 を含む。

10

#### 【 0039 】

次いで、図 6 ( b ) に示す構造体を切断線 C-L に沿ってスライサー等により切断する。これにより、配線基板 100 に対応する構造体が個片化され、大判のコア配線基板 101 から第 1 の実施形態に係る配線基板 100 が複数得られる。このようにして、図 3 に示す第 1 の実施形態に係る配線基板 100 を製造することができる。

20

#### 【 0040 】

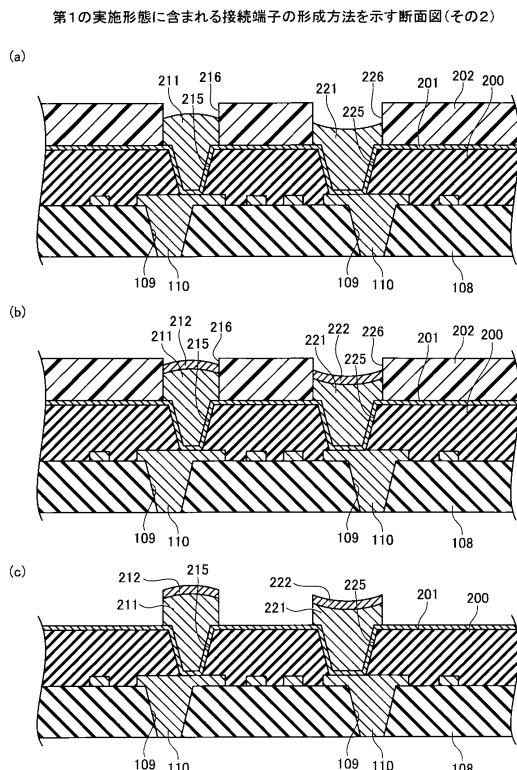

ここで、第 1 の接続端子 210 及び第 2 の接続端子 220 の形成方法について詳しく説明する。図 7 ~ 図 9 は、第 1 の接続端子 210 及び第 2 の接続端子 220 の形成方法を示す断面図である。

#### 【 0041 】

図 7 ( a ) に示すように、第 1 のビアホール 215 及び第 2 のビアホール 225 を形成した後、図 7 ( b ) に示すように、シード層 201 を形成する。シード層 201 は無電解銅めっき法により形成することができ、例えば、その厚さは 0.3 μm ~ 0.8 μm とする。

30

#### 【 0042 】

次いで、図 7 ( c ) に示すように、第 1 の接続端子 210 を形成する部分に第 1 の開口部 216 が設けられ、第 2 の接続端子 220 を形成する部分に第 2 の開口部 226 が設けられためっきレジスト層 202 をシード層 201 上に形成する。第 1 の開口部 216 及び第 2 の開口部 226 はフォトリソグラフィにより形成することができる。例えば、めっきレジスト層 202 の厚さは 25 μm ~ 35 μm とし、第 1 の開口部 216 の直径は 40 μm ~ 45 μm、第 2 の開口部 226 の直径は 80 μm ~ 85 μm とする。

#### 【 0043 】

その後、図 8 ( a ) に示すように、第 1 のビアホール 215 及び第 1 の開口部 216 内に第 1 のポスト 211 を形成し、第 2 のビアホール 225 及び第 2 の開口部 226 内に第 2 のポスト 221 を形成する。第 1 のポスト 211 及び第 2 のポスト 221 は電解めっき法により形成することができる。

40

#### 【 0044 】

電解めっき法により開口部内に銅めっき膜等のめっき膜を形成する場合、初期段階ではめっき膜の表面が凹状であり、徐々に平坦になり、その後に凸状になる。このような形状変化は開口部の直径及びめっき液の埋め込み性等に依存しており、特に埋め込み性が低いめっき液を用いた場合、めっき膜の表面が平坦又は凸状になるまでの時間が、開口部の直径に依存しやすい。本実施形態では、めっき液のこのような性質を利用して、第 2 のポスト 221 の表面が凹状、かつ第 1 のポスト 211 の表面が凸状の状態で成膜を停止する。この結果、図 8 ( a ) に示すように、表面が凸状の第 1 のポスト 211 及び表面が凹状の第 2 のポスト 221 が得られる。なお、第 2 のポスト 221 の表面が凹状、かつ第 1 のポスト 211 の表面が平坦な状態で成膜を停止してもよい。第 1 のポスト 211 及び第 2 のポスト 221 を、例えば銅めっき膜及びニッケルめっき膜の積層構造にしてもよい。

50

**【 0 0 4 5 】**

続いて、図 8 ( b ) に示すように、第 1 のポスト 2 1 1 上に第 1 のバンプ 2 1 2 を形成し、第 2 のポスト 2 2 1 上に第 2 のバンプ 2 2 2 を形成する。第 1 のバンプ 2 1 2 及び第 2 のバンプ 2 2 2 は電解めっき法により形成することができる。第 1 のバンプ 2 1 2 及び第 2 のバンプ 2 2 2 は、それぞれ第 1 のポスト 2 1 1 及び第 2 のポスト 2 2 1 の表面に倣うように形成される。従って、第 1 のバンプ 2 1 2 の表面は凸状又は平坦であり、第 2 のバンプ 2 2 2 の表面は凹状である。第 1 のバンプ 2 1 2 及び第 2 のバンプ 2 2 2 としては、例えば電解めっき法により錫バンプを形成する。

**【 0 0 4 6 】**

次いで、図 8 ( c ) に示すように、めっきレジスト層 2 0 2 を除去する。

10

**【 0 0 4 7 】**

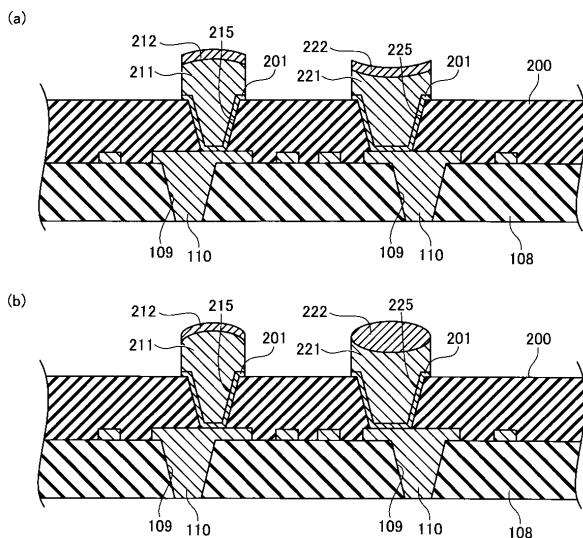

その後、図 9 ( a ) に示すように、第 1 のバンプ 2 1 2 、第 2 のバンプ 2 2 2 、第 1 のポスト 2 1 1 及び第 2 のポスト 2 2 1 をマスクにしてシード層 2 0 1 をウェットエッチングにより除去する。

**【 0 0 4 8 】**

続いて、第 1 のバンプ 2 1 2 及び第 2 のバンプ 2 2 2 の融点以上、第 1 のポスト 2 1 1 及び第 2 のポスト 2 2 1 の融点未満の温度でリフローを行う。この結果、図 9 ( b ) に示すように、第 1 のバンプ 2 1 2 及び第 2 のバンプ 2 2 2 の形状が、エネルギー的により安定な形状に変化し、特に、凹状であった第 2 のバンプ 2 2 2 の表面が凸状になる。このようにして、第 1 の接続端子 2 1 0 及び第 2 の接続端子 2 2 0 を形成することができる。また、このような方法で形成される第 1 の接続端子 2 1 0 及び第 2 の接続端子 2 2 0 の頂部のソルダレジスト層 2 0 0 の表面を基準とする高さは互いに同等になり、例えば  $15 \mu m$  ~  $25 \mu m$  となる。

20

**【 0 0 4 9 】**

このような製造方法によれば、第 1 の接続端子 2 1 0 又は第 2 の接続端子 2 2 0 を形成するためには独立の工程を要せずに、互いに頂部の高さが同等の第 1 の接続端子 2 1 0 及び第 2 の接続端子 2 2 0 を備えた配線基板 1 0 0 を製造することができる。

**【 0 0 5 0 】**

なお、図 3 及び図 6 ( b ) ではシード層 2 0 1 を省略してある。

30

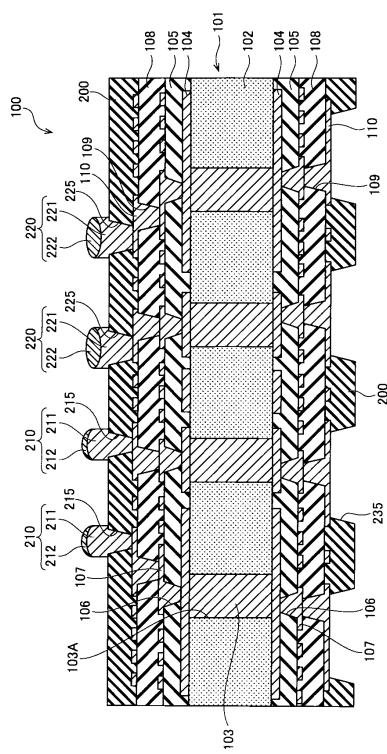

**【 0 0 5 1 】****( 第 2 の実施形態 )**

次に、第 2 の実施形態について説明する。第 2 の実施形態は半導体パッケージに関する。

図 1 0 は、第 2 の実施形態に係る半導体パッケージ 5 0 0 を示す断面図である。

**【 0 0 5 2 】**

図 1 0 に示すように、第 2 の実施形態に係る半導体パッケージ 5 0 0 は、第 1 の実施形態に係る配線基板 1 0 0 、半導体チップ 3 0 0 、第 3 のバンプ 3 1 2 及び第 4 のバンプ 3 2 2 、アンダーフィル樹脂 3 3 0 並びに外部接続端子 3 3 1 を有する。

**【 0 0 5 3 】**

半導体チップ 3 0 0 は、第 3 のバンプ 3 1 2 を介して第 1 の接続端子 2 1 0 に接続される第 3 の接続端子 3 1 1 、及び第 4 のバンプ 3 2 2 を介して第 2 の接続端子 2 2 0 に接続される第 4 の接続端子 3 2 1 を含む。第 3 の接続端子 3 1 1 及び第 4 の接続端子 3 2 1 は、例えば電極パッドであり、第 4 の接続端子 3 2 1 の直径は第 3 の接続端子 3 1 1 の直径よりも大きい。第 3 のバンプ 3 1 2 及び第 4 のバンプ 3 2 2 には、例えば、はんだボールが用いられる。はんだボールの材料としては、第 1 のバンプ 2 1 2 及び第 2 のバンプ 2 2 2 と同様に、錫銀 ( SnAg ) 系合金、錫亜鉛 ( SnZn ) 系合金及び錫銅 ( SnCu ) 系合金等の無鉛はんだ、並びに鉛錫 ( PbSn ) 系合金の有鉛はんだが例示される。半導体チップ 3 0 0 と配線基板 1 0 0 のソルダレジスト層 2 0 0 との間に、エポキシ樹脂等のアンダーフィル樹脂 3 3 0 が充填されている。

40

**【 0 0 5 4 】**

配線基板 1 0 0 の半導体チップ 3 0 0 とは反対側の面において、第 3 の配線層 1 1 0 上に

50

外部接続端子 331 が設けられている。外部接続端子 331 には、例えば、第 3 のバンプ 312 及び第 4 のバンプ 322 と同様のはんだボールが用いられる。

【0055】

このような半導体パッケージ 500 を製造するには、個片化後の配線基板 100 を準備し、第 3 のバンプ 312 及び第 4 のバンプ 322 を用いて、半導体チップ 300 を配線基板 100 にフリップチップ実装する。このとき、配線基板 100 の第 1 の接続端子 210 及び第 2 の接続端子 220 の頂部の高さがほぼ揃っているため、第 1 の接続端子 210 と第 3 の接続端子 311 とが良好に接続され、第 2 の接続端子 220 と第 4 の接続端子 321 とが良好に接続される。半導体チップ 300 の実装後、半導体チップ 300 とソルダレジスト層 200 との間にアンダーフィル樹脂 330 を充填する。また、外部接続端子 331 を第 3 の配線層 110 上に形成する。

10

【0056】

このようにして、半導体パッケージ 500 を製造することができる。

【0057】

以上、好ましい実施の形態等について詳説したが、上述した実施の形態等に制限されることはなく、特許請求の範囲に記載された範囲を逸脱することなく、上述した実施の形態等に種々の変形及び置換を加えることができる。例えば、上述した実施の形態ではコア基板が用いられているが、本開示はコアレス基板に適用することも可能である。

【符号の説明】

【0058】

20

|     |           |

|-----|-----------|

| 100 | 配線基板      |

| 101 | コア配線基板    |

| 102 | コア基板      |

| 200 | ソルダレジスト層  |

| 210 | 第 1 の接続端子 |

| 211 | 第 1 のポスト  |

| 212 | 第 1 のバンプ  |

| 220 | 第 2 の接続端子 |

| 221 | 第 2 のポスト  |

| 222 | 第 2 のバンプ  |

| 300 | 半導体チップ    |

| 311 | 第 3 の接続端子 |

| 312 | 第 3 のバンプ  |

| 321 | 第 4 の接続端子 |

| 322 | 第 4 のバンプ  |

| 330 | アンダーフィル樹脂 |

| 500 | 半導体パッケージ  |

30

40

50

【四面】

【 四 1 】

【 図 2 】

半導体パッケージに含まれる接続端子の例を示す断面図

半導体パッケージに含まれる接続端子の他の例を示す断面図

(b)

10

20

【 図 3 】

【 四 4 】

### 第1の実施形態に係る配線基板の構造を示す断面図

### 第1の実施形態に係る配線基板の製造方法を示す断面図(その1)

30

40

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図9】

【図10】

### 第1の実施形態に含まれる接続端子の形成方法を示す断面図(その3)

## 第2の実施形態に係る半導体パッケージを示す断面図

10

20

30

40

50

---

フロントページの続き

(56)参考文献 特開2019-140174 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/447 - 21/449

H01L 21/60

H01L 23/12 - 23/14

H05K 3/34