(11) *Número de Publicação:* PT 91023 B

(51) *Classificação Internacional:* (Ed. 6)

H03C003/09 A

H04L027/12 B

**(12) FASCÍCULO DE PATENTE DE INVENÇÃO**

|                                           |                                                        |                                                                                   |    |

|-------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|----|

| (22) <i>Data de depósito:</i>             | 1989.06.29                                             | (73) <i>Titular(es):</i>                                                          |    |

| (30) <i>Prioridade:</i>                   | 1988.10.28 DE 3836822                                  | AEG MOBILE COMMUNICATION GMBH<br>WILHELM-RUNGE-STRASSE 11, W7900<br>ULM/DONAU     | DE |

| (43) <i>Data de publicação do pedido:</i> | 1990.04.30                                             | (72) <i>Inventor(es):</i>                                                         |    |

| (45) <i>Data e BPI da concessão:</i>      | 12/94 1994.12.06                                       | MARTIN FRITZMANN                                                                  | DE |

| (54) <i>Epígrafe:</i>                     | MODULADOR DE FREQUÊNCIA COM CIRCUITO DE FASE BLOQUEADA | (74) <i>Mandatário(s):</i>                                                        |    |

| (57) <i>Resumo:</i>                       |                                                        | ANTÓNIO JOÃO COIMBRA DA CUNHA FERREIRA<br>RUA DAS FLORES 74 4/AND. 1294 LISBOA PT |    |

[Fig.]

PATENTE N° 91.023

"Modulador de frequência com circuito de fase bloqueada"

para que

AEG MOBILE COMMUNICATION GmbH, pretende obter privilégio de invenção em Portugal.

RESUMO

O presente invento refere-se a um modulador de frequência para transmissão alternativa de sinais de dados ou sinais vocais com um oscilador comandado por tensão através de um circuito fechado de regulação de fase que inclui um divisor de frequência de módulo duplo com relação de divisão ajustável constituído por um divisor ( $N$ ) ajustável, um divisor ( $A$ ) ajustável e um pré-divisor de módulo duplo ajustável comandado pelo divisor ( $A$ ). Os divisores ( $A$ ) e ( $N$ ) são carregáveis em série. No retorno da saída do divisor ( $A$ ) para a entrada de comando do pré-divisor de módulo duplo encontra-se previsto um controlador de flanco que, quando se transmitem sinais de dados NRZ (sem retorno a zero), retarda o flanco positivo ou negativo do sinal de saída do divisor ( $A$ ), que serve de sinal de controlo de módulo, de pelo menos, um período do sinal de saída do pré-divisor e conduz o sinal de controlo de módulo, assim modificado, à entrada de comando do pré-divisor e, quando se transmitem sinais vocais, deixa passar o sinal de controlo de módulo sem o modificar.

FIG.2

### MEMÓRIA DESCRIPTIVA

O presente invento refere-se a um modulador de frequência de acordo com os conceitos fundamentais contidos na reivindicação 1.

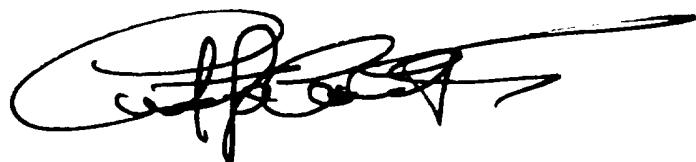

Para a transmissão por exemplo em alternativa de sinais de dados (No-Return-to-zero) ou de sinais vocais de banda limitada já foi proposto utilizar-se um modulador de frequência que engloba um oscilador (VCO) comandado por tensão, directamente modulado e regulado através de um circuito fechado de regulação de fase, cujo esquema de blocos se mostra na Fig. 1.

Como se pode ver na Fig. a frequência de saída  $f_a$  do VCO é directamente modulada através da entrada de modulação do VCO, aos sinais de dados NRZ ou aos sinais vocais. Através de um retorno a frequência de saída é conduzida a um divisor de frequência de módulo duplo com relação de divisão ajustável, cujo sinal de saída é conduzido, à frequência  $f_{IST}$ , a um detector de fases PD. No detector de fase PD este sinal  $f_{IST}$  é comparado com sinal de referência  $f_{REF}$  também dividido na sua frequência por um divisor de referência R, retirando-se desta comparação uma grandeza de regulação que, de forma conhecida se conduz a um filtro de circuito SF que efectua a regulação do VCO.

O divisor de frequência de módulo duplo é como se sabe constituído por um pré-divisor de módulo duplo V e bem como por um divisor ajustável N e um divisor ajustável A. O factor divisor total  $N'$  calcula-se pela expressão  $N' = P + A$ , em que N e A são os factores divisores, representados por um número inteiro, do divisor N ou do divisor A. P é o menor dos dois factores divisores P e  $P + 1$  é do pré-divisor de módulo duplo V, representados por números inteiros.

Normalmente o divisor N, o divisor A e o detector de fase PD assim como eventualmente também o divisor de referência R são realizados num circuito integrado LSIP.

É sabido que a modulação da voz só é possível até um certo limite inferior da frequência. Este é determinado pelos pa-

-3-

râmetros do enrolamento. Como na modulação de dados a divisão um/zero pode ser irregular torna-se necessário um modulador em que não se verifique qualquer passagem alta.

Na solução mostrada na Fig. 1 o divisor A, correspondente à série de dados, é ajustado através dos condutores de comando D1 e D2 a fim de manter a frequência de saída  $f_a$ . Este processo exige um divisor de frequência de módulo duplo no qual os factores de divisão possam ser ajustados em paralelo. Para carregar este divisor de frequência por meio de um microprocessador tornam-se necessárias, no exemplo da Fig. 1, dezanove condutores de comando para os divisores N, A e Z. O posto de corte é portanto de construção muito dispendiosa. Utilizando-se divisores de frequência carregáveis em série e baratos o factor de divisão A não pode ser transferido através do microprocessador, com a rapidez suficiente.

O objectivo do presente invento consiste em proporcionar um modulador de frequência do tipo anteriormente referido realizável com um dispendio de material o mais reduzido possível.

A solução preconizada pelo presente invento encontra-se descrita na reivindicação 1, cobrindo as reivindicações subordinadas concretizações vantajosas e aperfeiçoamentos do invento assim como uma aplicação preferencial do mesmo.

A solução preconizada pelo presente invento consiste em se utilizarem, em vez dos divisores N e A carregados em paralelo até agora usados, divisores N e A carregáveis em série no divisor de frequência de módulo duplo e se prever adicionalmente no retorno da saída do divisor A para a entrada de comando do pré-divisor de módulo duplo um controlador de flanco.

Ao transmitir sinais NRZ o controlo dos flancos retarda de um período, de acordo com o invento, o flanco positivo ou negativo do sinal de saída do pré-divisor de módulo duplo que serve de sinal de controlo de módulo e conduz este sinal de módulo de controlo modificado à entrada de comando do divisor módulo duplo.

Uma vantagem importante da solução preconizada pelo presente invento consiste no facto de a sua realização se conseguir

-4-

com muito menos condutores que os necessários nas soluções anteriores que utilizavam divisores A e N carregáveis em paralelo.

Deste modo torna-se possível, por um lado conceber o ponto de corte para o microprocessador de uma forma mais simples e barata e por outro, reduzir consideravelmente o volume necessário para a parte digital do modulador de frequência, conseguindo-se portanto uma construção compacta e económica do modulador.

Outra vantagem do esquema do presente invento consiste no facto de, na realização atrás referida, uma parte do esquema ser feito sob a forma de circuito integrado, exigindo portanto uma caixa IC mais pequena, visto que esta necessita de menos saídas.

O invento será em seguida explicado em pormenor, em correlação com as figuras. Estas mostram:

- a Fig. 1 - o esquema de blocos, já comentado, do modulador de frequência proposto anteriormente, com divisores A e N carregáveis em paralelo,

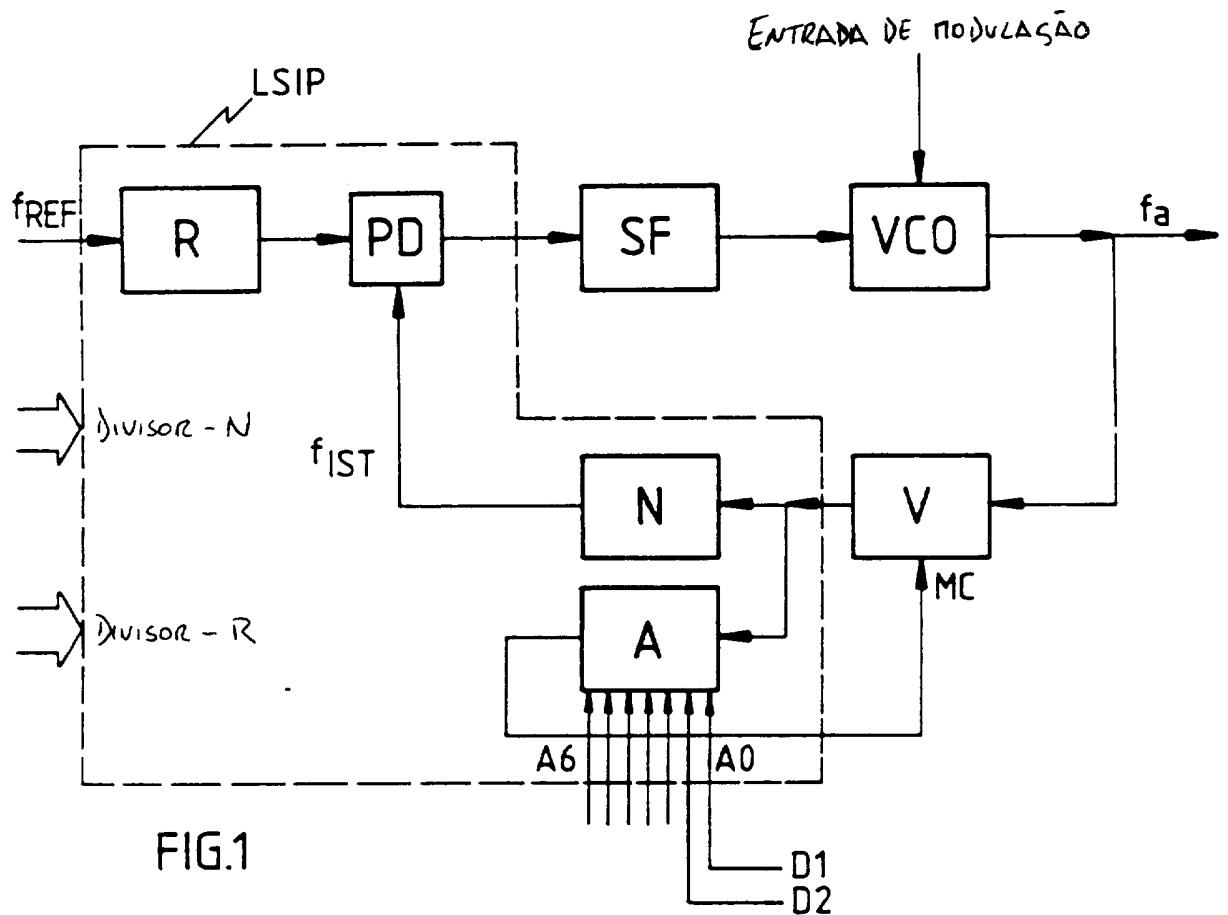

- a Fig. 2 - um esquema de blocos de uma forma de concretização vantajosa do modulador de frequência de acordo com o invento, com divisores A e N carregáveis em série e um controlador de flanco adicional,

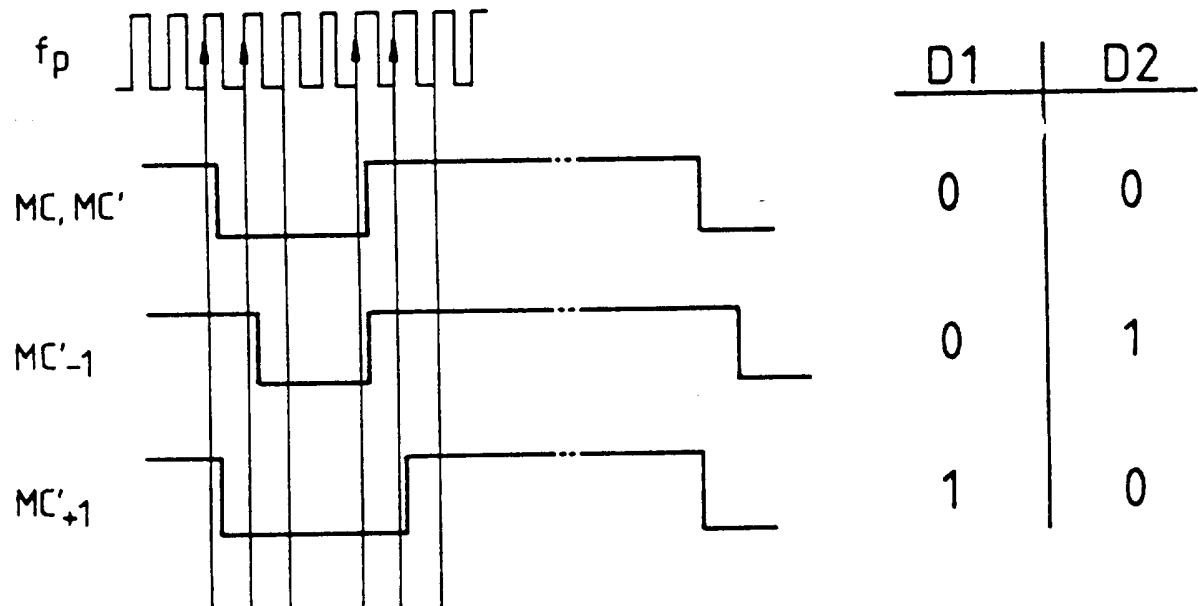

- a Fig. 3 - a relação temporal dos sinais de entrada e de saída do controlo de flancos de acordo com as Figs. 4 ou 5,

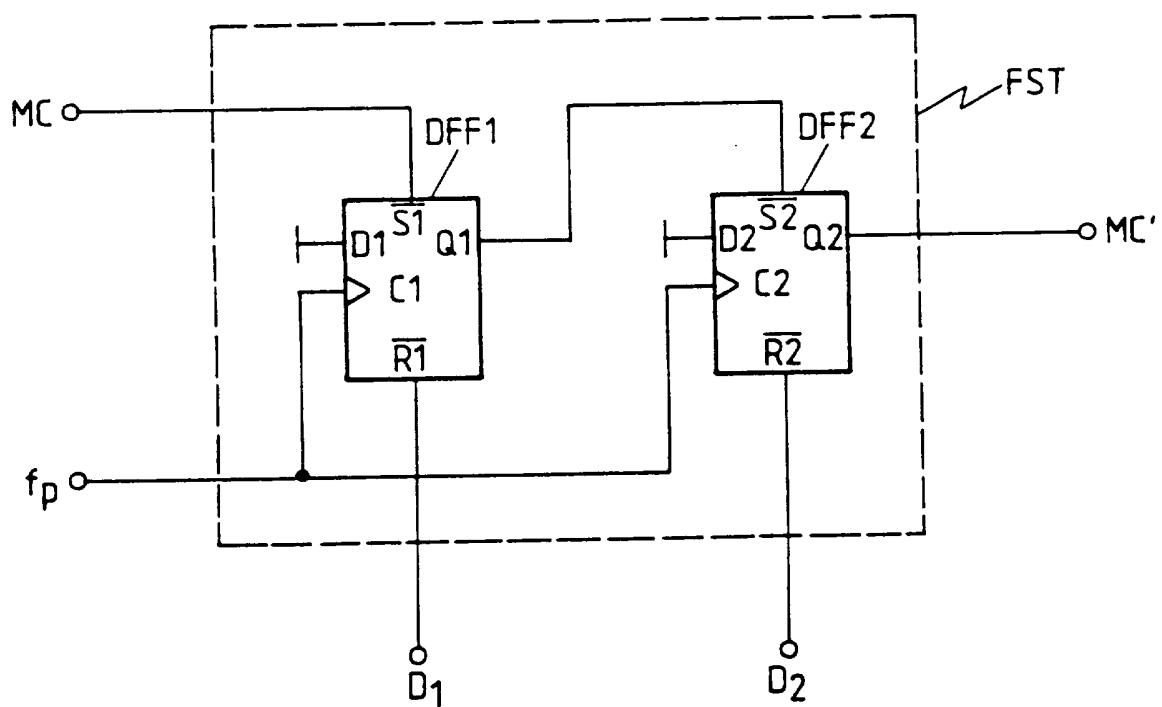

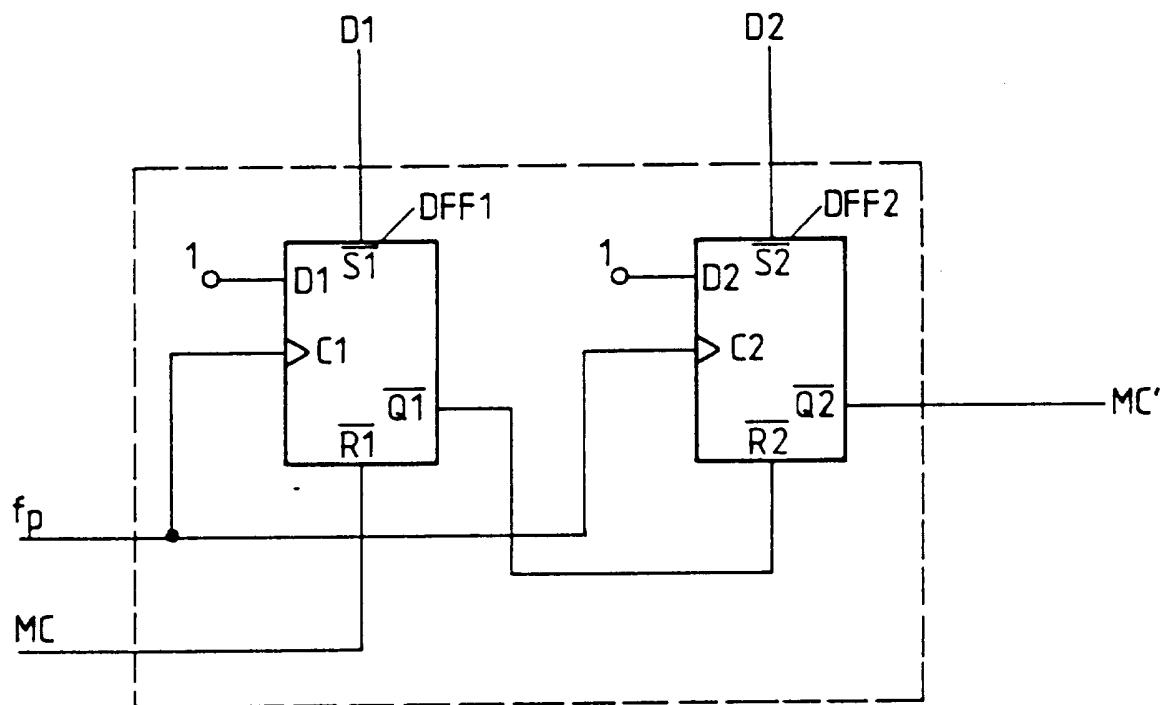

- as Figs. 4 e 5 - formas de realização preferenciais do controlador de flancos de acordo com a Fig. 2.

O modulador de frequência mostrado na Fig. 2 distingue-se do modulador do tipo anterior, mostrado na Fig. 1 por, em lugar dos divisores N e A carregados em paralelo, utilizar divisores N e A carregáveis em série e por, no retorno da saída do divisor A para a entrada de comando do pré-divisor de módulo duplo V, se encontrar montado o controlador de flanco FST. O número das vias de comando necessárias reduz-se, por efeito das medidas pre-

-5-

conizadas pelo presente invento, de 19 (9 condutores de comando para o divisor N, 3 para o divisor R e 7 para o divisor A da Fig. 1) para apenas 5 designadamente os condutores de comando Dados, Relógio e Permissão do "bus" de dados assim como pelos condutores de comando D1 e D2 para modificação do factor divisor total N' de +1 e -1, quando se transmitem sinais de dados NRZ, ou quando se transmitem sinais vocais.

Como se mostra na Fig. 3 a modificação do factor divisor total N' de +1 ou -1 é feita através do controlador de flancos FST, retardando de um período do sinal de saída  $f_p$  do pré-divisor de módulo duplo V o flanco positivo ou negativo do sinal de saída do divisor A que serve de sinal de controlo de módulo MC e conduzindo este sinal de controlo de módulo modificado MC' à entrada de comando do pré-divisor de módulo duplo V. Quando o factor divisor total N' não tenha sido modificado o sinal de controlo de módulo MC é conduzido, não modificado, à entrada de comando do pré-divisor de módulo duplo V.

Por  $f_p$  designa-se a duração do sinal de saída do pré-divisor de módulo duplo. MC e MC', no caso de transmissões vocais, têm durações iguais.  $MC'_{-1}$  e  $MC'_{+1}$  designam a duração em transmissões de dados NRZ. Da tabela de verdade, anexa, retiram-se as condições lógicas de D1 e D2.

As formas vantajosas de realização do controlador de flancos de acordo com o invento, mostradas na Fig. 4, têm o comportamento mostrado na Fig. 3. Se D1 e D2 são zeros lógicos, MC é duas vezes negativado em  $\bar{S}1$  e depois em  $\bar{S}2$  e portanto sai retardado sob a forma MC'. Se D1 é um zero lógico e D2 é um um lógico MC é negativado em Q1. Como a entrada de retorno e a entrada de avanço do segundo multivibrador biestável, quando MC é um zero lógico, ficam livres, só com o próximo flanco de subida de  $f_p$  sai em MC' a condição existente em D2. O flanco de queda de MC aparece em MC' retardado de um período de  $f_p$ . Se D1 é um um lógico e D2 um zero lógico Q1 aparece em MC', negativado. Como a entrada de retorno e a entrada de avanço, quando MC é um um lógico, ficam livres, só com o próximo flanco de subida de  $f_p$  sai em Q1 a condição

-6-

ção existente em D1. Como Q1 é invertido em MC', o flanco de subida de MC aparece em MC' retardado de um período de  $f_p$ .

O circuito mostrado na Fig. 5 é funcionalmente equivalente ao da Fig. 4 já descrito. Em particular as interdependências temporais representadas na Fig. 3 são válidas também neste caso.

Uma vantagem especial do circuito das Fig. 4 e 5 consiste no facto de se poderem usar componentes normalizados como por exemplo os multivibradores biestáveis D duplos da série 74 HC 74 com a consequente economia de produção.

Especialmente vantajosa é a aplicação do invento em aparelhos de radio móveis, como por exemplo telefones instalados em automóveis assim como em sistemas de radio como redes de rádio de ondas sincronizadas, quando se tenham que transmitir sinais de dados e sinais vocais através do mesmo canal de rádio.

É óbvio que o presente invento pode ser adaptado e desenvolvido pelos especialistas na matéria, não se entrando aqui em pormenores sobre esse tema.

Assim é, por exemplo, concebível realizar todos os componentes do modulador de frequência do presente invento, com exceção do VCO em circuito integrado.

Além disso é ainda concebível realizar o divisor de frequência de módulo duplo do presente invento em conjunto com o controlador de flanco, sob a forma de um circuito integrado especial e utilizar este componente, IC, em variadíssimas aplicações.

Para terminar é ainda possível, para modificar o factor de divisão total N' de mais de +1 ou -1 (por exemplo +2 ou -2 ou +100 ou -100, etc.), retardar o flanco positivo ou negativo do sinal de controlo de módulo MC de mais de um período do sinal de saída  $f_p$  do pré-divisor de módulo duplo V.

-7-

Por fim é concebível utilizar-se um multivibrador bies-tável D com entradas de avanço e retorno não invertidas em vez de um multivibrador biestável D com entradas de avanço e retorno invertidas.

Por fim ainda é concebível utilizar-se um multivibrador biestável JK em vez de um multivibrador biestável D.

R E I V I N D I C A Ç Õ E S

1 - Modulador de frequência para transmissão alternativa de sinais de dados NRZ (sem retorno a zero) ou sinais vocais com um oscilador regulado por tensão, através de um circuito fechado de regulação de fase que inclui um divisor de frequência de módulo duplo, com relação de divisão ajustável, constituído por um divisor ( $N$ ) ajustável, um divisor ( $A$ ) ajustável e um pré-divisor de módulo duplo ajustável, comandado pelo divisor ( $A$ ), caracterizado por:

- o divisor ( $A$ ) e o divisor ( $N$ ) serem carregáveis em série,

- se encontrar previsto no retorno da saída do divisor ( $A$ ) para a entrada de comando do pré-divisor de módulo duplo ( $V$ ) um controlador de flanco (FST),

- o controlador de flanco (FST), quando se transmitem sinais de dados NRZ, retardar o flanco positivo ou negativo do sinal de saída do divisor ( $A$ ) que serve de sinal de controlo de módulo (MC), de um período do sinal de saída ( $f_p$ ) do pré-divisor de módulo duplo ( $V$ ) e conduzir este sinal de controlo de módulo modificado ( $MC'$ ) à entrada de comando do pré-divisor de módulo duplo ( $V$ ) e, quando se transmitem sinais vocais, conduzir, sem qualquer modificação, o sinal de controlo de módulo (MC) à entrada de comando do pré-divisor de módulo duplo ( $V$ ).

2 - Modulador de frequência de acordo com a reivindicação 1, caracterizado por o controlador de flanco (FST) ser realizado por dois multivibradores biestáveis (DFF1, DFF2).

3 - Modulador de frequência de acordo com a reivindicação 2, caracterizado por:

- o sinal de saída ( $f_p$ ) do pré-divisor de módulo duplo ( $V$ ) ser conduzido à entrada do relógio (C1, C2) de ambos os multivibradores biestáveis D (DFF1, DFF2),

- o sinal de controlo de módulo (MC) ser conduzido à entrada de avanço invertida ( $\bar{S1}$ ) do primeiro multivibrador biestável D (DFF1),

-9-

- a saída ( $Q_1$ ) do primeiro multivibrador biestável D (DFF1) se encontrar ligada à entrada de avanço invertida ( $\bar{S}_2$ ) do segundo multivibrador biestável D (DFF2),

- ao transmitirem-se sinais de dados NRZ, na saída ( $Q_2$ ) do segundo multivibrador biestável D (DFF2), sair um sinal de controlo de módulo modificado ( $MC'$ ), por efeito do controlador de flanco (FST),

- as entradas de preparação ( $D_1, D_2$ ) de ambos os multivibradores biestáveis D (DFF1, DFF2) se encontrarem ligadas à massa,

- o comando ( $D_1, D_2$ ) do controlador de flanco se fazer através da entrada de retorno invertida ( $\bar{R}_1, \bar{R}_2$ ) de ambos os multivibradores biestáveis (DFF1, DFF2).

4 - Modulador de frequência de acordo com a reivindicação 2, caracterizado por:

- o sinal de saída ( $f_p$ ) do pré-divisor de módulo duplo ( $V$ ) ser conduzido à entrada do relógio ( $C_1, C_2$ ) de ambos os multivibradores biestáveis (DFF1, DFF2),

- o sinal de controlo de módulo ( $MC$ ) ser conduzido à entrada de retorno invertida ( $\bar{R}_1$ ) do primeiro multivibrador biestável D (DFF1),

- a saída invertida ( $\bar{Q}_1$ ) do primeiro multivibrador biestável D (DFF1) se encontrar ligada à entrada de retorno invertida ( $\bar{R}_2$ ) do segundo multivibrador biestável D (DFF2),

- ao transmitirem-se sinais de dados NRZ por meio do controlador de flanco FST, sair na saída invertida ( $\bar{Q}_2$ ) do segundo multivibrador biestável D (DFF2), um sinal de controlo de módulo modificado ( $MC'$ ),

- as entradas de preparação ( $D_1, D_2$ ) de ambos os multivibradores biestáveis (DFF1, DFF2), serem uns lógicos,

- o comando ( $D_1, D_2$ ) do controlador de flanco se fazer através das entradas de avanço invertidas ( $\bar{S}_1, \bar{S}_2$ ) de ambos os multivibradores biestáveis D (DFF1, DFF2).

-10-

5 - Modulador de frequência de acordo com uma das reivindicações de 1 a 4, caracterizado por quando associado a aparelhos de rádio de preferência em aparelhos rádio portáteis em especial telefones móveis e/rádio, de preferência em <sup>redes</sup> redes de feixes e em especial em redes de ondas rádio em circuito fechado permitir a transmissão por um mesmo canal rádio de sinais vocais e sinais de dados.

Lisboa, 20.JUN.1939

Por AEG OLYMPIA AKTIENGESELLSCHAFT

- O AGENTE OFICIAL -

1/3

FIG.1

FIG.2

2/3

FIG.3

FIG.4

3/3

FIG.5