(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-348041

(P2005-348041A)

(43) 公開日 平成17年12月15日(2005.12.15)

(51) Int.CI.<sup>7</sup>

H04N 5/335

F 1

H04N 5/335

テーマコード(参考)

5C024

審査請求 未請求 請求項の数 15 O L (全 15 頁)

(21) 出願番号

特願2004-164636 (P2004-164636)

(22) 出願日

平成16年6月2日 (2004.6.2.)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100065385

弁理士 山下 機平

(74) 代理人 100122921

弁理士 志村 博

(72) 発明者 菊池 伸

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内Fターム(参考) 5C024 GY31 HX01 HX02 HX17 HX28

HX35 HX50

(54) 【発明の名称】 固体撮像装置および撮像システム

## (57) 【要約】

【課題】 画素からの出力の負荷を軽減しゲインの低下、速度の遅延などを抑圧する。

【解決手段】 1次元もしくは2次元に配列され、光電変換された信号を出力する複数の画素1と、一画素又は一列に配列された画素からの出力信号が、それぞれ出力される複数の出力線Pix-out1～Pix-out3と、複数の出力線Pix-out1～Pix-out3からの各出力信号を任意に加算して出力する加算回路2(トランジスタMX1～MX3, コンデンサCA1～CA3)と、複数の出力線Pix-out1～Pix-out3からの各出力信号を非加算で出力する出力回路(トランジスタMX1～MX3)と、を有する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

1次元もしくは2次元に配列され、光電変換された信号を出力する複数の画素と、一画素又は一列に配列された複数の画素からの出力信号がそれぞれ出力される複数の出力線と、前記複数の出力線にそれぞれ接続され、前記画素からの信号を1を超えるゲインで増幅する複数の増幅器と、前記複数の増幅器からの各出力信号を任意に加算して出力する加算回路と、前記複数の増幅器からの各出力信号を非加算で出力する出力回路と、を有する固体撮像装置。

**【請求項 2】**

請求項1に記載の固体撮像装置において、前記加算回路又はノルム及び前記出力回路の後に増幅手段もしくはインピーダンス変換手段を有する固体撮像装置。 10

**【請求項 3】**

請求項1又は2に記載の固体撮像装置において、前記加算回路は、前記複数の出力線に接続される複数のスイッチ手段と、前記複数のスイッチ手段に一方の端子がそれぞれ接続され、他方の端子が共通接続される複数の容量とを備えている固体撮像装置。

**【請求項 4】**

請求項1又は2に記載の固体撮像装置において、前記加算回路は、前記複数の出力線に接続される複数の第1のスイッチ手段と、前記複数の第1のスイッチ手段に接続され、前記複数の出力線に出力された出力信号を蓄積する複数の蓄積容量と、前記複数の蓄積容量と共に接続された複数の第2のスイッチ手段とを有する固体撮像装置。 20

**【請求項 5】**

請求項1又は2に記載の固体撮像装置において、前記加算回路は、前記複数の出力線に接続される複数の第1のスイッチ手段と、前記複数の第1のスイッチ手段に一方の端子がそれぞれ接続され、他方の端子が共通接続される複数の容量と、共通接続された前記他方の端子に接続される複数の第2のスイッチ手段と、前記複数の第2のスイッチ手段に接続され、前記複数の出力線に出力された出力信号を蓄積する複数の蓄積容量と、前記複数の蓄積容量と共に接続された複数の第3のスイッチ手段とを有する固体撮像装置。

**【請求項 6】**

請求項1又は2に記載の固体撮像装置において、前記加算回路は、前記複数の出力線に接続される複数のスイッチ手段と、前記複数のスイッチ手段に一方の端子がそれぞれ接続され、他方の端子が共通接続される複数の容量と、共通接続された他方の端子が入力端子に接続され、出力端子と前記入力端子とが容量を介して接続される演算増幅器とを有する固体撮像装置。 30

**【請求項 7】**

請求項1～6のいずれか1項に記載の固体撮像装置において、前記出力回路は、前記複数の出力線に接続され、同時にオンオフ制御される複数の第4のスイッチ手段を有する固体撮像装置。

**【請求項 8】**

請求項1～7のいずれか1項に記載の固体撮像装置において、各出力線は、前記画素からの信号をクランプすることで前記画素のノイズを除去するための結合容量を介して前記増幅器に接続されることを特徴とする固体撮像装置。 40

**【請求項 9】**

請求項8に記載の固体撮像装置において、前記結合容量を第1の結合容量としたとき、前記増幅器は、帰還型の増幅器であって、前記増幅器の出力端子と入力端子とを容量結合する第2の結合容量と、前記増幅器の出力端子と前記入力端子とを容量結合する第3の結合容量とを有し、前記第1の結合容量と前記第2の結合容量との比により前記第1のモードで読み出すときのゲインを決め、前記第1の結合容量と前記第3の結合容量との比により前記第2のモードで読み出すときのゲインを決めることを特徴とする固体撮像装置。

**【請求項 10】**

請求項1～9のいずれか1項に記載の固体撮像装置において、前記加算回路又はノルム及び前

10

20

30

40

50

記出力回路の出力信号を保持するメモリ部を有することを特徴とする固体撮像装置。

【請求項 1 1】

請求項 1 0 に記載の固体撮像装置において、前記メモリ部は、少なくとも信号蓄積容量、信号を書き込むためのトランジスタ、及び該信号を増幅するためのトランジスタを備えた、前記複数の画素の少なくとも一部に対応した複数の増幅型メモリセルであることを特徴とする固体撮像装置。

【請求項 1 2】

請求項 1 1 に記載の固体撮像装置において、前記メモリ部の増幅型メモリセルの各列ごとに配列され、前記増幅器と前記メモリ部の増幅型メモリセルとの出力オフセット及び前記メモリ部の増幅型メモリセルからの信号を出力するための回路手段を有することを特徴とする固体撮像装置。

10

【請求項 1 3】

請求項 1 2 に記載の固体撮像装置において、前記回路手段は、前記出力オフセットを蓄積する第 1 の蓄積容量と、前記出力オフセットを前記第 1 の蓄積容量に転送する第 1 の転送トランジスタと、前記増幅型メモリセルからの信号を蓄積する第 2 の蓄積容量と、前記増幅型メモリセルからの信号を前記第 2 の蓄積容量に転送する第 2 の転送トランジスタと、を有する固体撮像装置。

【請求項 1 4】

請求項 1 3 に記載の固体撮像装置において、前記回路手段からの、前記出力オフセットと前記信号とを減算する手段を有する固体撮像装置。

20

【請求項 1 5】

請求項 1 ~ 1 4 のいずれか 1 項に記載の固体撮像装置と、前記固体撮像装置へ光を結像する光学系と、前記固体撮像装置からの出力信号を処理する信号処理回路とを有することを特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は 1 次元もしくは 2 次元の画素加算手段を有する固体撮像装置および撮像システムに関する。

30

【背景技術】

【0 0 0 2】

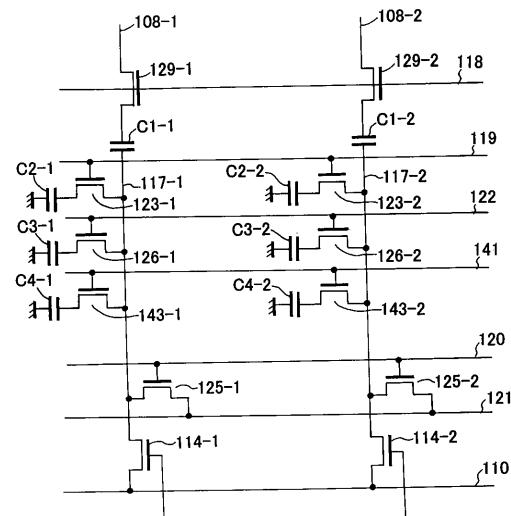

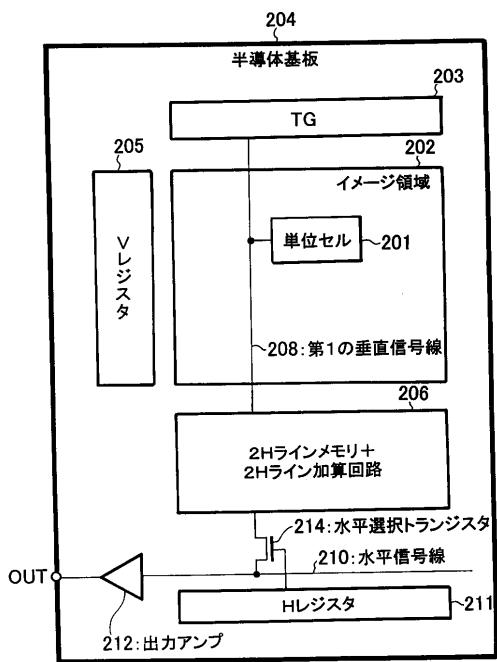

従来、固体撮像装置において、画素信号を加算する手法を開示するものとして、例えば特許文献 1 がある。図 1 4 は従来例であり、( 2 H ラインメモリ + 2 H ライン加算回路 ) 6 により 2 次元の画素の信号を加算することを表している。具体的な加算部分の構成回路は図 1 5 に示され、例えば、画素信号を出力線 8-1, 8-2 に受け MOS スイッチ 23-1, 26-1 を介して容量 C2-1, C3-1 などに画素信号を蓄積した後、MOS スイッチ 23-1, 26-1 を ONさせ、配線 17-1 にて加算(平均)出力を得るものである。

【特許文献 1】特開 2000-106653 号公報

【発明の開示】

【発明が解決しようとする課題】

40

【0 0 0 3】

このように、従来例では画素加算手段の入力部が画素の通常出力(非加算)を行う出力線に共通に接続されている。

【0 0 0 4】

しかしながら、このような共通出力線において、通常出力は加算手段が無い場合と比べて、信号線の負荷が増加し、出力時間の遅延を招くことになる。以下、図 1 4 、図 1 5 の例について説明する。図において通常(非加算)出力は配線 17-1 に出力されるが、その際加算回路の MOS スイッチ 23-1, 23-2, 23-3 があるために、浮遊容量が付加されてしまう。上記の特許文献 1 ではスイッチの数を増やすに従って付加される浮遊容量の値は大きくなり、加算の程度により浮遊容量が大きく影響し信号ゲインの低下、応答速度の低下などが生

50

することができる。

【課題を解決するための手段】

【0005】

本発明の固体撮像装置は、1次元もしくは2次元に配列され、光電変換された信号を出力する複数の画素と、一画素又は一列に配列された複数の画素からの出力信号がそれぞれ出力される複数の出力線と、前記複数の出力線にそれぞれ接続され、前記画素からの信号を1を超えるゲインで増幅する複数の増幅器と、前記複数の増幅器からの各出力信号を任意に加算して出力する加算回路と、前記複数の増幅器からの各出力信号を非加算で出力する出力回路と、を有するものである。

【0006】

本発明においては、画素出力から加算回路、出力回路へ送る経路を独立させることで、画素からの出力の負荷を軽減できゲインの低下、速度の遅延などを抑圧することができる。

【発明の効果】

【0007】

本発明によれば、画素からの出力の負荷を軽減できゲインの低下、速度の遅延などを抑圧することができる。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

(第一実施形態)

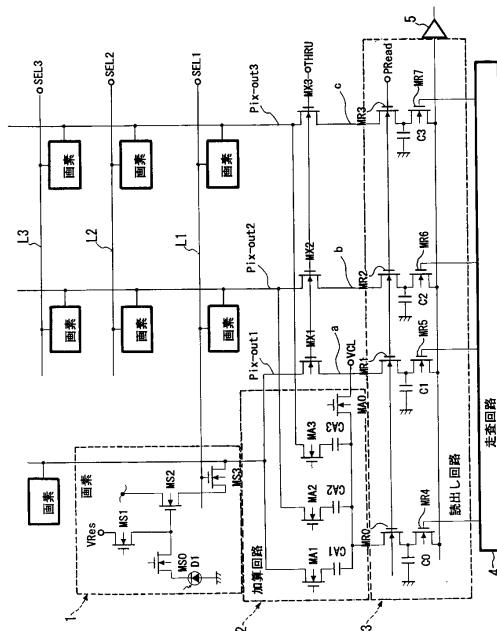

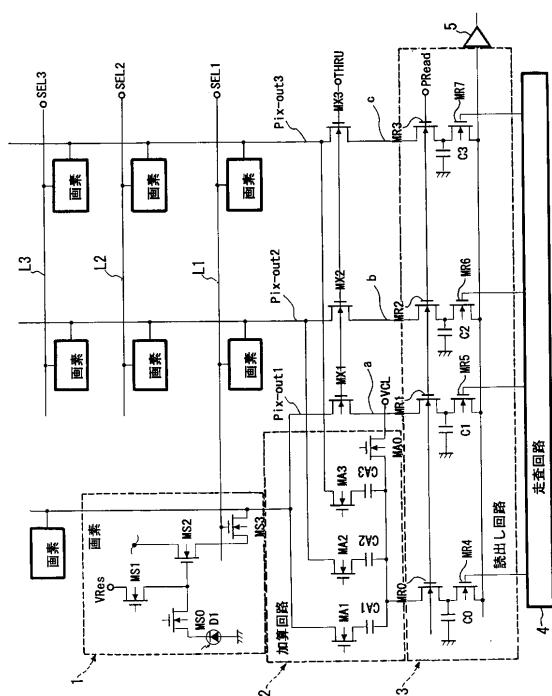

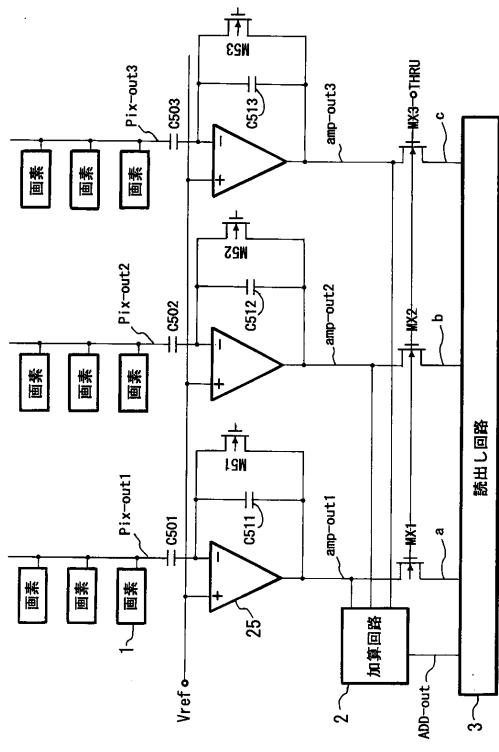

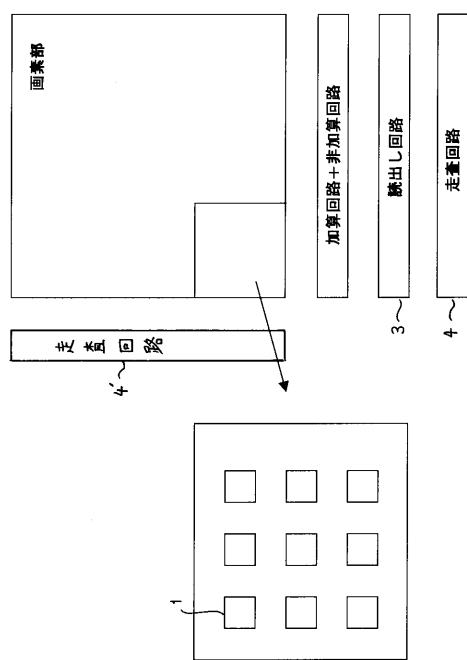

図1は本発明を最もよく表す図であり、第一実施形態の固体撮像装置の一部構成を示す回路図である。図1に示す構成は、図10に示す固体撮像装置の画素部の部分領域(3×3の画素からなる領域)とその部分領域についての加算回路、非加算回路(出力回路)、読み出し回路及び走査回路を示すものである。図10に示す固体撮像装置は、画素が2次元状に配列された複数の画素部、画素部の複数の画素を行ごとに制御する走査回路4'、加算回路及び非加算回路、読み出し回路3、走査回路4、不図示の出力アンプ5から構成される。

なお、本実施形態及び後述する他の実施形態においては画素を2次元状に配列した例について説明しているが、画素を1次元状に配列した場合についても各実施形態の構成(第三の実施形態を除く)を適用することができることは勿論である(1次元に画素を配列する場合は、2次元に画素を配列する場合の一画素行が選択された場合と同様である)。

【0009】

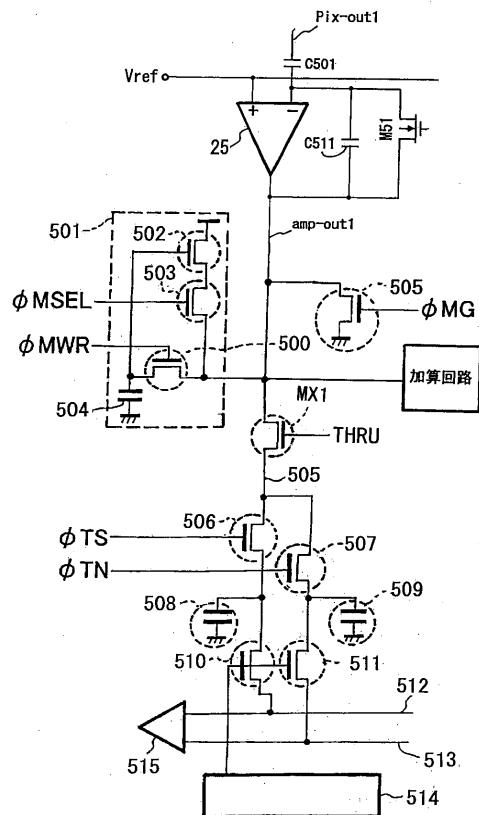

なお、図1においては不図示であるが、図7に示すように、共通出力線Pix-out1, Pix-out2, Pix-out3には、コンデンサC501～C503、コンデンサC501～C503が反転入力端子にそれぞれ接続され、1を超えるゲインの増幅器となるオペアンプ25、オペアンプ25の出力端子と反転入力端子との間に設けられたコンデンサC511～C513、コンデンサC511～C513に並列に接続されたスイッチトランジスタM51～M53が設けられている。オペアンプ25の非反転入力端子(+)には参照電圧(Vref)が印加される。なお、後述する第二実施形態から第四実施形態においても、コンデンサC501～C503、オペアンプ25、コンデンサC511～C513、スイッチトランジスタM51～M53は省略されている。

【0010】

図1において、1は画素であり、画素1はフォトダイオードD1、MOSトランジスタMS0, MS1, MS2, MS3から構成される。MOSトランジスタMS0はフォトダイオードD1より出力トランジスタMS2のゲート部およびその浮遊容量(FD)に電荷を送るためのトランジスタであり、MS1はFD部分をリセットするためのスイッチトランジスタ、MS3は出力トランジスタMS2により得られた信号を所望のタイミングで出力するためのスイッチトランジスタである。水平方向に配列された各画素のスイッチトランジスタMS3のゲートは信号SEL1～SEL3がそれぞれ印加される(不図示の走査回路により順次信号SEL1～SEL3がハイレベルとされる)信号線L1～L3に共通接続され、垂直方向に配列された各画素のスイッチトランジスタ

10

20

30

40

50

MS3のソースは共通出力線Pix-out1, Pix-out2, Pix-out3に共通接続される。すなわち、信号SEL1がハイレベルとなって信号線L1に接続されるスイッチトランジスタMS3がオンされた場合、信号線L1に繋がる画素の出力がスイッチトランジスタMS3を介して共通出力線Pix-out1, Pix-out2, Pix-out3へ出力される。ここで説明した画素はCMOSセンサと呼ばれるものであるが、画素に特にCMOSセンサに限定されず、V M I S (Threshold Voltage Modulation Image Sensor)、B C A S T (Buried Charge Accumulator and Sensing Transistor array)、L B C A S T (Lateral Buried Charge Accumulator and Sensing Transistor array)等も適用可能である。とくにB C A S TやL B C A S Tに対しては増幅用MOSトランジスタをJ F E Tトランジスタに置き換えることで、本質的な変更を伴わずに実現できる。また、光電変換部に蓄積された信号電荷を画素に備わったトランジスタの制御電極に導き、増幅された信号を主電極から出力するタイプのセンサが本実施形態の画素に用いることできる。増幅用トランジスタとしてSITを使ったSIT型イメージセンサ(A. Yusa, J. Nishizawa et al., "SIT image sensor: Design consideration and characteristics," IEEE trans. Vol. ED-33, pp.735-742, June 1986.)、バイポーラトランジスタを使ったBASIS (N.Tanaka et al., "A 310K pixel bipolar imager (BASIS)," IEEE Trans. Electron Devices, vol.35, pp. 646-652, may 1990)、制御電極が空乏化するJFETを使ったCMD(中村ほか“ゲート蓄積型MOSフォトトランジスタイメージセンサ”, テレビ学会誌, 41, 11, pp.1075-1082 Nov. , 1987)などがある。

## 【0011】

共通出力線Pix-out1, Pix-out2, Pix-out3へ出力された画素の出力は、図7に示すように、コンデンサC501～C503を介してオペアンプ25の反転入力端子(-)に接続され、増幅されて出力線amp-out1, amp-out2, amp-out3へ出力され、加算回路とスイッチトランジスタMX1, MX2, MX3に入力される。コンデンサC501とコンデンサC511との容量比、コンデンサC502とコンデンサC512との容量比、コンデンサC503とコンデンサC513との容量比でゲインが決められる。

## 【0012】

また、2は加算回路であり、加算回路2中コンデンサCA1, CA2, CA3は各々共通出力線Pix-out1, Pix-out2, Pix-out3上の画素信号をクランプするためのコンデンサである。クランプコンデンサCA1, CA2, CA3の一方の端子はスイッチトランジスタMA1, MA2, MA3を介して共通出力線Pix-out1, Pix-out2, Pix-out3に接続されており、クランプコンデンサCA1, CA2, CA3の他方の端子は共通接続されて後述する読み出し回路3のスイッチトランジスタMR0に接続されるとともに、スイッチトランジスタMA0を介して不図示の電圧源(電位VCL)に接続される。

## 【0013】

クランプコンデンサCA1, CA2, CA3の他方の端子(共通端)は画素リセット時もしくはFDリセット時にVCLにクランプさせる。その後、画素信号を出力した際に共通端に共通出力線Pix-out1, Pix-out2, Pix-out3の加算(平均)出力が電位VCLを基準として現れる。スイッチトランジスタMA1, MA2, MA3は画素の共通出力線とクランプ回路を分離、結合するためのスイッチである。スイッチトランジスタMA1, MA2, MA3を適宜制御することで、共通出力線Pix-out1, Pix-out2, Pix-out3を選択して加算することもできる。例えばスイッチトランジスタMA1, MA3をオンし、スイッチトランジスタMA2をオフすれば共通出力線Pix-out1, Pix-out3の加算(平均)出力が得られる。

## 【0014】

また、スイッチトランジスタMX1, MX2, MX3は前述の浮遊容量付加の課題を解決するために挿入したスイッチであり(スイッチトランジスタMX1, MX2, MX3は非加算で出力する出力回路(非加算回路)を構成する)、加算回路動作時にはスイッチトランジスタMX1, MX2, MX3をオフし、ノードa, b, cに係わる浮遊容量を排除し、非加算時にはスイッチトランジスタMA1, MA2, MA3をオフし加算回路の影響を排除する。スイッチトランジスタMX1, MX2, MX3とスイッチトランジスタMA1, MA2, MA3とに印加する加算、非加算の切り替え信号はセンサーの内部のタイミングジェネレーターで生成することができ、またカメラシステムやビデオシ

ステムから発生することも可能である。一般的には、カメラシステムまたはビデオシステムよりモード切替信号を通信端子より送信し、センサーを直接或いは、タイミングジェネレーターを介して制御することが好ましい。ゲインの切り替えは例えば、使用者が切り替えスイッチ等で行うことができる。図12に示したスチルカメラを例に取って説明すると、不図示の切り替えスイッチにより全体制御・演算部309にゲイン切り替え指示信号を送り、タイミング発生部308から固体撮像素子（固体撮像装置）のスイッチトランジスタMX1,MX2,MX3とスイッチトランジスタMA1,MA2,MA3とに加算、非加算の切り替え信号を送る。

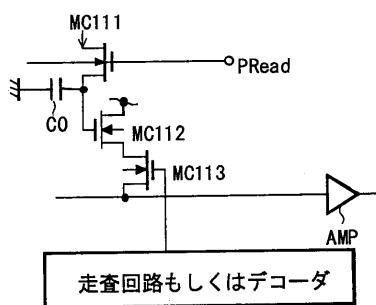

#### 【0015】

3は読み出し回路であり、加算回路2の出力、および、もしくは非加算時の出力をスイッチトランジスタMR0～MR3を介して容量C0,C1,C2,C3にそれぞれ一時格納し、走査回路4の走査順にスイッチトランジスタMR4～MR7が選択され順次出力アンプ5を介して出力される。

10

#### 【0016】

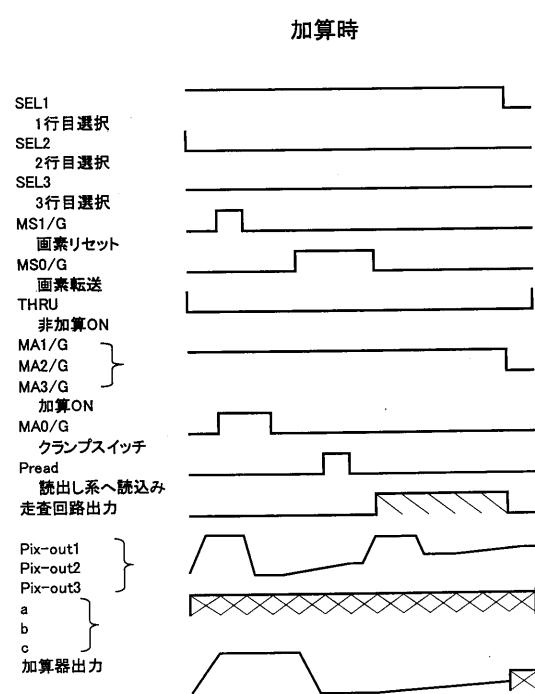

図2は加算回路を有効にした場合の駆動タイミングを示す図である。信号SEL1をハイレベルとして画素の1行目のスイッチトランジスタMS3をオンし、スイッチトランジスタMA1,MA2,MA3をオンした状態で、スイッチトランジスタMS1をオンさせ、画素内のFD（フローティングディフュージョン）部分を画素リセット電位Vresに固定すると同時にクランプ回路をオンし（スイッチトランジスタMA0をオン）、クランプコンデンサCA1,CA2,CA3の共通になっているノード（加算出力）を電位VCLに接続する。これにより、リセット後の各画素出力（固定パターンノイズ）がクランプコンデンサCA1,CA2,CA3に出力され、初期状態（各画素の固定パターンノイズがクランプコンデンサCA1,CA2,CA3に保持された状態）を保持する。次にスイッチトランジスタMS1、スイッチトランジスタMA0をオフした状態で、画素の1行目のトランジスタMS0をオンし、画素内フォトダイオードD1に蓄積された電荷をFDに転送する。その電荷に対応する各画素出力はクランプコンデンサCA1,CA2,CA3の一方の端子に出力され（この時の電位変化は画素出力から固定パターンノイズ分が減算された電位である）、クランプコンデンサCA1,CA2,CA3の他方の共通端子はノイズが除去された各画素からの信号の加算出力が現れる。この加算出力を、信号Preadをハイレベルにすることにより、スイッチトランジスタMR0を介してコンデンサC0へ加算結果を書き込む、その後、走査回路4を図2の斜線の区間走査しコンデンサC0の列のデータを出力アンプ5から読み出す。

20

30

#### 【0017】

この際、加算入力スイッチであるスイッチトランジスタMA1,MA2,MA3はオン、信号THRUはロウレベルでスイッチトランジスタMX1～MX3はオフである。

#### 【0018】

図2、図3において×印で示した期間はスイッチがオフ（OFF）しているために不定となっている状態を表している。

#### 【0019】

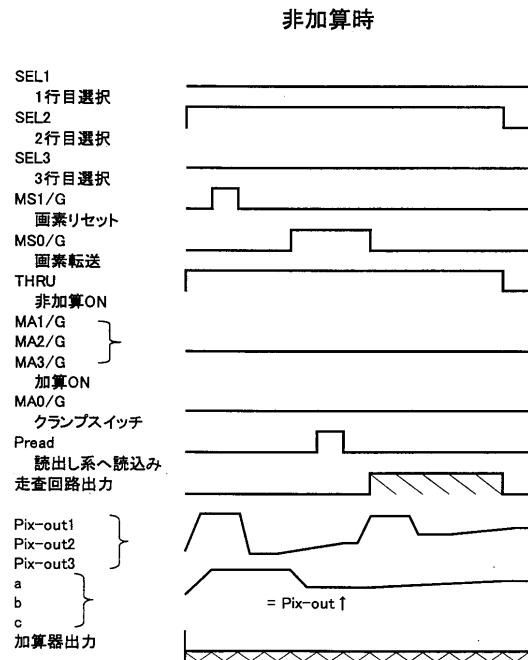

図3は非加算状態のタイミングを示す図である。

#### 【0020】

加算回路が動作しないためスイッチトランジスタMA0はオフ、加算入力スイッチであるスイッチトランジスタMA1,MA2,MA3はオフ、信号THRU端子はハイレベルでスイッチトランジスタMX1～MX3はオンである。図3中画素選択がSEL2になっているが、これは図2とは別の行を選択しているためである。画素の動作のMS1、Preadのタイミングは同一である。

40

#### 【0021】

信号SEL2をハイレベルとして画素の2行目のスイッチトランジスタMS3をオンし、信号THRUをハイレベルとしてスイッチトランジスタMX1,MX2,MX3をオンした状態で、スイッチトランジスタMS1をオンさせ、画素内のFD（フローティングディフュージョン）部分を画素リセット電位Vresに固定する。次にスイッチトランジスタMS1をオフした状態で、画素の2行目のトランジスタMS0をオンし、画素内フォトダイオードD1に蓄積された電荷

50

をFDに転送する。その電荷に対応する各画素出力は信号Preadをハイレベルにより、スイッチトランジスタMR1～MR3を介してコンデンサC1～C3へ書き込まれる、その後、走査回路4を図3の斜線の区間走査しコンデンサC1～C3のデータを出力アンプ5から読み出す。

#### 【0022】

この際、加算入力スイッチであるスイッチトランジスタMA1,MA2,MA3はオフ、信号THRUはハイレベルでスイッチトランジスタMX1～MX3はオンである。

#### (第二実施形態)

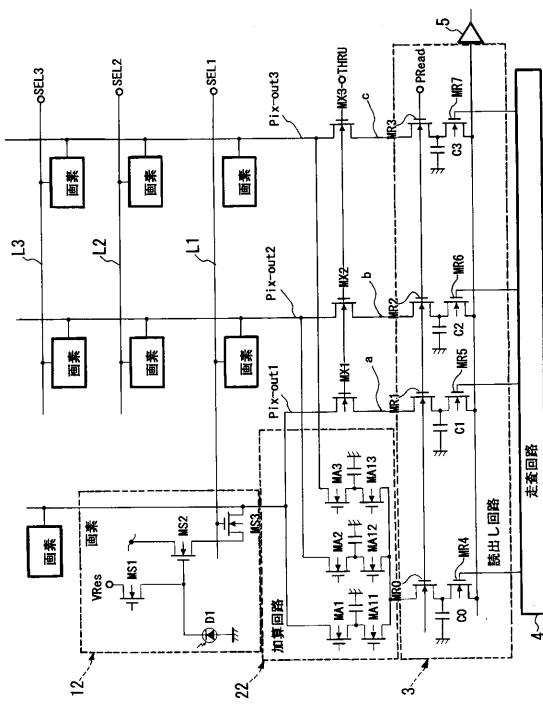

図4は本発明の第二実施形態の固体撮像装置の一部構成を示す回路図である。

#### 【0023】

基本的な構成およびその動作は第一実施形態と同様であるが、画素12が転送を行わないタイプであること、加査回路22が容量分割を用いて加査(平均)化を行っている点が異なる。

#### 【0024】

画素12はフォトダイオードD1、MOSトランジスタMS1,MS2,MS3から構成される。図1の画素1に比べてMOSトランジスタMS0が削除されており、フォトダイオードD1からの信号電荷は出力トランジスタMS2のゲート部およびその浮遊容量(FD)に送られる。

#### 【0025】

加査回路22は、スイッチトランジスタMA1～MA3、スイッチトランジスタMA1～MA3を介して共通出力線Pix-out1, Pix-out2, Pix-out3にそれぞれ接続される3つのコンデンサ、3つのコンデンサにそれぞれ接続され且つスイッチトランジスタMA1～MA3にそれぞれ直列接続されるスイッチトランジスタMA11～MA13から構成され、スイッチトランジスタMA11～MA13をオンすることで3つのコンデンサに保持された信号を加査する。

#### 【0026】

第2の実施形態においても、第1の実施形態と同様に、加査、非加査の分別を行うことで出力線に纏わる浮遊容量を排除、抑圧している。

#### (第三実施形態)

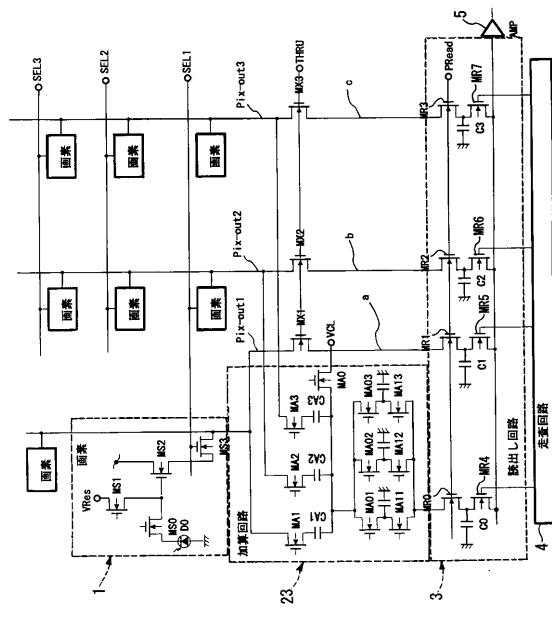

図5は本発明の第三実施形態の固体撮像装置の一部構成を示す回路図である。

#### 【0027】

基本的な構成およびその動作は第1実施形態と同様であるが、加査回路32がクランプした後、容量分割を用いて加査(平均)化を行っている点が異なる。クランプ回路により列(水平)方向加査を行い、サンプルホールドにより、行(垂直)方向加査を行うことができるため、2次元の加査結果を得ることができる。

#### 【0028】

加査回路23において、クランプコンデンサCA1,CA2,CA3の一方の端子はスイッチトランジスタMA1,MA2,MA3を介して共通出力線Pix-out1, Pix-out2, Pix-out3に接続されており、クランプコンデンサCA1,CA2,CA3の他方の端子は共通接続されてスイッチトランジスタMA01～MA03に共通接続される。

#### 【0029】

スイッチトランジスタMA01～MA03は3つのコンデンサにそれぞれ接続され、3つのコンデンサにそれぞれ接続され且つスイッチトランジスタMA01～MA03にそれぞれ直列接続されるスイッチトランジスタMA11～MA13は、読み出し回路3のスイッチトランジスタMR0に接続される。

#### 【0030】

クランプコンデンサCA1,CA2,CA3の他方の共通端子はノイズが除去された各画素からの信号の加査出力が現れる。例えば、第1行目の画素からの信号が共通出力線Pix-out1, Pix-out2, Pix-out3に出力されると、スイッチトランジスタMA1～MA3をオンすることで各画素からのノイズが除去された画素出力が加査され、スイッチトランジスタMA01をオンすることで第1のコンデンサに第1行目の画素の加査出力が保持される。次に第2行目の画素からの信号が共通出力線Pix-out1, Pix-out2, Pix-out3に出力されると、スイッチトラン

10

20

30

40

50

ジスタMA1～MA3をオンすることで各画素からのノイズが除去された画素出力が加算され、スイッチトランジスタMA02をオンすることで第2のコンデンサに第2行目の画素の加算出力が保持される。次に同様にして第3行目の画素からの画素出力がスイッチトランジスタMA03をオンすることでさらに第3のコンデンサに第3行目の画素の加算出力が保持される。スイッチトランジスタMA11～MA13をオンすることで第1～第3のコンデンサに保持された信号を加算する。

#### 【0031】

こうして、第1～第3行、第1～3列の $3 \times 3$ の画素の画素出力を加算して出力することができます。

#### 【0032】

スイッチトランジスタMA1, MA2, MA3, MA01, MA02, MA03, MA11, MA12, MA13を適宜制御することで、任意に垂直方向加算、水平方向加算、斜め方向加算、又はこれらの加算の組み合わせた加算を行うことができる。

#### 【0033】

第3の実施形態においても、画素出力における加算、非加算の分別を行うことで出力線に纏わる浮遊容量を排除、抑圧している。

#### (第四実施形態)

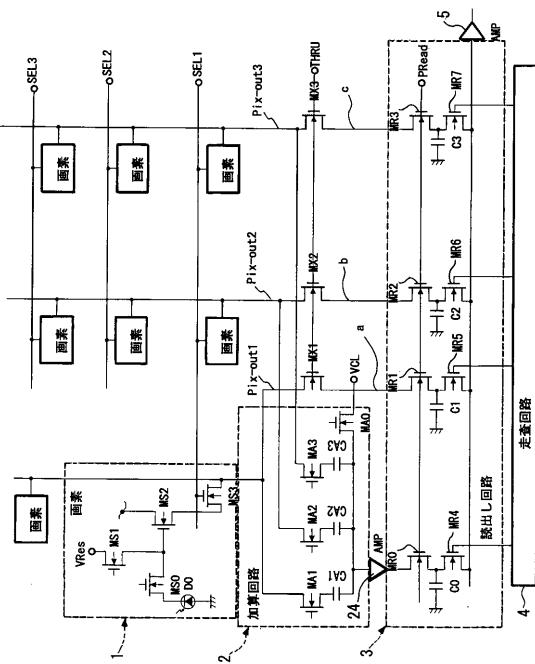

図6は本発明の第四実施形態の固体撮像装置の一部構成を示す回路図である。

#### 【0034】

基本的な構成は第一実施形態と同様であるが、加算回路2の出力をアンプ24にて受けている点が異なる。クランプ回路の出力自体が高いインピーダンスのために駆動能力が乏しく、コンデンサC0へ信号を伝搬すると容量分割になり、出力レベルが低下する。そのため、アンプ24のようなインピーダンス変換手段を用いた。第4の実施形態においても、加算、非加算の分別を行うことで出力線に纏わる浮遊容量を排除、抑圧している。

#### (第五実施形態)

図11は本発明の第六実施形態の固体撮像装置の一部構成を示す回路図である。ここでは簡易化のために、一つのメモリセル、一列分の読み出し手段について示してあるが、実際には画素数に対応してメモリセルは2次元状に配列されてメモリ部を構成し、読み出し手段は各列ごとに設けられている。画素数とメモリセル数は必要に応じて設定され、メモリセル数は画素数よりも少なくてもよい。例えば、複数の画素からの信号を加算或いは間引きしてメモリセルに蓄積させる場合には、メモリセル数は画素数よりも少なくてよい。

#### 【0035】

図11において、オペアンプ25は、その入力端子がクランプコンデンサとしての結合容量となるコンデンサC501に接続され、画素のクランプ信号を増幅する。オペアンプ25は帰還型のアンプであり、その出力は負入力端子(-)にコンデンサC511を介して伝達される。それゆえ、オペアンプ25のゲインはコンデンサC501とコンデンサC511との比で決められる。正入力端子(+)はクランプ電位Vrefに固定されている。負入力端子(-)はパルスCをスイッチトランジスタM51に印加してオンすることにより、クランプ電位Vrefにクランプされるが、これはオペアンプの入力端子がイマジナリショートの状態になっているからである。

#### 【0036】

コンデンサC501のクランプ動作はスイッチトランジスタM51をオンすることで、クランプ電位VrefにコンデンサC501のオペアンプ25の反転入力(-)側を設定した状態で、図1に示す画素の増幅用トランジスタMS2のゲート電極をリセット用トランジスタMS1により所定の電位にリセットし、画素からのノイズをコンデンサC501に入力する。その後スイッチトランジスタM51をオフしてコンデンサC501のオペアンプ25の反転入力側を浮遊状態にして、画素において、フォトダイオードD1から光信号を電荷転送トランジスタMS0を介して増幅用トランジスタMS2のゲート電極に送り、画素から増幅された信号をコンデンサC501に入力する。コンデンサC501の入力側端子の電位変化量は信号からノイズ成分が除去された量となり、画素からノイズが除去された

信号がオペアンプ 25 に入力されることになる。

#### 【0037】

オペアンプ 25 により増幅された信号はメモリセル 501 に書き込まれる。メモリセル 501 は増幅用トランジスタ 502、メモリ選択トランジスタ 503、書き込みトランジスタ 500、そしてメモリセル容量 504 から成っている。電流供給用トランジスタ 505 は増幅用トランジスタ 502 がソースフォロワとして働くように、電流を供給する。本実施形態では増幅型フレームメモリを用いているが、書き込み（読み出しを兼ねる）トランジスタ 500、メモリセル容量 504 から成るDRAM型のメモリを用いてもよい。増幅型メモリを用いることでメモリから蓄積容量への読み出しにおいては、メモリセル 501 の持つ増幅作用のおかげで信号電圧の低下を被ることがない。

10

#### 【0038】

メモリセル 501 からの信号読み出しが、メモリ選択トランジスタ 503、スイッチトランジスタ MX1 をオンさせることで行われる。選択されたメモリセルの出力はパルス TS によりスイッチトランジスタ 506 をオンさせて蓄積容量 508 にサンプリングされる。次に、オペアンプ 25 の反転入力端子と出力端子をスイッチトランジスタ M51 をオンすることで短絡し、オペアンプ 25 のオフセットをメモリセル 501 に書き込む。メモリセルに書き込まれたオフセットの読み出しとサンプリングは、メモリセルに書き込まれた信号の読み出し、サンプリングと同様である。メモリセルからのオフセット出力の蓄積容量 509 へのサンプリングは、パルス TN をスイッチトランジスタ 82 に印加することで行われる。蓄積容量 508 上の電圧は増幅された画素信号とオペアンプ 25 のオフセットとに加え、増幅トランジスタ 502 のオフセットを含んでいる。一方、蓄積容量 509 上の電圧はオペアンプ 25 のオフセットとに加え、増幅トランジスタ 502 のオフセットを含んでいる。

20

#### 【0039】

上記動作に引き続いておこなわれる水平走査は、水平走査回路 514 によって行われる。水平走査回路 514 はスイッチペアであるトランジスタ 510 とトランジスタ 511 を走査し、蓄積容量 510 と 511 上の電圧をそれぞれ、水平出力線 512 および 513 に転送する。差動アンプ 515 はオペアンプ 25 及び増幅トランジスタ 502 のオフセットを除去し、高SN比を持つセンサ信号を出力する。

30

#### 【0040】

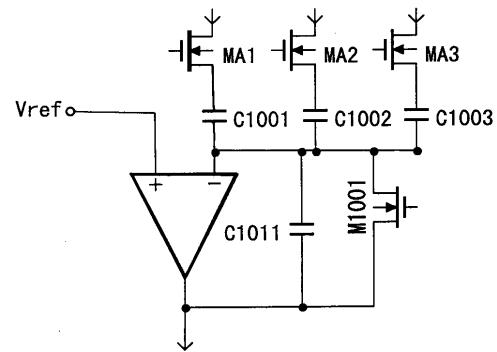

以上説明した各実施形態における加算回路、読み出し回路はあくまでも一例であり、他にオペアンプを用いた加算器（図 8）、ソースフォロワーを用いた読み出し系（図 9）などを用いても本発明の効果を実現することができることは言うまでも無い。図 8 において、スイッチトランジスタ MA1～MA3 はコンデンサ C1001～C1003 を介してオペアンプの反転入力端子に共通接続される。C1011 はオペアンプの出力端子と反転入力端子との間に設けられたコンデンサ、M1001 はコンデンサ C1011 に並列に接続されたスイッチトランジスタである。オペアンプの非反転入力端子には参照電圧（Vref）が印加される。図 9 において、ソースフォロワーは MOSトランジスタ MC112 と MC113 とで構成される。

#### 【0041】

各本実施形態において、固体撮像装置は同一半導体基板上に設けることができるが、差動増幅器 515 により生ずるノイズが他の回路部材に影響しないように差動増幅器 515 を基板外に設けてもよい。

40

また各本実施形態においては、一本の垂直出力線に着目すると二つに MOSトランジスタ MA1, MX1 が接続するだけですみ、出力の負荷（浮遊容量）を減少させることができる。

#### 【0042】

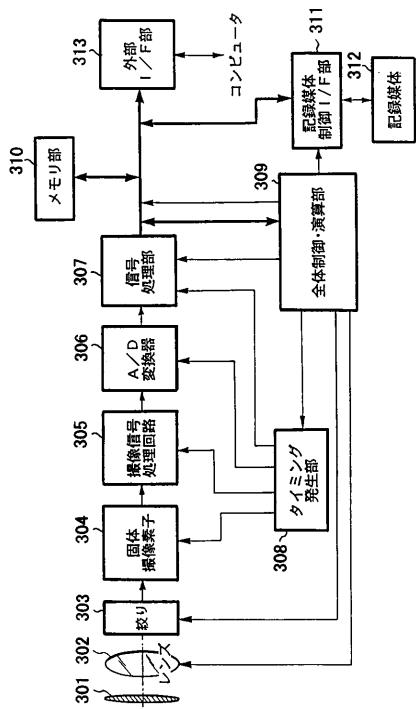

図 12 に基づいて、本発明に係わる固体撮像装置を動画対応のスチルカメラに適用した場合（撮像システム）の一実施形態について詳述する。

#### 【0043】

図 12 は、本発明に係わる固体撮像装置を動画対応の「スチルビデオカメラ」に適用した場合を示すブロック図である。

50

## 【0044】

図12において、301はレンズのプロテクトとメインスイッチを兼ねるバリア、302は被写体の光学像を固体撮像素子（固体撮像装置）304に結像させるレンズ、303はレンズ302を通った光量を可変するための絞り、304はレンズ302で結像された被写体を画像信号として取り込むための固体撮像素子、306は固体撮像素子304より出力される画像信号のアナログ・デジタル変換を行うA/D変換器、307はA/D変換器306より出力された画像データに各種の補正を行ったりデータを圧縮する信号処理部、308は撮像素子304、撮像信号処理回路305、A/D変換器306、信号処理部307に、各種タイミング信号を出力するタイミング発生部、309は各種演算とスチルビデオカメラ全体を制御する全体制御・演算部、310は画像データを一時的に記憶する為のメモリ部、311は記録媒体に記録または読み出しを行うためのインターフェース部、312は画像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体、313は外部コンピュータ等と通信する為のインターフェース部である。

10

## 【0045】

次に、前述の構成における撮影時のスチルビデオカメラの動作について説明する。

## 【0046】

バリア301がオープンされるとメイン電源がオンされ、次にコントロール系の電源がオンし、更にA/D変換器306などの撮像系回路の電源がオンされる。

## 【0047】

それから、露光量を制御する為に、全体制御・演算部309は絞り303を開閉にし、撮像素子304から出力された信号はA/D変換器306で変換された後、信号処理部307に入力される。そのデータを基に露出の演算を全体制御・演算部309で行う。

20

## 【0048】

この測光を行った結果により明るさを判断し、その結果に応じて全体制御・演算部309は絞りを制御する。

## 【0049】

次に、撮像素子304から出力された信号をもとに、高周波成分を取り出し被写体までの距離の演算を全体制御・演算部309で行う。その後、レンズを駆動して合焦か否かを判断し、合焦していないと判断した時は、再びレンズを駆動し測距を行う。そして、合焦が確認された後に本露光が始まる。

30

## 【0050】

露光が終了すると、撮像素子304から出力された画像信号はA/D変換器306でA/D変換され、信号処理部307を通り全体制御・演算部309によりメモリ部310に書き込まれる。

## 【0051】

その後、メモリ部310に蓄積されたデータは、全体制御・演算部309の制御により記録媒体制御I/F部311を通り半導体メモリ等の着脱可能な記録媒体312に記録される。

## 【0052】

また、外部I/F部313を通り直接コンピュータ等に入力して画像の加工を行ってよい。

40

## 【0053】

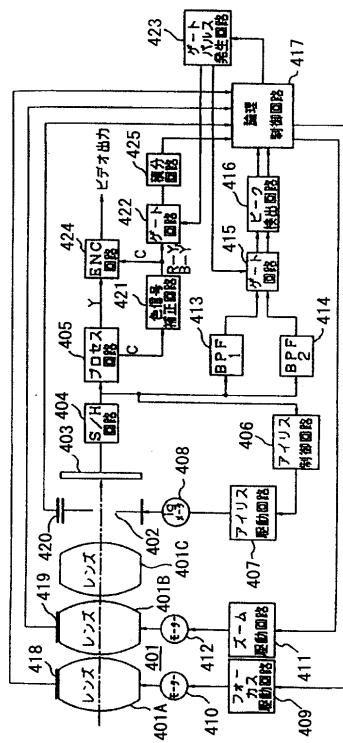

また図13に基づいて、本発明の固体撮像装置をビデオカメラに適用した場合（撮像システム）の例について詳述する。

## 【0054】

図13は、本発明の固体撮像装置をビデオカメラに適用した場合を示すブロック図で、401は撮影レンズで焦点調節を行うためのフォーカスレンズ401A、ズーム動作を行うズームレンズ401B、結像用のレンズ401Cを備えている。

## 【0055】

402は絞り、403は撮像面に結像された被写体像を光電変換して電気的な撮像信号

50

に変換する固体撮像素子（固体撮像装置）、404は固体撮像素子403より出力された撮像信号をサンプルホールドし、さらに、レベルをアンプするサンプルホールド回路（S/H回路）であり、映像信号を出力する。

#### 【0056】

405はサンプルホールド回路404から出力された映像信号にガンマ補正、色分離、ブランкиング処理等の所定の処理を施すプロセス回路で、輝度信号Yおよびクロマ信号Cを出力する。プロセス回路405から出力されたクロマ信号Cは、色信号補正回路421で、ホワイトバランス及び色バランスの補正がなされ、色差信号R-Y, B-Yとして出力される。

#### 【0057】

また、プロセス回路405から出力された輝度信号Yと、色信号補正回路421から出力された色差信号R-Y, B-Yは、エンコーダ回路（ENC回路）424で変調され、標準テレビジョン信号として出力される。そして、図示しないビデオレコーダ、あるいは電子ビューファインダ等のモニタEVFへと供給される。

#### 【0058】

次いで、406はアイリス制御回路で有り、サンプルホールド回路404から供給される映像信号に基づいてアイリス駆動回路407を制御し、映像信号のレベルが所定レベルの一定値となるように、絞り402の開口量を制御すべくメータを自動制御するものである。413, 414は、サンプルホールド回路404から出力された映像信号中より合焦検出を行うために必要な高周波成分を抽出する異なった帯域制限のバンドパスフィルタ（BPF）である。第一のバンドパスフィルタ413（BPF1）、及び第二のバンドパスフィルタ414（BPF2）から出力された信号は、ゲート回路415及びフォーカスゲート枠信号で各自でゲートされ、ピーク検出回路416でピーク値が検出されてホールドされると共に、論理制御回路417に入力される。

#### 【0059】

この信号を焦点電圧と呼び、この焦点電圧によってフォーカスを合わせている。

#### 【0060】

また、418はフォーカスレンズ401Aの移動位置を検出するフォーカスエンコーダ、419はズームレンズ401Bの焦点距離を検出するズームエンコーダ、420は絞り402の開口量を検出するアイリスエンコーダである。これらのエンコーダの検出値は、システムコントロールを行う論理制御回路417へと供給される。論理制御回路417は、設定された合焦検出領域内に相当する映像信号に基づいて、被写体に対する合焦検出を行い焦点調節を行う。即ち、各自のバンドパスフィルタ413、414より供給された高周波成分のピーク値情報を取り込み、高周波成分のピーク値が最大となる位置へとフォーカスレンズ401Aを駆動すべくフォーカス駆動回路409にフォーカスモータ410の回転方向、回転速度、回転／停止等の制御信号を供給し、これを制御する。

#### 【産業上の利用可能性】

#### 【0061】

本発明は、1次元もしくは2次元の画素加算手段を有する固体撮像装置に適用され、動画対応のデジタルカメラ（スチルカメラ）、デジタルビデオカメラ等に好適に用いられるものである。

#### 【図面の簡単な説明】

#### 【0062】

【図1】本発明の第一実施形態の固体撮像装置の一部構成を示す回路図である。

【図2】加算回路を有効にした場合の駆動タイミングを示す図である。

【図3】非加算状態のタイミングを示す図である。

【図4】本発明の第二実施形態の固体撮像装置の一部構成を示す回路図である。

【図5】本発明の第三実施形態の固体撮像装置の一部構成を示す回路図である。

【図6】本発明の第四実施形態の固体撮像装置の一部構成を示す回路図である。

【図7】本発明の第五実施形態の固体撮像装置の一部構成を示す回路図である。

【図8】オペアンプを用いた加算器を示す図である。

【図9】ソースフォロワーを用いた読み出し回路を示す図である。

【図10】本発明の第一実施形態の固体撮像装置の構成を示すブロック図である。

【図11】本発明の第六実施形態の固体撮像装置の一部構成を示す回路図である。

【図12】本発明に係わる固体撮像装置を「スチルビデオカメラ」に適用した場合を示すブロック図である。

【図13】本発明に係わる固体撮像装置をビデオカメラに適用した場合を示すブロック図である。

【図14】従来の固体撮像装置の構成を示すブロック図である。

【図15】従来の固体撮像装置の加算部の構成を示す回路図である。

10

### 【符号の説明】

#### 【0063】

- 1 画素

- 2, 22, 23 加算回路

- 3 読出し回路

- 4 走査回路

- 5 出力アンプ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】