(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4987696号

(P4987696)

(45) 発行日 平成24年7月25日(2012.7.25)

(24) 登録日 平成24年5月11日(2012.5.11)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/76  | (2006.01) | HO1L 21/76 | L    |

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 621  |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 301R |

| HO1L 29/78  | (2006.01) | HO1L 27/08 | 331A |

| HO1L 27/08  | (2006.01) | HO1L 27/08 | 321C |

請求項の数 4 (全 10 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-510752 (P2007-510752)  |

| (86) (22) 出願日 | 平成17年4月5日 (2005.4.5)          |

| (65) 公表番号     | 特表2007-535815 (P2007-535815A) |

| (43) 公表日      | 平成19年12月6日 (2007.12.6)        |

| (86) 國際出願番号   | PCT/US2005/011553             |

| (87) 國際公開番号   | W02005/112124                 |

| (87) 國際公開日    | 平成17年11月24日 (2005.11.24)      |

| 審査請求日         | 平成20年4月7日 (2008.4.7)          |

| (31) 優先権主張番号  | 10/836,150                    |

| (32) 優先日      | 平成16年4月30日 (2004.4.30)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100116322<br>弁理士 桑垣 衡                                                                                      |

| (72) 発明者  | イーブ、ショーフェイ<br>アメリカ合衆国 78749 テキサス州<br>オースティン テルライド トレイル<br>6806                                             |

最終頁に続く

(54) 【発明の名称】 分離トレンチ

## (57) 【特許請求の範囲】

## 【請求項 1】

分離トレンチを半導体構造に形成するための方法であって、

半導体材料のウェハを設ける工程と、

半導体材料の側壁を備えるトレンチを前記半導体材料の中に形成する工程と、

第1誘電体材料を前記トレンチの底面部分を覆うように、トレンチ上端から第1の深さまで堆積させ、かつ、前記第1誘電体材料が前記第1の深さよりも上の領域の側壁には堆積しないようにする、堆積工程と、

前記第1誘電体材料とは異なる第2誘電体材料を前記トレンチ内の前記第1誘電体材料を覆うように、前記トレンチ上端から第2の深さまで堆積させて、前記第2誘電体材料が前記第2の深さよりも上の領域の側壁には堆積しないようにし、かつ前記第1誘電体材料は第1膜厚を有し、及び前記第2誘電体材料は前記第1膜厚よりも薄い第2膜厚を有することとする、堆積工程と、

トレンチ側壁ライナーがトレンチ内部の第2誘電体材料の高さよりも低い位置に形成されるのを防止するように第2誘電体材料を機能させて、トレンチ側壁ライナーを前記トレンチ内部の前記半導体材料の一部分の上に高温酸化プロセスによって形成する、トレンチ側壁ライナーの形成工程と、

誘電体から成るトレンチ充填材料を前記トレンチ内の前記第2誘電体材料を覆うように堆積させる工程とを備え、

前記誘電体から成るトレンチ充填材料は、前記第2誘電体材料をエッチングしないよう

10

20

に選択的にエッティングすることができる、方法。

【請求項 2】

前記ウェハは、半導体が絶縁膜の上に配置されるセミコンダクタオニンシュレータ（S O I）構造を有する、請求項 1 記載の方法。

【請求項 3】

半導体材料が絶縁膜を覆い、

前記トレンチが前記半導体材料を下に向かって貫通して延びて前記絶縁膜に達する、請求項 1 記載の方法。

【請求項 4】

前記第 1 誘電体材料は酸化物を含む、請求項 1 記載の方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は概して半導体構造に関し、特に半導体構造の分離トレンチに関する。

【背景技術】

【0002】

分離トレンチは集積回路の活性領域を絶縁するために使用される。例えば、分離トレンチを使用して、分離トレンチが下地の絶縁物にまで延びる構造のセミコンダクタオニンシュレータ（semiconductor on insulator（S O I））ウェハの活性領域を絶縁する。このような構造の場合、トレンチを絶縁物に達するように掘り下げ、そして活性層のシリコン側壁を酸化してトレンチのコーナー部に丸みを付ける。その後、トレンチに誘電体材料を充填する。一つの問題は、シリコンを酸化することができる後続の加熱プロセスによって、酸化膜のバーズピークが活性層の底面の下でトレンチ底部から延びる恐れがあることである。

20

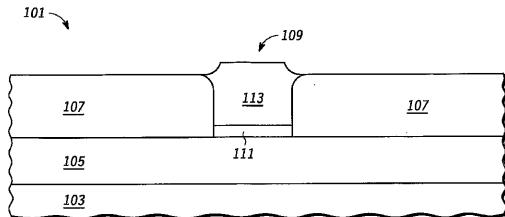

【0003】

図 1 は先行技術によるウェハの部分断面を示している。ウェハ 101 は、絶縁膜 105 の上に位置する活性シリコン層 107 を含む S O I 構造を有し、この絶縁膜は半導体基板 103 の上に位置する。分離トレンチ 109 の底面に位置するのは、窒化シリコンから成る「保護」層 111 である。次に、酸化膜 113 がトレンチ 109 の層 111 の上に形成される。層 111 は、後続の加熱プロセスの間に、酸化膜のバーズピークがトレンチ 109 の底面に位置する 107 層に食い込む形で形成される現象を防止するように機能する。

30

【0004】

図 1 の構造に関する一つの問題は、後続の酸化膜エッティングの間に、トレンチ充填材料 113 がトレンチから所望の深さを超えて除去される恐れがあることである。このような状態は、例えばポリシリコン片に起因する短絡を、後の工程で形成され、かつトレンチによって絶縁される活性領域に位置する複数のゲートの間に生じさせる恐れがある。また、トレンチ充填物の除去が深さ方向にばらつくとドランジスタの動作がばらつくが、これはトランジスタチャネル実効幅がゲートからチャネルに向かって（トレンチの深さ方向に）延びるからである。

【0005】

40

層 111 を厚くしてトレンチ 109 内の酸化物 113 の深さを減らすことができる。しかしながら、窒化膜層 111 の厚さを増やす処理は、例えば層 111 の材料を堆積させている間に、窒化物がトレンチの上に「パンをスライスしたような構造に形成される（bread loafing）」ので製造プロセス上、実行することができない。窒化膜層 111 の厚さを増やす処理に関連して生じる別の問題は、窒化膜の誘電率が高いので、層 107 から成る複数の活性領域の間の寄生容量が、窒化膜の高誘電率に起因して大きくなる恐れがあることである。

【0006】

必要なのは、分離トレンチの構造を改善することである。

【発明を実施するための最良の形態】

50

**【0007】**

添付の図を参照することにより本発明を一層深く理解することができ、そして本発明の多くの目的、特徴、及び利点をこの技術分野の当業者に対して明らかにすることができます。

**【0008】**

特に断らない限り、同じ参照符号を異なる図に使用して同じ構成要素を指すようにしている。これらの図は必ずしも寸法通りには描かれていない。

次に、本発明を実施する或るモードに関する詳細な記述を示す。この記述は、本発明を例示するために為されるのであり、本発明を制限するために為されるものとして捉えられるべきではない。

10

**【0009】**

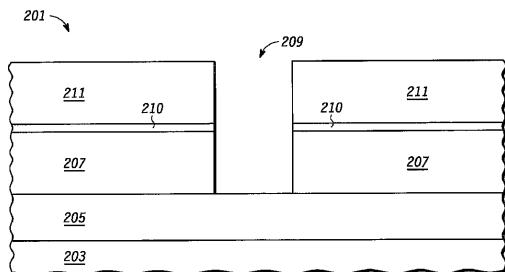

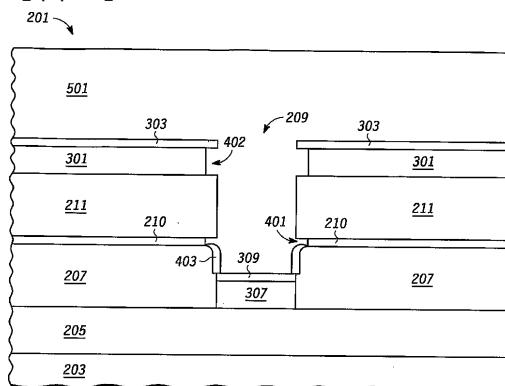

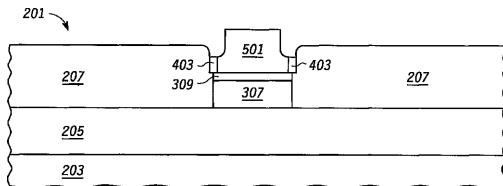

図2～10は、分離トレンチを本発明に従って形成するプロセスの間の種々の工程におけるウェハの部分側断面図を示している。

図2はウェハ201の部分側断面図である。図示の実施形態では、ウェハ201はSOI構造を有し、この構造では、絶縁膜205（例えば150nmの厚さ）が基板203の上に位置し、そして活性材料層207が絶縁膜205の上に位置する。一の実施形態では、絶縁膜205は、例えば酸化シリコンにより形成され、そして基板203はシリコンにより形成される。別の実施形態では、ウェハ201はSOI構造以外の構造（例えば、バルクシリコンウェハ）を含む他の構造、または他のSOI構造を有することができる。

**【0010】**

20

或る実施形態では、層207は70～200nmの厚さであり、かつシリコンにより形成される。別の実施形態では、層207は別の膜厚を有することができ、かつ別の半導体材料（例えば、シリコンゲルマニウム、砒化ガリウム）により形成することができる。更に、別の実施形態では、層207は異なる材料から成る複数の層（例えば、シリコンゲルマニウム層の上にシリコン層を有する構成）により形成することができる。

**【0011】**

図示の実施形態では、ウェハ201は、層207上に位置する熱酸化膜保護層210、及び層210上に位置する反射防止コーティング（ARC）層211を含む。一の実施形態では、層211は窒化膜（例えば、化学量論的組成の窒化シリコン）により形成される。保護層210（例えば、5～20nmの厚さ）は層207を、層211に対する後続のエッティングの間に渡って保護する。保護層210は別の実施形態では別の材料により形成することができる。

30

**【0012】**

層211を形成した後、トレンチ209はウェハ201に、例えばパターニングを行なうことによって形成される。図示の実施形態では、トレンチ209は絶縁膜205にまで延びる。他のトレンチ（図示せず）はウェハ201の他の位置に形成される。

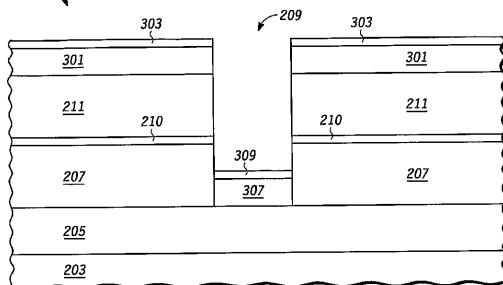

**【0013】**

図3は、酸化膜層301をウェハ201上に堆積させた後のウェハ201の部分側断面図である。層301を堆積させている間、層301の一部分をARC層211の上に堆積させ、かつ層301の別の部分307を絶縁膜205上のトレンチ209の内部に堆積させる。一の実施形態では、層301は層207の膜厚の約半分の膜厚を有するが、別の実施形態では別の厚さに形成することができる。或る実施形態では、層301は酸化膜（例えば、炭素含有酸化膜、フッ素添加酸化膜、多孔質酸化膜、TEOS、または他のタイプの酸化膜）である。別の実施形態では、層301は他のタイプの材料、例えば他のタイプの低K誘電体材料により形成することができる。

40

**【0014】**

一の実施形態では、層301は、異方性堆積法により堆積させる。或る異方性堆積法では、材料は制御方向（例えば、ウェハ表面の法線方向）から堆積する。異方性堆積法の場合、材料はほとんどが、制御方向に向いた表面（例えば、トレンチの底面及び層211の上部表面）の上にのみ堆積する。図示の実施形態では、異方性堆積法の場合、層301の

50

材料が堆積するとしても、トレンチ 209 の側壁にはほとんど堆積しない。一の実施形態では、層 301 は、分布に偏りの無い均一性の高いプラズマを生成し、かつ異方性堆積法である高密度プラズマ支援化学気相成長 (CVD) プロセスによって堆積する。一の実施形態では、層 301 は、スパッタリング (例えば、RFスパッタリング、コリメートスパッタリング、マグネットロンスパッタリング、または蒸着スパッタリング)、プラズマ気相成長 (PVD) プロセス、コリメートスパッタ法による PVD プロセス、熱 CVD プロセス、または高密度プラズマ (HDP) プロセスのような他の異方性堆積法を含む他のプロセスによって堆積させることができる。

#### 【0015】

異方性堆積法を使用することにより、トレンチの側壁への材料の堆積を最小化することができる。従って、或る実施形態では、トレンチ内の材料は、同様の材料が通過することができる大きな経路が決して、トレンチの頂部からトレンチの底面の間に形成されることがないということからすると、後続のエッティング処理及びクリーニング処理から保護することができる。

#### 【0016】

或る実施形態では、側壁に堆積する材料は、他の材料を後の工程でウェハ 201 に堆積させる前に除去することができる。

その後、層 303 を層 301 の上に堆積させる。層 303 の一部分 309 はトレンチ 209 内に堆積する。一の実施形態では、層 303 は窒化膜 (例えば、窒化シリコン) により形成され、かつ 10 nm の膜厚を有する。別の実施形態では、層 303 は、酸化膜をエッティングしないように選択的にエッティングすることができる、または後の工程で堆積するトレンチ充填材料 (例えば、層 501) をエッティングしないように選択的にエッティングすることができる他の誘電体材料により形成することができる。或る実施形態では、層 303 はプラズマ支援 CVD 窒化膜、低圧 CVD 窒化膜、ビスター・シャルプチルアミノシラン (BTBAS)、シリコンリッチ窒化膜、炭化シリコン (SiC)、または炭窒化シリコン (SiCN) により形成することができる。一の実施形態では、層 303 は、分布に偏りの無い均一性の高いプラズマを利用する高密度プラズマ支援化学気相成長 (CVD) プロセスによって堆積させるが、別の実施形態では、他の異方性堆積法を含む他の堆積プロセスによって堆積させることができる。別の実施形態では、層 303 は異なる膜厚を有することができる。一の実施形態では、層 303 は、後続のエッティング処理及びクリーニング処理の間に部分 307 を保護するように十分に厚い。或る実施形態では、層 303 の材料は堆積するとしても、トレンチ 209 の側壁にはほとんど堆積することができない。或る実施形態では、側壁に堆積する層 303 の材料は、材料を後の工程でウェハ 201 に堆積させる前に除去することができる。

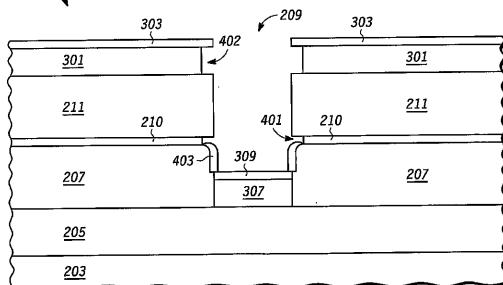

#### 【0017】

図 4 によれば、層 210 の側壁 (だけでなく層 301 の側壁も) を、酸化膜をエッティングするように酸化膜に対して選択性を示すエッチャント (例えば、HF) を用いてエッティングして層 210 に凹部 401 (そして、層 301 に凹部 402) を形成する。層 210 をエッティングすることにより、トレンチ 209 内の上部エッジ部分を露出させ、そして層 207 の上部コーナー部に丸みを付ける。続いて、ライナー 403 をトレンチ 209 内の層 207 の露出側壁の上に、例えば高温酸化プロセスによって形成する。高温酸化プロセスは、トレンチ 209 内の層 207 の露出上部コーナー部に更に丸みを付けるように作用する。丸みの付いたコーナー部は、動作中のリーク電流を減らし、かつ回路信頼性を高めるように機能することができる。部分 309 は、酸化膜のバーズピークがトレンチ 209 の底面に位置する層 207 に食い込んで形成される現象を防止するように機能する。

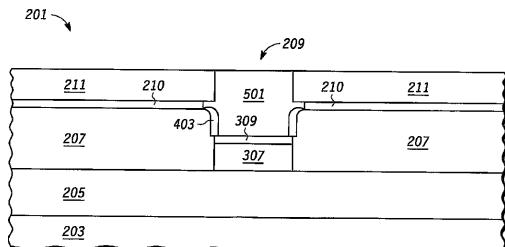

#### 【0018】

図 5 によれば、層 207 の上部コーナー部に丸みを付けた後、トレンチの内壁に忠実に沿った構造とはならないトレンチ充填材料から成る層 501 を、トレンチ 209 内部を含むウェハ 201 を覆うように堆積させる。一の実施形態では、層 501 は酸化膜 (例えば酸化シリコン) のような誘電体により形成される。一の実施形態では、層 501 は、分布

10

20

30

40

50

に偏りの無い均一性の高い高密度プラズマを使用して堆積させるが、別の実施形態では他の方法を使用して堆積させることができる。層 501 の材料は、層 303 の材料をエッチングしないように選択的にエッチングすることができる。

#### 【0019】

図 6 は、ウェハに化学的機械研磨 (C M P) プロセスを実施した後のウェハ 201 を示している。図示の実施形態では、ARC 層 211 を C M P プロセスにおける研磨停止層として使用する。図示の実施形態では、ウェハ 201 を、ARC 層 211 の膜厚の約半分が除去される位置まで研磨するが、別の実施形態では、別の位置まで研磨することができる。別の実施形態では、ウェハ 201 に対してエッチバックプロセス (例えば、化学エッチング) を行なうことができ、この場合、ARC 層 211 がエッチング停止層として使用される。その結果、トレンチ 209 内の層 501 の一部分のみが残る。10

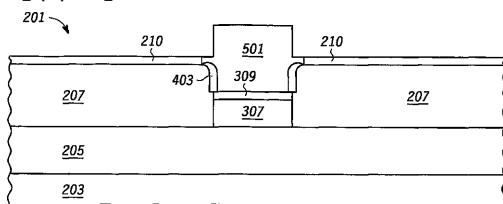

#### 【0020】

図 7 によれば、層 211 の残りの部分は、層 501 及び層 210 の酸化膜に対して、これらの層がエッチング後に残るような選択性を示すエッチャント (例えば、磷酸 H<sub>3</sub>PO<sub>4</sub> エッチャント) により除去される。部分 309 は、エッチングされることがないように層 501 の残りの部分、及びライナー 403 によって保護される。

#### 【0021】

図 8 によれば、例えばクリーニング及びエッチングのような後続のプロセスでは、層 501 の一部分、ライナー 403 の一部分、及び層 210 を除去する。或る実施形態では、層 501 及びライナー 403 の全てを後続のプロセスにおいて除去することができる。部分 309 は、層 501 の酸化膜をエッチングすることがないように選択的にエッチングすることができるので、部分 309 は後続のプロセスにおいてはエッチングされない。従って、後続のプロセスに起因して除去されるトレンチ材料の最大深さを小さくすることができるので、或る実施形態では、後続のプロセスにおける自由度を高くすることができる。従って、或る実施形態では、除去されるトレンチ充填材料の最大深さを小さくする機能を実現することによって、例えばポリシリコン片に起因する短絡の確率を低くすることができる。20

#### 【0022】

更に、トレンチの大部分が低 K 誘電体 (例えば、酸化膜) により形成されるので、トレンチに起因する寄生容量は、窒化物の量が少ないために小さくすることができる。30

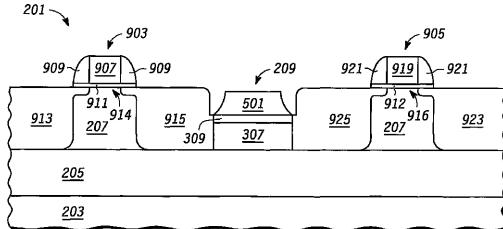

図 9 は、トランジスタ 903 及び 905 を形成した後のウェハ 201 の図である。トランジスタ 903 はゲート酸化膜 911 上に位置するゲート 907 (例えば、ポリシリコンまたは金属から成る) 及びスペーサ 909 を含む。トランジスタ 905 はゲート酸化膜 912 上のゲート 919 及びスペーサ 921 を含む。ソース / ドレイン領域 913, 915, 925, 及び 923 は層 207 に、これらの領域に選択ドーピングを行なうことにより形成される。トランジスタ 903 及び 905 はそれぞれ、該当するトランジスタのゲートの下方の層 207 にそれぞれ位置するチャネル領域 914 及び 916 を含む。ソース / ドレイン領域 925 はソース / ドレイン領域 915 から、トレンチ内の部分 309 及び 307 の誘電体材料によって電気的に絶縁される。図示の実施形態では、層 501 の残りの部分の一部分、及びライナー 403 は (図 8 の工程以降の工程に示すように)、図 9 に示す工程の前のウェハ 201 に実施されるプロセスの間に除去される。別の実施形態では、トレンチ 209 は、他の材料 (例えば、ILD (層間絶縁膜) の誘電体材料) を形成することにより再度充填することができる。40

#### 【0023】

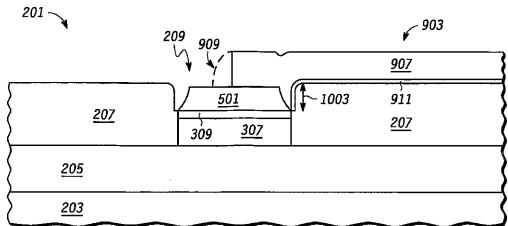

図 10 は、図 9 の図を 90 度だけ回転させたウェハ 201 の部分側断面図を示している。図 10 の図の場合、スペーサ 909 は、トレンチ 209 の中まで延在する部分以外は示されず、延在する部分を破線で示している。図示の実施形態では、ゲート 907 及びゲート酸化膜 911 はトレンチ 209 の中にまで延在する。この実施形態の場合、トレンチの側壁の一部分はトランジスタ 903 のチャネル領域の一部分として機能し、この部分は、トランジスタの実効チャネル幅を広くする (例えば、矢印 1003 によって示す長さだけ50

)。部分 309 が存在するので、トレンチ充填材料（層 501 の材料）が除去される深さを制御することができる。従って、ゲート 907 がトレンチの中にまで延在する距離、従ってトランジスタの実効チャネル幅を、ゲート材料堆積の前に実施されるエッティングプロセス及びクリーニングプロセスに関係なく制御することができる。従って、トランジスタ 903 を使用する回路の動作性能を予測することができ、かつこの動作性能は設計仕様に一層近いものとなる。また、或る実施形態では、ここに記載するトレンチが形成される複数の素子の電圧ミスマッチを小さくすることができ、かつ機械的応力に起因するこれらの素子のトランジスタばらつきを小さくすることができる。このような特性によって、或る実施形態では、メモリ回路及びロジック回路における最小動作電圧を低くすることができる。或る実施形態では、層 501 の全てをトレンチ 209 から、ゲート材料をウェハ 201 に堆積させる時点の前に除去することができる。

#### 【0024】

或る実施形態では、層 301, 303, 及び 501 の材料、これらの層の膜厚、及びこれらの層を形成するためのプロセスを調整して、トレンチに隣接する活性領域に位置するトランジスタ（例えば、903 及び 905）のチャネル領域の歪みを制御することができる。例えば、層 303 をプラズマ支援 CVD プロセスによって堆積させる場合、層 303 はわずかな圧縮歪みを有する。層 303 を低圧、低温 CVD プロセスにより堆積させる場合、層 303 は、層 303 をプラズマ支援 CVD プロセスによって堆積させる場合よりも強い張力を示す。従って、トレンチに隣接する活性領域は、層 303 を低圧、低温 CVD プロセスにより堆積させる場合に、層 303 をプラズマ支援 CVD プロセスによって堆積させる場合よりも大きい圧縮歪みを有することになる。

#### 【0025】

トランジスタのチャネル領域の歪みを調整することによりトランジスタの性能を制御することができる。例えば、チャネル領域の圧縮歪みが（トランジスタチャネル長方向に）大きくなると、P チャネルトランジスタの正孔移動度が大きくなり、チャネル領域の引っ張り歪みが（トランジスタチャネル長方向に）大きくなると、電子移動度が大きくなる。トランジスタチャネル幅方向の引っ張り歪みが大きくなると、P チャネルトランジスタの正孔移動度が大きくなる。更に、応力はウェハを回転させることによって制御することもできる。

#### 【0026】

一の実施形態においては、半導体構造を形成する方法では、ウェハを半導体材料により作製し、そしてトレンチを半導体材料の中に形成する。トレンチは半導体材料の側壁を含む。本方法では更に、第 1 誘電体材料をトレンチの底面部分を覆うように、トレンチ上端から第 1 の深さまで堆積させ、第 1 誘電体材料が第 1 の深さよりも上の領域の側壁にはほとんど堆積しないようにする。本方法では更に、第 2 誘電体材料をトレンチ内の第 1 材料を覆うように、トレンチ上端から第 2 の深さまで堆積させ、第 2 誘電体材料が第 2 の深さよりも上の領域の側壁にはほとんど堆積しないようにする。第 2 誘電体材料は第 1 誘電体材料とは異なる。本方法では更に、誘電体から成るトレンチ充填材料をトレンチ内の第 2 誘電体材料を覆うように堆積させる。誘電体から成るトレンチ充填材料は、第 2 誘電体材料をエッティングしないように選択的にエッティングすることができる。

#### 【0027】

別の実施形態においては、分離トレンチを半導体構造に形成する方法では、ウェハを半導体材料により作製し、そしてトレンチを半導体材料の中に形成する。トレンチは半導体材料の側壁を含む。本方法では更に、第 1 誘電体材料をトレンチの底面部分を覆うように、トレンチ上端から第 1 の深さまで堆積させ、第 1 誘電体材料が第 1 の深さよりも上の領域の側壁にはほとんど堆積しないようにする。本方法では更に、第 2 誘電体材料をトレンチ内の第 1 材料を覆うように、トレンチ上端から第 2 の深さまで堆積させ、第 2 誘電体材料が第 2 の深さよりも上の領域の側壁にはほとんど堆積しないようにする。第 2 誘電体材料は第 1 誘電体材料とは異なる。第 1 誘電体材料は第 1 膜厚を有し、そして第 2 誘電体材料は、第 1 膜厚よりも薄い第 2 膜厚を有する。本方法では更に、トレンチ側壁ライナーを

10

20

30

40

50

トレンチ内部の半導体材料の一部分の上に形成する。第2誘電体材料は、トレンチ側壁ライナーがトレンチ内部の第2誘電体材料の高さよりも低い位置に形成されるのを防止するよう機能する。本方法では更に、誘電体から成るトレンチ充填材料をトレンチ内の第2誘電体材料を覆うように堆積させる。誘電体から成るトレンチ充填材料は、第2誘電体材料をエッチングしないように選択的にエッチングすることができる。

#### 【0028】

別の実施形態では、半導体構造は、半導体材料、及び半導体材料の中に形成されるトレンチを含む。半導体構造は更に、トレンチの底面部分を覆うように、トレンチ上端から第1の深さまで堆積する誘電体材料、及びトレンチ内の第1材料を覆うように、トレンチ上端から第2の深さまで堆積する誘電体材料を含む。トレンチ内の第1誘電体材料の全てが第2誘電体材料によって覆われる。第2の深さは半導体材料の上面位置より下になる。第2誘電体材料は第1誘電体材料とは異なる。第1誘電体材料は第1の誘電率を有し、そして第2誘電体材料は、第1の誘電率よりも大きい第2の誘電率を有する。

10

#### 【0029】

本発明の特定の実施形態について示し、そして記載してきたが、この技術分野の当業者であれば、本明細書における示唆に基づいて、更に別の変更及び変形を、本発明及び本発明の広い局面から逸脱しない範囲において加えることができ、従って添付の請求項は、これらの請求項に示す技術範囲にこのような変更及び変形の全てを本発明の真の技術思想及び技術範囲のものとして含むものであることが理解できるであろう。

#### 【図面の簡単な説明】

20

#### 【0030】

【図1】先行技術によるウェハの部分側断面図。

【図2】本発明による或る製造工程の間のウェハの部分側断面図。

【図3】本発明による別の製造工程の間のウェハの部分側断面図。

【図4】本発明による別の製造工程の間のウェハの部分側断面図。

【図5】本発明による別の製造工程の間のウェハの部分側断面図。

【図6】本発明による別の製造工程の間のウェハの部分側断面図。

【図7】本発明による別の製造工程の間のウェハの部分側断面図。

【図8】本発明による別の製造工程の間のウェハの部分側断面図。

【図9】本発明による別の製造工程の間のウェハの部分側断面図。

30

【図10】本発明による別の製造工程の間のウェハの部分側断面図。

【図1】

FIG. 1

-PRIOR ART-

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図 10】

FIG. 10

---

フロントページの続き

|                          |                      |

|--------------------------|----------------------|

| (51)Int.Cl.              | F I                  |

| H 01 L 21/8238 (2006.01) | H 01 L 27/08 3 3 1 E |

| H 01 L 27/092 (2006.01)  | H 01 L 21/76 D       |

| H 01 L 21/762 (2006.01)  | H 01 L 27/12 F       |

| H 01 L 27/12 (2006.01)   |                      |

(72)発明者 ジエン、ヨンジュー

アメリカ合衆国 78717 テキサス州 オースティン マテオ コープ 9905

(72)発明者 ターナー、マイケル デイ。

アメリカ合衆国 78209 テキサス州 サン アントニオ パーシング アベニュー 219

(72)発明者 バン ゴンペル、トニ デイ。

アメリカ合衆国 78751 テキサス州 オースティン アベニュー ジー. 3910

審査官 松本 陶子

(56)参考文献 特開2003-258083(JP,A)

特開2004-111429(JP,A)

特開昭61-198745(JP,A)

米国特許第06524929(US,B1)

特表2004-527916(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 21/762

H01L 21/336

H01L 21/8238

H01L 27/08

H01L 27/092

H01L 27/12

H01L 29/78

H01L 29/786