(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6817895号

(P6817895)

(45) 発行日 令和3年1月20日(2021.1.20)

(24) 登録日 令和3年1月4日(2021.1.4)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 21/336 (2006.01)H01L 29/78 652H

H01L 29/78 653C

H01L 29/78 658E

H01L 29/78 658F

H01L 29/78 652F

請求項の数 4 (全 14 頁)

(21) 出願番号

特願2017-102560 (P2017-102560)

(22) 出願日

平成29年5月24日(2017.5.24)

(65) 公開番号

特開2018-198267 (P2018-198267A)

(43) 公開日

平成30年12月13日(2018.12.13)

審査請求日

令和1年8月9日(2019.8.9)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73) 特許権者 317011920

東芝デバイス&amp;ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74) 代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 藤農 佑樹

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 横山 昇

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1方向に延びる第1導電形の第1半導体領域と、

前記第1方向に延び、前記第1方向に交差する第2方向に前記第1半導体領域と配置され、空隙を囲む第2導電形の第2半導体領域と、

前記空隙と、前記第2半導体領域との間に設けられ、シリコン酸化物を含む第1絶縁膜と、シリコン窒化物を含む第2絶縁膜と、シリコン酸化物を含む第3絶縁膜とを有する絶縁部と、

を備え、

前記第1絶縁膜、前記第2絶縁膜及び前記第3絶縁膜は、前記第2半導体領域から前記空隙に向かって順に位置し、

前記第1絶縁膜と前記第3絶縁膜の厚さの合計は、前記第2絶縁膜の厚さの0.5倍以上であって4倍以下である半導体装置。

## 【請求項 2】

前記第1絶縁膜は、前記第2半導体領域の側面上及び底面上に位置し、

前記第2絶縁膜は、前記第1絶縁膜の側面上及び底面上に位置し、

前記第3絶縁膜は、前記第2絶縁膜の側面上及び底面上に位置する請求項1記載の半導体装置。

## 【請求項 3】

前記第1半導体領域及び前記第2半導体領域上に設けられた第2導電形の第3半導体領

10

20

域と、

前記空隙上に設けられ、前記第3半導体領域との間で前記絶縁部が位置するカバー膜と

、

をさらに備えた請求項1または2に記載の半導体装置。

【請求項4】

第1方向に延びる第1導電形の第1半導体領域と、

前記第1方向に延び、前記第1方向に交差する第2方向に空隙を介して前記第1半導体領域と配置される第2導電形の第2半導体領域と、

前記空隙と、前記第1半導体領域及び前記第2半導体領域との間に設けられ、シリコン酸化物を含む第1絶縁膜と、シリコン窒化物を含む第2絶縁膜と、シリコン酸化物を含む第3絶縁膜とを有する絶縁部と、

10

を備えた半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、半導体装置に関する。

【背景技術】

【0002】

電力制御などの用途に用いられる半導体装置として、MOSFET (Metal Oxide Semiconductor Field Effect Transistor) がある。このようなMOSFETには、n形半導体領域とp形半導体領域とがトレンチを介して交互に設けられた、スーパージャンクション構造を有するものがある。このような構造を有するMOSFETには、セルのピッチの微細化に伴って高アスペクト比のトレンチが形成され、各半導体領域の保護と共にトレンチの埋め込み性を向上することが課題となる。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003-309261号公報

【発明の概要】

【発明が解決しようとする課題】

30

【0004】

実施形態の目的は、信頼性が向上した半導体装置を提供することである。

【課題を解決するための手段】

【0005】

実施形態に係る半導体装置は、第1方向に延びる第1導電形の第1半導体領域と、前記第1方向に延び、前記第1方向に交差する第2方向に前記第1半導体領域と配置され、空隙を囲む第2導電形の第2半導体領域と、前記空隙と、前記第2半導体領域との間に設けられ、シリコン酸化物を含む第1絶縁膜と、シリコン窒化物を含む第2絶縁膜と、シリコン酸化物を含む第3絶縁膜とを有する絶縁部と、を備える。前記第1絶縁膜、前記第2絶縁膜及び前記第3絶縁膜は、前記第2半導体領域から前記空隙に向かって順に位置し、前記第1絶縁膜と前記第3絶縁膜の厚さの合計は、前記第2絶縁膜の厚さの0.5倍以上であって4倍以下である。

40

【図面の簡単な説明】

【0006】

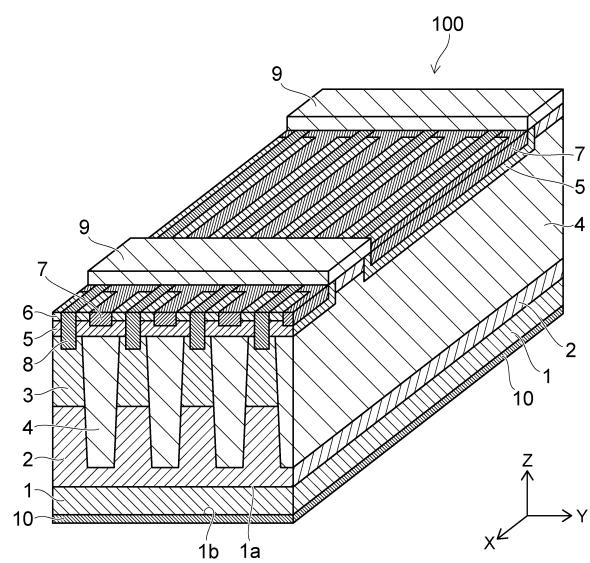

【図1】第1実施形態に係る半導体装置を示す斜視図である。

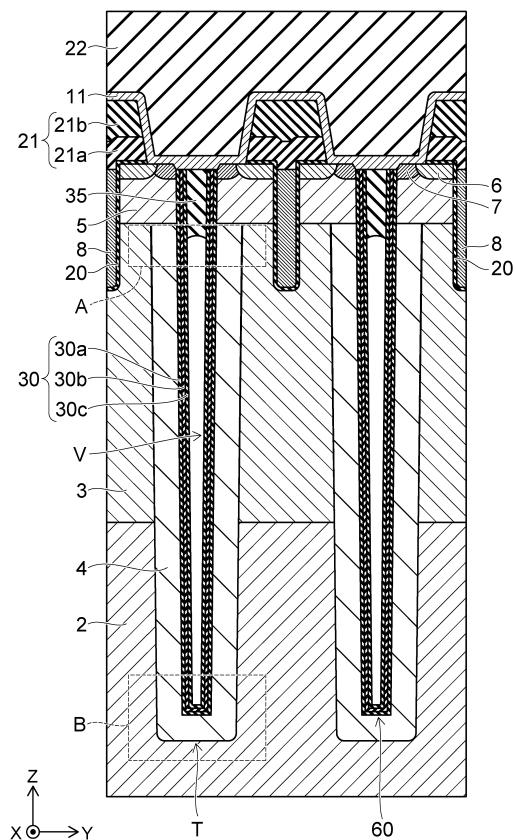

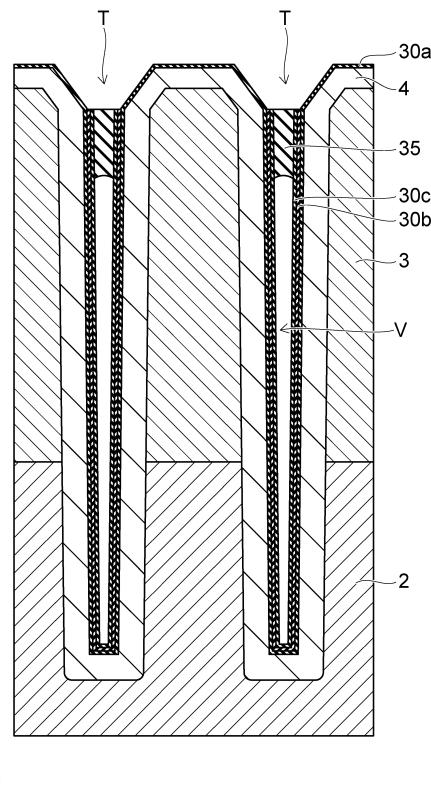

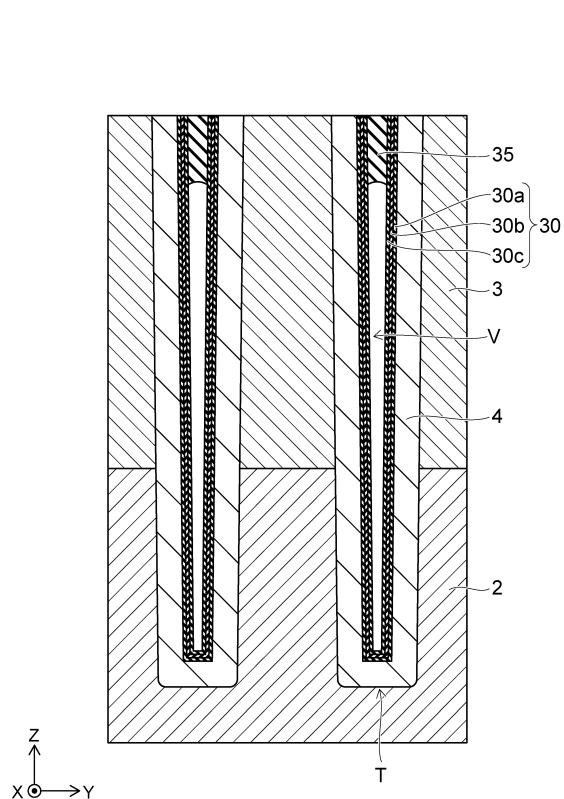

【図2】第1実施形態に係る半導体装置を示す断面図である。

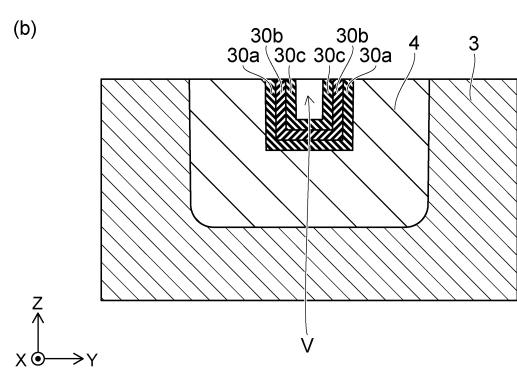

【図3】図3(a)は、図2の領域Aの拡大図であって、図3(b)は、図2の領域Bの拡大図である。

【図4】第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】第1実施形態に係る半導体装置の製造方法を示す断面図である。

50

【図6】第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図8】第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】第1実施形態に係る半導体装置の製造方法を示す断面図である。

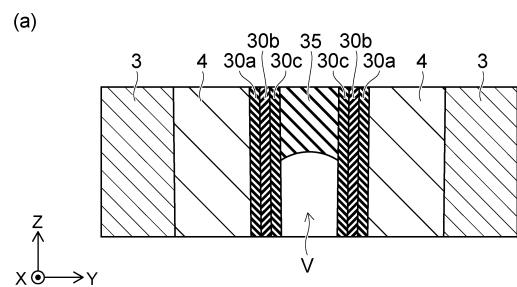

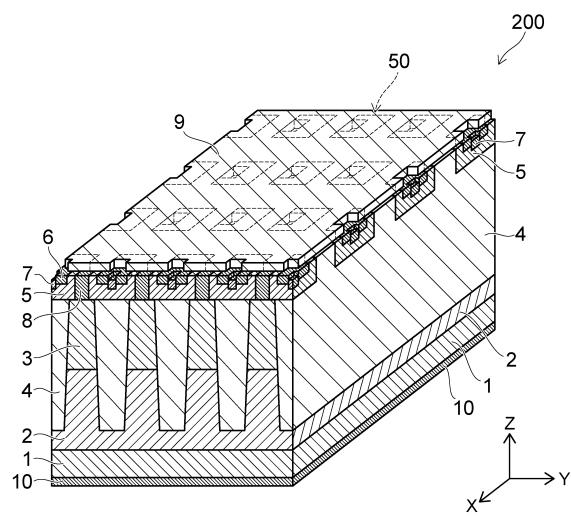

【図10】第2実施形態に係る半導体装置を示す斜視図である。

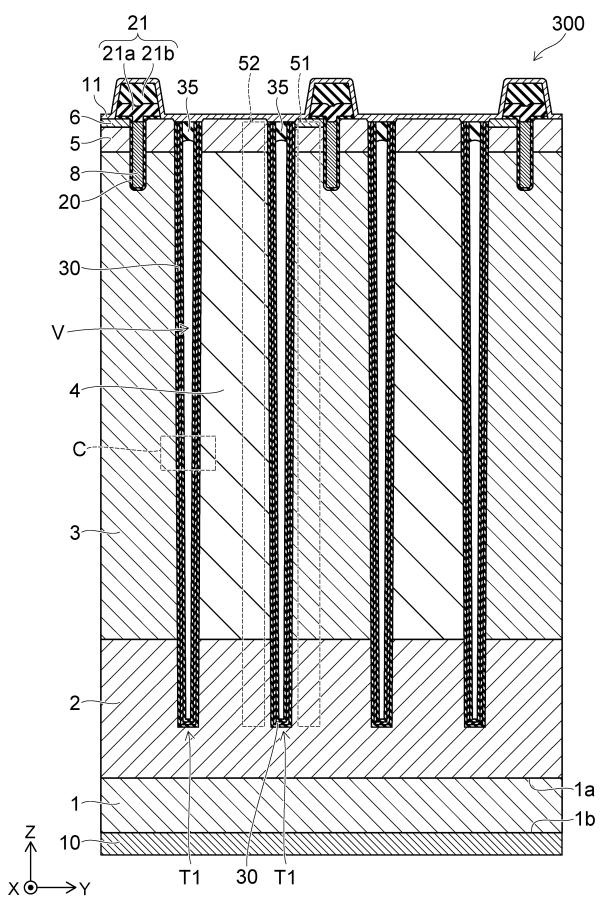

【図11】第3実施形態に係る半導体装置を示す断面図である。

【図12】図11の領域Cの拡大図である。

## 【発明を実施するための形態】

## 【0007】

以下に、本発明の各実施形態について図面を参照しつつ説明する。 10

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

## 【0008】

以下、本明細書においては、XYZ直交座標系を採用する。ドレイン領域1から半導体領域2に向かう方向をZ方向とし、Z方向に対して垂直な方向であって相互に直交する2方向をX方向及びY方向とする。

なお、以下で説明する各実施形態について、各半導体領域のp形とn形を反転させて各実施形態を実施しても良い。 20

## 【0009】

## (第1実施形態)

図1は、本実施形態に係る半導体装置を示す斜視図である。

図2は、本実施形態に係る半導体装置を示す断面図である。

図3(a)及び図3(b)は、図2の領域A及び領域Bの拡大図である。

図1及び図2は、半導体装置100の斜視図及び断面図をそれぞれ示している。図2は、図1の半導体装置100の一部を拡大して示している。なお、図1において、ソース電極11及び柱状部60の図示が省略されている。

半導体装置100は、例えば、MOSFETである。 30

## 【0010】

図1に示すように、半導体装置100には、ドレイン領域1と、第1導電形の半導体領域2と、第1導電形の半導体領域3と、第2導電形の半導体領域4と、第2導電形の半導体領域5と、第1導電形の半導体領域6と、コンタクト領域7と、ゲート電極8と、ゲートコンタクト9と、ドレイン電極10と、が設けられている。

ドレイン領域1の導電形は、例えばn<sup>+</sup>形である。

## 【0011】

n<sup>+</sup>、n、n<sup>-</sup>及びp<sup>+</sup>、p、p<sup>-</sup>の表記は、各導電形における実効的な不純物濃度の相対的な高低を表す。すなわち、「+」が付されている表記は、「+」及び「-」のいずれも付されていない表記よりも不純物濃度が相対的に高く、「-」が付されている表記は、いずれも付されていない表記よりも不純物濃度が相対的に低いことを示す。 40

## 【0012】

また、「実効的な不純物濃度」とは、半導体材料の導電性に寄与する不純物の濃度をいい、ドナーとなる不純物とアクセプタとなる不純物の双方が含まれている場合は、その相殺分を除いた濃度をいう。なお、n形不純物は、例えば、リン(P)であり、p形不純物は、例えば、ホウ素(B)である。

## 【0013】

半導体領域2は、ドレイン領域1の上面1a上に設けられ、その導電形は、例えばn<sup>-</sup>形である。

半導体領域3は、半導体領域2上に複数設けられ、その導電形は、例えばn形である。 50

半導体領域3は、例えば、nピラー領域である。複数の半導体領域3は、半導体領域2上に選択的に位置する。複数の半導体領域3は、X方向に延びており、Y方向に互いに離間して配置されている。

#### 【0014】

半導体領域4は、半導体領域2上に複数設けられ、その導電形は、例えばp形である。半導体領域4は、例えば、pピラー領域である。複数の半導体領域4は、半導体領域2上に選択的に位置する。複数の半導体領域4は、X方向に延びており、Y方向で隣り合う半導体領域3の間に位置するようにY方向に互いに離間して配置されている。

#### 【0015】

n形の半導体領域3と、p形の半導体領域4とは、Y方向において交互に設けられている。つまり、本実施形態の半導体装置100は、MOSFETであって、スーパージャンクション構造を有するものである。10

#### 【0016】

半導体領域5は、半導体領域3上、及び、半導体領域4上に複数設けられ、その導電形は、例えばp形である。半導体領域5は、例えば、pベース領域である。複数の半導体領域5は、半導体領域3上に選択的に位置する。複数の半導体領域5は、X方向に延びており、Y方向に互いに離間して配置されている。

#### 【0017】

半導体領域6は、半導体領域5上に複数設けられ、その導電形は、例えばn<sup>+</sup>形である。半導体領域6は、例えば、ソース領域である。複数の半導体領域6は、半導体領域5上に選択的に位置する。複数の半導体領域6は、X方向に延びており、Y方向に互いに離間して配置されている。20

#### 【0018】

コンタクト領域7は、半導体領域5上に複数設けられ、その導電形は、例えばp<sup>+</sup>形である。複数のコンタクト領域7は、半導体領域5上に選択的に位置する。複数のコンタクト領域7は、X方向に延びており、Y方向で隣り合う半導体領域6の間に位置するようにY方向に互いに離間して配置されている。コンタクト領域7は、後述するソース電極11に接続される。

#### 【0019】

ゲート電極8は、ゲート絶縁膜20(図2参照)を介して、半導体領域3上に複数設けられている。複数のゲート電極8は、半導体領域3上に選択的に位置する。30

複数のゲート電極8は、X方向に延びており、Y方向で隣り合う半導体領域5の間に位置するようにY方向に互いに離間して配置されている。また、複数のゲート電極8は、Y方向で隣り合う半導体領域6の間に位置するようにY方向に互いに離間して配置されている。つまり、コンタクト領域7及びゲート電極8は、半導体領域6を介してY方向に交互に配置されている。

ゲート電極8は、例えば、n形不純物を含有した多結晶シリコンを含む。

#### 【0020】

ゲートコンタクト9は、ゲート電極8上に複数設けられている。複数のゲートコンタクト9は、Y方向に延びており、X方向に所定の間隔で配置されている。ゲートコンタクト9は、例えば、金属材料によって形成される。40

#### 【0021】

ゲートコンタクト9を介して、ゲート電極8は、外部の周辺回路(図示せず)に電気的に接続される。ゲートコンタクト9を介して、ゲート電極8に閾値以上の電圧が印加されることで、MOSFETがオン状態となり、半導体領域5の表面にチャネル(反転層)が形成される。

ドレイン電極10は、ドレイン領域1の下面1b上に設けられている。ドレイン電極10は、ドレイン領域1に電気的に接続される。ドレイン電極10は、例えば、金属材料によって形成される。

#### 【0022】

10

20

30

40

50

図2に示すように、半導体領域6の一部上と、ゲート電極8の側面上及び底面上とには、ゲート絶縁膜20が設けられている。ゲート絶縁膜20は、例えば、シリコン酸化物(SiO)を含む。

ゲート電極8上、及び、ゲート絶縁膜20上には、層間絶縁膜21が設けられている。例えば、層間絶縁膜21は、膜21a及び膜21bの2層構造を有する。膜21aは、例えばシリコン酸化物を含む。膜21bは、膜21a上に設けられ、例えばBPSG(Boro-phospho silicate glass)を含む。

#### 【0023】

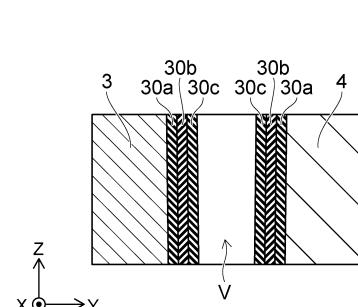

半導体領域4、5内には絶縁部30が設けられている。絶縁部30は、X方向に延びている。絶縁部30は、半導体領域2、3に形成されたトレンチT内に設けられている。トレンチTの内面上に、半導体領域4を介して絶縁部30が位置する。10

#### 【0024】

トレンチTは空隙部Vを含む。絶縁部30は、半導体領域4及び空隙部Vの間に位置する。

トレンチT内であって、空隙部V上にはカバー膜35が設けられている。カバー膜35は、例えばBPSGを含む。カバー膜35は、例えば、トレンチTにおけるキャップ膜として機能する。絶縁部30は、カバー膜35と、半導体領域4の一部及び半導体領域5との間に位置する。

絶縁部30及びカバー膜35は、内部に空隙部Vが形成された柱状部60を構成する。

#### 【0025】

なお、図2に示す例では、カバー膜35は空隙部V上に設けられているが、空隙部Vの側面の少なくとも一部上に設けられても良い。つまり、カバー膜35は、Y方向において絶縁部30及び空隙部Vの間に位置しても良い。

#### 【0026】

絶縁部30は、絶縁膜30aと、絶縁膜30bと、絶縁膜30cと、を有する。

絶縁膜30aは、例えば、シリコン酸化物(SiO)を含む。絶縁膜30bは、引張応力を有する材料、例えば、シリコン窒化物(SiN)を含む。絶縁膜30cは、例えば、シリコン酸化物(SiO)を含む。

絶縁膜30a、絶縁膜30b及び絶縁膜30cの形状は、例えば、底を有する筒状である。また、半導体領域4の形状は、例えば、底を有する筒状である。30

#### 【0027】

図3(a)に示すように、絶縁膜30aは、半導体領域4の側面上に位置する。絶縁膜30bは、絶縁膜30aの側面上に位置する。絶縁膜30cは、絶縁膜30bの側面上に位置する。絶縁部30は、カバー膜35の側面、及び、空隙部Vの側面を覆っており、絶縁膜30c、30b、30aがこれらの側面から離れる方向にこの順で位置する。

#### 【0028】

図3(b)に示すように、絶縁膜30aは、半導体領域4の底面上に位置する。絶縁膜30bは、絶縁膜30aの底面上に位置する。絶縁膜30cは、絶縁膜30bの底面上に位置する。絶縁部30は、空隙部Vの底面を覆っており、絶縁膜30c、30b、30aがこの底面から離れる方向にこの順で位置する。40

#### 【0029】

絶縁部30内の膜厚においては、絶縁膜30aを絶縁膜30b及び絶縁膜30cより大きくして、絶縁膜30bを絶縁膜30cより大きくすることが可能である。また、絶縁膜30aの膜厚を薄くして、絶縁膜30cをCVD(Chemical Vapor Deposition)膜により形成しても良い。この場合、絶縁膜30cを絶縁膜30a及び絶縁膜30bより大きくして、絶縁膜30bを絶縁膜30aより大きくすることが可能である。なお、絶縁膜30cをCVD膜によって形成する代わりに、他の被覆性の良い材料を用いて形成しても良い。

絶縁膜30aと絶縁膜30cの合計膜厚は、絶縁膜30bの膜厚の0.5倍以上であつて4倍以下である。絶縁膜30aと絶縁膜30cの合計膜厚は、絶縁膜30bの膜厚の150

倍以上（または同等以上）であって4倍以下であれば、さらに望ましい。絶縁膜30aと絶縁膜30cが、例えばシリコン酸化物(SiO)を含み、絶縁膜30bが、例えばシリコン窒化物(SiN)を含む場合、絶縁膜30aと絶縁膜30cの合計膜厚は、絶縁膜30bの膜厚の1.8倍程度であることが望ましい。

#### 【0030】

絶縁膜30a、30b、30cの膜厚とは、半導体領域4の側面上に絶縁膜30a、30b、30cが順に位置する場合(図3(a)の場合)、絶縁膜30a、30b、30cのY方向の厚さに相当し、半導体領域4の底面上に絶縁膜30a、30b、30cが順に位置する場合(図3(b)の場合)、絶縁膜30a、30b、30cのZ方向の厚さに相当する。

10

#### 【0031】

絶縁膜30aは、例えば、半導体領域3及び半導体領域4を保護する。絶縁膜30bは、例えば、絶縁膜30aの応力(例えば、圧縮応力)を緩和させる。絶縁膜30cは、例えば、トレンチT内にカバー膜35を埋め込み易くする。

#### 【0032】

図2に示すように、半導体領域6の一部上と、コンタクト領域7上と、層間絶縁膜21の側面上及び上面上とには、ソース電極11が設けられている。また、ソース電極11は、絶縁部30上及びカバー膜35上に設けられている。ソース電極11は、例えば、金属材料によって形成される。

ソース電極11上には、層間絶縁膜22が設けられている。層間絶縁膜22は、例えば、シリコン酸化物を含む。

20

#### 【0033】

次に、本実施形態に係る半導体装置の製造方法について説明する。

図4～図9は、半導体装置100の製造方法を示す断面図である。

なお、図4～図9に示された領域は、図2に示された領域の一部に相当する。なお、図4～図9においては、柱状部60より上の部分、及び、半導体領域2より下の部分は示されていない。

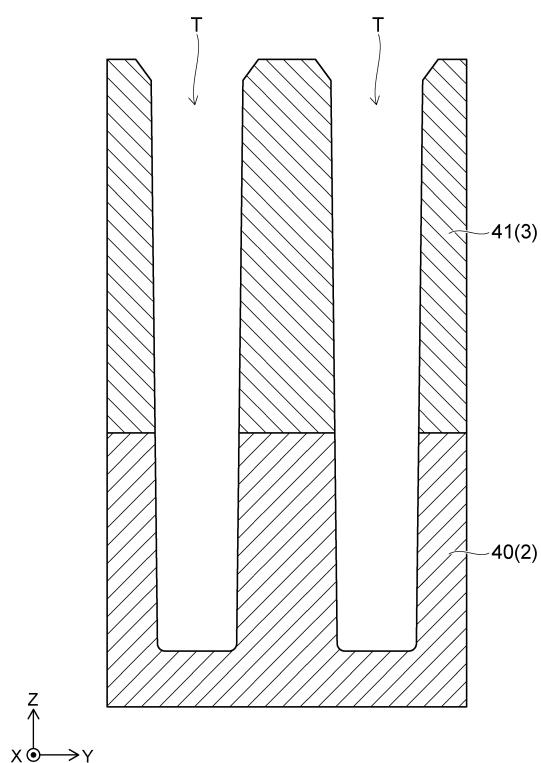

まず、図4に示すように、第1導電形の半導体基板40上に、第1導電形の半導体層41をエピタキシャル成長させる。

#### 【0034】

30

続いて、半導体層41上に、シリコン酸化膜等を含むマスク材を形成する。例えば、マスク材は、CVD法により半導体層41上に膜を堆積した後、リソグラフィ法及びRIE(Reactive Ion Etching)法により形成される。

#### 【0035】

続いて、パターニングされたマスク材をマスクに、半導体基板40及び半導体層41にトレンチTを形成する。トレンチTは、例えば、RIE法により形成される。その後、マスク材を剥離する。なお、トレンチTを形成した後の半導体基板40は、半導体領域2に相当する。また、トレンチTを形成した後の半導体層41は、半導体領域3に相当する。

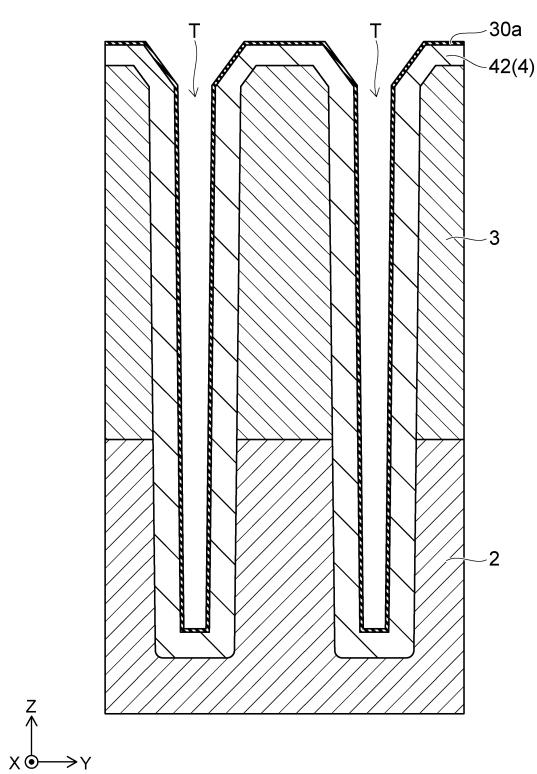

#### 【0036】

次に、図5に示すように、トレンチTの内壁面上及び底面上に、エピタキシャル成長法により、p形不純物を含む半導体膜42を形成する。半導体膜42は、トレンチT間の半導体領域3上にも形成される。半導体膜42は、例えば、ノンドープの単結晶シリコンを含む。半導体膜42は、半導体領域4に相当する。

40

#### 【0037】

続いて、トレンチT内であって半導体領域4の側面及び底面に、例えば熱酸化により、絶縁膜30aを形成する。絶縁膜30aは、トレンチT間の半導体領域4にも形成される。例えば、絶縁膜30aは、シリコン酸化物によって形成される。

#### 【0038】

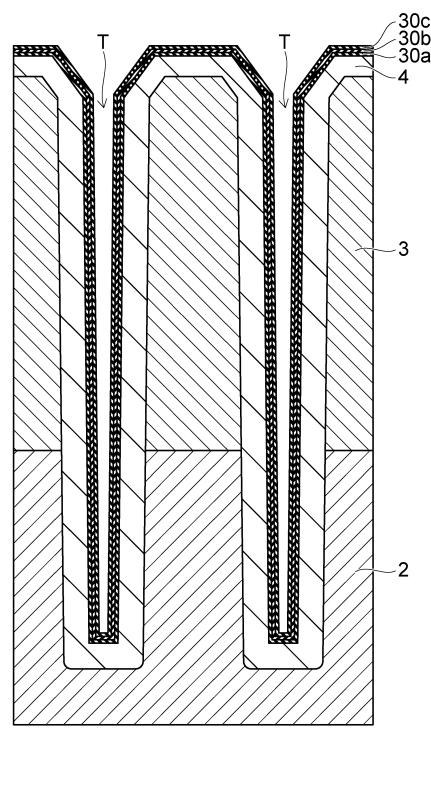

次に、図6に示すように、トレンチT内であって絶縁膜30aの側面上及び底面上に、例えばLPCVD(Low Pressure Chemical Vapor Deposition)法により、絶縁膜30b

50

を形成する。絶縁膜30bは、トレンチT間の絶縁膜30a上にも形成される。例えば、絶縁膜30bは、シリコン窒化物によって形成される。

#### 【0039】

続いて、トレンチT内であって絶縁膜30bの側面及び底面に、例えば熱酸化により、絶縁膜30cを形成する。絶縁膜30cは、トレンチT間の絶縁膜30bにも形成される。例えば、絶縁膜30cは、シリコン酸化物によって形成される。

#### 【0040】

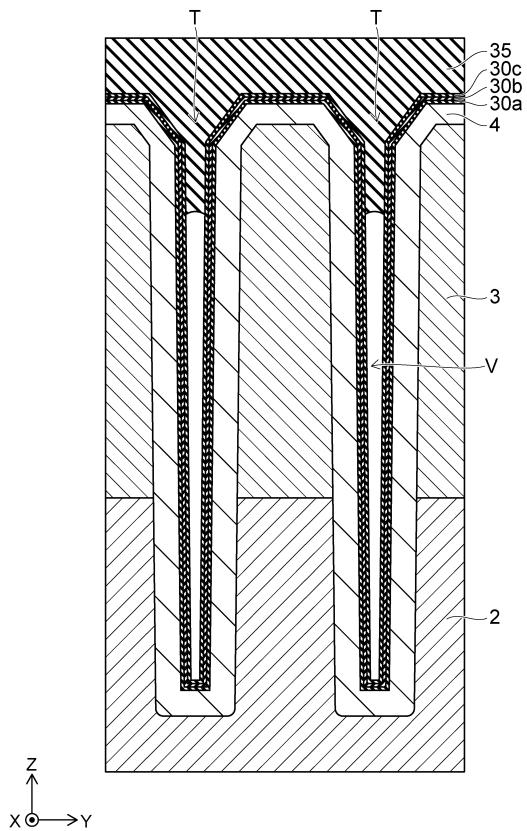

次に、図7に示すように、トレンチTを埋め込むように、絶縁膜30c上に、例えばCVD法により、カバー膜35を形成する。例えば、カバー膜35は、BPSGによって形成される。これにより、トレンチT内に、カバー膜35が上に位置する空隙部Vが形成される。続いて、カバー膜35にリフロー及びアニール処理を施す。

10

#### 【0041】

絶縁膜30bの側面上及び底面上に絶縁膜30c(シリコン酸化膜)が形成されているので、トレンチTの上部にカバー膜35が形成され易い。つまり、絶縁膜30cによって、トレンチTの深さ方向(-Z方向)におけるカバー膜35の埋め込み性が向上する。

#### 【0042】

次に、図8に示すように、エッティング処理を施してカバー膜35の一部を除去する。トレンチT上、及び、トレンチT間に位置するカバー膜35を除去するようにエッチバックする。続いて、例えばCDE(Chemical Dry Etching)法により、トレンチT間の絶縁膜30a上に位置する絶縁膜30b、30cを除去する。

20

#### 【0043】

次に、図9に示すように、エッティング処理を施して、トレンチT間の半導体領域4上に位置する絶縁膜30aを除去する。続いて、例えばCMP(Chemical Mechanical Polishing)法により、半導体領域3の一部、及び、半導体領域4の一部を除去する。これにより、絶縁膜30a、30b、30cの上面、及び、カバー膜35の上面が平坦化され、絶縁膜30a、絶縁膜30b及び絶縁膜30cを有する絶縁部30が形成される。

#### 【0044】

その後、公知の製造方法により、半導体領域5、6と、コンタクト領域7と、ゲート絶縁膜20と、ゲート電極8と、を形成する。続いて、層間絶縁膜21と、ソース電極11と、層間絶縁膜22と、ゲートコンタクト9と、ドレイン電極10と、を形成することで、半導体装置100が形成される。

30

#### 【0045】

次に、本実施形態の効果について説明する。

n形半導体領域とp形半導体領域とがトレンチを介して交互に設けられたスーパージャンクション構造を有するMOSFETでは、セルのピッチの微細化に伴って高アスペクト比のトレンチが形成され易い。トレンチの内面上及び上部上には、p形半導体領域及びカバー膜がそれぞれ形成され、トレンチの一部(p形半導体領域及びカバー膜で囲まれた部分)には空隙部が形成される場合がある。

#### 【0046】

このようなMOSFETでは、p形半導体領域から空隙部に電流が漏れ易くなる。空隙部へのリーク電流によってMOSFETの動作に不具合が生じる虞がある。また、トレンチの上部上にカバー膜を形成する場合、カバー膜が側面に位置する膜の材料によってはトレンチに対するカバー膜の埋め込み性が低下し易くなる。

40

#### 【0047】

また、カバー膜に含まれるホウ素やリン等の不純物がn形半導体領域及びp形半導体領域に染み出す場合があり、これらの半導体領域を保護するためにp形半導体領域の側壁に厚い膜を形成することが考えられる。しかし、p形半導体領域の側壁に圧縮応力を有する膜(例えば、シリコン酸化膜)を形成すると、圧縮応力を有する膜が厚く形成されることでウェーハの反りが大きくなってしまう。ウェーハの大きな反りは、製造工程中における加工精度を低下させ、製造装置の安定した稼働を妨げる原因となる。

50

**【0048】**

本実施形態の半導体装置100において、トレンチT内の半導体領域4上に絶縁膜30a、30b、30cが順に設けられている。このような絶縁膜30a、30b、30c(例えば、ONO膜)を設けると、半導体領域4から空隙部Vに電流が漏れることを抑制する。

**【0049】**

また、本実施形態では、絶縁膜30aによってカバー膜35の不純物等から半導体領域3及び半導体領域4を保護する。そして、絶縁膜30bは引張応力を有する材料(例えば、シリコン窒化物)を含むので、絶縁膜30bによって絶縁膜30aの応力を相殺してウェーハの反りを抑制する。例えば、絶縁膜30aの膜厚と、絶縁膜30bの膜厚とを所定の比率になるように設定すると(例えば、絶縁膜30aと絶縁膜30cの合計膜厚を絶縁膜30bの膜厚の1.8倍程度にすると)、カバー膜35の不純物の染み出しと、ウェーハの反りとがより抑制される。10

**【0050】**

また、本実施形態では、絶縁膜30cは、例えばシリコン酸化物を含むので、絶縁膜30cの側面上にカバー膜35が形成され易くなる。つまり、トレンチTに対するカバー膜35の埋め込み性が向上する。

本実施形態によれば、信頼性が向上した半導体装置及びその製造方法を提供することができる。20

**【0051】****(第2実施形態)**

図10は、本実施形態に係る半導体装置を示す斜視図である。

図10は、半導体装置200を示す斜視図である。図10に示された領域は、図1に示された領域に相当する。なお、図10において、ソース電極11及び柱状部60の図示が省略されている。

本実施形態において、半導体領域3及び半導体領域4より上の構成が第1実施形態と異なる。よって、これ以外の構成の詳細な説明は省略する。

**【0052】**

図10に示すように、半導体装置200には、ドレイン領域1と、半導体領域2と、半導体領域3と、半導体領域4と、半導体領域5と、半導体領域6と、コンタクト領域7と、ゲート電極8と、ゲートコンタクト9と、ドレイン電極10と、が設けられている。30

**【0053】**

半導体領域5は、半導体領域3上、及び、半導体領域4上に複数設けられている。複数の半導体領域5は、X-Y平面を島状に配置されている。

半導体領域6は、半導体領域5上に複数設けられている。複数の半導体領域6は、X-Y平面を島状に配置されている。

**【0054】**

コンタクト領域7は、半導体領域5上に複数設けられている。複数のコンタクト領域7は、X-Y平面を島状に配置されている。また、複数のコンタクト領域7は、Y方向で隣り合う半導体領域6の間に位置するようにY方向に互いに離間して配置されている。40

半導体領域5、半導体領域6及びコンタクト領域7をそれぞれ有する複数の領域50は、X-Y平面を島状に配置されている。

**【0055】**

ゲート電極8は、半導体領域3上に格子状に設けられている。ゲート電極8は、X方向及びY方向で隣り合う半導体領域5の間に位置する。

ゲートコンタクト9は、ゲート電極8上に設けられている。

**【0056】**

本実施形態において、絶縁部30の構成及び配置は第1実施形態と同じである。つまり、図2、図3(a)及び図3(b)に示すように、絶縁部30は、絶縁膜30a、30b、30cを有し、半導体領域4、5内に設けられている。50

本実施形態の効果は、前述の第1実施形態と同じである。

**【0057】**

(第3実施形態)

図11は、本実施形態に係る半導体装置を示す断面図である。

図12は、図11の領域Cの拡大図である。

図11に示すように、半導体装置300には、ドレイン領域1と、半導体領域2と、半導体領域3と、半導体領域4と、半導体領域5と、半導体領域6と、ゲート電極8と、ドレイン電極10と、ソース電極11と、ゲート絶縁膜20と、層間絶縁膜21と、絶縁部30と、カバー膜35と、が設けられている。層間絶縁膜21は、膜21a及び膜21bを有する。

10

**【0058】**

半導体領域2は、ドレイン領域1の上面1a上に設けられている。

半導体領域3は、半導体領域2上に複数設けられている。複数の半導体領域3は、X方向に延びてあり、Y方向に互いに離間して配置されている。

半導体領域4は、半導体領域2上に複数設けられている。複数の半導体領域4は、X方向に延びており、Y方向で隣り合う半導体領域3の間に位置するようにY方向に互いに離間して配置されている。

**【0059】**

複数の半導体領域3及び複数の半導体領域4は、多段エピタキシャル法を用いて形成される。例えば、リソグラフィ法を用いたイオン注入と、エピタキシャル成長法とをZ方向に交互に繰り返す。これにより、n形の半導体領域3と、p形の半導体領域4とがY方向において交互に位置するように半導体領域2上に設けられる。つまり、本実施形態の半導体装置300は、MOSFETであって、スーパージャンクション構造を有するものである。

20

**【0060】**

半導体領域5は、半導体領域3上、及び、半導体領域4上に複数設けられている。複数の半導体領域5は、Y方向に互いに離間して配置されている。

半導体領域6は、半導体領域5上に複数設けられている。複数の半導体領域6は、Y方向に互いに離間して配置されている。

**【0061】**

30

ゲート電極8は、半導体領域3上にゲート絶縁膜20を介して複数設けられている。複数のゲート電極8は、Y方向に互いに離間して配置されている。

ドレイン電極10は、ドレイン領域1の下面1b上に設けられている。

ソース電極11は、半導体領域5の一部上と、半導体領域6の一部上と、層間絶縁膜21上と、絶縁部30上と、カバー膜35上とに設けられている。

**【0062】**

絶縁部30は、トレンチT1内に設けられている。トレンチT1は、破線で示すように、半導体領域2、半導体領域3、半導体領域5及び半導体領域6からなる半導体領域51と、半導体領域2、半導体領域4及び半導体領域5からなる半導体領域52との間に形成される。トレンチT1の内面上に絶縁部30が位置する。

40

**【0063】**

カバー膜35は、トレンチT1の空隙部V上に設けられている。絶縁部30は、半導体領域51と、空隙部V及びカバー膜35との間に位置する。また、絶縁部30は、半導体領域52と、空隙部V及びカバー膜35との間に位置する。

**【0064】**

図12に示すように、絶縁部30は、絶縁膜30a、絶縁膜30b及び絶縁膜30cを有する。

絶縁膜30aは、半導体領域51の側面上、及び、半導体領域52の側面上に位置する。また、絶縁膜30aは、トレンチT1の底面上であって半導体領域2上に位置する。

絶縁膜30bは、絶縁膜30aの側面上及び底面上に位置する。

50

絶縁膜30cは、絶縁膜30bの側面上及び底面上に位置する。

つまり、絶縁部30は、カバー膜35の側面と、空隙部Vの側面及び底面とを覆っており、絶縁膜30c、30b、30aがこれらの側面及び底面から離れる方向にこの順で位置する。絶縁膜30a、絶縁膜30b及び絶縁膜30cの形状は、例えば、底を有する筒状である。

本実施形態の効果は、前述の第1実施形態と同じである。

#### 【0065】

前述したように、一例として、スーパージャンクション構造を有するMOSFETを例に説明したが、各実施形態に係る半導体装置は、スーパージャンクション構造を有するIGBT (Insulated Gate Bipolar Transistor) 等、その他の半導体装置に適用しても良い。

10

#### 【0066】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。

#### 【符号の説明】

#### 【0067】

20

1：ドレイン領域、1a：上面、1b：下面、2～6、51、52：半導体領域、7：コンタクト領域、8：ゲート電極、9：ゲートコンタクト、10：ドレイン電極、11：ソース電極、20：ゲート絶縁膜、21、22：層間絶縁膜、21a、21b：膜、30：絶縁部、30a、30b、30c：絶縁膜、35：カバー膜、40：半導体基板、41：半導体層、42：半導体膜、50：領域、60：柱状部、100、200、300：半導体装置、T、T1：トレンチ、V：空隙部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 奥村 秀樹

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 恩田 和彦

(56)参考文献 特開2003-309261(JP,A)

米国特許出願公開第2014/0327069(US,A1)

特開2006-135150(JP,A)

特開2000-196074(JP,A)

特開2008-047602(JP,A)

特開2004-214511(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336