(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4733434号

(P4733434)

(45) 発行日 平成23年7月27日(2011.7.27)

(24) 登録日 平成23年4月28日(2011.4.28)

(51) Int.Cl.

H01L 33/62 (2010.01)

F 1

H01L 33/00 440

請求項の数 3 (全 9 頁)

(21) 出願番号 特願2005-164899 (P2005-164899)

(22) 出願日 平成17年6月3日 (2005.6.3)

(65) 公開番号 特開2006-339541 (P2006-339541A)

(43) 公開日 平成18年12月14日 (2006.12.14)

審査請求日 平成20年5月20日 (2008.5.20)

(73) 特許権者 000131430

シチズン電子株式会社

山梨県富士吉田市上暮地1丁目23番1号

(74) 代理人 100085280

弁理士 高宗 寛暁

(72) 発明者 菊池 悟

山梨県富士吉田市上暮地1丁目23番1号

株式会社シチズン電子内

(72) 発明者 深澤 孝一

山梨県富士吉田市上暮地1丁目23番1号

株式会社シチズン電子内

審査官 土屋 知久

最終頁に続く

(54) 【発明の名称】チップ型LED

## (57) 【特許請求の範囲】

## 【請求項1】

発光色が異なる複数個のLED素子を並列接続して、同一小型基板上に搭載するチップ型LEDにおいて、前記複数個のLED素子を搭載し、各下面電極をダイボンドペースト材により接続する前記小型基板の共通電極は、それぞれのLED素子毎に分離し、前記各LED素子のマウントする面以外の前記小型基板の端部で共通接続した電極パターンであり、前記複数個のLED素子の各下面電極と前記小型基板の共通電極間との電気的接続に通常の導電ペーストにカーボンブラックを一定の割合で混合し、各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材を使用して前記小型基板の共通電極上に前記LED素子をマウントし、前記複数個のLED素子の各上面電極と前記小型基板の他の共通電極間との接続にワイヤボンディングを使用したことを特徴とするチップ型LED。

## 【請求項2】

前記各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材は、各色調のLED素子毎に異なる種類のダイボンドペースト材を用いることを特徴とする請求項1記載のチップ型LED。

## 【請求項3】

前記各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材は、各色調のLED素子毎に前記ダイボンドペースト材の印刷範囲又は層厚が異なることを特徴とする請求項1記載のチップ型LED。

10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は発光ダイオード、すなわちLED (Light Emitting Diode) に係り、一般照明用、携帯電話機搭載カメラのフラッシュ用あるいは携帯電話機、携帯機器等の操作キーの照明等に用いる小型チップ型発光ダイオード(以下チップ型LED)の構造に関する。

## 【背景技術】

## 【0002】

LEDは集積回路と同様にウェーハー状で多数個を同時に作製し、個々にスクライプしたペアチップ、すなわちLED素子を取扱が容易な小型パッケージに封止して使用に供することが多いが、そのパッケージ形状のひとつがチップ型LEDであり、前記チップ型LEDは小型基板に前記LED素子を搭載し、ワイヤボンディングで前記LED素子のアノードあるいはカソードの電極と前記小型基板の電極間との電極配線を行った後に樹脂モールド形成したものである。あるいは、LEDを更に微細実装する場合は、直接プリント基板等にLED素子を搭載し、ワイヤボンディングで前記プリント基板に電極配線を行った後に樹脂モールド形成する場合もある。

## 【0003】

LEDは発光電力効率に優れ、信号表示用のほか、近年は高輝度LEDによる照明装置としての用途も多い。しかし、高輝度LEDとはいえ単体のLEDでは使用目的によっては光量不足もあり、複数個のLED素子を直列あるいは並列接続して光量の増強を計っている。特にハイパワーが要求される一般照明やフラッシュ照明用には、同一パッケージ内に4個以上の素子を封止することが多い。

## 【0004】

LEDはアノードに正、カソードに負の電圧をかけ、約2Vの電圧で電流が流れはじめて発光するが、指数的な電圧電流特性であり、並列接続により駆動する場合はそれぞれの順方向電圧(Vf)値に依存した電流が流れる。従って、同一パッケージ内の複数のLEDの順方向電圧値VfのばらつきによりそれぞれのLEDに流れる順方向電流値(If)もばらつくため、それぞれのLED素子に直列に外部抵抗を接続し、各LEDの順方向電流値Ifのばらつきを抑える必要がある。また、発光色の異なる赤色(R)緑色(G)黄色(Y)等のLED素子を同一パッケージに封止する場合は、各LED素子の順方向電圧値Vfが大きく異なるため、各々のLED素子に対して整流、すなわち電流制限のための直列抵抗付加が不可欠になる。

## 【0005】

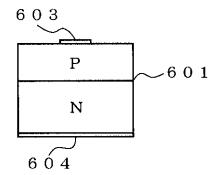

以下図面にもとづいて従来技術におけるLED素子の並列接続について説明する。図6aは一般的なPN接合LED素子の断面構造図であって、601はP層が上面のLED素子である。603はP層上面に形成したアノード電極、604はN層下面に形成したカソード電極であって、図示していないが、LEDをマウントする基板電極上にN層下面、すなわちカソードを導電接着して、ワイヤボンディングでアノード電極603を引き出す。図6bは図6aに示したLED601の等価回路図であって、順方向電圧、すなわちアノード電極603に正電圧、カソード電極604に負電圧を印加することでLED601を点灯する。

## 【0006】

図7は一般的なLEDの電圧電流特性図であって発光色の異なる赤色(R)緑色(G)黄色(Y)のLED素子の電圧電流特性例を符号R、G、Yで示す。各LEDは2V付近から急峻な立ち上がり特性を示しているが、それぞれ異なる電圧電流特性である。

## 【0007】

さらに同一色調のLEDであっても、個々のLED素子毎に電圧電流特性は僅かながら差異があり、LEDの電圧電流特性が急峻な立ち上がり特性であることから、僅かな特性の違いであってもLED素子を並列接続すると電流の不均衡を生ずる。従って、従来技術

10

20

30

40

50

においては以下に説明する方法で並列接続した LED の電流均衡を実現していた。

【0008】

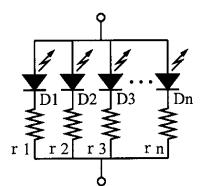

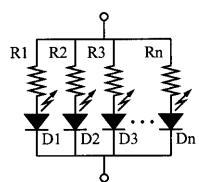

すなわち、図 8 a は従来技術の LED 素子の並列接続回路図であって、同一パッケージのそれぞれの LED 素子に対応した抵抗を付加する方法である。符号 D 1、D 2、D 3、D n に示す各 LED 素子に符号 R 1、R 2、R 3、R n の各電流制限抵抗を各々対応して直列接続してある。あるいは、LED 素子 D 1、D 2、D 3、D n を搭載するパッケージは小型に形成するためこの電流制限抵抗 R 1、R 2、R 3、R n は LED 素子 D 1、D 2、D 3、D n のパッケージ外のプリント基板等に実装することもあり、さらにはプリント基板に電流制限抵抗として印刷抵抗を形成する場合もある。

【0009】

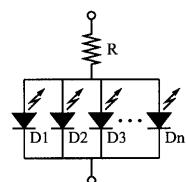

10

図 8 b は従来技術の LED 素子のもうひとつの並列接続回路図であって、同一パッケージ内の LED 素子の電圧電流特性を厳密に揃える方法である。符号 D 1、D 2、D 3、D n に示す各 LED 素子はあらかじめ点灯に適した一定の順方向電流 I f を流し、このときの順方向電圧値 V f を測定して分類するのであるが、この順方向電圧値 V f の分類幅を細分化して、同一分類した LED を同一パッケージに搭載して並列接続するのである。従つて、この場合は LED 素子の順方向電圧特性が揃っているので電流制限抵抗は符号 R で示す 1 個の電流制限抵抗で良いため電流制限抵抗の実装面積を縮小化することができる。

【0010】

【特許文献 1】特開 2002-344023 号公報

20

【特許文献 2】特開 2004-179372 号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、図 8 a により説明した従来技術における複数の LED 素子を並列接続にする方法にあっては、LED 素子 D 1、D 2、D 3、D n それぞれに対応した電流制限抵抗を付加する必要があるため、実装面積やコスト増大の要因となる。さらに、電流制限抵抗 R 1、R 2、R 3、R n を LED 素子 D 1、D 2、D 3、D n のパッケージ外のプリント基板等に実装する場合はチップ型 LED のパッケージ内の各 LED 素子 D 1、D 2、D 3、D n 毎にカソード端子配線を外部に引き出す必要があり、パッケージ形状の増大とコスト増大を招く結果となる。

30

【0012】

また、図 8 b により説明した従来技術における複数個の LED 素子を並列接続する方法にあっては、同一パッケージに封止する LED 素子 D 1、D 2、D 3、D n の順方向電圧電流特性の分類幅の細分化を強いられ、工程増とコスト増大を招くという問題があった。

【0013】

(発明の目的)

すなわち、本発明の目的は、前記図 8 b により説明した同一パッケージ内に順方向電圧 V f を揃えた複数の LED 素子 D 1、D 2、D 3、D n を並列接続して封止するチップ型 LED において、各 LED 素子 D 1、D 2、D 3、D n の順方向電圧電流特性の分類精度を緩和し、かつ、同一パッケージ内に前記複数個の LED 素子を並列接続構成としても各 LED 素子間の電流不均衡を生じないチップ型 LED を提供することにある。

40

【課題を解決するための手段】

【0014】

上記目的を達成するために、本発明は、発光色が異なる複数個の LED 素子を並列接続して、同一小型基板上に搭載するチップ型 LED において、前記複数個の LED 素子を搭載し、各下面電極をダイボンドペースト材により接続する前記小型基板の共通電極は、それぞれの LED 素子毎に分離し、前記各 LED 素子のマウントする面以外の前記小型基板の端部で共通接続した電極パターンであり、前記複数個の LED 素子の各下面電極と前記小型基板の共通電極との電気的接続に通常の導電ペーストにカーボンブラックを一定の割合で混合し、各色調の LED 素子毎に異なる抵抗値としたダイボンドペースト材を使用

50

して前記小型基板の共通電極上に前記LED素子をマウントし、前記複数個のLED素子の各上面電極と前記小型基板の他の共通電極間との接続にワイヤボンディングを使用したことを特徴とする。

【0015】

すなわち、前記抵抗成分を有するダイボンドペースト材は、発光色が異なる前記複数個のそれぞれのLED素子に対して各々の直列抵抗成分とすることで、前記複数個のLED素子の電圧電流特性の勾配を個々に緩和し、前記複数個のLED素子を並列接続しても各LED素子間の電流不均衡を少なくするのである。また、前記各LED素子をマウントする電極面を分離することで隣接するLED素子の下面電極同士がダイボンドペースト材のはみだしにより短絡することを防止する。

10

【0018】

また、前記各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材は、各色調のLED素子毎に異なる種類のダイボンドペースト材を用いることを特徴とする。

【0019】

すなわち、前記各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材として、各色調のLED素子毎に異なる種類のダイボンドペースト材を用いることでそれぞれの色調毎に異なるLED素子の順方向電圧に対応した直列抵抗値を持たせ各LED素子間の電流不均衡を少なくするのである。

20

【0020】

また、前記各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材は、各色調のLED素子毎に前記ダイボンドペースト材の印刷範囲又は層厚が異なることを特徴とする。

【0021】

すなわち、前記各色調のLED素子毎に異なる抵抗値としたダイボンドペースト材として、各色調のLED素子毎に前記ダイボンドペースト材の印刷範囲を変え又は異なる厚さにすることでそれぞれの色調毎に異なるLED素子の順方向電圧に対応した直列抵抗値を持たせ各LED素子間の電流不均衡を少なくするのである。

30

【発明の効果】

【0022】

以上のように本発明によれば、同一小型基板上に抵抗成分を有するダイボンドペースト材を使用して複数個のLED素子を並列接続搭載することで前記抵抗成分を有するダイボンドペースト材が前記複数個のそれぞれのLED素子に対して各々の直列抵抗成分を形成するため前記複数個のLED素子の電圧電流特性の勾配を個々に緩和し、前記複数個の各LED素子間の電流不均衡を少なくなり、複数個のLED素子を並列接続した強発光チップ型LED、あるいは発光色の異なるLED素子の並列混載チップ型LEDの作製が容易になる。

40

【発明を実施するための最良の形態】

【0023】

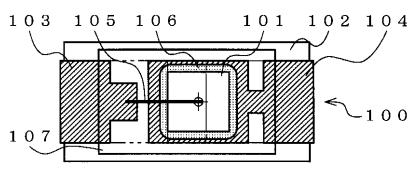

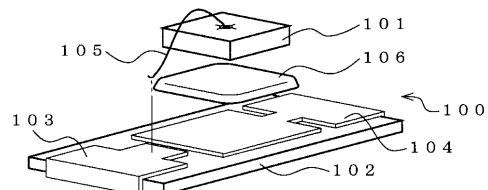

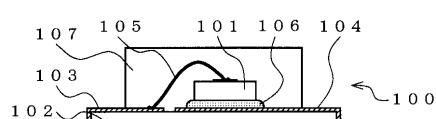

以下、本発明の実施形態について図面を用いて説明する。図1aは本発明の実施形態におけるチップ形LEDの平面図を示す。図1bは本発明の実施形態におけるチップ型LEDの側面図である。図2は本発明の実施形態におけるチップ型LEDの組立斜視図である。

【0024】

図1a、図1bおよび図2において、100はLED素子を1個搭載したチップ型LED

50

D であって、本発明の基本的な構造を示す。101 は LED 素子、102 は小型基板、103 は小型基板 102 上に形成したアノード電極、104 は小型基板 102 上に形成したカソード電極、105 は前記 LED 素子 101 のアノードと前記小型基板 102 上に形成したアノード電極 103 を接続するボンディングワイヤ、106 は前記 LED 素子 101 下面のカソードと前記小型基板 102 上に形成したカソード電極 104 を接続する抵抗成分を有するダイボンドペースト材であって、前記小型基板 102 上に前記 LED 素子 101 を固着マウントする抵抗成分を有する導電接着層、107 は前記小型基板 102 上に搭載した前記 LED 素子 101 およびボンディングワイヤ 105 等を保護し、かつ前記 LED 素子 101 の発光を妨げないスモークあるいはクリア樹脂である。なお、図 2 ではクリア樹脂 107 は省略してある。

10

#### 【0025】

すなわち、本発明は図 1a、図 1b および図 2 における前記小型基板 102 上に前記 LED 素子 101 を固着マウントする接着層であるダイボンドペースト材 106 が抵抗成分を有することが特徴的なのである。従って、本発明においてはダイボンドペースト材 106 には抵抗が大きな素材、例えば、通常の導電ペーストにカーボンブラック等を一定の割合で混合してダイボンドペースト材の抵抗成分を積極的に使用することを特徴としている。

#### 【0026】

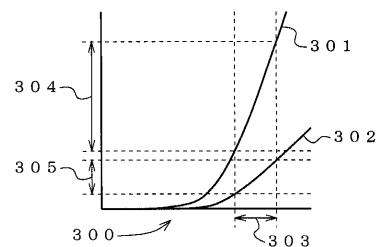

図 3 は本発明の実施形態におけるチップ型 LED の電圧電流特性図であって、X 軸が LED への印加電圧、Y 軸が LED の電流を示す。ここで、301 は従来の LED の電圧電流特性を示し、印加電圧範囲 303 における電流変化は 304 に示すように急峻で大きく変化する。302 は本発明のチップ型 LED の電圧電流特性を示し、印加電圧範囲 303 における電流変化は 305 に示すように前記従来の LED の電圧電流特性に比較して電圧電流特性の勾配が大幅に緩和される。

20

#### 【0027】

その理由は、従来の LED はチップ内のダイボンドペースト材の抵抗が極めて小さく、かつ、発光領域における LED の電圧電流特性が急峻であることから、前記発光領域における動作抵抗値が極めて小さいことに起因する。この従来の LED に対して本発明はダイボンドペースト材による抵抗成分を付加してあるため前記発光領域における動作抵抗値は大凡前記ダイボンドペースト材により付加した抵抗値となる。本発明におけるダイボンドペースト材は通常の導電ペーストにカーボンブラック等を一定の割合で混合するので付加できる抵抗値は数 10 オームと低いが、素の LED の動作抵抗値に比較すれば本発明のチップ型 LED の発光領域における動作抵抗値は充分大きな値である。従って、前述のように複数個の LED 素子を同一パッケージに封止する場合の LED 素子の順方向電圧電流特性分類を粗くしても並列接続の各 LED 素子間の電流不均衡が少なくなる。

30

#### 【0028】

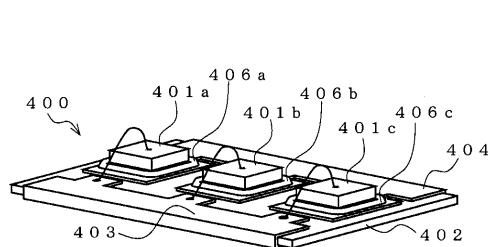

図 4 は図 1a、図 1b および図 2 に示し説明した本発明の実施形態を複数の LED 素子の並列接続に適用したチップ型 LED の斜視図であって、400 は LED 素子を 3 個搭載したチップ型 LED である。401a、401b、401c は LED 素子であって、402 は前記 LED 素子 401a、401b、401c を搭載する小型基板である。403 は小型基板 402 上に形成したアノード電極、404 は小型基板 402 上に形成したカソード電極である。406a、406b、406c はカソード電極 404 上に LED 素子 401a、401b、401c 下面の各カソード面を固着マウントする抵抗成分を有するダイボンドペースト材である。

40

#### 【0029】

すなわち、カソード電極 404 は各 LED 素子 401a、401b、401c 下面の各カソード面を固着マウントする電極部分は分離してあるが前記各 LED 素子をマウントする面以外の前記小型基板 402 の端部でカソード電極 404 のパターンは共通接続しており、前記各 LED 素子 401a、401b、401c 下面の各カソード面は抵抗成分を有するダイボンドペースト材で固着マウントすることで前記各 LED 素子 401a、401b、401c

50

b、401cのカソード側にはそれぞれ独立してダイボンドペースト材の抵抗成分が挿入付加される。いっぽう、アノード電極403は共通で各LED素子401a、401b、401c上面のアノードと前記アノード電極403はボンディングワイヤで導通接続する。

【0030】

なお、ここでカソード電極404の各LED素子401a、401b、401c下面の各カソード面を固着マウントする電極部分を分離するのは隣接するLED素子の下面電極同士がダイボンドペースト材のはみだしにより短絡することを防ぐためである。仮に隣接するLED素子の下面同士が前記ダイボンドペースト材のはみだしで短絡すると前記隣接するLED素子のカソード同士が接続してしまい、前記各LED素子のカソード側にそれぞれ独立してダイボンドペースト材の抵抗成分を挿入付加する機能が失われてしまう。

10

【0031】

図5は図4に示し説明した本発明による複数のLED素子をカソード側に抵抗成分を有するダイボンドペースト材でマウントしたチップ型LEDの等価回路図であって、ここでは複数のLED素子はn個である。符号D1、D2、D3、Dnに示す各LED素子のカソード側それぞれに直列に接続したr1、r2、r3、rnが抵抗成分を有するダイボンドペースト材による抵抗である。

【0032】

すなわち、LED素子D1、D2、D3、Dnのカソード側それぞれに挿入した直列抵抗r1、r2、r3、rnが素のLEDの動作抵抗値に付加されLED素子D1、D2、D3、Dnの各々の電圧電流特性勾配を緩和するので並列接続の各LED素子間の電流不均衡が少なくなる。つまり、並列接続するLED素子の順方向電圧電流特性分類を粗くしても並列接続が容易なためLED素子選別の歩留まりも高くコスト低減の効果もある。

20

【0033】

さらに、順方向電圧電流特性の異なるLED素子、例えば発光色の異なる赤色(R)緑色(G)黄色(Y)のLED素子を並列接続する場合はそれぞれの電圧電流特性に応じた比抵抗のダイボンドペースト材を使用してマウントすることで色調の異なるLED素子を並列接続することができる。すなわち、前記ダイボンドペースト材は一般的にディスペンサーでLED素子をマウントする電極に塗布するが、LED素子の電圧電流特性に応じたダイボンドペースト材毎のディスペンサーを使い分けるのである。また、同一ダイボンドペースト材を順方向電圧電流特性の異なるLED素子のマウント電極に印刷する場合はLED素子の電圧電流特性に応じたダイボンドペースト材の印刷範囲を変えることで、各々のLED素子をマウントするペースト量を変えることで前記ダイボンドペースト材の広がりが一定なら前記ダイボンドペースト材の厚みが異なり、各LED素子の電圧電流特性に応じた接合抵抗が得られる。

30

【0034】

以上、本発明はP層が上面、N層が下面のLED素子にもとづいて説明したが、N層が上面、P層が下面のLED素子であってもLED素子のアノードとカソードが入れ替わるだけであり、アノード側が抵抗成分を有するダイボンドペースト材でアノード電極にマウントされ、カソード側はワイヤボンディングでカソード電極へ引き出す。従って、この場合はLED素子のアノード側に個々に抵抗成分が挿入されることになる。

40

【図面の簡単な説明】

【0035】

【図1a】図1aは本発明の実施形態におけるチップ型LEDの平面図である。

【図1b】図1bは本発明の実施形態におけるチップ型LEDの側面図である。

【図2】図2は実施形態におけるチップ型LEDの組立斜視図である。

【図3】図3は本発明の実施形態におけるチップ型LEDの電圧電流特性図である。

【図4】図4は本発明の複数のLED素子をマウントしたチップ型LEDの斜視図である。

。

【図5】図5は本発明の複数のLED素子をマウントしたチップ型LEDの等価回路図で

50

ある。

【図6a】図6aは一般的なPN接合LED素子の断面構造図である。

【図6b】図6bは図6aに示したLED600の等価回路図である。

【図7】図7は一般的なLEDの電圧電流特性図である。

【図8a】図8aは従来技術のLED素子の並列接続回路図である。

【図8b】図8bは従来技術のLED素子のもうひとつの並列接続回路図である。

【符号の説明】

【0036】

100、400 チップ型LED

101、401a、401b、401c、601、D1、D2、D3、Dn LED素子 10

102、402 小型基板

103、403、603 アノード電極

104、404、604 カソード電極

105 ポンディングワイヤ

106、406a、406b、406c ダイボンドペースト材

107 クリア樹脂

【図1a】

【図2】

【図1b】

【図3】

【図4】

【図6 a】

【図6 b】

【図5】

【図7】

【図8 b】

【図8 a】

---

フロントページの続き

(56)参考文献 特開平11-162233(JP,A)

特開平05-061420(JP,A)

特開2005-019838(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64