(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-28362

(P2008-28362A)

(43) 公開日 平成20年2月7日(2008.2.7)

| (51) Int.Cl.             | F 1          |       | テーマコード (参考) |

|--------------------------|--------------|-------|-------------|

| HO 1 L 43/08 (2006.01)   | HO 1 L 43/08 | Z     | 4 M 1 1 9   |

| HO 1 L 21/8246 (2006.01) | HO 1 L 27/10 | 4 4 7 | 5 E O 4 9   |

| HO 1 L 27/105 (2006.01)  | HO 1 L 29/82 | Z     | 5 F O 9 2   |

| HO 1 L 29/82 (2006.01)   | HO 1 F 10/30 |       |             |

| HO 1 F 10/30 (2006.01)   | HO 1 F 10/32 |       |             |

審査請求 有 請求項の数 14 O L (全 25 頁) 最終頁に続く

|              |                              |          |                                       |

|--------------|------------------------------|----------|---------------------------------------|

| (21) 出願番号    | 特願2007-44176 (P2007-44176)   | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (22) 出願日     | 平成19年2月23日 (2007.2.23)       | (74) 代理人 | 100058479<br>弁理士 鈴江 武彦                |

| (31) 優先権主張番号 | 特願2006-172844 (P2006-172844) | (74) 代理人 | 100091351<br>弁理士 河野 哲                 |

| (32) 優先日     | 平成18年6月22日 (2006.6.22)       | (74) 代理人 | 100088683<br>弁理士 中村 誠                 |

| (33) 優先権主張国  | 日本国 (JP)                     | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                |

|              |                              | (74) 代理人 | 100075672<br>弁理士 峰 隆司                 |

|              |                              | (74) 代理人 | 100109830<br>弁理士 福原 淑弘                |

最終頁に続く

(54) 【発明の名称】磁気抵抗素子及び磁気メモリ

## (57) 【要約】

【課題】磁化反転の際の反転電流をより低減する。

【解決手段】磁気抵抗素子は、磁化の方向が固定された第1の磁化参照層11と、スピン偏極した電子の作用により磁化の方向が変化する磁化自由層13と、磁化の方向が固定された第2の磁化参照層15と、第1の磁化参照層11と磁化自由層13との間に設けられた第1の中間層12と、磁化自由層13と第2の磁化参照層15との間に設けられた第2の中間層14とを具備し、磁化自由層13及び第1の磁化参照層11の容易磁化方向は、膜面に対して垂直或いは平行であり、第1の磁化参照層11と第2の磁化参照層15との容易磁化方向は、互いに直交する。

【選択図】 図1

図1

**【特許請求の範囲】****【請求項 1】**

磁化の方向が固定された第1の磁化参照層と、

スピニ偏極した電子の作用により磁化の方向が変化する磁化自由層と、

磁化の方向が固定された第2の磁化参照層と、

前記第1の磁化参照層と前記磁化自由層との間に設けられた第1の中間層と、

前記磁化自由層と前記第2の磁化参照層との間に設けられた第2の中間層と、

を具備し、

前記磁化自由層及び前記第1の磁化参照層の容易磁化方向は、膜面に対して垂直或いは平行であり、

前記第1の磁化参照層と前記第2の磁化参照層との容易磁化方向は、互いに直交することを特徴とする磁気抵抗素子。

**【請求項 2】**

前記磁化自由層及び前記第1の磁化参照層の容易磁化方向は、膜面に対して垂直であり、

前記第2の磁化参照層の容易磁化方向は、膜面に対して平行であることを特徴とする請求項1に記載の磁気抵抗素子。

**【請求項 3】**

前記第1の中間層は、絶縁体或いは半導体からなることを特徴とする請求項1又は2に記載の磁気抵抗素子。

**【請求項 4】**

前記第2の中間層は、導電体からなることを特徴とする請求項1乃至3のいずれかに記載の磁気抵抗素子。

**【請求項 5】**

前記磁化自由層は、順に積層された第1の界面磁性層と主磁性層と第2の界面磁性層とを含み、

前記第1の界面磁性層は、前記第1の中間層に接するように配置され、

前記第2の界面磁性層は、前記第2の中間層に接するように配置されることを特徴とする請求項1乃至4のいずれかに記載の磁気抵抗素子。

**【請求項 6】**

前記第1の磁化参照層は、積層された主磁性層と第3の界面磁性層とを含み、

前記第3の界面磁性層は、前記第1の中間層に接するように配置されることを特徴とする請求項1乃至5のいずれかに記載の磁気抵抗素子。

**【請求項 7】**

前記界面磁性層は、強磁性体からなることを特徴とする請求項5又は6に記載の磁気抵抗素子。

**【請求項 8】**

前記第1及び第2の磁化参照層の少なくとも1つは、順に積層された第1の磁性層と非磁性層と第2の磁性層とを含むことを特徴とする請求項1乃至7のいずれかに記載の磁気抵抗素子。

**【請求項 9】**

前記磁化自由層は、順に積層された第1の磁性層と非磁性層と第2の磁性層とを含むことを特徴とする請求項1乃至7のいずれかに記載の磁気抵抗素子。

**【請求項 10】**

交換結合力により前記第1の磁化参照層の磁化の方向を固定する第1の反強磁性層をさらに具備することを特徴とする請求項1乃至9のいずれかに記載の磁気抵抗素子。

**【請求項 11】**

交換結合力により前記第2の磁化参照層の磁化の方向を固定する第2の反強磁性層をさらに具備することを特徴とする請求項1乃至10のいずれかに記載の磁気抵抗素子。

**【請求項 12】**

10

20

30

40

50

請求項 1 乃至 11 のいずれかに記載の磁気抵抗素子と、この磁気抵抗素子に対して通電を行う第 1 及び第 2 の電極とを含むメモリセルを具備することを特徴とする磁気メモリ。

### 【請求項 13】

前記第 1 及び第 2 の電極に電気的に接続され、かつ前記磁気抵抗素子に双方向に電流を供給する電源回路をさらに具備することを特徴とする請求項 12 に記載の磁気メモリ。

### 【請求項 14】

前記メモリセルは、前記第 2 の電極と前記電源回路との間に電気的に接続された選択トランジスタを含むことを特徴とする請求項 13 に記載の磁気メモリ。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、磁気抵抗素子及び磁気メモリに係り、例えば双方向に電流を供給することで情報を記録することが可能な磁気抵抗素子及びそれを用いた磁気メモリに関する。

#### 【背景技術】

#### 【0002】

近年、新しい原理に基づいて情報を記録する固体メモリが多数提案されているが、中でも、固体磁気メモリとして、トンネル磁気抵抗 (TMR : Tunneling Magnetoresistive) 効果を利用する磁気ランダムアクセスメモリ (MRAM : Magnetoresistive Random Access Memory) が脚光を浴びている。MRAM は、データを MTJ (Magnetic Tunnel Junction) 素子の磁化状態により記憶する点に特徴を有する。

#### 【0003】

従来型の配線電流による磁場で書き込みを行う MRAM においては、MTJ 素子サイズを縮小すると保持力  $H_c$  が大きくなるために、書き込みに必要な電流が大きくなる傾向がある。実際には、256 M bits 以上の大容量を有する MRAM を作製するには、チップサイズの縮小が必要であり、それを実現するためにはチップ内におけるセルアレイ占有率を上げ、MTJ 素子サイズの縮小を抑えつつ、書き込み電流の  $\mu A$  レベルへの低減が必要である。MTJ 素子サイズの縮小と書き込み電流の低減は、相反的な関係にあり、従来型 MRAM では、256 M bits を超えるような大容量化に向けたセルサイズの微細化と低電流化の両立は困難である。

#### 【0004】

このような課題を克服する書き込み方式としてスピン角運動量移動 (SMT : Spin Momentum Transfer) 書き込み方式を用いた MRAM が提案されている（例えば、特許文献 1、非特許文献 1～2）。スピン角運動量移動（以下、スピン注入と称する）磁化反転では、磁化反転に必要な反転電流  $I_c$  は、電流密度  $J_c$  で規定される。従って、素子面積が小さくなれば、スピン注入により磁化反転するための反転電流  $I_c$  も小さくなる。

#### 【0005】

先に述べた従来型の磁場書き込み方式に比べると、電流密度を一定にして書き込む場合、MTJ 素子サイズが小さくなれば書き込み電流も小さくなるために、スケーラビリティ性に優れることが期待される。しかしながら、現状のスピン注入 MRAM においては、その磁化反転に必要な電流密度  $J_c$  は  $10 \text{ mA/cm}^2$  以上と非常に大きく、 $100 \text{ nA/m}^2$  サイズの MTJ 素子を用いた場合でも、書き込み電流としては  $1 \text{ mA}$  程度必要となる。

#### 【0006】

これは、スピン注入磁化反転方式の場合、双方向の通電が必要となり、通電方向によりスピン注入効率が異なることに起因している。すなわち、スピン注入磁化反転カーブは非対称となる。これは、磁化自由層（以下、フリー層と称する）と磁化参照層（以下、ピン層と称する）との磁化配列が平行から反平行になるようにフリー層の磁化の方向を反転させる場合の電流は、反平行から平行に反転させる場合に比べて 2 倍程度必要となる。

#### 【0007】

この非対称性に伴う問題として、トンネル磁気抵抗 (TMR) 効果膜を用いる場合、フリー層とピン層との磁化配列を反平行から平行に反転させるために通電して書き込む場合

10

20

30

40

50

は、電流閾値が小さく問題がない。しかし、フリー層とピン層との磁化配列を平行から反平行に反転させるために通電して書き込む場合には、大きな書き込み電流が原因となり、一定の電流密度  $I_{a-ap}$  で書き込むとすると、TMR効果に見合った分だけ反平行配列時の素子抵抗  $R_{ap}$  が上昇することになり、結果的に、書き込み電圧  $V_{p-ap}$  は上昇する。

#### 【0008】

従って、トンネルバリア層の耐圧が十分高くない場合、反平行磁化配列になる前に、トンネルバリア層の破壊電圧  $V_{bd}$  に到達してしまい、トンネルバリア層が絶縁破壊するという課題を有している。また、たとえ絶縁破壊しなくとも、高電圧下での動作信頼性が確保されないという問題がある。

10

#### 【特許文献1】米国特許第6,256,223号明細書

【非特許文献1】C. Slonczewski, "Current-driven excitation of magnetic multilayers", JOURNAL OF MAGNETISM AND MAGNETIC MATERIALS, VOLUME 159, 1996, pp.L1-L7

【非特許文献2】L. Berger, "Emission of spin waves by a magnetic multilayer traversed by a current", PHYSICAL REVIEW B, VOLUME 54, NUMBER 13, 1996, pp.9353-9358

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

本発明は、上記のような事情に鑑みてなされたもので、磁化反転の際の反転電流をより低減することが可能な磁気抵抗素子及びそれを用いた磁気メモリを提供することを目的とする。

30

#### 【課題を解決するための手段】

#### 【0010】

本発明の第1の視点に係る磁気抵抗素子は、磁化の方向が固定された第1の磁化参照層と、スピン偏極した電子の作用により磁化の方向が変化する磁化自由層と、磁化の方向が固定された第2の磁化参照層と、前記第1の磁化参照層と前記磁化自由層との間に設けられた第1の中間層と、前記磁化自由層と前記第2の磁化参照層との間に設けられた第2の中間層と、を具備し、前記磁化自由層及び前記第1の磁化参照層の容易磁化方向は、膜面に対して垂直或いは平行であり、前記第1の磁化参照層と前記第2の磁化参照層との容易磁化方向は、互いに直交することを特徴とする。

30

#### 【0011】

本発明の第2の視点に係る磁気メモリは、上記第1の視点に係る磁気抵抗素子と、この磁気抵抗素子に対して通電を行う第1及び第2の電極とを含むメモリセルを具備することを特徴とする。

40

#### 【発明の効果】

#### 【0012】

本発明によれば、磁化反転の際の反転電流をより低減することが可能な磁気抵抗素子及びそれを用いた磁気メモリを提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、本発明の実施の形態について図面を参照して説明する。なお、以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

#### 【0014】

##### (第1の実施形態)

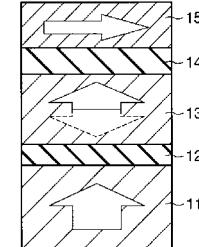

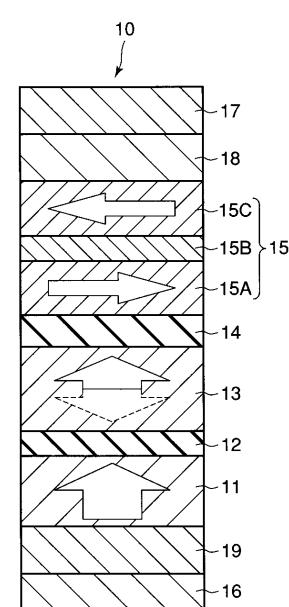

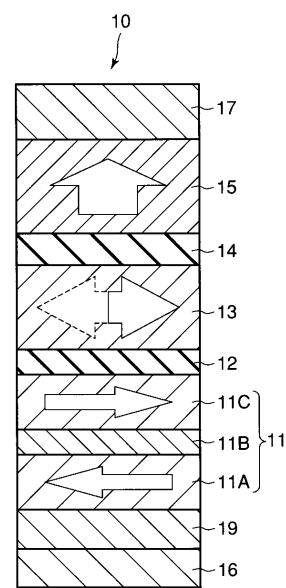

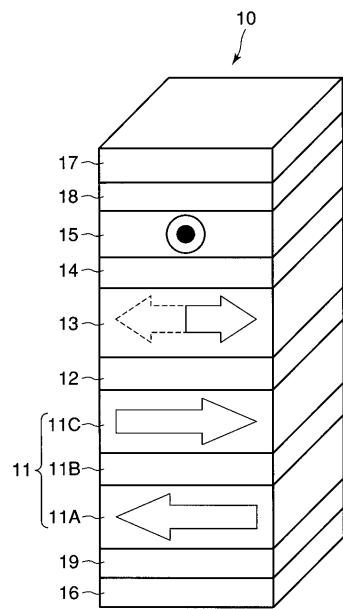

図1は、本発明の第1の実施形態に係るMTJ素子10の構成を示す断面図である。図1は、本実施形態のMTJ素子10の基本構成を示している。なお、図中の矢印は、磁化の方向を示している。

#### 【0015】

50

M T J 素子 1 0 は、第 1 の磁化参照層（ピン層）1 1、第 1 の中間層 1 2、磁化自由層（フリー層）1 3、第 2 の中間層 1 4、第 2 の磁化参照層 1 5 が順に積層された積層構造を有している。なお、この基本構成は、積層順序が逆転しても構わない。

#### 【0 0 1 6】

ピン層 1 1 とピン層 1 5 とは、磁化（或いはスピン）の方向が固着されている。フリー層 1 3 は、磁化の方向が変化（反転）する。また、ピン層 1 1 及びフリー層 1 3 の容易磁化方向は膜面（或いは積層面）に対して垂直であり（以下、垂直磁化と称する）、ピン層 1 5 の容易磁化方向は膜面に対して平行である（以下、面内磁化と称する）。すなわち、ピン層 1 1 とピン層 1 5 とは、容易磁化方向が互いに直交している。

#### 【0 0 1 7】

なお、容易磁化方向とは、あるマクロなサイズの強磁性体を想定して、外部磁界のない状態で自発磁化がその方向を向くと最も内部エネルギーが低くなる方向である。困難磁化方向とは、あるマクロなサイズの強磁性体を想定して、外部磁界のない状態で自発磁化がその方向を向くと最も内部エネルギーが大きくなる方向である。

#### 【0 0 1 8】

本実施形態では、フリー層 1 3 として垂直磁化膜を用いている。フリー層 1 3 に垂直磁化膜を用いることにより、M T J 素子サイズのアスペクト比  $A_r$ （素子の短辺長と長辺長との比、すなわち、 $A_r = \text{長辺長} / \text{短辺長}$ ）を 1 に設計することが可能となる。これは、面内磁化膜の場合は、熱的に安定するのに必要な異方性磁界（ $H_k$ ）は形状磁気異方性エネルギーにより賄われるために、M T J 素子のアスペクト比が 1 より大きくなる。これに対して、垂直磁化膜の場合は、熱的に安定するのに必要な異方性磁界（ $H_k$ ）は結晶磁気異方性エネルギーにより賄われるために、この異方性磁界（ $H_k$ ）は M T J 素子のアスペクト比に依存しないからである。

#### 【0 0 1 9】

この結果、M T J 素子サイズを微細化することが可能となる。この場合、スピン注入による磁化反転に必要な電流密度  $J_c$  が同じ T M R 膜を用いたならば、同じ M T J 素子幅を有する面内磁化膜と垂直磁化膜とでは、スピン注入反転電流  $I_c$  は、垂直磁化膜の方がアスペクト比  $A_r$  が小さくなるので低減される。

#### 【0 0 2 0】

このように構成された M T J 素子 1 0 において、データの書き込みは、以下のように行われる。なお、本実施形態において、電流は、電子の流れをいうものとする。先ず、M T J 素子 1 0 は、膜面（或いは積層面）に垂直な方向において、双方向に電流通電される。

#### 【0 0 2 1】

これにより、フリー層 1 3 に、マジョリティとマイノリティに偏極した電子スピンが供給される。そして、マジョリティな電子スピンのスピン角運動量がフリー層 1 3 に移動することにより、スピントルクがフリー層 1 3 に印加され、フリー層 1 3 の磁化回転を誘起する。スピントルクは、ピン層とフリー層との磁化方向の単位ベクトルの外積で表されるので、2 つの直交するピン層の両方からフリー層にスピントルクを印加できる。これにより、スピン注入による磁化反転電流を低減できる。

#### 【0 0 2 2】

具体的には、ピン層 1 1 側から電子（すなわち、ピン層 1 1 からフリー層 1 3 へ向かう電子）を供給した場合、ピン層 1 1 の容易磁化方向と同じ方向にスピン偏極された電子と、ピン層 1 5 により反射されることでピン層 1 5 の容易磁化方向と反対方向にスpin偏極された電子とがフリー層 1 3 に注入される。この場合、フリー層 1 3 の磁化の方向は、ピン層 1 1 の容易磁化方向と同じ方向に揃えられる。これにより、ピン層 1 1 とフリー層 1 3 との磁化の方向が平行配列となる。この平行配列のときは M T J 素子 1 0 の抵抗値は最も小さくなり、この場合をデータ“0”と規定する。

#### 【0 0 2 3】

一方、ピン層 1 5 側から電子（すなわち、ピン層 1 5 からフリー層 1 3 へ向かう電子）を供給した場合、ピン層 1 5 の容易磁化方向と同じ方向にスpin偏極された電子と、ピン

10

20

30

40

50

層 1 1 により反射されることでピン層 1 1 の容易磁化方向と反対方向にスピン偏極された電子とがフリー層 1 3 に注入される。この場合、フリー層 1 3 の磁化の方向は、ピン層 1 1 の容易磁化方向と反対方向に揃えられる。これにより、ピン層 1 1 とフリー層 1 3 との磁化の方向が反平行配列となる。この反平行配列のときは M T J 素子 1 0 の抵抗値は最も大きくなり、この場合をデータ“1”と規定する。

#### 【 0 0 2 4 】

次に、データの読み出しが、以下のように行われる。M T J 素子 1 0 に読み出し電流を流し、M T J 素子 1 0 の抵抗値の変化を検出する。この読み出し電流は、書き込み電流よりも小さい値に設定される。

#### 【 0 0 2 5 】

ここで、フリー層 1 3 の容易磁化方向は膜面に対して垂直であるので、磁化配列が平行となるピン層 1 1 との間では中間層 1 2 を介して磁気抵抗効果が発現するが、磁化配列が垂直となるピン層 1 5 との間では中間層 1 4 を介した磁気抵抗効果は発現しない。これは、大きなメリットであり、デュアルピン層構造（すなわち、フリー層の両側にそれぞれ中間層を介して 2 つのピン層が配置される構造）を有する磁気抵抗効果素子で問題であった 2 つ目のピン層による読み出し出力の劣化を回避することが可能となる。

#### 【 0 0 2 6 】

すなわち、本実施形態の M T J 素子 1 0 においては、2 つのピン層（ピン層 1 1 とピン層 1 5）の磁化の方向が直交している。このため、中間層 1 2 及び中間層 1 4 の両方で同じ材料、例えば、M g O（酸化マグネシウム）、A l O<sub>x</sub>（酸化アルミニウム）などの絶縁体を用いた場合、2 つのピン層によって高いスピン注入効率が得られると同時に、磁気抵抗効果が一方の中間層のみで発現するという効果を有している。

#### 【 0 0 2 7 】

よって、従来のデュアルピン層構造においては、高いスピン注入効率は得られるものの、中間層 1 2 及び中間層 1 4 の両方で互いに相反な磁気抵抗効果が発現するために、読み出し時に必要な T M R 比を下げてしまうという問題が生じていたが、本実施形態では、この問題を回避することができる。

#### 【 0 0 2 8 】

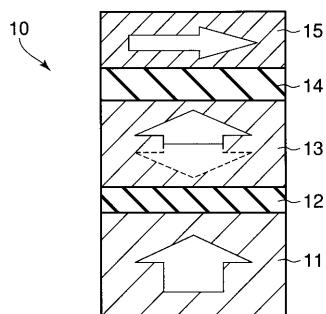

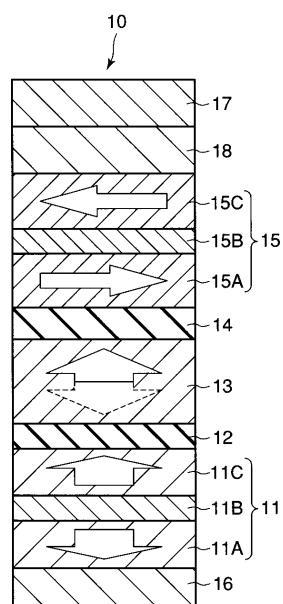

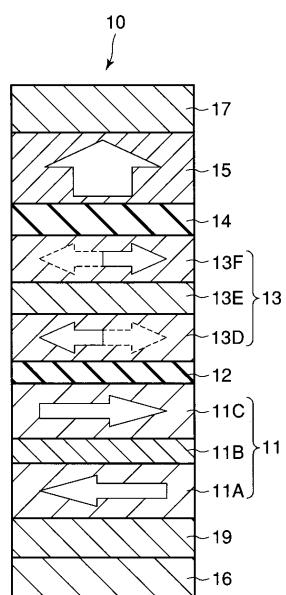

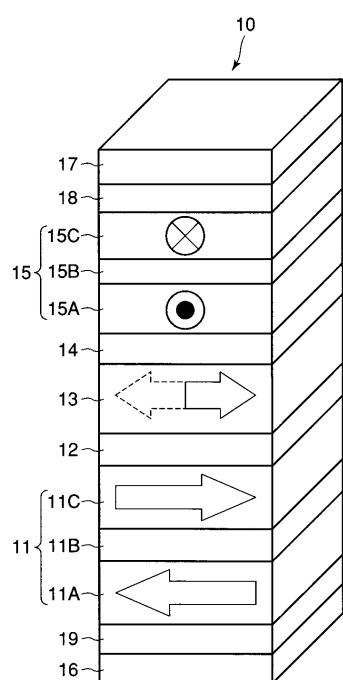

次に、本実施形態の M T J 素子 1 0 のより詳細な具体例について説明する。図 2 は、M T J 素子 1 0 の具体例を示す断面図である。例えば、平面形状において、フリー層 1 3 のアスペクト比は、ほぼ 1 に設定される。

#### 【 0 0 2 9 】

基板（図示せず）側の最下層には、基本構成の結晶配向性或いは結晶性を制御するための下地層 1 6 が設けられている。この下地層 1 6 には、例えば非磁性金属層が用いられる。最上層には、基本構成を酸化及び腐食などの劣化から保護するためのキャップ層 1 7 が設けられている。キャップ層 1 7 には、例えば非磁性金属層が用いられる。

#### 【 0 0 3 0 】

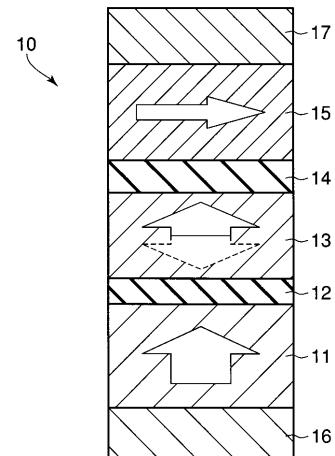

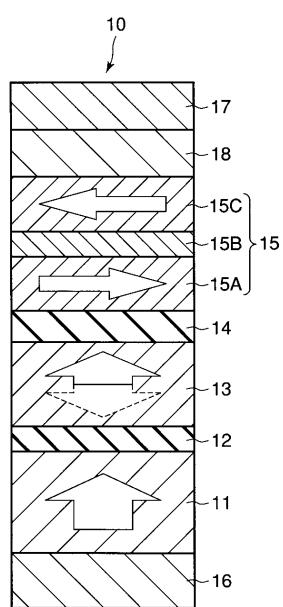

図 3 は、ピン層 1 5 の他の構成を示す断面図である。ピン層 1 5 の容易磁化方向は、膜面に対して平行である。ピン層 1 5 は、ピン層 1 5 C / 中間層 1 5 B / ピン層 1 5 A の積層構造を有している。さらに、ピン層 1 5 C 上（ピン層 1 5 とキャップ層 1 7 の間）には、ピン層 1 5 C と接するように、反強磁性層 1 8 が設けられている。ピン層 1 5 C は、反強磁性層 1 8 と交換結合することで、膜面に対して平行に磁化の方向が固着されている。

#### 【 0 0 3 1 】

ピン層 1 5 A 及びピン層 1 5 C の容易磁化方向は、膜面に対して平行である。また、ピン層 1 5 A とピン層 1 5 C との磁化の方向は互いに反平行（反対方向）に設定され、ピン層 1 5 A とピン層 1 5 C とは中間層 1 5 B を挟んで反強磁性結合している。中間層を介して互いの磁化の方向が反平行である第 1 の磁性層 / 中間層（非磁性層）/ 第 2 の磁性層の積層構造をシンセティックアンチフェロ（S A F : Synthetic Anti-Ferromagnet）構造という。この S A F 構造を用いることで、ピン層 1 5 の磁化固着力が増強され、外部磁場に

対する耐性及び熱的な安定性を向上させることができる。具体的には、ピン層15の磁化固着力の温度依存性が向上する。

#### 【0032】

S A F構造において、第1の磁性層（ピン層15Cに対応する）の飽和磁化をMs1、膜厚をt1、第2の磁性層（ピン層15Aに対応する）の飽和磁化をMs2、膜厚をt2とすると、Ms1・t1 Ms2・t2に設定することで、ピン層15の見かけ上の飽和磁化と磁性層膜厚との積Ms・tをほぼゼロとすることが可能となる。これにより、ピン層15は、外部磁場に反応しにくくなり、さらに外部磁場耐性を向上させることができる。

#### 【0033】

S A F構造における中間層15Bには、Ru（ルテニウム）やOs（オスミウム）などの金属材料が用いられ、その膜厚は3nm以下に設定される。これは、中間層15Bを介して十分強い反強磁性結合を得るためにある。このような中間層15Bを用いることで、ピン層15の磁化固着力が増強され、外部磁場に対する耐性及び熱的な安定性が向上する。

#### 【0034】

図4は、ピン層11の他の構成を示す断面図である。ピン層11の下（ピン層11と下地層16との間）には、ピン層11と接するように、反強磁性層19が設けられている。ピン層11は、反強磁性層19と交換結合することで、膜面に対して垂直に磁化の方向が固着されている。この構造を用いることで、ピン層11の磁化固着力が増強され、外部磁場に対する耐性及び熱的な安定性が向上する。

#### 【0035】

図5は、ピン層11の他の構成を示す断面図である。ピン層11は、ピン層11C / 中間層11B / ピン層11Aの積層構造を有している。すなわち、ピン層11は、S A F構造を有している。

#### 【0036】

ピン層11A及びピン層11Cの容易磁化方向は、膜面に対して垂直である。また、ピン層11Aとピン層11Cとの磁化の方向は互いに反平行に設定され、ピン層11Aとピン層11Cとは中間層11Bを挟んで反強磁性結合している。このS A F構造を用いることで、ピン層11の磁化固着力が増強され、外部磁場に対する耐性及び熱的な安定性が向上する。なお、本構成において、ピン層11Aに接するようにピン層11Aの下に反強磁性層が設けられ、ピン層11Aと反強磁性層とが交換結合していても構わない。

#### 【0037】

図6は、フリー層13及びピン層11の他の構成を示す断面図である。フリー層13は、界面フリー層13C / フリー層13B / 界面フリー層13Aの積層構造を有している。このように、フリー層13Bと中間層12との間、或いは、フリー層13Bと中間層14との間に強磁性体からなる界面フリー層が挿入されることが好ましい。

#### 【0038】

また、図6に示すように、ピン層11は、界面ピン層11E / ピン層11Dの積層構造を有している。このように、ピン層11Dと中間層12との間に強磁性体からなる界面ピン層11Eが挿入されることが好ましい。

#### 【0039】

界面ピン層及び界面フリー層は、磁気抵抗効果を増大させる効果があり、さらには、スピン注入書き込み時に書き込み電流を低減する効果がある。さらに、磁気抵抗効果を増大させる界面層には、その材料自身のバルク的な分極率が大きいことが望ましく、さらには、中間層との界面分極率が増大されるように材料を選択することが好ましい。

#### 【0040】

次に、MTJ素子10を構成する各層の材料について説明する。

#### 【0041】

[1] 中間層12及び中間層14に用いられる材料

10

20

30

40

50

本実施形態のMTJ素子10においては、中間層12には、絶縁体或いは半導体が用いられる。この場合、フリー層13／中間層12／ピン層11の構成部分でトンネル磁気抵抗効果が発現する。従って、読み出し時は、ピン層11及びフリー層13の磁化の方向が平行或いは反平行になることで、MTJ素子10の抵抗値が低抵抗或いは高抵抗となり、それぞれの状態をデータ“0”或いはデータ“1”と判別する。

#### 【0042】

一方で、ピン層15／中間層14／フリー層13の構成部分では、フリー層13及びピン層15の磁化の方向が直交しているためにトンネル磁気抵抗効果は発現しない。従って、中間層14には、金属導電体、絶縁体或いは半導体のどれを用いてもよい。但し、絶縁体及び半導体を用いた場合は、MTJ素子の抵抗値が上昇するので、金属導電体を用いることが好ましい。10

#### 【0043】

ここで、中間層14に用いられる金属導電体としては、Cu(銅)、Al(アルミニウム)、Ag(銀)及びAu(金)などが好ましい。さらには、局所的に電流密度を高めた電流集中効果を用いてスピノ注入効率を向上させるために、MgO-Cu、Al<sub>x</sub>-Cuなどの導電性金属相と絶縁相との混晶構造材料を用いることもフリー層の磁化反転電流を低減する効果がある。

#### 【0044】

中間層12及び中間層14の膜厚はそれぞれ、トンネル磁気抵抗効果を利用する場合には、3nm以下となるように設定される。これは、情報の書き込み時に $1 \times 10^5 \sim 1 \times 10^7 \text{ A/cm}^2$ 程度のトンネル電流を流す必要があるため、MTJ素子の抵抗×面積(RA : resistance and area product)を $100 \mu\text{m}^2$ 以下程度に小さくする必要があるからである。20

#### 【0045】

中間層12及び中間層14に用いられる絶縁体としては、Al<sub>2</sub>O<sub>3</sub>(酸化アルミニウム)、MgO(酸化マグネシウム)、CaO(酸化カルシウム)、SrO(酸化ストロンチウム)、TiO(酸化チタン)、EuO(酸化ユーロビウム)、ZrO(酸化ジルコニウム)及びHfO(酸化ハフニウム)などの酸化物があげられる。また、半導体としては、Ge(ゲルマニウム)、Si(シリコン)、GaAs(ガリウムヒ素)及びInAs(インジウムヒ素)などの化合物半導体、TiO<sub>2</sub>(酸化チタン)などの酸化物半導体があげられる。MgO、CaO、SrO、TiO、及びEuOは、NaCl構造を有する。30

#### 【0046】

この中でも、NaCl構造を有するMgOは、中間層12としては好ましい材料である。これは、MgOを用いた場合が最もTMR比が大きくなるからである。MgOを用いた場合、MTJ素子のRAが $5 \mu\text{m}^2$ 以上 $1000 \mu\text{m}^2$ 以下の範囲内で100%以上のTMR比を得ることが可能である。このMgOはNaCl構造を有しており、TMR比の観点から結晶配向性としては(100)面配向が最も好ましい。また、MgO層形成時に、MgO上部或いは下部には、1nm以下のMg層を挿入することで、TMR比をさらに向上させることができる。

#### 【0047】

MgO層は、MgOターゲットを用いて希ガス(Ar(アルゴン)、Ne(ネオン)、Kr(クリプトン)或いはXe(キセノン))でのスパッタ法により形成する、或いは、Mgターゲットを用いたO<sub>2</sub>雰囲気中の酸化反応性スパッタ法により形成する。また、Mg層を成膜した後に、酸素ラジカル、酸素イオン或いはオゾンなどにより酸化することでも形成可能である。さらに、MgOを用いた分子線エピタキシー(MBE : Molecular Beam Epitaxy)法或いは電子ビーム蒸着(electron beam evaporation)法によりエピタキシャル成長させることでも形成可能である。40

#### 【0048】

ここで、大きいTMR比を得るためにMgOの配向度の向上が必要である。MgOの面配向に基づいて、選択すべき下地層となる磁性層の配向性が決定される。MgOは、50

(100)面配向が好ましい。MgOを(100)面優先配向させるためには、その下地層(フリー層、ピン層、界面フリー層或いは界面ピン層など)は、BCC(Body-Centred Cubic)構造(100)配向面、FCC(Face-Centered Cubic)構造(100)配向面、或いは、アモルファス構造であることが好ましい。

#### 【0049】

BCC構造の材料としては、BCC-Fe<sub>100-x</sub>Co<sub>x</sub>(0×70at%(原子)%), BCC構造上にエピタキシャル成長させた1nm以下のBCC-Coなどがあげられる。或いは、BCC-Fe<sub>100-x</sub>(CoNi)<sub>x</sub>(0×70at%)などを用いてもよい。この場合、10at%以下の希薄Ni添加により10~20%のTMR比の上昇効果が得られる。アモルファス材料としては、Co(コバルト)-Fe(鉄)-B(ホウ素)合金、Fe-Co-Zr合金などがあげられる。10

#### 【0050】

##### [2] 垂直磁化フリー層及び垂直磁化ピン層に用いられる磁性材料

本実施形態においては、フリー層13及びピン層11に垂直磁化膜が用いられる。面内磁化フリー層を用いた場合、スイッチング磁界はMTJ素子のサイズに強く依存するが、垂直磁化フリー層を用いることにより、MTJ素子サイズの依存性が小さくなる。

#### 【0051】

すなわち、面内磁化の場合、飽和磁化を利用した形状磁気異方性エネルギーにより磁化の安定性を維持させるため、素子形状及び素子サイズに依存してスイッチング磁界が変化する。一方、垂直磁化の場合、飽和磁化を小さくし、素子形状及び素子サイズに依存しない結晶磁気異方性エネルギーにより磁化の安定性を維持するために、素子形状及び素子サイズに依存してスイッチング磁界が変わることが小さくなる。従って、垂直磁化フリー層を用いることで、MTJ素子を小さくするとMTJ素子のスイッチング磁界が大きくなるという面内磁化膜を用いたMTJ素子の問題が解決され、MTJ素子の微細化には好ましい。20

#### 【0052】

本実施形態のMTJ素子10に用いられる垂直磁化膜としては、Fe(鉄)、Co(コバルト)、Ni(ニッケル)及びMn(マンガン)のうち少なくとも1種類以上と、Pt(白金)、Pd(パラジウム)、Ir(イリジウム)、Rh(ロジウム)、Os(オスミウム)、Au(金)、Ag(銀)、Cu(銅)、及びCr(クロム)のうち少なくとも1種類以上とを含むことを基本とする。さらには、飽和磁化の調整、結晶磁気異方性エネルギーの制御、結晶粒径及び結晶粒間結合の調整のために、B(ホウ素)、C(炭素)、Si(シリコン)、Al(アルミニウム)、Mg(マグネシウム)、Ta(タンタル)、Zr(ジルコニウム)、Ti(チタン)、Hf(ハフニウム)、Y(イットリウム)、及び希土類元素から選ばれる少なくとも1種類以上の元素を添加してもよい。これらの元素の添加により、飽和磁化Ms及び結晶磁気異方性エネルギーKuを、垂直磁化を損なわせることなく低下させることが可能となり、結晶粒の分断及び微細化を促進できる。30

#### 【0053】

Coを主成分とする材料として、具体的には、HCP(Hexagonal Closest Packing)構造を有するCo-Cr-Pt合金、Co-Cr-Ta合金、或いはCo-Cr-Pt-Ta合金などがあげられる。これらは、各元素の組成を調整することにより、 $1 \times 10^5$ 以上 $1 \times 10^7$ erg/cc未満の範囲内で結晶磁気異方性エネルギーを調整することが可能である。これらの材料を基板に近い側のピン層に用いる場合、下地層としてHCP構造を有するRuを用いることが好ましい。40

#### 【0054】

Co-Pt合金は、Co<sub>50</sub>Pt<sub>50</sub>(at%)付近の組成域において、L1<sub>0</sub>-CoPt規則合金を形成する。この規則合金は、FCT(Face-Centered Tetragonal)構造を有する。中間層12としてMgO(100)を用いる場合、(001)面配向したFCT-CoPt規則合金は、中間層12との界面ミスフィットも小さくできるので好ましい。また、中間層とフリー層(或いはピン層)との間に界面層を挿入した場合でも、界面層を50

(100)面配向しやすくできる。

#### 【0055】

Feを主成分とする材料として、具体的には、Fe-Pt合金或いはFe-Pd合金があげられる。中でも、Fe-Pt合金は、組成がFe<sub>50</sub>Pt<sub>50</sub>(at%)において規則化し、FCCT構造を基本構造とするL1<sub>0</sub>構造を有する。また、Fe-Pt合金は、組成がFe<sub>75</sub>Pt<sub>25</sub>(at%)において規則化し、FCCT構造を基本構造とするL1<sub>2</sub>構造(Fe<sub>3</sub>Pt構造)を有する。これにより、1×10<sup>7</sup>erg/cc以上の大さな結晶磁気異方性エネルギーを発現することができる。

#### 【0056】

Fe<sub>50</sub>Pt<sub>50</sub>合金は、L1<sub>0</sub>構造に規則化する前は、FCC構造を有する。この場合の結晶磁気異方性エネルギーは、1×10<sup>6</sup>erg/cc程度である。従って、アニール温度、組成の調整、積層構成による規則度の制御、及び添加物の添加により、5×10<sup>5</sup>erg/cc以上5×10<sup>8</sup>erg/cc以下の範囲内で結晶磁気異方性エネルギーを調整することができる。また、飽和磁化も添加前はおよそ800~1100emu/ccであるが、800emu/cc以下に低減することが可能である。これは、フリー層に使う場合において、電流密度Jcの低減という点で好ましい。

10

#### 【0057】

具体的には、L1<sub>0</sub>規則構造を有するFe-Pt合金にCu(銅)、Ti(チタン)、V(バナジウム)、Mn(マンガン)、或いはCr(クロム)などを30at%以下の範囲で添加することで、Fe-Pt合金の飽和磁化(Ms)、及び結晶磁気異方性エネルギー(Ku)を制御することが可能である。また、Vに関しては、スピノ注入磁化反転において重要なダンピング定数(磁化制動定数)を下げる効果があり、反転電流を低減する効果もある。

20

#### 【0058】

L1<sub>0</sub>構造或いはL1<sub>2</sub>構造に規則化したFe-Pt合金はFCCT構造を有し、規則化する前はFCC構造を有する。従って、MgO(100)とは非常に整合性がよい。具体的には、MgO(100)面上に(100)面配向したBCC-Feを成長させ、その上にPt(100)を積層することで、MgO(100)上に(100)面優先配向成長したL1<sub>0</sub>構造或いはL1<sub>2</sub>構造のFe-Pt規則合金を形成することが可能である。また、Fe-Pt規則合金とMgO(100)との間にBCC-Crを形成すると、さらにFe-Pt規則合金の(100)面配向が優先的となり望ましい。

30

#### 【0059】

また、L1<sub>0</sub>構造或いはL1<sub>2</sub>構造のFe-Pt規則合金を形成する場合、[Fe/Pt]<sub>n</sub>(nは1以上の整数)の多層構造を形成すると理想的な規則に近いL1<sub>0</sub>構造或いはL1<sub>2</sub>構造のFe-Pt規則合金を形成できる。この場合、Fe及びPtの膜厚は、0.1nm以上3nm以下となるように設定されることが望ましい。これは、均一な組成状態を作り出すためには必須であり、それにより、L1<sub>0</sub>構造或いはL1<sub>2</sub>構造のFe-Pt合金の規則化の場合、FCC構造からFCCT構造へのマルテンサイト変態(martensitic transformation)を伴うため、この変態が促進されるので重要である。

40

#### 【0060】

また、L1<sub>0</sub>構造或いはL1<sub>2</sub>構造のFe-Pt合金の規則化温度は500度以上と高く、耐熱性に優れている。この点は、後工程でのアニール処理に対する耐性があることとなり、非常に好ましい。また、上述したCuやPdなどの30at%以下の範囲での添加元素により、その規則化温度を低下させることが可能である。

40

#### 【0061】

本実施形態のMTJ素子10に用いられる他の垂直磁化膜としては、Fe、Co、Ni、Mn、Cr及び希土類元素のうち少なくとも1種類以上を含むフェリ磁性体があげられる。希土類元素としては、La(ランタン)、Ce(セリウム)、Pr(プラセオジウム)、Nd(ネオジム)、Pm(プロメチウム)、Sm(サマリウム)、Eu、Gd(ガドリニウム)、Tb(テルビウム)、Dy(ジスプロシウム)、Ho(ホルミウム)、Er

50

(エルビウム)、Tm(ツリウム)、Yb(イッテルビウム)、及びLu(ルテチウム)などがあげられる。

#### 【0062】

希土類元素を含むフェリ磁性体は、アモルファス構造を有する。このフェリ磁性体は、組成の調整により、飽和磁化を400emu/cc以下に低減し、かつ、結晶磁気異方性エネルギーを $1 \times 10^6$ erg/cc以上に向上させることが可能である。

#### 【0063】

さらに、本実施形態のMTJ素子10に用いられる垂直磁化膜としては、金属磁性相と絶縁相との混晶からなる強磁性体を用いてもよい。この場合、金属磁性相は、Fe、Co、Ni、及びMnのうち少なくとも1種類以上と、Pt、Pd、Ir、Rh、Os、Au、Ag、Cu、Cr、Ta、及び希土類元素のうち少なくとも1種類以上とを含む強磁性体から構成される。絶縁相は、B、C、Si、Al、Mg、Ta、Cr、Zr、Ti、Hf、Y、及び希土類元素から選ばれる少なくとも1種類以上の元素を含む酸化物、窒化物、及び酸窒化物から構成される。10

#### 【0064】

金属磁性相と絶縁相との混晶からなる強磁性体は、導電性を有する金属磁性体部と非導電性の絶縁体部とに分離しているために、金属磁性体部に電流が集中して通電面積が小さくなり、局所的な電流密度が上昇する。これにより、実質的に必要となる反転電流が小さくなる効果を有する。20

#### 【0065】

このような効果を得るためには、結晶性を制御する必要がある。2相分離構造としては、グラニュラー(結晶粒分散)型構造、アイランド(島状)型構造、及びコラムナー(柱状)型構造がある。コラムナー型構造の場合は、磁性層中で金属磁性体部が上下に貫通しているので、電流狭窄効果が得られやすい。グラニュラー型構造及びアイランド型構造の場合は、電流はもっともトンネル障壁が小さいパスを通電することとなるので、コラムナー型構造と同様に電流狭窄効果が得られる。20

#### 【0066】

その他、本実施形態のMTJ素子10に用いられる垂直磁化膜としては、Mn系強磁性合金、或いは、Cr系強磁性合金があげられる。Mn系強磁性合金としては、Mn-Al合金、Mn-Au合金、Mn-Zn合金、Mn-Ga合金、Mn-Ir合金、及びMn-Pt<sub>3</sub>合金などがあり、これらは、規則格子を有する特徴がある。また、Cr系磁性合金としては、Cr-Pt<sub>3</sub>合金などがあげられる。これは、L<sub>1</sub><sub>0</sub>規則格子を有し、フェリ磁性体の特性を有する。30

#### 【0067】

##### [3] 面内磁化ピン層に用いられる磁性材料

本実施形態においては、磁化の方向がピン層11に直交しているピン層15には、面内磁化膜が用いられる。

#### 【0068】

本実施形態のMTJ素子10に用いられる面内磁化膜としては、Fe、Co、Ni、Mn、及びCrのうち少なくとも1種類以上を含む強磁性体が用いられる。Fe、Co、及びNiを主成分とする材料として、具体的には、 FCC構造或いはBCC構造を有するFe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>合金(x=0, y=0, z=0, x+y+z=1)があげられる。40

#### 【0069】

ピン層に用いられる材料としては、分極率が大きく、原理的に100%分極率を実現できるハーフメタル的な材料が好ましい。

#### 【0070】

Mnを含む材料としては、Mn系強磁性ホイスラー合金がハーフメタル材料としてあげられる。ここで、Mn系強磁性ホイスラー合金は、A<sub>2</sub>MnXで表される規則格子を有する体心立方晶系(body-centered cubic system)合金である。A元素は、Cu、Au、Pd、Ni、及びCoから選択される材料である。X元素は、Al(アルミニウム)、In50

(インジウム)、Sn(スズ)、Ga(ガリウム)、Ge(ゲルマニウム)、Sb(アンチモン)、及びSi(シリコン)から選択される材料である。ホイスラー合金のうち、BCC構造を有するCo<sub>2</sub>MnAl合金などは、BCC(100)面配向させることにより、MgO(100)との整合性が良好となる。

#### 【0071】

ピン層中の強磁性層の膜厚は、1nm以上が必要である。なぜなら、上記の膜厚未満では、強磁性層が連続膜にならず、磁性層としての特性が十分に発揮されず、十分な磁気抵抗効果比(TMR比或いはGMR(Giant Magnetoresistive)比)が得られない。また、最大膜厚は、3nm以下であることが望ましい。これは、膜厚が3nmを超えると、コヒーレントなスピノの歳差運動長さをはるかに越えてしまうために、スピノ注入磁化反転に必要な電流閾値が大幅に大きくなってしまうからである。

10

#### 【0072】

また、上述した面内磁化ピン層がMgOバリア層の下地層となる場合、組成式Fe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>合金(x=0, y=0, z=0, x+y+z=1)で表される材料において、(100)面配向を有し、BCC構造を有することが好ましい。さらには、組成式Fe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>合金(x=0, y=0, z=0, x+y+z=1)で表される材料にB、C、Nなどを30at%以下の濃度で添加し、アモルファス構造にすることも好ましい。これは、アモルファス構造を有する膜上では、MgO膜は(100)面を優先配向しやすいからである。

#### 【0073】

20

##### [4] 界面フリー層及び界面ピン層に用いられる材料

図6に示した界面ピン層及び界面フリー層(以下、両方を指して界面層)は、磁気抵抗効果を増大させる効果があり、さらには、スピノ注入書き込み時に書き込み電流を低減する効果がある。磁気抵抗効果を増大させる界面層は、その材料自身のバルク的な分極率が大きいことが望ましく、さらには、中間層との界面分極率が増大されるように材料を選択することが好ましい。

#### 【0074】

30

本実施形態のMTJ素子10に用いられる界面層としては、Fe、Co、Ni、Mn、及びCrのうち少なくとも1種類以上を含む強磁性体が用いられる。Fe、Co、及びNiを主成分とする材料として、具体的には、 FCC構造或いはBCC構造を有するFe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>合金(x=0, y=0, z=0, x+y+z=1)があげられる。また、上記のFe-Co-Ni合金の飽和磁化(Ms)を低減するために、(Fe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>)<sub>100-a</sub>X<sub>a</sub>合金(x=0, y=0, z=0, x+y+z=1, a(at%)>0, Xは添加元素)も好ましい。飽和磁化(Ms)を低減することにより、反転電流を大幅に低減することが可能となる。FeCoNiが50at%以上であることが好ましいが、これはx+y+z>50at%である場合、バリア層界面でのFeCoNi磁性層の被覆率が50%以上になるために、TMR現象効果を抑制できるからである。

#### 【0075】

40

BCC構造を崩さずに添加することができ、かつ、飽和磁化(Ms)を低減できる添加物、すなわち、置換型で固溶できる全率固溶体或いはある程度固溶源を有する添加物としては、V(バナジウム)、Nb(ニオブ)、Ta(タンタル)、W(タングステン)、Cr(クロム)、Mo(モリブデン)、Si(シリコン)、Ga(ガリウム)、及びGe(ゲルマニウム)などがあげられる。この中でも、Vは、ダンピング定数(磁化制動定数)を低減する効果もあり有效である。

#### 【0076】

40

また、B、C及びNなどの侵入型元素を添加する、或いは、ほとんど固溶源を持たないZr、Ta、Ti、Hf、Y、及び希土類元素などを添加することにより、結晶構造をアモルファス構造に変えることで飽和磁化(Ms)を低減できる。このような材料として、例えば、アモルファス構造を有する(Fe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>)<sub>100-b</sub>X<sub>b</sub>合金(x=0, y=0, z=0, x+y+z=1, b(at%)>0, XはB、C、N、Zr、Ta、

50

T i、H f、Y、及び希土類元素などの添加元素)があげられる。但し、ある程度のT M R比を得るためにには、部分的に、すなわち、M g Oとの界面において再結晶化を促進させることが重要となる。

#### 【0077】

M nを含む材料としては、M n系強磁性ホイスラー合金があげられる。ここで、M n系強磁性ホイスラー合金は、A<sub>2</sub>M nXで表される規則格子を有する体心立方晶系合金である。A元素は、C u、A u、P d、N i、及びC oから選択される材料である。X元素は、A l、I n、S n、G a、G e、S b、及びS iから選択される材料である。ホイスラーアルミニウムのうち、B C C構造を有するC o<sub>2</sub>M nA l合金などは、B C C(100)面配向させることにより、M g O(100)との整合性が良好となる。M n系ホイスラー合金は、ハーフメタル的な伝導特性を示す場合がある。10

#### 【0078】

また、酸化物材料を用いることもできる。酸化物材料としては、F e<sub>2</sub>O<sub>3</sub>などのハーフメタルなどが界面層として適用可能である。

#### 【0079】

フリー層或いはピン層などの金属層の上に形成される界面層の最小膜厚としては、0.5nm以上が必要であり、絶縁層或いは半導体層上に形成される界面層の最小膜厚としても、0.5nm以上が必要である。なぜなら、上記の膜厚未満では、界面層が連続膜にならず、界面フリー層或いは界面ピン層としての特性が十分に発揮されず、十分な磁気抵抗効果比(T M R比或いはG M R比)が得られない。また、最大膜厚は、5nm以下であることが望ましい。これは、膜厚が5nmを超えると、コヒーレントなスピンの歳差運動長さをはるかに越えてしまうために、スピン注入磁化反転に必要な電流閾値が大幅に大きくなってしまうからである。20

#### 【0080】

以上詳述したように本実施形態によれば、互いに垂直な磁化の方向を有する2つのピン層をデュアルピン層構造で有することにより、フリー層13へのスピン注入効率を向上させることができる。これにより、M T J素子10のスイッチング速度を向上させることができる。さらに、スピン注入効率が向上する結果、磁化反転に必要な書き込み電流を低減することが可能となる。

#### 【0081】

また、フリー層13とピン層11との磁化の方向は互いに平行に設定され、一方、フリー層13とピン層15との磁化の方向は互いに直交するように設定されている。従って、中間層12では磁気抵抗効果が発現するが、中間層14では磁気抵抗効果が発現しない。これにより、情報の読み出し時において、M T J素子10のT M R比をより大きくすることができます。30

#### 【0082】

また、磁気抵抗効果が発現しない中間層14に金属等の導電体を用いることが可能となる。これにより、M T J素子10の抵抗値を低減することができる。

#### 【0083】

また、フリー層13に垂直磁化膜を用いている。すなわち、フリー層13が熱的に安定するのに必要な異方性磁界(H k)は、結晶磁気異方性エネルギーにより賄われる。これにより、フリー層13のアスペクト比を小さくできるため、M T J素子サイズを微細化することが可能である。40

#### 【0084】

また、フリー層13と中間層12、或いは、フリー層13と中間層14との間に強磁性体からなる界面フリー層を挿入している。さらに、ピン層11と中間層12との間に強磁性体からなる界面ピン層を挿入している。これらの界面フリー層及び界面ピン層に材料自身のバルク的な分極率が大きい材料を用いることで、磁気抵抗効果を増大させることができ、さらには、書き込み時の書き込み電流を低減することができる。

#### 【0085】

10

20

30

40

50

M T J 素子に用いられるT M R 膜のより具体的な積層構造としては、下記のようなものがあげられる。なお、実施例1乃至実施例3において、各層の後に記載した数値は、膜厚を示している。

#### 【0086】

(実施例1)

T a 5 / P t M n 1 5 / C o F e 2 . 5 / R u 0 . 8 5 / C o F e 2 . 5 / C u 3 (中間層14) / C o F e B 0 . 5 / F e P t (L1<sub>0</sub>)2 / F e 0 . 5 / M g O 0 . 7 5 (中間層12) / C o F e B 1 / F e P t (L1<sub>0</sub>)10 / P t 5 / C r 2 0 / M g O 2 / C o F e B 2 / T a 5 // 基板

(実施例2)

T a 5 / I r M n 1 0 / C o F e 2 . 5 / R u 0 . 8 5 / C o F e 2 . 5 / C u 3 (中間層14) / C o F e B 0 . 5 / C o F e T b 3 / C o F e B 0 . 7 5 / M g O 0 . 7 5 (中間層12) / C o F e B 2 / C o F e T b 3 0 / R u 5 / T a 5 // 基板

(実施例3)

T a 5 / I r M n 1 0 / C o F e 2 . 5 / R u 0 . 8 5 / C o F e 2 . 5 / C u 3 (中間層14) / C o F e B 0 . 5 / C o P t 3 / C o F e B 0 . 5 / M g O 0 . 7 5 (中間層12) / C o F e B 2 / C o P t 2 0 / R u 1 0 / T a 5 // 基板

実施例1及び実施例3においては、面内方向磁場中かつ真空中で270°のアニールを施した。これらのM T J膜を用いて、四端子測定が可能なM T J素子を作成し、スピニ注入磁化反転に必要な電流密度J<sub>c</sub>を評価した。測定はパルス幅が1m秒で行った。M T J素子サイズはおおよそ100nm×100nmであり、アスペクト比は1である。また、M T J素子の抵抗×面積(RA)がそれぞれ15μm<sup>2</sup>になるように、M g O膜厚を調整した。

#### 【0087】

それぞれの実施例において、中間層14の上に面内磁化ピン層がない場合の比較例と比較した結果、電流密度J<sub>c</sub>はそれぞれ、10%から30%程度の低減効果が得られた。また、それぞれの実施例において中間層14にC uを用いたため、抵抗×面積(RA)の上昇はほとんど見られず、T M R比の大きな劣化も測定されなかった。

#### 【0088】

(第2の実施形態)

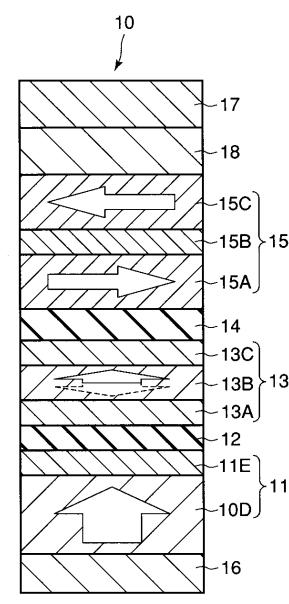

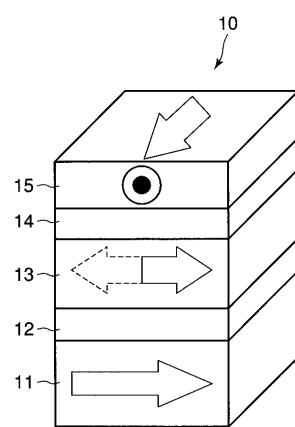

第2の実施形態は、フリー層13に面内磁化膜を用いてM T J素子10を構成するよう正在する。図7は、本発明の第2の実施形態に係るM T J素子10の構成を示す断面図である。図7は、本実施形態のM T J素子10の基本構成を示している。

#### 【0089】

M T J素子10は、第1のピン層11、第1の中間層12、フリー層13、第2の中間層14、第2のピン層15が順に積層された積層構造を有している。なお、この基本構成は、積層順序が逆転していても構わない。

#### 【0090】

ピン層11及びフリー層13の容易磁化方向は膜面に対して平行であり、ピン層15の容易磁化方向は膜面に対して垂直である。すなわち、ピン層11とピン層15とは、容易磁化方向が互いに直交している。従って、磁化配列が平行となるフリー層13とピン層11との間では中間層12を介して磁気抵抗効果が発現するが、磁化配列が垂直となるフリー層13とピン層15との間では中間層14を介した磁気抵抗効果は発現しない。

#### 【0091】

図8は、M T J素子10の具体例を示す断面図である。図7に示した基本構成の最上層及び最下層にそれぞれ、キャップ層17及び下地層16が設けられている。ピン層11は、ピン層11C/中間層11B/ピン層11Aの積層構造を有している。すなわち、ピン層11は、S A F構造を有している。

#### 【0092】

ピン層11A及びピン層11Cの容易磁化方向は、膜面に対して平行である。また、ピ

10

20

30

40

50

ン層 11A とピン層 11C との磁化の方向は互いに反平行に設定され、ピン層 11A とピン層 11C とは中間層 11B を挟んで反強磁性結合している。S A F 構造における中間層には、R u やO s などの金属材料が用いられ、その膜厚は 3 nm 以下に設定される。これは、中間層を介して十分強い反強磁性結合を得るためである。

#### 【0093】

さらに、ピン層 11A の下（ピン層 11A と下地層 16 の間）には、ピン層 11A と接するように、反強磁性層 19 が設けられている。ピン層 11A は、反強磁性層 19 と交換結合することで、膜面に対して平行に磁化の方向が固着されている。

#### 【0094】

この構造を用いることで、ピン層 11 の磁化固着力が増強され、外部磁場に対する耐性及び熱的な安定性を向上させることができる。また、外部磁場に対する耐性を向上させるために、ピン層 11 の見かけ上の飽和磁化と磁性層膜厚との積  $M_s \cdot t$  をほぼゼロとなるように設定することが好ましい。

10

#### 【0095】

図 9 は、フリー層 13 の他の構成を示す断面図である。フリー層 13 は、フリー層 13F / 中間層 13E / フリー層 13D の積層構造を有している。すなわち、フリー層 13 は、S A F 構造を有している。フリー層 13D 及びフリー層 13F の容易磁化方向は、膜面に対して平行である。また、フリー層 13D とフリー層 13F との磁化の方向は互いに反平行に設定され、フリー層 13D とフリー層 13F とは中間層 13E を挟んで反強磁性結合している。S A F フリー層の場合、磁化反転時の歳差運動を促進する効果がある。S A F フリー層では、見かけ上のネット  $M_s$  はゼロに設定できるために、膜面垂直方向において、反磁界を抑制できる。従って、フリー層 13 の歳差運動を促進し、スピノ注入磁化反転を低減する効果がある。

20

#### 【0096】

このようにして M T J 素子 10 を構成した場合でも、上記第 1 の実施形態と同様の効果を得ることができます。なお、上記第 1 の実施形態で示したように、フリー層 13 及びピン層 11 に界面層を挿入してもよい。

30

#### 【0097】

さらに、ピン層 15 は、中間層 14 が薄い場合においては、フリー層 13 の磁化反転時の歳差運動を容易にする効果を有する。面内磁化膜におけるスピノ注入磁化反転において、膜面垂直方向の反磁界は磁化の歳差運動を阻害し、スピノ注入磁化反転電流を上昇させる要因となっている。この時の膜面垂直方向における反磁界とは、フリー層 13 の膜面に磁荷が発生することにより生じる。従って、膜面に発生する磁荷をキャンセルすれば、膜面垂直方向の反磁界が低下し、フリー層 13 の磁化は歳差運動をしやすくなる。結果的に、スピノ注入磁化反転電流を低下させることが可能である。

40

#### 【0098】

本実施形態の M T J 素子 10 の場合、中間層 14 を介して形成されているピン層 15 は、垂直磁化であり、膜面に磁荷を出している。従って、フリー層 13 が歳差運動する際には、フリー層 13 の膜面の磁荷をキャンセルする効果が働く。この効果を最大限に発揮するためには、中間層 14 はなるべく薄い方が好ましく、1 nm 以下であることが好ましい。1 nm を超える厚さを有する中間層 14 の場合、ピン層 15 の磁化の影響は距離に反比例するために、かなり部分の漏洩磁界が減衰してしまう。歳差運動を促進する効果だけを得る場合においては、中間層 14 は無い方が良い。ただし、この場合は、垂直磁化膜の部分は、ピン層としての機能が失われ、フリー層 13 の一部として振舞うことになる。すなわち、面内磁化方向と垂直磁化方向の 2 方向の異方性を有するフリー層 13 となる。

#### 【0099】

本実施形態のフリー層 13 には、Fe - Co - Ni 合金が主として用いられる。また、Fe - Co - Ni 合金の飽和磁化 ( $M_s$ ) を低減するために、(Fe<sub>x</sub>Co<sub>y</sub>Ni<sub>z</sub>)<sub>100-a</sub>X<sub>a</sub> 合金 ( $x = 0, y = 0, z = 0, x + y + z = 1, a (at\%) > 0, X$  は添加元素) も好ましい。飽和磁化 ( $M_s$ ) を低減することにより、反転電流を大幅に低減

50

することができる。

#### 【0100】

BCC構造を崩さずに添加することができ、かつ、飽和磁化( $M_s$ )を低減できる添加物、すなわち、置換型で固溶できる全率固溶体或いはある程度固溶源を有する添加物としては、V、Nb、Ta、W、Cr、Mo、Si、Ga及びGeなどがあげられる。この中でも、Vは、ダンピング定数(磁化制動定数)を低減する効果もあり有效である。

#### 【0101】

また、B、C及びNなどの侵入型元素を添加する、或いは、ほとんど固溶源を持たないZr、Ta、Ti、Hf、Y及び希土類元素などを添加することにより、結晶構造をアモルファス構造に変えることで飽和磁化( $M_s$ )を低減できる。このような材料として、例えば、アモルファス構造を有する( $Fe_xCo_yNi_z$ )<sub>100-b</sub>X<sub>b</sub>合金(x=0、y=0、z=0、x+y+z=1、b(at%)>0、XはB、C、N、Zr、Ta、Ti、Hf、Y、及び希土類元素などの添加元素)があげられる。10

#### 【0102】

Mnを含む材料としては、Mn系強磁性ホイスラー合金があげられる。ホイスラー合金は、ハーフメタル的な伝導特性を示す材料である。ここで、Mn系強磁性ホイスラー合金は、A<sub>2</sub>MnXで表される規則格子を有する体心立方晶系(body-centered cubic system)合金である。A元素は、Cu、Au、Pd、Ni、及びCoから選択される材料である。X元素は、Al、In、Sn、Ga、Ge、Sb、及びSiから選択される材料である。ホイスラー合金のうち、BCC構造を有するCo<sub>2</sub>MnAl合金などは、BCC(100)面配向させることにより、MgO(100)との整合性が良好となる。20

#### 【0103】

また、MTJ素子10を構成する他の層の材料についても、上記第1の実施形態で示した材料を用いることができる。

#### 【0104】

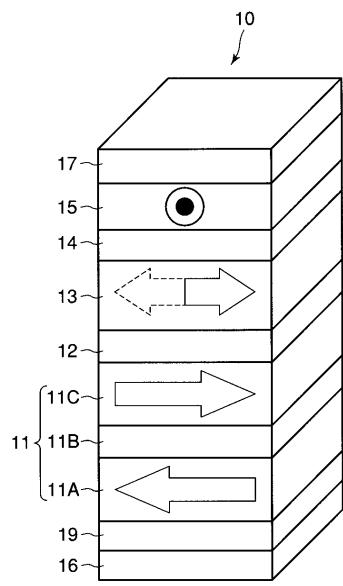

##### (第3の実施形態)

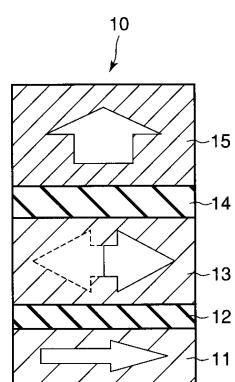

第3の実施形態は、フリー層及び2つのピン層のそれぞれに面内磁化膜を用いて、MTJ素子10を構成するようにしている。図10は、本発明の第3の実施形態に係るMTJ素子10の構成を示す斜視図である。図10は、本実施形態のMTJ素子10の基本構成を示している。30

#### 【0105】

MTJ素子10は、第1のピン層11、第1の中間層12、フリー層13、第2の中間層14、第2のピン層15が順に積層された積層構造を有している。なお、この基本構成は、積層順序が逆転していても構わない。

#### 【0106】

ピン層11、フリー層13、ピン層15の容易磁化方向は、膜面に対して平行である。すなわち、全ての磁性層として面内磁化膜を用いることが可能となり、MTJ素子10を容易に形成することができる。

#### 【0107】

また、ピン層11とフリー層13とは容易磁化方向が平行であり、ピン層11とピン層15とは容易磁化方向が互いに直交している。従って、磁化配列が平行となるフリー層13とピン層11との間では中間層12を介して磁気抵抗効果が発現するが、磁化配列が垂直となるフリー層13とピン層15との間では中間層14を介した磁気抵抗効果は発現しない。40

#### 【0108】

図11は、MTJ素子10の具体例を示す斜視図である。図10に示した基本構成の最上層及び最下層にそれぞれ、キャップ層17及び下地層16が設けられている。ピン層11は、ピン層11C/中間層11B/ピン層11Aの積層構造を有している。すなわち、ピン層11は、SAF構造を有している。ピン層11A及びピン層11Cの容易磁化方向は、膜面に対して平行である。また、ピン層11Aとピン層11Cとの磁化の方向は互いに垂直である。50

に反平行に設定され、ピン層 11A とピン層 11C とは中間層 11B を挟んで反強磁性結合している。

【0109】

さらに、ピン層 11A の下（ピン層 11A と下地層 16との間）には、ピン層 11A と接するように、反強磁性層 19 が設けられている。ピン層 11A は、反強磁性層 19 と交換結合することで、膜面に対して平行に磁化の方向が固着されている。この構造を用いることで、ピン層 11A の磁化固着力が増強され、外部磁場に対する耐性及び熱的な安定性が向上する。

【0110】

また、ピン層 15 は、フリー層 13 と明確な保持力差を設ける必要がある。このため、

10 ピン層 15 としては、面内磁化型硬質磁性層を用いることが好ましい。

【0111】

面内磁化型硬質磁性層の材料としては、Co-Pt 合金、或いは Co-Pt-X 合金（X は、Cr、Ta、Pd、B、Si、Ru から選ばれる少なくとも 1 つ以上の元素）があげられる。また、面内磁化型硬質磁性層を用いた硬質磁性層 / 中間層 / 硬質磁性層の構成を有する SAF 構造も形成可能である。この場合、中間層には Ru 或いは Os が用いられる。

【0112】

図 12 は、ピン層 15 の他の構成を示す斜視図である。ピン層 15 上（ピン層 15 とキャップ層 17 との間）には、ピン層 15 と接するように、反強磁性層 18 が設けられている。ピン層 15 は、反強磁性層 18 と交換結合することで、膜面に対して平行に磁化の方向が固着されている。

20

【0113】

図 13 は、ピン層 15 の他の構成を示す斜視図である。ピン層 15 は、ピン層 15C / 中間層 15B / ピン層 15A の積層構造を有している。すなわち、ピン層 15 は、SAF 構造を有している。ピン層 15A 及びピン層 15C の容易磁化方向は、膜面に対して平行である。また、ピン層 15A とピン層 15C との磁化の方向は互いに反平行に設定され、ピン層 15A とピン層 15C とは中間層 15B を挟んで反強磁性結合している。

【0114】

図 12 および図 13 に示した反強磁性層 19 及び反強磁性層 18 は、強磁性層との結合の臨界温度すなわちブロッキング温度に差をつけることで、アニールシーケンスによりピン層 11 とピン層 15 との容易磁化方向を直交化することが可能となる。より具体的には、反強磁性層 19 には PtMn や NiMn などの高いブロッキング温度を有する材料を行い、反強磁性層 18 には FeMn や IrMn などの比較的低いブロッキング温度を有するものを用いることが好ましい。

30

【0115】

また、フリー層 13 は、強磁性層 / 中間層 / 強磁性層の積層構造、すなわち、SAF 構造を有していても構わない。SAF 構造において、強磁性層同士の磁化の方向は互いに反平行に設定され、中間層を挟んで反強磁性結合している。

【0116】

このようにして MTJ 素子 10 を構成した場合でも、上記第 1 の実施形態と同様の効果を得ることができる。なお、上記第 1 の実施形態で示したように、フリー層 13 及びピン層 11 に界面層を挿入してもよい。また、MTJ 素子 10 を構成する各層の材料については、上記第 1 及び第 2 の実施形態で示した材料を用いることができる。

40

【0117】

（第 4 の実施形態）

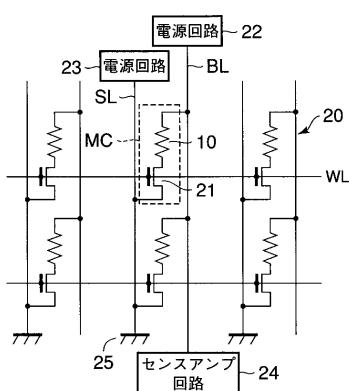

第 4 の実施形態は、前述した MTJ 素子 10 を用いて MRAM を構成した場合の実施例について示している。

【0118】

図 14 は、本発明の第 4 の実施形態に係る MRAM の構成を示す回路図である。MRAM

50

Mは、マトリクス状に配列された複数のメモリセルMCを有するメモリセルアレイ20を備えている。メモリセルアレイ20には、それぞれが列(カラム)方向に延在するよう、複数のピット線BLが配置されている。また、メモリセルアレイ20には、それぞれが行(ロウ)方向に延在するよう、複数のワード線WLが配置されている。

#### 【0119】

ピット線BLとワード線WLとの交差部分には、前述したメモリセルMCが配置されている。各メモリセルMCは、MTJ素子10と選択トランジスタ21により構成されている。MTJ素子10の一端は、ピット線BLに接続されている。MTJ素子10の他端は、選択トランジスタ21のドレインに接続されている。選択トランジスタ21のゲートには、ワード線WLが接続されている。選択トランジスタ21のソースは、ソース線SLに接続されている。10

#### 【0120】

ピット線BLの一端には、電源回路22が接続されている。ピット線BLの他端には、センスアンプ回路24が接続されている。ソース線SLの一端には、電源回路23が接続されている。ソース線SLの他端は、図示しないスイッチ素子を介して電源25に接続されている。

#### 【0121】

電源回路22は、ピット線BLの一端に正の電位を印加する。センスアンプ回路24は、MTJ素子10の抵抗値を検出する他、ピット線BLの他端に例えれば接地電位を印加する。電源回路23は、ソース線SLの一端に、正の電位を印加する。電源25は、この電源25に接続されたスイッチ素子をオンすることにより、ソース線SLの他端に例えれば接地電位を印加する。また、各電源回路は、対応する配線との電気的な接続を制御するスイッチ素子を含んでいる。20

#### 【0122】

メモリセルMCへのデータ書き込みは、以下のように行われる。先ず、データ書き込みを行うメモリセルMCを選択するために、このメモリセルMCに接続されたワード線WLが活性化される。これにより、選択トランジスタ21がターンオンする。

#### 【0123】

ここで、MTJ素子10には、双方向の書き込み電流Iwが供給される。具体的には、MTJ素子10に上から下へ書き込み電流Iwを供給する場合、電源回路22はピット線BLの一端に正の電位を印加し、電源25はこの電源25に対応するスイッチ素子をオンすることによりソース線SLの他端に接地電位を印加する。30

#### 【0124】

また、MTJ素子10に下から上へ書き込み電流Iwを供給する場合、電源回路23はソース線SLの一端に正の電位を印加し、センスアンプ回路24はピット線BLの他端に接地電位を印加する。ここでは、電源25に対応するスイッチ素子はオフされている。このようにして、メモリセルMCにデータ“0”或いはデータ“1”を書き込むことができる。

#### 【0125】

メモリセルMCからのデータ読み出しは、以下のように行われる。先ず、メモリセルMCが選択される。次に、電源回路23及びセンスアンプ回路24により、MTJ素子10には、電源回路23からセンスアンプ回路24へ流れる読み出し電流Irが供給される。そして、センスアンプ回路24は、この読み出し電流Irに基づいて、MTJ素子10の抵抗値を検出する。このようにして、MTJ素子10に記憶された情報を読み出すことができる。40

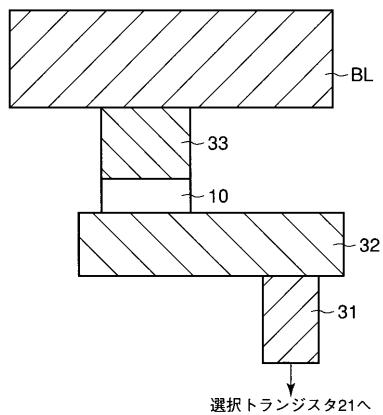

#### 【0126】

次に、MRAMの構造について説明する。図15は、MTJ素子10を中心に示したMRAMの断面図である。MTJ素子10は、シリコンなどからなる半導体基板(図示せず)に形成された選択トランジスタ21の上方に層間絶縁層を介して形成される。

#### 【0127】

10

20

30

40

50

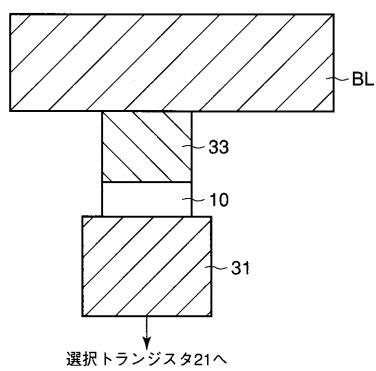

引き出し電極 3 2 上には、MTJ 素子 1 0 が設けられている。引き出し電極 3 2 は、ビアプラグ 3 1 を介して選択トランジスタ 2 1 のドレイン領域に電気的に接続される。MTJ 素子 1 0 上には、導電性のハードマスク 3 3 が設けられている。ハードマスク 3 3 上には、ビット線 BL が設けられている。

【0128】

ビット線 BL、ハードマスク 3 3 及びビアプラグ 3 1 としては、W、A1、Cu 及び AlCu などが用いられる。Cu を用いた金属配線層或いはビアプラグの場合には、Cu ダマシン或いは Cu デュアルダマシンプロセスが用いられる。

【0129】

図 16 は、MTJ 素子 1 0 を中心に示した MRAM の他の構成例である。ビアプラグ 3 1 上には、直接に MTJ 素子 1 0 が設けられている。すなわち、図 16 の MRAM は、図 15 の MRAM と比べて、引き出し電極 3 2 が省略されている。MTJ 素子 1 0 上には、ハードマスク 3 3 が設けられている。ハードマスク 3 3 上には、ビット線 BL が設けられている。

【0130】

MTJ 素子 1 0 は、図 15 に示されるように引き出し電極 3 2 によりビアプラグ 3 1 と電気的に接続される場合と、図 16 に示されるように MTJ 素子 1 0 がビアプラグ 3 1 上に直接形成される場合とがある。図 16 の構成を用いる場合、ビアサイズよりも MTJ 素子サイズが小さい方が好ましい。

【0131】

リソグラフィやエッチング技術等によって決まる最小加工寸法を F (Minimum Feature Size) とすると、図 15 のレイアウトを用いた場合、最小セルサイズは  $8F^2$  である。これに対して、図 16 のレイアウトを用いた場合、最小セルサイズが  $4F^2$  にまで縮小することが可能となる。

【0132】

このように構成された MRAM において、MTJ 素子 1 0 に情報を書き込む際の書き込み速度を向上させることができる。具体的には、書き込み速度としては、数ナノ秒から数マイクロ秒までのパルス幅を有する電流でスピン注入書き込みを行うことが可能となる。

【0133】

なお、読み出し時に MTJ 素子 1 0 に供給される読み出し電流 Ir は、書き込み時に MTJ 素子 1 0 に供給される書き込み電流 Iw よりもパルス幅が短いことが望ましい。これにより、読み出し電流 Ir での誤書き込みを低減することができる。これは、書き込み電流 Iw のパルス幅が短い方が、書き込み電流値の絶対値が大きくなるということに基づいている。

【0134】

本発明は、上述した実施形態に限定されるものではなく、その要旨を逸脱しない範囲内で、構成要素を変形して具体化できる。また、実施形態に開示されている複数の構成要素の適宜な組み合わせにより種々の発明を構成することができる。例えば、実施形態に開示される全構成要素から幾つかの構成要素を削除してもよいし、異なる実施形態の構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0135】

【図 1】本発明の第 1 の実施形態に係る MTJ 素子 1 0 の構成を示す断面図。

【図 2】第 1 の実施形態に係る MTJ 素子 1 0 の具体例を示す断面図。

【図 3】第 1 の実施形態に係る PIN 層 1 5 の他の構成を示す断面図。

【図 4】第 1 の実施形態に係る PIN 層 1 1 の他の構成を示す断面図。

【図 5】第 1 の実施形態に係る PIN 層 1 1 の他の構成を示す断面図。

【図 6】第 1 の実施形態に係るフリー層 1 3 及び PIN 層 1 1 の他の構成を示す断面図。

【図 7】本発明の第 2 の実施形態に係る MTJ 素子 1 0 の構成を示す断面図。

【図 8】第 2 の実施形態に係る MTJ 素子 1 0 の具体例を示す断面図。

10

20

30

40

50

【図9】第2の実施形態に係るフリー層13の他の構成を示す断面図。

【図10】本発明の第3の実施形態に係るMTJ素子10の構成を示す斜視図。

【図11】第3の実施形態に係るMTJ素子10の具体例を示す斜視図。

【図12】第3の実施形態に係るピン層15の他の構成を示す斜視図。

【図13】第3の実施形態に係るピン層15の他の構成を示す斜視図。

【図14】本発明の第4の実施形態に係るMRAMの構成を示す回路図。

【図15】MTJ素子10を中心に示したMRAMの断面図。

【図16】MTJ素子10を中心に示したMRAMの他の構成例を示す断面図。

【符号の説明】

【0136】

10

10...MTJ素子、11...第1の磁化参照層(ピン層)、11A, 11C, 11D...ピン層、11B...中間層、11E...界面ピン層、12...第1の中間層、13...磁化自由層(フリー層)、13A, 13C...界面フリー層、13B, 13F, 13D...フリー層、13E...中間層、14...第2の中間層、15...第2の磁化参照層(ピン層)、15A, 15C...ピン層、15B...中間層、16...下地層、17...キャップ層、18, 19...反強磁性層、20...メモリセルアレイ、21...選択トランジスタ、22, 23...電源回路、24...センスアンプ回路、25...電源、31...ビアプラグ、32...引き出し電極、33...ハードマスク、MC...メモリセル、BL...ピット線、WL...ワード線、SL...ソース線。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図 1 1】

図 11

【図 1 2】

図 12

【図 1 3】

図 13

【図 1 4】

図 14

【図15】

図15

【図16】

図16

---

フロントページの続き

|                        |              |            |

|------------------------|--------------|------------|

| (51) Int.Cl.           | F I          | テーマコード(参考) |

| H 01 F 10/32 (2006.01) | H 01 F 41/18 |            |

| H 01 F 41/18 (2006.01) |              |            |

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 吉川 将寿

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 甲斐 正

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 永瀬 俊彦

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 岸 達也

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 與田 博明

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

F ターム(参考) 4M119 AA03 AA11 BB01 CC05 DD05 DD06 DD09 DD10 DD17 DD32

DD45 EE22 EE27 FF05 FF13 FF15

5E049 AA01 AA04 AA07 BA08 BA23 BA25 DB12 DB14 GC02

5F092 AA01 AB08 AC12 AD23 AD25 BB17 BB22 BB23 BB24 BB31

BB34 BB35 BB36 BB38 BB42 BB43 BB44 BB55 BC07 BC08

BC32 BC33 BC46 BE06 BE13 BE21 BE25