(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5373817号

(P5373817)

(45) 発行日 平成25年12月18日(2013.12.18)

(24) 登録日 平成25年9月27日(2013.9.27)

(51) Int.Cl.

F 1

G06F 12/14 (2006.01)

G06F 12/10 (2006.01)G06F 12/14 510E

G06F 12/10 551C

G06F 12/10 505Z

G06F 12/10 541

請求項の数 12 (全 58 頁)

(21) 出願番号 特願2010-541763 (P2010-541763)

(86) (22) 出願日 平成21年1月5日 (2009.1.5)

(65) 公表番号 特表2011-509470 (P2011-509470A)

(43) 公表日 平成23年3月24日 (2011.3.24)

(86) 國際出願番号 PCT/EP2009/050050

(87) 國際公開番号 WO2009/087133

(87) 國際公開日 平成21年7月16日 (2009.7.16)

審査請求日 平成23年10月17日 (2011.10.17)

(31) 優先権主張番号 11/972,688

(32) 優先日 平成20年1月11日 (2008.1.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 フェッチ保護を有する動的アドレス変換

## (57) 【特許請求の範囲】

## 【請求項 1】

仮想アドレスを主ストレージ内のデータ・ブロックの変換アドレスに変換するために用いられる変換テーブル階層構造を有するコンピュータ・システムにおけるデータを保護するための方法であって、前記変換アドレスへの変換を行う動的アドレス変換部が、

変換すべき前記仮想アドレスを取得するステップと、

前記変換テーブル階層構造の変換テーブルの初期基点アドレスを取得するステップであって、前記変換テーブル階層構造がセグメント・テーブルを含むステップと、

前記取得された初期基点に基づいて、前記セグメント・テーブルからセグメント・テーブル・エントリを取得するステップであって、前記セグメント・テーブル・エントリがフォーマット制御フィールドを含むように構成されているステップと、

強化型 DAT ファシリティがイネーブルであることに応答して、前記セグメント・テーブル・エントリ内の前記フォーマット制御フィールドがイネーブルであるかどうかを判定するステップと、

前記フォーマット制御フィールドがイネーブルであることに応答して、

前記セグメント・テーブル・エントリ内のアクセス妥当性フィールドがイネーブルであるかどうかを判定するステップであって、前記セグメント・テーブル・エントリが、前記アクセス妥当性フィールド、セグメント・アクセス制御フィールド、セグメント・フェッチ保護フィールド、及び主ストレージ内のデータ・ブロックのセグメント・フレームの絶対アドレスを含むステップ

10

20

を実施するステップと、

前記アクセス妥当性フィールドがイネーブルであることに応答して、

所望のメモリ・ブロックへのストアを許可するステップであって、前記ストアは前記仮想アドレスに関連付けられており、前記ストアが、前記セグメント・アクセス制御フィールドが、プログラムによって与えられるプログラム・ステータス・ワード又は実行中のプログラム命令のオペランドのうちのいずれか1つのプログラム・アクセス・キーに一致したことに応答してのみ許可されるステップと、

前記所望のデータ・ブロックからのフェッチを許可するステップであって、前記フェッチは前記仮想アドレスに関連付けられており、a)前記セグメント・フェッチ保護フィールドがディスエーブルであること、又はb)前記セグメント・フェッチ保護フィールドがイネーブルであり、且つ前記仮想アドレスに関連付けられた前記プログラム・アクセス・キーが前記セグメント・アクセス制御フィールドと等しいこと、のいずれかに応答してのみ許可されるステップを実施するステップと

を実施するステップと、

強化型D A T ファシリティがイネーブルでないことに応答して、

前記セグメント・テーブル・エントリからページ・テーブルの基点を取得するステップであって、前記仮想アドレスのページ・インデックス部分を用いて前記ページ・テーブル内のページ・テーブル・エントリを参照するステップと、

前記ページ・テーブル・エントリから、主ストレージ内の小データ・ブロックのページ・フレーム実アドレスを取得するステップであって、前記小データ・ブロックは前記大データ・ブロックよりもサイズが小さく、且つ、ストレージ・キーに関連付けられた4キロバイトのデータ・ブロックから成り、前記ストレージ・キーは、ストレージ・アクセス制御フィールドとストレージ・フェッチ保護フィールドとを含み、主ストレージ内の所望の実データ・ブロックの変換アドレスは、前記ページ・フレーム実アドレスと前記仮想アドレスのバイト・インデックス部分との組合せを含む、ステップと、

を実施するステップと

を含む方法。

#### 【請求項2】

前記変換アドレスが、実アドレス又は絶対アドレスのうちのいずれか1つであり、前記実アドレスに対してプレフィックス付加を行うことによって前記絶対アドレスが形成され、前記変換テーブル階層構造が、領域第1テーブル、領域第2テーブル、領域第3テーブル、及び前記セグメント・テーブルのうちの1つ又は複数から成り、前記セグメント・テーブルから前記セグメント・テーブル・エントリを取得する前記ステップが、A、B、C、Dのうちのいずれか1つを含み、

A)前記領域第1テーブルの前記取得された初期基点アドレスに基づいて、前記仮想アドレスの第1インデックス部分を用いて前記領域第2テーブルの基点アドレスを含む前記領域第1テーブル内の領域第1テーブル・エントリを参照し、

前記領域第2テーブルの前記基点アドレスに基づいて、前記仮想アドレスの第2インデックス部分を用いて前記領域第3テーブルの基点アドレスを含む前記領域第2テーブル内の領域第2テーブル・エントリを参照し、前記領域第3テーブルの前記基点アドレスに基づいて、前記仮想アドレスの第3インデックス部分を用いて前記セグメント・テーブルの基点アドレスを含む前記領域第3テーブル内の領域第3テーブル・エントリを参照し、前記セグメント・テーブルの前記基点アドレスに基づいて、前記仮想アドレスのセグメント・インデックス部分を用いて前記セグメント・テーブル内のセグメント・テーブル・エントリを参照するステップ、

B)前記領域第2テーブルの前記取得された初期基点アドレスに基づいて、前記仮想アドレスの前記第2インデックス部分を用いて前記領域第3テーブルの基点アドレスを含む前記領域第2テーブル内の前記領域第2テーブル・エントリを参照し、前記領域第3テーブルの前記基点アドレスに基づいて、前記仮想アドレスの前記第3インデックス部分を用いて前記セグメント・テーブルの前記基点アドレスを含む前記領域第3テーブル内の前記

10

20

30

40

50

領域第3テーブル・エントリを参照し、前記セグメント・テーブルの前記基点アドレスに基づいて、前記仮想アドレスの前記セグメント・インデックス部分を用いて前記セグメント・テーブル内の前記セグメント・テーブル・エントリを参照するステップ、

C) 前記領域第3テーブルの前記取得された初期基点アドレスに基づいて、前記仮想アドレスの前記第3インデックス部分を用いて前記セグメント・テーブルの前記基点アドレスを含む前記領域第3テーブル内の前記領域第3テーブル・エントリを参照し、前記セグメント・テーブルの前記基点アドレスに基づいて、前記仮想アドレスの前記セグメント・インデックス部分を用いて前記セグメント・テーブル内の前記セグメント・テーブル・エントリを参照するステップ、及び

D) 前記セグメント・テーブルの前記取得された初期基点アドレスに基づいて、前記仮想アドレスの前記セグメント・インデックス部分を用いて前記セグメント・テーブル・エントリを参照するステップ 10

である、請求項1に記載の方法。

【請求項3】

前記強化型DATファシリティがイネーブルであり、且つ前記フォーマット制御フィールドがイネーブルでないことに応答して、

前記セグメント・テーブル・エントリからページ・テーブルの基点を取得するステップであって、前記仮想アドレスのページ・インデックス部分を用いて前記ページ・テーブル内のページ・テーブル・エントリを参照するステップと、

前記ページ・テーブル・エントリから、主ストレージ内の小データ・ロックのページ・フレーム実アドレスを取得するステップであって、前記小データ・ロックは前記大データ・ロックよりもサイズが小さく、且つ4キロバイトのデータ・ロックから成り、前記小データ・ロックは、ストレージ・アクセス制御フィールドとストレージ・フェッチ保護フィールドとを含むストレージ・キーに関連付けられており、主ストレージ内の所望の実データ・ロックの変換アドレスは、前記ページ・フレーム実アドレスと前記仮想アドレスのバイト・インデックス部分との組合せを含む、ステップと、 20

前記プログラムのアクセス制御フィールドが前記ストレージ・アクセス制御フィールドに一致したことに応答してのみ、前記所望の実メモリ・ロックに対するストアを許可するステップであって、前記ストアは前記仮想アドレスに関連付けられており、前記プログラムのアクセス制御フィールドは、プログラム・ステータス・ワード又は実行中のプログラム命令のオペランドのうちのいずれか1つを含むプログラム・エンティティによって与えられる、ステップと、 30

a) 前記ストレージ・フェッチ保護フィールドがディスエーブルであること、又はb) 前記ストレージ・フェッチ保護フィールドがイネーブルであり、且つ前記仮想アドレスに関連付けられたプログラム・アクセス・キーが前記ストレージ・アクセス制御フィールドと等しいこと、のいずれかにのみ応答して、前記所望のデータ・ロックからのフェッチを許可するステップであって、前記フェッチは前記仮想アドレスに関連付けられており、前記プログラム・アクセス・キーは、プログラム・ステータス・ワード又は実行中のプログラム命令のオペランドのうちのいずれか1つによって与えられる、ステップとを実施する、請求項2に記載の方法。 40

【請求項4】

前記強化型DATファシリティがイネーブルでないことに応答して、

前記セグメント・テーブル・エントリからページ・テーブルの基点を取得し、前記仮想アドレスのページ・インデックス部分を用いて前記ページ・テーブル内のページ・テーブル・エントリを参照するステップと、

前記ページ・テーブル・エントリから、主ストレージ内の小データ・ロックのページ・フレーム実アドレスを取得するステップであって、前記小データ・ロックは前記大データ・ロックよりもサイズが小さく、且つ、ストレージ・キーに関連付けられた4キロバイトのデータ・ロックから成り、前記ストレージ・キーは、ストレージ・アクセス制御フィールド及びストレージ・フェッチ保護フィールドを含み、主ストレージ内の所望の 50

実データ・ブロックの変換アドレスは、前記ページ・フレーム実アドレスと前記仮想アドレスのバイト・インデックス部分との組合せを含む、ステップと、

前記プログラムのアクセス制御フィールドが前記ストレージ・アクセス制御フィールドに一致したことに応答してのみ、前記所望の実メモリ・ブロックに対するストアを許可するステップであって、前記ストアが前記仮想アドレスに関連付けられる、ステップと、

a ) 前記ストレージ・フェッチ保護フィールドがディスエーブルであること、又はb ) 前記ストレージ・フェッチ保護フィールドがイネーブルであり、且つ前記仮想アドレスに関連付けられたプログラム・アクセス・キーが前記ストレージ・アクセス制御フィールドに等しいこと、のいずれかにのみ応答して、前記所望のデータ・ブロックからのフェッチを許可するステップであって、前記フェッチは前記仮想アドレスに関連付けられており、前記プログラム・アクセス・キーは、プログラム・ステータス・ワード又は実行中のプログラム命令のオペランドのうちのいずれか1つによって与えられる、ステップと

10

を実施する、請求項2に記載の方法。

【請求項5】

前記プログラム・アクセス・キーが0であることに応答して、前記所望のメモリ・ブロックへのストア及び前記所望のメモリ・ブロックからのフェッチを許可し、前記ストア及びフェッチが前記仮想アドレスに関連付けられる、請求項1に記載の方法。

【請求項6】

前記アクセス妥当性フィールド及び前記フェッチ保護フィールドがイネーブルであることに応答して、保護例外が、前記所望のメモリ・ブロックからのフェッチ動作が試行されたこと、且つ前記セグメント・アクセス制御フィールドが前記プログラムのアクセス制御フィールドに一致しないことに応答して示され、前記フェッチ動作が前記仮想アドレスに関連付けられている、請求項1に記載の方法。

20

【請求項7】

前記アクセス妥当性フィールドがイネーブルであるかどうかを判定する前記ステップが、a ) 制御レジスタのストレージ保護オーバーライド・フィールドがディスエーブルかどうか、又はb ) 前記ストレージ保護オーバーライド・フィールドがイネーブルであり、且つ前記セグメント・アクセス制御フィールドがイネーブルでないかどうか、のうちのいずれか1つを判定するステップをさらに含む、請求項1に記載の方法。

30

【請求項8】

前記仮想アドレスの前記変換に用いられた情報を、少なくとも1つの変換ルックアサイド・バッファ内にストアするステップと、

その後の仮想アドレスの、主ストレージ内の前記データ・ブロックの前記絶対アドレスへのそれ以降の変換を、前記変換テーブル階層構造ではなく前記変換ルックアサイド・バッファ由来の前記ストアされた情報を用いて実施するステップと

をさらに含む、請求項1に記載の方法。

【請求項9】

前記変換が前記システムのアーキテクチャに対してネイティブではないことに応答して、

前記変換をエミュレートするための所定のソフトウェア・ルーチンを識別するステップであって、前記所定のソフトウェア・ルーチンが複数の命令を含むステップと、

40

前記所定のソフトウェア・ルーチンを実行するステップと

をさらに含む、請求項1に記載の方法。

【請求項10】

前記大データ・ブロックが、少なくとも1メガバイトのサイズのブロックを含む、請求項1に記載の方法。

【請求項11】

方法に係る請求項1から請求項10のいずれか1項に記載の方法の全てのステップを実行するように適合された手段を備える、システム。

【請求項12】

10

20

30

40

50

コンピュータ・プログラムであって、前記コンピュータ・プログラムがコンピュータ・システム上で実行されるときに、請求項1から請求項10のいずれか1項に記載の方法の全てのステップをコンピュータに実行させる、コンピュータ・プログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、コンピュータ・システムにおいて仮想アドレスを変換するためのシステム及び方法に関し、より具体的には、仮想アドレス変換が変換テーブル階層構造を経て生じる動的アドレス・ファシリティを有するコンピュータ・システムにおいて、仮想アドレスをデータ・ブロックの実アドレス又は絶対アドレスに変換するシステム及び方法に関する。 10

【背景技術】

【0002】

動的アドレス変換は、任意の瞬間にプログラムの実行への割り込みを行い、そのプログラム及びそのプログラムのデータを直接アクセス・ストレージ・デバイスなどの補助ストレージに記録し、後の時点で、プログラム及びデータを異なる主ストレージ位置に戻して実行を再開する能力を提供する。主ストレージと補助ストレージとの間のプログラム及びデータの転送は断片的に行うことができ、主ストレージへの情報のリターンは、その情報が実行のために必要になった時点でC P Uによるアクセスの試行に応答して行われるものとすることができる。これらの機能は、プログラム及びそのデータを変更又は検査することなく実施することができ、再配置されたプログラムにおけるいかなる明示的なプログラミング規則も必要とせず、時間的遅延が伴うことを除いて、プログラムの実行を妨げない。 20

【0003】

オペレーティング・システムによる適切なサポートがあれば、動的アドレス変換ファシリティを用いて、ユーザに、ストレージがその構成において利用可能な主ストレージより大きく見えるようなシステムを提供することができる。この見かけの主ストレージは、しばしば仮想ストレージと呼ばれ、仮想ストレージ内の位置を指定するために用いられるアドレスは、しばしば仮想アドレスと呼ばれる。ユーザの仮想ストレージは、その構成において利用可能な主ストレージのサイズを遥かに超過することができ、通常は補助ストレージ内で維持される。仮想ストレージは、一般にページと呼ばれる（セグメント及び領域とも呼ばれる）データのブロックで構成されるものと見なされる。仮想ストレージのうち、直前に参照されたページのみが、物理的主ストレージのブロックを占有するように割り当てられる。ユーザが、主ストレージに現れていない仮想ストレージのページを参照する際には、それらのページを取り込んで、必要とされる可能性の低い主ストレージ内のページを置き換える。幾つかの場合には、仮想ストレージは、ストレージが参照されるかどうかに関わりなく、長期間にわたって（又は永続的に）主ストレージに割り当てられる。ストレージのページのスワッピングは、オペレーティング・システムによって、ユーザが知ることなく行われる。 30

【0004】

プログラムは、アドレス（又は仮想アドレス）を用いて仮想ストレージにアクセスする。プログラムは仮想アドレスを用いて、仮想ストレージから命令をフェッチすることができ、又は仮想ストレージからデータをロードするか若しくはデータをストアすることができる。ある範囲の仮想ストレージに関連付けられた仮想アドレスが、アドレス空間を定める。オペレーティング・システムによる適切なサポートがあれば、動的アドレス変換ファシリティを用いて、多数のアドレス空間を提供することができる。これらのアドレス空間を用いて、ユーザ間に様々な度合いの分離を提供することができる。このようなサポートは、ユーザごとに完全に異なるアドレス空間から成ることによって完全な分離を提供することもでき、又は各アドレス空間の一部を单一の共通ストレージ領域にマッピングすることによって共有エリアを提供することもできる。また、半特権的プログラムが1つより多 40

くのこのようなアドレス空間にアクセスすることを許可する命令も、提供される。

【0005】

動的アドレス変換は、多数の異なるアドレス空間からの仮想アドレスの変換を規定する。これらのアドレス空間は、一次アドレス空間、二次アドレス空間、及びアクセス・レジスタ指定アドレス空間と呼ばれる。特権的プログラムは、アクセスすべきホーム・アドレス空間を生じさせることもできる。動的アドレス変換は、CPUによって生成された命令及びデータ・アドレスに対して指定することができる。

【0006】

当該技術分野において今まで知られていない更なる機能、能力、及び保護を提供する、強化された動的アドレス変換ファシリティが必要とされている。

10

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第5,551,013号

【特許文献2】米国特許第5,574,873号

【特許文献3】米国特許第5,790,825号

【特許文献4】米国特許第6,009,261号

【特許文献5】米国特許第6,308,255号

【特許文献6】米国特許第6,463,582号

【非特許文献】

20

【0008】

【非特許文献1】「z/Architecture(登録商標) Principles of Operation」、IBM(登録商標)刊行番号SA22-7832-05、第6版、2007年4月

【非特許文献2】「IBM(登録商標) System/370 Extended Architecture」、IBM(登録商標)刊行番号SA22-7095、1985年

【発明の概要】

【発明が解決しようとする課題】

【0009】

仮想アドレスを、変換のために用いられる変換テーブル階層構造を備えたマシン・アーキテクチャを有するコンピュータ・システムの主ストレージ内の所望のデータ・ブロックの実アドレス又は絶対アドレスに変換する強化型動的アドレス変換ファシリティのためのシステム、方法、及びコンピュータ・プログラム製品が提供される。実アドレスにプリフィックス付加を行って、絶対アドレスを形成することができる。

30

【課題を解決するための手段】

【0010】

1つの例示的な実施形態において、変換されるべき仮想アドレス、及び変換テーブル階層構造の変換テーブルの初期基点アドレスが取得される。変換テーブルは、領域第1テーブル、領域第2テーブル、領域第3テーブル、又はセグメント・テーブルから成る。取得された初期基点アドレスに基づいて、セグメント・テーブル・エントリがセグメント・テーブルから取得される。セグメント・テーブル・エントリは、フォーマット制御フィールドを含むように構成される。強化型DATファシリティ及びフォーマット制御フィールドがイネーブルであれば、セグメント・テーブル・エントリ内のアクセス妥当性フィールドがイネーブルであるかどうかが判定される。アクセス妥当性フィールドがイネーブルであれば、セグメント・テーブル・エントリは、アクセス制御フィールド、保護フィールド、及び主ストレージ内のデータ・ブロックのセグメント・フレーム絶対アドレスをさらに含む。データ・ブロックは少なくとも1メガバイトのサイズのブロックである。アクセス制御フィールドがイネーブルであれば、所望のデータ・ブロックへのストア動作は、アクセス制御フィールドがプログラム・ステータス・ワード又は実行中のプログラム命令のオペランドのいずれかによって与えられるプログラム・アクセス・キーに一致した場合に

40

50

のみ、許可される。所望のデータ・ブロックからのフェッチ動作は、仮想アドレスに関連付けられたプログラム・アクセス・キーがアクセス制御フィールドに等しい場合にのみ、許可される。

【0011】

さらに別の実施形態において、アクセス妥当性フィールドがイネーブルであれば、フェッチ動作又はストア動作が所望のメモリ・ブロックにおいて試行され、且つセグメント・アクセス制御フィールドがプログラム・アクセス制御フィールドと一致しないことに応答して、保護例外が示される。

【0012】

本発明は、次に、特定の例示的な実施形態との関連で説明される。当業者であれば本発明の精神及び範囲から逸脱することなく種々の変更及び修正を行うことが可能であることを理解されたい。 10

【0013】

添付の図面において、同一又は機能的に類似の要素には別々の図の全体を通じて同様の参照符号が付されており、これらの図面は以下の詳細な説明と共に本明細書に組み入れられ、その一部を形成するものであり、種々の実施形態をさらに例証し、且つ、全て本発明に従う種々の原理及び利点を説明する役割を果たす。

【図面の簡単な説明】

【0014】

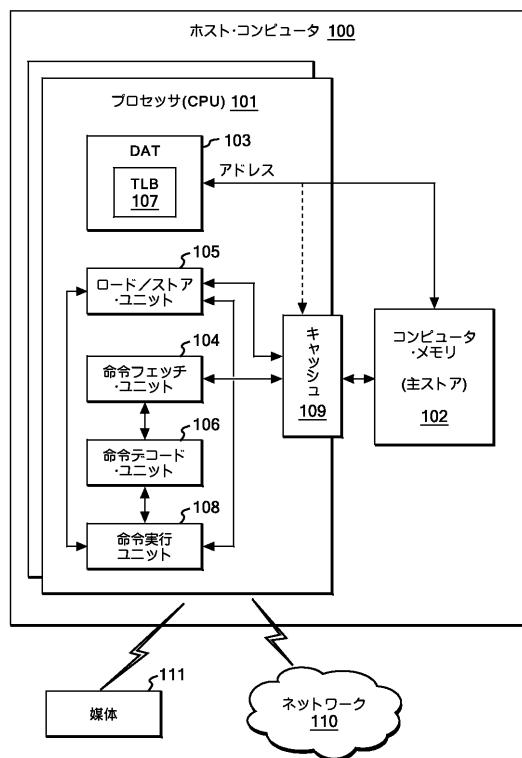

【図1】強化型動的アドレス変換を実施することができるホスト・コンピュータ・システムの一実施形態を示す。 20

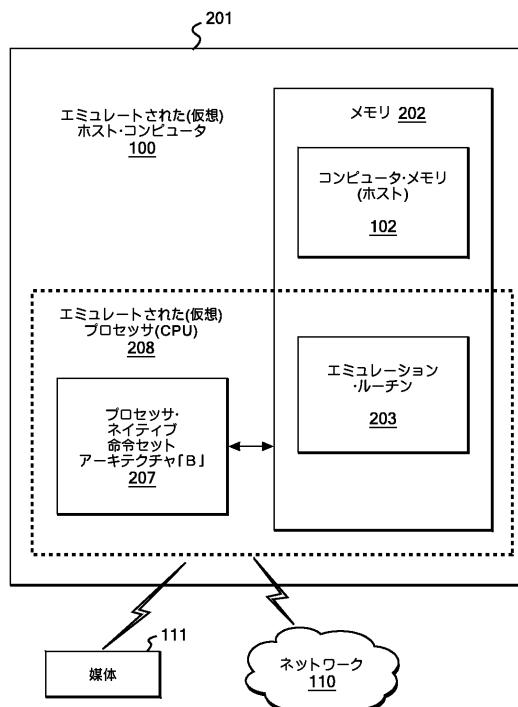

【図2】ホスト・アーキテクチャのホスト・コンピュータ・システムをエミュレートする、エミュレートされたホスト・コンピュータ・システムの一例を示す。

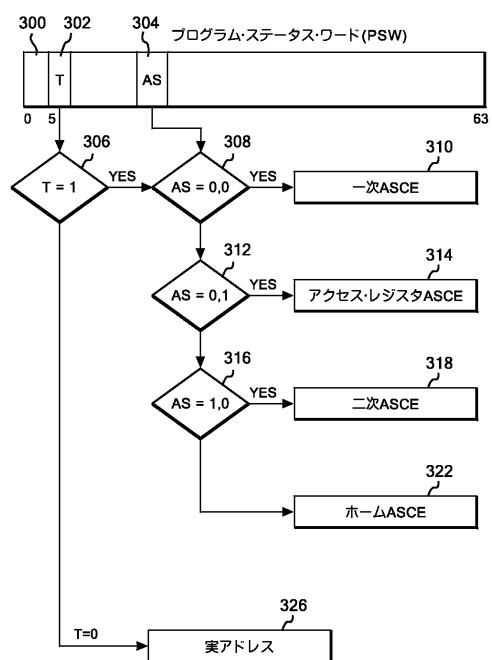

【図3】プログラム・ステータス・ワードを用いて仮想アドレスの動的アドレス変換のための実効A S C Eを判定する手法の一実施形態を示す。

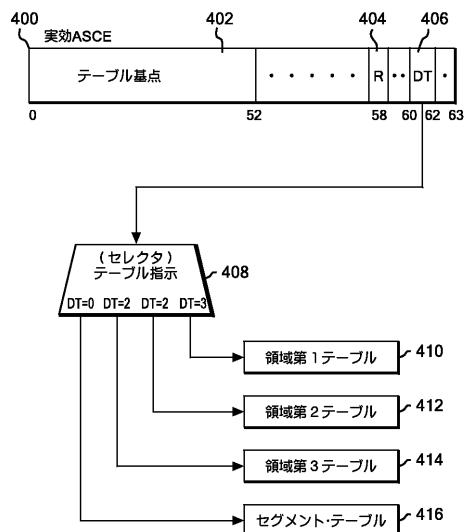

【図4】図3において判定された実効A S C Eを用いて、仮想アドレスの変換に用いられる変換テーブル階層構造の中で最も高位の変換テーブルを判定する一実施形態を示す。

【図5】変換テーブル階層構造をセグメント・テーブル・レベルまで用いて仮想アドレスを動的アドレス変換するプロセスの一実施形態を示す。

【図6】セグメント・テーブル・エントリ(S T E)フォーマット制御(F C)が0である場合の、図5の動的アドレス変換の続きを示す。 30

【図7】セグメント・テーブル・エントリ(S T E)フォーマット制御(F C)が1である場合の、図5の動的アドレス変換の続きを示す。

【図8】セグメント・テーブル・エントリ内のフォーマット制御フィールドを取得するための強化型(enhanced)動的アドレス変換(e D A T)の一実施形態の流れ図を示す。

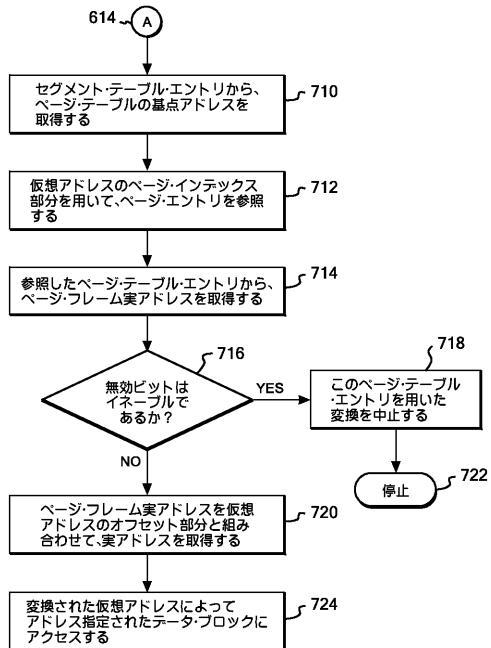

【図9】図8のノード614からの流れ図の続きを示す。

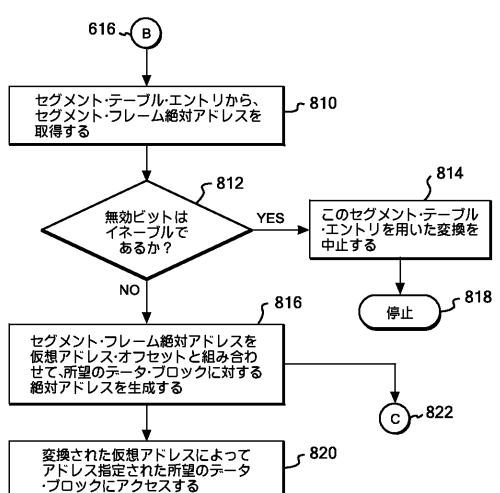

【図10】図8のノード616からの流れ図の続きを示す。

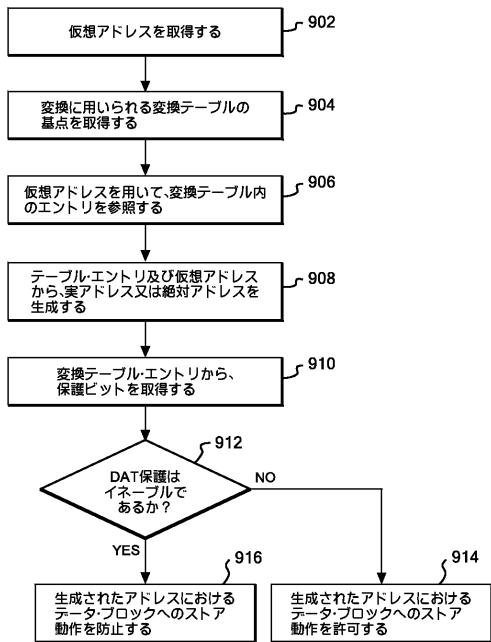

【図11】変換された仮想アドレスによってアドレス指定された所望のデータ・ブロックに適用すべきD A T保護のレベルを判定する一実施形態の流れ図を示す。

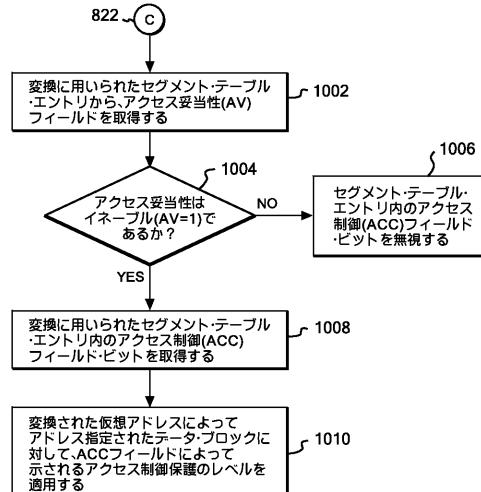

【図12】変換された仮想アドレスによってアドレス指定された所望のデータ・ブロックに適用すべきアクセス制御保護のレベルを判定する、図10のノード822からの流れ図の続きを示す。 40

【図13】変換された仮想アドレスによってアドレス指定された所望のデータ・ブロックに適用すべきフェッチ保護のレベルを判定する、図10のノード822からの流れ図の続きを示す。

【図14】変更記録オーバーライド・フィールドがセグメント・テーブル・エントリから取得される、図10のノード822からの流れ図の続きを示す。

【発明を実施するための形態】

【0015】

本出願の明細書における記述は、特許請求される種々の発明いずれをも必ずしも限定す 50

るものではないことを理解されたい。さらに、幾つかの記述は、幾つかの発明の特徴に当てはまることがあるが、他の発明の特徴には当てはまらないこともある。特に断りのない限り、単数形の要素は、一般性を失うことなく、複数形の場合もあり、その逆もまた真である。

#### 【0016】

当業者であれば、コンピュータ環境内のストレージに対してアドレス指定すること、及び、様々な状態及びそれらの状態上での動作を示すためにレジスタ又はアドレス・フィールド内のビットを使用することに容易に精通するはずである。さらに、当業者であれば、コンピュータ・プログラム分野の知識を有し、かつ、コンピュータ・システムのコンポーネント間の働き及び相互関係についての知識を有しているはずである。

10

#### 【0017】

##### 概要

強化型動的アドレス変換 (D A T) ファシリティの例示的な実施形態が提供される。強化型 D A T ファシリティがインストールされており、且つインエーブルである場合、D A T 変換は、ページ・フレーム実アドレス、又はセグメント・テーブル・エントリ内のセグメント・テーブル・エントリ (S T E) フォーマット制御によって決定されるセグメント・フレーム絶対アドレスを生成することができる。本明細書において用いられる「強化型 D A T を適用する」という用語は、以下の全てが真であることを意味する。即ち、1) E D A T ファシリティがインストールされており、2) E D A T ファシリティが制御レジスター 0 (C R 0) ビット 4 0 を通じてインエーブルになっており、且つ3) アドレスは D A T テーブル・エントリによって変換される。

20

#### 【0018】

強化型 D A T を適用する場合、D A T プロセスにおいて以下の追加機能が利用可能である。即ち、

D A T 保護ビットが領域テーブル・エントリに追加され、セグメント・テーブル・エントリ及びページ・テーブル・エントリ内の D A T 保護ビットと同様の機能を与える。

S T E フォーマット制御がセグメント・テーブル・エントリに追加される。S T E フォーマット制御が 0 である場合、D A T は、そのページに対する変更ビットの設定がバイパスされるかどうかをページ・テーブル・エントリ内の変更記録オーバーライドが示すこと以外は、現在定められている通りに進行する。

30

#### 【0019】

S T E フォーマット制御が 1 である場合、セグメント・テーブル・エントリは、さらに以下を含む。即ち、

1 メガバイト・ブロックの絶対ストレージ位置を指定するセグメント・フレーム絶対アドレス (ページ・テーブル基点ではなく)。

セグメントの個々のストレージ・キーの中の対応するビットの代わりに随意的に用いることができる、アクセス制御ビット及びフェッチ保護ビット。

セグメント・テーブル・エントリ内のアクセス制御ビット及びフェッチ保護ビットの妥当性を決定するビット。

セグメントの個々のストレージ・キーにおいて変更ビットの設定をバイパスすることができるかどうかを示す、変更記録オーバーライド。

40

#### 【0020】

##### ホスト・コンピュータ・システム

図 1 を参照すると、ホスト・コンピュータ・システム 1 0 0 の代表的なコンポーネントが描かれている。他のコンポーネント構成をコンピュータ・システムにおいて用いることもでき、これは当該技術分野において周知である。

#### 【0021】

ホスト・コンピュータ環境は、ニューヨーク州 Armonk 所在の International Business Machines Corporation (IBM (登録商標)) により提供される、z / Architecture (登録商標) に基づくもの

50

であることが好ましい。z/Architecture(登録商標)は、引用によりその全体をここに組み入れる非特許文献1に、より詳細に記載されている。z/Architecture(登録商標)に基づくコンピュータ環境は、例えば、共にIBM(登録商標)によるeServer及びzSeries(登録商標)を含む。

#### 【0022】

代表的なホスト・コンピュータ100は、1つ又は複数のCPU101を含み、これは、主ストア(コンピュータ・メモリ102)、並びに、ストレージ・デバイス111に対するI/Oインターフェース、及び他のコンピュータ又はストレージ・エリア・ネットワーク(SAN)などとの通信のためのネットワーク110に対するI/Oインターフェースと通信する。CPUは、プログラム・アドレス(仮想アドレス)をメモリの実アドレスに変換するための動的アドレス変換(DAT)ファシリティ(機能又はユニット)103を含む。DATファシリティは、典型的には、後でコンピュータ・メモリ102のプロックにアクセスしたときにアドレス変換による遅延を必要とせずに済むように変換をキャッシュに入れるための、変換ルックアサイド・バッファ107を含む。典型的には、キャッシュ109は、コンピュータ・メモリ102とプロセッサ101との間で用いられる。キャッシュ109は、1つより多くのCPUが利用できる大型キャッシュと、大型キャッシュと各CPUとの間のより小型でより高速な(下位レベルの)キャッシュとを有する階層構造とすることができます。幾つかの実装において、下位レベルのキャッシュは、命令のフェッチ及びデータ・アクセスのための個別の低レベルキャッシュを提供するように分割される。一実施形態において、命令は、命令フェッチ・ユニット104によりメモリ102からキャッシュ109を経由してフェッチされる。命令は、命令デコード・ユニット(106)内でデコードされ、(幾つかの実施形態においては他の命令と共に)命令実行ユニット108へディスパッチされる。典型的にはいくつかの実行ユニット108、例えば、算術演算実行ユニット、浮動小数点実行ユニット、及び分岐命令実行ユニットが用いられる。命令は、実行ユニットにより、必要に応じて命令が指定するレジスタ又はメモリからのオペランドにアクセスしながら実行される。オペランドがメモリ102からアクセスされる(ロードされる又はストアされる)場合には、典型的には、ロード・ストア・ユニット105が、実行されている命令の制御下でアクセスを取り扱う。

#### 【0023】

一実施形態において、本発明は、ソフトウェア(ライセンス内部コード(LIC)、ファームウェア、マイクロ・コード、ミリ・コード、ピコ・コードなどと呼ばれる場合もあるが、そのいずれも本発明と整合性がある)により実施することができる。本発明を具体化するソフトウェア・プログラム・コードは、典型的には、コンピュータ・システム100のCPU(中央演算処理装置)101としても知られるプロセッサにより、CD-ROMドライブ、テープ・ドライブ又はハード・ドライブといった長期ストレージ媒体111からアクセスされる。ソフトウェア・プログラム・コードは、ディスクケット、ハード・ドライブ又はCD-ROMといった、データ処理システムと共に使用するための種々の公知の媒体のいずれかの上で具体化することができる。コードは、そのような媒体上で配布することができ、又は1つのコンピュータ・システムのコンピュータ・メモリ102若しくはストレージから、他のシステムのユーザが使用するために、ネットワーク110を介してそのような他のコンピュータ・システムに配布することができる。

#### 【0024】

あるいは、プログラム・コードをメモリ102内で具体化し、プロセッサ・バスを用いてプロセッサ101によってアクセスすることができる。このようなプログラム・コードは、種々のコンピュータ・コンポーネント及び1つ又は複数のアプリケーション・プログラムの機能及び相互作用を制御するオペレーティング・システムを含む。プログラム・コードは、通常、高密度ストレージ媒体111から高速メモリ102にページングされ、そこでプロセッサ101による処理のために利用可能になる。ソフトウェア・プログラム・コードをメモリ内、物理媒体上で具体化し、及び/又はネットワークを介してソフトウェア・コードを配布する技術及び方法は周知であり、ここではこれ以上論じない。プログラ

10

20

30

40

50

ム・コードは、作成され、有形の媒体（電子メモリ・モジュール（RAM）、フラッシュメモリ、コンパクトディスク（CD）、DVD、磁気テープなどを含むがこれらに限定されない）に格納された場合には、しばしば「コンピュータ・プログラム製品」と呼ばれる。コンピュータ・プログラム製品媒体は、典型的には、処理回路によって実行されるために、好ましくはコンピュータ・システム内にある処理回路によって読み出し可能である。

#### 【0025】

図2に、ホスト・アーキテクチャのホスト・コンピュータ・システム100をエミュレートする、エミュレートされたホスト・コンピュータ・システム201の一例を示す。エミュレートされたホスト・コンピュータ・システム201において、ホスト・プロセッサ（CPU）208は、エミュレートされたホスト・プロセッサ（又は仮想ホスト・プロセッサ）であり、ホスト・コンピュータ100のプロセッサ101によって用いられるものとは異なるネイティブ命令セット・アーキテクチャを有するエミュレーション・プロセッサ207を備える。エミュレートされたホスト・コンピュータ・システム201は、エミュレーション・プロセッサ207によってアクセス可能なメモリ202を有する。例示的な実施形態において、メモリ202は、ホスト・コンピュータ・メモリ102部分と、エミュレーション・ルーチン203部分（エミュレーションを提供するルーチンはホスト・メモリの一部とすることができる）とのパーティションに分けられている。ホスト・コンピュータ・メモリ102は、ホスト・コンピュータ・アーキテクチャに従い、エミュレートされたホスト・コンピュータ・システム201のプログラムによって利用可能である。エミュレーション・プロセッサ207は、エミュレートされたプロセッサ208のアーキテクチャ以外のアーキテクチャのアーキテクチャ化された（architected）命令セットのネイティブ命令を実行し、このネイティブ命令はエミュレーション・ルーチン・メモリ203から取得されたものであり、且つ、エミュレーション・プロセッサ207は、シーケンス及びアクセス/デコード・ルーチンにおいて取得される1つ又は複数の命令を用いることによって、ホスト・コンピュータ・メモリ102の中のプログラム由来の実行のためのホスト命令にアクセスすることができ、このシーケンス及びアクセス/デコード・ルーチンは、アクセスされたホスト命令をデコードして、アクセスされたホスト命令の機能をエミュレートするためのネイティブ命令実行ルーチンを判定することができる。

#### 【0026】

ホスト・コンピュータ・システム100アーキテクチャのために定義された、例えば、汎用レジスタ、制御レジスタ、動的アドレス変換、並びにI/Oサブシステム・サポート及びプロセッサ・キャッシュといったファシリティを含む他のファシリティを、アーキテクチャ化ファシリティ・ルーチンによってエミュレートすることができる。エミュレーション・ルーチンは、エミュレーション・ルーチンの性能を高めるために、エミュレーション・プロセッサ207において利用可能な（汎用レジスタ、及び仮想アドレスの動的変換といった）ファシリティを利用することもできる。ホスト・コンピュータ100の機能をエミュレートする際にプロセッサ207を補助するために、特殊ハードウェア及びオフ・ロード・エンジンを設けることもできる。

#### 【0027】

##### コンピュータ・プロセッサ及びレジスタ

一実施形態において、CPUのプログラム命令機能は、通信バスを介して複数のレジスタと通信する。通信バスは、CPUの内部にあっても、又は外部にあってもよい。いくつかのレジスタは読み出し専用とすることができます。他のハードウェア及び/又はソフトウェアも、CPUによってアクセス可能な1つ又は複数のレジスタを読み出す/書き込むことができる。命令動作コード（オペコード）が、いずれかの特定のマシン命令動作において、どのタイプのレジスタが用いられるかを決定する。

#### 【0028】

##### 汎用レジスタ

命令は、16個の汎用レジスタのうちの1つ又は複数の中の情報を指示することができる。汎用レジスタは、アドレス算術演算におけるベース・アドレス・レジスタ及びインデ

10

20

30

40

50

ツクス・レジスタとして用いることができ、且つ、一般算術演算及び論理演算におけるアキュムレータとして用いることができる。各レジスタは、64個のビット位置を含む。汎用レジスタは、番号0-15によって識別され、命令内の4ビットのRフィールドによって指示される。ある命令は、数個のRフィールドを有することによって、複数の汎用レジスタをアドレス指定することを規定する。命令によっては、特定の汎用レジスタの使用は、命令のRフィールドによって明示的に指示されるのではなく暗黙的であることもある。

#### 【0029】

演算によっては、2つの隣接する汎用レジスタのビット32-63又は0-63のいずれかを結合して、それぞれ、64ビット又は128ビット形式を提供する場合もある。これらの演算においては、プログラムは、最左端（高位）の32ビット又は64ビットを含む偶数番号のレジスタを指示しなければならない。次に高位の番号のレジスタは最右端（低位）の32ビット又は64ビットを含む。一般算術演算及び論理演算におけるアキュムレータとしての使用に加えて、16個の汎用レジスタのうちの15個は、アドレス生成におけるベース・アドレス及びインデックス・レジスタとして用いることもできる。これらの場合において、レジスタは、命令内の4ビットのBフィールド又はXフィールドによって指示される。B又はXフィールドにおける0の値は、適用されるべきベース又はインデックスが存在しないことを指定し、従って、汎用レジスタ0を、ベース・アドレス又はインデックスを含むものとして指示することはできない。

#### 【0030】

##### 制御レジスタ

制御レジスタは、プログラム・ステータス・ワードの外部での制御情報の保持及び操作を規定する。CPUは、各々が64のビット位置を有する16個の制御レジスタを有する。レジスタ内のビット位置は、プログラム・イベント記録のようなシステム内の特定のファシリティに割り当てられ、ある演算を行うことができることを指定すること、又はそのファシリティが要求する特別な情報を供給することのどちらかのために用いられる。制御レジスタは、番号0-15によって識別され、LOAD CONTROL命令及びSTORE CONTROL命令内の4ビットのRフィールドによって指示される。複数の制御レジスタを、これらの命令によってアドレス指定することが可能である。

#### 【0031】

##### 制御レジスタ1

制御レジスタ1は、一次アドレス空間制御要素（PASE）を含む。一実施形態において、制御レジスタ1は、レジスタ内の実空間制御ビット（R）に応じて、以下の2つのフォーマットのうちの1つを有する。

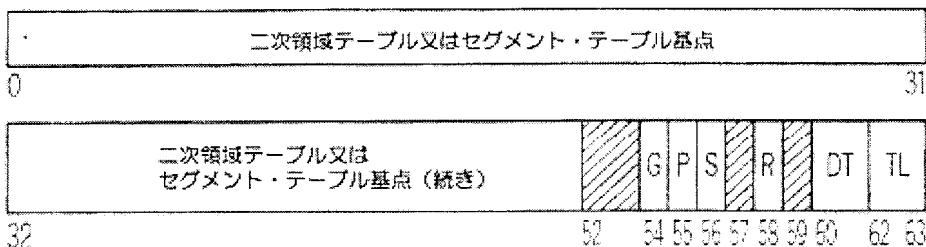

##### 【表1】

一次領域テーブル又は

セグメント・テーブル指示（R=0）

| 一次領域テーブル又はセグメント・テーブル基点         |    |    |    |    |    |    |    |    |       |

|--------------------------------|----|----|----|----|----|----|----|----|-------|

|                                |    |    |    |    |    |    |    |    | 31    |

| 一次領域テーブル又は<br>セグメント・テーブル基点（続き） |    |    |    |    |    |    |    |    |       |

| 32                             | 52 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 62 63 |

一次実空間指示（R=1）

| 一次実空間トークン基点     |    |    |    |    |    |    |    |    |    |

|-----------------|----|----|----|----|----|----|----|----|----|

|                 |    |    |    |    |    |    |    |    | 31 |

| 一次実空間トークン基点（続き） |    |    |    |    |    |    |    |    |    |

| 32              | 52 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 63 |

## 【0032】

一次アドレス空間制御要素 (P A S C E) 内の選択されたフィールドは、以下のように割り振られる。

一次領域テーブル又はセグメント・テーブル基点：制御レジスタ1の中の一次領域テーブル又はセグメント・テーブル指示のビット0 - 51は、右に12個の0が付加されると、一次領域テーブル又はセグメント・テーブルの開始位置を指示する64ビット・アドレスを形成する。このアドレスが実であるか絶対であるかは予測不可能である。このテーブルは、一次アドレス空間における仮想アドレスを変換するために用いられるので、一次領域テーブル又はセグメント・テーブルと呼ばれる。

## 【0033】

10

一次実空間制御 (R)：制御レジスタ1のビット58が0であれば、レジスタは領域テーブル又はセグメント・テーブル指示を含む。ビット58が1であれば、レジスタは実空間指示を含む。ビット58が1である場合、セグメント・テーブル・エントリの変換ルックアサイド・バッファ表示内の共通セグメント・ビットの値1は、制御レジスタ1の中のトークン基点と変換ルックアサイド・バッファ・エントリの中のテーブル基点との間に一致が存在したとしても、一次アドレス空間への参照を変換するときにエントリ及びそれが指示する変換ルックアサイド・バッファ・ページ・テーブル・コピーが用いられることを防止する。

## 【0034】

20

一次指示タイプ制御 (DT)：Rが0である場合、制御レジスタ1の中のテーブル指示タイプは、レジスタ内のビット60及び61によって以下のように指定される。

## 【表2】

| ビット60<br>及び61 | 指示タイプ      |

|---------------|------------|

| 11            | 領域第1テーブル   |

| 10            | 領域第2テーブル   |

| 01            | 領域第3テーブル   |

| 00            | セグメント・テーブル |

30

## 一次指示タイプ(DT)制御ビット

## 【0035】

Rが0である場合、最左端の1ビットがアドレスのビット位置0 - 10にある仮想アドレスを変換するためにP A S C Eの使用が試行される場合には、ビット60及び61は二進数字11でなければならない。同様に、最左端の1ビットがアドレスのビット位置11 - 21にある場合には、ビット60及び61は二進数字11又は10でなければならない、最左端の1ビットがアドレスのビット位置22 - 32にある場合には、二進数字11、10、又は01でなければならない。それ以外の場合には、A S C Eタイプ例外が認識される。

40

## 【0036】

一次領域テーブル又はセグメント・テーブル長 (TL)：制御レジスタ1の中の一次領域テーブル指示又はセグメント・テーブル指示のビット62及び63は、一次領域テーブル又はセグメント・テーブルの長さを4,096バイトの単位で指定し、従って、領域テーブル又はセグメント・テーブルの長さを512エントリの倍数として可変にする。一次領域テーブル又はセグメント・テーブルの長さは、4,096バイト単位で、TLの値より1多い。長さフィールドの内容は、そのテーブルによって変換されるべき仮想アドレスの一部 (R F X、R S X、R T X、又はS X) が、そのテーブルの範囲内にあるエントリを指示しているかどうかを確立するために用いられる。

50

## 【0037】

一次実空間トークン基点：制御レジスタ1の中の一次実空間のビット0 - 51は、右に12個の0が付加されると、64ビットのアドレスを形成し、このアドレスは、一次アドレス空間の参照のための仮想と実が等しい変換(virtual equals real translation)を提供する変換ルックアサイド・バッファ・エントリの形成及び使用の際に用いることができる。このアドレスはトークンとしてのみ用いられるものであり、ストレージ参照を実施するために用いられるものではないが、それでもなお、有効なアドレスでなければならない。そうでなければ、制御レジスタ1の内容が用いられるときに、正しくない変換ルックアサイド・バッファ・エントリが用いられることがある。

## 【0038】

10

制御レジスタ1の以下のビット、即ち、レジスタが領域テーブル指示又はセグメント・テーブル指示を含む場合のビット52、53及び59、レジスタが実空間指示を含む場合のビット52、53及び59 - 63は、割り当てられず、無視される。

## 【0039】

制御レジスタ7

制御レジスタ7は、二次アドレス空間制御要素(SASC E)を含む。一実施形態において、制御レジスタ7は、レジスタ内の実空間制御ビット(R)に応じて、以下の2つのフォーマットのうちの1つを有する。即ち、

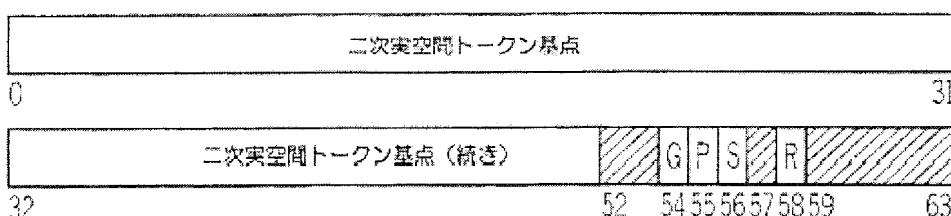

## 【表3】

二次領域テーブル又は

セグメント・テーブル指示(R=0)

20

二次実空間指示(R=1)

30

## 制御レジスタ7のフォーマット

## 【0040】

制御レジスタ13

制御レジスタ13は、ホーム・アドレス空間制御要素(HASC E)を含む。一実施形態において、制御レジスタ13は、レジスタ内の実空間制御ビット(R)に応じて、以下の2つのフォーマットのうちの1つを有する。即ち、

40

【表4】

ホーム領域テーブル又は

セグメント・テーブル指示 (R=0)

| ホーム領域テーブル又はセグメント・テーブル基点 |                                  |  |  |  |  |  |

|-------------------------|----------------------------------|--|--|--|--|--|

| 0                       | 31                               |  |  |  |  |  |

| 32                      | ホーム領域テーブル<br>又はセグメント・テーブル基点 (続き) |  |  |  |  |  |

52 55 56 57 58 59 60 62 63

ホーム実空間指示 (R=1)

| ホーム実空間トークン基点 |                   |  |  |  |  |  |

|--------------|-------------------|--|--|--|--|--|

| 0            | 31                |  |  |  |  |  |

| 32           | ホーム実空間トークン基点 (続き) |  |  |  |  |  |

52 54 55 56 57 58 59 63

### 制御レジスタ 1 3 のフォーマット

#### 【0041】

##### アクセス・レジスタ

CPUは、0 - 15の番号を与えられた16個のアクセス・レジスタを有する。アクセス・レジスタは、ASC Eの間接的な指定を含む32個のビット位置から成る。ASC Eは、動的アドレス変換 (DAT) 機構によって、対応するアドレス空間に対する参照を変換するために用いられるパラメータである。CPUがアクセス・レジスタ・モードと呼ばれるモード (プログラム・ステータス・ワード内のビットによって制御される) にある場合、ストレージ・オペランド参照のための論理アドレスを指定するために用いられる命令Bフィールドがアクセス・レジスタを指示し、そのアクセス・レジスタによって指定されるASC Eが、DATによって、行われている参照のために用いられる。命令によっては、Bフィールドの代わりにRフィールドが用いられることがある。アクセス・レジスタの内容をロード及びストアするための命令、並びに1つのアクセス・レジスタの内容を別のアクセス・レジスタに移動するための命令が与えられる。

#### 【0042】

アクセス・レジスタ1 - 15の各々は、現在の命令空間 (一次アドレス空間) を含めた任意のアドレス空間を指示することができる。アクセス・レジスタ0は、一次アドレス空間を指示する。アクセス・レジスタ1 - 15のうちの1つがアドレス空間を指示するために用いられている場合、CPUは、そのアクセス・レジスタの内容を変換することによって、どのアドレス空間が指示されているかを判定する。アクセス・レジスタ0がアドレス空間を指示するために用いられる場合、CPUは、そのアクセス・レジスタが一次命令空間を指示するものとして扱い、アクセス・レジスタの実際の内容は検査しない。従って、16個のアクセス・レジスタは、任意の一時点に、一次命令空間と、最大で15個の他の空間とを指示することができる。

#### 【0043】

##### プログラム・ステータス・ワード (PSW)

プログラム・ステータス・ワードは、命令アドレスと、条件コードと、命令の順序付けを制御し、CPUの状態を決定するために用いられる他の情報とを含む。アクティブな又は制御中のプログラム・ステータス・ワードは、カレント・プログラム・ステータス・ワードと呼ばれる。これは、現在実行されているプログラムを支配する。

#### 【0044】

CPUは割り込み能力を有し、これにより、CPUを例外条件及び外部刺激に応答して別のプログラムに迅速に切り替えることが可能になる。割り込みが発生すると、CPUは、カレント・プログラム・ステータス・ワードを、古いプログラム・ステータス・ワード

10

20

30

40

50

位置と呼ばれる、特定の割り込みのクラス毎に割り当てられたストレージ位置に置く。C P Uは、第2の割り当てられたストレージ位置から新たなプログラム・ステータス・ワードをフェッチする。この新たなプログラム・ステータス・ワードが、次に実行されるプログラムを決定する。割り込みの処理が終了すると、割り込みを扱うプログラムは、割り込まれたプログラムが続行できるように、古いプログラム・ステータス・ワードをリロードして、それを再びカレント・プログラム・ステータス・ワードとすることができる。

#### 【0045】

割り込みには、外部、I/O、マシン・チェック、プログラム、再起動、及びスーパーバイザー・コールの6つのクラスがある。各クラスは、実ストレージに永続的に割り当てられた、古いプログラム・ステータス・ワード位置と新しいプログラム・ステータス・ワード位置との別個のペアを有する。 10

#### 【0046】

##### カレント・プログラム・ステータス・ワード

C P U内のカレント・プログラム・ステータス・ワードは、現在アクティブなプログラムの実行に必要な情報を含む。プログラム・ステータス・ワードは、128ビット長であり、命令アドレス、条件コード、及び他の制御フィールドを含む。一般に、プログラム・ステータス・ワードは、命令の順序付けを制御し、C P Uの状態のうちの多くのを、現在実行中のプログラムとの関係で保持及び表示するために用いられる。付加的な制御及び状態情報は、制御レジスタ及び永続的に割り当てられたストレージ位置に含まれる。C P Uの状態は、新たなプログラム・ステータス・ワード又はプログラム・ステータス・ワードの一部をロードすることによって変更することができる。 20

#### 【0047】

C P Uの割り込み中に、C P Uの状態を保存するためにカレント・プログラム・ステータス・ワードをストアし、次いで新たなプログラム・ステータス・ワードをロードすることによって、制御が切り替えられる。LOAD PSW又はLOAD PSW EXTENDの実行、又は初期プログラム・ロード・シーケンスの終結の成功により、新たなプログラム・ステータス・ワードが導入される。命令アドレスは、逐次的な命令実行によって更新され、成功した分岐によって置換される。プログラム・ステータス・ワードの一部の上で動作する他の命令が与えられる。

#### 【0048】

プログラム・ステータス・ワードを変更する命令の割り込み又は実行が完了すると、新たな又は修正されたプログラム・ステータス・ワードがアクティブになる（即ち、カレント・プログラム・ステータス・ワードに導入された情報がC P Uに対する制御を担う）。プログラム・ステータス・ワードを変更する命令に関連するプログラム・イベント記録（PER）のための割り込みは、その動作の開始時に有効なPERマスクの制御下で生じる。プログラム・ステータス・ワードのビット0-7は集合的にシステム・マスクと呼ばれる。一実施形態において、プログラム・ステータス・ワードは以下のフォーマットを有する。 30

【表5】

## プログラム・ステータス・ワードのフォーマット

〔 0 0 4 9 〕

以下は選択されたプログラム・ステータス・ワードフィールドの機能の概要である。

〔 0 0 5 0 〕

D A T モード ( T ) : ビット 5 は、ストレージにアクセスするために用いられる論理アドレス及び命令アドレスの暗黙的な動的アドレス変換が行われるかどうかを制御する。ビット 5 が 0 である場合には、D A T はオフであり、論理アドレス及び命令アドレスは実アドレスとして扱われる。ビット 5 が 1 である場合には、D A T はオンであり、動的アドレス変換機構が起動される。

【 0 0 5 1 】

PSWキー：ビット8-11は、CPUによるストレージ参照のためのアクセス・キーを形成する。参照がキー制御保護を受ける場合は、情報がストアされるとき又は情報がフェッチに対して保護されている位置からフェッチされるときに、PSWキーは、ストレージ・キーと照合される。しかし、MOVE TO PRIMARY、MOVE TO SECUNDARY、MOVE WITH KEY、MOVE WITH SOURCE KEY、及びMOVE WITH DESTINATION KEYの各々のオペランドのうちの1つについては、オペランドとして指定されるアクセス・キーがPSWキーの代わりに用いられる。

【 0 0 5 2 】

アドレス空間制御 ( A S ) : ビット 16 及び 17 は、プログラム・ステータス・ワードのビット 5 と共に、変換モードを制御する。

【 0 0 5 3 】

条件コード ( C C ) : ビット 18 及び 19 は 2 ビットの条件コードである。条件コードは、特定の命令の実行で得られた結果に応じて、0、1、2、又は 3 に設定される。ほとんどの算術演算及び論理演算、並びに幾つかの他の演算は、条件コードを設定する。BRANCH ON CONDITION 命令は、分岐のための基準として、条件コード値のいずれかの選択を指定することができる。

[ 0 0 5 4 ]

命令アドレス：プログラム・ステータス・ワードのビット 64 - 127 は、命令アドレスである。このアドレスは、CPU が待機状態（プログラム・ステータス・ワードのビット 14 が 1）でない限り、次に実行される命令の最左端のバイトの位置を指示する。

[ 0 0 5 5 ]

## アドレスのタイプ及びフォーマット

主ストレージをアドレス指定するために、絶対、実、及び仮想の3つの基本的なアドレスのタイプが認識される。アドレスは、ストレージ・アクセスの間にアドレスに適用される変形に基づいて区別される。アドレス変換は、仮想アドレスを実アドレスに変換する。プリフィックス付加は、実アドレスを絶対アドレスに変換する。3つの基本的なアドレス

・タイプに加えて、命令及びカレント・モードに応じて、3つの基本的なタイプのうちの1つ又は他の1つとして扱われる付加的なタイプが定義される。

#### 【0056】

##### 絶対アドレス

絶対アドレスは、主ストレージ位置に割り当てられたアドレスである。絶対アドレスは、いかなる変形も行われることなく、ストレージ・アクセスのために用いられる。構成内のチャネル・サブシステム及び全てのCPUは、同じ絶対アドレスを用いることによって、共有された主ストレージ位置を参照する。利用可能な主ストレージには、通常、0から始まる連続した絶対アドレスが割り当てられ、このアドレスは整数の境界上の完全な4キロバイトのブロックで割り当てられる。物理位置に割り当てられていないブロック内の絶対アドレスを用いようとする試行が行われた場合、例外が認識される。幾つかのモデルでは、オペレータが絶対アドレスと物理位置との間の対応を変更することを許可する、ストレージ再構成制御が提供されることがある。しかし、どの時点であっても、1つの物理位置に1つより多くの絶対アドレスが割り当てられることはない。その絶対アドレスに従って配列されたバイト位置から成るストレージを、絶対ストレージと呼ぶ。

10

#### 【0057】

##### 実アドレス

実アドレスは、実ストレージにおける位置を特定する。主ストレージへのアクセスのために実アドレスが用いられる場合には、実アドレスをプリフィックス付加によって変換して、絶対アドレスが形成される。任意の一瞬において、構成内のCPUごとに、実アドレスから絶対アドレスへのマッピングが1つ存在する。実アドレスが、CPUによって主ストレージにアクセスするために用いられる場合には、実アドレスをプリフィックス付加によって絶対アドレスに変換することができる。具体的な変形は、そのCPUのためのプリフィックス・レジスタ内の値によって定められる。その実アドレスに従って配列されたバイト位置から成るストレージを、実ストレージと呼ぶ。

20

#### 【0058】

##### 仮想アドレス

仮想アドレスは、仮想ストレージにおける位置を特定する。主ストレージへのアクセスのために仮想アドレスが用いられる場合には、仮想アドレスは、動的アドレス変換によって、プリフィックス付加を行うと絶対アドレスを形成することができる実アドレスに変換されるか、又は直接、絶対アドレスに変換されるかのいずれかである。

30

#### 【0059】

##### 一次仮想アドレス

一次仮想アドレスは、一次アドレス空間制御要素(PASC E)によって変換されるべき仮想アドレスである。論理アドレスは、一次空間モードにある場合に一次仮想アドレスとして扱われる。命令アドレスは、一次空間モード、二次空間モード、又はアクセス・レジスタ・モードにある場合に一次仮想アドレスとして扱われる。MOVE TO PRIMARYの第1オペランド・アドレス、及びMOVE TO SECONDARYの第2オペランド・アドレスは、一次仮想アドレスとして扱われる。

40

#### 【0060】

##### 二次仮想アドレス

二次仮想アドレスは、二次アドレス空間制御要素(SASC E)によって変換されるべき仮想アドレスである。論理アドレスは、二次空間モードにある場合に二次仮想アドレスとして扱われる。MOVE TO PRIMARYの第2オペランド・アドレス、及びMOVE TO SECONDARYの第1オペランド・アドレスは、二次仮想アドレスとして扱われる。

#### 【0061】

##### AR指定仮想アドレス

AR指定仮想アドレスは、アクセス・レジスタ指定アドレス空間制御要素によって変換されるべき仮想アドレスである。論理アドレスは、アクセス・レジスタ・モードにある場

50

合に A R 指定仮想アドレスとして扱われる。

【 0 0 6 2 】

## ホーム仮想アドレス

ホーム指定仮想アドレスは、ホーム・アドレス空間制御要素（H A S C E）によって変換されるべき仮想アドレスである。論理アドレス及び命令アドレスは、ホーム空間モードにある場合にホーム仮想アドレスとして扱われる。

【 0 0 6 3 】

## 命令アドレス

ストレージから命令をフェッチするために用いられるアドレスは、命令アドレスと呼ばれる。命令アドレスは、実モードにあるときには実アドレスとして扱われ、一次空間モード、二次空間モード、又はアクセス・レジスタ・モードにあるときには一次仮想アドレスとして扱われ、ホーム空間モードにあるときにはホーム仮想アドレスとして扱われる。カレント・プログラム・ステータス・ワード内の命令アドレス、及び EXECUTE のターゲット・アドレスは、命令アドレスである。

10

[ 0 0 6 4 ]

## 実効アドレス

ある状況においては、「実効アドレス」という用語を用いることが便利である。実効アドレスは、動的アドレス変換又はプリフィックス付加によるいずれかの変形が行われる前に存在するアドレスである。実効アドレスは、レジスタ内において直接指定されることもあり、又はアドレス算術演算の結果であることもある。アドレス算術演算は、ベースと変位との加算、又はベースとインデックスと変位との加算である。

30

〔 0 0 6 5 〕

## プリフィックス付加

プリフィックス付加は、実アドレスの 0 - 8191 の範囲を、CPUごとに絶対ストレージ内の異なるブロックに割り当て、それにより、特に割り込みの処理の際に、主ストレージを共有する 1 つより多くの CPU が最小限の干渉で同時に動作することを可能にする能力を提供する。プリフィックス付加により、0 - 8191 の範囲の実アドレスを、その CPU のためのプリフィックス・レジスタのビット位置 0 - 50 における値によって識別される 8 K バイトの絶対アドレス・ブロック（プリフィックス領域）に 1 対 1 で対応させ、且つ、プリフィックス・レジスタ内のその値によって識別される実アドレス・ブロックを、絶対アドレス 0 - 8191 に 1 対 1 で対応させる。残りの実アドレスは、対応する絶対アドレスと同一である。この変形により、各 CPU は、最初の 8 K バイトと、他の CPU のプリフィックス・レジスタによって指示される位置とを含む、主ストレージの全てにアクセスする事が可能になる。

30

〔 0 0 6 6 〕

プリフィックスは、プリフィックス・レジスタのビット位置 0 - 5 0 に含まれる 5 1 ビット量である。一実施形態において、プリフィックス・レジスタは、以下のフォーマットを有する。

【表 6】

|       |                  |    |

|-------|------------------|----|

| 0     | ブリフィックス・ビット33-50 | 31 |

| 32-33 | 51               | 63 |

10

## プリフィックス・レジスタのフォーマット

[ 0 0 6 7 ]

プリフィックス付加が適用された場合、実アドレスは、実アドレスのビット 0 - 50 に応じて、以下の規則のうちの 1 つを用いることによって絶対アドレスに変形される。即ち

50

アドレスのビット 0 - 50 は、全てが 0 であれば、プリフィックスのビット 0 - 50 で置き換えられる。

アドレスのビット 0 - 50 は、プリフィックスのビット 0 - 50 と等しければ、0 で置き換えられる。

アドレスのビット 0 - 50 は、0 でないものがあり、且つプリフィックスのビット 0 - 50 と等しくなければ、変更されないままである。

#### 【0068】

ストレージに提示されたアドレスのみがプリフィックス付加によって変換される。アドレスのソースの内容は変更されないままである。

#### 【0069】

実アドレスと絶対アドレスとは、プリフィックス・レジスタが全て 0 を含み、従って実アドレスと対応する絶対アドレスとが同一である場合でさえ、区別される。

10

#### 【0070】

図 15 は、実アドレスと絶対アドレスとの間の関係を示す。

#### 【0071】

アドレス空間は、整数番号の連続シーケンス（仮想アドレス）であり、各番号をストレージ内のバイト位置に関連付けることを可能にする特定の変形パラメータを伴う。シーケンスは、0 から開始して左から右へと進む。

#### 【0072】

仮想アドレスは、CPU によって主ストレージにアクセスするために用いられる場合、最初に、動的アドレス変換 (DAT) によって実アドレス又は絶対アドレスに変換される。実アドレスに対してさらにプリフィックス付加を行って、絶対アドレスを形成することができる。DAT は、変形パラメータとして、領域第 1 テーブル、領域第 2 テーブル、領域第 3 テーブル、セグメント・テーブル、及びページ・テーブルを用いることができる。特定のアドレス空間のための最も高位のレベルのテーブルの指示（基点及び長さ）はアドレス空間制御要素 (ASC E) と呼ばれ、これは、DAT による使用のために制御レジスタ内に見出されるか、又はアクセス・レジスタによって指定された通りのものである。あるいは、アドレス空間のための ASC E が実空間指示の場合もあり、これは、DAT が、いかなるテーブルも用いることなく単に仮想アドレスを実アドレスとして扱うことで仮想アドレスを変換するということを示す。

20

#### 【0073】

DAT は、異なる時点で、異なる制御レジスタ内の ASC E か、又はアクセス・レジスタによって指定された ASC E を用いる。選択は、カレント・プログラム・ステータス・ワードにおいて指定される変換モードによって決定される。一次空間モード、二次空間モード、アクセス・レジスタ・モード、及びホーム空間モードの 4 つの変換モードが利用可能である。変換モードに応じて、異なるアドレス空間をアドレス指定することが可能である。

30

#### 【0074】

CPU が一次空間モード又は二次空間モードにある場合にはいつでも、CPU は、2 つのアドレス空間、即ち一次アドレス空間及び二次アドレス空間に属する仮想アドレスを変換することができる。CPU がアクセス・レジスタ・モードにある場合にはいつでも、CPU は、最大で 16 個のアドレス空間、即ち、一次アドレス空間及び最大で 15 個の AR 指定アドレス空間の仮想アドレスを変換することができる。CPU がホーム空間モードにある場合にはいつでも、CPU は、ホーム・アドレス空間の仮想アドレスを変換することができる。

40

#### 【0075】

一次アドレス空間は、一次アドレス空間制御要素 (PASC E) によって変換される一次仮想アドレスから成るので、それ自体として識別される。同様に、二次アドレス空間は、二次アドレス空間制御要素 (SASC E) によって変換される二次仮想アドレスから成る。AR 指定アドレス空間は、アクセス・レジスタ指定アドレス空間制御要素 (AR 指定

50

A S C E ) によって変換される A R 指定仮想アドレスから成り、ホーム・アドレス空間は、ホーム・アドレス空間制御要素 ( H A S C E ) によって変換されるホーム仮想アドレスから成る。一次 A S C E 及び二次 A S C E は、それぞれ制御レジスタ 1 及び 7 の中にある。A R 指定 A S C E は、制御レジスタ 1 及び 7 の中にある場合もあり、又は、A S N 第 2 テーブル・エントリと呼ばれるテーブル・エントリの中にある場合もある。H A S C E は、制御レジスタ 1 3 の中にある。

#### 【 0 0 7 6 】

##### 動的アドレス変換

動的アドレス変換は、仮想アドレスを（例えば、ストレージ参照中に）対応するメイン・メモリ・アドレス（本実施形態においては実アドレス又は絶対アドレス）に変換するプロセスである。仮想アドレスは、一次仮想アドレス、二次仮想アドレス、アクセス・レジスタ指定仮想アドレス、又はホーム仮想アドレスとすることができます。これらのアドレスは、それぞれ、P A S C E 、S A S C E 、A R 指定 A S C E 、又はH A S C E によって変換される。適切な A S C E を選択した後の変換プロセスは、4つのタイプの仮想アドレスの全てについて同一である。

#### 【 0 0 7 7 】

##### アドレス指定変換モード

実効アドレスは、動的アドレス変換又はプリフィックス付加によるいずれかの変形が行われる前に存在するアドレス（仮想アドレス）である。動的アドレス変換を制御するプログラム・ステータス・ワード内の3つのビットは、D A T モード・ビットであるビット 5 と、アドレス空間制御ビットであるビット 1 6 及び 1 7 である。D A T モード・ビットが 0 である場合、D A T はオフであり、C P U は実モードにある。D A T モード・ビットが 1 の場合、D A T はオンであり、C P U はアドレス空間制御ビットによって指示される変換モードにある。即ち、二進数字 0 0 は一次空間モードを指示し、二進数字 0 1 はアクセス・レジスタ・モードを指示し、二進数字 1 0 は二次空間モードを指示し、二進数字 1 1 はホーム空間モードを指示する。種々のモードを、各モードにおけるアドレスの取り扱いと共に以下に示す。

#### 【表 7 】

| P S Wビット |    |    | DAT | モード           | アドレスの取り扱い |          |

|----------|----|----|-----|---------------|-----------|----------|

| 5        | 16 | 17 |     |               | 命令アドレス    | 論理アドレス   |

| 0        | 0  | 0  | オフ  | 実モード          | 実         | 実        |

| 0        | 0  | 1  | オフ  | 実モード          | 実         | 実        |

| 0        | 1  | 0  | オフ  | 実モード          | 実         | 実        |

| 0        | 1  | 1  | オフ  | 実モード          | 実         | 実        |

| 1        | 0  | 0  | オン  | 一次空間モード       | 一次仮想      | 一次仮想     |

| 1        | 0  | 1  | オン  | アクセス・レジスタ・モード | 一次仮想      | A R 指定仮想 |

| 1        | 1  | 0  | オン  | 二次空間モード       | 一次仮想      | 二次仮想     |

| 1        | 1  | 1  | オン  | ホーム空間モード      | ホーム仮想     | ホーム仮想    |

#### 変換モード

#### 【 0 0 7 8 】

プログラム・ステータス・ワードは 1 2 8 ビット・ワードであり、これは、一部が、アドレス指定モードを示す 2 ビットを与える。一実施形態において、ビット 3 1 は拡張アドレス指定モード ( E A ) ビットであり、ビット 3 2 はベース・アドレス指定モード ( B A ) ビットである。これらの 2 つのビットは、アドレスのサイズを示す。これらの 2 つのビットの各々の状態は、二進数（1 又は 0）である。E A ビットが 0 であり、且つ B A ビットが 0 であるならば、2 4 ビット・アドレス指定が示される。2 4 ビット・アドレス指定

10

20

30

40

50

が示される場合、64ビット・ワード(64ビット・エンティティは一般に倍長語と呼ばれる)のビット40-63が、アドレスが配置される位置である。命令アドレスが128ビット・エンティティ(4倍長語)の2番目の64ビットを占める場合、プログラム・ステータス・ワードにおけるビット位置は以下の通りである。24ビット・モードでは、命令アドレスは、プログラム・ステータス・ワードのビット104-127に置かれる。31ビット・モードでは、命令アドレスは、プログラム・ステータス・ワードのビット97-127に置かれる。64ビット・モードでは、命令アドレスは、プログラム・ステータス・ワードのビット64-127に置かれる。EAビットが0であり、且つBAビットが1であるならば、31ビット・アドレス指定が示される。適切な64ビット・ワードは、ビット位置33-63に配置された31ビット・アドレスを含む。EAビットが1であり、且つBAビットが1であるならば、64ビット・ワードのビット0-63、即ち64ビット全体がアドレスを含む。そうでない場合には、例外条件が示される。一旦、アドレス指定モードが取得されると、ASC Eを決定する必要がある。

#### 【0079】

##### アドレス空間制御要素(ASC E)

ここで、プログラム・ステータス・ワードを用いて仮想アドレスの動的アドレス変換のための実効アドレス空間制御要素(ASC E)を決定する方法の一実施形態を示す、図3を参照する。ASC Eは、例えば、2ギガバイト(ギガ=2<sup>30</sup>)のアドレス空間を指定することができる。又は、ASC Eは、例えば、4テラバイト(テラ=2<sup>40</sup>)、8ペタバイト(ペタ=2<sup>50</sup>)、又は16エクサバイト(エクサ=2<sup>60</sup>)のアドレス空間を指定することができる。又は、ASC Eは、実空間指示を指定することができる。実空間指示は、仮想アドレスを、1つ又は複数のアドレス変換テーブルを参照することなく、ストレージ内で実アドレスとして扱うようにさせる。

#### 【0080】

プログラム・ステータス・ワード300は、変換(T)ビット302及びアドレス空間(AS)ビット304を含む。306において、変換(T)ビットが0であれば、アドレスは実アドレス326である。308において、アドレス空間(AS)が0に等しければ(二進数字00)、この仮想アドレスのための実効ASC Eは、一次アドレス空間制御要素(PASC E)310である。312において、アドレス空間(AS)が1に等しければ(二進数字01)、実効ASC Eは、アクセス・レジスタ指定アドレス空間制御要素314である。316において、アドレス空間(AS)が2に等しければ(二進数字10)、実効ASC Eは、二次アドレス空間制御要素(SASC E)318である。それ以外の場合には、アドレス空間(AS)は3に等しく(二進数字11)、実効ASC Eはホーム・アドレス空間制御要素(HASC E)322である。

#### 【0081】

実効ASC Eを選択した後の動的アドレス変換プロセスは、好ましくは、4つのタイプの仮想アドレスの全てについて同一である。

#### 【0082】

セグメント・テーブル指示又は領域テーブル指示は、オペレーティング・システムによって実ストレージ又は絶対ストレージ内に確立されたテーブルによる変換を実行させる。実空間指示は、ストレージ内のテーブルを用いることなく、仮想アドレスを単に実アドレスとして扱わせる。

#### 【0083】

セグメント・テーブル指示又は領域テーブル指示を用いる場合の変換プロセスにおいて、3つのタイプの情報単位、即ち、領域、セグメント、及びページが認識される。領域は、2ギガバイトにわたり、且つ2ギガバイト境界から始まる逐次的な仮想アドレス・ブロックである。セグメントは、1ギガバイトにわたり、且つ1ギガバイト境界から始まる逐次的な仮想アドレス・ブロックである。ページは、4キロバイトにわたり、且つ4キロバイト境界から始まる逐次的な仮想アドレス・ブロックである。

#### 【0084】

10

20

30

40

50

### 仮想アドレスのフォーマット

仮想アドレスの変換は、実アドレス又は絶対アドレスを取得するために、変換テーブル階層構造の複数の変換テーブルを参照することを伴うことができる。実アドレスに対してさらにプリフィックス付加を行って、絶対アドレスを形成することができる。仮想アドレスは、変換テーブル階層構造の変換テーブル内のエントリに対するインデックスを含む。仮想アドレスは、従って、4つの主要フィールドに分割される。ビット0 - 32は領域インデックス(RX)と呼ばれ、ビット33 - 43はセグメント・インデックス(SX)と呼ばれ、ビット44 - 51はページ・インデックスと呼ばれ、ビット52 - 63はバイト・インデックス(BX)と呼ばれる。一実施形態において、仮想アドレスは以下のフォーマットを有する。

10

【表8】

| RX | SX | PX | BX |

|----|----|----|----|

| 0  | 33 | 44 | 52 |

### 仮想アドレスのフォーマット

【0085】

仮想アドレス空間は、そのASC Eによって決定される通りに、1つの領域から成る2ギガバイトの空間とすることができる、又は最大8ギガバイト領域から成る最大で16エクサバイトまでの空間とすることができます。2ギガバイトのアドレス空間に適用される仮想アドレスのRX部分は、全て0でなければならない。そうでない場合には、例外が認識される。仮想アドレスのRX部分は、それ自体が3つのフィールドに分割される。ビット0 - 10は領域第1インデックス(RFX)と呼ばれ、ビット11 - 21は領域第2インデックス(RSX)と呼ばれ、ビット22 - 32は領域第3インデックス(RTX)と呼ばれる。一実施形態において、仮想アドレスのビット0 - 32は、以下のフォーマットを有する。

20

【表9】

| RFX | RSX | RTX |    |

|-----|-----|-----|----|

| 0   | 11  | 22  | 33 |

### 仮想アドレスのRXのフォーマット

【0086】

RTXが最左端の有効部分(significant part)となっている仮想アドレス(42ビット・アドレス)は、4テラバイト(2048領域)をアドレス指定することができ、RSXが最左端の有効部分となっている仮想アドレス(53ビット・アドレス)は、8ペタバイト(4,193,044領域)をアドレス指定することができ、RFXが最左端の有効部分となっている仮想アドレス(64ビット・アドレス)は、16エクサバイト(8,589,934,592領域)をアドレス指定することができる。

30

【0087】

RXが0である仮想アドレスは、2つの変換テーブル、即ちセグメント・テーブル及びページ・テーブルによって実アドレスに変換することができる。EDATファシリティがイネーブルであれば、変換はセグメント・テーブルのみで完了させることができる。RFXは非0であってもよく、その場合は、領域第1テーブル、領域第2テーブル、及び領域第3テーブルが必要とされる。RFXが0である場合でも、RSXが非0であってもよく、その場合、領域第2テーブル及び領域第3テーブルが必要とされる。RFX及びRSXが0である場合でも、RTXは非0であってもよく、その場合、領域第3テーブルが必要とされる。

40

50

## 【0088】

あるアドレス空間のための A S C E が、そのアドレス空間に対する参照を変換するためには必要とされる最も高レベルのテーブル（領域第 1 テーブルから始まり、下位に向けてセグメント・テーブルまで続く）を指示していない場合、例外が認識される。

## 【0089】

## 仮想アドレスの動的変換

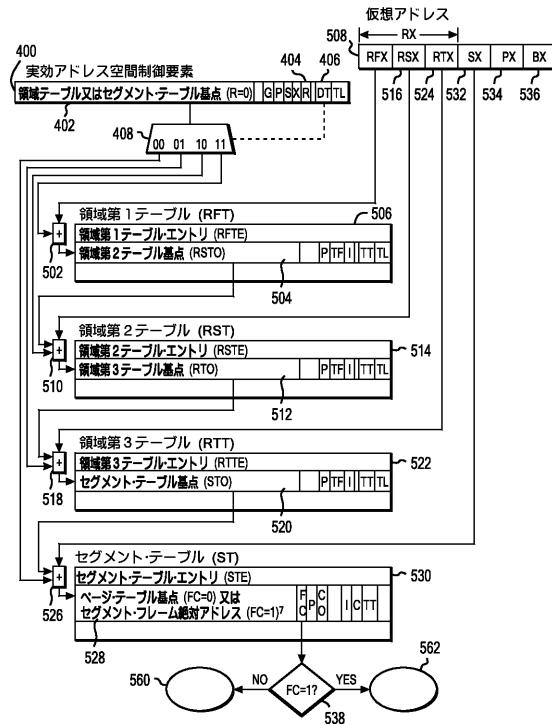

ここで、図 3 において決定された実効 A S C E を用いて、仮想アドレスの変換に用いられる変換テーブル階層構造内の最初の変換テーブルを決定する一実施形態を示す、図 4 を参照する。

## 【0090】

一実施形態において、制御レジスタ 1 ( C R 1 ) は P A S C E を含む。制御レジスタ 7 ( C R 7 ) は S A S C E を含む。制御レジスタ 13 ( C R 13 ) は H A S C E を含み、アクセス・レジスタ変換 ( A R T ) プロセスによって導出されるアドレス空間第 2 テーブル・エントリ ( A S T E ) はアクセス・レジスタ指定アドレス空間制御要素を含む。実効 A S C E 4 0 0 は、これらの位置のうちの 1 つから選択される。

## 【0091】

実効 A S C E 4 0 0 の第 1 の部分は、領域第 1 テーブル、領域第 2 テーブル、領域第 3 テーブル、又はセグメント・テーブルのうちのいずれかを指示する基点アドレスを含んだテーブル基点 4 0 2 を含む。テーブル基点 ( ビット 0 . . . 5 1 ) に対して 12 個の二進数字 0 が付加されると、仮想アドレスの変換に用いられる変換テーブル階層構造の中で最も高位の変換テーブルの 64 ビットの基点アドレスが形成される。実効 A S C E 4 0 0 はさらに、実空間制御 ( R ) ビット 4 0 4 及び D T ビット 4 0 6 も含む。実空間制御 ( R ) ビットが 0 の場合、どの特定の基点アドレスがテーブル基点 4 0 2 であるのかを判定するために D T がセレクタ 4 0 8 によってデコードされる。D T ビットが 3 ( 二進数字 1 1 ) に等しい場合、テーブル基点 4 0 2 は領域第 1 テーブル 4 1 0 を指示する。D T ビットが 2 ( 二進数字 1 0 ) に等しい場合、テーブル基点 4 0 2 は領域第 2 テーブル 4 1 2 を指示する。D T ビットが 1 ( 二進数字 0 1 ) に等しい場合、テーブル基点 4 0 2 は領域第 3 テーブル 4 1 4 指示する。そうではなくて、D T ビットが 0 ( 二進数字 0 0 ) に等しい場合、テーブル基点 4 0 2 はセグメント・テーブル 4 1 6 を指示する。

## 【0092】

領域第 1 テーブル、領域第 2 テーブル、又は領域第 3 テーブルは、単に領域テーブルと呼ばれることがある。同様に、領域第 1 テーブル指示、領域第 2 テーブル指示、又は領域第 3 テーブル指示は、領域テーブル指示と呼ばれることもある。領域テーブル、セグメント・テーブル、及びページ・テーブルは、実ストレージの現在の割り当てを反映する。ページは、仮想ストレージの割り当てに対して用いられる用語である。実ストレージは固定ブロック単位で割り振られる。ページは、逐次的な仮想アドレスの組に対して割り当てられた場合でさえも、実ストレージ内で隣接している必要はない。

## 【0093】

変換に用いられる A S C E が領域第 1 テーブル指示である場合には、変換プロセスは、例えば、領域第 1 テーブル、領域第 2 テーブル、領域第 3 テーブル、セグメント・テーブル、及び随意にページ・テーブルを用いたマルチ・レベル・ルックアップから成る。これらのテーブルは、実ストレージ又は絶対ストレージ内に存在する。A S C E が、領域第 2 テーブル指示、領域第 3 テーブル指示、又はセグメント・テーブル指示である場合、指示されたレベルより高位のレベルのテーブルにおけるルックアップは省かれ、より高位レベルのテーブル自体が省かれる。

## 【0094】

ここで、変換テーブル階層構造を用いた仮想アドレスの動的アドレス変換の一実施形態を示す、図 5 を参照する。

## 【0095】

図 4 の実効 A S C E 4 0 0 は、指示タイプ ( D T ) ビット 4 0 6 を含む。A S C E の実

10

20

30

40

50

空間制御( R )ビット 4 0 4 が 0 の場合、テーブル基点 4 0 2 がどの基点アドレスを指示するのかを判定するために、DT ビットはセレクタ 4 0 8 によってデコードされる。実空間制御( R )ビットが 1 の場合、動的アドレス変換は、図 6 のノード D 5 6 4 において示されるようにして行われる。

【 0 0 9 6 】

セレクタ 4 0 8 において、DT ビットが 3 (二進数字 1 1 ) に等しい場合、変換テーブル階層構造において指示される最初のテーブルは、領域第 1 テーブルである。テーブル基点 4 0 2 に対して、5 0 2 において、仮想アドレスの領域第 1 インデックス ( R F X ) 5 0 8 部分が算術的に加算され、領域第 1 テーブル内の領域第 1 テーブル・エントリ 5 0 6 が参照される。テーブル基点 (右側に 1 2 個の 0 が付加されたもの、又は 4 0 9 6 を乗じたもの) が、インデックスに 8 を乗じた積 (又は右側に 3 つの 0 が付加されたインデックス) に対して加算される。領域第 1 テーブル・エントリは、変換に用いられる変換テーブル階層構造の中で次に下位のテーブルに対する領域第 2 テーブル基点 5 0 4 を含む。領域第 1 テーブルの次に下位のテーブルは、領域第 2 テーブルである。領域第 1 テーブル・エントリの無効 ( I ) ビットが 1 に等しい場合には、その領域第 1 テーブル・エントリは無効であり、変換に用いることはできない。例外条件が示される。

10

【 0 0 9 7 】

セレクタ 4 0 8 において、DT ビットが 2 (二進数字 1 0 ) に等しい場合、変換テーブル階層構造において指示される最初のテーブルは、領域第 2 テーブルである。テーブル基点 4 0 2 に対して、5 1 0 において、仮想アドレスの領域第 2 インデックス ( R S X ) 5 1 6 部分が算術的に加算され、領域第 2 テーブル内の領域第 2 テーブル・エントリ 5 1 4 が参照される。テーブル基点 (右側に 1 2 個の 0 が付加されたもの、又は 4 0 9 6 を乗じたもの) が、インデックスに 8 を乗じた積 (又は右側に 3 つの 0 が付加されたインデックス) に対して加算される。領域第 2 テーブル・エントリは、変換に用いられる変換テーブル階層構造の中で次に下位のテーブルに対する領域第 3 テーブル基点 5 1 2 を含む。領域第 2 テーブルの次に下位のテーブルは、領域第 3 テーブルである。領域第 2 テーブル・エントリの無効 ( I ) ビットが 1 に等しい場合には、その領域第 2 テーブル・エントリは無効であり、例外条件が示される。

20

【 0 0 9 8 】

セレクタ 4 0 8 において、DT ビットが 1 (二進数字 ( 0 1 ) に等しい場合、変換テーブル階層構造において指示される最初のテーブルは、領域第 3 テーブルである。テーブル基点 4 0 2 に対して、5 1 8 において、仮想アドレスの領域第 3 インデックス ( R T X ) 5 2 4 部分が算術的に加算され、領域第 3 テーブル内の領域第 3 テーブル・エントリ 5 2 2 が参照される。テーブル基点 (右側に 1 2 個の 0 が付加されたもの、又は 4 0 9 6 を乗じたもの) が、インデックスに 8 を乗じた積 (又は、右側に 3 つの 0 が付加されたインデックス) に対して加算される。領域第 3 テーブル・エントリは、変換に用いられる変換テーブル階層構造の中で次に下位のテーブルに対するセグメント・テーブル基点 5 2 0 を含む。領域第 3 テーブルの次に下位のテーブルは、セグメント・テーブルである。領域第 3 テーブル・エントリの無効 ( I ) ビットが 1 に等しい場合には、その領域第 3 テーブル・エントリは無効であり、例外条件が示される。

30

【 0 0 9 9 】

セレクタ 4 0 8 において、DT ビットが 0 (二進数字 ( 0 0 ) に等しい場合、変換テーブル階層構造において指示される最初のテーブルは、セグメント・テーブルである。テーブル基点 4 0 2 に対して、5 2 6 において、仮想アドレスのセグメント・インデックス ( S X ) 5 3 2 部分が算術演算的に加算され、セグメント・テーブル内のセグメント・テーブル・エントリ 5 3 0 が参照される。テーブル基点 (右側に 1 2 個の 0 が付加されたるか、又は 4 0 9 6 を乗じたもの) が、インデックスに 8 を乗じた積 (又は右側に 3 つの 0 が付加されたインデックス) に対して加算される。セグメント・テーブル・エントリは、どちらも 5 2 8 で示される、ページ・テーブルに対する基点アドレスか、又はセグメント・フレーム絶対アドレス ( S F A A ) を含む。セグメント・テーブル・エントリの無効 ( I )

40

) ビットが 1 に等しい場合には、そのセグメント・テーブル・エントリは無効であり、例外条件が示される。

【 0 1 0 0 】

538において、セグメント・テーブルの S T E フォーマット制御 ( F C ) ビットが検査される。S T E フォーマット制御が 1 である場合、セグメント・テーブル・エントリ 530 はセグメント・フレーム絶対アドレス ( S F A A ) 552 を含み、動的アドレス変換は図 7 のノード 562 を参照して続行する。そうでない場合には、セグメント・テーブルから取得されたセグメント・テーブル・エントリはページ・テーブル基点アドレスを含み、動的アドレス変換は図 6 のノード 560 を参照して続行する。

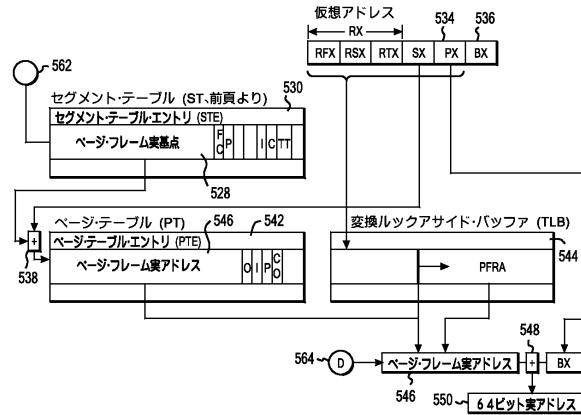

【 0 1 0 1 】

ここで、図 6 を参照する。セグメント・テーブル・エントリ内の S T E フォーマット制御が 0 である場合、セグメント・テーブルから取得されたセグメント・テーブル・エントリは、変換テーブル階層構造の中で次に下位のテーブルに対する基点アドレスを含む。セグメント・テーブルの次に下位のテーブルは、ページ・テーブルである。図 5 のセグメント・テーブル・エントリ 530 から取得されたページ・テーブル基点 528 に対して、538において、仮想アドレスのページ・インデックス ( P X ) 534 部分が算術的に加算され、ページ・テーブル内のページ・テーブル・エントリ 542 が参照される。ページ・テーブル・エントリは、ページ・フレーム実アドレス ( P F R A ) 546 を含む。ページ・フレーム実アドレスの最左端のビットが、548において、仮想アドレスのバイト・インデックス ( B X ) 536 部分に連結されると、64 ビットの実アドレス 550 が得られる。64 ビット実アドレスに対してさらにプリフィックス付加操作を行って、絶対アドレスを形成することができる。変換された仮想アドレスは、主ストレージ又はメモリ内の所望の 4 キロバイト ( 4096 バイト ) のデータ・ブロックを参照する。

【 0 1 0 2 】

好ましくは、仮想アドレスからメモリ・アドレスへの動的アドレス変換に用いられた情報は、変換ルックアサイド・バッファ・エントリ・タグ内に、その仮想アドレスと関連付けられたメモリのブロックのアドレスと共にストアされる。その後のストレージ・アクセスは、A S C E 情報及び仮想アドレス情報を変換ルックアサイド・バッファ・タグと比較することによって、仮想アドレスを迅速に変換することができる。あるタグがその仮想アドレスのものであることが分かれば、関与する各変換テーブルへの時間のかかる逐次的なアクセスを実行する代わりに、そのメモリ・ブロックの変換ルックアサイド・バッファ・アドレスを用いることができる。一実施形態において、ページ・フレーム実アドレス ( P F R A ) は、例えば、A S C E と仮想アドレスの R X 、 S X 及び P X 部分とから成るタグと共に、変換ルックアサイド・バッファ 544 のエントリ内にストアされる。この仮想アドレスのその後の変換は、これ以降、変換ルックアサイド・バッファ内にストアされた情報から導出される。

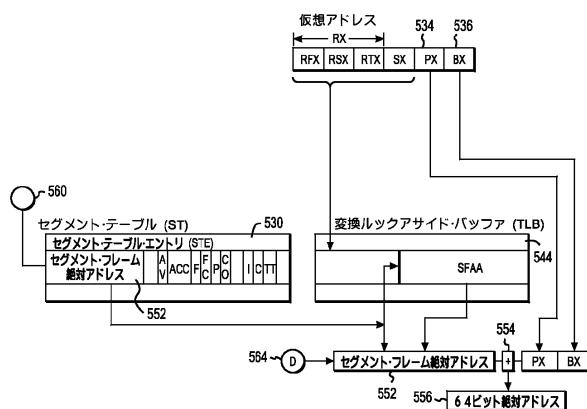

【 0 1 0 3 】

ここで、図 5 C を参照する。セグメント・テーブル・エントリ 530 内の S T E フォーマット制御が 1 である場合、セグメント・テーブル・エントリは、セグメント・フレーム絶対アドレス ( S F A A ) 552 を含む。セグメント・フレーム絶対アドレスの最左端のビットが、554において、仮想アドレスのページ・インデックス 534 部分及びバイト・インデックス 536 部分に連結されると、64 ビットの絶対アドレス 556 が得られる。変換された仮想アドレスは、主ストレージ又はメモリ内の所望の大データ・ブロックを参照する。大データ・ブロックは少なくとも 1 メガバイト ( 1,048,576 バイト ) のサイズである。

【 0 1 0 4 】

一実施形態において、セグメント・フレーム絶対アドレス ( S F A A ) は、仮想アドレスの R X 及び S X 部分と共に、変換ルックアサイド・バッファ 544 内にストアされる。この仮想アドレスのその後の変換は、これ以降、変換ルックアサイド・バッファ内にストアされた情報から導出される。

10

20

30

40

50

## 【0105】

## 変換テーブル・エントリのフォーマット

変換に用いられる変換テーブル階層構造における種々の変換テーブル・エントリの実施形態は以下の通りである。

## 【0106】

## 領域テーブル・エントリ

「領域テーブル・エントリ」という用語は、領域第1テーブル・エントリ、領域第2テーブル・エントリ、又は領域第3テーブル・エントリを意味する。領域第1テーブル、領域第2テーブル、及び領域第3テーブルからフェッチされたエントリは、以下のフォーマットを有する。あるエントリを含むテーブルのレベル（第1、第2、又は第3）は、エントリ内のテーブル・タイプ（TT）ビットによって識別される。

10

## 【0107】

一実施形態において、領域第1テーブル・エントリ、領域第2テーブル・エントリ、及び領域第3テーブル・エントリのフォーマットは以下の通りである。

## 【表10】

## 領域第1テーブル・エントリ（TT=11）

| 領域第2テーブル基点 |    |    |    |    |    |    |    |    |

|------------|----|----|----|----|----|----|----|----|

| 32         | 31 | 30 | 29 | P  | TF | I  | TT | TL |

| 52         | 54 | 56 | 58 | 59 | 60 | 62 | 63 |    |

## 領域第2テーブル・エントリ（TT=10）

| 領域第3テーブル基点 |    |    |    |    |    |    |    |    |

|------------|----|----|----|----|----|----|----|----|

| 32         | 31 | 30 | 29 | P  | TF | I  | TT | TL |

| 52         | 54 | 56 | 58 | 59 | 60 | 62 | 63 |    |

## 領域第3テーブル・エントリ（TT=01）

| セグメント・テーブル基点 |    |    |    |    |    |    |    |    |

|--------------|----|----|----|----|----|----|----|----|

| 32           | 31 | 30 | 29 | P  | TF | I  | TT | TL |

| 52           | 54 | 55 | 55 | 59 | 60 | 62 | 63 |    |

## 領域テーブル・エントリのフォーマット

## 【0108】

領域第2テーブル基点、領域第3テーブル基点、及びセグメント・テーブル基点：領域第1テーブル・エントリは、領域第2テーブル基点を含む。領域第2テーブル・エントリは、領域第3テーブル基点を含む。領域第3テーブル・エントリは、セグメント・テーブル基点を含む。以下の説明は3つのテーブル基点の各々に対して適用される。エントリのビット0 - 51は、右に12個の0を付加すると、次に下位レベルのテーブルの開始を指

50

示する 64 ビットのアドレスを形成する。

【 0109 】

D A T 保護ビット ( P ) : 強化型 D A T が適用される場合には、ビット 54 は、変換に用いられる後続の各領域テーブル・エントリ、セグメント・テーブル・エントリ、及び、適用可能な場合にはページ・テーブル・エントリの中の D A T 保護ビットと O R (論理和) 演算されたものとして扱われる。それゆえ、そのビットが 1 であるときには、D A T 保護は、領域全体又は領域テーブル・エントリによって指定される領域に対して適用される。強化型 D A T ファシリティがインストールされていない場合、又はファシリティはインストールされているが強化型 D A T イネーブルメント制御が 0 である場合には、領域テーブル・エントリのビット 54 は無視される。

10

【 0110 】

領域第 2 テーブル・オフセット、領域第 3 テーブル・オフセット、及びセグメント・テーブル・オフセット ( T F ) : 領域第 1 テーブル・エントリは、領域第 2 テーブル・オフセットを含む。領域第 2 テーブル・エントリは、領域第 3 テーブル・オフセットを含む。領域第 3 テーブル・エントリは、セグメント・テーブル・オフセットを含む。以下の説明は、3 つのテーブル・オフセットの各々に対して適用される。エントリのビット 56 及び 57 は、次に下位レベルのテーブルの中で、テーブルの始めのところで欠落している部分の長さを指定するものであり、即ち、このビットは、次に下位レベルのテーブル内で実際に存在する最初のエントリの位置を指定する。このビットは、欠落部分の長さを 4, 096 バイト単位で指定するので、従って、欠落部分の長さは 512 エントリの倍数として可変になる。4, 096 バイト単位で表された欠落部分の長さは、T F の値に等しい。オフセット・フィールドの内容を、長さフィールドであるビット 62 及び 63 と組み合わせて用いて、次に下位レベルのテーブルによって変換される仮想アドレスの部分 ( R S X 、 R T X 、又は S X ) がテーブル内に実際に存在するエントリを指示するのかどうかが確立される。

20

【 0111 】

領域無効ビット ( I ) : 領域第 1 テーブル・エントリ又は領域第 2 テーブル・エントリ内のビット 58 は、そのエントリに関連付けられた領域の組が利用可能かどうかを制御する。領域第 3 テーブル・エントリ内のビット 58 は、エントリに関連付けられた単一の領域が利用可能であるかどうかを制御する。ビット 58 が 0 である場合には、アドレス変換は領域テーブル・エントリを用いることによって進行する。ビットが 1 である場合には、そのエントリを変換に用いることはできない。

30

【 0112 】

テーブル・タイプ・ビット ( T T ) : 領域第 1 テーブル・エントリ、領域第 2 テーブル・エントリ、又は領域第 3 テーブル・エントリのビット 60 及び 61 は、そのエントリを含むテーブルのレベルを以下のように識別する。ビット 60 及び 61 は、変換に用いられる A S C E であるテーブル指示のタイプ、及び、それまでに用いられたテーブル・レベルの数を考慮して、正しいテーブル・レベルを識別しなければならない。そうでない場合には、変換指定例外 ( translation specification exception ) が認識される。以下のテーブルはテーブル・タイプ・ビットを示す。

40

【表 1 1】

| ビット 60 及び 61 | 領域テーブル・レベル |

|--------------|------------|

| 11           | 第1         |

| 10           | 第2         |

| 01           | 第3         |

### 領域テーブル・エントリのための テーブル・タイプ・ビット

10

【0 1 1 3】

領域第2テーブル長、領域第3テーブル長、及びセグメント・テーブル長 (TL)：領域第1テーブル・エントリは、領域第2テーブル長を含む。領域第2テーブル・エントリは、領域第3テーブル長を含む。領域第3テーブル・エントリは、セグメント・テーブル長を含む。以下の説明は、3つのテーブル長の各々に対して適用される。エントリのビット62及び62は、次に下位レベルのテーブルの長さを4,096バイト単位で指定するので、従って、テーブルの長さは512エントリの倍数として可変になる。4,096バイト単位で表された次に下位レベルのテーブルの長さは、TLの値より1大きい。長さフィールドの内容を、オフセット・フィールドであるビット56及び57と組み合わせて用いて、次に下位レベルのテーブルによって変換される仮想アドレスの部分 (RSX、RTX、又はSX) がテーブル内に実際に存在するエントリを指示するかどうかを確立する。領域テーブル・エントリの他の全てのビット位置は、可能性のある将来的な拡張のために未使用とされ、0を含むべきである。そうしなければ、プログラムが将来、互換的に動作できなくなるおそれがある。強化型DATが適用される場合、領域テーブル・エントリ内の未使用のビット位置は、そのテーブル・エントリがたとえ無効だとしても、0を含むべきである。

20

【0 1 1 4】

### セグメント・テーブル・エントリ

30

強化型DATが適用されない場合、又は強化型DATは適用されるが、STEフォーマット制御、即ちセグメント・テーブル・エントリのビット53が0である場合には、セグメント・テーブルからフェッチされるエントリは、一実施形態において、以下のフォーマットを有する。

【表 1 2】

### セグメント・テーブル・エントリ (T=00, FC=0)

|                 |        |   |  |        |        |  |  |

|-----------------|--------|---|--|--------|--------|--|--|

| ページ・テーブル基点      |        |   |  |        |        |  |  |

| 0               |        |   |  |        |        |  |  |

| ページ・テーブル基点 (続き) |        |   |  |        |        |  |  |

|                 | F<br>C | P |  | I<br>C | T<br>T |  |  |

32

53 54 55 58 59 60 52 63

31

40

### セグメント・テーブル・エントリのフォーマット I

【0 1 1 5】

強化型DATが適用され、且つSTEフォーマット制御が1である場合には、セグメント・テーブルからフェッチされるエントリは、一実施形態において、以下のフォーマットを有する。

## 【表13】

セグメント・テーブル・エントリ (T=00, FC=1)

| セグメント・フレーム絶対アドレス      |    |        |                |          |        |             |  |  |        |    |    |

|-----------------------|----|--------|----------------|----------|--------|-------------|--|--|--------|----|----|

| 0                     |    |        |                |          |        |             |  |  |        |    | 31 |

| セグメント・フレーム絶対アドレス (続き) |    | A<br>V | ACC            | F<br>C   | F<br>C | P<br>C<br>0 |  |  | I<br>C | IT |    |

| 32                    | 44 | 47 48  | 52 53 54 55 56 | 58 59 60 | 62 63  |             |  |  |        |    |    |

## セグメント・テーブル・エントリのフォーマットII

10

## 【0116】

セグメント・テーブル・エントリ内の選択されたフィールドは、以下のように割り振られる。

ページ・テーブル基点：強化型DATが適用されない場合、又は強化型DATは適用されるが、STEフォーマット制御、即ちセグメント・テーブル・エントリのビット53が0である場合には、ビット0-52は、右に11個の0を付加すると、ページ・テーブルの開始を示す64ビットのアドレスを形成する。アドレスが実であるか絶対であるかは予測不可能である。

## 【0117】

セグメント・フレーム絶対アドレス(SFAA)：強化型DATが適用され、且つSTEフォーマット制御が1である場合には、エントリのビット0-43は、右に20個の0を付加すると、セグメントの64ビット絶対アドレスを形成する。

20

## 【0118】

ACCFF妥当性制御(AV)：強化型DATが適用され、且つSTEフォーマット制御が1である場合には、ビット47はアクセス制御ビット及びフェッチ保護ビット(ACCFF)妥当性制御である。AV制御が0である場合、セグメント・テーブル・エントリのビット48-52は無視される。AV制御が1である場合、ビット48-52は以下で説明されるように用いられる。

## 【0119】

アクセス制御ビット(ACC)：強化型DATが適用され、STEフォーマット制御が1であり、且つ、AV制御が1である場合には、セグメント・テーブル・エントリのビット48-51は、そのアドレスに適用されるいずれのキー制御アクセス・チェックにも用いることができるアクセス制御ビットを含む。

30

## 【0120】

フェッチ保護ビット(F)：強化型DATが適用され、STEフォーマット制御が1であり、且つ、AV制御が1である場合には、セグメント・テーブル・エントリのビット52は、そのアドレスに適用されるいずれのキー制御アクセス・チェックにも用いることができるフェッチ保護ビットを含む。

## 【0121】

STEフォーマット制御(FC)：強化型DATが適用される場合には、ビット53は以下のように、セグメント・テーブル・エントリのためのフォーマット制御である。即ち、

40

## 【0122】

FCビットが0である場合、エントリのビット0-52はページ・テーブル基点を形成し、ビット55は未使用とされる。

## 【0123】

FCビットが1である場合、エントリのビット0-43はセグメント・フレーム絶対アドレスを形成し、ビット47はACCFF妥当性制御であり、ビット48-51はアクセス制御ビットであり、ビット52はフェッチ保護ビットであり、ビット55は変更記録オーバーライドである。強化型DATが適用されない場合には、ビット53は無視される。

50

## 【0124】

DAT保護ビット(P)：ビット54は、1である場合には、DAT保護がセグメント全体に適用されることを示す。

## 【0125】

強化型DATが適用されない場合には、ビット54は、変換に用いられるページ・テーブル・エントリの中のDAT保護ビットと論理和(OR)演算されたものとして扱われる。

## 【0126】

強化型DATが適用される場合には、変換に用いられるいずれかの及び全ての領域テーブル・エントリ内のDAT保護ビットは、セグメント・テーブル・エントリ内のDAT保護ビットと論理和演算されたものとして扱われ、STEフォーマット制御が0である場合には、STEの中のDAT保護ビットはさらに、ページ・テーブル・エントリ内のDAT保護ビットと論理和演算されたものとして扱われる。

## 【0127】

変更記録オーバーライド(CO)：強化型DATが適用され、且つ、STEフォーマット制御が1である場合、セグメント・テーブル・エントリのビット55は、そのセグメントについての変更記録オーバーライドである。強化型DATが適用されない場合、又は、強化型DATは適用されるがSTEフォーマット制御が0である場合には、セグメント・テーブル・エントリのビット55は無視される。

## 【0128】

セグメント無効ビット(I)：ビット58は、そのセグメント・テーブル・エントリに関連付けられたセグメントが利用可能であるかどうかを制御する。

## 【0129】

このビットが0である場合、アドレス変換はそのセグメント・テーブル・エントリを用いることによって進行する。

## 【0130】

このビットが1である場合、そのセグメント・テーブル・エントリを変換に用いることができない。

## 【0131】

共通セグメント・ビット(C)：ビット59は、セグメント・テーブル・エントリの変換ルックアサイド・バッファ・コピーの使用を制御する。強化型DATが適用されない場合、又は、強化型DATは適用されるがフォーマット制御が0である場合には、ビット59は、そのセグメント・テーブル・エントリによって指示されるページ・テーブルの変換ルックアサイド・バッファ・コピーの使用も制御する。

## 【0132】

0はプライベート・セグメントを識別し、この場合、セグメント・テーブル・エントリ及びそれが指示するいずれのページ・テーブルも、そのセグメント・テーブル・エントリが存在するセグメント・テーブルを指示するセグメント・テーブル基点との関連でのみ用いることができる。

## 【0133】

1は共通セグメントを識別し、この場合、セグメント・テーブル・エントリ及びそれが指示するいずれのページ・テーブルも、異なるセグメント・テーブルが指定されたとしても、引き続き、そのセグメント・インデックスに対応するアドレスを変換するために用いることができる。

## 【0134】

しかしながら、共通セグメントのための、セグメント・テーブル・エントリ及びいずれかのページ・テーブルの変換ルックアサイド・バッファ・コピーは、変換に用いられるASC Eの中のプライベート空間制御であるビット55が1である場合、又は、そのASC Eが実空間指示である場合には、使用可能ではない。用いられているASC Eの中のプライベート空間制御が1である場合に、セグメント・テーブル・エントリが変換中にストレ

10

20

30

40

50

ページからフェッチされたのであれば、その共通セグメント・ビットは 0 でなければならぬ。そうでない場合には、変換指定例外が認識される。

【 0 1 3 5 】

テーブル・タイプ・ビット ( T T ) : セグメント・テーブル・エントリのビット 6 0 及び 6 1 は、そのエントリを含むテーブルのレベルを識別するための二進数字 0 0 である。領域テーブル・エントリ又はセグメント・テーブル・エントリの中のビット 6 0 及び 6 1 の可能な全ての値の意味は、以下の通りである。

【表 1 4 】

| ビット 6 0<br>及び 6 1 | テーブル・レベル |

|-------------------|----------|

| 1 1               | 領域第 1    |

| 1 0               | 領域第 2    |

| 0 1               | 領域第 3    |

| 0 0               | セグメント    |

テーブル・タイプ・ビット 6 0, 6 1

【 0 1 3 6 】

ビット 6 0 及び 6 1 は、変換に用いられる A S C E であるテーブル指示のタイプ、及び、それまでに用いられたテーブル・レベルの数を考慮して、正しいテーブル・レベルを識別するものでなければならない。そうでない場合には、変換指定例外が認識される。セグメント・テーブル・エントリの他の全てのビット位置は、可能性のある将来的な拡張のために未使用とされ、0 を含むべきである。そうしなければ、プログラムが将来、互換的に動作できなくなるおそれがある。強化型 D A T が適用される場合、セグメント・テーブル・エントリ内の未使用のビット位置は、そのテーブル・エントリがたとえ無効だとしても、0 を含むべきである。

【 0 1 3 7 】

ページ・テーブル・エントリ

一実施形態において、ページ・テーブルからフェッチされるエントリは、以下のフォーマットを有する。

【表 1 5 】

|                      |    |    |                   |

|----------------------|----|----|-------------------|

| ページ・フレーム実アドレス        |    |    |                   |

| 30                   | 31 | 32 | 33                |

| ページ・フレーム実アドレス ( 続き ) |    |    | 52 53 54 55 56 63 |

| 32                   | 33 | 34 | 35                |

ページ・テーブル・エントリのフォーマット

【 0 1 3 8 】

ページ・テーブル・エントリの選択されたフィールドは、以下のように割り振られる。即ち、

ページ・フレーム実アドレス ( P F R A ) : ビット 0 - 5 1 は、実ストレージのアドレスの最左端のビットを与える。これらのビットの右に仮想アドレスの 1 2 ビット・バイトのインデックス・フィールドを連結すると、6 4 ビットの実アドレスが得られる。

【 0 1 3 9 】

ページ無効ビット ( I ) : ビット 5 3 は、ページ・テーブル・エントリに関連付けられたページが利用可能であるかどうかを制御する。ビットが 0 である場合、アドレス変換はそのページ・テーブル・エントリを用いることによって進行する。ビットが 1 である場合

10

20

30

40

50

、そのページ・テーブル・エントリを変換に用いることはできない。

#### 【0140】

DAT保護ビット(P)：ビット54は、そのページでストア・アクセスを行うことができるかどうかを制御する。この保護機構は、キー制御保護及び低いアドレス保護機構に加えてのものである。このビットは、フェッチ・アクセスに対して影響を与えない。このビットが0である場合、以下の追加的制約に従って、そのページへのストアが許可される。即ち、

変換に用いられるセグメント・テーブル・エントリ内のDAT保護ビットが0である。

強化型DATが適用される場合には、変換に用いられる全ての領域テーブル・エントリ内のDAT保護ビットが0である。

10

#### 【0141】

##### 他の保護機構

ビットが1である場合、ストアは許可されない。より優先順位の高い例外条件が存在しない場合には、DAT保護ビットが1であるときにストアしようとする試行は、保護例外の認識を発生させる。セグメント・テーブル・エントリ内のDAT保護ビットは、そのページに対してDAT保護が適用されるかどうかを判定するときに、ビット54と論理和演算されたものとして扱われる。強化型DATが適用される場合、変換に用いられるいずれの領域テーブル・エントリ内のDAT保護ビットもまた、DAT保護が適用されるかどうかを判定するときに、ビット54と論理和演算されたものとして扱われる。

#### 【0142】

20

変更記録オーバーライド(CO)：強化型DATが適用されない場合、ページ・テーブル・エントリのビット55は、0を含んでいなければならない。そうしなければ、アドレス変換のためにそのエントリを用いる命令の実行の一部として、変換指定例外が認識される。強化型DATが適用され、且つ、STEフォーマット制御が0である場合、ページ・テーブル・エントリのビット55は、そのページについての変更記録オーバーライドである。

#### 【0143】

エントリのビット位置52は、0を含んでいなければならない。そうしなければ、アドレス変換のためにそのエントリを用いる命令の実行の一部として、変換指定例外が認識される。ビット56-63は割り当てられず、無視される。

30

#### 【0144】

##### 動的変換の別の実施形態

このセクションは、仮想アドレスを用いて主ストレージにアクセスする前に暗黙的に実施されるときの変換プロセスを説明する。

#### 【0145】

仮想アドレスの変換は、プログラム・ステータス・ワード内のDATモード・ビット及びアドレス空間制御ビットにより制御され、且つ、制御レジスタ1、7、及び13内のASC Eにより制御され、そして、アクセス・レジスタによって指定されるように制御される。変換に用いられるASC Eが領域第1テーブル指示である場合には、変換は領域第1テーブル、領域第2テーブル、領域第3テーブル、セグメント・テーブル、及びページ・テーブルによって実施され、その全てが実ストレージ又は絶対ストレージ内に存在する。ASC Eがより下位レベルのタイプのテーブル指示（領域第2テーブル指示、領域第3テーブル指示、又はセグメント・テーブル指示）である場合には、変換は、指示されたレベルから始まるテーブル・レベルのみを用いて実施され、非0であればより高位の1つ又は複数のレベルのテーブルの使用を要求するはずの仮想アドレスのビットは、全て0でなければならずそうでない場合には、ASC Eタイプ例外が認識される。ASC Eが実空間指示である場合には、仮想アドレスは実アドレスとして扱われ、実ストレージ又は絶対ストレージの内のテーブル・エントリは用いられない。

40

#### 【0146】

特定のアドレス変換に用いられるASC Eを、実効ASC Eと呼ぶ。従って、一次仮想

50

アドレスが変換される場合には、制御レジスタ1の内容が実効A S C Eとして用いられる。同様に、二次仮想アドレスの場合には制御レジスタ7の内容が用いられ、A R指定仮想アドレスの場合にはアクセス・レジスタによって指定されたA S C Eが用いられ、ホーム仮想アドレスの場合には制御レジスタ13の内容が用いられる。

#### 【0147】

実効A S C Eの中の実空間制御が0である場合、A S C Eの中の指示タイプはテーブル指示タイプ、即ち、領域第1テーブル、領域第2テーブル、領域第3テーブル、又はセグメント・テーブルを指定する。仮想アドレスの対応する部分（領域第1インデックス、領域第2インデックス、領域第3インデックス、又はセグメント・インデックス）が、指示の中のテーブル長フィールドに対してチェックされ、これを指示内の基点に加算して、指示されたテーブルの中のエントリを選択する。選択されたエントリが、指示内のテーブル長フィールドによって判定してテーブルの外部にある場合、又は選択されたエントリ内のIビットが1である場合は、指示によって指定されたテーブル・レベルに応じて、領域第1変換、領域第2変換、領域第3変換、又はセグメント変換の例外が認識される。選択されたエントリ内のテーブル・タイプ・ビットが予期されたテーブル・レベルを示していない場合には、変換指定例外が認識される。

#### 【0148】

実効A S C Eによって選択されたテーブル・エントリは、用いられるべき次に下位レベルのテーブルを指示する。現在のテーブルが領域第1テーブル、領域第2テーブル、又は領域第3テーブルであれば、仮想アドレスの次の部分（それぞれ、領域第2インデックス、領域第3インデックス、又はセグメント・インデックス）が現在のテーブル・エントリ内のテーブル・オフセット及びテーブル長フィールドに対してチェックされ、これをエントリ内の基点に加算して、次に下位レベルのテーブルの中のエントリを選択する。次のテーブルの中の選択されたエントリが、現在のテーブル・エントリ内のテーブル・オフセット及びテーブル長フィールドによって判定して、そのテーブルの外部にある場合、又は、選択されたエントリ内のIビットが1である場合は、次のテーブルのレベルに応じて、領域第2変換、領域第3変換、又はセグメント変換の例外が認識される。選択されたエントリ内のテーブル・タイプ・ビットが予期されたテーブル・レベルを示していない場合には、変換指定例外が認識される。

#### 【0149】

逐次的なテーブル・レベルによる仮想アドレスの部分の処理は、セグメント・テーブル・エントリが選択されるまで続く。セグメント・テーブル・エントリは、指定されたセグメントの中の全てのページに適用されるページ保護ビットを含む。

#### 【0150】

仮想アドレスのページ・インデックス部分を、セグメント・テーブル・エントリ内のページ・テーブル基点に加算して、ページ・テーブル内のエントリを選択する。ページ・テーブル・エントリ内のIビットが1である場合には、ページ変換例外が認識される。ページ・テーブル・エントリは、仮想アドレスの変換を示す実アドレスの最左端のビットを含み、且つ、そのページ・テーブル・エントリによって指定されるページのみに適用されるページ保護ビットを含む。

#### 【0151】

仮想アドレスのバイト・インデックス・フィールドは、実アドレスの最右端のビット位置として、変更せずに用いられる。

#### 【0152】

実ストレージ又は絶対ストレージ内の変換テーブルを参照することに関連する遅延を排除するために、テーブルからフェッチされた情報は通常、特別なバッファである変換ルックアサイド・バッファ内にも置かれ、同じテーブル・エントリが関与するその後の変換は、変換ルックアサイド・バッファ内に記録された情報を用いて行うことができる。変換ルックアサイド・バッファは、実空間指示に関係した、仮想と実が等しい（virtual equals real）変換を記録することもできる。

10

20

30

40

50

## 【0153】

領域テーブル、セグメント・テーブル、又はページ・テーブルからエントリをフェッチする目的で、アドレス変換プロセス中に実ストレージ又は絶対ストレージにアクセスする場合であればいつでも、キー制御保護は適用されない。

## 【0154】

ASC Eによって指示されるテーブルにおけるルックアップ

実効ASC EのDT制御であるビット60-61は、ASC Eのテーブル指示タイプ、及び、指示されたテーブルによって変換される仮想アドレスの部分の両方を以下のように指定する。

【表16】

10

| ビット60<br>及び61 | 指示タイプ      | テーブルによって変換される<br>仮想アドレス部分 |

|---------------|------------|---------------------------|

| 11            | 領域第1テーブル   | 領域第1インデックス<br>(ビット0-10)   |

| 10            | 領域第2テーブル   | 領域第2インデックス<br>(ビット11-21)  |

| 01            | 領域第3テーブル   | 領域第3インデックス<br>(ビット22-32)  |

| 00            | セグメント・テーブル | 領域第4インデックス<br>(ビット33-43)  |

20

## 指示されたテーブルによる変換

## 【0155】

ビット60及び61が二進数字11の値を有する場合、仮想アドレスの領域第1インデックス部分を、ASC Eに含まれる領域第1テーブル基点と組み合わせて用いて、領域第1テーブルからエントリを選択する。実ストレージ又は絶対ストレージの中の領域第1テーブル・エントリの64ビット・アドレスは、領域第1テーブル指示のビット0-51の右側に12個の0を付加すること、及び、最右端に3つ、最左端に50個の0が付加された領域第1インデックスを加算することによって得られる。領域第1テーブル・ルックアップ・プロセスの一部として、アドレス指定されたエントリが領域第1テーブル内にあるかどうかを確立するために、仮想アドレスのビット0及び1(領域第1インデックスのビット0及び1である)が、領域第1テーブル指示のテーブル長、即ちビット62及び63に対して比較される。テーブル長フィールドにおける値が仮想アドレスの対応するビット位置における値より小さい場合には、領域第1変換例外が認識される。変換ルックアサイド・バッファ内の領域第1テーブル・エントリの等価物が変換に用いられる場合には、テーブル長に対する比較を省略することができる。領域第1テーブルからフェッチされたエントリは、対応する領域第2テーブルの開始位置を示し、そのオフセット及び長さを指定する。

30

## 【0156】

ASC Eのビット60及び61が二進数字10の値を有する場合、仮想アドレスの領域第2インデックス部分を、ASC Eに含まれる領域第2テーブル基点と組み合わせて用いて、領域第2テーブルからエントリを選択する。仮想アドレスのビット11及び12(領域第2インデックスのビット0及び1である)が、ASC Eの中のテーブル長に対して比較される。テーブル長フィールドにおける値が、仮想アドレスの対応するビット位置における値より小さい場合には、領域第2変換例外が認識される。変換ルックアサイド・バッファ内の領域第2テーブル・エントリの等価物が変換に用いられる場合には、テーブル長

40

50

に対する比較を省略することができる。その他の点では、領域第2テーブル・ルックアップ・プロセスは、領域第1テーブル・ルックアップ・プロセスと同じであり、領域第2テーブルからフェッチされたエントリは、対応する領域第3テーブルの開始位置を示し、そのオフセット及び長さを指定する。

【0157】

ASC Eのビット60及び61が二進数字01の値を有する場合、仮想アドレスの領域第3インデックス部分を、ASC Eに含まれる領域第3テーブル基点と組み合わせて用いて、領域第3テーブルからエントリを選択する。仮想アドレスのビット22及び23（領域第3インデックスのビット0及び1である）が、ASC Eの中のテーブル長に対して比較される。テーブル長フィールドにおける値が、仮想アドレスの対応するビット位置における値より小さい場合には、領域第3変換例外が認識される。その他の点では、領域第3テーブル・ルックアップ・プロセスは領域第1テーブル・ルックアップ・プロセスと同じであり、領域第3テーブル・エントリ内のテーブル・タイプ・ビットをチェックすることを含む。領域第3テーブルからフェッチされたエントリは、対応するセグメント・テーブルの開始位置を示し、そのオフセット及び長さを指定する。

【0158】

ASC Eのビット60及び61が二進数字00の値を有する場合、仮想アドレスのセグメント・インデックス部分を、ASC Eに含まれるセグメント・テーブル基点と組み合わせて用いて、セグメント・テーブルからエントリを選択する。仮想アドレスのビット33及び34（セグメント・インデックスのビット0及び1である）が、ASC Eの中のテーブル長に対して比較される。テーブル長フィールドにおける値が、仮想アドレスの対応するビット位置における値より小さい場合には、セグメント変換例外が認識される。変換ルックアサイド・バッファ内のセグメント・テーブル・エントリの等価物が変換に用いられる場合には、テーブル長に対する比較を省略することができる。その他の点では、セグメント・テーブル・ルックアップ・プロセスは領域第1テーブル・ルックアップ・プロセスと同じであり、セグメント・テーブル・エントリ内のテーブル・タイプ・ビットをチェックすることを含む。処理は以下の通りである。

【0159】

強化型DATが適用されない場合、又は、強化型DATは適用されるが、STEフォーマット制御が0である場合には、セグメント・テーブルからフェッチされたエントリは、対応するページ・テーブルの開始位置を示し、処理は以下の「ページ・テーブル・ルックアップ」において説明されるように続行する。

【0160】

強化型DATが適用され、且つ、STEフォーマット制御が1である場合には、セグメント・テーブルからフェッチされたエントリは、セグメント・フレーム絶対アドレスの最左端のビットを含む。変換に用いられるいずれかの領域テーブル・エントリ、又はセグメント・テーブル・エントリのどちらかにおいてDAT保護ビットが1であり、且つ、変換が実施されているストレージ参照がストアであれば、保護例外が認識される。

【0161】

領域テーブル・エントリによって指示されるテーブルにおけるルックアップ

実効ASC Eが領域テーブル指示である場合には、前掲のセクションにおいて説明されたように領域テーブル・エントリが選択される。次いで、選択されたエントリの内容と、仮想アドレスの次のインデックス部分とを用いて、次に下位レベルのテーブルにおけるエントリが選択され、このテーブルは、別の領域テーブルの場合もあり、セグメント・テーブルの場合もある。ASC Eによって選択されたテーブル・エントリが領域第1テーブル・エントリである場合には、仮想アドレスの領域第2インデックス部分を領域第1テーブル・エントリに含まれる領域第2テーブル基点と組み合わせて用いて、領域第2テーブルからエントリを選択する。実ストレージ又は絶対ストレージの中の領域第2テーブル・エントリの64ビット・アドレスは、領域第1テーブル・エントリのビット0-51の右側に12個の0を付加すること、及び、最右端に3つ、最左端に50個の0が付加された領

10

20

30

40

50

域第2インデックスを加算することによって得られる。

【0162】

領域第2テーブル・エントリ、領域第3テーブル・エントリ、又はセグメント・テーブル・エントリのアドレスを形成する際に、プリフィックス付加が行われる場合には、それは、より高位レベルのテーブル・エントリに含まれるそれぞれのテーブル基点に対してテーブル・インデックスの値を加算する前に適用されるのか、又はテーブル基点とテーブル・インデックス値との加算によって形成されたテーブル・エントリ・アドレスに対して適用されるのかは、予測不可能である。

【0163】

領域第2テーブル・ルックアップ・プロセスの一部として、仮想アドレスのビット11及び12（領域第2インデックスのビット0及び1である）は、領域第1テーブル・エントリのテーブル・オフセットであるビット56及び57に対して、及び領域第1テーブル・エントリのテーブル長であるビット62及び63に対して比較され、アドレス指定されたエントリが領域第2テーブルの範囲内にあるどうかを確立する。テーブル・オフセット・フィールドにおける値が仮想アドレスの対応するビット位置における値より大きい場合、又はテーブル長フィールドにおける値が仮想アドレスの対応するビット位置における値より小さい場合には、領域第2変換例外が認識される。

【0164】

領域第2テーブルは、対応する領域第3テーブルの開始位置を示し、そのオフセット及び長さを指定する。

【0165】

ASC Eによって選択されたテーブル・エントリが領域第2テーブル・エントリである場合、又は領域第2テーブル・エントリが領域第1テーブル・エントリの内容によって選択されている場合には、仮想アドレスの領域第3インデックス部分を、領域第2テーブル・エントリに含まれる領域第3テーブル基点と組み合わせて用いて、領域第3テーブルからエントリを選択する。仮想アドレスのビット22及び23（領域第3インデックスのビット0及び1である）が、領域第2テーブル・エントリ内のテーブル・オフセット及びテーブル長に対して比較される。テーブル・オフセットがビット22及び23より大きい場合、又はテーブル長がビット22及び23より小さい場合には、領域第3変換例外が認識される。その他の点では、領域第3テーブル・ルックアップ・プロセスは、領域第2テーブル・ルックアップ・プロセスと同一である。領域第3テーブルからフェッチされたエントリは、対応するセグメント・テーブルの開始位置を示し、そのオフセット及び長さを指定する。

【0166】

ASC Eによって選択されたテーブル・エントリが領域第3テーブル・エントリである場合、又は領域第3テーブル・エントリが領域第2テーブル・エントリの内容によって選択されている場合には、仮想アドレスのセグメント・インデックス部分を、領域第3テーブル・エントリに含まれるセグメント・テーブル基点と組み合わせて用いて、セグメント・テーブルからエントリを選択する。仮想アドレスのビット33及び34（セグメント・インデックスのビット0及び1である）が、領域第3テーブル・エントリ内のテーブル・オフセット及びテーブル長に対して比較される。テーブル・オフセットがビット33及び34より大きい場合、又はテーブル長がビット33及び34より小さい場合には、セグメント変換例外が認識される。変換指定例外は、（1）ASC Eの中のプライベート空間制御であるビット55が1であり、且つ（2）セグメント・テーブルからフェッチされたエントリ内の共通セグメント・ビットであるビット59が1である場合に、認識される。その他の点では、セグメント・テーブル・ルックアップ・プロセスは、領域第2テーブル・ルックアップ・プロセスと同一である。処理は以下の通りである。

【0167】

強化型DATが適用されない場合、又は、強化型DATは適用されるがSTEフォーマット制御が0である場合には、セグメント・テーブルからフェッチされたエントリは、対

10

20

30

40

50

応するページ・テーブルの開始位置を示し、処理は後述の「ページ・テーブル・ルックアップ」において説明されるように続行する。

#### 【0168】

強化型DATが適用され、且つ、STEフォーマット制御が1である場合には、セグメント・テーブルからフェッチされたエントリは、セグメント・フレーム絶対アドレスの最左端ビットを含む。変換に用いられるいずれかの領域テーブル・エントリ、又はセグメント・テーブル・エントリのどちらかにおいて、DAT保護ビットが1であり、且つ、変換が実施されている対象のストレージ参照がストアであれば、保護例外が認識される。

#### 【0169】

ページ・テーブルのルックアップ

10

強化型DATが適用されない場合、又は強化型DATは適用されるがSTEフォーマット制御が0である場合には、仮想アドレスのページ・インデックス部分を、セグメント・テーブル・エントリに含まれるページ・テーブル基点と組み合わせて用いて、ページ・テーブルからエントリを選択する。

#### 【0170】

実ストレージ又は絶対ストレージ内のページ・テーブル・エントリの64ビット・アドレスは、ページ・テーブル基点の右に11個の0を付加すること、及び、最右端に3つ、最左端に53個の0が付加されたページ・インデックスを加算することによって得られる。ビット位置0のキャリーアウトは、生じることができない。

#### 【0171】

ページ・テーブルからフェッチされたエントリは、そのページの可用性を示し、ページ・フレーム絶対アドレスの最左端ビットを含む。対応するページが利用可能であるかどうかを確立するために、ページ無効ビットであるビット53が検査される。このビットが1である場合、ページ変換例外が認識される。ビット位置52が1を含んでいる場合、変換指定例外が認識される。強化型DATが適用されない場合、又は強化型DATは適用されるがSTEフォーマット制御が0である場合には、ビット位置55が1を含む場合にも変換指定例外が認識される。変換に用いられるセグメント・テーブル・エントリ、ページ・テーブル・エントリ、又は強化型DATが適用される場合に変換中に用いられるいずれかの領域テーブル・エントリのうちのいずれかにおいて、DAT保護ビットが1であり、且つ、変換が実施されている対象のストレージ参照がストアであれば、保護例外が認識される。

20

#### 【0172】

実アドレス及び絶対アドレスの形成

実効ASC Eが実空間指示である場合には、仮想アドレスのビット0-63は直接、実ストレージ・アドレスとして用いられる。実アドレスに対してさらにプリフィックス付加を行って、絶対アドレスを形成することができる。実効ASC Eが実空間指示ではなく、変換プロセスにおいて例外が発生しない場合には、以下の条件が適用される。

#### 【0173】

強化型DATが適用されない場合、又は強化型DATは適用されるがSTEフォーマット制御が0である場合には、ページ・フレーム実アドレスは、ページ・テーブル・エントリから得られる。ページ・フレーム実アドレスと仮想アドレスのバイト・インデックス部分とを、ページ・フレーム実アドレスが最左端部分を形成するようにして連結させる。その結果が、その仮想アドレスに対応する実ストレージ・アドレスである。実アドレスに対してさらにプリフィックス付加を行って、絶対アドレスを形成することができる。

30

#### 【0174】

強化型DATが適用され、且つ、STEフォーマット制御が1である場合には、セグメント・フレーム絶対アドレスと仮想アドレスのページ・インデックス部分及びバイト・インデックス部分とを左から右に連結して、仮想アドレスに対応する絶対アドレスを形成する。

#### 【0175】

50

### 変換中の例外の認識

無効アドレス及び無効フォーマットは、変換プロセス中に認識される例外を発生することがある。テーブル・エントリに含まれる情報が変換のために用いられ、それが正しくない正しくないことが見いだされた場合に、例外が認識される。

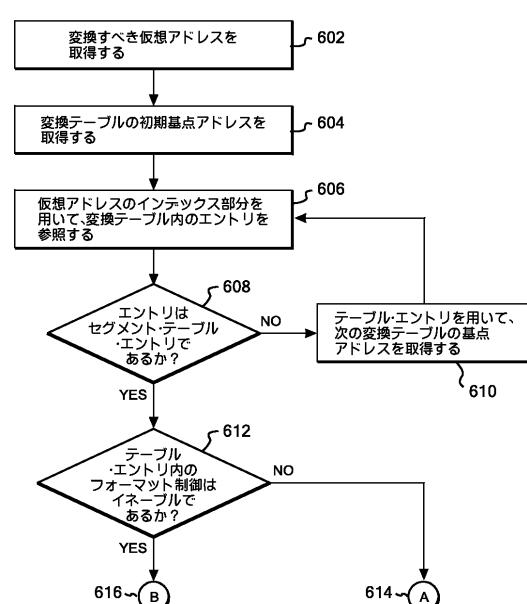

#### 【0176】

ここで、動的アドレス変換の一実施形態の流れ図をセグメント・テーブル・エントリからフォーマット制御フィールドを取得する時点まで示す、図8を参照する。

#### 【0177】

602において、変換する仮想アドレスが取得される。604において、仮想アドレスの変換に用いられる最も高位の変換テーブルの基点アドレスが取得される。変換に用いられる最初の変換テーブルの基点アドレスは、ADC E及びDTビットに依存する。606において、仮想アドレスの一部を用いて、変換テーブル内の適切なテーブル・エントリを参照する。608において、変換テーブルからフェッチされたエントリがセグメント・テーブル・エントリでない場合には、変換テーブル階層構造の中のセグメント・テーブルはまだ参照されていない。この場合、610において、変換テーブル階層構造内の次に低位の変換テーブルの基点アドレスが、テーブル・エントリから取得される。仮想アドレスの適切な部分を用いて、変換に用いられる次に低位のテーブル内の対応するテーブル・エントリを参照する。

10

#### 【0178】

例えば、変換に用いられる最初の変換テーブルの基点アドレスが領域第1テーブルであれば、仮想アドレスのRFX部分を用いて、領域第1テーブル内の領域第1テーブル・エントリを参照する。テーブル基点アドレスが領域第2テーブルに対するものであれば、仮想アドレスのRSX部分を用いて、領域第2テーブル内の領域第2テーブル・エントリを参照する。テーブル基点アドレスが領域第3テーブルに対するものであれば、仮想アドレスのRTX部分を用いて、領域第3テーブル内の領域第3テーブル・エントリを参照する。テーブル基点アドレスがセグメント・テーブルに対するものであれば、仮想アドレスのSX部分を用いて、セグメント・テーブル内のセグメント・テーブル・エントリを参照するセグメント・テーブル・エントリがフェッチされるまで、逐次的なテーブルが参照される。

20

#### 【0179】

一旦セグメント・テーブル・エントリがフェッチされると、612において、セグメント・テーブル・エントリ(STE)フォーマット制御ビットが検査され、この特定の仮想アドレスに対してフォーマット制御がイネーブルであるかどうかを判定する。STEフォーマット制御が0であれば、動的アドレス変換はノード614に関して行われる。STEフォーマット制御が1であれば、動的アドレス変換はノード616に関して行われる。

30

#### 【0180】

動的アドレス変換(STEフォーマット制御が0)

ここで、STEフォーマット制御が0である場合の図8のノード614からの流れ図の続きを示す、図9を参照する。

#### 【0181】

710において、セグメント・テーブル・エントリから、ページ・テーブルの基点アドレスが取得される。712において、仮想アドレスのPX部分を用いて、ページ・テーブル内のページ・エントリを参照する。714において、ページ・テーブル・エントリから、ページ・フレーム実アドレス(PFRA)が取得される。無効(I)ビットがページ・テーブル・エントリから取得される。716において、無効(I)ビットが1である場合、このページ・テーブル・エントリは無効であるものとしてマークされているので、718において、このページ・テーブル・エントリを用いた仮想アドレスの変換を続けることはできない。このページ・テーブル・エントリを用いた仮想アドレスのそれ以上の変換は、停止する(722)。716において、無効(I)ビットが0である場合、720において、ページ・フレーム実アドレス(PFRA)を仮想アドレスのBX部分と組み合わせ

40

50

て、実アドレスを生成する。実アドレスに対してさらにプリフィックス付加操作を行って、絶対アドレスを形成することができる。724において、実アドレスを用いて、変換された仮想アドレスによってアドレス指定されたデータ・ブロックにアクセスする。

【0182】

動的アドレス変換 (STEフォーマット制御が1)

ここで、図8のノード616からの流れ図の続きを示す、図10を参照する。

【0183】

810において、セグメント・フレーム絶対アドレス(SFAA)が、セグメント・テーブル・エントリの一部から取得される。無効(I)ビットがセグメント・テーブル・エントリから取得される。812において、無効(I)ビットが1である場合、セグメント・テーブル・エントリは無効であるものとしてマークされているので、814において、このセグメント・テーブル・エントリを用いた仮想アドレスのそれ以上の変換を続けることはできない。一実施形態において、変換を要求するプログラム・エンティティに対して、例外コードが戻される。このセグメント・テーブル・エントリを用いた仮想アドレスのそれ以上の変換は、停止する(818)。

【0184】

812において、無効(I)ビットが0である場合、816において、セグメント・フレーム絶対アドレス(SFAA)を仮想アドレスのPX部分及びBX部分と組み合わせて、主ストレージ又はメモリ内の所望の大データ・ブロックに対する絶対アドレスを生成する。820において、変換された仮想アドレスによってアドレス指定される所望の大データ・ブロックにアクセスする。

【0185】

各テーブル・エントリにおいて、取得されたテーブル・エントリの妥当性を判定するために、無効ビットが検査される。変換された仮想アドレスによってアドレス指定されるデータ・ブロックを保護する他の変換保護機構について、本明細書においてさらに検討する。

【0186】

別の実施形態において、制限情報が変換テーブル・エントリから取得される。制限情報は、アクセスを仮想アドレス範囲の制限部分に対するものに限定するために用いられる。これ以降は、変換されたアドレスによってアドレス指定される所望の大データ・ブロックに対するアクセスは、アドレス範囲の制限部分に対してのみ許可される。制限情報は、テーブル・オフセット又はテーブル長のどれか1つである。

【0187】

さらに別の実施形態において、仮想アドレスの変換に用いられる情報は、少なくとも1つの変換ルックアサイド・バッファ内にストアされる。その後の仮想アドレスの、主ストレージ内のデータ・ブロックの絶対アドレスへの変換は、それ以降、変換テーブル階層構造ではなく変換ルックアサイド・バッファ由来のストアされた情報を用いて実施される。

【0188】

さらに別の実施形態において、変換がマシン・アーキテクチャに対してネイティブでない場合には、変換をエミュレートするための所定のソフトウェア・ルーチンが識別される。所定のソフトウェア・ルーチンは、複数の命令を含む。所定のソフトウェア・ルーチンが実行される。

【0189】

アドレス指定されたデータ・ブロックの保護

本明細書で説明されるように、仮想アドレスが強化型DATファシリティを用いて変換されると、変換された仮想アドレスによってアドレス指定される主ストレージ又はメモリ内の所望のデータ・ブロックに対して、付加的な保護機構を適用することができる。

【0190】

DAT保護

DAT保護機能は、仮想ストレージへのアクセスを、各ページ・テーブル・エントリ及

10

20

30

40

50

びセグメント・テーブル・エントリ内の D A T 保護ビット、及び、強化型 D A T ファシリティがインストールされている場合には各領域テーブル・エントリ内の D A T 保護ビットを用いることによって、制御する。これは不正なストアに対する保護を与える。

【 0 1 9 1 】

ページ・テーブル・エントリの D A T 保護ビット（ビット 54）は、対応する 4 キロバイトのページへのストアが許可されるかどうかを制御する。ビットが 0 である場合にはフェッチ及びストアの両方が許可され、ビットが 1 である場合にはフェッチのみが許可される。保護されたページへのストアが試行された場合、ページの内容は変更されず、操作単位（unit of operation）又は命令の実行が抑制され、保護のためのプログラム割り込みが発生する。

10

【 0 1 9 2 】

セグメント・テーブル・エントリの D A T 保護ビット（ビット 54）は、対応する 1 メガバイトのセグメントへのストアが許可されるかどうかを以下のように制御する。

【 0 1 9 3 】

強化型 D A T が適用されない場合、又は強化型 D A T が適用され、且つ S T E フォーマット制御が 0 である場合には、セグメント・テーブル・エントリの D A T 保護ビットは、そのセグメント・テーブル・エントリによって指示されるページ・テーブル内の各エントリの D A T 保護ビット位置内へと論理和演算されたものとして扱われる。よって、セグメント・テーブル・エントリの D A T 保護ビットが 1 である場合、その効果は、あたかも指示されたページ・テーブルの中の各エントリ内の D A T 保護ビットが 1 であるかのようなものである。

20

【 0 1 9 4 】

強化型 D A T が適用され、且つ S T E フォーマット制御が 1 である場合には、セグメント・テーブル・エントリの D A T 保護ビットは、対応する 1 メガバイトのセグメントへのストアが許可されるかどうかを制御する。ビットが 0 である場合にはフェッチ及びストアの両方が許可され、ビットが 1 である場合にはフェッチのみが許可される。保護されたセグメントへのストアが試行された場合、セグメントの内容は変更されず、操作単位又は命令の実行が抑制され、保護のためのプログラム割り込みが発生する。

【 0 1 9 5 】

強化型 D A T が適用される場合、領域テーブル・エントリの D A T 保護ビットは、対応する領域へのストアが許可されるかどうかを制御する。領域テーブル・エントリ内の D A T 保護ビットは、変換に用いられるいづれかの後続の領域テーブル・エントリ及びセグメント・テーブル・エントリの D A T 保護ビット位置内へと論理和演算されたものとして扱われる。 S T E フォーマット制御が 0 である場合、 D A T 保護ビットは、さらにページ・テーブル・エントリまで伝搬される。

30

【 0 1 9 6 】

D A T 保護は、仮想アドレスを用いる全てのストア・タイプ参照に適用される。

【 0 1 9 7 】

ここで、変換に用いられるセグメント・テーブル・エントリから D A T 保護ビットを得る一実施形態の流れ図を示す、図 1 1 を参照する。

40

【 0 1 9 8 】

9 0 2 において、変換される仮想アドレスが取得される。9 0 4 において、仮想アドレスの変換に用いられる最初の変換テーブルの基点が取得される。9 0 6 において、前述された手法で、仮想アドレスの一部を用いて変換テーブル内のエントリを参照する。9 0 8 において、実アドレス又は絶対アドレスが、取得されたセグメント・フレーム絶対アドレス（S F A A ）又はページ・フレーム実アドレス（P F R A ）から生成される。

【 0 1 9 9 】

9 1 0 において、D A T 保護（P）ビットが、仮想アドレスの変換に用いられた変換テーブルの各エントリから取得される。D A T 保護の実効レベルは、変換に用いられた各テーブル・エントリから取得される複数の P ビットの論理和であることを理解すべきである

50

。912において、DAT保護ビットが検査され、変換された仮想アドレスによってアドレス指定されたデータ・ブロックがDAT保護されるかどうかを判定する。912において、DAT保護(P)ビットが0である場合、914において、変換された仮想アドレスによってアドレス指定されるデータ・ブロックへのストア動作が許可される。912において、DAT保護(P)ビットが1である場合、916において、変換された仮想アドレスによってアドレス指定されたデータ・ブロックへのストア動作が防止される。あるいは、DAT保護フィールドによって示される保護レベルが、その仮想アドレスを用いる全てのストア・タイプ参照に対して適用される。DAT保護フィールドがイネーブルである場合、変換された仮想アドレスによってアドレス指定された所望のデータ・ブロックへのストアが試行されると、保護例外条件が示される。

10

### 【0200】

#### キー制御保護

キー制御保護がストレージ・アクセスに適用される場合、ストアは、ストレージ・キーがストレージ・アクセス要求に関連付けられたアクセス・キーと一致する場合にのみ許可され、フェッチは、キーが一致する場合、又はストレージ・キーのフェッチ保護ビットが0である場合に許可される。ストレージ・キーの4つのアクセス制御ビットがアクセス・キーに等しい場合、又はアクセス・キーが0である場合に、キーが一致したと言う。保護アクションは、以下のように要約される。

### 【表17】

20

| 条件                 |       | ストレージへのアクセスは許可されているか |     |

|--------------------|-------|----------------------|-----|

| ストレージ・キーのフェッチ保護ビット | キーの関係 | フェッチ                 | ストア |

| 0                  | 一致    | はい                   | はい  |

| 0                  | 不一致   | はい                   | いいえ |

| 1                  | 一致    | はい                   | はい  |

| 1                  | 不一致   | いいえ                  | いいえ |

| 説明： |                                                   |

|-----|---------------------------------------------------|

| 一致  | ストレージ・キーの4つのアクセス制御ビットがアクセス・キーに等しい、又はアクセス・キーが0である。 |

| はい  | アクセスが許可される。                                       |

| いいえ | アクセスは許可されない。                                      |

|     | フェッチの場合、情報はプログラムに対して利用可能にされない。                    |

|     | ストアの場合、ストレージ位置の内容は変更されない。                         |

30

### 保護アクションの要約

### 【0201】

40

ストレージへのアクセスがCPUによって開始され、且つキー制御保護が適用される場合には、PSWキーがアクセス・キーであるが、但し、MOVE TO SECONDARY及びMOVE WITH DESTINATION KEYの第1オペランド、MOVE TO PRIMARY、MOVE WITH KEY、及びMOVE WITH SOURCE KEYの第2オペランド、並びに第MOVE PAGEの1オペランド又は第2オペランドのいずれかについて、アクセス・キーは汎用レジスタ内で指定される。PSWキーは、カレント・プログラム・ステータス・ワードの8-11のビット位置を占める。

### 【0202】

キー制御保護が原因でCPUアクセスが禁止されるとき、命令の実行は停止し、保護例

50

外のためのプログラム割り込みが発生する。しかしながら、操作単位又は命令の実行は抑制されることもある。

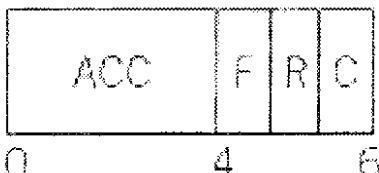

【0203】

ストレージ・キー

ストレージ・キーは、構成内で利用可能なストレージの各々の4キロバイト・ブロックに関連付けられる。ストレージ・キーはアドレス指定可能なストレージの一部ではない。一実施形態において、ストレージ・キーは以下のフォーマットを有する。

【表18】

10

## ストレージ・キーのフォーマット

【0204】

ストレージ・キーの中のビット位置は以下のように割り振られる。

アクセス制御ビット (ACC)：参照がキー制御保護を受けているならば、情報がストアされる場合、及びフェッチに対して保護されている位置から情報がフェッチされる場合に、4つのアクセス制御ビットが、4ビットのアクセス・キーと照合される。

20

【0205】

フェッチ保護ビット (F)：参照がキー制御保護を受けているならば、フェッチ保護ビットは、キー制御保護がフェッチ・タイプ参照に適用されるかどうかを制御し、0は、ストア・タイプ参照のみが監視され、どのようなアクセス・キーを有するフェッチも許可されることを示し、1は、キー制御保護がフェッチ及びストアの両方に適用されることを示す。

【0206】

参照ビット (R)：参照ビットは通常、対応するストレージ・ブロック内の位置が情報のストア又はフェッチのいずれかのために参照される都度、1に設定される。

30

【0207】

変更ビット (C)：変更ビットは、対応するストレージ・ブロック内の位置に情報がストアされる都度、1に設定される。

【0208】

強化型DATが適用される場合、以下の追加条件が効力をもつ。

【0209】

STEフォーマット制御 (変換中に用いられるセグメント・テーブル・エントリのビット53であるFC)が0である場合、変換中に用いられるページ・テーブル・エントリのビット55は、そのページのための変更記録オーバーライド(CO)である。ページ・テーブル・エントリ内のCOビットが1である場合、そのページに対するいずれのストア動作についても変更記録は予測不可能である。

40

【0210】

セグメント・テーブル・エントリの中のフォーマット制御ビット(CO)が1である場合、以下が適用される。

【0211】

セグメント・テーブル・エントリのビット位置47は、ACC F妥当性制御を含む。ACC F妥当性制御は、STEの中のアクセス制御ビット及びフェッチ保護ビットの妥当性を決定する。ACC F妥当性制御が0である場合、キー制御保護は、そのアドレスに対応する4KBバイト・ブロックのためのストレージ・キーの中のアクセス制御ビット及びフェッチ保護ビットを用いる。

50

## 【0212】

ACC F妥当性制御が1である場合、セグメント・テーブル・エントリのビット位置48-52は、そのセグメントについてのアクセス制御ビット及びフェッチ保護ビットを含む。ストレージ・オペランドに対するアクセス可能性を判定するときに、STEのビット48-52、又は、セグメントを構成する4Kバイト・ブロックのための個々のストレージ・キーのビット0-4のどちらが検査されるかは、予測不可能である。

## 【0213】

セグメント・テーブル・エントリのビット55は、そのセグメントについての変更記録オーバーライド(CO)である。セグメント・テーブル・エントリ内のCOビットが1である場合、そのセグメントに対するいずれかのストア動作について変更記録が設定されるかどうかは予測不可能である。 10

## 【0214】

## ストレージ・キー・アクセス

ストレージ・キーへの参照は、以下のように取り扱われる。

## 【0215】

ストレージの参照が行われ、且つキー制御保護が参照に適用される場合には常に、そのストレージ位置に関連付けられた4つのアクセス制御ビット及びフェッチ保護ビットが同時に、且つストレージ位置に対する参照と同時に、検査される。(1)強化型DATが適用されない場合、(2)強化型DATは適用されるが、STEフォーマット制御が0であるセグメント・テーブル・エントリによってストレージがアクセスされる場合、又は(3)強化型DATが適用され、STEフォーマット制御が1であるが、ACC F妥当性制御が0であるセグメント・テーブル・エントリによってストレージがアクセスされる場合、アクセス制御ビット及びフェッチ保護ビットは、4Kバイト・ブロックのためのストレージ・キーのビット0-4に存在する。強化型DATが適用され、STEフォーマット制御及びACC F妥当性制御の両方が1であるセグメント・テーブル・エントリによってストレージがアクセスされる場合、ストレージ・キーのビット0-4又はセグメント・テーブル・エントリのビット48-52のどちらがアクセス制御ビット及びフェッチ保護ビットを与えるかは予測不可能である。さらに、セグメント・テーブル・エントリがアクセス制御ビット及びフェッチ保護ビットを与える場合には、変換ルックアサイド・バッファ由來のバッファされたコピーを用いることができる。 30

## 【0216】

強化型DATが適用され、且つ、(a)STEフォーマット制御が0であり、且つ、DATによって用いられるページ・テーブル・エントリ内の変更記録オーバーライドが1であるか、又は(b)STEフォーマット制御が1であり、且つ、DATによって用いられるセグメント・テーブル・エントリ内の変更記録オーバーライドが1であるかのいずれかの場合、CPUがストア動作を実施するときに変更ビットを設定するかどうかは予測不可能である。変更記録オーバーライドは、pte又はSTEの変換ルックアサイド・バッファ・コピーの中にバッファリングすることができる。

## 【0217】

条件付きSSKE特徴がインストールされていない場合、SET STORAGE KEY EXTENDED命令によって、ストレージ・キーの中の7つのビットの全てが同時に設定される。条件付きSSKEがインストールされている場合、SET STORAGE KEY EXTENDED命令を用いて、プログラム指定基準に基づいてストレージ・キーの全て又は一部を設定することができる。 40

## 【0218】

INSERT STORAGE KEY EXTENDED命令は、4Kバイト・ブロックのためのストレージ・キーのビット0-6の一貫したイメージを提供する。同様に、INSERT VIRTUAL STORAGE KEY命令及びTEST PROTECTION命令は、アクセス制御ビット及びフェッチ保護ビットの一貫したイメージを提供する。 50

## 【0219】

RESET REFERENCE BIT EXTENDED命令は、参照ビットのみを修正する。ストレージ・キーの他の全てのビットは変更されないままである。条件コードを設定するために、参照ビット及び変更ビットが同時に検査される。

## 【0220】

参照ビットによって提供される参照の記録は、必ずしも正確でない。しかし、大部分の状況において、参照記録は、関連するストレージ参照とほぼ一致する。変更ビットを、ストアが発生しなかった場合に設定することができる。

## 【0221】

他のCPUによって観察される際に、ストレージ・キーを明示的に操作する命令 (INSERT STORAGE KEY EXTENDED, INSERT VIRTUAL STORAGE KEY, RESET REFERENCE BIT EXTENDED、及びSET STORAGE KEY EXTENDED) に起因するストレージ・キー・フェッチ及びストアは、あたかもストレージ・キー・アクセス自体がそれぞれストレージ・オペランド・フェッチ及びストアであるかのように、それ自体の中で、及びストレージ・オペランド参照の中で順序付けられる。

## 【0222】

アクセス制御及びフェッチ保護 (ACC/F)

主ストレージ又はメモリ内のデータ・ブロックは、セグメント・テーブル・エントリ内に与えられたアクセス制御ビット及びフェッチ保護ビットによって、さらに保護することができる。

## 【0223】

アクセス妥当性 (AV) 及びアクセス制御 (ACC)

ここで、変換された仮想アドレスによってアドレス指定される所望のデータ・ブロックに適用されるアクセス制御保護を判定する流れ図の一実施形態を示す、図12を参照する。

## 【0224】

動的アドレス変換は、図8においてノード616のところまで説明されたように、変換に用いられるセグメント・テーブルからセグメント・テーブル・エントリがフェッチされた時点まで進行する。アドレス変換は、図10においてノード822のところまで説明されたように、ストレージ又はメモリ内の所望のデータ・ブロックに対する絶対アドレスが取得されたところまで続行する。図12のフローはノード822から開始する。

## 【0225】

1002において、アクセス妥当性 (AV) フィールドがセグメント・テーブル・エントリから取得される。1004において、セグメント・テーブル・エントリ内のアクセス妥当性がイネーブルである (AV = 1) かどうかの判定が行われる。アクセス妥当性フィールドが0であれば、セグメント・テーブル・エントリ内のアクセス制御 (ACC) フィールドは有効ではない。1006において、アクセス制御 (ACC) フィールドのビットは無視される。アクセス妥当性フィールドがイネーブルであれば、アクセス制御フィールドは有効である。1008において、アクセス制御 (ACC) フィールドのビットがセグメント・テーブル・エントリから取得される。1010において、セグメント・テーブル・エントリ内のACCフィールドによって示されるアクセス制御保護レベルが、変換された仮想アドレスによってアドレス指定される所望のデータ・ブロックに適用される。

## 【0226】

別の実施形態において、所望のデータ・ブロックへのストア動作は、アクセス制御フィールドが、プログラム・ステータス・ワード又は実行中のプログラム命令のオペランドといったプログラム・エンティティによって与えられるアクセス・キーに一致した場合にのみ、許可される。所望のデータ・ブロックにおいてストアが試行され、且つアクセス制御フィールドがアクセス・キーに一致しなければ、保護例外が示されることが好ましい。

## 【0227】

10

20

30

40

50

さらに別の実施形態において、アクセス妥当性フィールドがイネーブルである場合、所望のメモリ・ブロックにおいてフェッチ動作又はストア動作が試行され、且つセグメント・アクセス制御フィールドがプログラム・アクセス制御フィールドに一致しなければ、保護例外が示される。

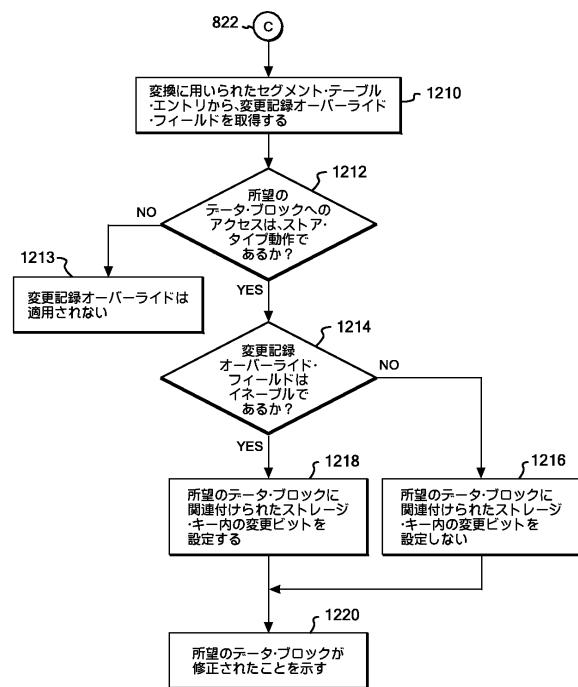

【0228】

アクセス妥当性 (AV) 及びフェッチ保護 (F)

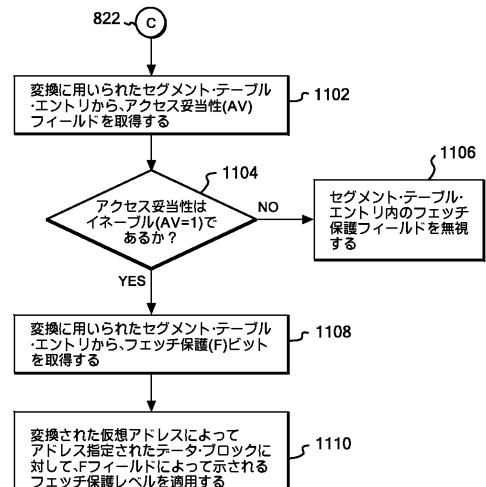

ここで、変換された仮想アドレスによってアドレス指定される所望のデータ・ブロックに適用されるフェッチ保護を判定する流れ図の一実施形態を示す、図13を参照する。

【0229】

動的アドレス変換は、図8においてノード616のところまで説明されたように、変換に用いられるセグメント・テーブルからセグメント・テーブル・エントリがフェッチされた時点まで進行する。アドレス変換は、図10においてノード822のところまで説明されたように、ストレージ又はメモリ内の所望のデータ・ブロックに対する絶対アドレスが取得されたところまで続行する。図13のフローはノード822から開始する。

【0230】

1102において、アクセス妥当性 (AV) フィールドがセグメント・テーブル・エントリから取得される。1104において、セグメント・テーブル・エントリ内のアクセス妥当性がイネーブルである (AV = 1) かどうかの判定が行われる。1104において、アクセス妥当性フィールドが0であれば、1106において、フェッチ保護ビットは無視される。1104において、アクセス妥当性フィールドがイネーブルであれば、1108において、フェッチ保護ビットがセグメント・テーブル・エントリから取得される。1110において、セグメント・テーブル・エントリ内のFフィールドによって示されるフェッチ保護レベルが、変換された仮想アドレスによってアドレス指定される所望のデータ・ブロックに適用される。変換された仮想アドレスによってアドレス指定されるデータ・ブロックからのフェッチ動作は、フェッチ保護フィールドがアクセス・キーに一致した場合にのみ、許可される。アクセス・キーは、プログラム・ステータス・ワード又は実行中のプログラム命令のオペランドによって与えられる。所望のデータ・ブロックからのフェッチ動作は、フェッチ保護フィールドがディスエーブルである場合、又はフェッチ保護フィールドがイネーブルであり、且つ仮想アドレスに関連付けられたアクセス制御フィールドがアクセス・キーに等しい場合にのみ、許可される。アクセス・キーが0であれば、所望のデータ・ブロックからのフェッチが許可される。

【0231】

さらに別の実施形態において、プログラム・アクセス・キーが0であれば、所望のメモリ・ブロックへのストア動作及び所望のメモリ・ブロックからのフェッチ動作が許可される。

【0232】

さらに別の実施形態において、アクセス妥当性フィールド及びフェッチ保護フィールドがイネーブルである場合、所望のメモリ・ブロックからのフェッチ動作が試行され、且つセグメント・アクセス制御フィールドがプログラム・アクセス制御フィールドに一致しないことに応答して、保護例外が示される。

【0233】

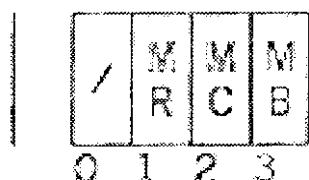

SET STORAGE KEY EXTENDED (SSKE)

ストレージ・キーは、SET STORAGE KEY EXTENDED (SSKE) 命令によって設定することができる。一実施形態において、SSKE命令は、以下のフォーマットを有する。

10

20

30

40

【表19】

| SSKE | $R_1, R_2 \& M_2$ | [RRF]       |

|------|-------------------|-------------|

| B22B | $M_3$             | ///         |

| 0    | 16                | 20 24 28 31 |

## SSKE命令のフォーマット

10

【0234】

1つ又は複数の4Kバイト・ブロックのためのストレージ・キーが、第1オペランド・レジスタ内の値で置換される。条件付きSSKEファシリティがインストールされている場合には、キー設定動作の特定の機能をバイパスすることができる。条件付きSSKEファシリティがインストールされていない場合、又は条件付きSSKEファシリティがインストールされ、且つM3フィールドのMRビット及びMCビットの両方が0である場合には、汎用レジスタR2の内容によってアドレス指定される4Kバイト・ブロックのためのストレージ・キーが、汎用レジスタR1からのビットで置換される。命令は、条件コードを変更することなく完了する。

【0235】

20

条件付きSSKEファシリティがインストールされ、且つMRビット及びMCビットの一方又は両方が1である場合には、汎用レジスタR2の内容によってアドレス指定されるストレージ・キーのアクセス制御ビット、フェッチ保護ビット、及び隨意に参照ビット及び変更ビットが、汎用レジスタR1内の対応するビットと比較される。比較されたビットが等しければ、キーに対する変更は行われない。そうでない場合には、キーの選択されたビットが、汎用レジスタR1内の対応するビットによって置換される。いずれかの変更の前のストレージ・キーは、汎用レジスタR1の中に挿入され、結果は条件コードによって示される。

【0236】

30