### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4822182号 (P4822182)

(45) 発行日 平成23年11月24日(2011.11.24)

(24) 登録日 平成23年9月16日 (2011.9.16)

| (51) Int.Cl. | FI                           |           |                        |        |

|--------------|------------------------------|-----------|------------------------|--------|

| HO1L 21/28   | ( <b>2006.01)</b> HO1L       | 21/28     | 3 O 1 B                |        |

| HO1L 29/12   | (2006.01) HO1L               | 21/28     | 3 O 1 R                |        |

| HO1L 29/78   | (2006.01) HO1L               | 21/28     | K                      |        |

| HO1L 29/417  | ( <b>2006.01)</b> HO1L       | 29/78 €   | 6 5 2 T                |        |

|              | HO1L                         | 29/78 €   | 654                    |        |

|              |                              |           | 請求項の数 7 (全 16 頁) 最終頁に紛 | きく<br> |

| (21) 出願番号    | 特願2006-191106 (P2006-191106) | (73) 特許権者 | 者 000003207            |        |

| (22) 出願日     | 平成18年7月12日 (2006.7.12)       |           | トヨタ自動車株式会社             |        |

| (65) 公開番号    | 特開2008-21757 (P2008-21757A)  |           | 愛知県豊田市トヨタ町1番地          |        |

| (43) 公開日     | 平成20年1月31日 (2008.1.31)       | (73)特許権者  | 者 301023238            |        |

| 審査請求日        | 平成21年2月12日 (2009.2.12)       |           | 独立行政法人物質・材料研究機構        |        |

|              |                              |           | 茨城県つくば市千現一丁目2番地1       |        |

|              |                              | (73)特許権者  | 者 000003609            |        |

|              |                              |           | 株式会社豊田中央研究所            |        |

|              |                              |           | 愛知県愛知郡長久手町大字長湫字横道4     | 1      |

|              |                              |           | 番地の1                   |        |

|              |                              | (74) 代理人  | 110000110              |        |

|              |                              |           | 特許業務法人快友国際特許事務所        |        |

|              |                              | (72) 発明者  | 杉本 雅裕                  |        |

|              |                              |           | 愛知県豊田市トヨタ町1番地 トヨタ自     | 動      |

|              |                              |           | 車株式会社内                 |        |

|              |                              |           | 最終頁に続く                 |        |

(54) 【発明の名称】半導体装置とその製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体装置を製造する方法であって、

p型の不純物を含む窒化ガリウム系半導体の第1部分領域とn型の不純物を含む窒化ガリウム系半導体の第2部分領域が表面に露出している半導体領域を酸化し、第1部分領域の少なくとも一部に酸化ガリウムを含む第1コンタクト層を形成するとともに第2部分領域の少なくとも一部にも酸化ガリウムを含む第2コンタクト層を形成する工程と、

第1コンタクト層に電気的に接続する第1電極を形成する工程と、

第2コンタクト層に電気的に接続する第2電極を形成する工程と、を備えており、

第1部分領域と第1電極は、第1コンタクト層を介してオーミック接続されており、

第2部分領域と第2電極は、第2コンタクト層を介してオーミック接続されている製造方法。

### 【請求項2】

半導体装置であって、

p型の不純物を含む窒化ガリウム系半導体の第1部分領域とn型の不純物を含む窒化ガリウム系半導体の第2部分領域を有する半導体領域と、

第1部分領域に電気的に接続する第1電極と、

第1部分領域と第1電極の間に形成されているとともに酸化ガリウムを含む第1コンタクト層と、

第2部分領域に電気的に接続する第2電極と、

第2部分領域と第2電極の間に形成されているとともに酸化ガリウムを含む第2コンタクト層と、を備えており、

第1部分領域と第1電極は、第1コンタクト層を介してオーミック接続されており、 第2部分領域と第2電極は、第2コンタクト層を介してオーミック接続されている半導体装置。

#### 【請求項3】

ゲート部とコンタクト部が横方向に並んで配置されている半導体装置であって、

ゲート部は、

p型の不純物を含む窒化ガリウム系半導体のp型半導体領域と、

ゲート電極と、

p型半導体領域とゲート電極の間に形成されているとともに窒化ガリウム系半導体の チャネル領域を有し、

コンタクト部は、

前記p型半導体領域に電気的に接続しているとともにp型の不純物を含む窒化ガリウム系半導体のp型部分領域と、

p型部分領域に電気的に接続する第1電極と、

p型部分領域と第1電極の間に形成されているとともに酸化ガリウムを含む第1コンタクト層と、

前記チャネル領域に電気的に接続しており、n型の不純物を含む窒化ガリウム系半導体のn型部分領域と、

n型部分領域に電気的に接続する第2電極と、

n型部分領域と第2電極の間に形成されているとともに酸化ガリウムを含む第2コンタクト層と、を備えており、

p型部分領域と第1電極は、第1コンタクト層を介してオーミック接続されており、 n型部分領域と第2電極は、第2コンタクト層を介してオーミック接続されている半導体装置。

### 【請求項4】

p型部分領域とn型部分領域が直接的に接しており、第1コンタクト層と第2コンタクト層が連続していることを特徴とする請求項3の半導体装置。

## 【請求項5】

チャネル領域は、第1チャネル領域と第2チャネル領域を有し、

第1チャネル領域のバンドギャップの幅と第2チャネル領域のバンドギャップの幅が異なっており、第1チャネル領域と第2チャネル領域がヘテロ接合していることを特徴とする請求項3又は4の半導体装置。

### 【請求項6】

第1チャネル領域は、アルミニウムを含まない窒化ガリウムであり、

第2 チャネル領域は、アルミニウムを含む窒化ガリウムであることを特徴とする請求項5 の半導体装置。

## 【請求項7】

請求項6の半導体装置を製造する方法であり、

ゲート部とコンタクト部に連続して伸びているp型半導体領域と第1チャネル領域と第2チャネル領域の積層体を準備し、コンタクト部の範囲に存在する第1チャネル領域及び第2チャネル領域の一部にn型の不純物を導入し、n型部分領域を形成する工程と、

その n 型部分領域の第 2 チャネル領域の一部を除去し、第 1 チャネル領域が露出する溝を形成する工程と、

その溝の底面において露出している第1チャネル領域の表面、及びその溝よりも反ゲート部側の第2チャネル領域の表面の一部を酸化し、第1チャネル領域の少なくとも一部に酸化ガリウムを含むコンタクト層を形成し、第2チャネル領域の少なくとも一部に酸化アルミニウムを含む絶縁領域する工程と、

前記コンタクト層に電気的に接続する第2電極を形成する工程と、

10

20

30

40

を備えている製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、窒化ガリウム系半導体を用いた半導体装置に関する。

#### 【背景技術】

#### [0002]

室化ガリウム系半導体を用いた半導体装置の開発が進められている。室化ガリウム系半導体は、高い破壊電界強度と高い飽和電子移動度を備えている。このため、窒化ガリウム系半導体を用いた半導体装置は、スイッチング素子としての利用が期待されている。この種の半導体装置には、種々の構造が提案されている。例えば、バンドギャップの幅が異なる窒化ガリウム系半導体で構成されたヘテロ接合を有する半導体装置の開発が進められている。

#### [0003]

ヘテロ接合を有する半導体装置は、ヘテロ接合面に形成される2次元電子ガス層を電子が走行する現象を利用する。ヘテロ接合に対向してゲート電極を形成すれば、ゲート電圧を利用して電子の走行を制御することができ、半導体装置のオン・オフを切換えることができる。一般的に、窒化ガリウム系半導体を用いたこの種の半導体装置は、負のゲート電圧を印加したときに電子が走行を停止し、ゲート電圧を印加していないときに電子が走行するノーマリオン型である。

#### [0004]

安全に使い易く、用途範囲が広いノーマリオフ型のスイッチング用の半導体装置が必要とされている。特許文献 1 に、ノーマリオフ型のスイッチング用の半導体装置が開示されている。特許文献 1 では、ヘテロ接合を構成しているチャネル領域に対向してp型の不純物を含むp型半導体領域を形成する技術が提案されている。p型半導体領域は、ゲート電圧が印加していない状態において、チャネル領域を空乏化する。このため、p型半導体領域が設けられていると、ゲート電圧を印加していない状態において、ヘテロ接合面に 2 次元電子ガス層が形成されない状態を作り出すことができる。したがって、p型半導体領域が設けられた半導体装置は、ゲート電圧が印加されていない状態で電子が走行を停止し、正のゲート電圧を印加したときに電子が走行するノーマリオフ型である。

## [0005]

特許文献1の構造では、p型半導体領域の電位を安定させるために、p型半導体領域と電極(例えば、ソース電極)を電気的に接続している。特許文献1の構造ではさらに、n型の半導体領域(ソース領域又はドレイン領域)と電極(ソース電極又はドレイン電極)を電気的に接続している。特許文献1の構造では、p型の半導体領域と電極のコンタクト特性(特に、オーミック性)と、n型の半導体領域と電極のコンタクト特性(特に、接触抵抗)の両者を改善する技術が望まれている。

#### [0006]

特許文献 2 には、 p 型の不純物を含む窒化ガリウム系半導体の半導体領域と電極のコンタクト特性を改善するために、 p 型の半導体領域と電極の間に、PdAu合金やNi Au合金を形成する技術が提案されている。

一方、n型の不純物を含む窒化ガリウム系半導体の半導体領域と電極のコンタクト特性を改善するためには、TiやAIなどが一般的に用いられる。

#### [0007]

また、特許文献 3 ~ 5 には、発光素子の透明電極に酸化ガリウム( $Ga_2O_3$ )を用いる技術が提案されている。

### [0008]

【特許文献 1 】特開 2 0 0 4 - 2 6 0 1 4 0 号公報

【特許文献2】特表2005-503041号公報

10

20

30

10

20

30

40

50

【特許文献3】特開2005-217437号公報

【特許文献 4 】特開 2 0 0 5 - 2 3 5 9 6 1 号公報

【特許文献 5 】特開 2 0 0 5 - 2 6 0 1 0 1 号公報

【発明の開示】

【発明が解決しようとする課題】

[0009]

p型の半導体領域と電極の間のコンタクト特性とn型の半導体領域と電極の間のコンタクト特性の両者を改善したいという要求は、様々な半導体装置において存在する。p型の半導体領域と電極の間にPdAu合金やNiAu合金を用い、n型の半導体領域と電極の間にTiやAIを用いれば、それぞれのコンタクト特性を改善することができる。しかしながら、そのような半導体装置を製造しようとすると、PdAu合金やNiAu合金を局所的に形成する工程とTiやAIを局所的に形成する工程のそれぞれが必要となる。このため、製造工程数が増加し、製造コストを増加させてしまう。少ない工程数で製造することが可能であるとともに、p型の半導体領域と電極の間のコンタクト特性とn型の半導体領域と電極の間のコンタクト特性の両者を改善する技術が必要とされている。

本発明は、上記の課題を解決する技術を提供する。

【課題を解決するための手段】

[0010]

本発明は、半導体装置を製造する方法を提供する。本発明の製造方法は、p型の不純物を含む窒化ガリウム系半導体の第1部分領域とn型の不純物を含む窒化ガリウム系半導体の第2部分領域が表面に露出している半導体領域を酸化し、第1部分領域の少なくとも一部に酸化ガリウムを含む第1コンタクト層を形成するとともに第2部分領域の少なくとも一部にも酸化ガリウムを含む第2コンタクト層を形成する工程を備えている。本発明の製造方法はさらに、第1コンタクト層に電気的に接続する第1電極を形成する工程と、第2コンタクト層に電気的に接続する第2電極を形成する工程を備えている。第1部分領域と第1電極は、第1コンタクト層を介してオーミック接続されている。第2部分領域と第2電極は、第2コンタクト層を介してオーミック接続されている。第1電極と第2電極は、共通の電極でもよく、別個の電極でもよい。

本発明は、第1コンタクト層と第2コンタクト層に共通の材料である酸化ガリウムを用いることを特徴としている。酸化ガリウムは導電性を有しており、p型の半導体領域と電極の間を良好に電気的に接続することができる。さらに、酸化ガリウムは、n型の半導体領域と電極の間も良好に電気的に接続することができる。本発明の製造方法では、p型の第1部分領域の表面とn型の第2部分領域の表面のそれぞれに専用のコンタクト層を形成しない。本発明の製造方法では、第1コンタクト層と第2コンタクト層の両者が、同一工程で作成される。本発明の製造方法を利用すると、少ない工程数で製造することが可能であるとともに、p型の第1部分領域と第1電極の間のコンタクト特性とn型の第2部分領域と第2電極の間のコンタクト特性の両者を改善することができる。

なお、特許文献 3~5には、発光素子の透明電極に酸化ガリウムを用いる技術が提案されている。特許文献 3~5の技術思想は、酸化ガリウムが透明であるという特性に着目して創作されたものである。本発明の技術思想は、透明であるという特性に全く着目している。透明であるという特性に全く着目している。透明であるという特性に全く着目している。透明であるという特性の改善に係る技術思想は相容れないものである。例えば、コンタクト特性の改善に係る技術思想は相容れないものである。例えば、コンタクト特性の改善のよば、p型の半導体領域にはPdAu合金やNiAu合金を用い、n型の半導体領域にはTiやAIを用いようとする。透明であるという特性で注目されている酸化ガリウムが従来から知られていたとしても、その材料をコンタクト特性の改善のために用いようとする着想は得られない。なぜなら、酸化ガリウムは、PdAu合金、NiAu合金、Ti及びAIの材料よりもコンタクト特性を悪化させ得るからである。本発明は、P型の大導体領域のコンタクト特性を積極にしてでも工程数が削減できるという利益を享受するものである。本発明は、P型の半導体領域とn型の半導体領域のコンタク

ト特性の改善と工程数の削減を同時に得ることができる有用な技術である。

#### [0011]

本発明は、半導体装置をも提供する。本発明の一つの半導体装置は、p型の不純物を含む窒化ガリウム系半導体の第1部分領域とn型の不純物を含む窒化ガリウム系半導体の第2部分領域を有する半導体領域を備えている。本発明の半導体装置はさらに、第1部分領域に電気的に接続する第1電極と、第1部分領域と第1電極の間に形成されているとともに酸化ガリウムを含む第1コンタクト層を備えている。本発明の半導体装置はさらに、第2部分領域に電気的に接続する第2電極と、第2部分領域と第2電極の間に形成されているとともに酸化ガリウムを含む第2コンタクト層を備えている。第1部分領域と第1電極は、第1コンタクト層を介してオーミック接続されている。第2部分領域と第2電極は、第2コンタクト層を介してオーミック接続されている。

本発明の半導体装置では、第1コンタクト層が第1部分領域と第1電極の間を良好に電気的に接続し、第2コンタクト層が第2部分領域と第2電極の間を良好に電気的に接続する。第1コンタクト層と第2コンタクト層は、共通の材料であり、同一工程で作成することができる。本発明の半導体装置は、少ない工程数で製造することが可能であるとともに、p型の第1部分領域と第1電極の間のコンタクト特性とn型の第2部分領域と第2電極の間のコンタクト特性の両者を改善することができる。

## [0012]

本発明は、ゲート部とコンタクト部が横方向に並んで配置されている半導体装置に具現化することができる。本発明の半導体装置のゲート部は、p型の不純物を含む窒化ガリウム系半導体のp型半導体領域と、ゲート電極と、p型半導体領域とゲート電極の間に形成されているとともに窒化ガリウム系半導体のチャネル領域を有している。本発明の半導体装置のコンタクト部は、p型半導体領域に電気的に接続しているとともにp型の不純物を含む窒化ガリウム系半導体のp型部分領域と、そのp型部分領域に電気的に接続する第1電極と、p型部分領域と第1電極の間に形成されているとともに酸化ガリウムを含む第1コンタクト層を備えている。本発明のコンタクト部はさらに、チャネル領域に電気的に接続しているとともにn型の不純物を含む窒化ガリウム系半導体のn型部分領域と、n型部分領域に電気的に接続する第2電極と、n型部分領域と第2電極の間に形成されているとともに酸化ガリウムを含む第2コンタクト層を備えている。p型部分領域と第1電極は、第1コンタクト層を介してオーミック接続されている。

上記の半導体装置では、ゲート電極に電圧が印加していない状態において、p型半導体領域から伸展する空乏層がチャネル領域を空乏化する。このため、上記の半導体装置は、ノーマリオフで動作することができる。この種の半導体装置では、p型半導体領域の電位を安定させるために、コンタクト部に設けられたp型部分領域を介してp型半導体領域と第1電極を電気的に接続している。一方、この種の半導体装置では、チャネル領域に電子を供給するために、コンタクト部に設けられたn型部分領域を介してチャネル領域と第2電極を電気的に接続している。本発明の半導体装置では、p型部分領域と第1電極の間のコンタクト特性が第1コンタクト層によって改善されており、n型部分領域と第2電極の間のコンタクト特性が第2コンタクト層によって改善されている。

第1コンタクト層と第2コンタクト層は、共通の材料であり、同一工程で作成することができる。本発明の半導体装置は、少ない工程数で製造することが可能であるとともに、p型の第1部分領域と第1電極の間のコンタクト特性とn型の第2部分領域と第2電極の間のコンタクト特性の両者を改善することができる。

### [0013]

ゲート部とコンタクト部を有する半導体装置では、p型部分領域とn型部分領域が直接的に接しており、第1コンタクト層と第2コンタクト層が連続していることが好ましい。

10

20

30

40

第 1 コンタクト層と第 2 コンタクト層を共通化することによって、第 1 コンタクト層と 第 2 コンタクト層がセルフアライン的に形成され、半導体装置が小型化される。

#### [0014]

チャネル領域を有する半導体装置では、そのチャネル領域が、第1チャネル領域と第2 チャネル領域を有しているのが好ましい。第1チャネル領域のバンドギャップの幅と第2 チャネル領域のバンドギャップの幅が異なっており、第1チャネル領域と第2チャネル領域がヘテロ接合していることが好ましい。

上記の半導体装置では、第1チャネル領域と第2チャネル領域の間に2次元電子ガス層が形成され、電子はその2次元電子ガス層を利用して走行することができる。上記の半導体装置のチャネル抵抗は小さい。

[0015]

第1チャネル領域には、アルミニウムを含まない窒化ガリウムを用いることができる。 第2チャネル領域には、アルミニウムを含む窒化ガリウムを用いることができる。アルミニウムを含む窒化ガリウムのバンドギャップの幅は、アルミニウムの含有比を増加させることによって、アルミニウムを含まない窒化ガリウムのバンドギャップの幅よりも大きくすることができる。

[0016]

本発明は、第1チャネル領域にアルミニウムを含まない窒化ガリウムが用いられ、第2 チャネル領域にアルミニウムを含む窒化ガリウムが用いられている半導体装置を製造する 方法を提供することができる。

本発明の製造方法は、ゲート部とコンタクト部に連続して伸びている p 型半導体領域と第 1 チャネル領域と第 2 チャネル領域の積層体を準備し、コンタクト部の範囲に存在する第 1 チャネル領域及び第 2 チャネル領域の一部に n 型の不純物を導入し、 n 型部分領域を形成する工程を備えている。本発明の製造方法は、その n 型部分領域の第 2 チャネル領域の一部を除去し、第 1 チャネル領域が露出する溝を形成する工程を備えている。本発明の製造方法は、その溝の底面において露出している第 1 チャネル領域の表面、及びその溝よりも反ゲート部側の第 2 チャネル領域の表面の一部を酸化し、第 1 チャネル領域の少なくとも一部に酸化アルミニウムを含む絶縁領域する工程を備えている。本発明の製造方法はさらに、コンタクト層に電気的に接続する第 2 電極を形成する工程を備えている。 p 型部分領域と第 1 電極は、第 1 コンタクト層を介してオーミック接続されている。

上記の製造方法では、溝の底面において露出している第1チャネル領域の表面、及び第2チャネル領域の表面の一部を同時に酸化することによって、第1チャネル領域の少なくとも一部に酸化ガリウムを含むコンタクト層を形成し、第2チャネル領域の少なくとも一部に酸化アルミニウムを含む絶縁領域することを特徴としている。この工程によって、第2電極に接続するためのコンタクト層が形成されるとともに、半導体装置を周囲から絶縁分離するための絶縁領域も同時に形成することができる。

## 【発明の効果】

[0017]

本発明によると、p型の半導体領域とn型の半導体領域の両者に対して、少ない工程数で電極を設けることができる。

【発明を実施するための最良の形態】

[0018]

本発明の好ましい形態を列記する。

(第1形態) 窒化ガリウム系半導体は、一般式がAl<sub>X</sub>Ga<sub>Y</sub>In<sub>1-X-Y</sub>N(ただし、0 X 1、0 < Y 1、0 1 - X - Y 1)で表される。

(第2形態) p型部分領域の表面及びn型部分領域の表面に対する酸化処理は、熱酸化処理、オゾン処理等を利用することができる。

【実施例】

10

20

30

#### [0019]

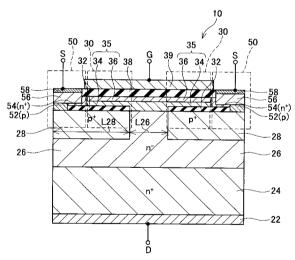

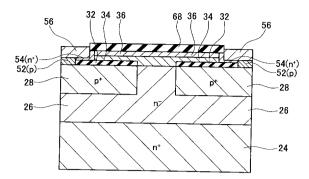

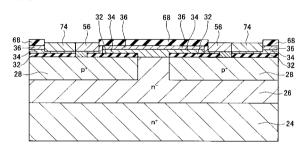

図1に、ヘテロ接合を有する縦型の半導体装置10の要部断面図を模式的に示す。

半導体装置 10 は、アルミニウム(AI)のドレイン電極 22 を裏面に備えている。半導体装置 10 は、そのドレイン電極 22 上に形成されており、窒化ガリウム(GaN)を主材料とする  $n^{+}$ 型のドレイン層 24 を備えている。ドレイン層 24 の不純物には、シリコン(Si)又は酸素(0)が用いられており、そのキャリア濃度は約  $3\times10^{18}$  cm<sup>-3</sup> に調整されている。ドレイン層 24 の厚みは、約 200 u mである。

## [0020]

半導体装置 10 は、ドレイン層 24 上に形成されており、窒化ガリウムを主材料とする n 型の低濃度半導体領域 26 を備えている。低濃度半導体領域 26 の不純物にはシリコンが用いられており、そのキャリア濃度は約  $1\times10^{16}$  cm<sup>-3</sup> に調整されている。

#### [0021]

半導体装置10は、低濃度半導体領域26上の一部に形成されており、窒化ガリウムを主材料とするp<sup>+</sup>型のp型半導体領域28を備えている。p型半導体領域28は、低濃度半導体領域26上に相互間に間隔を残して分散して配置されている。p型半導体領域28の不純物にはマグネシウム(Mg)が用いられており、そのキャリア濃度は約1×10<sup>18</sup> cm <sup>-3</sup>に調整されている。p型半導体領域28の厚みは、約0.5μmである。p型半導体領域28は、低濃度半導体領域26上に複数個が形成されている。複数個のp型半導体領域28は、低濃度半導体領域26上に分散して形成されている。p型半導体領域28とそれに隣合うp型半導体領域28の間には、低濃度半導体領域26の一部が介在しており、その一部は凸状の形状を有している。

#### [0022]

図1に示すように、この例では、紙面左右に2つのp型半導体領域28が図示されている。平面視したときに、p型半導体領域28は、紙面奥行き方向に長く伸びている。複数個のp型半導体領域28は、低濃度半導体領域26上にストライプ状に配置されている。後述するように、p型半導体領域28とそれに隣合うp型半導体領域28の間に介在する凸状の低濃度半導体領域26の一部は、電流が縦方向に流れる領域である。したがって、p型半導体領域28が分散して形成されていることによって、電流が縦方向に流れる凸状の低濃度半導体領域26の一部が、半導体装置10の面内に多く確保される。このため、半導体装置10は、小さなオン抵抗を得ることができる。

p型半導体領域28の横方向の距離L28は、約10~25μmである。なお、図1は、半導体装置10の単位構造を表しており、実際には、その単位構造が紙面左右に繰り返し形成されている。したがって、実際のp型半導体領域28の横方向の距離は、前記距離L28の約2倍になる。p型半導体領域28とそれに隣合うp型半導体領域28の間の距離L26は、約1~10μmである。

#### [0023]

半導体装置10は、p型半導体領域28上に形成されており、窒化アルミニウム(AIN)を主材料とする不純物拡散抑制膜32を備えている。不純物拡散抑制膜32は、p型半導体領域28に含まれているマグネシウムが、チャネル領域35等に拡散するのを抑制する。不純物拡散抑制膜32は、p型半導体領域28上の全範囲を覆っていない。後述するように、p型半導体領域28とソース電極58が電気的に接続するために、p型半導体領域28の上面の一部は、不純物拡散抑制膜32で被覆されていない。

#### [0024]

半導体装置10は、低濃度半導体領域26上及び不純物拡散抑制膜32上に形成されているチャネル領域35を備えている。チャネル領域35は、バンドギャップの幅が異なる第1チャネル領域34と第2チャネル領域36を備えている。第1チャネル領域34は、p型半導体領域28側に設けられている。第1チャネル領域34と第2チャネル領域36は直接的に接しており、第1チャネル領域34と第2チャネル領域36によってヘテロ接合が構成されている。

## [0025]

10

20

30

第 1 チャネル領域 3 4 には、窒化ガリウムが用いられている。第 1 チャネル領域 3 4 の不純物にはシリコンが用いられており、そのキャリア濃度は約  $1 \times 1 \ 0^{16} \text{ cm}^{-3}$ に調整されている。第 1 チャネル領域 3 4 の厚みは、約  $1 \ 0 \ 0 \text{ nm}$ である。

#### [0026]

第 2 チャネル領域 3 6 には、窒化ガリウム・アルミニウム( $AI_{0.3}Ga_{0.7}N$ )が用いられている。第 2 チャネル領域 3 6 の結晶構造にはアルミニウムが含まれており、そのバンドギャップの幅は、第 1 チャネル領域 3 4 のバンドギャップの幅よりも広い。第 2 チャネル領域 3 6 の不純物にはシリコンが用いられており、そのキャリア濃度は約 1  $\times$  1 0  $^{16}cm^{-3}$ に調整されている。第 2 チャネル領域 3 6 の厚みは、約 2 5 nmである。

## [0027]

半導体装置10は、第2チャネル領域36上に形成されており、酸化シリコンを主材料とするゲート絶縁膜38を備えている。半導体装置10はさらに、ゲート絶縁膜38上に形成されており、ポリシリコンを主材料とするゲート電極39を備えている。なお、本実施例のゲート電極39は、チャネル領域35のほぼ全範囲に対向して形成されているが、後述するように、ゲート電極39は、p型半導体領域28に対向する位置の少なくとも一部に形成されていればよい。ゲート電極39は、ソース領域54とp型半導体領域28の中央側端部の間に存在するチャネル領域35に対向する部分に形成されていればよい。この場合、半導体装置10のオン・オフを正確に切替えることができる。p型半導体領域28、不純物拡散抑制膜32、第1チャネル領域34、及び第2チャネル領域36が積層している部分をゲート部30という。

#### [0028]

半導体装置10はさらに、コンタクト部50を備えている。コンタクト部50は、窒化ガリウムを主材料とするp型のp型部分領域52を備えている。p型部分領域52は、不純物拡散抑制膜32に形成されている開孔を介してp型半導体領域28に直接的に接している。後述するが、p型部分領域52は、p型半導体領域28に存在するマグネシウムが拡散することによって形成される。

### [0029]

コンタクト部 5 0 は、室化ガリウムを主材料とする n  $^+$  型のソース領域 5 4 (n 型部分領域の一例)を備えている。ソース領域 5 4 は、チャネル領域 3 5 に直接的に接している。ソース領域 5 4 は、 p 型半導体領域 2 8 に対向する位置に形成されている。ソース領域 5 4 は、 p 型半導体領域 2 8 とそれに隣合う p 型半導体領域 2 8 の間に介在している凸状の低濃度半導体領域 2 6 の一部に対して、ゲート部 3 0 を挟んで対向している。換言すると、水平方向において、 p 型半導体領域 2 8 とそれに隣合う p 型半導体領域 2 8 の間に介在している凸状の低濃度半導体領域 2 6 の一部とソース領域 5 4 の間には、ゲート部 3 0 が介在している。ソース領域 5 4 の不純物にはシリコンが用いられており、そのキャリア濃度は約 3 × 1 0 18 cm 18 cm

## [0030]

コンタクト部 5 0 は、アルミニウムのソース電極 5 8 を備えている。コンタクト部 5 0 はさらに、 p 型部分領域 5 2 とソース電極 5 8 の間に形成されており、酸化ガリウム (  $Ga_2O_3$  ) を主材料とするコンタクト層 5 6 を備えている。コンタクト層 5 6 は、ソース領域 5 4 とソース電極 5 8 の間にも形成されている。コンタクト層 5 6 は、 p 型部分領域 5 2 とソース電極 5 8 の間を良好に電気的に接続するとともに、ソース領域 5 4 とソース電極 5 8 の間も良好に電気的に接続している。

## [0031]

次に、半導体装置10の動作を説明する。

p型半導体領域28が不純物拡散抑制膜32を介して第1チャネル領域34に間接的に接している。このため、ゲート電極39に電圧を印加していない状態では、第1チャネル領域34に空乏層が形成され、その空乏層は第1チャネル領域34と第2チャネル領域36のヘテロ接合面にまで伸びている。これにより、ヘテロ接合面の伝導体のエネルギー準位は、フェルミ準位よりも上側に存在することになる。このため、ゲート電極39に電圧

10

20

30

40

を印加していない状態では、2次元電子ガス層は、ヘテロ接合面に形成されない。したがって、ゲート電極39に電圧が印加されていない状態では、電子の走行が停止され、半導体装置10は、ノーマリオフとして動作する。

### [0032]

ゲート電極39に正の電圧が印加されている状態では、第1チャネル領域34に形成されていた空乏層が縮小し、第1チャネル領域34と第2チャネル領域36のヘテロ接合面の伝導体のエネルギー準位は、フェルミ準位よりも下側に存在することになる。これにより、ヘテロ接合面に2次元電子ガス層が形成される。このため、ゲート電極39に正の電圧が印加されている状態では、2次元電子ガス層内のポテンシャル井戸内に電子が存在する状態が作り出される。この結果、2次元電子ガス層内を電子が走行し、半導体装置10はオンとなる。ソース領域54からヘテロ接合面の2次元電子ガス層に沿って横方向に走行してきた電子は、低濃度半導体領域26の凸部(p型半導体領域28を隔てている部分であり、低濃度半導体領域26が第1チャネル領域34に接する部分である)を縦方向に流れ、低濃度半導体領域26及びドレイン層24を経由してドレイン電極22まで流れる。これにより、ソース電極58とドレイン電極22の間が導通する。

#### [0033]

上記したように、半導体装置10のオン・オフの制御は、p型半導体領域28、不純物拡散抑制膜32、第1チャネル領域34、第2チャネル領域36、ゲート絶縁膜38及びゲート電極39が積層しているゲート部30で行われている。即ち、半導体装置10のオン・オフの制御は、ゲート電極39に印加する電圧によって、第1チャネル領域34に形成されている空乏層の厚み方向の幅を制御することによって行われている。

#### [0034]

p型半導体領域28は、p型部分領域52とコンタクト層56を介してソース電極58に電気的に接続している。コンタクト層56は、p型部分領域52とソース電極58の間に良好なオーミック接続を提供する。このため、p型半導体領域28の電位は、ソース電極58の電位、即ち接地電位に安定して固定される。このため、p型半導体領域28から第1チャネル領域34内に伸展する空乏層も安定して形成される。この結果、半導体装置10のオン・オフの制御は、ゲート電極39に印加する電圧に基づいて良好に制御される

さらに、コンタクト層 5 6 は、ソース領域 5 4 とソース電極 5 8 の間にも良好な電気的な接続を提供する。このため、ソース領域 5 4 とソース電極 5 8 の間のコンタクト抵抗が小さい。この結果、半導体装置 1 0 のオン抵抗は、小さい値になる。

さらに、コンタクト層 5 6 は、p型部分領域 5 2 とソース領域 5 4 の両者に共通して設けられている。半導体装置 1 0 は、p型部分領域 5 2 とソース領域 5 4 のそれぞれに専用のコンタクト層を形成しない。コンタクト層 5 6 は、同一工程で作成することができる。半導体装置 1 0 は、少ない工程数で製造することが可能であるとともに、p型部分領域 5 4 とソース電極 5 8 の間のコンタクト特性とソース領域 5 2 とソース電極の間のコンタクト特性の両者を改善することができる。

## [0035]

## (半導体装置10の製造方法)

次に半導体装置10の製造方法を説明する。

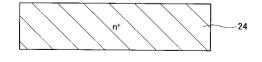

まず、図2に示すように、n<sup>+</sup>型の窒化ガリウムを主材料とする半導体基板24(後にドレイン層24となる)を用意する。半導体基板24の厚みは約200μmである。

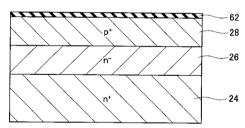

次に、図3に示すように、MOCVD (Metal Organic Chemical Vapor Deposition) 法を利用して、半導体基板24上にn 型の低濃度半導体領域26を結晶成長する。低濃度半導体領域26の厚みは、約6μmである。さらに、MOCVD法を利用して、低濃度半導体領域26上にp 型のp型半導体領域28を結晶成長する。p型半導体領域28の厚みは、約0.5μmである。次に、CVD (Chemical Vapor Deposition) 法を利用して、p型半導体領域28上に酸化シリコンのマスク62を成膜する。

## [0036]

10

20

30

40

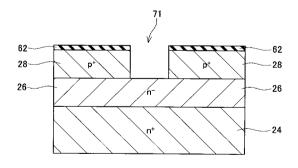

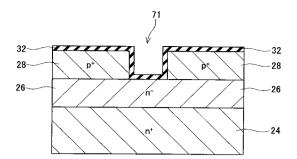

次に、図4に示すように、リソグラフィー技術を利用して、マスク62の一部を除去する。次に、RIE技術を利用して、露出するp型半導体領域28の一部を貫通して低濃度半導体領域26にまで達するトレンチ71を形成する。トレンチ71を形成した後に、マスク62を除去する。

次に、図5に示すように、MOCVD法を利用して、p型半導体領域28及び低濃度半導体領域26の表面に窒化アルミニウムの不純物拡散抑制膜32を成膜する。

次に、図6に示すように、リソグラフィー技術を利用して、トレンチ71の内壁に形成されている不純物拡散抑制膜32を除去するとともに、p型半導体領域28がコンタクトするための開孔に対応する部分の不純物拡散抑制膜32を除去する。

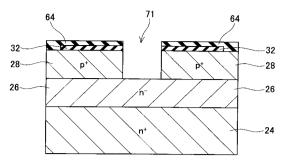

次に、図7に示すように、CVD法を利用して、不純物拡散抑制膜32及び露出するp型半導体領域28上に酸化シリコンのマスク64を形成する。

### [0037]

次に、図8に示すように、MOCVD法を利用して、トレンチ71の底面において露出している低濃度半導体領域26の表面から窒化ガリウムを結晶成長する。結晶成長は、p型半導体領域28と同一の高さになるまで続ける。形成される結晶の不純物濃度は、低濃度半導体領域26の不純物濃度と同一に調整されている。このため、結晶成長した部分と低濃度半導体領域26は、連続した一つの領域と評価することができる。

## [0038]

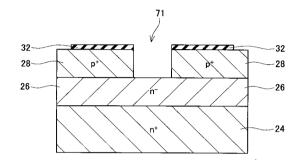

次に、図9に示すように、マスク64を除去した後に、トレンチ71において露出している低濃度半導体領域26の表面、不純物拡散抑制膜32の表面及び露出しているp型半導体領域28の表面から窒化ガリウムを結晶成長し、第1チャネル領域34を形成する。第1チャネル領域34の厚みは、100mである。第1チャネル領域34の不純物濃度は、低濃度半導体領域26の不純物濃度と同一に調整されている。

なお、不純物抑制膜 3 2 の材料に、酸化シリコン又は窒化シリコンを用いると、この工程において選択横方向成長法 (ELO) の技術を利用することができる。酸化シリコン又は窒化シリコンは、それらの表面から結晶成長が生じない。したがって、トレンチ 7 1 において露出している低濃度半導体領域 2 6 の表面からの結晶成長が、不純物拡散抑制膜 3 2 の表面を横方向に進行する。このとき、不純物拡散抑制膜 3 2 の表面を覆って形成される部分は、結晶欠陥の密度が低減化された良質な半導体層になる。なお、ELO技術で成長した半導体層の厚みが厚い場合は、エッチング、研磨などにより所望の厚さに調整することができる。

## [0039]

次に、図10に示すように、MOCVD法を利用して、第1チャネル領域34上に第2チャネル領域36を結晶成長する。第2チャネル領域36の厚みは25nmである。

なお、第1チャネル領域34及び第2チャネル領域36を形成すると同時に、p型半導体領域28に含まれていたマグネシウムの一部が、不純物拡散抑制膜32の開孔から第1チャネル領域34及び第2チャネル領域36の一部に拡散し、p型部分領域52を形成する。

次に、CVD法を利用して、第2チャネル領域36の表面に酸化シリコンのマスク66を 形成する。次に、マスク66は、リソグラフィー技術とエッチング技術を利用して、コン タクト部に対応する部分が選択的に除去される。

次に、イオン注入技術を利用して、マスク66の開孔から露出している第2チャネル領域36及び第1チャネル領域34に不純物を導入する。このとき、窒素をドーズ量1×10 $^{15}$  cm $^{-2}$ 、加速電圧35eVで注入した後に、シリコンをドーズ量1×10 $^{15}$  cm $^{-2}$ 、加速電圧65eVで注入する。イオン注入をした後に、マスク66を除去する。

## [0040]

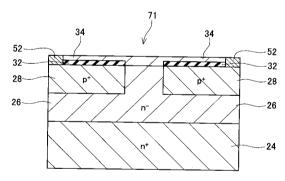

次に、図11に示すように、第2チャネル領域36の表面全体に、酸化シリコンのマスク67を形成する。マスク67を形成した後に、アニール処理(N₂雰囲気下、1100、20分)を実施する。アニール処理を実施すると、先のイオン注入で導入された窒素及び酸素の不純物が活性化してソース領域54が形成される。アニール処理後、酸化シリコ

10

20

30

10

20

30

40

50

ンのマスク67を除去する。

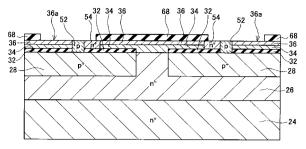

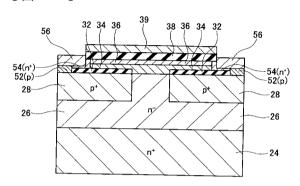

## [0041]

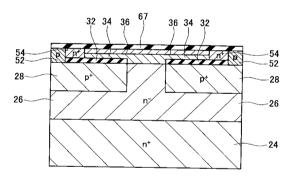

次に、図12に示すように、CVD法を利用して、100nmの厚さのポリシリコンのマスク68を形成する。次に、リソグラフィー技術とエッチング技術を利用して、マスク68の一部に開孔を形成する。この開口部は、後に酸化ガリウムのコンタクト層を形成する部分に対応している。さらに、その開口部から露出しているソース領域54及びp型部分領域52のうち第2チャネル領域36に対応する部分を除去し、ソース領域54及びp型部分領域52のうち第1チャネル領域34に対応する部分の表面を露出する。

次に、図13に示すように、酸化処理(酸素雰囲気下、880 、5時間)を実施する。酸化処理によって、p型部分領域52の表面及びソース領域54の表面が酸化され、酸化ガリウムのコンタクト層56が形成される。コンタクト層56は、p型部分領域52とソース領域54の両者に連続して形成される。なお、詳細には、コンタクト層56のうちp型部分領域52を酸化して形成される部分の厚みとコンタクト層56のうちソース領域54を酸化して形成される部分の厚みは異なっていることが多い。図13では、コンタクト層56がp型部分領域52とソース領域54の両者に連続して形成されていることを明瞭にするために、簡単化して図示している。また、本工程の酸化処理によってマスク68も酸化され、酸化シリコンとポリシリコンの積層膜となるが、図12では簡単化して図示している。マスク68は、酸化処理後にフッ酸によるエッチングによって除去する。

## [0042]

次に、HTO(High Temperature Oxide)法を利用して、酸化シリコンのゲート絶縁膜38を形成する。ゲート絶縁膜38の厚みは、50nmである。

次に、CVD法を利用して、ゲート絶縁膜38の表面に不純物が高濃度に導入されたポリシリコンのゲート電極39を形成する。次に、リソグラフィー技術及びエッチング技術を利用して、ゲート絶縁膜38とゲート電極39を所望の形状に加工する。この工程を経て、図14に示す構造が得られる。

### [0043]

次に、スパッタ法を利用して、コンタクト層 5 6 の表面にソース電極 5 8 を蒸着する。 ソース電極 5 8 は、コンタクト層 5 6 を介して p 型部分領域 5 2 及びソース領域 5 4 の両者に電気的に接続している。

酸化ガリウムのコンタクト層 5 6 は導電性を有しており、 p 型部分領域 5 2 とソース電極 5 8 の間を良好に電気的に接続することができる。さらに、コンタクト層 5 6 は、ソース領域 5 4 とソース電極 5 8 の間も良好に電気的に接続することができる。本実施例の製造方法では、 p 型部分領域 5 2 の表面とソース領域 5 4 の表面のそれぞれに専用のコンタクト層を形成しない。本実施例の製造方法を利用すると、少ない工程数で製造することが可能であるとともに、 p 型部分領域 5 2 とソース電極 5 8 の間のコンタクト特性とソース領域 5 4 とソース電極 5 8 の間のコンタクト特性の両者を改善することができる。さらに、コンタクト層 5 6 及びソース電極 5 8 を少ない面積にすることができる。本実施例の製造方法は、半導体装置 1 0 の小型化に寄与することができる。

### [0044]

次に、スパッタ法を利用して、ドレイン層 2 4 の裏面にドレイン電極 2 2 を形成する。 最後にアニール処理を実施する。これらの工程を経て、図 1 に示す半導体装置 1 0 を得る ことができる。

## [0045]

上記の製造方法は、他に以下の工程を含んでいてもよい。

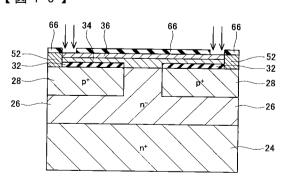

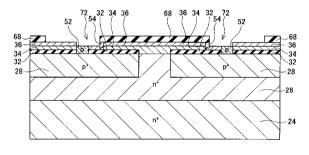

図15に、半導体装置10の他の製造方法の製造過程を示す。図15の製造過程は、ソース領域54及びp型部分領域52のうち第2チャネル領域36に対応する部分を除去する前の段階であり、図12の製造過程に対応している。

### [0046]

図15に示すように、マスク68の一部を除去し、ソース領域54、p型部分領域72

、及び反ゲート部側の第2チャネル領域36の表面36aを露出させる。

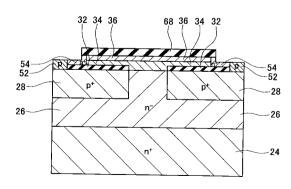

次に、図16に示すように、ソース領域54の一部及びp型部分領域52の一部を除去 し、溝72を形成する。溝72は、ソース領域54及びp型部分領域52に形成され、第 2 チャネル領域 3 6 に形成されていない。溝 7 2 の深さは、第 2 チャネル領域 3 6 の厚み に対応している。したがって、溝 7 2 を形成することによって、ソース領域 5 4 及び p 型 部分領域52のうち第2チャネル領域36に対応する部分が除去され、ソース領域54及 びp型部分領域52のうち第1チャネル領域34に対応する部分の表面が露出する。

### [0047]

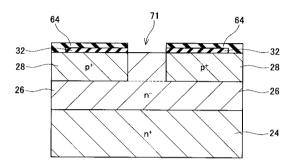

次に、図17に示すように、酸化処理(酸素雰囲気下、880 、5時間)を実施する 。酸化処理によって、ソース領域54の表面及びp型部分領域52の表面が酸化され、酸 化ガリウムのコンタクト層56が形成される。同時に、第2チャネル領域36の表面36 aが酸化され、酸化アルミニウムを含む絶縁領域74が形成される。

絶縁領域74は、第2チャネル領域36及び第1チャネル領域34内に形成され、ヘテ 口接合面を実質的に破壊する。このため、素子分離を良好に行うことができる。この素子 分離技術は、複数の半導体装置10群とその周囲に形成される他の素子の間を電気的に分 離するときに有用である。

### [0048]

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を 限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々 に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによっ て技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものでは ない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであ り、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

#### 【図面の簡単な説明】

## [0049]

- 【図1】実施例の半導体装置の要部断面図を示す。

- 【図2】実施例の半導体装置の製造過程を示す(1)。

- 【図3】実施例の半導体装置の製造過程を示す(2)。

- 【図4】実施例の半導体装置の製造過程を示す(3)。

- 【図5】実施例の半導体装置の製造過程を示す(4)。

- 【図6】実施例の半導体装置の製造過程を示す(5)。

- 【図7】実施例の半導体装置の製造過程を示す(6)。

- 【図8】実施例の半導体装置の製造過程を示す(7)。

- 【図9】実施例の半導体装置の製造過程を示す(8)。

- 【図10】実施例の半導体装置の製造過程を示す(9)。

- 【図11】実施例の半導体装置の製造過程を示す(10)。

- 【図12】実施例の半導体装置の製造過程を示す(11)。

- 【図13】実施例の半導体装置の製造過程を示す(12)。

- 【図14】実施例の半導体装置の他の製造過程を示す(13)。

- 【図15】実施例の半導体装置の他の製造過程を示す(1)。

- 【図16】実施例の半導体装置の他の製造過程を示す(2)。

- 【図17】実施例の半導体装置の他の製造過程を示す(3)。

## 【符号の説明】

#### [0050]

- 22:ドレイン電極

- 24:ドレイン層

- 26:低濃度半導体領域

- 2 8 : p型半導体領域

30:ゲート部

20

10

30

40

3 2 : 不純物拡散抑制膜 3 4 : 第 1 チャネル領域 3 5 : チャネル領域 3 6 : 第 2 チャネル領域

3 8: ゲート絶縁膜 3 9: ゲート電極 5 0: コンタクト電 5 2: p型部分領域 5 4: ソース領域 5 6: コンタクト層

58:ソース電極

10

# 【図1】

# 【図2】

## 【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

# 【図13】

# 【図15】

【図14】

【図16】

【図17】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/50

(72)発明者 島村 清史

茨城県つくば市千現一丁目2番1号 独立行政法人物質・材料研究機構内

(72)発明者 ガルシア ビジョラ エンカルナシオン アントニオ

茨城県つくば市千現一丁目2番1号 独立行政法人物質・材料研究機構内

(72)発明者 北村 健二

茨城県つくば市千現一丁目2番1号 独立行政法人物質・材料研究機構内

(72) 発明者 加地 徹

愛知県愛知郡長久手町大字長湫字横道41番地の1 株式会社豊田中央研究所内

審査官 須賀 亮介

(56)参考文献 特開2004-260140(JP,A)

特開2007-173742(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/28-21/288

H01L 21/44-21/445

H01L 29/40-29/49

H01L 29/872

H01L 29/78

H01L 21/336